Intersil Corporation ACS161MS Datasheet

January 1996

ACS161MS

Radiation Hardened

4-Bit Synchronous Counter

Features

• Devices QML Qualified in Accordance with MIL-PRF-38535

• Detailed Electrical and Screening Requirements are Contained in

SMD# 5962-96706 and Intersil’ QM Plan

• 1.25 Micron Radiation Hardened SOS CMOS

• Total Dose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . >300K RAD (Si)

-10

• Single Event Upset (SEU) Immunity: <1 x 10

Errors/Bit/Day

(Typ)

• SEU LET Threshold . . . . . . . . . . . . . . . . . . . . . . . >100 MEV-cm

11

• Dose Rate Upset . . . . . . . . . . . . . . . . >10

• Dose Rate Survivability. . . . . . . . . . . >10

RAD (Si)/s, 20ns Pulse

12

RAD (Si)/s, 20ns Pulse

2

/mg

• Latch-Up Free Under Any Conditions

o

• Military Temperature Range . . . . . . . . . . . . . . . . . . -55

C to +125oC

• Significant Power Reduction Compared to ALSTTL Logic

• DC Operating Voltage Range . . . . . . . . . . . . . . . . . . . . 4.5V to 5.5V

• Input Logic Levels

- VIL = 30% of VCC Max

- VIH = 70% of VCC Min

• Input Current ≤ 1µA at VOL, VOH

• Fast Propagation Delay. . . . . . . . . . . . . . . . 21ns (Max), 14ns (Typ)

Description

The Intersil ACS161MS is a Radiation Hardened 4-Bit Binary Synchronous

Counter. The

Synchronous Parallel Enable which disables counting and allows data at the

preset inputs (P0 - P3) to load the counter. CP is the positiv e edge clock. TC is

the terminal count or carry output. Both TE and PE must be high for counting

to occur, but are irrele v ant to loading. TE lo w will keep TC lo w.

MR is an active low master reset. SPE is an active low

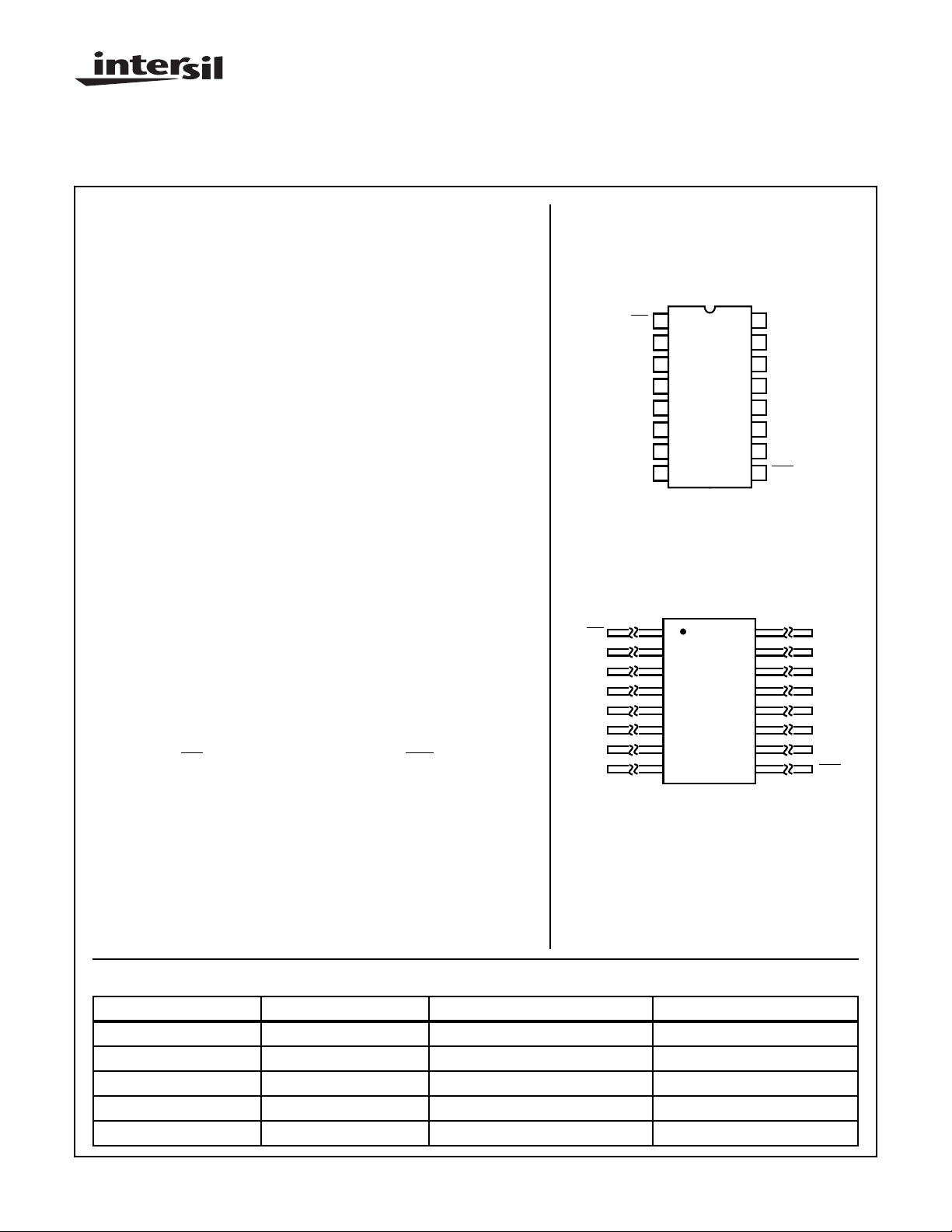

Pinouts

16 PIN CERAMIC DUAL-IN-LINE

MIL-STD-1835, DESIGNATOR CDIP2-T16,

LEAD FINISH C

TOP VIEW

MR

1

CP

2

P0

3

P1

4

P2

5

P3

6

PE

7

GND

8

16 PIN CERAMIC FLATPACK

MIL-STD-1835, DESIGNATOR CDFP4-F16,

LEAD FINISH C

TOP VIEW

MR

CP

P0

P1

P2

P3

PE

GND

116

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

15

14

13

12

11

10

9

VCC

TC

Q0

Q1

Q2

Q3

TE

SPE

VCC

TC

Q0

Q1

Q2

Q3

TE

SPE

The ACS161MS utilizes advanced CMOS/SOS technology to achieve

high-speed operation. This device is a member of a radiation hardened,

high-speed, CMOS/SOS Logic family.

The ACS161MS is supplied in a 16 lead Ceramic Flatpack (K suffix) or a

Ceramic Dual-In-Line Package (D suffix).

Ordering Information

PART NUMBER TEMPERATURE RANGE SCREENING LEVEL PACKAGE

5962F9670601VEC -55oC to +125oC MIL-PRF-38535 Class V 16 Lead SBDIP

5962F9670601VXC -55oC to +125oC MIL-PRF-38535 Class V 16 Lead Ceramic Flatpack

ACS161D/Sample 25oC Sample 16 Lead SBDIP

ACS161K/Sample 25oC Sample 16 Lead Ceramic Flatpack

ACS161HMSR 25oC Die Die

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

1

Spec Number

File Number 3600.1

518818

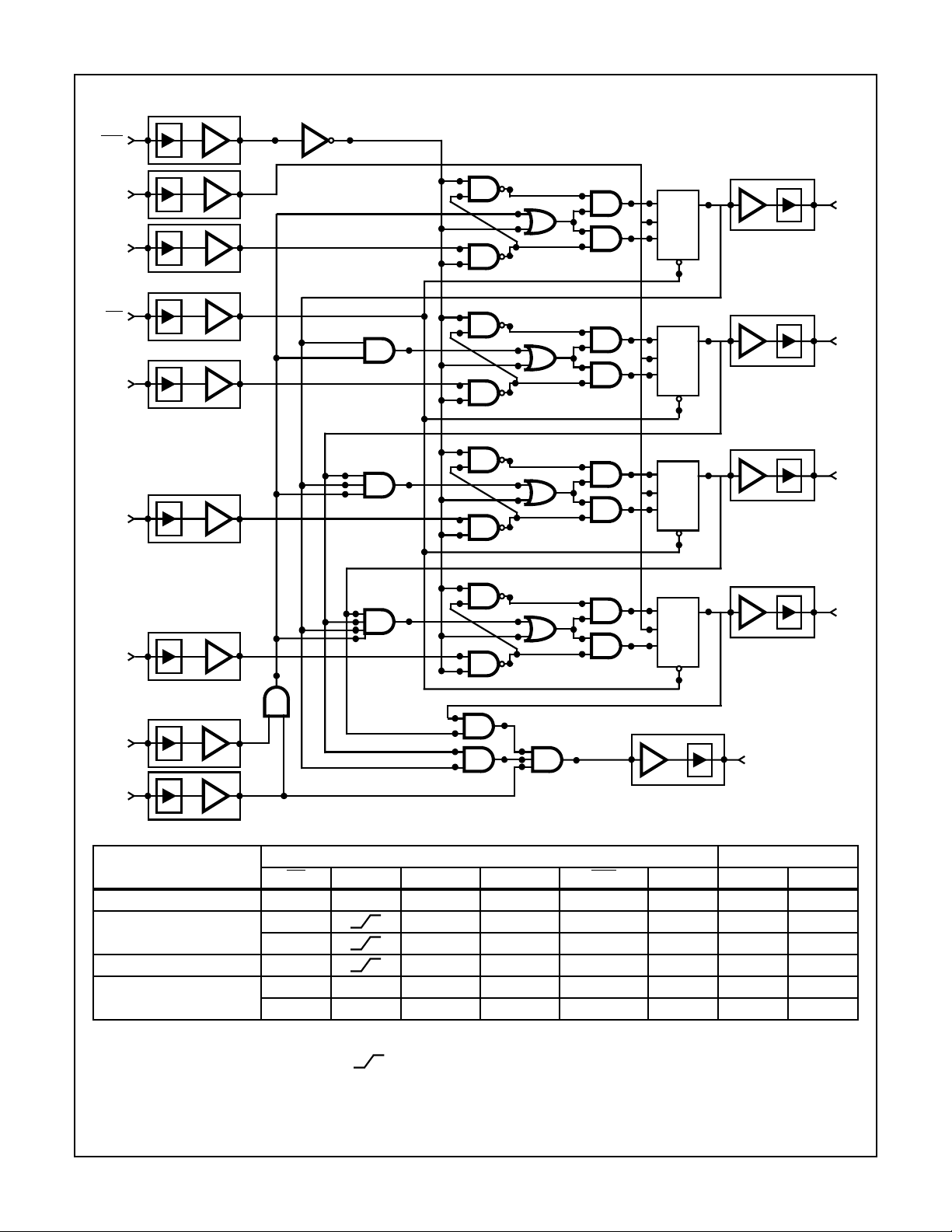

Functional Diagram

SPE

ACS161MS

CP

P0

MR

P1

P2

P3

JQ

CP

K

QN

CD

JQ

CP

K

QN

CD

JQ

CP

K

QN

CD

JQ

CP

K

QN

CD

Q0

Q1

Q2

Q3

PE

TC

TE

TRUTH TABLE

INPUTS OUTPUTS

OPERATING MODE

MR CP PE TE SPE P

N

Q

N

TC

Reset (Clear) L X X X X X L L

Parallel Load H X X I I L L

H X X I h H (Note 1)

Count H h h h (Note 3) X count (Note 1)

Inhibit H X I (Note 2) X h (Note 3) X q

H X X I (Note 2) h (Note 3) X q

N

N

(Note 1)

L

H = High Steady State, L = Low Steady State, h = High voltage level one setup time prior to the Low-to-High clock transition, I = Low voltage level one setup time prior to the Low-to-High clock transition, X = Don’t Care,q = Lower case letters indicate the state of the referenced

output prior to the Low-to-High clock transition, = Low-to-High Transition.

NOTES:

1. The TC output is High when TE is High and the counter is at Terminal Count (HHHH).

2. The High-to-Low transition of PE or TE should only occur while ZCP is High for conventional operation.

3. The Low-to-High transition of SPE should only occur while CP is High for conventional operation.

4. The TC output is High when TE is High and the counter is at Terminal Count (HHHH).

Spec Number 518818

2