Intersil Corporation 82C84A Datasheet

82C84A

March 1997

Features

• Generates the System Clock For CMOS or NMOS

Microprocessors

• Up to 25MHz Operation

• Uses a Parallel Mode Crystal Circuit or External

Frequency Source

• Provides Ready Synchronization

• Generates System Reset Output From Schmitt Trigger

Input

• TTL Compatible Inputs/Outputs

• Very Low Power Consumption

• Single 5V Power Supply

• Operating Temperature Ranges

- C82C84A . . . . . . . . . . . . . . . . . . . . . . . . .0

- I82C84A. . . . . . . . . . . . . . . . . . . . . . . . -40

- M82C84A. . . . . . . . . . . . . . . . . . . . . . -55

o

C to +70oC

o

C to +85oC

o

C to +125oC

CMOS Clock Generator Driver

Description

The Intersil 82C84A is a high performance CMOS Clock Generatordriver which is designed to service the requirements of both CMOS

and NMOS microprocessors such as the 80C86, 80C88, 8086 and

the 8088. The chip contains a crystal controlled oscillator, a divide-bythree counter and complete “Ready” synchronization and reset logic.

Static CMOS circuit design permits operation with an external frequency source from DC to 25MHz. Crystal controlled operation to

25MHz is guaranteed with the use of a parallel, fundamental mode

crystal and two small load capacitors.

All inputs (except X1 and RES) are TTL compatible over temperature and voltage ranges.

Power consumption is a fraction of that of the equivalent bipolar circuits. This speed-power characteristic of CMOS permits the

designer to custom tailor his system design with respect to power

and/or speed requirements.

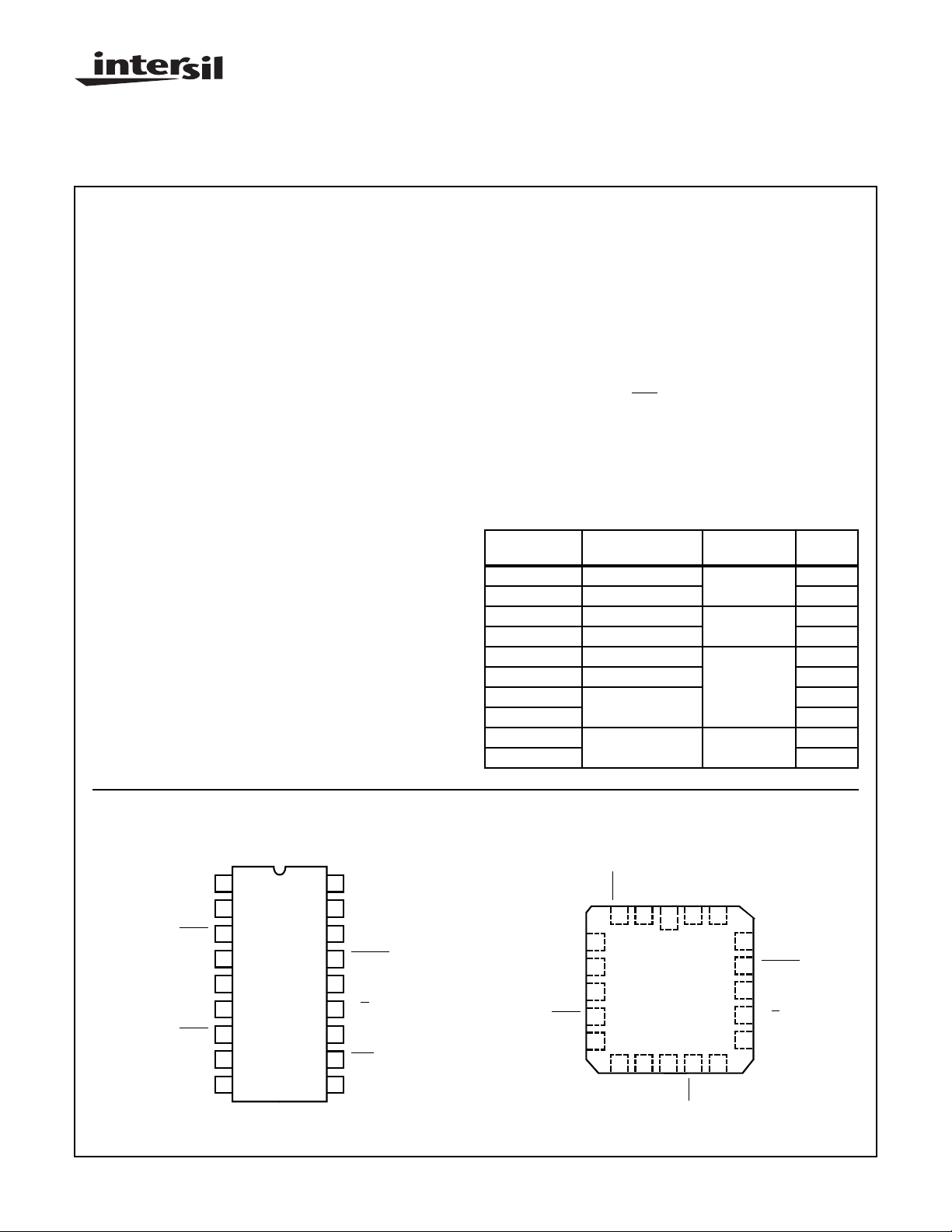

Ordering Information

PART

NUMBER TEMP. RANGE PACKAGE

CP82C84A 0oC to +70oC 18 Ld PDIP E18.3

IP82C84A -40oC to +85oC E18.3

CS82C84A 0oC to +70oC 20 Ld PLCC N20.35

IS82C84A -40oC to +85oC N20.35

CD82C84A 0oC to +70oC 18 Ld CERDIP F18.3

ID82C84A -40oC to +85oC F18.3

MD82C84A/B -55oC to +125oC F18.3

8406801VA SMD# F18.3

MR82C84A/B -55oC to +125oC 20 Pad CLCC J20.A

84068012A SMD# J20.A

PKG.

NO.

Pinouts

82C84A (PDIP, CERDIP)

TOP VIEW

PCLK

AEN1

RDY1

RDY2

AEN2

CLK

GND

1

2

3

4

5

6

7

8

9

| Copyright © Intersil Corporation 1999

CSYNC

READY

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

18

17

16

15

14

13

12

11

10

V

CC

X1

X2

ASYNC

EFI

C

F/

OSC

RES

RESET

RDY1

READY

RDY2

AEN2

4-287

82C84A (PLCC, CLCC)

TOP VIEW

AEN1

3212019

4

5

6

7

8

NC

9101112

CLK

PCLK

GND

CSYNC

V

RESET

CC

X1

18

X2

17

ASYNC

EFI

16

15

C

F/

14

NC

13

RES

OSC

File Number 2974.1

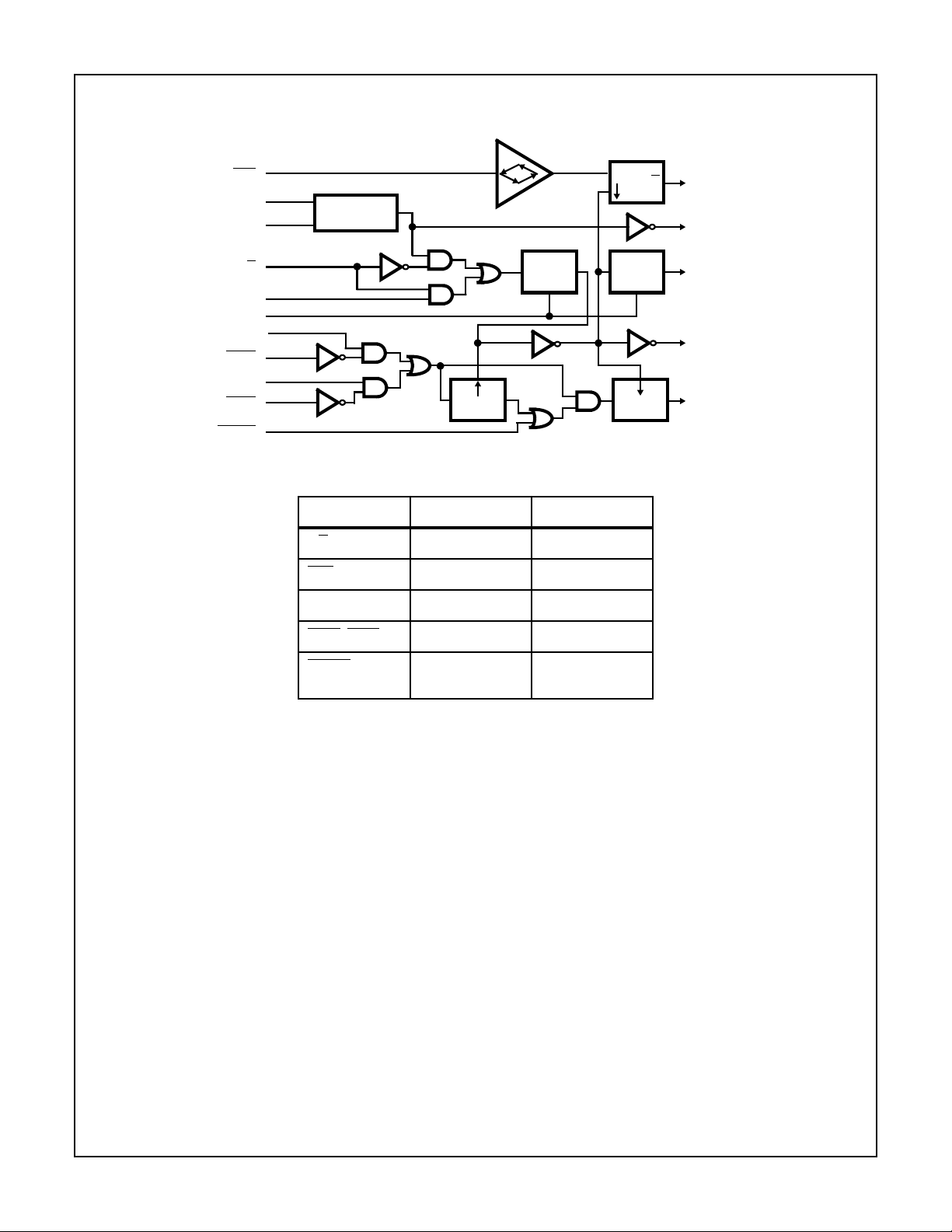

Functional Diagram

82C84A

RES

X1

X2

F/

EF1

CSYNC

RDY1

AEN1

RDY2

AEN2

ASYNC

11

17

16

13

C

14

1

4

3

6

7

15

XTAL

OSCILLATOR

CK

DQ

FF1

÷ 3

SYNC

D

CK

SYNC

CK

DQ

÷ 2

FF2

10

Q

RESET

12

OSC

2

PCLK

8

CLK

5

READY

CONTROL PIN LOGICAL 1 LOGICAL 0

F/C External Clock Crystal Drive

RES Normal Reset

RDY1, RDY2 Bus Ready Bus Not Ready

AEN1, AEN2 Address Disabled Address Enable

ASYNC 1 Stage Ready

Synchronization

2 Stage Ready

Synchronization

4-288

82C84A

Pin Description

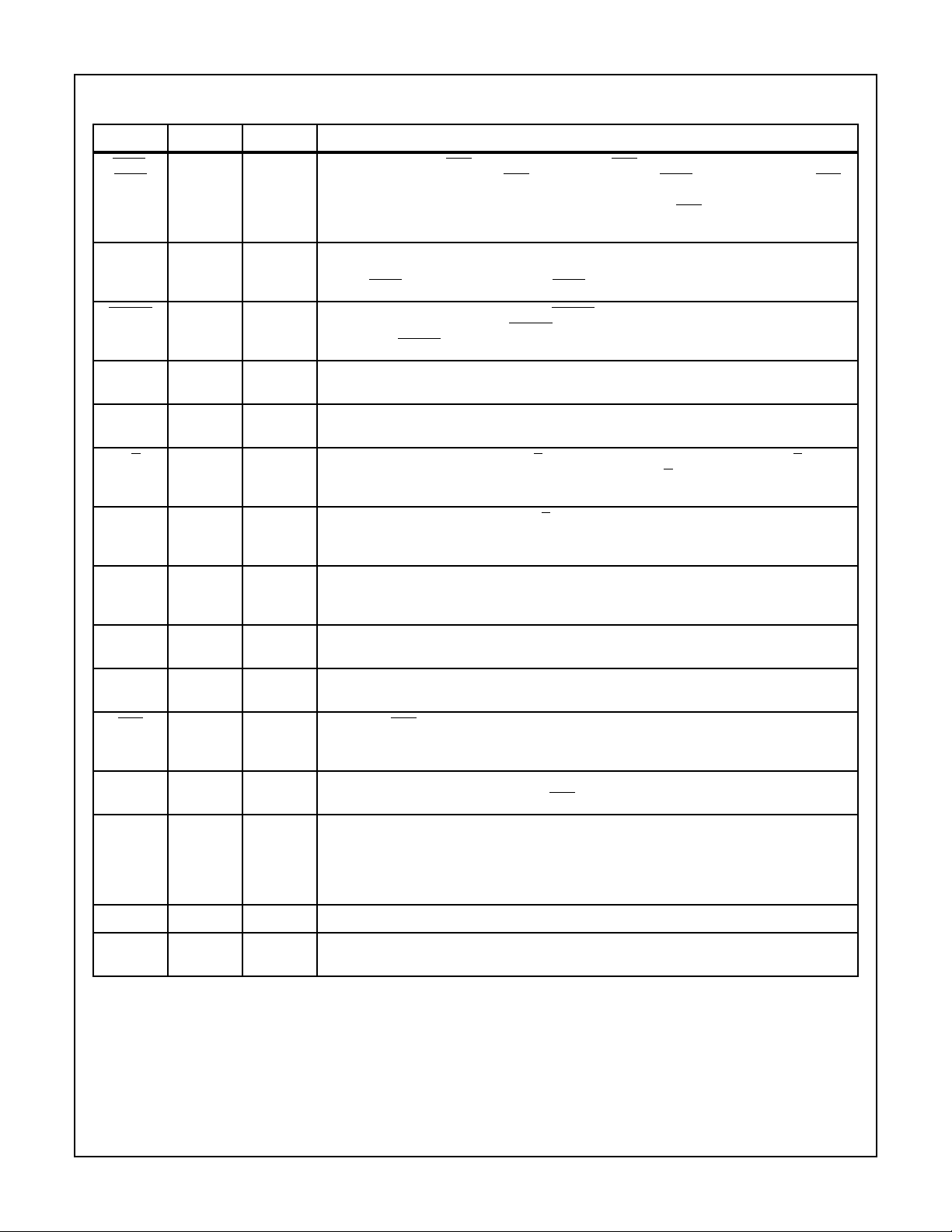

SYMBOL NUMBER TYPE DESCRIPTION

AEN1,

AEN2

RDY1,

RDY2

ASYNC 15 I READY SYNCHRONIZATION SELECT: ASYNC is an input which defines the synchronization

READY 5 O READY: READY is an active HIGH signal which is the synchronized RDY signal input. READY

X1, X2 17, 16 I O CRYSTAL IN: X1 and X2 are the pins to which a crystal is attached. The crystal frequency is 3

F/C 13 I FREQUENCY/CRYSTAL SELECT: F/C is a strapping option. When strapped LOW. F/C permits

EFI 14 I EXTERNAL FREQUENCY IN: When F/C is strapped HIGH, CLK is generated from the input fre-

CLK 8 O PROCESSOR CLOCK: CLK is the clock output used by the processor and all devices which di-

3, 7 I ADDRESS ENABLE: AEN is an active LOW signal. AEN serves to qualify its respective Bus

Ready Signal (RDY1 or RDY2). AEN1 validates RDY1 while AEN2 validates RDY2. Two AEN

signal inputs are useful in system configurations which permit the processor to access two MultiMaster System Busses. In non-Multi-Master configurations, the AEN signal inputs are tied true

(LOW).

4, 6 I BUS READY (Transfer Complete). RDY is an active HIGH signal which is an indication from a

device located on the system data bus that data has been received, or is available RDY1 is qualified by AEN1 while RDY2 is qualified by AEN2.

mode of the READY logic. When ASYNC is low, two stages of READY synchronization are provided. When ASYNC is left open or HIGH, a single stage of READY synchronization is provided.

is cleared after the guaranteed hold time to the processor has been met.

times the desired processor clock frequency, (Note 1).

the processor’s clock to be generated by the crystal. When F/C is strapped HIGH, CLK is generated for the EFI input, (Note 1).

quency appearing on this pin. The input signal is a square wave 3 times the frequency of the desired CLK output.

rectly connect to the processor’s local bus. CLK has an output frequency which is 1/3 of the crystal or EFI input frequency and a 1/3 duty cycle.

PCLK 2 O PERIPHERAL CLOCK: PCLK is a peripheral clock signal whose output frequency is 1/2 that of

CLK and has a 50% duty cycle.

OSC 12 O OSCILLATOR OUTPUT: OSC is the output of the internal oscillator circuitry. Its frequency is

equal to that of the crystal.

RES 11 I RESET IN: RES is an active LOW signal which is used to generate RESET. The 82C84A pro-

vides a Schmitt trigger input so that an RC connection can be used to establish the power-up

reset of proper duration.

RESET 10 O RESET: RESET is an active HIGH signal which is used to reset the 80C86 family processors. Its

timing characteristics are determined by RES.

CSYNC 1 I CLOCK SYNCHRONIZATION: CSYNC is an active HIGH signal which allows multiple 82C84As

to be synchronized to provide clocks that are in phase. When CSYNC is HIGH the internal

counters are reset. When CSYNC goes LOW the internal counters are allowed to resume counting. CSYNC needs to be externally synchronized to EFI. When using the internal oscillator

CSYNC should be hardwired to ground.

GND 9 Ground

V

CC

NOTE:

1. If the crystal inputs are not used X1 must be tied to VCC or GND and X2 should be left open.

18 VCC: The +5V power supply pin. A 0.1µF capacitor between VCC and GND is recommended for

decoupling.

4-289

Loading...

Loading...