Intersil Corporation 82C284 Datasheet

March 1997

82C284

Clock Generator and Ready Interface

for 80C286 Processors

Features

• Generates System Clock for 80C286 Processors

• Generates System Reset Output from Schmitt

Trigger Input

- Improved Hysteresis

• Uses Crystal or External Signal for Frequency Source

• Dynamically Switchable between Two Input

Frequencies

• Provides Local

READY and MULTIBUSREADY

Synchronization

• Static CMOS Technology

• Single +5V Power Supply

• Available in 18 Lead CerDIP Package

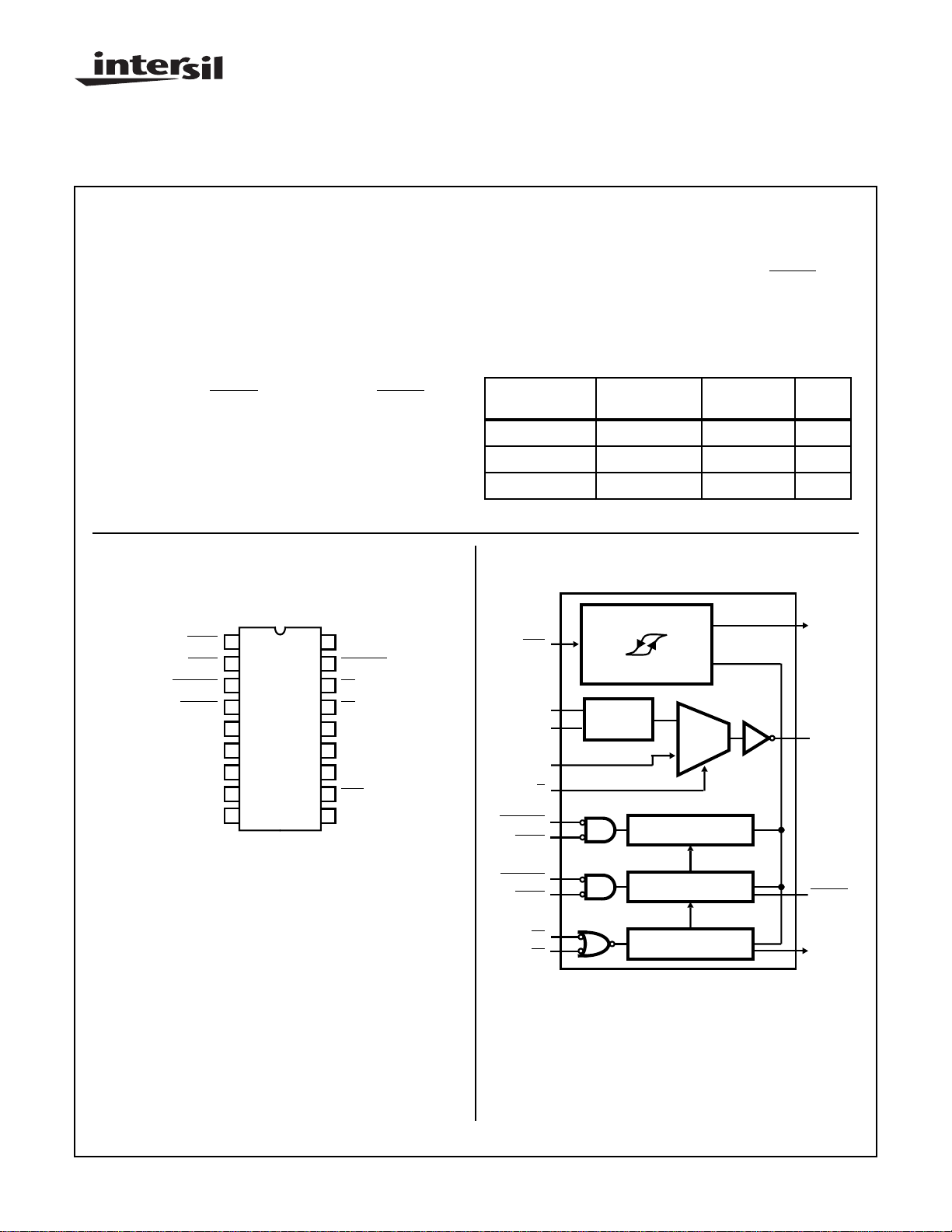

Pinout

82C284 (CERDIP)

TOP VIEW

1

ARDY

SRDY

SRDYEN

READY

EFI

F/C

X1

X2

GND

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

VCC

ARDYEN

S1

S0

NC

PCLK

RESET

RES

CLK

Description

The Intersil 82C284 is a clock generator/driver which

provides clock signals for 80C286 processors and support

components. It also contains logic to supply

READY to the

CPU from either asynchronous or synchronous sources and

synchronous RESET from an asynchronous input with

hysteresis.

Ordering Information

PKG.

PART NUMBER TEMP. RANGE PACKAGE

CD82C284-12 0oC to +70oC 18 Ld CERDIP F18.3

ID82C284-10 -40oC to +85oC 18 Ld CERDIP F18.3

ID82C284-12 -40oC to +85oC 18 Ld CERDIP F18.3

NO.

Functional Diagram

RES

X1

X2

EFI

F/

ARDYEN

ARDY

RESET

SYNCHRONIZER

XTAL

OSC

MUX

C

SYNCHRONIZER

RESET

CLK

SRDYEN

SRDY

S1

S0

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

MULTIBUS

is a patented Intel bus.

| Copyright © Intersil Corporation 1999

1

READY LOGIC

PCLK GENERATOR

READY

PCLK

File Number 2966.1

82C284

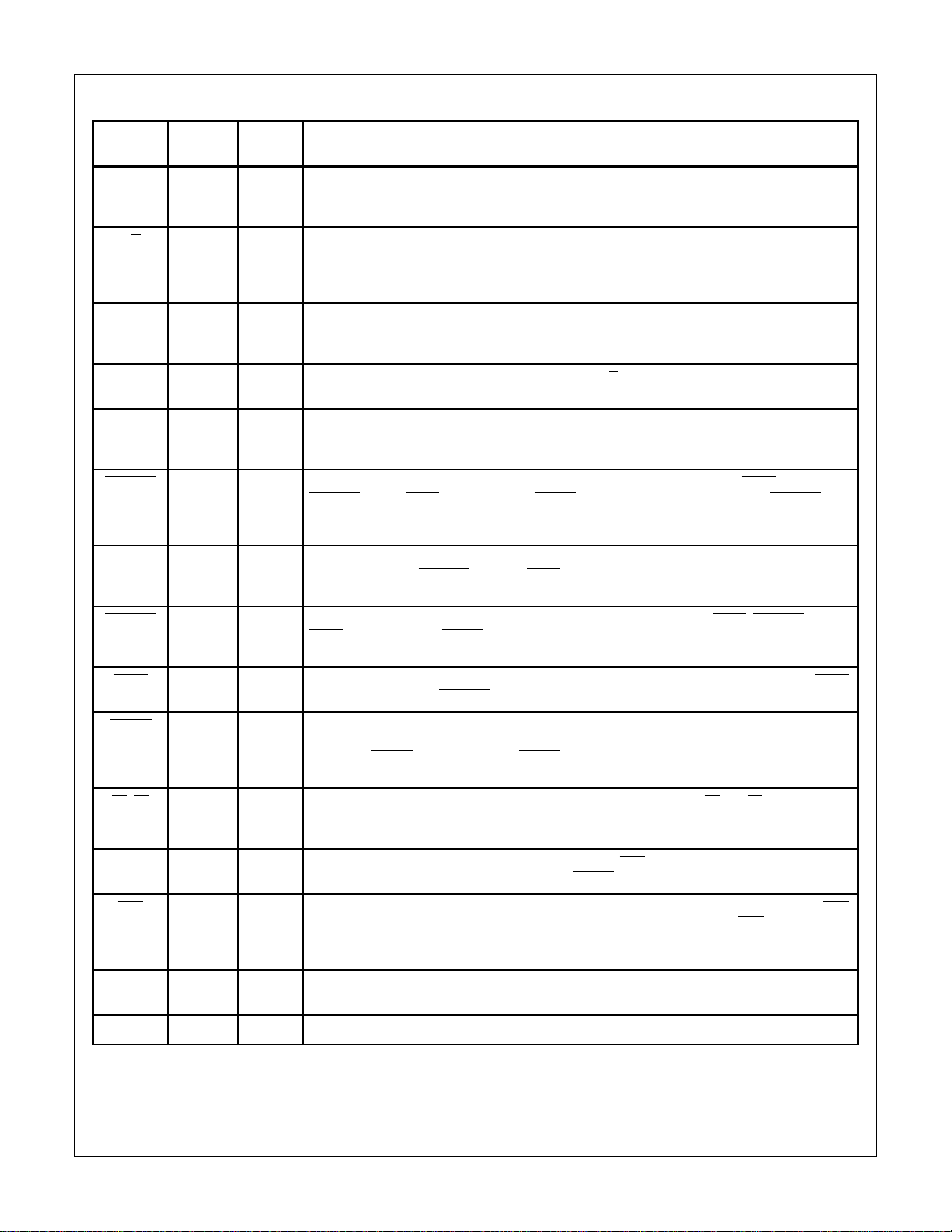

Pin Description

PIN

SYMBOL NUMBER TYPE DESCRIPTION

CLK 10 O SYSTEM CLOCK: the signal used by the processor and support devices which must be synchro-

C 6 I FREQUENCY/CRYSTAL SELECT: this pin selects the source for the CLK output. When there is a

F/

X1, X2 7, 8 I CRYSTAL IN: the pin stop which parallel resonant, fundamental mode crystal is attached for the in-

EFI 5 I EXTERNAL FREQUENCY IN: drives CLK when the F/C input is HIGH. The EFI input frequency

PCLK 13 O PERIPHERAL CLOCK: the output which provides a 50% duty cycle clock with one-half the frequen-

ARDYEN 17 I ASYNCHRONOUS READY ENABLE: an active LOW input which qualifies the ARDY input.

The following pin function descriptions are for the 82C284 clock generator.

nous with the processor. The frequency of the CLK output has twice the desired internal processor

clock frequency. CLK can drive both TTL and CMOS level inputs.

LOW level on this input, the internal crystal oscillator drives CLK. When there is a HIGH level on F/C,

the EFI input drives the CLK input. This pin can be dynamically switched, which allows changing the

processor CLK frequency while running for low-power operation, etc.

ternal oscillator. When F/C is LOW, the internal oscillator will drive the CLK output at the crystal frequency. The crystal frequency must be twice the desired internal processor clock frequency.

must be twice the desired internal processor clock frequency.

cy of CLK. PCLK will be in phase with the internal processor clock following the first bus cycle after

the processor has been reset.

ARDYEN selects ARDY as the source of READY for the current bus cycle. Inputs to ARDYEN may

be applied asynchronously to CLK. Setup and hold times are given to assure a guaranteed response

to synchronous outputs.

ARDY 1 I ASYNCHRONOUS READY: an active LOW input used to terminate the current bus cycle. TheARD Y

input is qualified by ARDYEN. Inputs to ARDY may be applied asynchronously to CLK. Setup and

hold times are given to assure a guaranteed response to synchronous outputs.

SRDYEN 3 I SYNCHRONOUS READY ENABLE: an active LOW input which qualifies SRDY. SRDYEN selects

SRDY as the source for READY to the CPU for the current bus cycle. Setup and hold time must be

satisfied for proper operation.

SRDY 2 I SYNCHRONOUS READY: an active LOW input used to terminate the current bus cycle. The SRDY

input is qualified by the SRDYEN input. Setup and hold time must be satisfied for proper operation.

READY 4 O READY: an active LOW output which signals to the processor that the current bus cycle is to be com-

pleted. The SRDYSRDYEN, ARDY,ARDYEN, S1, S0, and RES inputs control READ Y as explained

later in the READY generator section. READY is an open drain output requiring an external pull-up

resistor.

S0, S1 15,16 I STATUS: these inputs prepare the 82C284 for a subsequent bus cycle. S0 and S1 synchronize

PCLK to the internal processor clock and control READY. Setup and hold times must be satisfied for

proper operation

RESET 12 O RESET: an active HIGH output which is derived from the RES input RESET is used to force the sys-

tem into an initial state. When RESET is active, READY will be active (LOW).

RES 11 I RESET IN: an active LOW input which generates the system reset signal (RESET). Signals to RES

may be applied asynchronously to CLK. A Schmitt trigger input is provided on RES, so that an RC

circuit can be used to provide a time delay. Setup and hold times are given to assure a guaranteed

response to synchronous inputs.

V

CC

18 SYSTEM POWER: The +5V Power Supply Pin. A 0.1µF capacitor between VCC and GND is recom-

mended for decoupling.

GND 9 SYSTEM GROUND: 0V

2

82C284

Functional Description

Introduction

The 82C284 generates the clock, ready, and reset signals

required for 80C286 processors and support components.

The 82C284 is packaged in an 18-pin DIP and contains a

crystal controlled oscillator, clock generator, per ipheral clock

generator, MULTIBUS® ready synchronization logic, and

system reset generation logic.

Clock Generator

The CLK output provides the basic timing control for an

80C286 system. CLK has output characteristics sufficient to

drive CMOS devices. CLK is generated by either an internal

crystal oscillator, or an external source as selected by the

F/

C input pin. When F/C is LOW, the cr ystal oscillator dr ives

the CLK output. When F/

CLK output.

The F/

C pin on the Intersil 82C284 is dynamically switchable. This allows the CLK frequency to the processor to be

changed from one frequency to another in a running system.

With this feature, a system can be designed which operates

at maximum speed when needed, and then dynamically

switched to a lower frequency to implement a low-power

mode. The lower frequency can be anything down to, but

excluding, DC. The following 3 conditions apply when

dynamically switching the F/

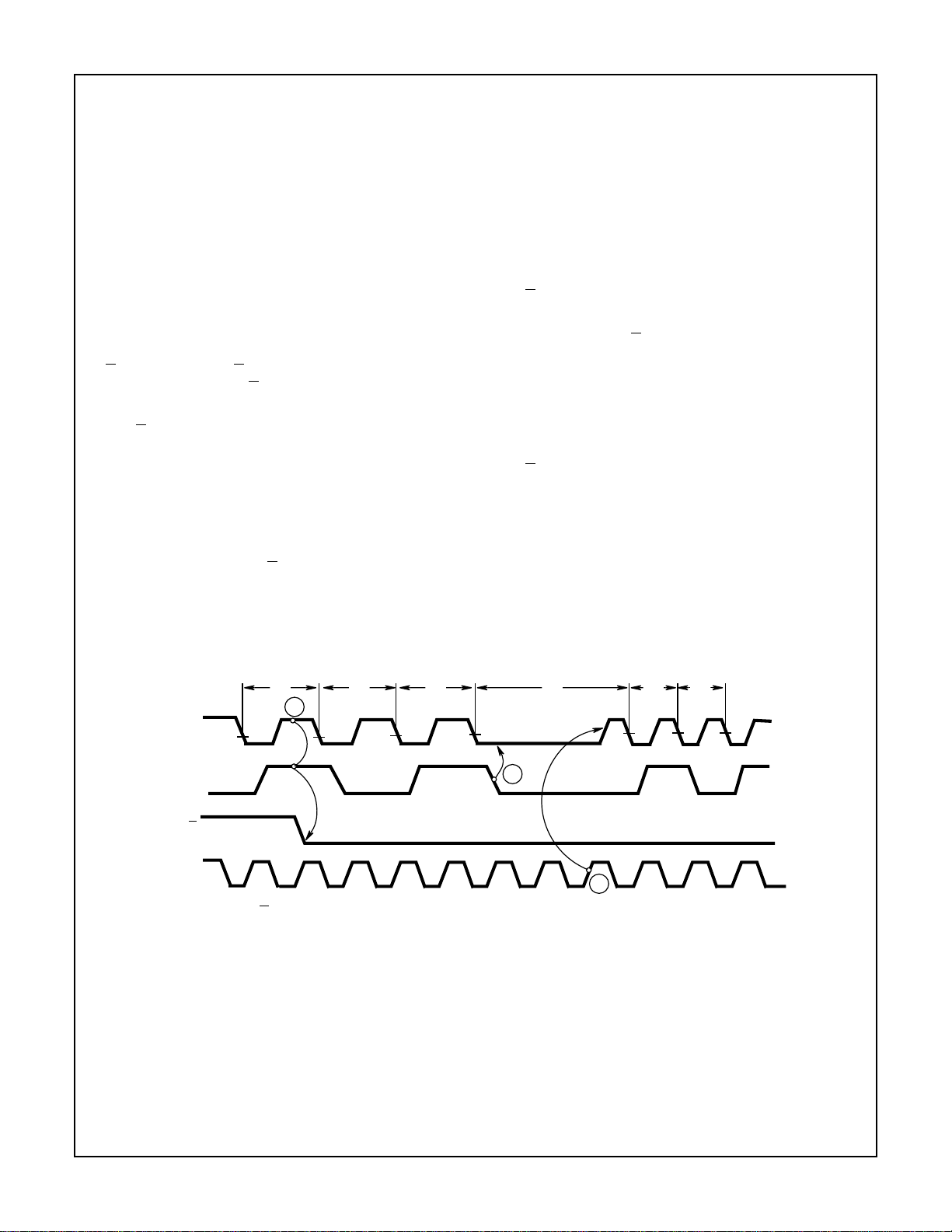

1) The CLK is stretched in the low portion of the φ2 phase

of its cycle during transition from one CLK frequency to

the other (see Waveforms).

C is HIGH, the EFI input drives the

C pin (see Figure 1):

2) When switching CLK frequency sources, there is a maximum transition latency of 2.5 clock cycles of the frequency being switched to, from the time CLK freezes

low, until CLK restarts at the new frequency (see Waveforms).

3) The maximum latency from the time F/C is dynamically

switched, to the time CLK freezes low, is 4 CLK cycles

(see Waveforms).

The following steps describe the sequence of events that

transpire when F/C is dynamically switched:

A) F/

C switched from high (using EFI input) to low (using

the crystal input X1 - see Figure 1A).

1) The state of F/

C is sampled when both CLK and

PCLK are high until a change is detected.

2) On the second following falling edge of PCLK, CLK is

frozen low.

3) CLK restarts at the crystal frequency on the rising

edge of Xl, after the second falling edge of X1.

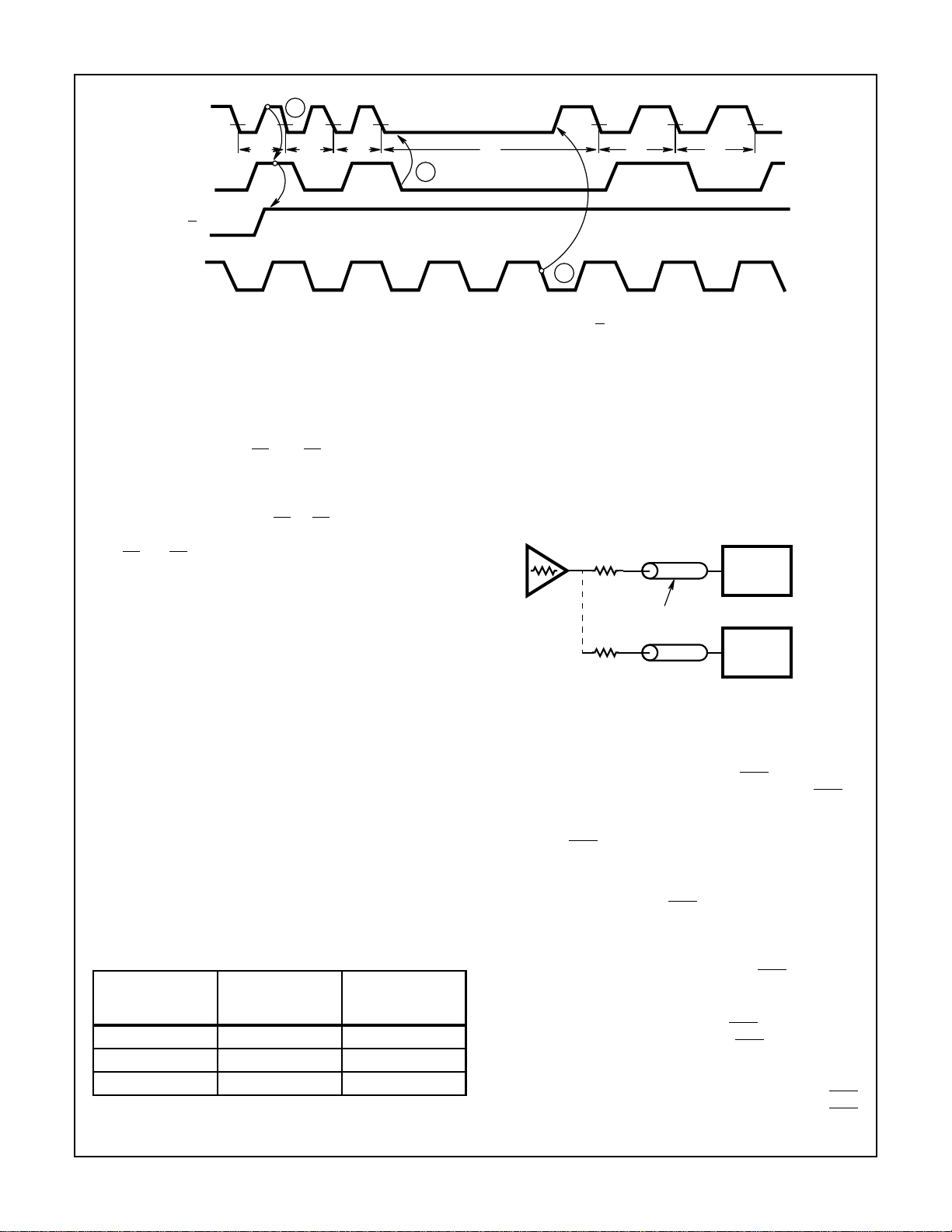

B) F/

C switched from low (using the crystal input Xl) to high

(using the EFI input - see Figure 1B).

1) The state of F/C is sampled when both CLK and

PCLK are high until a change is detected.

2) On the second following falling edge of PCLK, CLK is

frozen low.

3) CLK restarts at the EFI input frequency on the falling

edge of EFl after the second rising edge of EFI.

φ2φ1φ2φ1φ2φ1

1

CLK

PCLK

C

F/

X1

FIGURE 1A. F/C SWITCHED FROM HIGH (USING EFI INPUT) TO LOW (USING THE CRYSTAL INPUT X1)

2

3

3

82C284

CLK

PCLK

F/C

EFI

FIGURE 1B. F/C SWITCHED FROM LOW (USING THE CRYSTAL INPUT X1) TO HIGH (USING THE EFI INPUT)

1

φ1

φ2 φ1 φ2 φ1 φ2

2

FIGURE 1. DYNAMICALLY SWITCHING THE F/C PIN

The 82C284 provides a second clock output, PCLK, for peripheral devices. PCLK is CLK divided by two. PCLK has a duty

cycle of 50% and CMOS output drive characteristics. PCLK is

normally synchronized to the internal processor clock.

After reset, the PCLK signal may be out of phase with the internal processor clock. The

S1 and S0 signals of the first bus

cycle are used to synchronize PCLK to the internal processor

clock. The phase of the PCLK output changes by extending its

HIGH time beyond one system clock (see wa v ef orms). PCLK is

forced HIGH whenever either

S0 or S1 were active (LOW) for

the two previous CLK cycles. PCLK continues to oscillate when

both

S0 and S1 are HIGH.

Since the phase of the internal processor clock will not change

except during reset, the phase of PCLK will not change except

during the first bus cycle after reset.

Oscillator

The oscillator circuit of the 82C284 is a linear Pierce oscillator

which requires an external parallel resonant, fundamental

mode, crystal. The output of the oscillator is internally buffered.

The crystal frequency chosen should be twice the required

internal processor clock frequency. The cr ystal should have a

typical load capacitance of 32pF.

X1 and X2 are the oscillator crystal connections. For stable

operation of the oscillator, two loading capacitors are recommended, as shown in Table 1. The sum of the board capacitance and loading capacitance should equal the values shown.

It is advisable to limit stray board capacitances (not including

the effect of the loading capacitors or crystal capacitance) to

less than 10pF between the X1 and X2 pins. Decouple V

CC

and GND as close to the 82C284 as possible with a 0.1µF polycarbonate capacitor.

TABLE 1. 82C284 CRYSTAL LOADING CAPACITANCE VALUES

Cl

CRYSTAL

FREQUENCY

1MHz to 8MHz 60pF 40pF

8MHz to 20MHz 25pF 15pF

20MHz to 25MHz 15pF 15pF

CAPACITANCE

(PIN 7)

C2

CAPACITANCE

(PIN 8)

3

CLK Termination

Due to the CLK output having a very fast rise and fall time , it is

recommended to properly terminate the CLK line at frequencies above 10MHz to avoid signal reflections and ringing. Termination is accomplished by inserting a small resistor

(typically 10-74Ω) in series with the output, as shown in Figure

2. This is known as series termination. The resistor value plus

the circuit output impedance (approximately 25Ω) should be

made equal to the impedance of the transmission line.

CLK

OUT

RO ≈ 25

R

Z

TRANSMISSION

LINE

Z

FIGURE 2. SERIES TERMINATION

CLOSELY

PLACED

LOADS

CLOSELY

PLACED

LOADS

Reset Operation

The reset logic provides the RESET output to force the system into a known, initial state. When the

(LOW), the RESET output becomes active (HIGH),

RES input is active

RES is

synchronized internally at the falling edge of CLK before

generating the RESET output (see wavefor ms). Synchronization of the

RES input introduces a one or two CLK delay

before affecting the RESET Output.

At power up, a system does not ha ve a stable V

To prevent spurious activity,

V

and CLK stabilize at their operating values. 80C286

CC

RES should be asserted until

and CLK.

CC

processors and support components also require their

RESET inputs be HIGH a minimum of 16 CLK cycles. An RC

network, as shown in Figure 3, will keep

RES LOW long

enough to satisfy both needs.

A Schmitt trigger input with hysteresis on

transition of RESET with an RC circuit on

RES assures a single

RES. The hysteresis

separates the input voltage level at which the circuit output

switches from HIGH to LOW from the input voltage level at

which the circuit output switches from LOW to HIGH. The

HIGH to LOW input transition voltage is lower than the

RES

RES

4

Loading...

Loading...