Intersil Corporation 80C86 Datasheet

80C86

[ /Title

(80C86

)

/Subject

(CMO

S 16Bit

Microprocessor)

/Autho

r ()

/Keywords

(Intersil

Corporation,

Intersil

Corporation,

16 Bit

uP,

microprocessor,

8086,

PC)

/Cre-

March 1997

Features

• Compatible with NMOS 8086

• Completely Static CMOS Design

- DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5MHz (80C86)

- DC . . . . . . . . . . . . . . . . . . . . . . . . . . . .8MHz (80C86-2)

• Low Power Operation

- lCCSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500µA Max

- ICCOP . . . . . . . . . . . . . . . . . . . . . . . . . 10mA/MHz Typ

• 1MByte of Direct Memory Addressing Capability

• 24 Operand Addressing Modes

• Bit, Byte, Word and Block Move Operations

• 8-Bit and 16-Bit Signed/Unsigned Arithmetic

- Binary, or Decimal

- Multiply and Divide

• Wide Operating Temperature Range

- C80C86 . . . . . . . . . . . . . . . . . . . . . . . . . .0

- l80C86 . . . . . . . . . . . . . . . . . . . . . . . . . -40

- M80C86 . . . . . . . . . . . . . . . . . . . . . . . -55

o

o

o

C to +125oC

C to +70oC

C to +85oC

CMOS 16-Bit Microprocessor

Description

The Intersil 80C86 high performance 16-bit CMOS CPU is

manufactured using a self-aligned silicon gate CMOS process (Scaled SAJI IV). Two modes of operation, minimum f or

small systems and maximum for larger applications such as

multiprocessing, allow user configuration to achieve the

highest performance level. Full TTL compatibility (with the

exception of CLOCK) and industry standard operation allow

use of existing NMOS 8086 hardware and software designs.

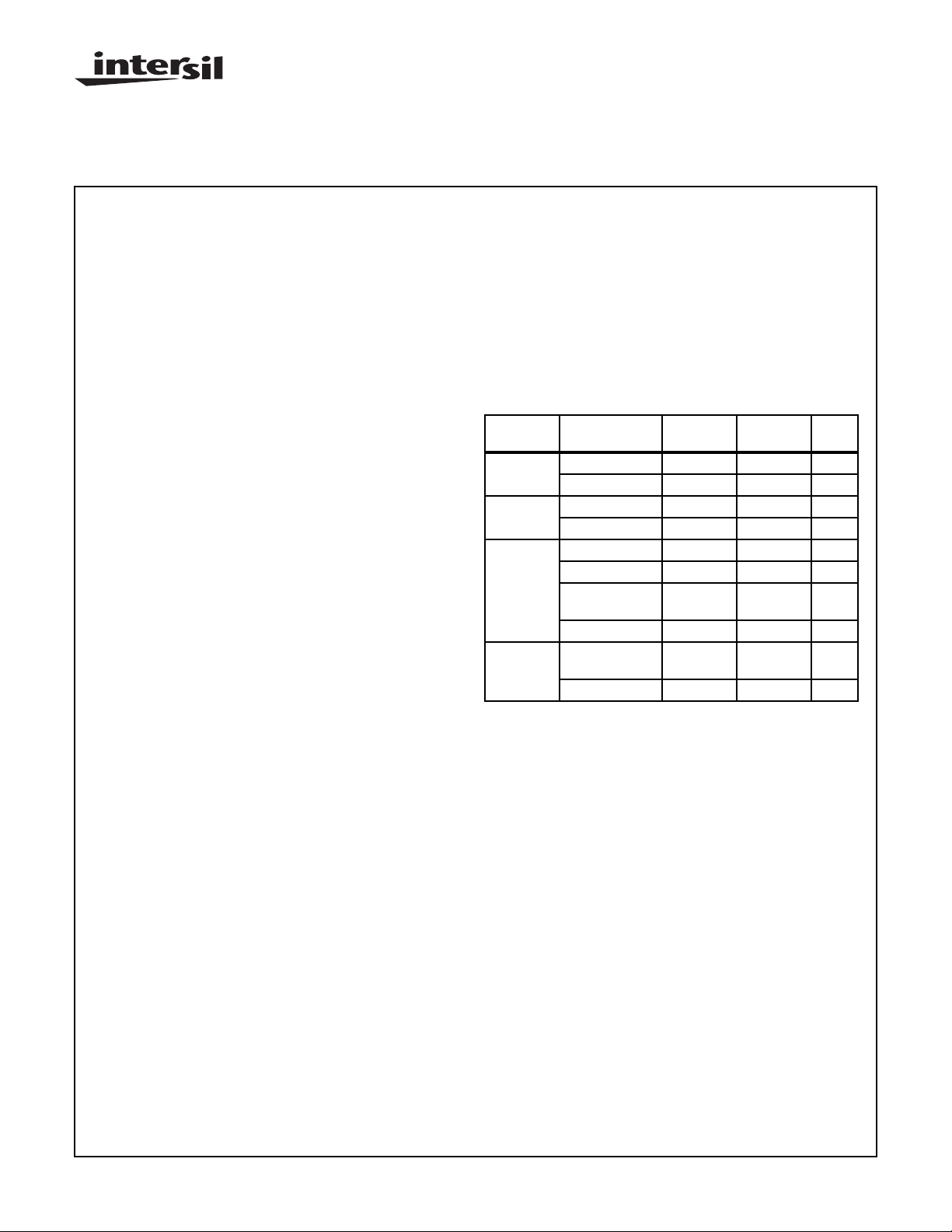

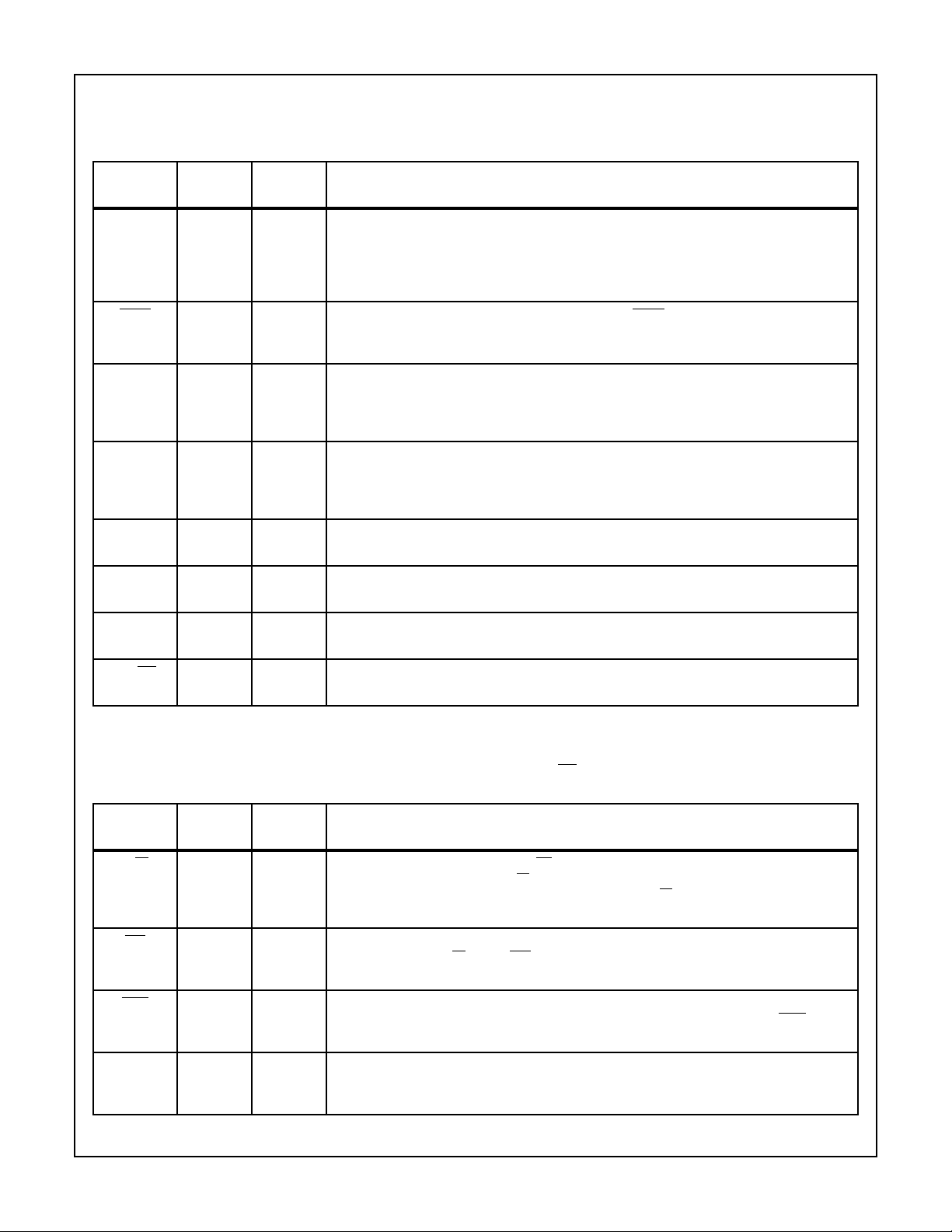

Ordering Information

PKG.

PACKAGE TEMP. RANGE 5MHz 8MHz

PDIP 0oC to +70oC CP80C86 CP80C86-2 E40.6

-40oC to +85oC lP80C86 IP80C86-2 E40.6

PLCC 0oC to +70oC CS80C86 CS80C86-2 N44.65

-40oC to +85oC lS80C86 IS80C86-2 N44.65

CERDIP 0oC to +70oC CD80C86 CD80C86-2 F40.6

-40oC to +85oC ID80C86 ID80C86-2 F40.6

-55oC to +125oC MD80C86/B MD80C862/B

SMD# -55oC to +125oC 8405201QA 8405202QA F40.6

CLCC -55oC to +125oC MR80C86/B MR80C86-

2/B

SMD# -55oC to +125oC 8405201XA 8405202XA J44.A

NO.

F40.6

J44.A

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

3-141

File Number

2957.1

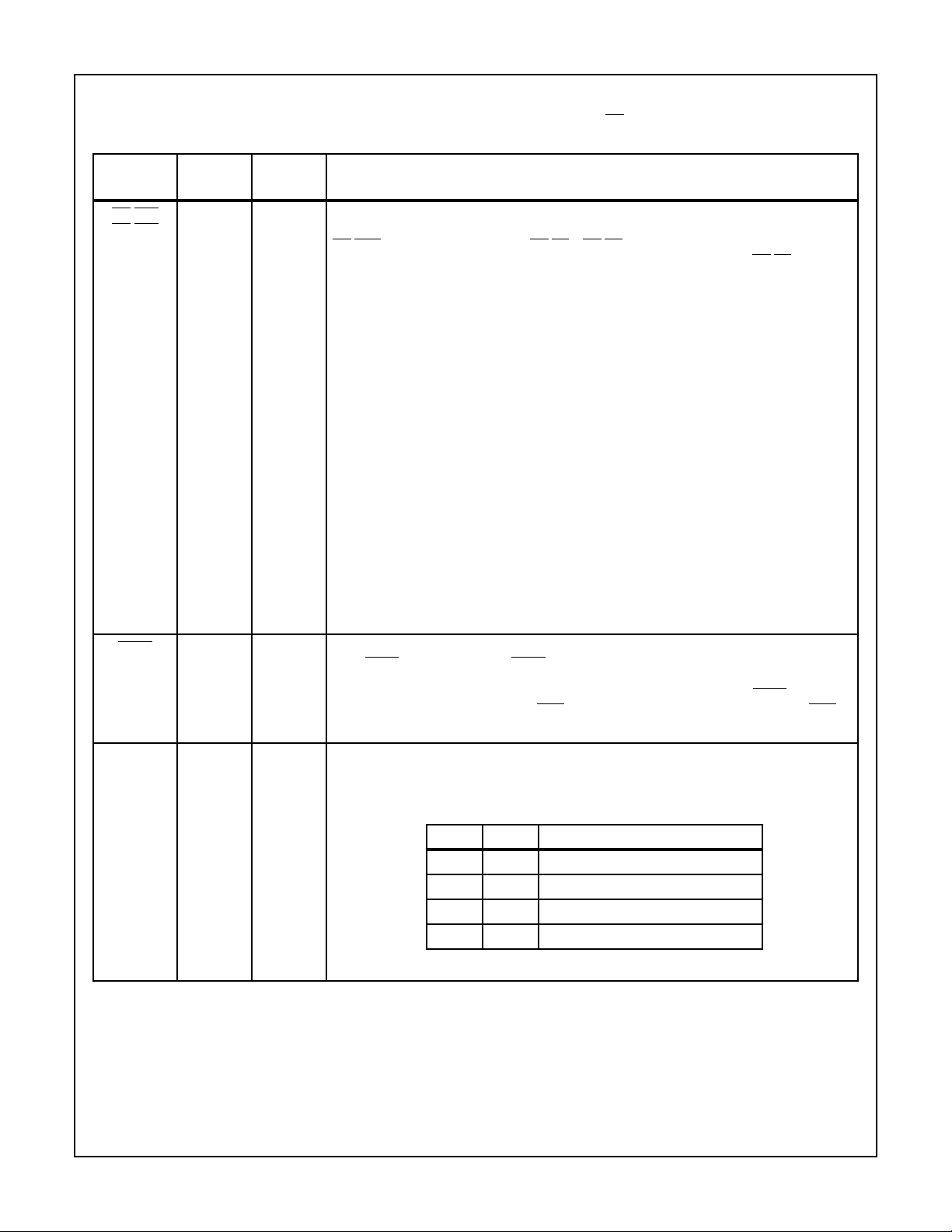

Pinouts

GND

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NMI

INTR

CLK

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

80C8680C86

80C86 (DIP)

TOP VIEW

MAX (MIN)

40

V

CC

AD15

39

A16/S3

38

A17/S4

37

A18/S5

36

A19/S6

35

BHE/S7

34

MX

MN/

33

RD

32

RQ/GT0

31

RQ/GT1

30

LOCK

29

S2

28

S1

27

S0

26

QS0

25

QS1

24

TEST

23

READY

22

RESET

21

(HOLD)

(HLDA)

(WR)

(M/IO)

(DT/R))

(DEN)

(ALE)

(INTA)

MAX MODE

80C86

MIN MODE

80C86

AD10 AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

6 3

7

8

9

10

11

12

13

14

15

16

17

80C86 (PLCC, CLCC)

TOP VIEW

AD13

AD13

4

INTR

AD14

AD14

25

CLK

GND

GND

GND

AD11 AD11

AD12

AD12

NMI

CC

NC

V

AD15

A16/S3

A17/S4

A18/S5

CC

NC

V

AD15

A16/S3

A17/S4

A18/S5

44

1

NC

RESET

40414243

39

NC NC

BHE/S7

MX

RD

RQ/GT0

RQ/GT1

IO

R

MAX MODE

80C86

A19/S6

MN/

MX

RD

LOCK

S2

S1

S0

A19/S6

38

BHE/S7

37

MN/

36

35

HOLD

34

HLDA

33

WR

32

M/

31

DT/

30

DEN

29

2827262524232221201918

MIN MODE

80C86

ALE

INTA

TEST

READY

NC NC

NMI

INTR

CLK

NC

GND

3-142

RESET

READY

TEST

QS1

QS0

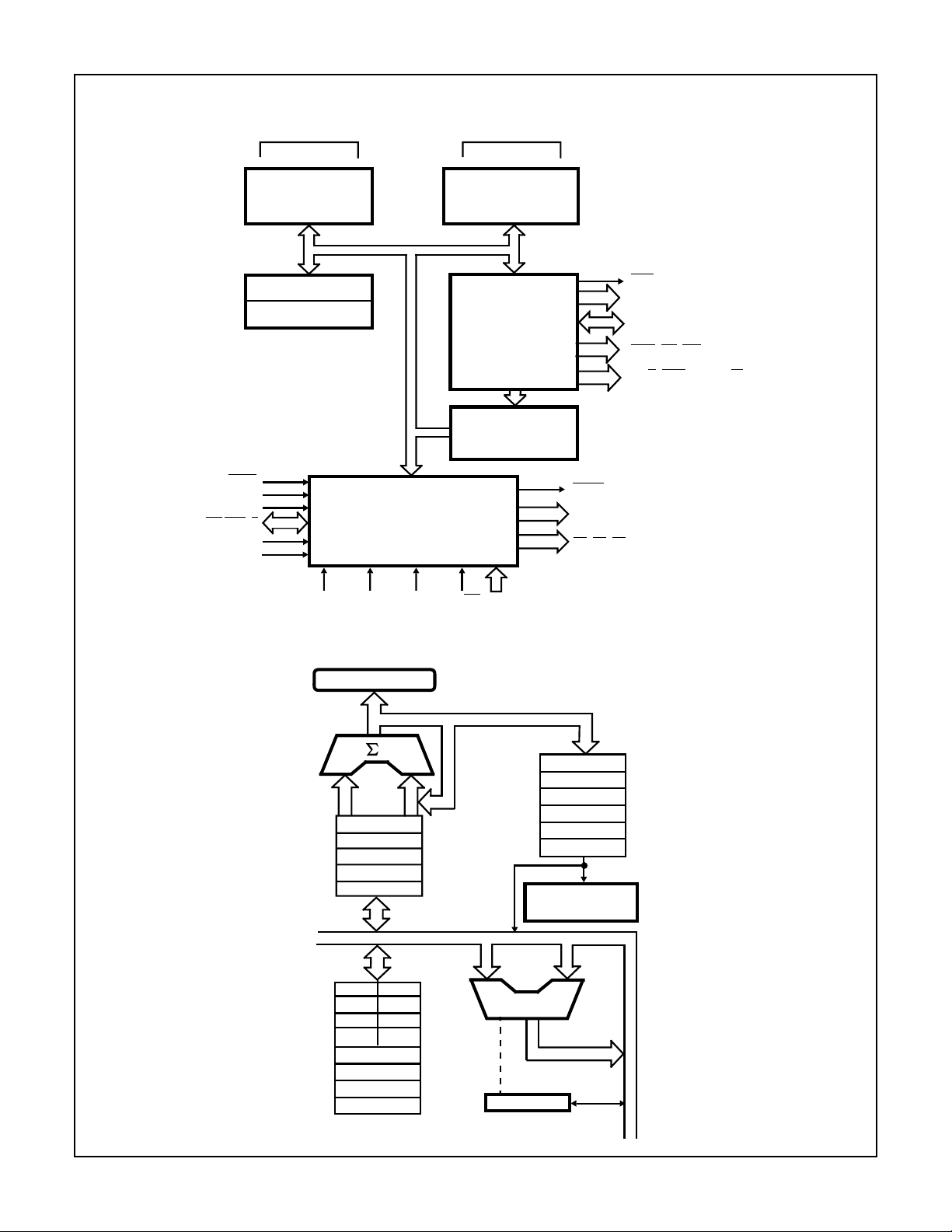

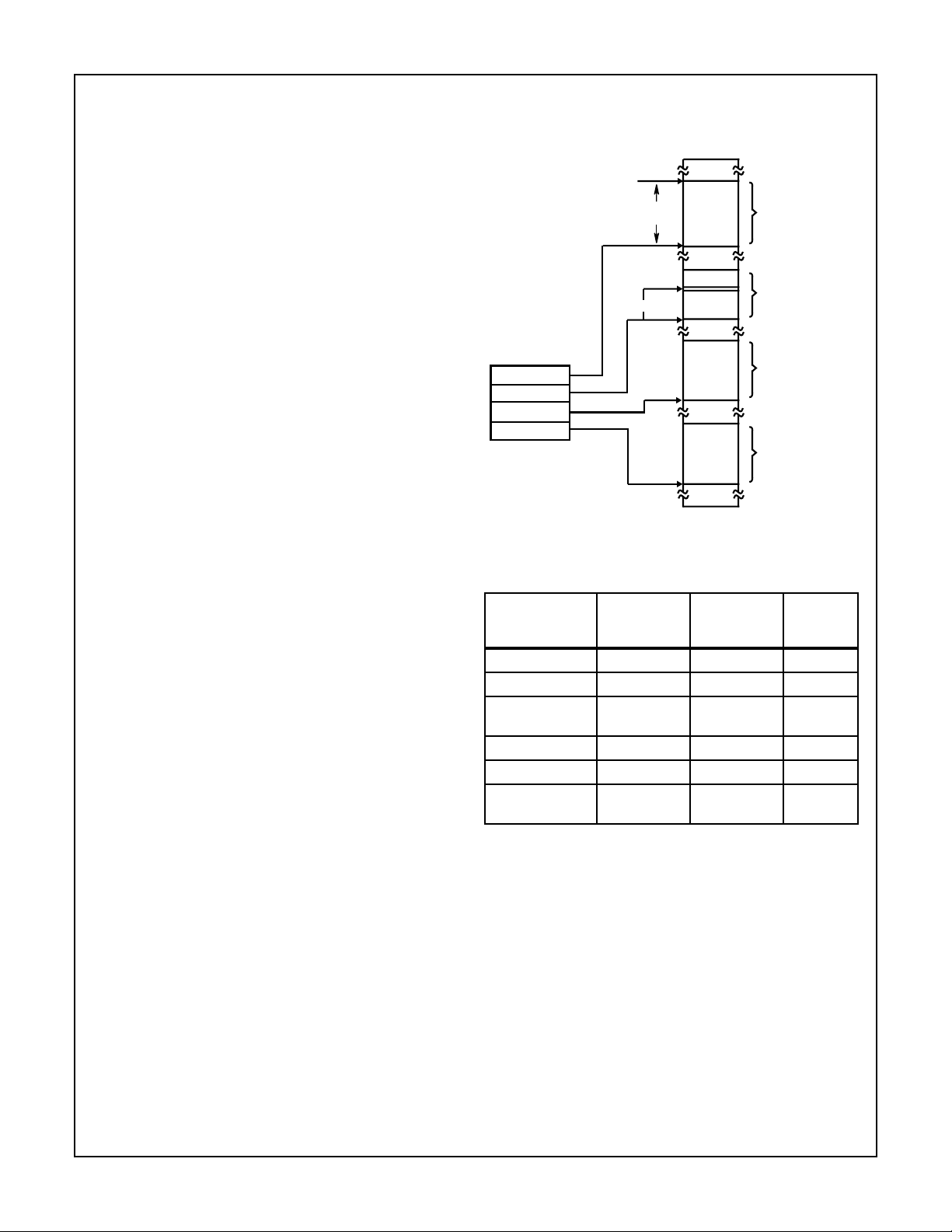

Functional Diagram

80C86

TEST

INTR

NMI

RQ/GT0, 1

HOLD

HLDA

EXECUTION UNIT

REGISTER FILE

DATA POINTER

AND

INDEX REGS

(8 WORDS)

16-BIT ALU

FLAGS

2

CLK RESET READY

BUS INTERFACE UNIT

SEGMENT REGISTERS

INSTRUCTION POINTER

BUS INTERFACE UNIT

CONTROL AND TIMING

MN/

RELOCATION

REGISTER FILE

AND

(5 WORDS)

6-BYTE

INSTRUCTION

QUEUE

3

GND

MX

V

CC

2

3

4

16

3

4

LOCK

QS0, QS1

S2, S1, S0

BHE/S7

A19/S6

A16/S3

AD15-AD0

INTA,RD, WR

R, DEN, ALE, M/IO

DT/

BUS

INTERFACE

UNIT

EXECUTION

UNIT

MEMORY INTERFACE

B-BUS

ES

CS

SS

DS

IP

AH

BH

CH

DH

AL

BL

CL

DL

SP

BP

SI

DI

C-BUS

INSTRUCTION

STREAM BYTE

QUEUE

A-BUS

ARITHMETIC/

LOGIC UNIT

FLAGS

EXECUTION UNIT

CONTROL SYSTEM

3-143

80C86

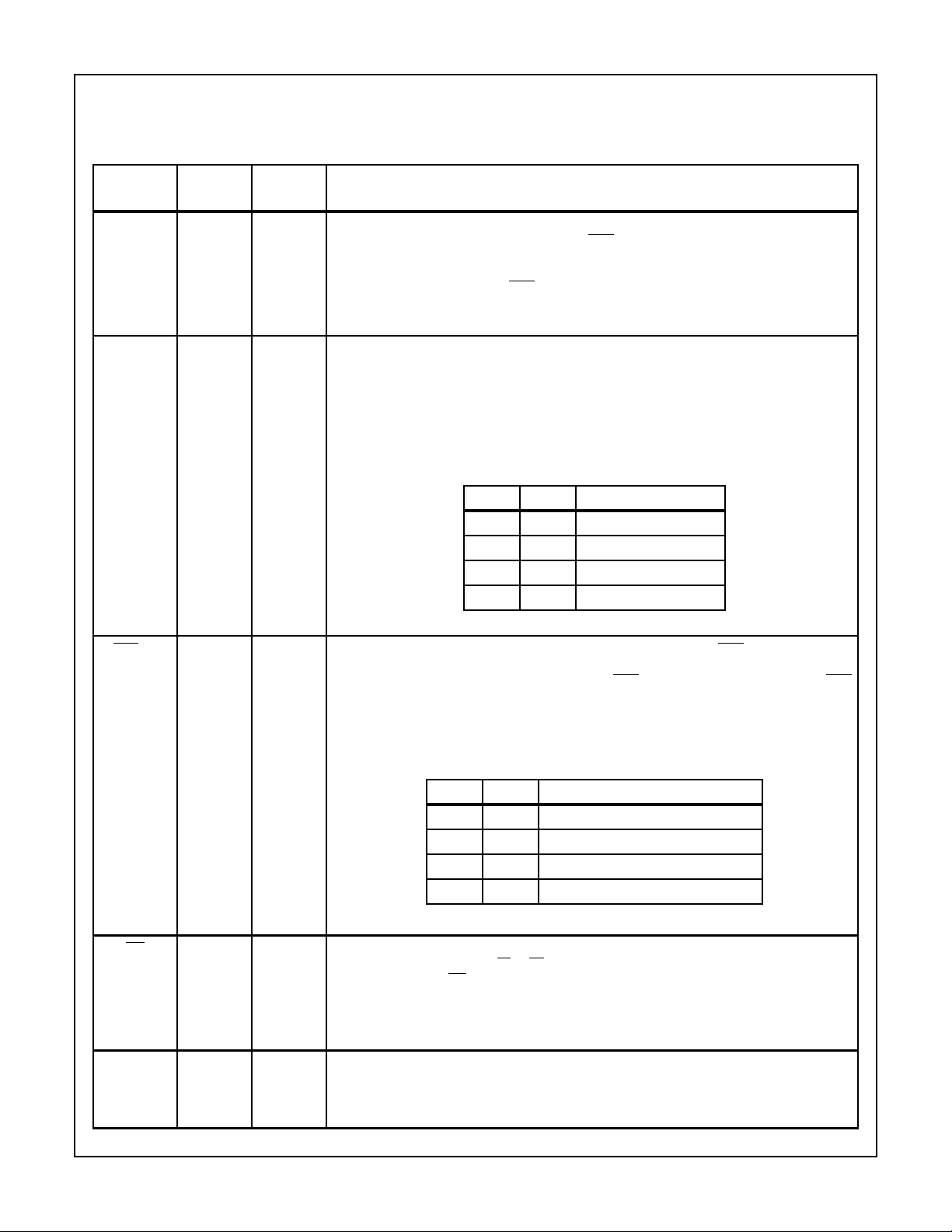

Pin Description

The following pin function descriptions are for 80C86 systems in either minimum or maximum mode. The “Local Bus” in these description is

the direct multiplexed bus interface connection to the 80C86 (without regard to additional bus buffers).

PIN

SYMBOL

AD15-AD0 2-16, 39 I/O ADDRESS DATA B US: These lines constitute the time multiplex ed memory/lO address (T1) and

NUMBER TYPE DESCRIPTION

data (T2, T3, TW, T4) bus. A0 is analogous to BHE for the lower byte of the data bus, pins D7D0. It is LOW during Ti when a byte is to be transferred on the low er portion of the bus in memory

or I/O operations. Eight-bit oriented devices tied to the lower half would normally use A0 to condition chip select functions (See BHE). These lines are active HIGH and are held at high impedance to the last valid logic level during interrupt ackno wledge and local bus “hold acknowledge”

or “grant sequence”.

A19/S6

A18/S5

A17/S4

A16/S3

BHE/S7 34 O BUS HIGH ENABLE/STATUS: During T1 the bus high enable signal (BHE) should be used to

35-38 O ADDRESS/ST ATUS: During T1, these are the f our most significant address lines for memory op-

erations. During I/O operations these lines are LOW. During memory and I/O operations, status

information is available on these lines during T2, T3, TW, T4. S6 is always LOW. The status of

the interrupt enable FLAG bit (S5) is updated at the beginning of each clock cycle. S4 and S3

are encoded as shown.

This information indicates which segment register is presently being used for data accessing.

These lines are held at high impedance to the last valid logic level during local bus “hold ac-

knowledge” or “grant sequence”.

S4 S3 CHARACTERISTICS

0 0 Alternate Data

0 1 Stack

1 0 Code or None

1 1 Data

enable data onto the most significant half of the data bus, pins D15-D8. Eight bit oriented devices

tied to the upper half of the bus would normally use BHE to condition chip select functions. BHE

is LOW during T1 for read, write, and interrupt acknowledge cycles when a byte is to be transferred on the high portion of the bus. The S7 status information is available during T2, T3 and

T4. The signal is active LOW, and is held at high impedance to the last valid logic level during

interrupt acknowledge and local bus “hold acknowledge” or “grant sequence”, it is LOW during

T1 for the first interrupt acknowledge cycle.

BHE A0 CHARACTERISTICS

0 0 Whole Word

0 1 Upper Byte From/to Odd Address

1 0 Lower Byte From/to Even address

1 1 None

RD 32 O READ: Read strobe indicates that the processor is performing a memory or I/O read cycle, de-

pending on the state of the M/IO or S2 pin. This signal is used to read devices which reside on

the 80C86 local bus. RD is active LOW during T2, T3 and TW of any read cycle, and is guaranteed to remain HIGH in T2 until the 80C86 local bus has floated.

This line is held at a high impedance logic one state during “hold acknowledge” or “grand sequence”.

READY 22 I READ Y: is the acknowledgment from the addressed memory or I/O device that will complete the

data transfer . The RDY signal from memory or I/O is synchronized by the 82C84A Clock Generator to form READY. This signal is active HIGH. The 80C86 READY input is not synchronized.

Correct operation is not guaranteed if the Setup and Hold Times are not met.

3-144

80C86

Pin Description

The following pin function descriptions are for 80C86 systems in either minimum or maximum mode. The “Local Bus” in these description is

the direct multiplexed bus interface connection to the 80C86 (without regard to additional bus buffers).

SYMBOL

INTR 18 I INTERRUPT REQUEST: is a level triggered input which is sampled during the last clock cycle

TEST 23 I TEST: input is e xamined by the “W ait” instruction. If theTEST input is LOW ex ecution continues,

NMI 17 I NON-MASKABLE INTERRUPT: is an edge triggered input which causes a type 2 interrupt. A

RESET 21 I RESET: causes the processor to immediately terminate its present activity. The signal must tran-

CLK 19 I CLOCK: provides the basic timing for the processor and bus controller. It is asymmetric with a

NUMBER TYPE DESCRIPTION

(Continued)

PIN

of each instruction to determine if the processor should enter into an interrupt acknowledge operation. A subroutine is vectored to via an interrupt vector lookup table located in system memory. It can be internally masked by software resetting the interrupt enable bit.

lNTR is internally synchronized. This signal is active HIGH.

otherwise the processor waits in an “Idle”state. This input is synchronized internally during each

clock cycle on the leading edge of CLK.

subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is

not maskable internally by software. A transition from LOW to HIGH initiates the interrupt at the

end of the current instruction. This input is internally synchronized.

sition LOW to HIGH and remain active HIGH for at least four clock cycles. It restarts execution,

as described in the Instruction Set description, when RESET returns LOW. RESET is internally

synchronized.

33% duty cycle to provide optimized internal timing.

VCC 40 VCC: +5V power supply pin. A 0.1µF capacitor between pins 20 and 40 is recommended for de-

coupling.

GND 1, 20 GND: Ground. Note: both must be connected. A 0.1µF capacitor between pins 1 and 20 is rec-

ommended for decoupling.

MN/MX 33 I MINIMUM/MAXIMUM: Indicates what mode the processor is to operate in. The two modes are

discussed in the following sections.

Minimum Mode System

The following pin function descriptions are for the 80C86 in minimum mode (i.e., MN/MX = VCC). Only the pin functions which are unique to

minimum mode are described; all other pin functions are as described below.

PIN

SYMBOL

M/IO 28 O ST ATUS LINE: logically equivalent to S2 in the maximum mode. It is used to distinguish a mem-

WR 29 O WRITE: indicates that the processor is performing a write memory or write I/O cycle, depending

INTA 24 O INTERRUPT ACKNOWLEDGE: is used as a read strobe for interrupt acknowledge cycles. It is

NUMBER TYPE DESCRIPTION

ory access from an I/O access. M/lO becomes valid in the T4 preceding a bus cycle and remains

valid until the final T4 of the cycle (M = HIGH, I/O = LOW). M/lO is held to a high impedance logic

one during local bus “hold acknowledge”.

on the state of the M/IO signal. WR is active for T2, T3 and TW of any write cycle. It is active

LOW, and is held to high impedance logic one during local bus “hold acknowledge”.

active LOW during T2, T3 and TW of each interrupt acknowledge cycle. Note thatINTA is never

floated.

ALE 25 O ADDRESS LATCH ENABLE: is provided by the processor to latch the address into the

82C82/82C83 address latch. It is a HIGH pulse active during clock LOW of T1 of any b us cycle .

Note that ALE is never floated.

3-145

80C86

Minimum Mode System (Continued)

The following pin function descriptions are for the 80C86 in minimum mode (i.e., MN/MX = VCC). Only the pin functions which are unique to

minimum mode are described; all other pin functions are as described below.

PIN

SYMBOL

DT/R 27 O DATA TRANSMIT/RECEIVE: is needed in a minimum system that desires to use a data bus

DEN 26 O DATA ENABLE: provided as an output enable for a bus transceiver in a minimum system which

NUMBER TYPE DESCRIPTION

transceiver. It is used to control the direction of data flow through the transceiver. Logically,

DT/R is equivalent to S1 in maximum mode, and its timing is the same as for M/IO (T = HIGH,

R = LOW). DT/R is held to a high impedance logic one during local bus “hold acknowledge”.

uses the transceiver. DEN is active LOW during each memory and I/O access and for INTA cycles. For a read or INTA cycle it is active from the middle of T2 until the middle of T4, while for a

write cycle it is active from the beginning of T2 until the middle of T4. DEN is held to a high impedance logic one during local bus “hold acknowledge”.

HOLD

HLDA

31, 30 I

HOLD: indicates that another master is requesting a local bus “hold”. To be an acknowledged,

O

HOLD must be active HIGH. The processor receiving the “hold” will issue a “hold acknowledge”

(HLDA) in the middle of a T4 or TI clock cycle. Simultaneously with the issuance of HLDA, the

processor will float the local bus and control lines. After HOLD is detected as being LOW, the

processor will lower HLDA, and when the processor needs to run another cycle, it will again drive

the local bus and control lines.

HOLD is not an asynchronous input. External synchronization should be provided if the system

cannot otherwise guarantee the setup time.

Maximum Mode System

The following pin function descriptions are for the 80C86 system in maximum mode (i.e., MN/MX - GND). Only the pin functions which are

unique to maximum mode are described below.

PIN

SYMBOL

S0

S1

S2

NUMBER TYPE DESCRIPTION

26

27

28

O

O

O

STATUS: is active during T4, T1 and T2 and is returned to the passive state (1, 1, 1) during T3

or during TW when READY is HIGH. This status is used b y the 82C88 Bus Controller to generate

all memory and I/O access control signals. Any change by S2, S1 or S0 during T4 is used to

indicate the beginning of a bus cycle, and the return to the passive state in T3 or TW is used to

indicate the end of a bus cycle.

These signals are held at a high impedance logic one state during “grant sequence”.

S2 S1 S0 CHARACTERISTICS

0 0 0 Interrupt Acknowledge

0 0 1 Read I/O Port

0 1 0 Write I/O Port

0 1 1 Halt

1 0 0 Code Access

1 0 1 Read Memory

1 1 0 Write Memory

1 1 1 Passive

3-146

80C86

Maximum Mode System (Continued)

The following pin function descriptions are for the 80C86 system in maximum mode (i.e., MN/MX - GND). Only the pin functions which are

unique to maximum mode are described below.

PIN

SYMBOL

NUMBER TYPE DESCRIPTION

RQ/GT0

RQ/GT1

LOCK 29 O LOCK: output indicates that other system bus masters are not to gain control of the system bus

31, 30 I/O REQUEST/GRANT: pins are used by other local bus masters to force the processor to release

the local bus at the end of the processor’s current bus cycle. Each pin is bidirectional with

RQ/GTO having higher priority than RQ/GT1. RQ/GT has an internal pull-up bus hold device so

it may be left unconnected. The request/grant sequence is as follows (see RQ/GT Sequence

Timing)

1. A pulse of 1 CLK wide from another local bus master indicates a local bus request (“hold”)

to the 80C86 (pulse 1).

2. Dur ing a T4 or TI clock cycle, a pulse 1 CLK wide from the 80C86 to the requesting master

(pulse 2) indicates that the 80C86 has allowed the local bus to float and that it will enter the

“grant sequence” state at the next CLK. The CPU’s bus interface unit is disconnected logically from the local bus during “grant sequence”.

3. A pulse 1 CLK wide from the requesting master indicates to the 80C86 (pulse 3) that the

“hold” request is about to end and that the 80C86 can reclaim the local bus at the next CLK.

The CPU then enters T4 (or TI if no bus cycles pending).

Each Master-Master exchange of the local bus is a sequence of 3 pulses. There must be one

idle CLK cycle after each bus exchange. Pulses are active low.

If the request is made while the CPU is performing a memory cycle, it will release the local

bus during T4 of the cycle when all the following conditions are met:

1. Request occurs on or before T2.

2. Current cycle is not the low byte of a word (on an odd address).

3. Current cycle is not the first acknowledge of an interrupt acknowledge sequence.

4. A locked instruction is not currently executing.

If the local bus is idle when the request is made the two possible events will follow:

1. Local bus will be released during the next cycle.

2. A memory cycle will start within three clocks. Now the four rules for a currently active memory

cycle apply with condition number 1 already satisfied.

while LOCK is active LOW. The LOCK signal is activated by the “LOCK” prefix instruction and

remains active until the completion of the next instruction. This signal is active LO W, and is held

at a high impedance logic one state during “grant sequence”. In MAX mode, LOCK is automatically generated during T2 of the first INTA cycle and removed during T2 of the second INTA

cycle.

QS1, QSO 24, 25 O QUEUE STATUS: The queue status is valid during the CLK cycle after which the queue opera-

tion is performed.

QS1 and QS0 provide status to allow external tracking of the internal 80C86 instruction queue.

Note that QS1, QS0 never become high impedance.

QSI QSO

0 0 No Operation

0 1 First byte of op code from queue

1 0 Empty the queue

1 1 Subsequent byte from queue

3-147

80C86

Functional Description

Static Operation

All 80C86 circuitry is of static design. Internal registers,

counters and latches are static and require no refresh as

with dynamic circuit design. This eliminates the minimum

operating frequency restriction placed on other microprocessors. The CMOS 80C86 can operate from DC to the specified upper frequency limit. The processor clock may be

stopped in either state (HIGH/LOW) and held there indefinitely. This type of operation is especially useful for system

debug or power critical applications.

The 80C86 can be single stepped using only the CPU clock.

This state can be maintained as long as is necessary. Single

step clock operation allows simple interface circuitry to provide critical information for bringing up your system.

Static design also allows very low frequency operation

(down to DC). In a power critical situation, this can provide

extremely low power operation since 80C86 power dissipation is directly related to operating frequency. As the system

frequency is reduced, so is the operating power until, ultimately, at a DC input frequency, the 80C86 power requirement is the standby current, (500µA maximum).

Internal Architecture

The internal functions of the 80C86 processor are partitioned logically into two processing units. The first is the Bus

Interface Unit (BlU) and the second is the Execution Unit

(EU) as shown in the CPU functional diagram.

These units can interact directly, but for the most part perform

as separate asynchronous operational processors. The bus

interface unit provides the functions related to instruction

fetching and queuing, operand fetch and store, and address

relocation. This unit also provides the basic bus control. The

overlap of instruction pre-fetching provided by this unit serves

to increase processor performance through improved bus

bandwidth utilization. Up to 6 bytes of the instruction stream

can be queued while waiting for decoding and execution.

The instruction stream queuing mechanism allows the BIU

to keep the memory utilized very efficiently. Whenever there

is space for at least 2 bytes in the queue, the BlU will attempt

a word fetch memory cycle. This greatly reduces “dead-time”

on the memory bus. The queue acts as a First-In-First-Out

(FIFO) buffer, from which the EU extracts instruction bytes

as required. If the queue is empty (following a branch

instruction, for example), the first byte into the queue immediately becomes available to the EU.

The execution unit receives pre-fetched instructions from the

BlU queue and provides un-relocated operand addresses to

the BlU. Memory operands are passed through the BIU for processing by the EU, which passes results to the BIU f or stor age.

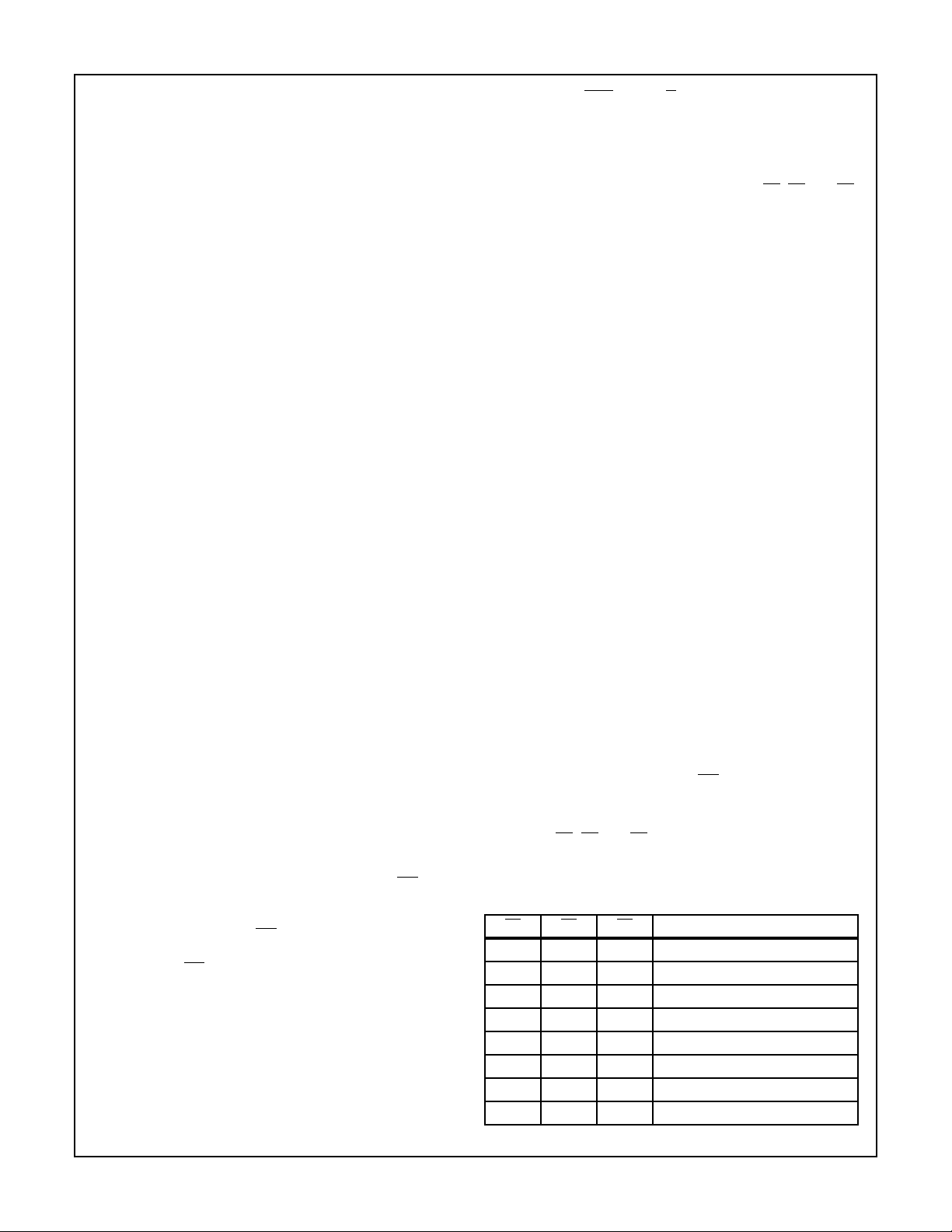

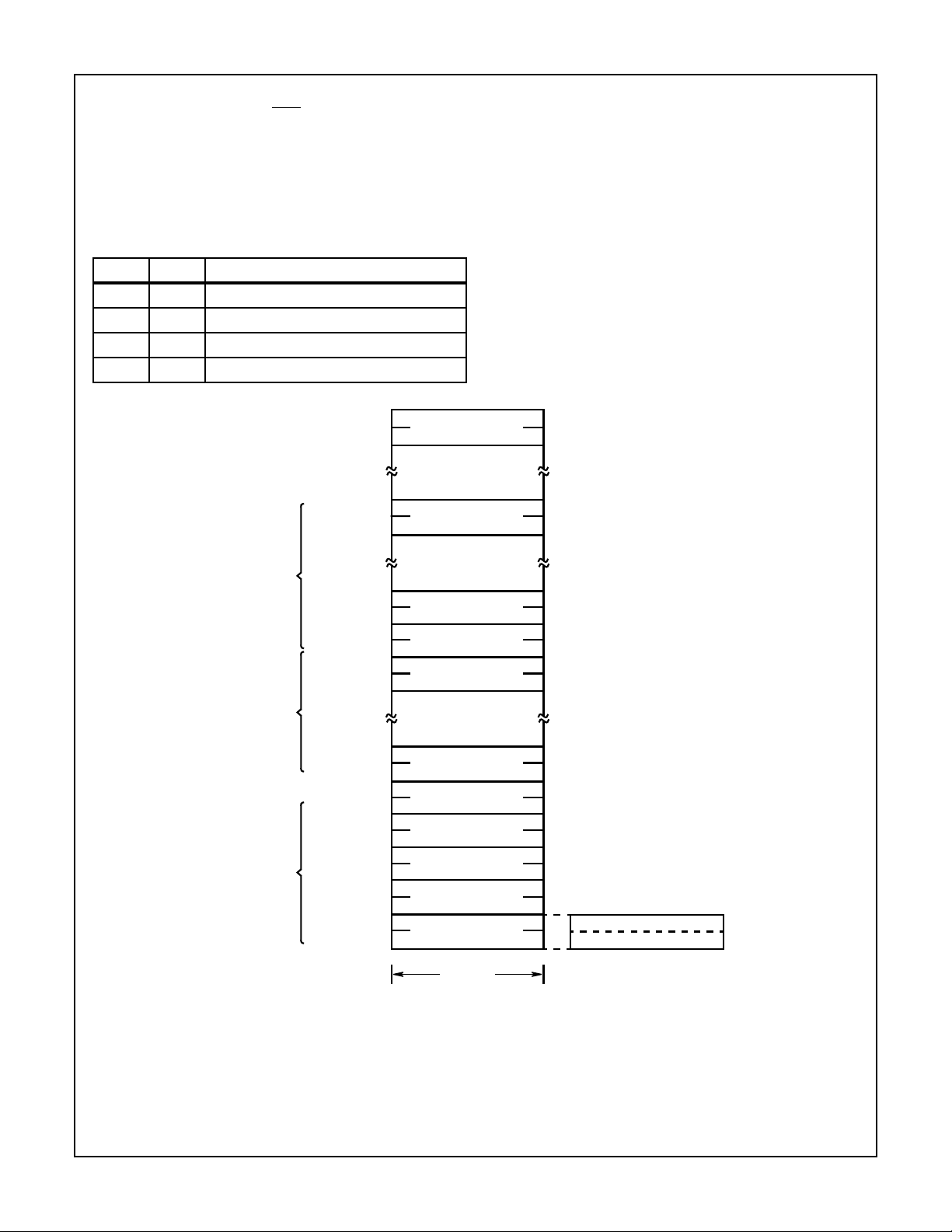

Memory Organization

The processor provides a 20-bit address to memory, which

locates the byte being referenced. The memory is organized

as a linear array of up to 1 million bytes, addressed as

00000(H) to FFFFF(H). The memory is logically divided into

code, data, extra and stack segments of up to 64K bytes

each, with each segment falling on 16-byte boundaries. (See

Figure 1).

FFFFFH

64K-BIT

+ OFFSET

SEGMENT

REGISTER FILE

CS

SS

DS

ES

FIGURE 1. 80C86 MEMORY ORGANIZATION

TABLE 1.

TYPE OF

MEMORY

REFERENCE

Instruction Fetch CS None IP

Stack Operation SS None SP

Variable (except

following)

String Source DS CS, ES, SS SI

String Destination ES None DI

BP Used As Base

Register

DEFAULT

SEGMENT

BASE

DS CS, ES, SS Effective

SS CS, DS, ES Effective

ALTERNATE

SEGMENT

CODE SEGMENT

XXXXOH

STACK SEGMENT

DATA SEGMENT

EXTRA SEGMENT

00000H

BASE OFFSET

Address

Address

All memory references are made relative to base addresses

contained in high speed segment registers. The segment

types were chosen based on the addressing needs of programs. The segment register to be selected is automatically

chosen according to the specific rules of Table 1. All information in one segment type share the same logical attributes

(e.g. code or data). By structuring memory into re-locatable

areas of similar characteristics and by automatically selecting segment registers, programs are shorter, faster and

more structured. (See Table 1).

Word (16-bit) operands can be located on even or odd

address boundaries and are thus, not constrained to even

boundaries as is the case in many 16-bit computers. For

address and data operands, the least significant byte of the

word is stored in the lower valued address location and the

most significant byte in the next higher address location. The

BIU automatically performs the proper number of memory

3-148

80C86

accesses; one, if the word operand is on an even byte

boundary and two, if it is on an odd byte boundary. Except

for the performance penalty, this double access is transpar-

ent to the software. The performance penalty does not occur

for instruction fetches; only word operands.

Physically, the memor y is organized as a high bank (D15D8) and a low bank (D7-D0) of 512K bytes addressed in parallel by the processor’s address lines.

Byte data with even addresses is transferred on the D7-D0

bus lines, while odd addressed byte data (A0 HIGH) is transferred on the D15-D8 bus lines. The processor provides two

enable signals, BHE and A

, to selectively allow reading

0

from or writing into either an odd byte location, even byte

location, or both. The instruction stream is fetched from

memory as words and is addressed internally by the processor at the byte level as necessary.

In referencing word data, the BlU requires one or two memory

cycles depending on whether the starting byte of the word is

on an even or odd address, respectively. Consequently, in referencing word operands performance can be optimized by

locating data on even address boundaries. This is an especially useful technique for using the stack, since odd address

references to the stack may adversely affect the context

switching time for interrupt processing or task multiple xing.

Certain locations in memory are reser ved for specific CPU

operations (See Figure 2). Locations from address FFFF0H

through FFFFFH are reserved for operations including a jump

to the initial program loading routine. Following RESET, the

CPU will always begin execution at location FFFF0H where

the jump must be located. Locations 00000H through 003FFH

are reserved for interrupt operations. Each of the 256 possible

interrupt service routines is accessed thru its own pair of 16bit pointers (segment address pointer and offset address

pointer). The first pointer, used as the offset address, is

loaded into the lP and the second pointer, which designates

the base address is loaded into the CS. At this point program

control is transferred to the interrupt routine. The pointer elements are assumed to have been stored at the respective

places in reserved memory prior to occurrence of interrupts.

Minimum and Maximum Operation Modes

The requirements for supporting minimum and maximum

80C86 systems are sufficiently different that they cannot be

met efficiently using 40 uniquely defined pins. Consequently,

the 80C86 is equipped with a strap pin (MN/

MX) which

defines the system configuration. The definition of a certain

subset of the pins changes, dependent on the condition of the

strap pin. When the MN/

MX pin is strapped to GND, the

80C86 defines pins 24 through 31 and 34 in maximum mode.

When the MN/

MX pin is strapped to VCC, the 80C86 gener-

ates bus control signals itself on pins 24 through 31 and 34.

The minimum mode 80C86 can be used with either a multi-

plexed or demultiplexed bus. This architecture provides the

80C86 processing power in a highly integrated form.

The demultiplexed mode requires two 82C82 latches (for 64K

addressability) or three 82C82 latches (for a full megabyte of

addressing). An 82C86 or 82C87 transceiver can also be

used if data bus buffering is required. (See Figure 6A.) The

80C86 provides

DEN and DT/R to control the transceiver , and

ALE to latch the addresses. This configuration of the minimum

mode provides the standard demultiplexed bus structure with

heavy bus buffering and relaxed bus timing requirements.

The maximum mode employs the 82C88 bus controller (See

Figure 6B). The 82C88 decodes status lines

S0, S1 and S2,

and provides the system with all bus control signals.

Moving the bus control to the 82C88 provides better source

and sink current capability to the control lines, and frees the

80C86 pins for extended large system features. Hardware

lock, queue status, and two request/grant interfaces are provided by the 80C86 in maximum mode. These features allow

coprocessors in local bus and remote bus configurations.

Bus Operation

The 80C86 has a combined address and data bus commonly referred to as a time multiplexed bus. This technique

provides the most efficient use of pins on the processor

while permitting the use of a standard 40 lead package. This

“local bus” can be buffered directly and used throughout the

system with address latching provided on memory and I/O

modules. In addition, the bus can also be demultiplexed at

the processor with a single set of 82C82 address latches if a

standard non-multiplexed bus is desired for the system.

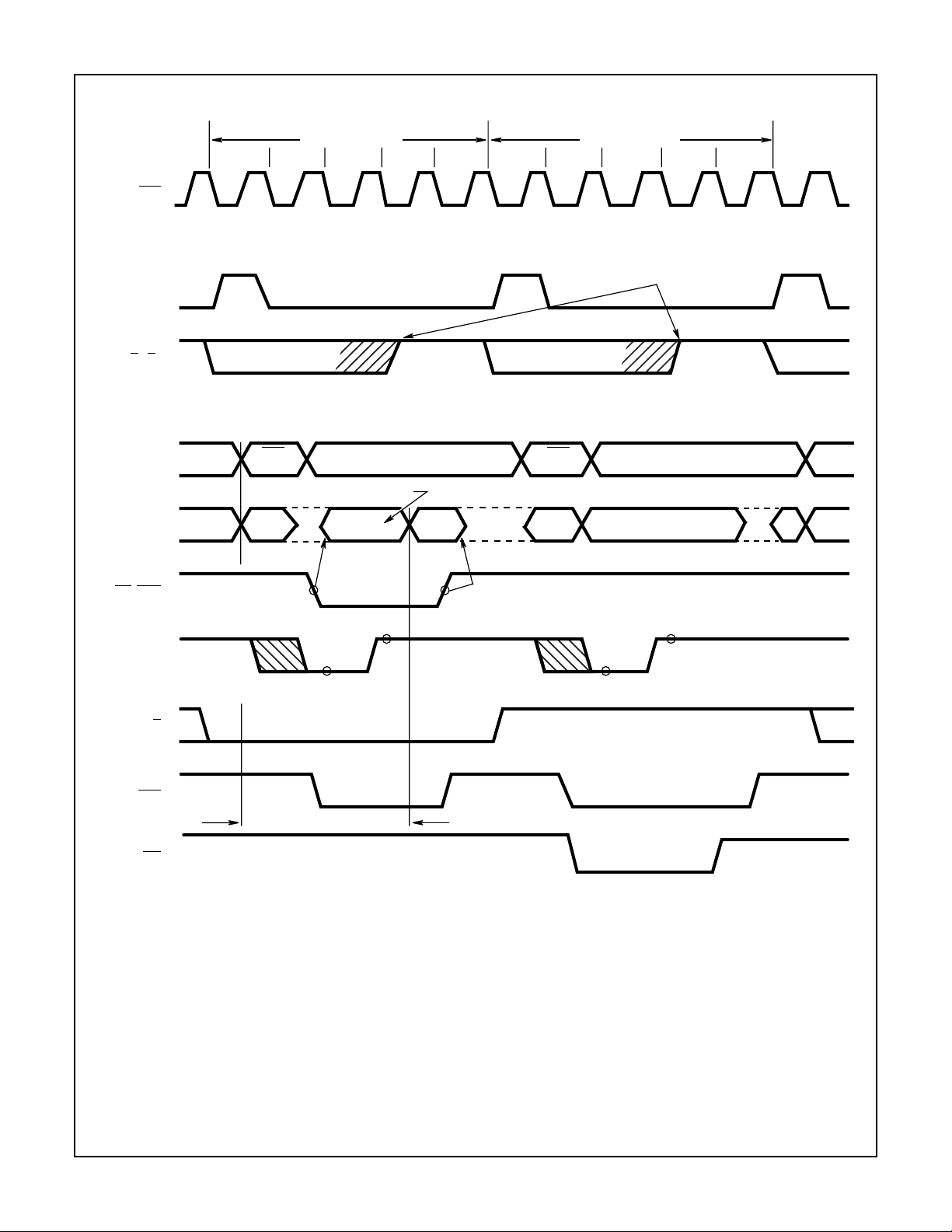

Each processor bus cycle consists of at least four CLK

cycles. These are referred to as T1, T2, T3 and T4 (see Figure 3). The address is emitted from the processor during T1

and data transfer occurs on the bus during T3 and T4. T2 is

used primarily for changing the direction of the bus during

read operations. In the event that a “NOT READY” indication

is given by the addressed device, “Wait” states (TW) are

inserted between T3 and T4. Each inser ted wait state is the

same duration as a CLK cycle. Periods can occur between

80C86 driven bus cycles. These are referred to as idle”

states (T

) or inactive CLK cycles. The processor uses these

I

cycles for internal housekeeping and processing.

During T1 of any bus cycle, the ALE (Address Latch Enable)

signal is emitted (by either the processor or the 82C88 bus

controller, depending on the MN/

MX strap). At the trailing

edge of this pulse, a valid address and certain status information for the cycle may be latched.

Status bits

S0, S1 and S2 are used by the bus controller, in

maximum mode, to identify the type of bus transaction

according to Table 2.

TABLE 2.

S2 S1 S0 CHARACTERISTICS

0 0 0 Interrupt

0 0 1 Read I/O

0 1 0 Write I/O

0 1 1 Halt

1 0 0 Instruction Fetch

1 0 1 Read Data from Memory

1 1 0 Write Data to Memory

1 1 1 Passive (No Bus Cycle)

3-149

80C86

Status bits S3 through S7 are time multiplexed with high

order address bits and the

BHE signal, and are therefore

valid during T2 through T4. S3 and S4 indicate which segment register (see Instruction Set Description) was used for

this bus cycle in forming the address, according to Table 3.

S5 is a reflection of the PSW interrupt enable bit. S3 is

always zero and S7 is a spare status bit.

TABLE 3.

S4 S3 CHARACTERISTICS

0 0 Alternate Data (Extra Segment)

0 1 Stack

1 0 Code or None

1 1 Data

FFFFFH

FFFF0H

3FFH

3FCH

RESET BOOTSTRAP

PROGRAM JUMP

TYPE 225 POINTER

(AVAILABLE)

I/O Addressing

In the 80C86, I/O operations can address up to a maximum

of 64K I/O byte registers or 32K I/O word registers. The I/O

address appears in the same format as the memory address

on bus lines A15-A0. The address lines A19-A16 are zero in

I/O operations. The variable I/O instructions which use register DX as a pointer have full address capability while the

direct I/O instructions directly address one or two of the 256

I/O byte locations in page 0 of the I/O address space.

I/O ports are addressed in the same manner as memory locations. Even addressed bytes are transferred on the D7-D0 bus

lines and odd addressed bytes on D15-D8. Care must be taken

to ensure that each register within an 8-bit peripheral located on

the lower portion of the bus be addressed as even.

AVAILABLE

INTERRUPT

POINTERS

(224)

RESERVED

INTERRUPT

POINTERS

(27)

DEDICATED

INTERRUPT

POINTERS

(5)

TYPE 33 POINTER

084H

080H

07FH

014H

010H

00CH

008H

004H

000H

(AVAILABLE)

TYPE 32 POINTER

(AVAILABLE)

TYPE 31 POINTER

(AVAILABLE)

TYPE 5 POINTER

(RESERVED)

TYPE 4 POINTER

OVERFLOW

TYPE 3 POINTER

1 BYTE INT INSTRUCTION

TYPE 2 POINTER

NON MASKABLE

TYPE 1 POINTER

SINGLE STEP

TYPE 0 POINTER

DIVIDE ERROR

CS BASE ADDRESS

IP OFFSET

16 BITS

FIGURE 2. RESERVED MEMORY LOCATIONS

3-150

80C86

CLK

ALE

S2-S0

ADDR/

STATUS

ADDR/DATA

(4 + NWAIT) = TCY

T1 T2 T3 T4TWAIT T1 T2 T3 T4TWAIT

BHE,

A19-A16

A15-A0

BUS RESERVED

FOR DATA IN

S7-S3

D15-D0

VALID

A19-A16

A15-A0 DATA OUT (D15-D0)

(4 + NWAIT) = TCY

GOES INACTIVE IN THE STATE

JUST PRIOR TO T

BHE

S7-S3

4

RD, INTA

READY

DT/

DEN

WR

READYREADY

WAIT WAIT

R

MEMORY ACCESS TIME

FIGURE 3. BASIC SYSTEM TIMING

3-151

Loading...

Loading...