International Rrectifier IR3831WMPbF User Manual

SupIRBuck

TM

HIGHLY EFFICIENT INTEGRATED

IR3831WMPbF

SYNCHRONOUS BUCK REGULATOR FOR DDR APPLICATIONS

Features

• Wide Input Voltage Range 1.5V to 16V

• Wide Output Voltage Range 0.6V to 0.9*Vin

• Continuous 8A Load Capability

• Integrated Bootstrap-diode

• High Bandwidth E/A for excellent transient

performance

• Programmable Switching Frequency up to 1.5 MHz

• Programmable Over Current Protection

• PGood output

• Hiccup Current Limit

• Programmable Soft-Start

• Enable Input with Voltage Monitoring Capability

• Enhanced Pre-Bias Start-up

• Vp input for DDR Tracking applications

o

• -40

C to 125oC operating junction temperature

• Thermal Protection

• 5mm x 6mm Power QFN Package, 0.9 mm height

• Lead-free, halogen-free and RoHS compliant

Applications

• Server Applications

• Storage Applications

• Embedded Telecom Systems

Description

The IR3831W SupIRBuck

fully integrated and highly efficient DC/DC

regulator. The MOSFETS co-packaged with the

on-chip PWM controller make IR3831W a spaceefficient solution, providing accurate power

delivery for DDR memory applications.

IR3831W is configured to generate termination

voltage (VTT) for DDR memory applications.

IR3831W offers programmability of start up time,

switching frequency and current limit while

operating in wide input and output voltage range.

The switching frequency is programmable from

250kHz to 1.5MHz for an optimum solution.

It also features important protection functions,

such as Pre-Bias startup, hiccup current limit and

thermal shutdown to give required system level

security in the event of fault conditions.

• Distributed Point of Load Power Architectures

• Netcom Applications

TM

is an easy-to-use,

Rev 13.0

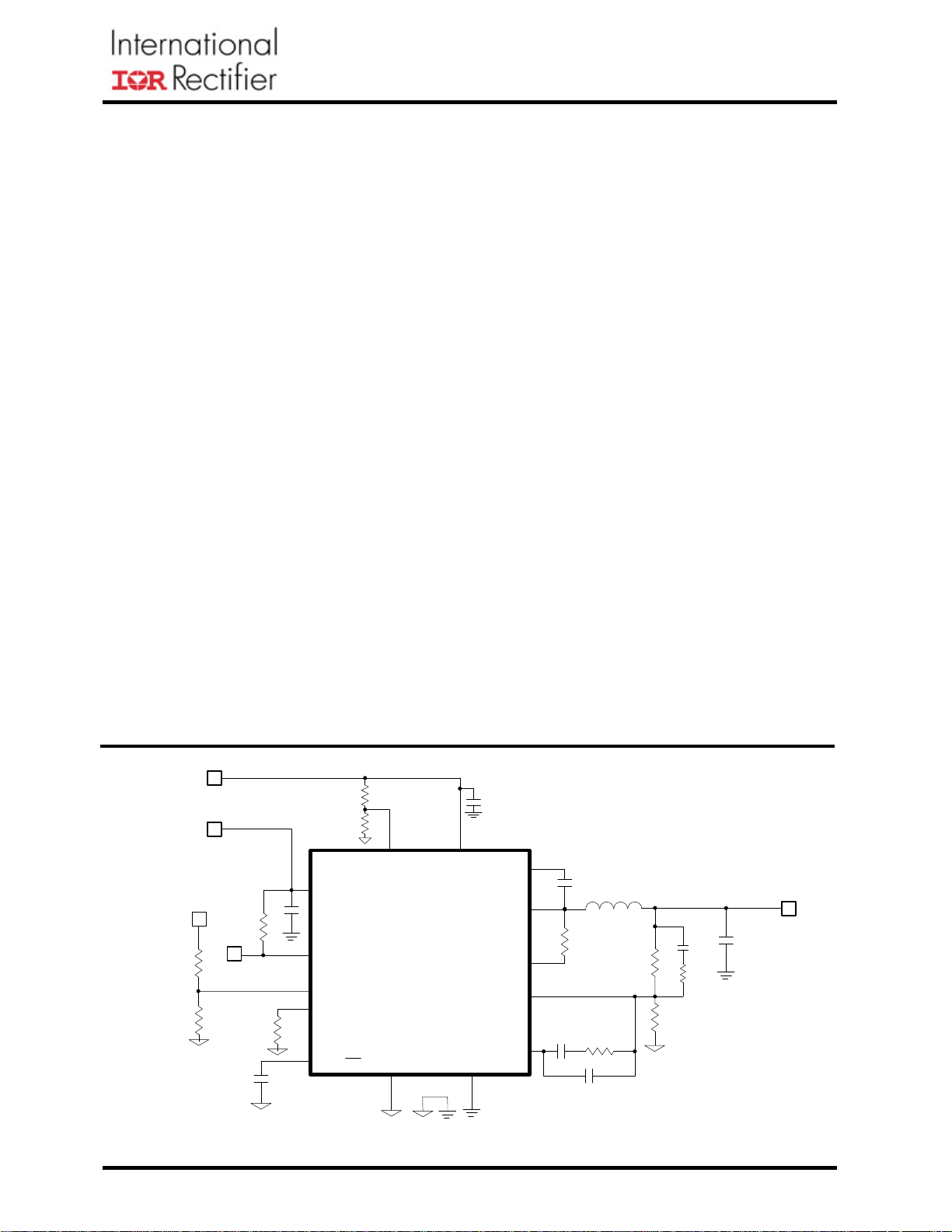

1.5V <Vin<16V

4.5V <Vcc<5.5V

VDDQ

PGood

Vcc

PGood

Vp

Rt

SS/ SD

Enable

Gnd

Vin

PGnd

Boot

SW

OCSet

Fb

Comp

Fig. 1. Typical application diagram

Vo

1

IR3831WMPbF

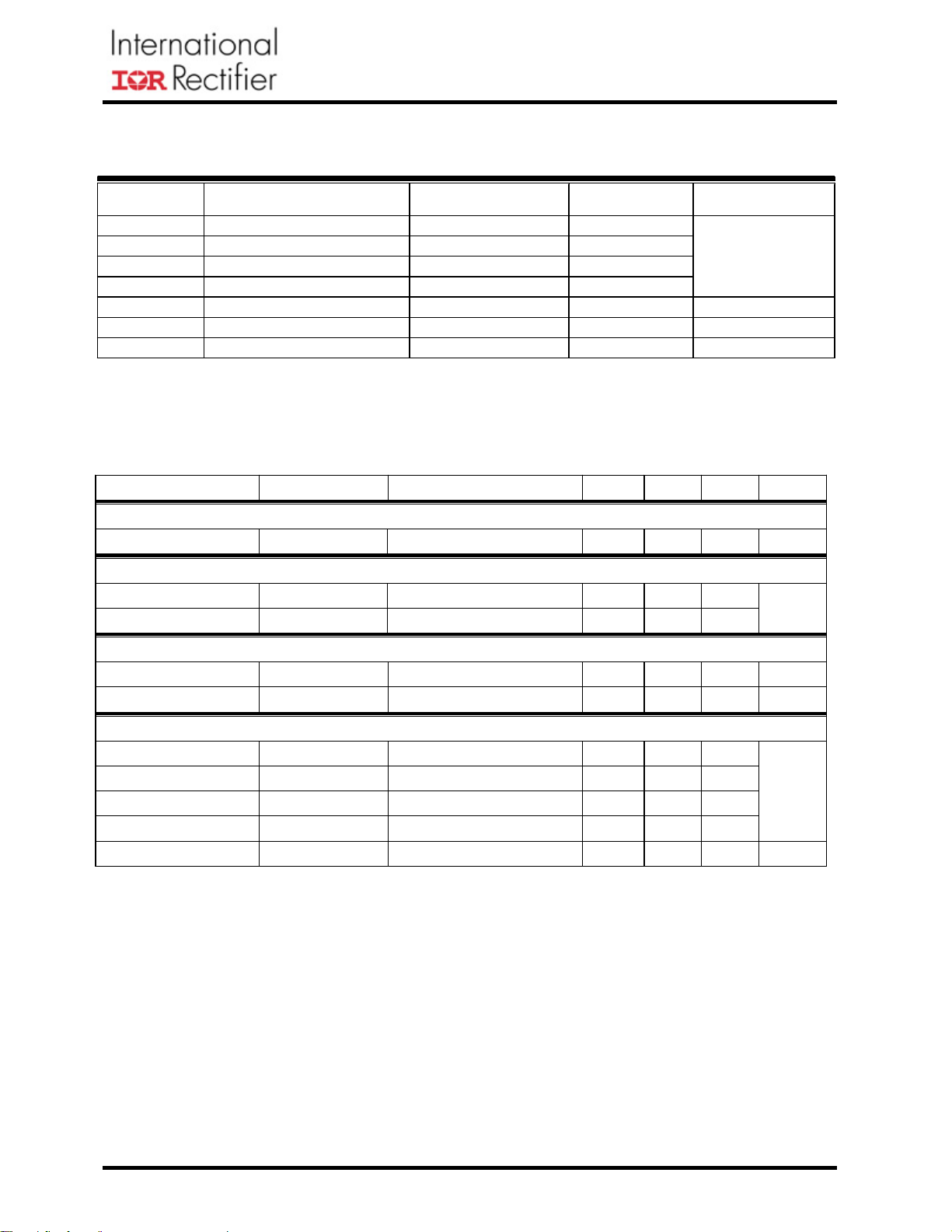

ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to GND unless otherwise specified)

• Vin ……………………………………………………. -0.3V to 25V

• Vcc ……………….….…………….……..……….…… -0.3V to 8V (Note2)

• Boot ……………………………………..……….…. -0.3V to 33V

• SW …………………………………………..……… -0.3V to 25V(DC), -4V to 25V(AC, 100ns)

• Boot to SW ……..…………………………….…..….. -0.3V to Vcc+0.3V (Note1)

• OCSet ………………………………………….……. -0.3V to 30V, 30mA

• Input / output Pins ……………………………….. ... -0.3V to Vcc+0.3V (Note1)

• PGND to GND ……………...………………………….. -0.3V to +0.3V

• Storage Temperature Range ................................... -55°C To 150°C

• Junction Temperature Range ................................... -40°C To 150°C (Note2)

• ESD Classification …………………………… ……… JEDEC Class 1C

• Moisture sensitivity level………………...………………JEDEC Level 3@260 °C

Note1: Must not exceed 8V

Note2: Vcc must not exceed 7.5V for Junction Temperature between -10

o

C and -40oC

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the

device. These are stress ratings only and functional operation of the device at these or any other

conditions beyond those indicated in the operational sections of the specifications are not implied.

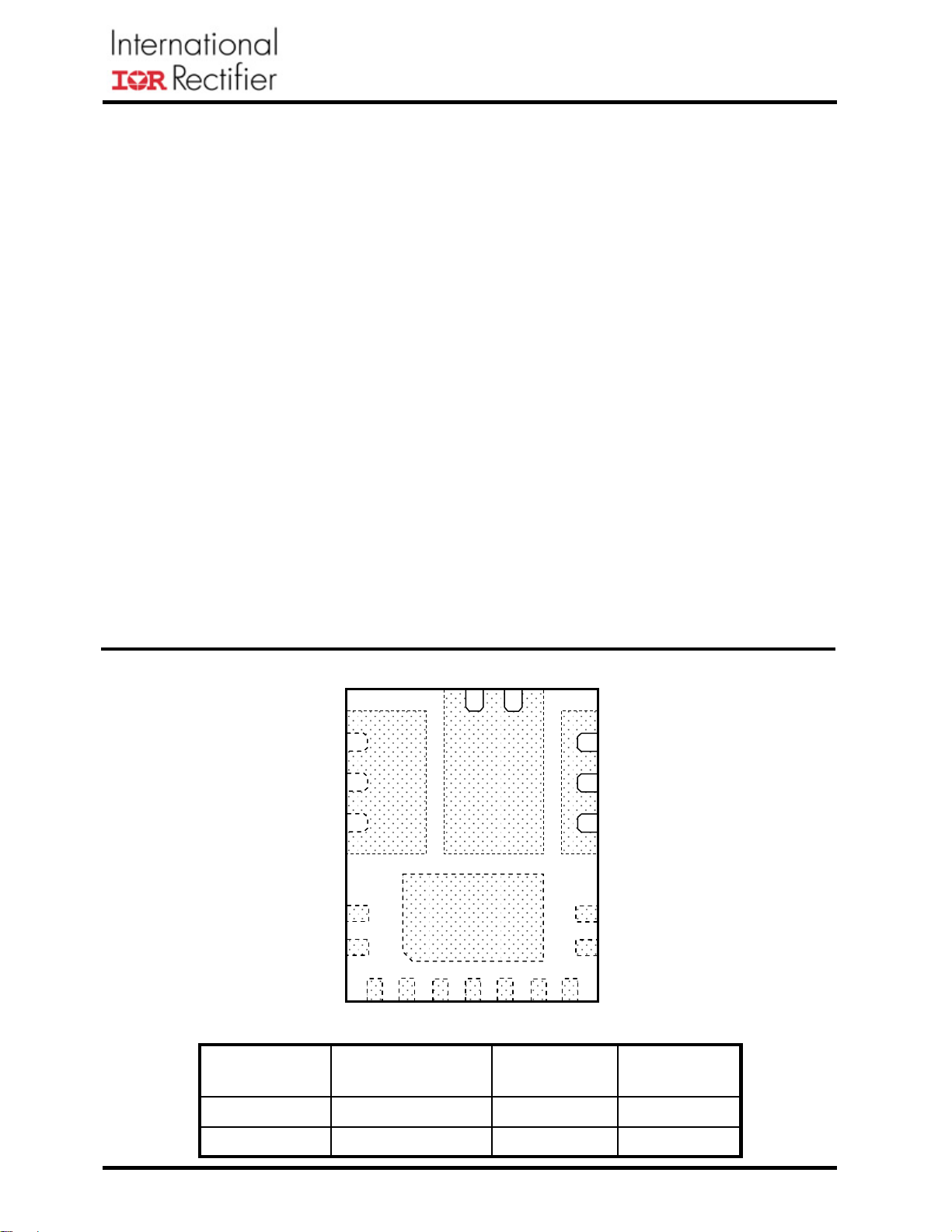

PACKAGE INFORMATION

SW

5mm x 6mm POWER QFN

V

ORDERING INFORMATION

IN

Boot

Enable

12

13

14

1

23

Vp FB COMP Gnd Rt SS OCSet

15

Gnd

4

11

PGnd

10

=

JA

-

PCBJ

V

9

8

5

7

6

CC

PGood

=

o

W/C35θ

o

W/C2θ

Rev 13.0

PACKAGE

DESIGNATOR

M

PACKAGE

DESCRIPTION

IR3831WMTR1PbF

PIN COUNT

15

PARTS PER

REEL

400015IR3831WMTRPbFM

750

2

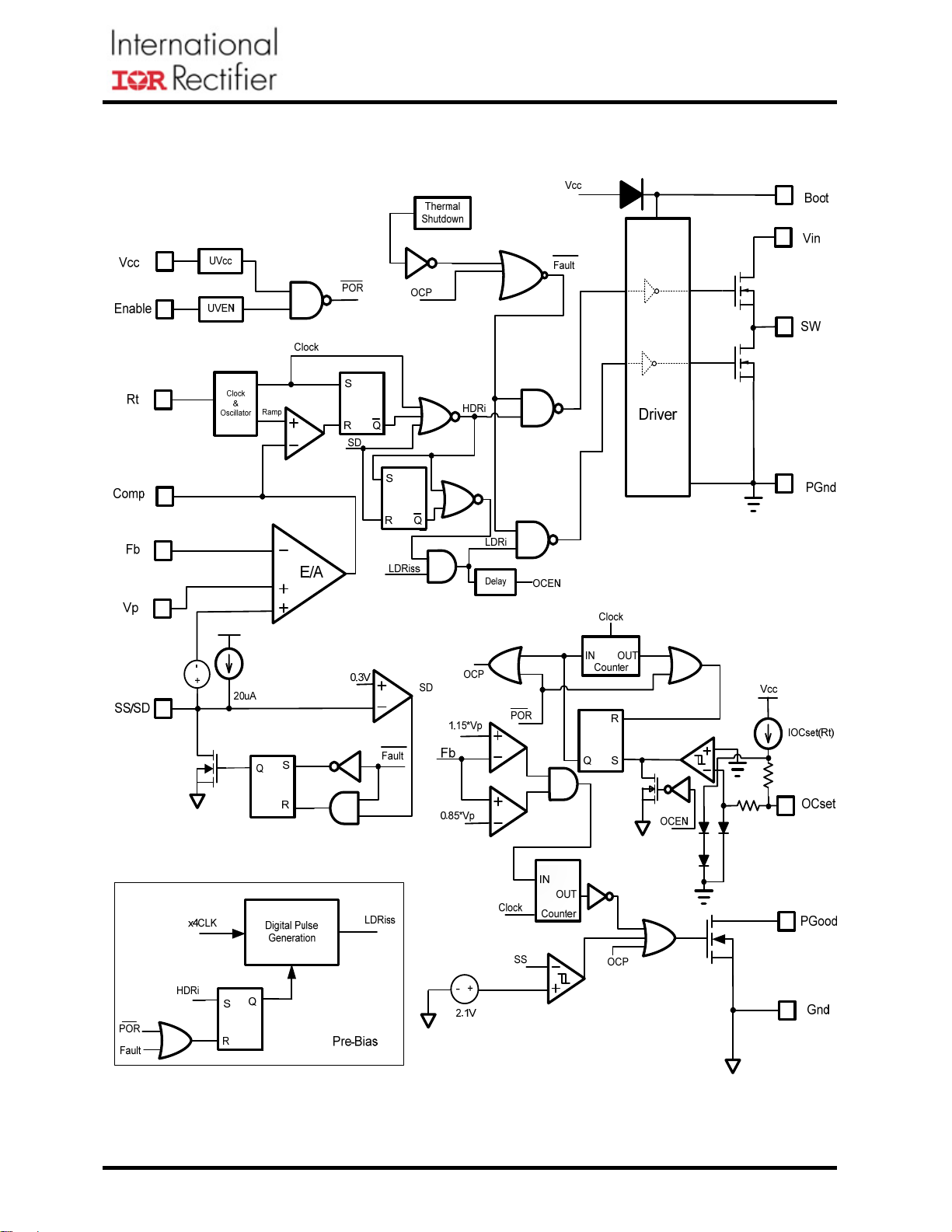

Block Diagram

IR3831WMPbF

Rev 13.0

Fig. 2. Simplified block diagram of the IR3831W

3

Pin Description

Pin Name Description

Track pin. Use External resistors from VDDQ rail. The Vp voltage can

1 Vp

2 Fb

3 Comp

4 Gnd Signal ground for internal reference and control circuitry.

5 Rt

6 SS/SD¯¯

7 OCSet

8

PGood

9

10 PGnd

11

12

13 Boot

V

CC

SW

V

IN

be set to 0.9V for DDR2 application and 0.75 or 0.6V for DDR3

application.

Inverting input to the error amplifier. This pin is connected directly to the

output of the regulator via resistor divider to set the output voltage and

provide feedback to the error amplifier.

Output of error amplifier. An external resistor and capacitor network is

typically connected from this pin to Fb pin to provide loop

compensation.

Set the switching frequency. Connect an external resistor from this pin

to Gnd to set the switching frequency.

Soft start / shutdown. This pin provides user programmable soft-start

function. Connect an external capacitor from this pin to Gnd to set the

start up time of the output voltage. The converter can be shutdown by

pulling this pin below 0.3V.

Current limit set point. A resistor from this pin to SW pin will set the

current limit threshold.

Power Good status pin. Output is open drain. Connect a pull up resistor

from this pin to Vcc. If unused, it can be left open.

This pin powers the internal IC and drivers. A minimum of 1uF high

frequency capacitor must be connected from this pin to the power

ground (PGnd).

Power Ground. This pin serves as a separated ground for the MOSFET

drivers and should be connected to the system’s power ground plane.

Switch node. This pin is connected to the output inductor.

Input voltage connection pin.

Supply voltage for high side driver. Connect a 0.1uF capacitor from this

pin to SW.

IR3831WMPbF

14 Enable Enable pin to turn on and off the device.

15 Gnd Signal ground for internal reference and control circuitry.

Rev 13.0

4

IR3831WMPbF

Recommended Operating Conditions

Symbol Definition Min Max Units

V

mΩ

μA

V

μA

Vin Input Voltage 1.5 16

Vcc Supply Voltage 4.5 5.5

Boot to SW Supply Voltage 4.5 5.5

Vo Output Voltage 0.6 0.90*Vin

Io Output Current 0 8 A

Fs Switching Frequency 225 1650 kHz

Tj Junction Temperature -40 125 oC

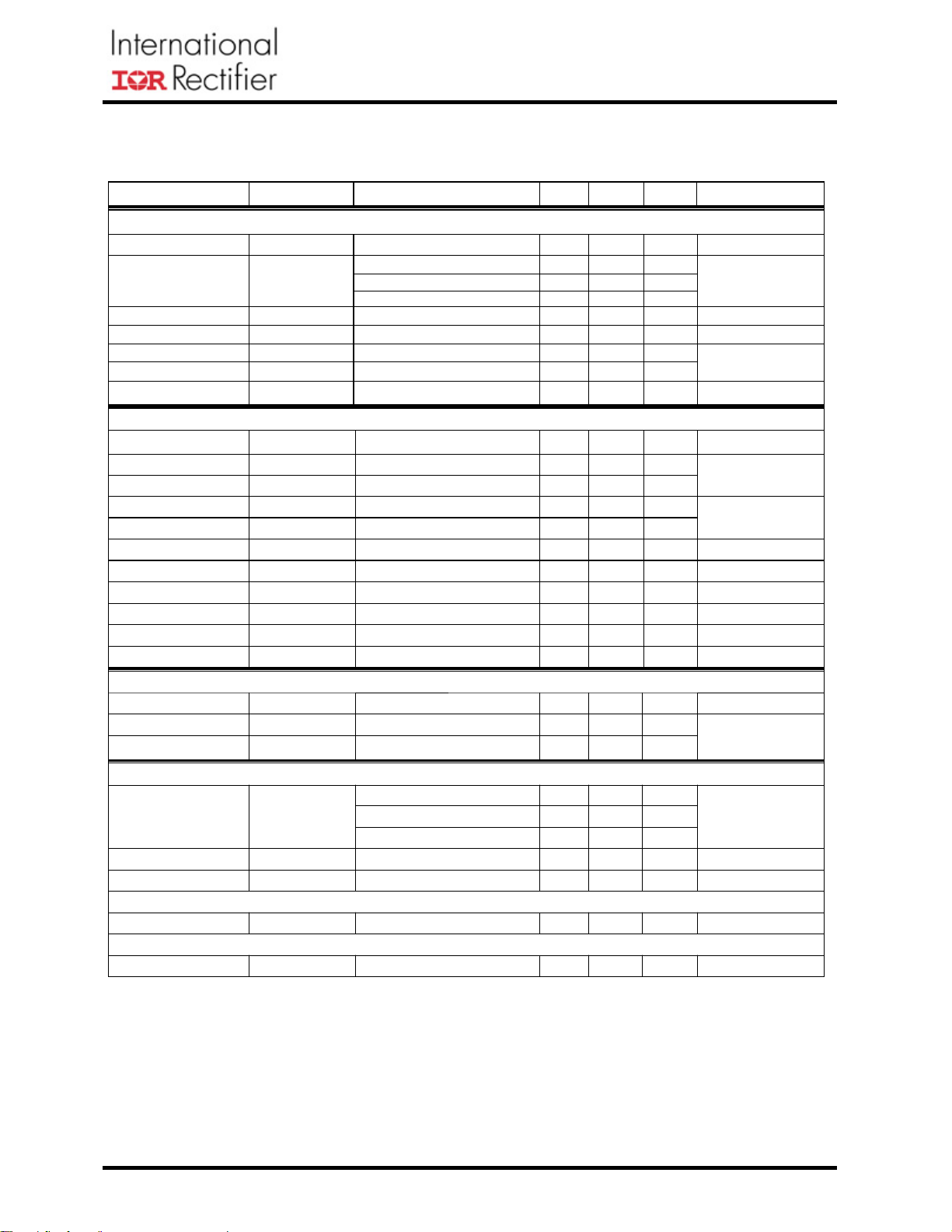

Electrical Specifications

Unless otherwise specified, these specification apply over 4.5V< Vcc<5.5V, Vp=0.6V, Vin=12V,

o

0

C<Tj< 125oC. Typical values are specified at Ta= 25oC.

Parameter Symbol Test Condition Min TYP MAX Units

Power Loss

Power Loss

MOSFET R

Top Switch R

Bottom Switch

Supply Current

VCC Supply Current (Standby)

Vcc Supply Current (Dyn) I

Under Voltage Lockout

VCC-Start-Threshold VCC_UVLO_Start

VCC-Stop-Threshold VCC_UVLO_Stop Vcc Falling Trip Level 3.65 3.85 4.05

Enable-Start-Threshold Enable_UVLO_Start

Enable-Stop-Threshold Enable_UVLO_Stop Supply ramping down 0.9 1.0 1.06

Enable leakage current Ien Enable=3.3V 15

ds(on)

P

Vcc=5V, Vin=12V, Vo=0.75V, Io=8A,

loss

ds(on)_Top

R

ds(on)_Bot

I

SS=0V, No Switching, Enable low 500

CC(Standby)

SS=3V, Vcc=5V, Fs=500kHz

CC(Dyn)

Fs=400kHz, L=0.6uH, Note4

V

=5V, ID=10A, Tj=

Boot -Vsw

Vcc=5V, ID=10A, Tj=

Enable high

Vcc Rising Trip Level 3.95 4.15 4.35

Supply ramping up 1.14 1.2 1.36

25oC

25oC

12 mA

1.28 W

17.8 26.5

8.5 10.7

Rev 13.0

5

IR3831WMPbF

Electrical Specifications (continued)

Unless otherwise specified, these specification apply over 4.5V< Vcc<5.5V, Vp=0.6V, Vin=12V,

o

0

C<Tj< 125oC. Typical values are specified at Ta= 25oC.

Parameter Symbol Test Condition Min TYP MAX Units

Oscillator

Rt Voltage

Frequency F

Ramp Amplitude Vramp Note4 1.8 Vp-p

Ram p Offs et Ramp (os) Note4 0.6 V

Min Pulse Width Dmin(ctrl) Note4 50

Fixe d Off Time Note4 130 200

Max Duty Cycle Dmax Fs=250kHz 92 %

S

Error Amplifie r

Input Offset Voltage Vos Vfb-Vp

Input B ias Current IF b(E/A) -1 +1

Input B ias Current IVp(E/A) -1 +1

Sink Current Isink(E/A) 0.40 0.85 1.2

Source Current Isource(E/A) 8 10 13

Slew Rate SR Note4 7 12 20

Gain-Bandwidth Produ ct GBW P Note4 20 30 40 M Hz

DC Gai n Gain Note4 100 110 120 dB

Maximum Volt age Vmax(E/A) Vc c=4.5V 3.4 3.5 3.75 V

Minim um Voltage Vmin(E/A) 120 220 mV

Common Mode Voltage Note4 0 1 V

Rt=59K 225 250 275

Rt=28.7K 450 500 550

Rt=9.31K, Note4 1350 1500 1650

Vp=0. 6V

0.665 0.7 0.735 V

kHz

ns

-5 0 +5 mV

μA

mA

V/μs

Soft Start/SD

Soft Start Current ISS Source 14 20 26

Soft Start Clamp Voltage Vss(clamp) 2.7 3.0 3.3

Shutdown Output

Thre shol d

SD 0.3

μA

V

Over Current Protection

OCSET Current I

OC Comp Offset Voltage V

SS off time SS_Hiccup 4096 Cycles

OCSET

OFFS ET

Fs=250kHz 20.8 23.6 26.4

Fs=500kHz 43 48.8 54.6

Fs=1500k Hz 136 154 172

Note4 -1 0 0 +10 mV

μA

Bootstrap Diode

Forward V oltage I(Boot)=30mA 180 260 470 mV

Deadband

Deadband time Note4 5 10 30 ns

Rev 13.0

6

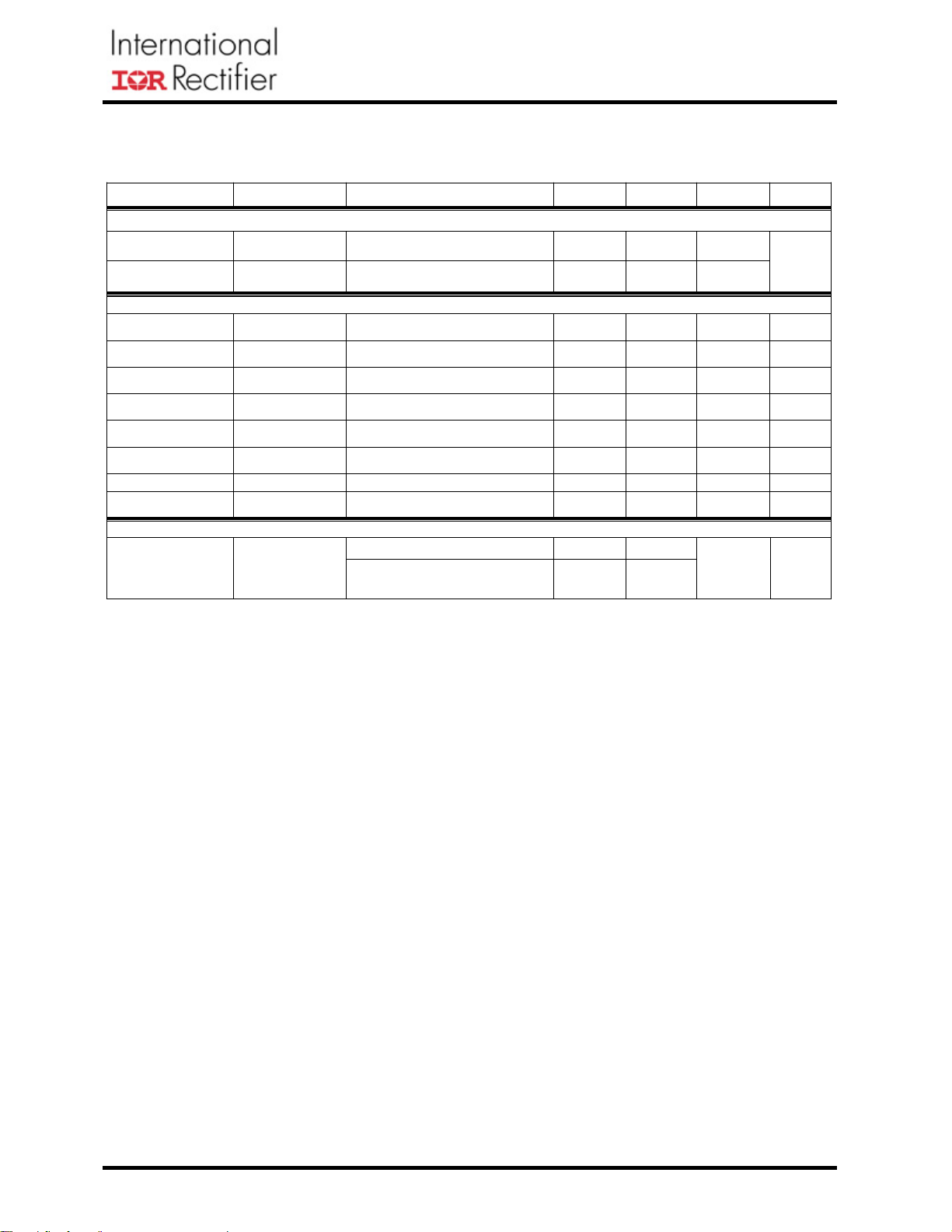

IR3831WMPbF

Electrical Specifications (continued)

Unless otherwise specified, these specification apply over 4.5V< Vcc<5.5V, Vp=0.6V, Vin=12V,

o

0

C<Tj< 125oC. Typical values are specified at Ta= 25oC.

Parameter SYM Test Condition Min TYP MAX Units

Thermal Shutdown

Thermal Shutdown

Hysteresis

Power Good

Power Good upper

Threshold

Upper Threshold

Delay

Power Good lower

Threshold

Lower Threshold

Delay

Delay Comparator

Threshold

Delay Comparator

Hysteresis

PGood Voltage Low PG(voltage) I

Leakage Current I

VPG(upper) Fb Rising 0.660 0.690 0.720 V

VPG(upper)_Dly Fb Rising 256/Fs S

VPG(lower) Fb Falling 0.480 0.510 0.540 V

VPG(lower)_Dly Fb Falling 256/Fs S

PG(Delay) Relative to charge voltage, SS rising 2 2.1 2.3 V

Delay(hys)

0 10

leakage

Switch Node

Isw

Note4

Note4

Note4

=-5mA 0.5 V

PGood

SW=0V, Enable=0V SW Bias Current

SW=0V,Enable=high,SS=3V,Vp=0V,

Note4

140

20

260 300 340 mV

6

o

C

μA

μA

Note3: Cold temperature performance is guaranteed via correlation using statistical quality control. Not tested in production.

Note4: Guaranteed by Design but not tested in production.

Rev 13.0

7

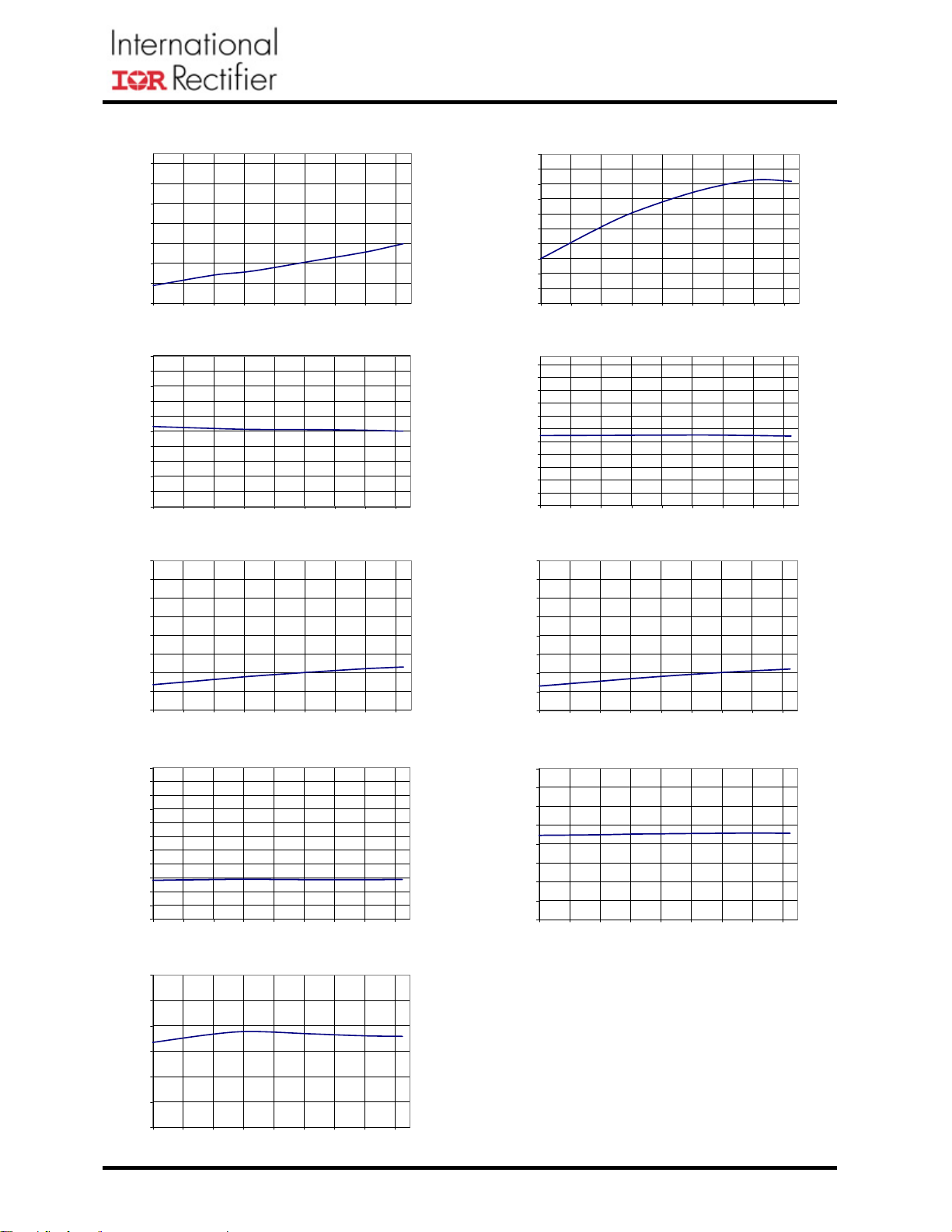

IR3831WMPbF

TYPICAL OPERATING CHARACTERISTICS (-40oC - 125oC) Fs=500 kHz

Icc(Standby)

290

270

250

230

[uA]

210

190

170

150

-40 -20 0 20 40 60 80 1 00 120

550

540

530

520

510

500

[kHz]

490

480

470

460

450

-40 -20 0 20 40 60 80 100 120

4.46

4.41

4.36

4.31

4.26

[V]

4.21

4.16

4.11

4.06

-40-20 0 20406080100120

Temp[ oC]

FREQUENCY

Temp[

Vcc(UVLO) Start

o

C]

Temp[ oC]

1.36

1.34

1.32

1.30

1.28

1.26

[V]

1.24

1.22

1.20

1.18

1.16

1.14

-40 -20 0 20 40 60 80 100 120

Enable(UVLO) Start

Temp[ oC]

26.0

24.0

22.0

20.0

[uA]

18.0

16.0

14.0

-40-20 0 20406080100120

ISS

Temp[ oC]

12.5

12.4

12.3

12.2

12.1

12.0

[mA]

11.9

11.8

11.7

11.6

11.5

-40-20 0 20406080100120

54.0

53.0

52.0

51.0

50.0

49.0

[uA]

48.0

47.0

46.0

45.0

44.0

43.0

-40-20 0 20406080100120

4.16

4.11

4.06

4.01

3.96

[V]

3.91

3.86

3.81

3.76

-40-20 0 20406080100120

1.06

1.04

1.02

1.00

0.98

[V]

0.96

0.94

0.92

0.90

-40 -20 0 20 40 60 80 100 120

Ic(Dyn)

o

Temp[

C]

IOCSET(500kHz)

Temp[ oC]

Vcc(UVLO) Stop

Temp[ oC]

Enable(UVLO) Stop

ο

C]

Temp[

Rev 13.0

8

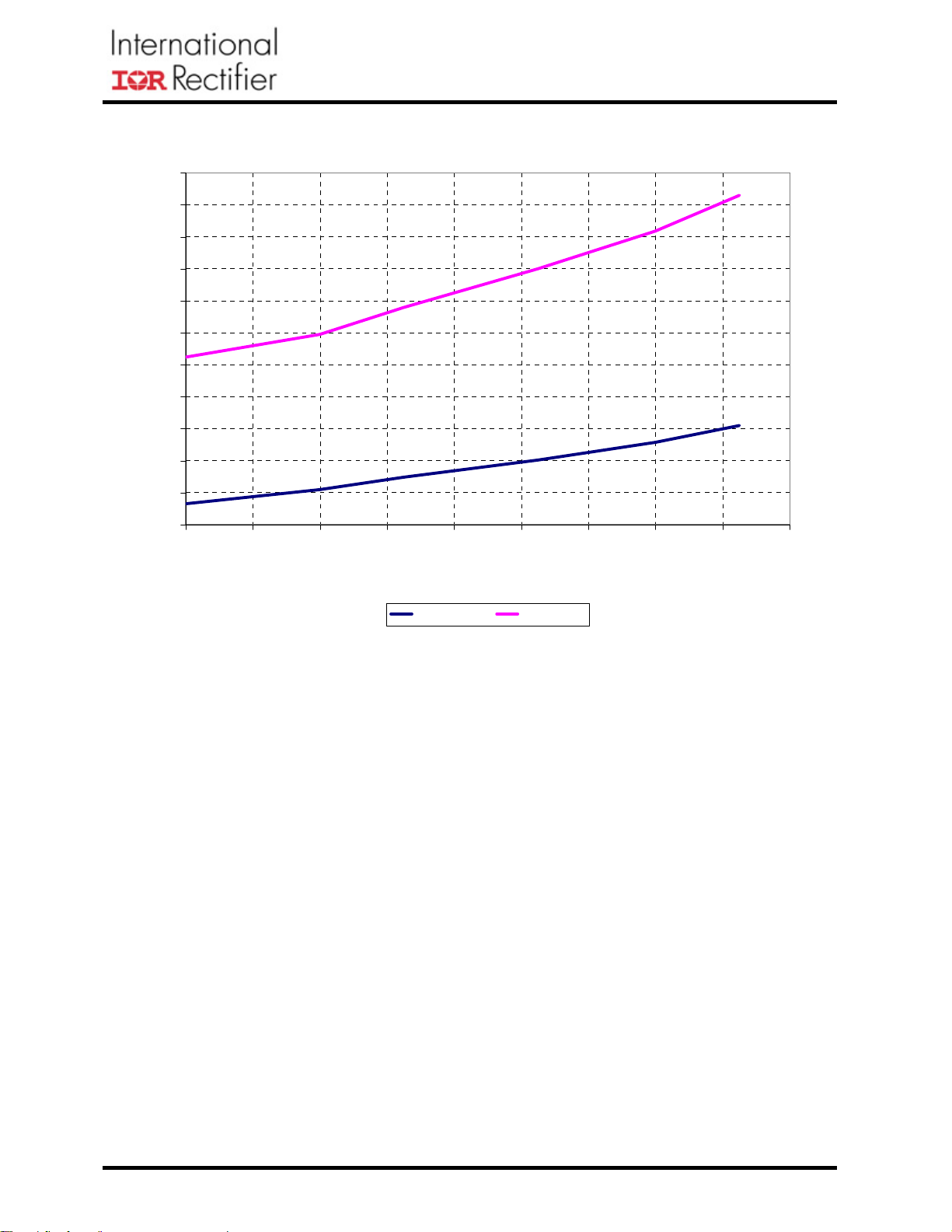

Rdson of MOSFETs Over Temperature at Vcc=5V

28

26

24

22

]

Ω

20

18

16

14

Resistance [m

12

10

8

6

-40 -20 0 20 40 60 80 100 120 140

IR3831WMPbF

Temperature [°C]

Sync-FET Ctrl-FET

Rev 13.0

9

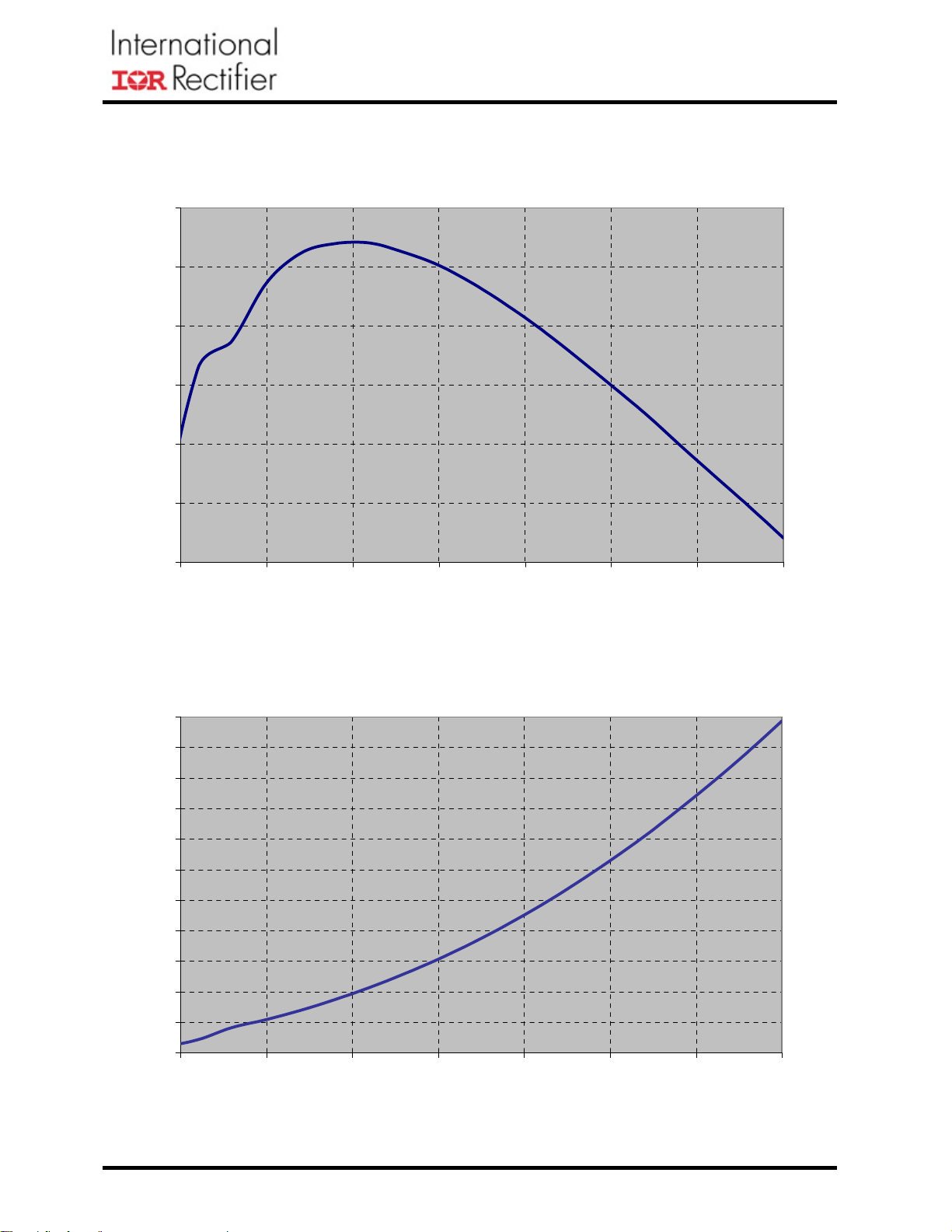

Typical Efficiency and Power Loss Curves

Vin=12V, Vo=0.75V, Vcc=5V, Io=1.0A-8A, F

Temperature, No Air Flow

89

88

87

86

Efficiency (%)

85

84

IR3831WMPbF

=400kHz, L=0.6uH (MPL104-0R from Delta), Room

s

83

12345678

Load Current (A)

1.2

1.1

1.0

0.9

0.8

0.7

0.6

0.5

Power Loss (W)

0.4

0.3

0.2

0.1

Rev 13.0

12345678

Load Current (A)

10

Loading...

Loading...