Data Sheet No. PD94713

IR3637SPBF

1% ACCURA TE SYNCHRONOUS PWM CONTROLLER

FEATURES

0.8V Reference Voltage

Operates with a single 5V Supply Volt age

Internal 400kHz Oscillator

Soft-St art Function

Fixed Frequency Volt age Mode

Short Circuit Protection

APPLICATIONS

Computer Peripheral Voltage Regulator

Memory Power supplies

Graphics Card

Low cost on-board DC to DC

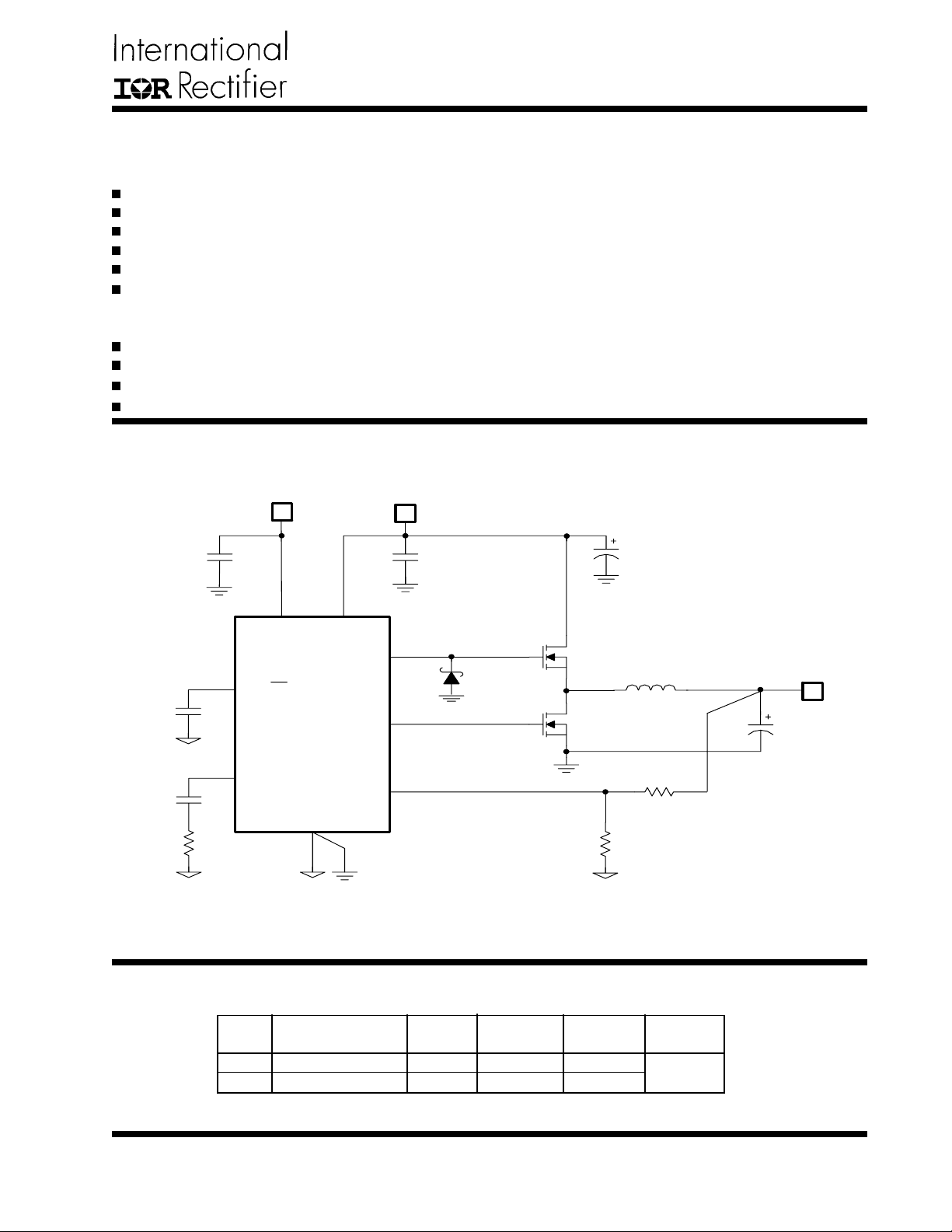

TYPICAL APPLICA TION

12V

C3

5V

C2

DESCRIPTION

The IR3637 controller IC is designed to provide a simple

synchronous Buck regulator for on-board DC to DC applications in a small 8-pin SOIC. The output voltage can

be precisely regulated using the internal 0.8V reference

voltage for low voltage applications.

The IR3637 operates at a fixed internal 400kHz switching frequency to reduce the component size.

The device features under-voltage lockout for both input

supplies, an external programmable soft-start function

as well as output under-voltage detection that latches

off the device when an output short is detected.

C1

C4

C5

R1

Vc Vcc

Q1

L1

Q2

R3

R2

SS/SD

IR3637

Comp

HDrv

D1

LDrv

Fb

Gnd

Figure 1 - T ypical application of IR3637.

ORDERING INFORMA TION

PKG PACKAGE PIN PARTS PARTS T & R

DESIG DESCRIPTION COUNT PER TUBE PER REEL Oriantation

S IR3637SPBF 8 95 ----- S IR3637STRPBF 8 ------- 2500

Fig A

Vout

C6

Rev. 1.1

06/16/05

www.irf.com

1

IR3637SPBF

ABSOLUTE MAXIMUM RA TINGS

Vcc Supply Voltage ................................................ 16V

Vc Supply Voltage .................................................. 25V

Storage Temperature Range ..................................... -65°C To 150°C

Operating Junction Temperature Range ..................... 0°C T o 125°C

ESD Classification ................................................. HMB Class 2 (2KV) JEDEC Standard

Moisture Sensitivity Level ........................................ JEDEC Level 1 @ 260°C

Caution: Stresses above those listed in “Absolute Maximum Rating” may cause permanent damage to the device. These are stress

ratings only and function of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to “Absolute Maximum Rating” conditions for extended periods may affect device reliability

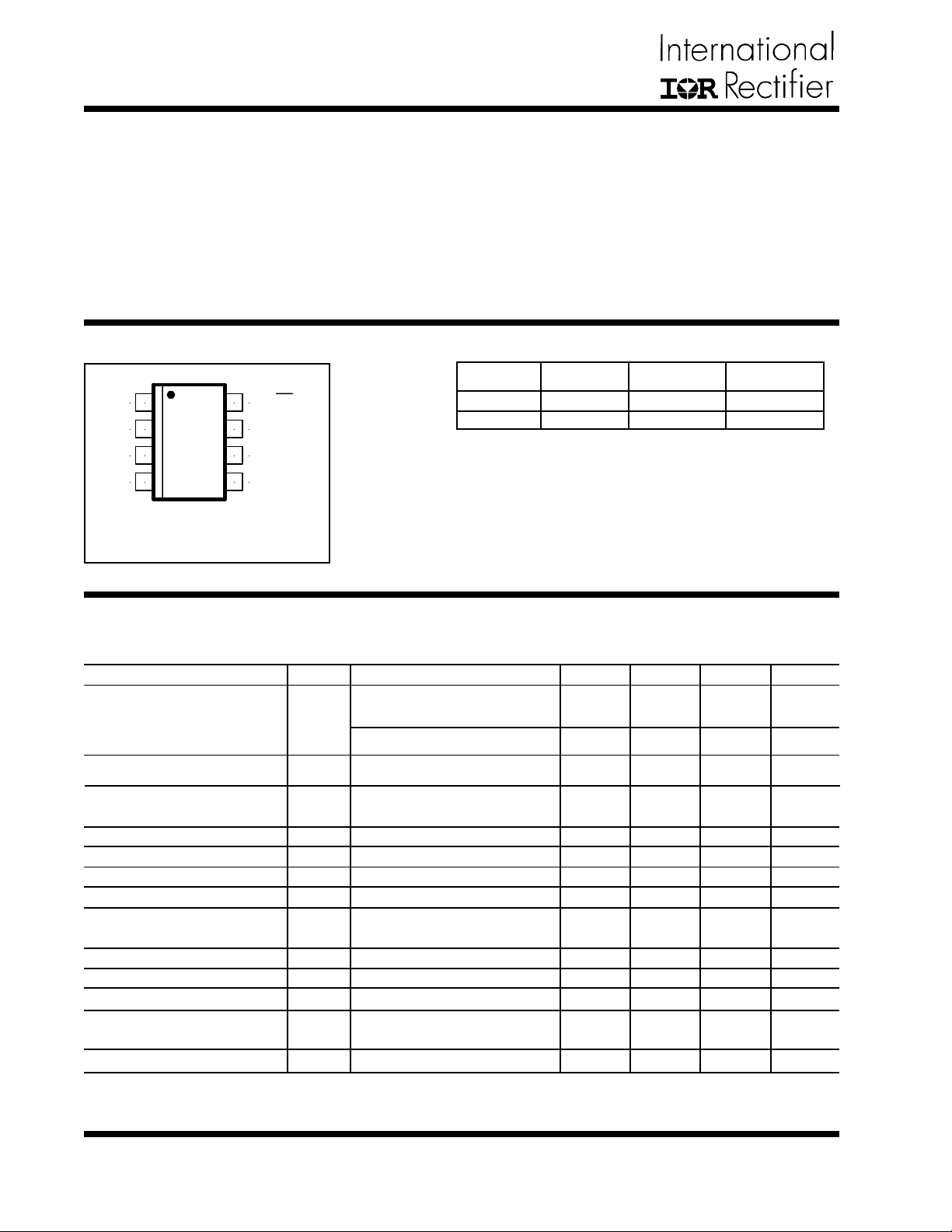

P ACKAGE INFORMA TION

1

Fb

2

Vcc

3

LDrv

4

Gnd HDrv

θJA=154°C/W

θJC=41.2°C/W

8

7

6

5

SS/SD

Comp

Vc

Recommended Operating Conditions

Parameter Min Max Units

Vcc 4.5 5.5 V

Vc 8 14 V

ELECTRICAL SPECIFICA TIONS

Unless otherwise specified, these specifications apply over Vcc=5V , Vc=12V and 0°C<Tj<125°C.

PARAMETER SYM TEST CONDITION MIN TYP MAX UNITS

Feedback Voltage

Fb Voltage

Fb Volt age Line Regulation

UVLO

UVLO Threshold - Vcc

UVLO Hysteresis - Vcc

UVLO Threshold - Vc

UVLO Hysteresis - Vc

UVLO Threshold - Fb

Supply Current

Vcc Dynamic Supply Current

Vc Dynamic Supply Current

Vcc Static Supply Current

Vc Static Supply Current

Soft-Start Section

Charge Current

Shutdown Threshold

VFB

LREG

UVLO Vcc

UVLO Vc

UVLO Fb

Dyn Icc

Dyn Ic

ICCQ

ICQ

SSIB

SD

25°C<Tj<75°C

0°C<Tj<125°C

4.5<Vcc<5.5

Supply Ramping Up

Supply Ramping Up

Fb Ramping Down

Freq=400kHz, CL=1500pF

Freq=400kHz, CL=1500pF

SS=0V

SS=0V

SS=0V

Note1

0.792

0.789

4.0

3.1

0.3

4

6

1

0.5

-15

0.800

0.800

4.2

0.25

3.3

0.2

0.4

8

15

3.3

1

-25

0.808

0.81 1

0.1

4.4

3.5

0.5

16

20

6

4.7

-35

0.4

V

V

%

V

V

V

V

V

mA

mA

mA

mA

µA

V

Note1: Guaranteed by design. Not production tested.

2

www.irf.com

Rev.1.1

06/16/05

IR3637SPBF

PARAMETER SYM TEST CONDITION MIN TYP MAX UNITS

Error Amp

Fb Voltage Input Bias Current

Fb Voltage Input Bias Current

Transconductance

Oscillator

Frequency

SS=3V, Fb=0.6V

IFB1

SS=0V, Fb=0.6V

IFB2

gm

Freq

450

360

-0.1

-64

600

400

800

440

µA

µA

µmho

kHz

Ramp-Amplitude Volt age

V

RAMP

Output Drivers

Rise Time, Hdrv , Ldrv

Fall Time,Hdrv , Ldrv

Dead Band Time

Max Duty Cycle

Min Duty Cycle

CL=1500pF, Vcc=12V,2V to 9V

Tr

C

Tf

TDB

TON

TOFF

L=1500pF, Vcc=12V, 9V to 2V

Vcc=12V, 2V to 2V

Fb=0.6V , Freq=400kHz

Fb=1V

PIN DESCRIPTIONS

PIN# PIN SYMBOL PIN DESCRIPTION

1

2

3

4

Fb

Vcc

LDrv

Gnd

This pin is connected directly to the output of the switching regulator via resistor divider to

set the output voltage and provide feedback to the error amplifier .

This pin provides biasing for the internal blocks of the IC as well as powers the low side

driver. A minimum of 0.1µF, high frequency capacitor must be connected from this pin to

ground to provide peak drive current capability .

Output driver for the synchronous power MOSFET .

IC's ground pin. This pin must be connected directly to the ground plane. A high frequency

capacitor (0.1 to 1µF) must be connected from Vcc and Vc pins to this pin for noise free

operation.

40

81

1.25

30

30

150

85

60

60

200

0

V

ns

ns

ns

%

%

5

6

7

8

Rev. 1.1

06/16/05

HDrv

Vc

Comp

SS / SD

Output driver for the high side power MOSFET . The negative voltage at this pin may cause

instability for the gate drive circuit. To prevent this, a low forward voltage drop diode (e.g.

BA T54 or 1N4148) is required between this pin and ground.

This pin is connected to a voltage that must be at least 4V higher than the bus voltage

(assuming 5V threshold MOSFET) and powers the high side output driver. A minimum of

0.1µF, high frequency capacitor must be connected from this pin to ground to provide

peak drive current capability .

Compensation pin of the error amplifier. An external resistor and capacitor network is

typically connected from this pin to ground to provide loop compensation.

This pin provides user programmable soft-start function. Connect an extrnal capacitor

from this pin to ground to set the start up time of the output. The converter can be shutdown by pulling this pin below 0.4V . During shutdown the upper FET is turned off and the

lower FET is turned on.

www.irf.com

3

IR3637SPBF

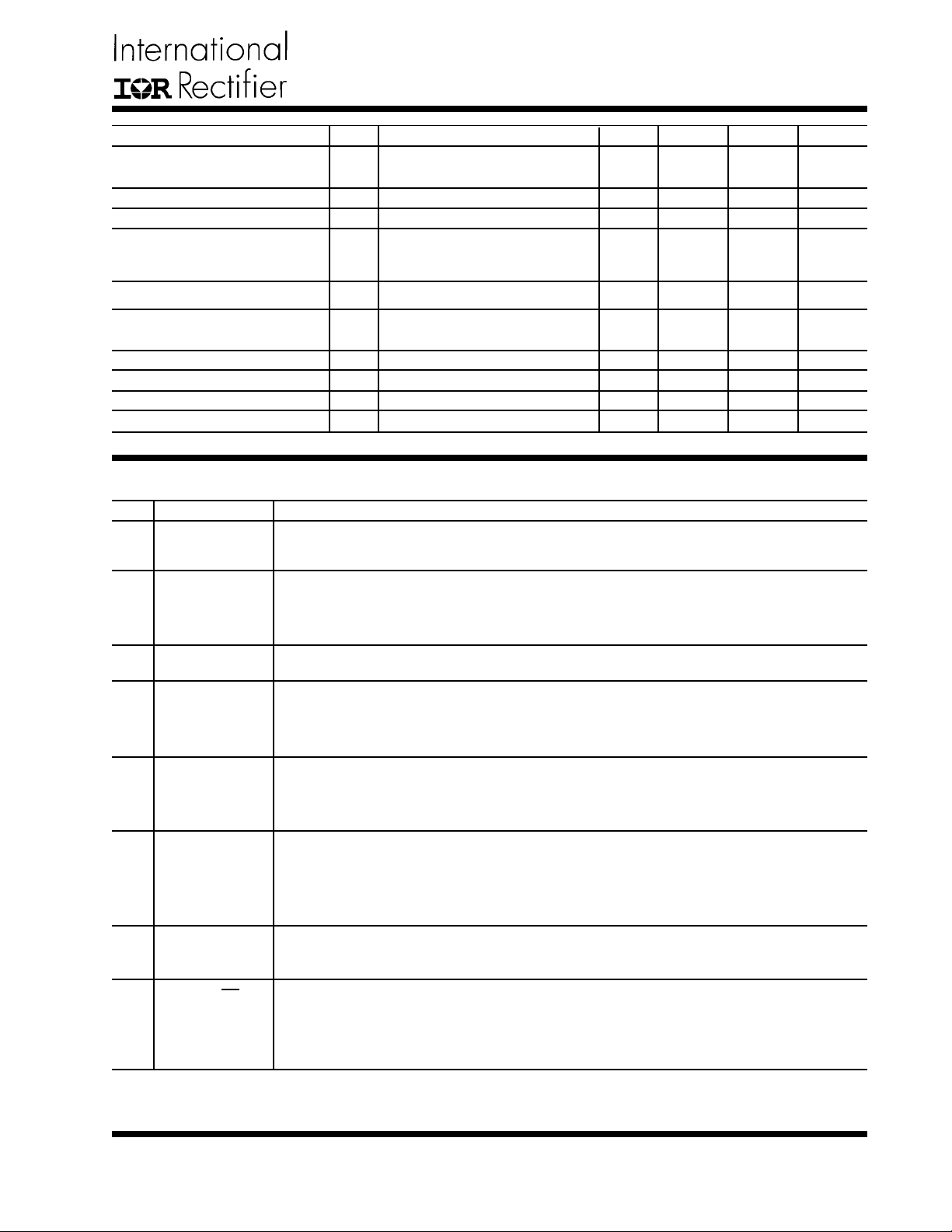

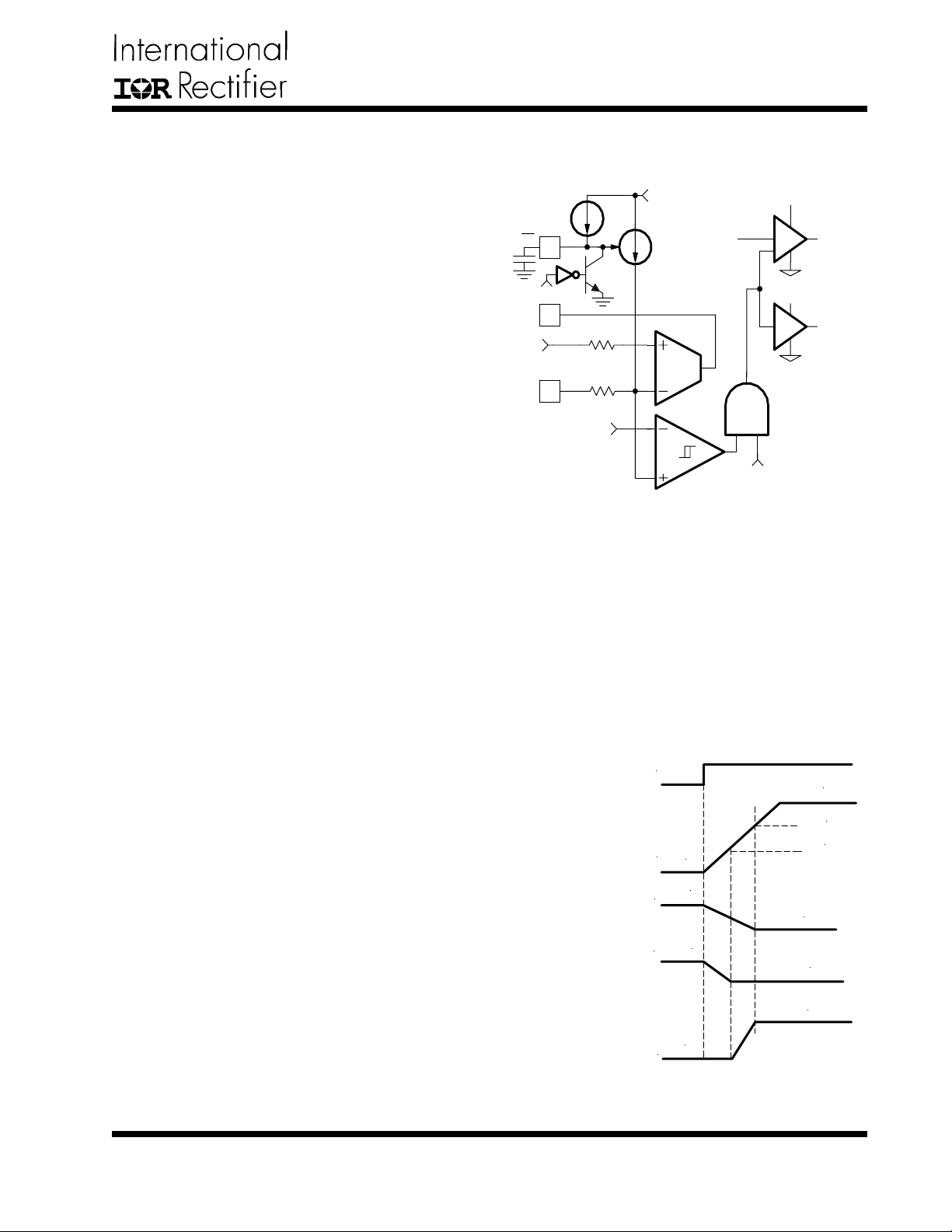

BLOCK DIAGRAM

SS/SD

POR

Fb

Comp

8

0.8V

1

7

3V

25uA

25K

25K

64uA Max

Error Amp

Vcc

4.2V

Vc

3.3V

0.4V

Ct

Oscillator

Error Comp

FbLo Comp

POR

Bias

Generator

S

R

Reset Dom

3V

0.8V

POR

6

Vc

5

HDrv

Q

2

Vcc

3

LDrv

Gnd

4

Figure 2 - Simplified block diagram of the IR3637.

THEORY OF OPERATION

Introduction

The IR3637 is a fixed frequency , voltage mode synchronous controller and consists of a precision reference

voltage, an error amplifier, an internal oscillator , a PWM

comparator , 0.5A peak gate driver, soft-start and shutdown circuits (see Block Diagram).

The output voltage of the synchronous converter is set

and controlled by the output of the error amplifier; this is

the amplified error signal from the sensed output voltage

and the reference voltage.

This voltage is compared to a fixed frequency linear

sawtooth ramp and generates fixed frequency pulses of

variable duty-cycle, which drives the two N-channel external MOSFET s.The timing of the IC is provided through

an internal oscillator circuit which uses on-chip capacitor to set the oscillation frequency to 400kHz.

Short-Circuit Protection

The output is protected against the short-circuit. The

IR3637 protects the circuit for shorted output by sensing the output voltage (through the external resistor divider). The IR3637 shuts down the PWM signals, when

the output voltage drops below 0.4V .

Under-V oltage Lockout

The under-voltage lockout circuit assures that the

MOSFET driver outputs remain in the off state whenever

the supply voltage drops below set parameters. Lockout

occurs if Vc or Vcc fall below 3.3V and 4.2V respectively . Normal operation resumes once Vc and Vcc rise

above the set values.

Shutdown

The converter can be shutdown by pulling the soft-start

pin below 0.4V. This can be easily done by using an

external small signal transistor. During shut down the control MOSFET driver is turned off and the synchronous

MOSFET driver is turned on.

4

www.irf.com

Rev.1.1

06/16/05

THEORY OF OPERATION

IR3637SPBF

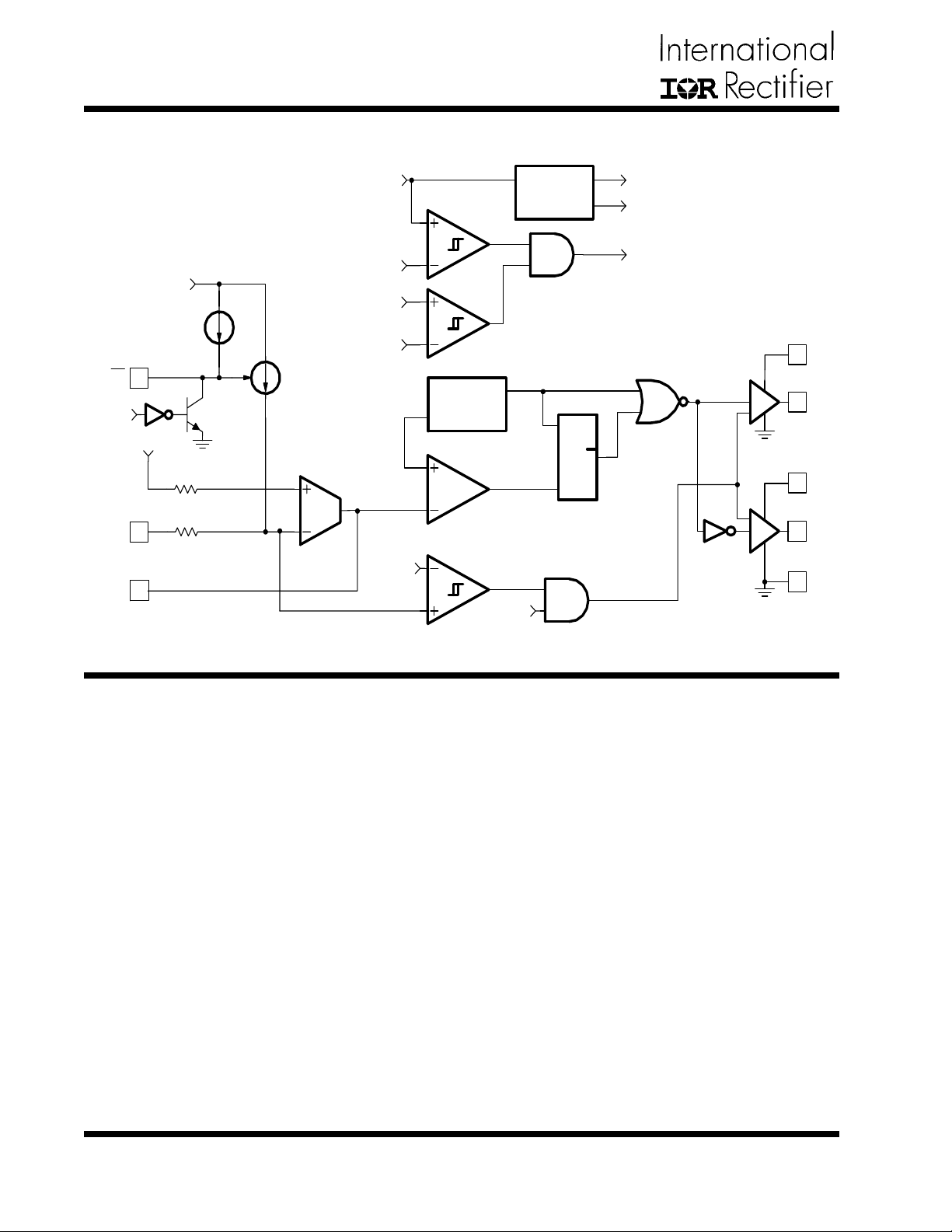

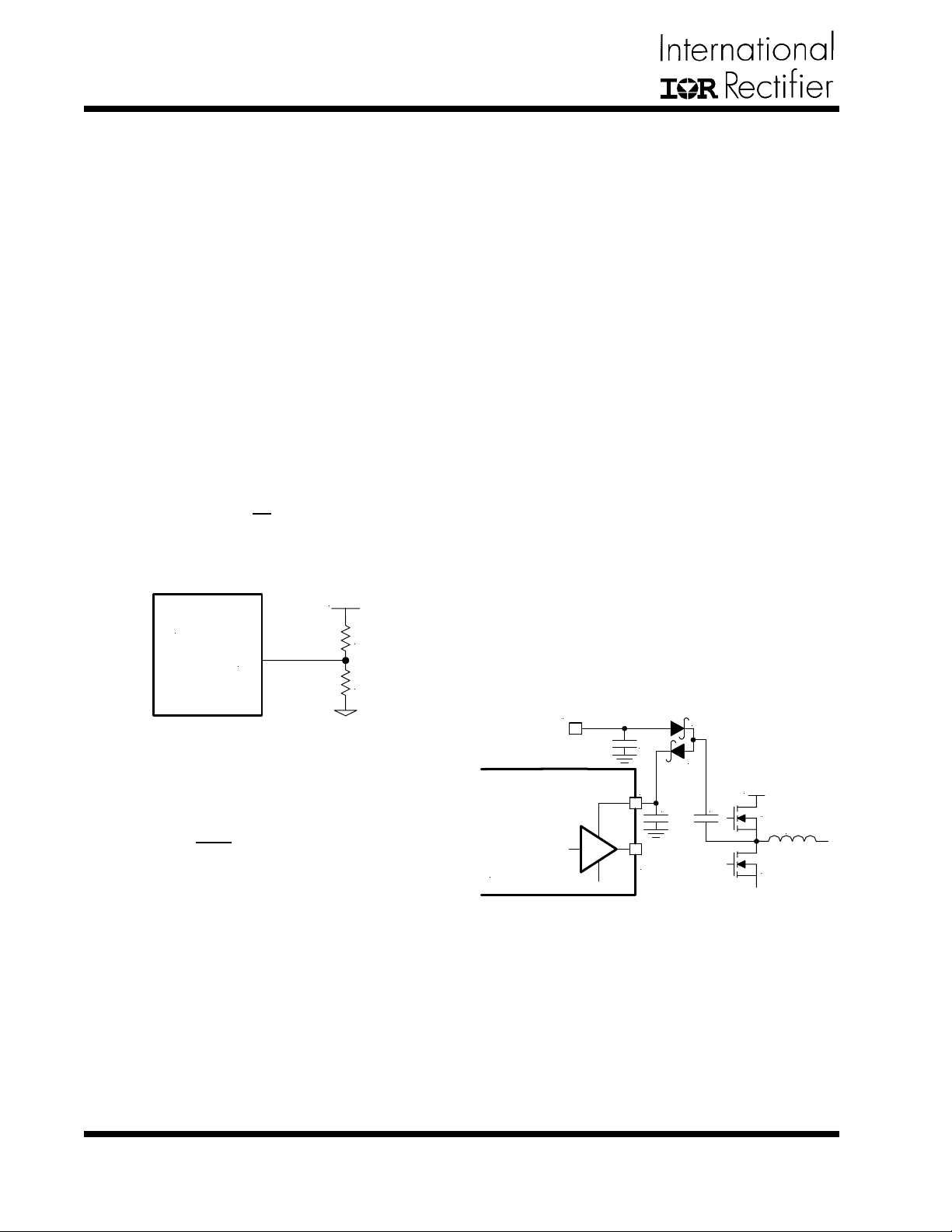

Soft-Start

The IR3637 has a programmable soft-start to control the

output voltage rise and limit the current surge at the startup. To ensure correct start-up, the soft-start sequence

initiates when the Vc and Vcc rise above their threshold

(3.3V and 4.2V respectively) and generates the Power

On Reset (POR) signal. Soft-start function operates by

sourcing an internal current to charge an external capacitor to about 3V . Initially , the soft-start function clamps

the E/A ’s output of the PWM converter and disables the

short circuit protection. During the power up, the output

starts at zero and voltage at Fb is below 0.4V. The feedback UVLO is disabled during this time by injecting a

current (64µA) into the Fb. This generates a voltage

about 1.6V (64µA×25K) across the negative input of E/

A and positive input of the feedback UVLO comparator

(see Figure 3).

The magnitude of this current is inversely proportional to

the voltage at soft-start pin.

The 20µA current source starts to charge up the external capacitor. In the mean time, the soft-start voltage

ramps up, the current flowing into Fb pin starts to decrease linearly and so does the voltage at the positive

pin of feedback UVLO comparator and the voltage negative input of E/A.

3V

64uA

Max

Error Amp

Feeback

UVLO Comp

HDrv

LDrv

POR

SS/SD

Comp

0.8V

Fb

25uA

POR

64uA

25K

25K

0.4V

×

25K=1.6V

When SS=0

Figure 3 - Soft-start circuit for IR3637.

The output start-up time is the time period when softstart capacitor voltage increases from 1V to 2V . The st artup time will be dependent on the size of the external

soft-start capacitor . The st art-up time can be estimated

by:

25µA×TSTART/CSS = 2V -1V

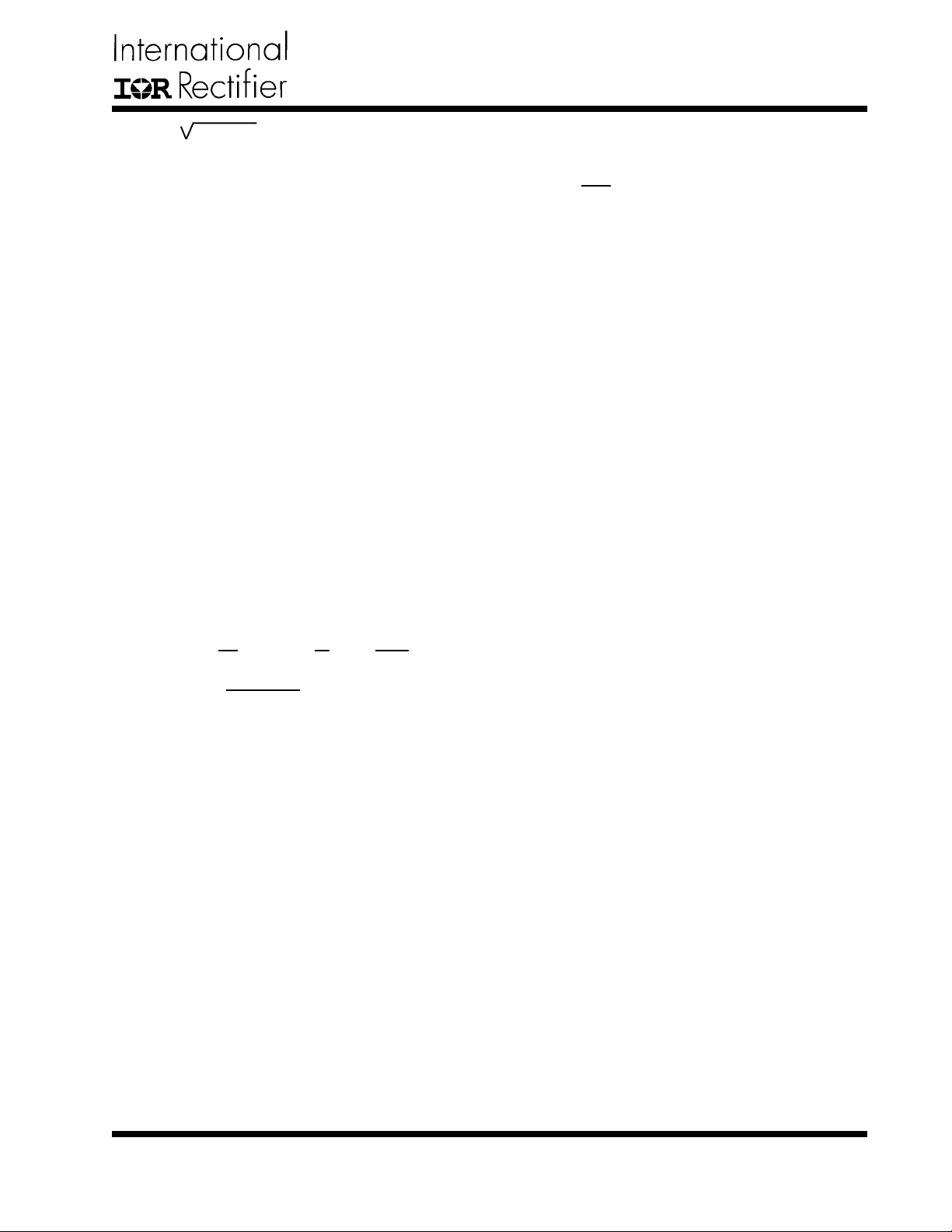

When the soft-start capacitor is around 1V, the current

flowing into the Fb pin is approximately 32µA. The voltage at the positive input of the E/A is approximately:

32µA×25K = 0.8V

The E/A will start to operate and the output voltage starts

to increase. As the soft-start capacitor voltage continues to go up, the current flowing into the Fb pin will keep

decreasing. Because the voltage at pin of E/A is regulated to reference voltage 0.8V , the voltage at the Fb is:

VFB = 0.8-25K×(Injected Current)

The feedback voltage increases linearly as the injecting

current goes down. The injecting current drops to zero

when soft-start voltage is around 2V and the output voltage goes into steady state.

As shown in Figure 4, the positive pin of feedback UVLO

comparator is always higher than 0.4V , therefore, feedback UVLO is not functional during soft-start.

For a given start up time, the soft-start capacitor can be

estimated as:

CSS ≅ 25µA×TSTART/1V

Output of UVLO

Current flowing

Voltage at negative input

of Error Amp and Feedback

UVLO comparator

Voltage at Fb pin

POR

Soft- Start

Voltage

into Fb p in

0V

64uA

≅

1.6V

0V

0uA

0.8V

0.8V

3V

≅

2V

≅

1V

Figure 4 - Theoretical operational waveforms

during soft-start.

Rev. 1.1

06/16/05

www.irf.com

5

IR3637SPBF

APPLICA TION INFORMA TION

Design Example:

The following example is a typical application for IR3637.

Appliaction circuit is shown in page 12.

VIN = Vcc = 5V

Vc=12V

VOUT = 1.8V

IOUT = 6A

∆VOUT = 50mV

FS = 400kHz

Output Voltage Programming

Output voltage is programmed by reference voltage and

external voltage divider . The Fb pin is the inverting input

of the error amplifier, which is internally referenced to

0.8V . The divider is ratioed to provide 0.8V at the Fb pin

when the output is at its desired value. The output voltage is defined by using the following equation:

R6

VOUT = VREF ×

When an external resistor divider is connected to the

output as shown in Figure 5.

1 +

( )

IR3637

Figure 5 - T ypical application of the IR3637 for pro-

gramming the output voltage.

---(1)

R5

Fb

V

OUT

R

6

R

5

Css ≅ 25×tSTART (µF) ---(2)

Where tSTART is the desired start-up time (ms)

For a start-up time of 4ms, the soft-start capacitor will

be 0.1µF. Choose a ceramic capacitor at 0.1µF.

Boost Supply for Single 5V appliaction

T o drive the high side switch, it is necessary to supply a

gate voltage at least 4V grater than the bus voltage. This

is achieved by using a charge pump configuration as

shown in Figure 6. This method is simple and inexpensive. The operation of the circuit is as follows: when the

lower MOSFET is turned on, the capacitor (C1) is pulled

down to ground and charges, up to VBUS value, through

the diode (D1). The bus voltage will be added to this

voltage when upper MOSFET turns on in next cycle,

and providing supply voltage (Vc) through diode (D2). Vc

is approximately:

Vc ≅ 2VBUS - (VD1 + VD2)

Capacitors in the range of 0.1µF and 1µF are generally

adequate for most applications. The diode must be a

fast recovery device to minimize the amount of charge

fed back from the charge pump capacitor into V

diodes need to be able to block the full power rail voltage, which is seen when the high side MOSFET is

switched on. For low voltage application, schottky diodes can be used to minimize forward drop across the

diodes at start up.

V

BUS

C3

D1

D2

BUS. The

Equation (1) can be rewritten as:

VOUT

R6 = R5 ×

Choose R5 = 1KΩ

This will result to R6 = 1.25KΩ

If the high value feedback resistors are used, the input

bias current of the Fb pin could cause a slight increase

in output voltage. The output voltage set point can be

more accurate by using precision resistor.

Soft-Start Programming

The soft-start timing can be programmed by selecting

the soft-start capacitance value. The start-up time of the

converter can be calculated by using:

6

- 1

( )

VREF

www.irf.com

V

C1

BUS

Q1

L

Q2

Rev.1.1

06/16/05

Vc

C2

IR3637

Figure 6 - Charge pump circuit.

Input Capacitor Selection

The input filter capacitor should be based on how much

ripple the supply can tolerate on the DC input line. The

ripple current generated during the on time of upper

MOSFET should be provided by input capacitor . The RMS

value of this ripple is expressed by:

HDrv

IR3637SPBF

RMS = IOUT D×(1-D) ---(3)

I

Where:

D is the Duty Cycle, D=VOUT/VIN.

IRMS is the RMS value of the input capacitor current.

IOUT is the output current for each channel.

For IOUT=6A and D=0.36, the IRMS=2.8A

For higher efficiency , low ESR capacitor is recommended.

Two capacitors of Sanyo's TPB series PosCap with

150µF, 6.3V, 40mΩ ESR and 1.4A ripple current will

meet the ripple current requirement.

Inductor Selection

The inductor is selected based on output power, operating frequency and efficiency requirements. Low inductor

value causes large ripple current, resulting in the smaller

size, faster response to a load transient but poor efficiency and high output noise. Generally , the selection of

inductor value can be reduced to desired maximum ripple

current in the inductor (∆i). The optimum point is usually

found between 20% and 50% ripple of the output current.

For the buck converter, the inductor value for desired

operating ripple current can be determined using the following relation:

VIN - VOUT = L× ; ∆t = D× ; D =

L = (VIN - VOUT)× ---(5)

∆i

∆t

VOUT

VIN×∆i×fS

1

fS

VOUT

VIN

Where:

VIN = Maximum Input Volt age

VOUT = Output Voltage

∆i = Inductor Ripple Current

fS = Switching Frequency

∆t = Turn On Time

D = Duty Cycle

The ESR of the output capacitor is calculated by the

following relationship:

ESR ≤ ---(4)

∆VO

∆IO

Where:

∆VO = Output Volt age Ripple

∆IO = Inductor Ripple Current

∆VO=50mV and ∆IO=2.4A

Results to ESR=20.8mΩ

The Sanyo TPB series, PosCap capacitor is a good

choice. The 6TPB150M 150µF , 6.3V has an ESR 40mΩ.

Selecting two of these capacitors in parallel, results to

an ESR of ≅ 20mΩ which achieves our low ESR goal.

Power MOSFET Selection

The IR3637 uses two N-Channel MOSFET s. The selections criteria to meet power transfer requirements is

based on maximum drain-source voltage (V

DSS), gate-

source drive voltage (VGS), maximum output current, Onresistance RDS(on) and thermal management.

The MOSFET must have a maximum operating voltage

(VDSS) exceeding the maximum input voltage (VIN).

The gate drive requirement is almost the same for both

MOSFET s. Logic-level transistor can be used and caution should be taken with devices at very low VGS to prevent undesired turn-on of the complementary MOSFET ,

which results a shoot-through current.

The total power dissipation for MOSFET s includes conduction and switching losses. For the Buck converter

the average inductor current is equal to the DC load current. The conduction loss is defined as:

PCOND (Upper Switch) = ILOAD × RDS(on) × D × ϑ

PCOND (Lower Switch) = ILOAD × RDS(on) × (1 - D) × ϑ

2

2

If ∆i = 40%(I

O), then the output inductor will be:

L = 1.2µH

The Coilcraft DO3316 series provides a range of inductors in different values, low profile suitable for large currents, 1.5µH, 8A(Isat) is a good choice for this application.

Output Capacitor Selection

The criteria to select the output capacitor is normally

based on the value of the Effective Series Resistance

(ESR). In general, the output capacitor must have low

enough ESR to meet output ripple and load transient

requirements, yet have high enough ESR to satisfy stability requirements.

Rev. 1.1

06/16/05

www.irf.com

ϑ = RDS(ON) T emperature Dependency

The RDS(ON) temperature dependency should be consid-

ered for the worst case operation. This is typically given

in the MOSFET data sheet. Ensure that the conduction

losses and switching losses do not exceed the package

ratings or violate the overall thermal budget.

7

Loading...

Loading...