Data Sheet No.PD60231 revB

IR3621 & ( PbF)

2-PHASE / DUAL SYNCHRONOUS PWM CONTROLLER WITH

OSCILLA TOR SYNCHRONIZA TION AND PRE-BIAS ST ARTUP

FEATURES

Dual Synchronous Controller with 180

Out of Phase Operation

Configurable to 2-Independent Outputs or

Current Share Single Output

Voltage Mode Control

Current Sharing Using Inductor's DCR

Selectable Hiccup or Latched Current

Limit using MOSFET's R

DS(on)

sensing

Latched Over-Voltage Protection

Pre-Bias Start Up

Programmable Switching Frequency up to 500KHz

Two Independent Soft-Starts/Shutdowns

Precision Reference Voltage 0.8V

Power Good Output

External Frequency Synchronization

Thermal Protection

APPLICATIONS

Embedded Networking & Telecom Systems

Distributed Point-of-Load Power Architectures

2-Phase Power Supply

Graphics Card

DDR Memory Applications

Vin

DESCRIPTION

The IR3621 IC combines a dual synchronous buck controller and drivers, providing a cost-effective, high performance

and flexible solution. The IR3621 operates in 2-Phase mode

to produce either 2-independent output voltages or current

share single output for high current application. The 180

out-of-phase operation allows the reduction of input and

output capacitance.

Other key features include two independently programmable

soft-start functions to allow system level sequencing of output voltages in various configurations. The pre-bias protection feature prevents the discharge of the output voltage and

possible damage to the load during start-up when a preexisting voltage is present at the output. Programmable

switching frequency up to 500KHz per phase allows flexibility to tune the operation of the IC to meet system level requirements, and synchronization allows the simplification

of system level filter design. Protection features such as

selectable hiccup or latched current limit, and under voltage

lock-out are provided to give required system level security

in the event of a fault condition.

Vin

IR3621

HDrv1

OCSet1

LDrv1

PGnd1

HDrv2

OCSet2

LDrv2

PGnd2

IR3621

HDrv1

OCSet1

LDrv1

PGnd1

HDrv2

OCSet2

LDrv2

PGnd2

Vout1

Vin

Vout2

Rt

Comp1

Vin

Vout

Comp2

SS1 / SD

SS2 / SD

Gnd

Rt

Comp1

Comp2

SS1 / SD

SS2 / SD

Gnd

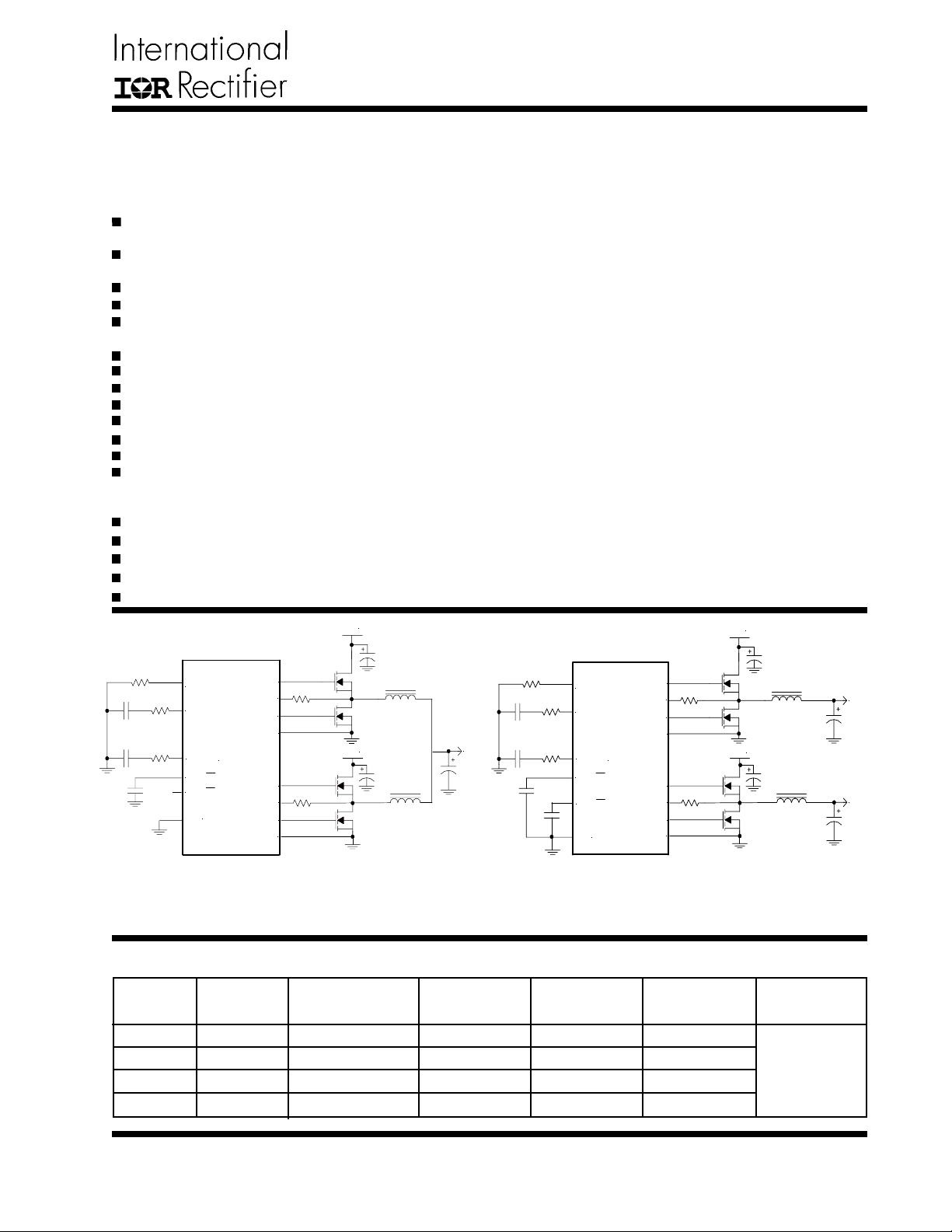

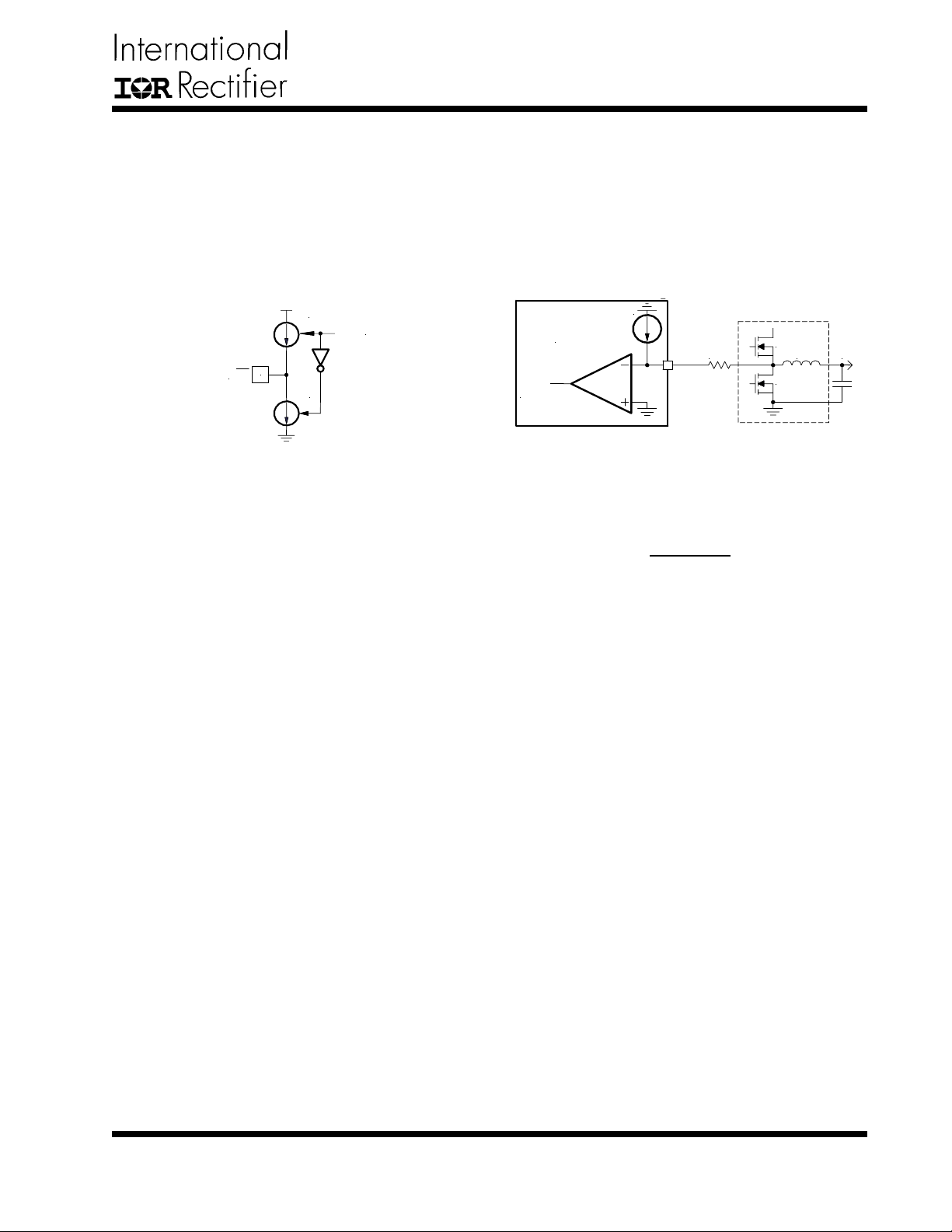

Current share, single output configuration 2-independent output voltage configuration

Figure 1 - Typical application of IR3621 in current share single output and 2-independent output voltage configuration

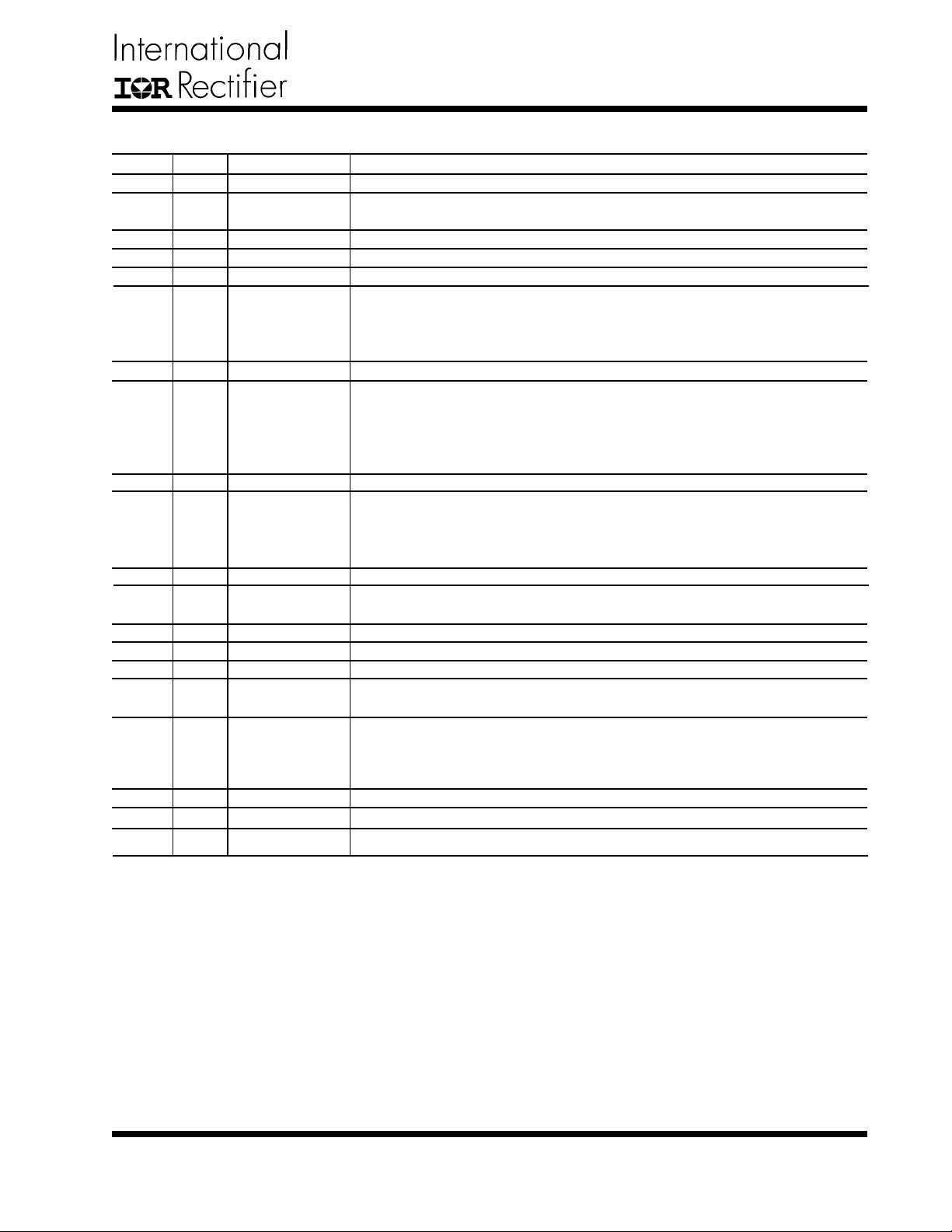

ORDERING INFORMATION

PKG

DESIG

M

M

F

F

PAR T LEADFREE

NUMBER P ART NUMBER

IR3621M IR3621MPbF

IR3621MTR IR3621MTRPbF

IR3621F IR3621FPbF

IR3621FTR IR3621FTRPbF

PIN

COUNT

32

32

28

28

P ARTS

PER TUBE

73

-----50

------

P ARTS

PER REEL

------

6000

------

2500

T & R

Orientation

Fig A

www.irf.com

1

IR3621 & ( PbF)

ABSOLUTE MAXIMUM RATINGS

Vcc, VCL Supply Voltage ........................................... -0.5V To 16V

VcH1 and VcH2 Supply Voltage ................................ -0.5V To 25V

PGOOD.................................................................... -0.5V To 16V

Storage Temperature Range ...................................... -55°C To 150°C

Junction Temperature Range ..................................... -40°C To 150°C

ESD Classification ................................................... JEDEC, JESD22-A114

Caution: Stresses above those listed in “Absolute Maximum Rating” may cause permanent damage to the device. These are stress

ratings only and function of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to “Absolute Maximum Rating” conditions for extended periods may affect device reliability

RECOMMENDED OPERATING CONDITIONS

Parameter Definition Min Max Units

Vcc Supply Voltage 5.5 14.5 V

VcH1,2 Supply Voltage 10 20 V

Fs Operating Frequency 200 500 kHz

Tj Junction Temperature -40 125 °C

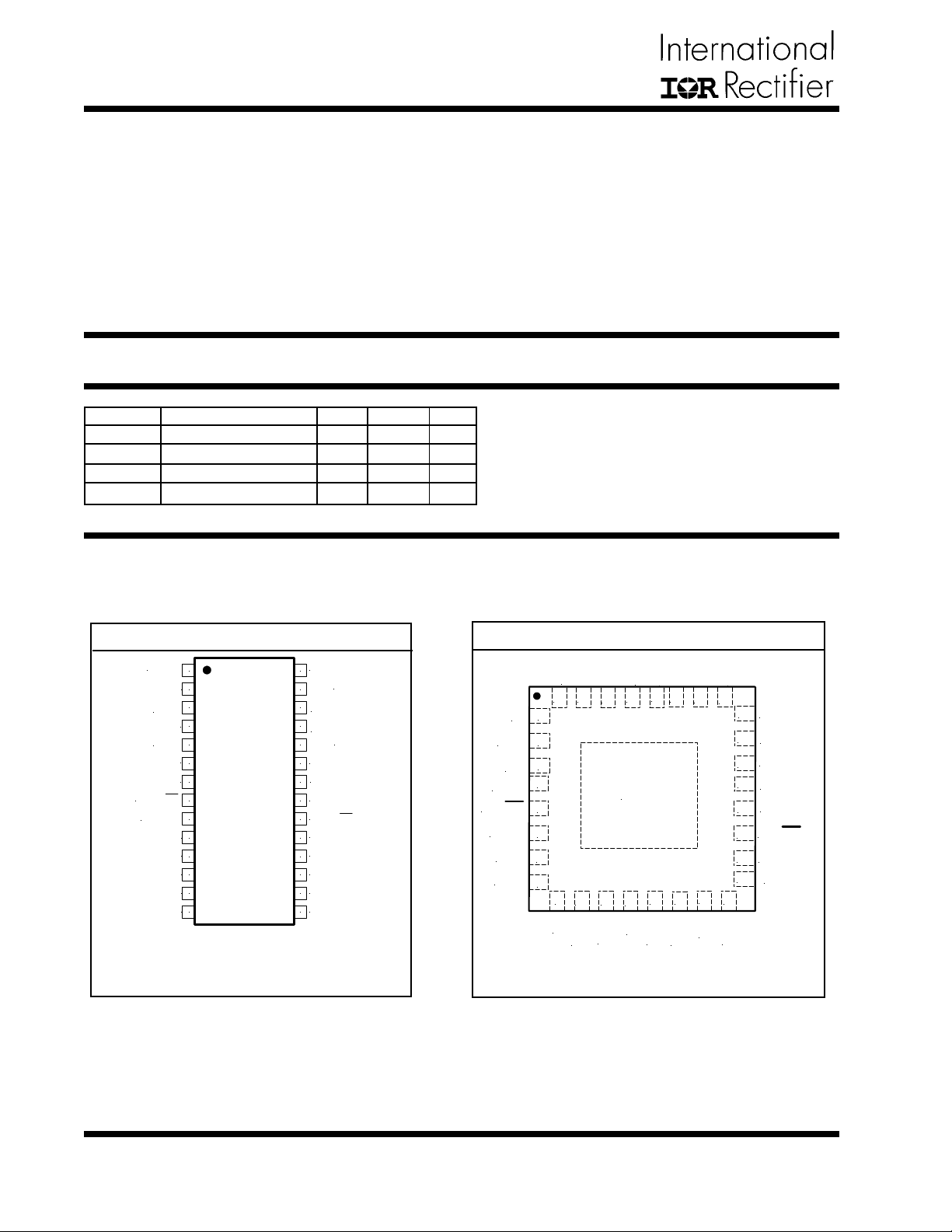

PACKAGE INFORMATION

IR3621F

28-PIN TSSOP (F)

1

PGood

2

CC

V

3

OUT3

V

4

Rt

5

SEN2

V

6

Fb2

7

Comp2

SS2 / SD

8 21

9 20

OCSet2

10 19

VcH2

11 18

HDrv2

12 17

PGnd2 HDrv1

13

LDrv2

14

CL

V

θJA = 75.5 °C/W

θJC =13.3 °C/W

28

Gnd

27

V

26

V

25

Hiccup

24

Sync

23

V

22

Fb1

Comp1

SS1 / SD

OCSet1

VcH1

16

PGnd1

15

LDrv1

REF

P2

SEN1

Rt

V

SEN2

Fb2

Comp2

SS2/SD2

OCSet2

VCH2

HDrv2

IR3621M & IR3621MPbF

32-Lead MLPQ 5mmx5mm (M)

OUT3

NC

V

Vcc

30

11

LDrv2

29

Pad

12

CL

V

3132

1

2

3

4

5

6

7

8

9

10

NC

PGnd2

PGood

13

LDrv1

REFVP2

Gnd

V

28

27

14

PGnd1

NC

26

25

15

16

NC

HDrv1

θJA = 36.0 °C/W

θJC = 1.0 °C/W

24

23

22

21

20

19

18

17

Hiccup

Sync

V

SEN1

Fb1

Comp1

SS1/SD1

OCSet1

VcH1

2

Exposed pad on underside is connected to a copper

pad through vias for 4-layer PCB board design.

www.irf.com

IR3621 & ( PbF)

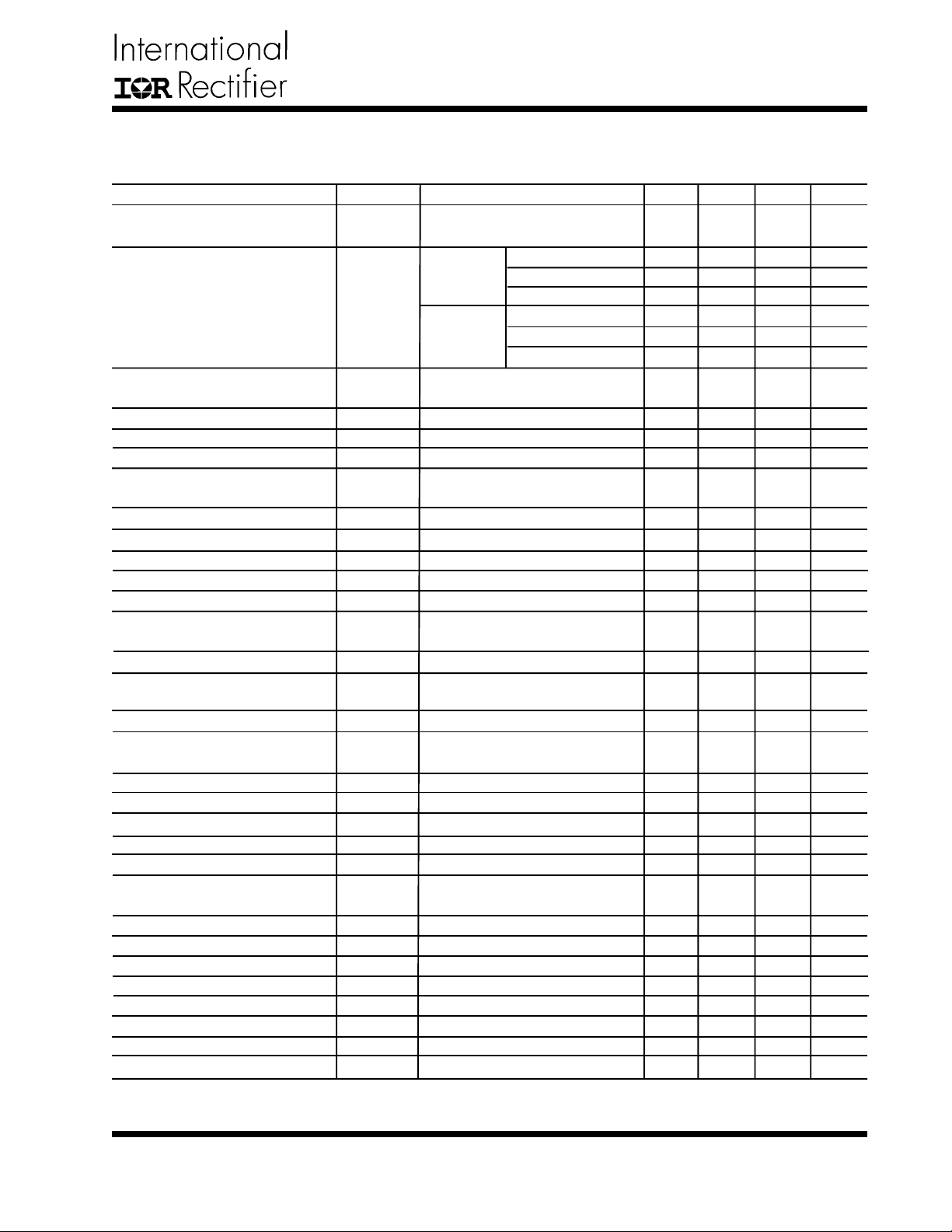

ELECTRICAL SPECIFICATIONS

Unless otherwise specified, these specifications apply over Vcc=12V , VcH1=VcH2=VCL=12V and 0°C<Tj<125°C.

PARAMETER SYMBOL TEST CONDITION MIN TYP MAX UNITS

Output V oltage Accuracy

2

0.80

1

0.75

10

15

15

10

6

6

28

0.9VREF

0.1

-0.1

100

0

1.25

300

+1

+1.35

+1.35

+1.35

+1.65

+1.65

5.3

4.0

15

25

25

15

10

10

35

0.25

0.95VREF

0.5

-0.5

2500

2500

140

+4

Vcc-2

345

0

1200

0.6

V

%

%

%

%

%

%

V

V

V

V

mA

mA

mA

mA

mA

mA

µA

V

V

V

µA

µmho

µmho

µA

mV

V

kHz

V

%

ns

%

kHz

ns

V

V

Feedback Voltage

Accuracy

UVLO Section

UVLO Threshold - Vcc

UVLO Hysteresis - Vcc

UVLO Threshold - VcH1,2

UVLO Hysteresis - VcH1,2

Supply Current Section

Vcc Dynamic Supply Current

VcH1 & VcH2 Dynamic Current

VCL Dynamic Supply Current

Vcc Static Supply Current

VcH1/VcH2 Static Current

VCL Static Supply Current

Soft-Start / SD Section

Charge Current

Shutdown Threshold

Power Good Section

VSENS1,2 Lower Trip Point

PGood Output Low Voltage

Error Amp Section

Fb Voltage Input Bias Current

Transconductance 1

Transconductance 2

Error Amp Source/Sink Current

Input Offset V oltage for E/A1,2

VP2 Voltage Range

Oscillator Section

Frequency

Ramp Amplitude

Min Duty Cycle

Min Pulse Width

Max Duty Cycle

Synch Frequency Range

Synch Pulse Duration

Synch High Level Threshold

Synch Low Level Threshold

Note1: Cold temperature performance is guaranteed via correlation using statistical quality control. Not 100% tested in production.

VFb1 , VFb2

UVLOVCC

UVLOVCH1,2

Dyn ICC

Dyn ICH

Dyn ICL

ICCQ

ICHQ

ICLQ

SSIB

SD

PGFB1,2L

PG(Voltage)

IFB1,2

gm1

gm2

I(E/A)1,2

VOS(ERR)

VP2

Freq

VRAMP

Dmin

Puls(ctrl)

Dmax

Sync(Fs)

Sync(puls)

Sync(H)

Sync(L)

Tj=25°C

MLPQ

TSSOP

Supply Ramping Up

Supply Ramp Up and Down

Supply Ramping Up

Supply Ramp Up and Down

Freq=300kHz, CL=1500pF

Freq=300kHz, CL=1500pF

Freq=300kHz, CL=1500pF

SS=0V

SS=0V

SS=0V

SS=0V

VSENS1,2 Ramping Down

ISINK=2mA

SS=3V

Fb1,2 to VREF

Note2

Rt(SET) to 30.9K

Note2

Fb=1V

FSW=300kHz, Note2

Fb=0.6V , FSW=200kHz

20% above free running freq

0°C <T

-40°C <T

Tj=25°C

0°C <Tj< 125°C

-40°C <Tj< 125°C

j< 125°C

j< 125°C

-1

-1.35

-2.5

-1.35

-1.65

-3.0

4.7

3.5

22

0.8VREF

1400

1400

60

-4

0.4

255

150

86.5

200

www.irf.com

3

IR3621 & ( PbF)

PARAMETER SYMBOL TEST CONDITION MIN TYP MAX UNITS

OUT3 Internal Regulator

V

Output Voltage

Output Current

Protection Section

OVP Trip Threshold

OVP Fault Prop Delay

OCSET Current

Hiccup Duty Cycle

Hiccup High Level Threshold

Hiccup Low Level Threshold

Thermal Shutdown Trip Point

Thermal Shutdown Hysteresis

Output Drivers Section

LO Drive Rise Time

HI Drive Rise Time

LO Drive Fall Time

Hi Drive Fall Time

Dead Band Time

OVP

OVP(delay)

IOCSet

Tr(LO)

Tr(HI)

Tf(LO)

Tf(HI)

TDB

Output forced to 1.25VREF

Note2

Hiccup pin pulled high, Note2

Note2

Note2

Note2

Note2

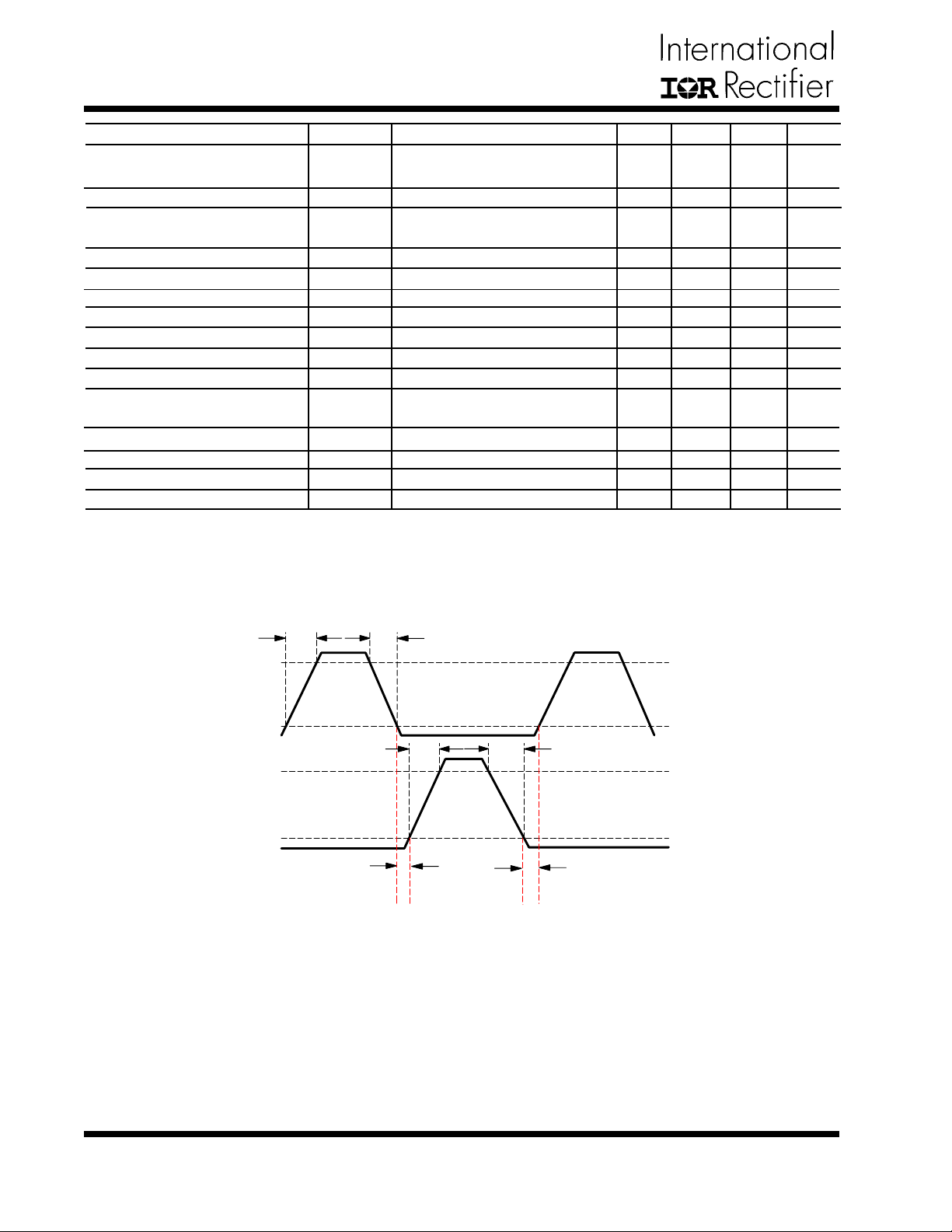

CL=1500pF ,Figure 2

CL=1500pF , Figure 2

CL=1500pF ,Figure 2

CL=1500pF ,Figure 2

See Figure 2

5.8

44

1.1VREF

16

2

6.25

1.15

140

20

20

18

18

25

25

50

5

VREF

1.2

6.7

VREF

5

24

0.8

50

50

50

50

100

V

mA

V

µs

µA

%

V

V

C

C

ns

ns

ns

ns

ns

Note 2: Guaranteed by design but not tested for production.

Tr

9V

High Side Driver

(HDrv )

2V

9V

Low Side Driver

(LDrv)

2V

Deadband

H_to_L

Tf

Tr

Tf

Deadband

L_to_H

4

Figure 2 - Rise Time, Fall Time and Deadband for Driver Section

www.irf.com

PIN DESCRIPTIONS

TSSOP MLPQ PIN SYMBOL PIN DESCRIPTION

1

2

3

4

5,23

6,22

7,21

8

20

9,19

10,18

1 1,17

12,16

13,15

14

24

25

26

27

28

29

30

31

1

2,22

3,21

4,20

5

19

6,18

7,17

8,16

10,14

1 1,13

12

23

24

26

27

28

9,15,25.32

PGood

Vcc

VOUT3

Rt

VSEN2, VSEN1

Fb2,Fb1

Comp2, Comp1

SS2 / SD

SS1 / SD

OCSet2,OCSet1

VcH2, VcH1

HDrv2, HDrv1

PGnd2, PGnd1

LDrv2, LDrv1

V

CL

Sync

Hiccup

VP2

VREF

Gnd

N/C

Power Good pin. Low when any of the outputs fall 10% below the set voltages.

Supply voltage for the internal blocks of the IC. The Vcc slew rate should be

<0.1V/us.

Output of the internal LDO. Connect a 1.0uF capacitor from this pin to ground.

Connecting a resistor from this pin to ground sets the oscillator frequency .

Sense pins for OVP and PGood. For current share tie these pins together.

Inverting inputs to the error amplifiers. In current sharing mode, Fb1 is connected to a resistor divider to set the output voltage and Fb2 is connected to

programming resistor to achieve current sharing. In independent 2-channel mode,

these pins work as feedback inputs for each channel.

Compensation pins for the error amplifiers.

These pins provide user programmable soft-start function for each outputs.

Connect external capacitors from these pins to ground to set the start up time

for each output. These outputs can be shutdown independently by pulling the

respective pins below 0.3V . During shutdown both MOSFET s will be turned of f.

For current share mode SS2 must be floating.

A resistor from these pins to switching point will set current limit threshold.

Supply voltage for the high side output drivers. These are connected to voltages

that must be typically 6V higher than their bus voltages. A 0.1µF high frequency capacitor must be connected from these pins to PGND to provide peak

drive current capability .

Output drivers for the high side power MOSFET s. Note3

These pins serve as the separate grounds for MOSFET drivers and should be

connected to the system’s ground plane.

Output drivers for the synchronous power MOSFET s.

Supply voltage for the low side output drivers.

The internal oscillator can be synchronized to an external clock via this pin.

When pulled High, it puts the device current limit into a hiccup mode. When

pulled Low, the output latches of f, after an overcurrent event.

Non-inverting input to the second error amplifier. In the current sharing mode, it

is connected to the programming resistor to achieve current sharing. In independent 2-channel mode it is connected to V

the resistor divider to set the output voltage.

Reference Voltage. The drive capability of this pin is about 2µA.

Analog ground for internal reference and control circuitry .

No Connect

IR3621 & ( PbF)

REF pin when Fb2 is connected to

Note3: The negative voltage at these pins may cause instability for the gate drive circuits. To prevent this, a low

forward voltage drop diode (Schottky) is required between these pins and power ground.

www.irf.com

5

IR3621 & ( PbF)

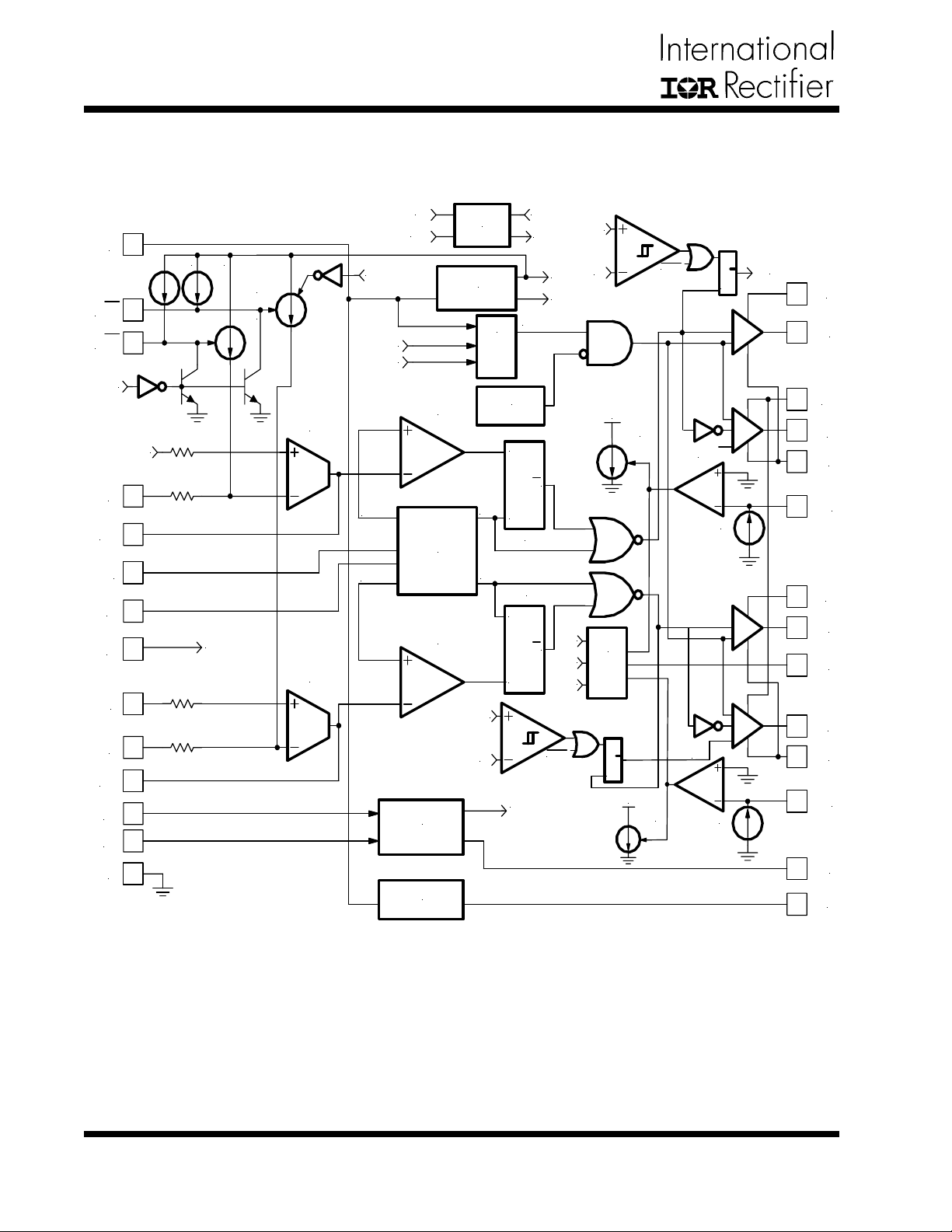

BLOCK DIAGRAM

Vcc

28uA

28uA

SS2 / SD

SS1 / SD

POR

Fb1

Comp1

Rt

Sync

V

REF

V

P2

Fb2

Comp2

V

SEN1

V

SEN2

0.8V

64uA

0.8V

64uA

Max

Error Amp1

Error Amp2

Mode

VcH1

VcH2

Ramp1

Ramp2

2

SS

0.8V

PWM Comp1

Two Phase

Osc illator

PWM Comp2

PGood / O V P

Mode

Control

Bias

Generator

UVLO

Set1

Set2

0.3V

SS2

POR

Mode

3V

0.8V

POR

Thermal

Shutdown

R

Q

S

Reset Dom

Reset Dom

S

Q

R

POR

OVP

HDrv OFF / LDrv ON

SS1

SS2

Mode

0.3V

SS1

Hiccup

Control

SS1

S

R

Q

SS2

3uA

3uA

POR

PBias1

PBias2

20uA

20uA

S

Q

PBias1

R

VcH1

HDrv1

V

CL

LDrv1

PGnd1

OCSet1

VcH2

HDrv2

Hiccup

LDrv2

PGnd2

OCSet2

6

Gnd

Regulator

Figure 3 - IR3621Block Diagram

www.irf.com

PGood

V

OUT3

FUNCTIONAL DESCRIPTION

Introduction

The IR3621 is a versatile device for high performance

buck converters. It consists of two synchronous buck

controllers which can be operated either in two independent mode or in current share mode.

The timing of the IC is provided by an internal oscillator

circuit which generates two out-of-phase clock that can

be programmed up to 500kHz per phase.

Supply Voltage

Vcc is the supply voltage for internal controller. The operating range is from 5.5V to 14.5V . It also is fed to the

internal LDO. When Vcc is below under-voltage threshold, all MOSFET drivers will be turned off.

Internal Regulator

The regulator powers directly from Vcc and generates a

regulated voltage (Typ. 6.2V@40mA). The output is protected for short circuit. This voltage can be used for charge

pump circuitry as shown in Figure12.

IR3621 & ( PbF)

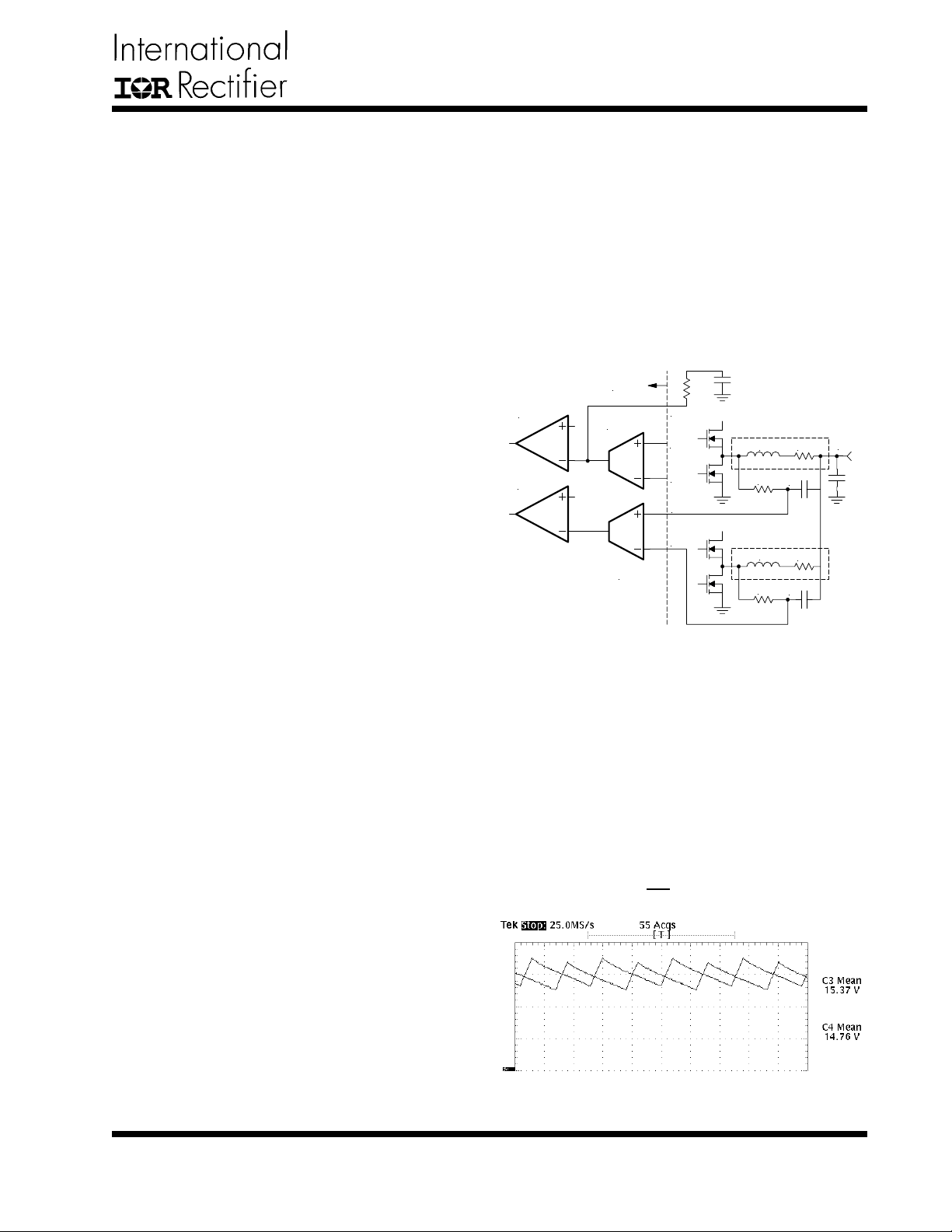

In this mode, one control loop acts as a master and sets

the output voltage as a regular Voltage Mode Buck controller and the other control loop acts as a slave and

monitors the current information for current sharing. The

voltage drops across the current sense resistors (or DCR

of inductors) are measured and their difference is amplified by the slave error amplifier and compared with the

ramp signal to generate the PWM pulses to match the

output current. In this mode the SS2 pin should be floating.

IR3621

PWM Comp1

PWM Comp2

Master E/A

Comp

0.8V

Fb1

VP2

V

L1

R1

C1

OUT

R

L1

Input Supplies UnderV oltage LockOut

The IR3621 UVLO block monitors three input voltages

(Vcc, VcH1 and VcH2) to ensure reliable start up. The

MOSFET driver output turn off when any of the supply

voltages drops below set thresholds. Normal operation

resumes once the supply voltages rise above the set

values.

Mode Selection

The SS2 pin is used for mode selection. In current share

mode this pin should be floating and in dual output mode

a soft start capacitor must be connected from this pin to

ground to program the start time for the second output.

Independent Mode

In this mode the IR3621 provides control to two independent output power supplies with either common or different input voltages. The output voltage of each individual

channel is set and controlled by the output of the error

amplifier, which is the amplified error signal from the

sensed output voltage and the reference voltage. The

error amplifier output voltage is compared to the ramp

signal thus generating fixed frequency pulses of variable

duty-cycle, which are applied to the FET drivers, Figure19 shows a typical schematic for such application.

FB2

Slave E/A

L2

L2

R

R2

C2

Figure 4 - Loss-less inductive current sensing

and current sharing.

In the diagram, L1 and L2 are the output inductors. RL1

and RL2 are inherent inductor resistances. The resistor

R1 and capacitor C1 are used to sense the average inductor current. The voltage across the capacitors C1

and C2 represent the average current flowing into resistance RL1 and RL2. The time constant of the RC network

should be equal or at most three times larger than the

time constant L1/RL1.

R1×C1=(1~3)× ---(1)

L1

RL1

Currnt Share Mode

This feature allows to connect both outputs together to

increase current handling capability of the converter to

support a common load. The current sharing can be done

either using external resistors or sensing the DCR of

inductors (see Figure 4).

www.irf.com

Figure 5 - 30A Current Sharing using Inductor sensing

(5A/Div)

7

IR3621 & ( PbF)

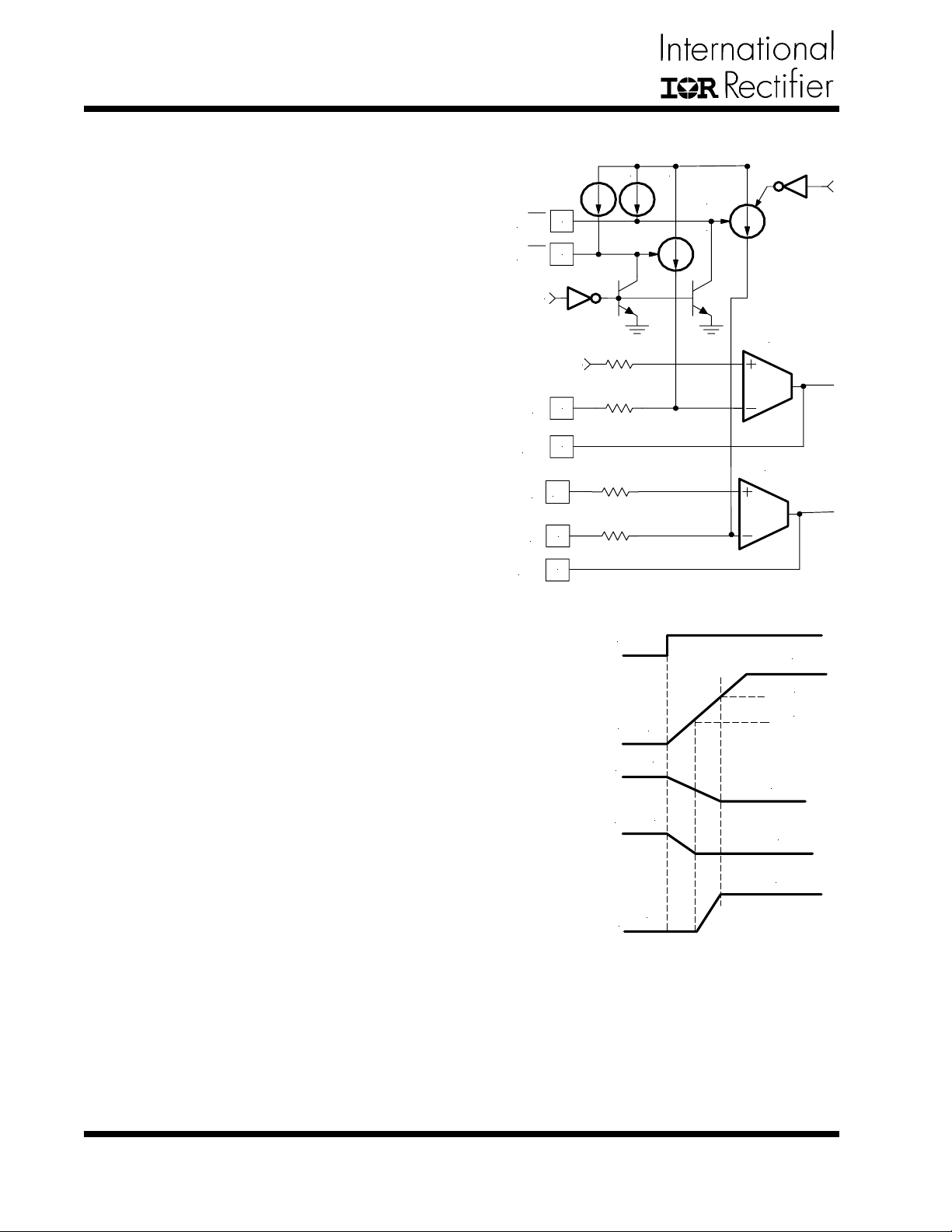

Dual Soft-Start

The IR3621 has programmable soft-start to control the

output voltage rise and limit the inrush current during

start-up. It provides a separate Soft-Start function for each

outputs. This will enable to sequence the outputs by

controlling the rise time of each output through selection

of different value soft-start capacitors. The soft-start pins

will be connected together for applications where, both

outputs are required to ramp-up at the same time.

To ensure correct start-up, the soft-start sequence initiates when the Vcc, VcH1 and VcH2 rise above their

threshold and generate the Power On Reset (POR) signal. Soft-start function operates by sourcing an internal

current to charge an external capacitor to about 3V . Initially, the soft-start function clamps the E/A’s output of

the PWM converter. During power up, the converter output starts at zero and thus the voltage at Fb is about 0V .

A current (64µA) injects into the Fb pin and generates a

voltage about 1.6V (64µA×25K) across the negative

input of E/A and (see Figure6).

The magnitude of this current is inversely proportional to

the voltage at soft-start pin. The 28µA current source

starts to charge up the external capacitor. In the mean

time, the soft-start voltage ramps up, the current flowing

into Fb pin starts to decrease linearly and so does the

voltage at negative input of E/A.

SS2 / SD

SS1 / SD

POR

Fb1

Comp1

V

P2

Fb2

Comp2

28uA

28uA

64uA

8

20

0.8V

22

21

26

6

7

Max

64uA

Error Amp1

Error Amp2

Figure 6 -Soft-start circuit for IR3621

Output of POR

3V

When the soft-start capacitor is around 1V , the current

flowing into the Fb pin is approximately 32µA. The voltage at the positive input of the E/A is approximately:

32µA×25K = 0.8V

The E/A will start to operate and the output voltage starts

to increase. As the soft-start capacitor voltage continues to go up, the current flowing into the Fb pin will keep

decreasing. Because the voltage at pin of E/A is regulated to reference voltage 0.8V , the voltage at the Fb is:

VFB = 0.8-(25K×Injected Current)

The feedback voltage increases linearly as the injecting

current goes down. The injecting current drops to zero

when soft-start voltage is around 1.8V and the output

voltage goes into steady state. Figure 7 shows the theoretical operational waveforms during soft-start.

Low Temperature Start-Up

The controller is capable of starting at -40C ambient

temperature.

≅

1.8V

≅

Soft-Start

Voltage

Current flowing

into Fb pin

Voltage at negative input

of Error Am p

Voltage at Fb pin

0V

64uA

≅

1.6V

0V

1V

0uA

0.8V

0.8V

Figure 7 - Theoretical operational waveforms

during soft-start.

The output start-up time is the time period when softstart capacitor voltage increases from 1V to 1.8V. The

start-up time will be dependent on the size of the external soft-start capacitor. The start-up time can be estimated by:

28µA×TSTART/CSS = 1.8V-1V

8

www.irf.com

IR3621 & ( PbF)

For a given start up time, the soft-start capacitor can be

calculated by:

SS ≅ 28µA×TSTART/0.8V

C

The soft-start is part of the Over Current Protection

scheme, during the overload or short circuit condition

the external soft start capacitors will be charged and

discharged in certain slope rate to achieve the hiccup

mode function.

SS1 / SD

28uA

Hiccup

20

3uA

Figure 8 - 3uA current source for discharging soft

start-capacitor during Hiccup mode

Out-of-Phase Operation

The IR3621 drives its two output stages 180 out-of-phase.

In 2-phase configuration, the two inductor ripple currents

cancel each other and result in a reduction of the output

current ripple and yield a smaller output capacitor for the

same ripple voltage requirement.

In single input voltage applications, the input ripple current

reduces. This results in much smaller input capacitor's

RMS current and reduces the input capacitor quantity .

Over-Current Protection

The IR3621 can provide two different schemes for OverCurrent Protection (OCP). When the Hiccup pin is pulled

high, the OCP will operate in hiccup mode. In this mode,

during overload or short circuit, the outputs enter hiccup

mode and stay in that mode until the overload or short

circuit is removed. The converter will automatically recover.

When the Hiccup pin is pulled low, the OCP scheme

will be changed to the latch up type, in this mode the

converter will be turned off during Overcurrent or short

circuit. The power needs to be recycled for normal

operation.

Each phase has its own independent OCP circuitry.

The OCP is performed by sensing current through the

R

DS(ON) of low side MOSFET. As shown in Figure 9, an

external resistor (RSET) is connected between OCSet pin

and the drain of low side MOSFET (Q2) which sets the

current limit set point.

If using one soft start capacitor in dual configuration for a

precise power up the OCP needs to be set to latch mode.

The internal current source develops a voltage across

RSET. When the low side switch is turned on, the inductor current flows through the Q2 and results a voltage

which is given by:

OCSET = IOCSET×RSET-RDS(ON)×iL ---(2)

V

I

OCSET

Hiccup

Control

IR3621

OCSet

R

SET

Q1

Q2

V

L1

OUT

Figure 9 - Diagram of the over current sensing.

The critical inductor current can be calculated by setting:

V

OCSET = IOCSET×RSET - RDS(ON)×IL = 0

RSET×IOCSET

ISET = IL(CRITICAL)= ---(3)

RDS(ON)

The value of RSET should be checked in an actual

circuit to ensure that the Over Current Protection

circuit activates as expected. The IR3621 current limit

is designed primarily as disaster preventing, "no blow

up" circuit, and is not useful as a precision current

regulator.

In two independent mode, the output of each channel

is protected independently which means if one output

is under overload or short circuit condition, the other

output will remain functional. The OCP set limit can be

programmed to different levels by using the external

resistors. This is valid for both hiccup mode and latch

up mode.

In 2-phase configuration, the OCP's output depends on

any one channel, which means as soon as one

channel goes to overload or short circuit condition the

output will enter either hiccup or latch-up, dependes on

status of Hiccup pin.

Pre-bias Startup

The IR3621 allows pre-bias startup without discharging

the output capacitors. The output starts in asynchronous fashion and keeps the synchronous MOSFET off

until the first gate signal for control MOSFET is generated.

www.irf.com

9

Loading...

Loading...