Page 1

IRDC3846-P1V2

SupIRBuck

TM

USER GUIDE FOR IR3846 EVALUATION BOARD

DESCRIPTION

The IR3846 is a synchronous buck

converter, providing a compact, high

performance and flexible solution in a small

5mmx7mm QFN package.

Key features offered by the IR3846 include

internal Digital Soft Start, precision 0.6V

reference voltage, Power Good, thermal

protection, programmable switching

frequency, Enable input, input under-voltage

lockout for proper start-up, enhanced line/

load regulation with feed forward, external

frequency synchronization with smooth

clocking, internal LDO, true differential

remote sensing and pre-bias start-up.

A thermally compensated output over-current

protection function is implemented by sensing

the voltage developed across the on-resistance

of the synchronous rectifier MOSFET for

optimum cost and performance.

This user guide contains the schematic and bill

of materials for the IR3846 evaluation board.

The guide describes operation and use of the

evaluation board itself. Detailed application

information for IR3846 is available in the

IR3846 data sheet.

BOARD FEATURES

• V

= +12V (+ 13.2V Max), No Vcc required.

in

= +1.2V @ 0-35A

• V

out

• F

=600kHz

s

• L= 0.250uH

• C

= 7x22uF (ceramic 1206) + 1x330uF (electrolytic)

in

• C

= 6x100uF (ceramic 1206)

out

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

1

AL

Page 2

IRDC3846-P1V2

CONNECTIONS and OPERATING INSTRUCTIONS

A well regulated +12V input supply should be connected to VIN+ and VIN-. A maximum of 35A load should

be connected to VOUT+ and VOUT-. The inputs and output connections of the board are listed in Table I.

IR3846 needs only one input supply and internal LDO generates Vcc from Vin. If operation with external Vcc

is required, then R3 should be removed and external Vcc can be applied between Vcc+ and Vcc- pins. Vin

pin and Vcc pins should be shorted together for external Vcc operation by installing a 0 ohm resistor at R4.

The board is configured for remote sensing. If local sense is desired, R18 should be uninstalled and R19

should be installed instead.

External Enable signal can be applied to the board via exposed Enable pad and R100 should be removed

for this purpose.

Table I. Connections

Connection Signal Name

VIN+ Vin (+12V)

VIN- Ground of Vin

Vout+ Vout(+1.2V)

Vout- Ground for Vout

Vcc+ Vcc Pin

Vcc- Ground for Vcc input

Enable Enable

PGood Power Good Signal

AGnd Analog ground

LAYOUT

The PCB is a 6-layer board. All of layers are 2 Oz. copper. The IR3846 and most of the passive

components are mounted on the top side of the board.

Power supply decoupling capacitors and feedback components are located close to IR3846. The

feedback resistors are connected to the output of the remote sense amplifier of the IR3846 and are

located close to the IR3846. To improve efficiency, the circuit board is designed to minimize the length

of the on-board power ground current path. Separate power ground and analog ground are used and

may be connected together using a 0 ohm resistor at R71.

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

2

AL

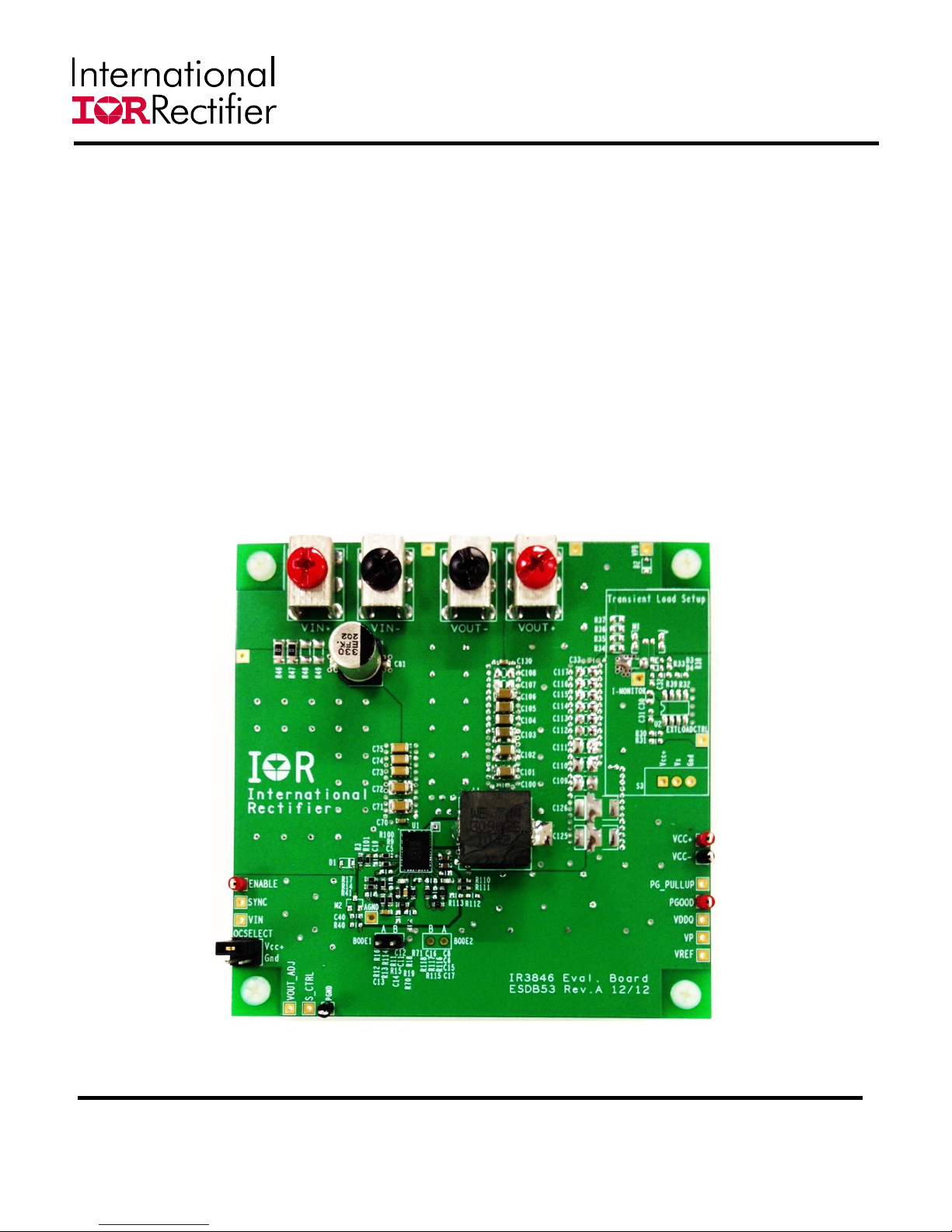

Page 3

IRDC3846-P1V2

CONNECTIONS and OPERATING INSTRUCTIONS

LAYOUT

The PCB is a 6-layer board. All of layers are 2 Oz. copper. The IR3846 and most of the passive

components are mounted on the top side of the board.

Power supply decoupling capacitors and feedback components are located close to IR3846. The

feedback resistors are connected to the output of the remote sense amplifier of the IR3846 and are

located close to the IR3846. To improve efficiency, the circuit board is designed to minimize the length

of the on-board power ground current path. Separate power ground and analog ground are used and

may be connected together using a 0 ohm resistor at R71.

Vin

Gnd

Gnd

Vo

Top View

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

3

AL

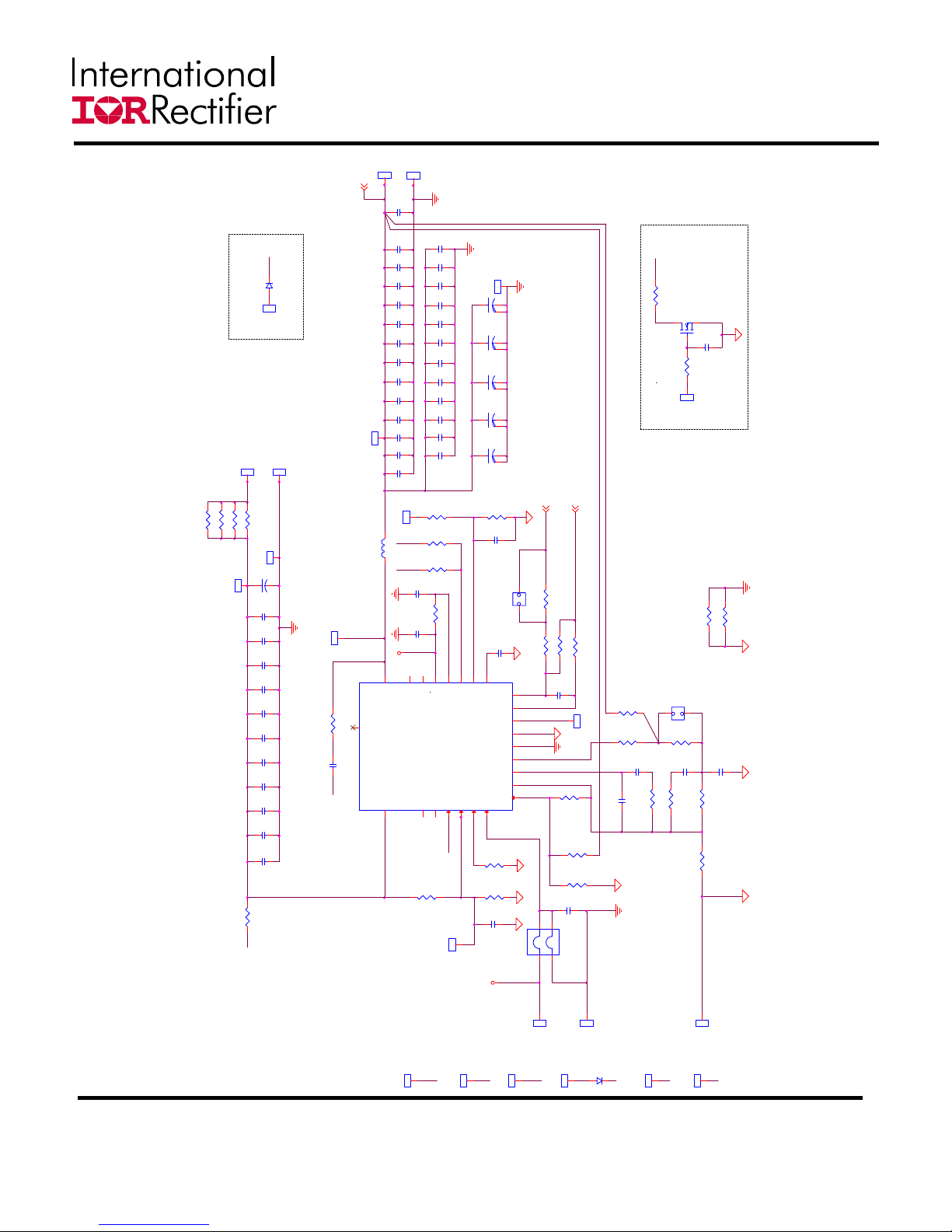

Page 4

R46-R49: 1206 pads

IRDC3846-P1V2

Vout+

Vout-

Vout

123456

123456

C130

0.1uF

N/S

N/S

C124

C112

N/S

N/S

C123

Vout

D2N/S

1 2

1

VPB

Optional Pre-Bias test circuit

Vin+

Vin-

123456

123456

R48

R49N/S

R470

R460

N/S

1

Vin

PVin

C81

330uF

1

Vin

C71-C80: 0805 / 1206 pads

PVin

Vin

330uF / 25V / Electrolytic Capacitor

+

C80

N/S

C79

N/S

C78

N/S

C77

22uF

C76

22uF

C75

22uF

C74

22uF

C73

22uF

C72

22uF

C71

22uF

C70

0.1uF

R30

1

SW

R100

C100.1uF

BOOT

7 x 22uF / 1206 / 25V / Ceramic Capacitor

C115

N/S

C122

C114

N/S

C113

C108

C107

C106

C105

C104

C100-C124: 0805 / 1206 pads

C103

6 x 100uF / 1206 / 6.3V / Ceramic Capacitor

C102

1

Vin

C101

C100

VDDQ

L1 250nH WE744309025

VCC

24

SW

NC5

26

U1

PVin

1

N/S

N/S

C121

N/S

C120

N/S

N/S

C119

N/S

N/S

C118

100uF

N/S

100uF

C117

N/S

100uF

C116

N/S

100uF

C111

N/S

100uF

C110

100uF

N/S

C109

N/S

R112

N/S

1

R111

10K

PG_PU

R110

10K

VCC

C6

1uF

R4N/S

C8

10uF

Vin

VCC

PGD

20

21

19

22

23

Vin

NC3

NC4

VCC

IR3846

BOOT

NC1

NC2

4

2

3

BOOT

R100

49.9K

PVin

Enable

1

Vin

C129

N/S

+

C128

N/S

+

C127

N/S

+

C126

N/S

+

C125

N/S

+

Vo_R_N

R113

C15

Vp

C17

Vref

18

17

Vp

Vref

PGD

RT/Sync6Enable5OCset

7

RT/Sync

R9

39.2K

R101

7.5K

C19

N/S

1

VCC

Vo_R_P

N/S

N/S

Vout

BODE2

JUMPER 3

R1150

R1160

R117

100pF

RS+

16

RS-

15

S_Ctrl

14

LGND

13

PGND

12

RSo

11

Comp

10

FB

9

Vsns

8

OCSelect

R1180

N/S

C16

N/S

1

S_Ctrl

FB

Vsns

N/S

R114

R16

4.02K

R17

4.02K

Vsns

C5

N/S

1

4pin jumper

2 3

4

FB

R41N/S

N/S

Optional "1-bit VID" circuit

M2

C40

N/S

R40N/S

1

Vout_Adj

R70N/S

R710

Single point of connection between Power

Ground and Signal ( “analog” ) Ground

BODE1

R19

N/S

R18

0

C11

C12160pF

JUMPER 2

R15

20

C14

8.2nF

R112.7K

R12127

N/S

C13

2200pF

R134.02K

FB

R144.02K

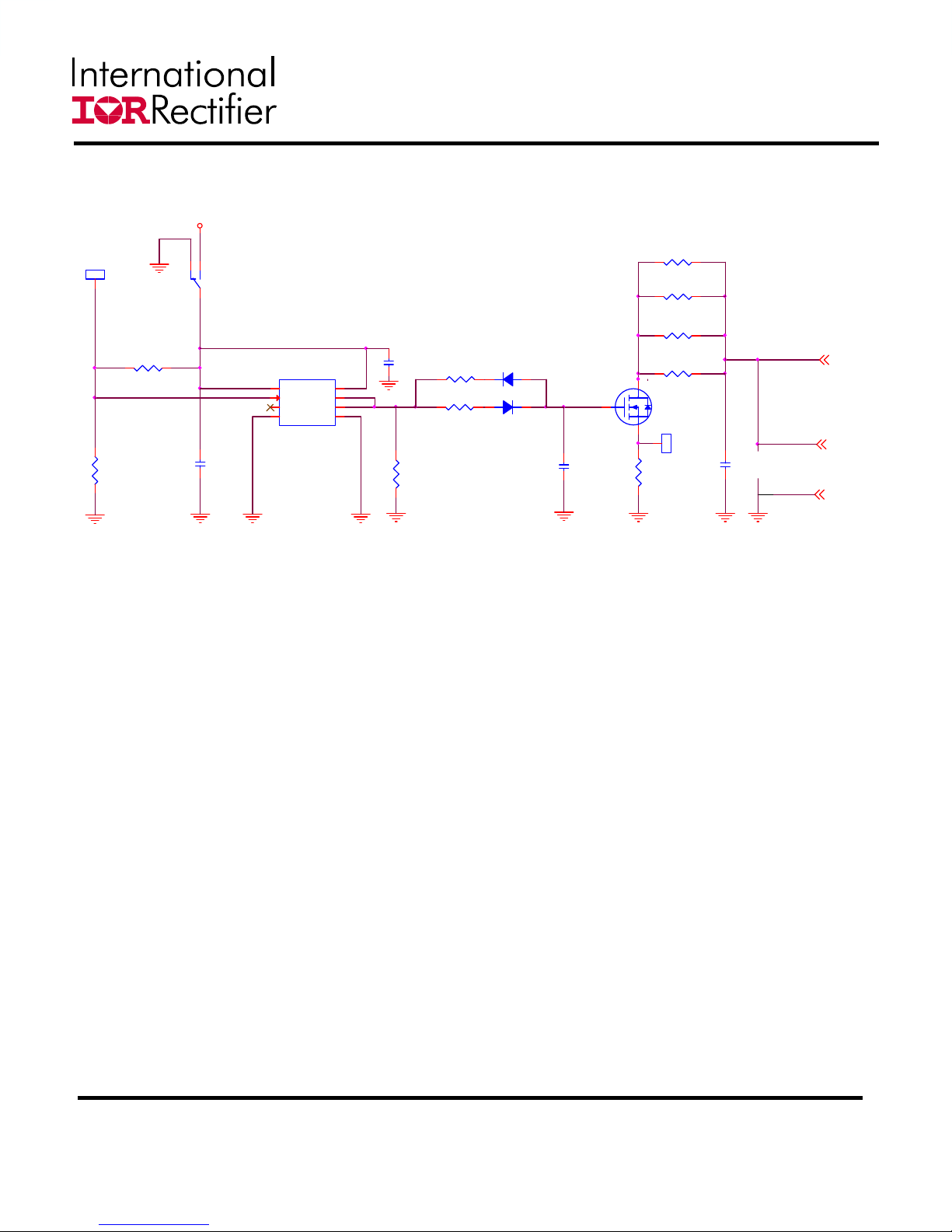

Fig. 1: Schematic of the IR3846 evaluation board

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Vin

1

Vin

Vref

Confidential

1

Vref

1

1

Vp

1

Vcc+

Vp

Vcc-

D1

N/S

Sync

Rt/Sync

12

1

Sync

PG_Pullup

1

PG_PU

PGood

1

Agnd

PGD

1

4

AL

Page 5

Schematic for Transient Load set up

VCC

IRDC3846-P1V2

ExtLoadC trl

1

R31

N/S

3

2 1

R30N/S

S3

SW

C31

N/S

N/S

1

2

3

U2

VS

VS

IN

OUT2

OUT1

N/A

GND4GND

MIC4452/SO8 N /S

C30

8

7

6

5

N/S

R32

N/S

D3

N/S

R38N/S

R39N/S

D4

N/S

M1

IRF 6721 N/ S

C32

N/S

R33

N/S

R34N/S

R35N/S

R36N/S

R37N/S

1

I-Monitor

C33

N/S

Vout

Vout

Vo_R_P

Vo_R_N

Optional transient load circuit

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

5

AL

Page 6

IRDC3846-P1V2

Bill of Materials

Item Qty Part Reference Value Description Manufacturer Part Number

C71 C72 C73

1

7

C74 C75 C76

C77

2

1

3

1

4

3 C10 C70 C130 0.1uF 0603, 25V, X7R, 10% Murata GRM188R71E104KA01D

5

1 C11 8200pF 0603, 50V, X7R, 10% Murata GRM188R71H822KA01D

6

1 C12 160pF 0603, 50V, NP0, 5% Murata GRM1885C1H161JA01D

7

1 C13 2200pF 0603, 50V, X7R, 10% Murata GRM188R71H222KA01D

8

1 C17 100pF 0603, 50V, C0G, 5% Murata GRM1885C1H101JA01D

9

1 C81 330uF

10

1 L1 250nH

11 6

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

C101 C102 C103

C104 C105 C106

6

R115 R116 R118

1 R9 39.2K 0603,1/10W,1% Panasonic ERJ-3EKF3922V

1 R11 2.7K 0603,1/10W,1% Panasonic ERJ-3EKF2701V

1 R12 127 0603,1/10W,1% Panasonic ERJ-3EKF1270V

4

1 R15 20 0603,1/10W,1% Vishay/Dale CRCW060320R0FKEA

2 R46 R47 0 1206,1/4W, Jumper Yageo RC1206JR-070RL

1 R71 0 0402, 1/16W, Jumper Yageo RC0402JR-070RL

1 R100 49.9K 0603,1/10 W,1% Panasonic ERJ-3EKF4992V

1 R101 7.5K 0603,1/10W,1% Panasonic ERJ-3EKF7501V

2 R110 R111 10K 0603,1/10 W,1% Panasonic ERJ-3EKF1002V

1 Jumper

2 Vin+ Vout+ RED SCREW TERMINAL

2 Vin- Vout- BLACK SCREW TERMINAL

1 U1 IR3846 IR3846 5mm X 7mm

C6 1uF 0603, X5R, 25V, 20% TDK

C8 10uF 0603, X5R, 10V, 20% TDK

R3 R10 R18

R13 R14 R16

R17

22uF 1206, 25V, X5R, 10% Murata GRM31CR61E226KE15L

C1608X5R1E105M

C1608X5R1A106M

SMD Elecrolytic, Fsize,

25V, 20%

250nH,

DCR=0.165mohm

100uF 1206, 6.3V, X5R, 20% Murata GRM31CR60J107ME39L

0 0603,1/10W, Jumper Vishay/Dale CRCW06030000Z0EA

4.02 K 0603,1/10W,1% Panasonic ERJ-3EKF4021V

PLUG 40 POS DBL

ROW STR

Panasonic EEV-FK1E331P

Wurth

Electronics Inc.

Omron

Electronics Inc.

Keystone

Electronics

Keystone

Electronics

International

Rectifier

744309025

XG8W-4041-ND

8199-2

8199-3

IR3846MPBF

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

6

AL

Page 7

IRDC3846-P1V2

TYPICAL OPERATING WAVEFORMS

Vin=12.0V, Vo=1.2V, Io=0A-35A, Fsw=600kHz, Room Temperature, No air flow

Fig. 2: Start up at 35A Load

Ch

, Ch2:Vo, Ch3:PGood, Ch4:Enable

1:Vin

Fig. 4: Start up with 1.08V Pre Bias, 0A Load

Ch

, Ch3:PGood

2:Vo

Fig. 3: Start up at 35A Load

Ch

, Ch2:Vo, Ch3:PGood, Ch4:V

1:Vin

cc

Fig. 5: Output Voltage Ripple, 35A load

Ch

: V

1

o

Fig. 6: Inductor node at 35A load

Ch

:LX

2

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

Fig. 7: Short (Hiccup) Recovery

Ch

, Ch3:PGood, Ch4:I

2:Vo

o

7

AL

Page 8

IRDC3846-P1V2

TYPICAL OPERATING WAVEFORMS

Vin=12.0V, Vo=1.2V, Io=3.5A-14A, Fsw=600kHz, Room Temperature, No air flow

Fig. 8: Transient Response, 3.5A to 14A step (2.5A/us)

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Ch

2:Vo

Confidential

8

AL

Page 9

IRDC3846-P1V2

TYPICAL OPERATING WAVEFORMS

Vin=12.0V, Vo=1.2V, Io=24.5A-35.0A, Fsw=600kHz, Room Temperature, No air flow

Fig. 9: Transient Response, 24.5A to 35A step (2.5A/us)

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Ch

2:Vo

Confidential

9

AL

Page 10

IRDC3846-P1V2

TYPICAL OPERATING WAVEFORMS

Vin=12.0V, Vo=1.2V, Io=0A-35A, Fsw=600kHz, Room Temperature, No air flow

Fig. 10: Bode Plot at 35A load: Fo = 100.6kHz; Phase Margin = 52.8º; Gain Margin = -17.2dB

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

10

AL

Page 11

IRDC3846-P1V2

TYPICAL OPERATING WAVEFORMS

Vin=12.0V, Vo=1.2V, Io=0A-35A, Fsw=600kHz, Room Temperature, No air flow

91

89

87

85

83

81

79

Efficiency [%]

77

75

73

71

0 5 10 15 20 25 30 35

Io [A]

Fig.11: Efficiency versus load current

7.5

7.0

6.5

6.0

5.5

5.0

4.5

4.0

3.5

3.0

2.5

Power Loss [W]

2.0

1.5

1.0

0.5

0.0

0 5 10 15 20 25 30 35

Io [A]

Fig.12: Power loss versus load current

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Confidential

11

AL

Page 12

THERMAL IMAGES

Vin=12.0V, Vo=1.2V, Io=35A, Fsw=600kHz, Room Temperature, No air flow

IRDC3846-P1V2

Fig. 13: Thermal Image of the board at 35A load

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Test point 1 is IR3846: 98.8

Test point 2 is inductor: 72.9

Confidential

0

C

0

C

12

AL

Page 13

THERMAL IMAGES

Vin=12.0V, Vo=1.2V, Io=35A, Fsw=600kHz, Room Temperature, LFM = 100

IRDC3846-P1V2

Fig. 14: Thermal Image of the board at 35A load

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

Test point 1 is IR3846: 74

Test point 2 is inductor: 46.9

Confidential

0

C

0

C

13

AL

Page 14

IRDC3846-P1V2

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

4/11/2013

This evaluation board is a preliminary version meant for the engineering evaluation of the IR3846. Based on the results

of the continuing evaluation, this board can evolve and change without notice

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information

Data and specifications subject to change without notice. 4/13

Confidential

14

AL

Loading...

Loading...