International Rectifier IRS2166D, IRS2166DSTRPBF Datasheet

www.irf.com Page 1

Data Sheet No. PD60292

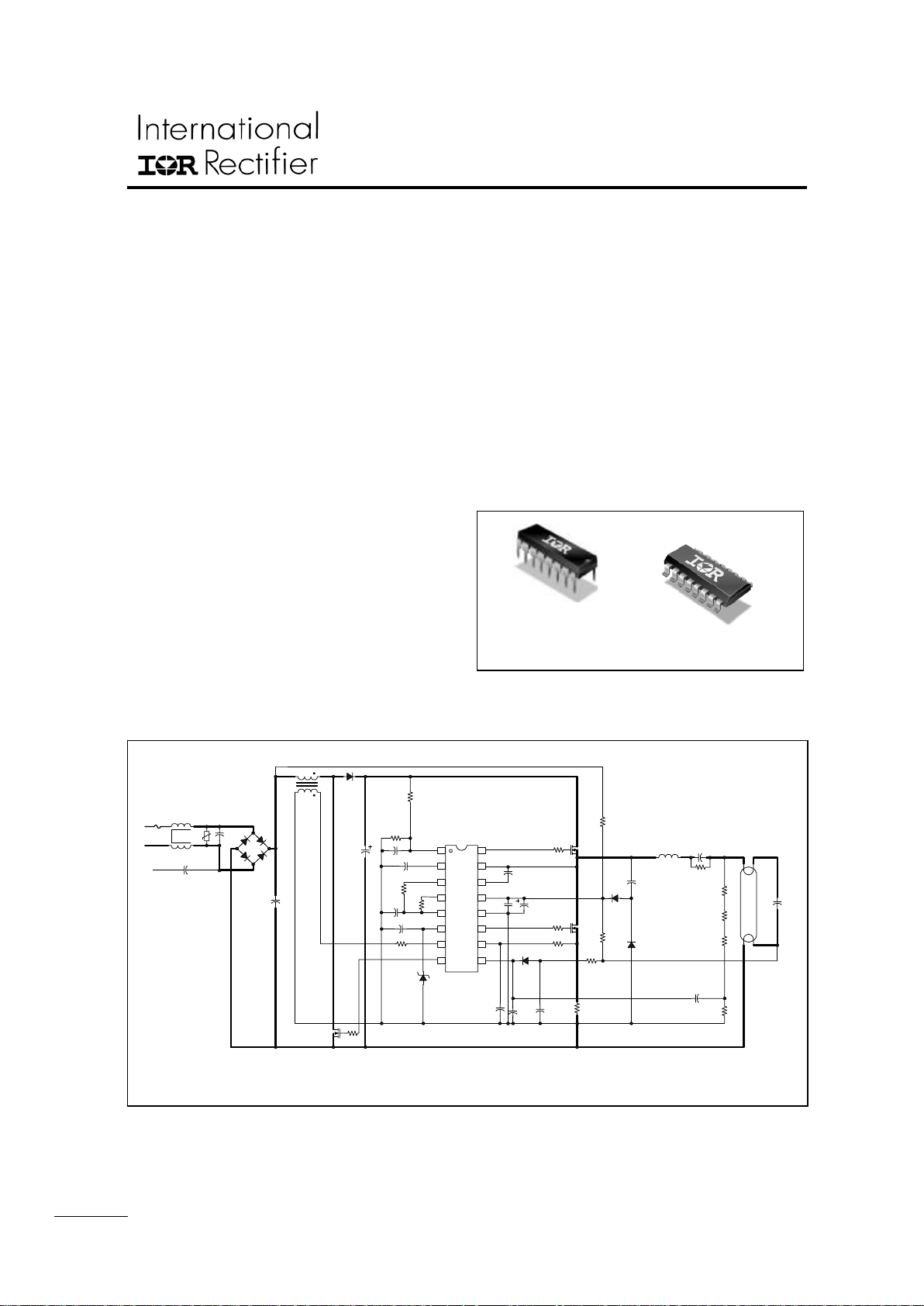

IRS2166D(S)PbF

PFC + BALLAST CONTROL IC

Features

PFC, ballast control and 600 V half-bridge driver in one IC

Critical-conduction mode boost-type PFC

Programmable half-bridge over-current protection

Programmable preheat frequency

Programmable deadtime

Programmable preheat time

Programmable run frequency

RoHS compliant

Description

The IRS2166D is a fully integrated, fully protected 600 V

ballast control IC designed to drive all types of fluorescent

lamps. The IRS2166D is based on the popular IR2166

control IC with additional improvements to increase ballast

performance. PFC circuitry operates in critical conduction

mode and provides high PF, low THD, and DC bus

regulation. The IRS2166D features include programmable

preheat and run frequencies, programmable preheat time,

and programmable end-of-life protection. Comprehensive

protection features such as protection from failure of a lamp

to strike, filament failures, end-of-life protection, DC bus

undervoltage reset as well as an automatic restart function,

have been included in the design.

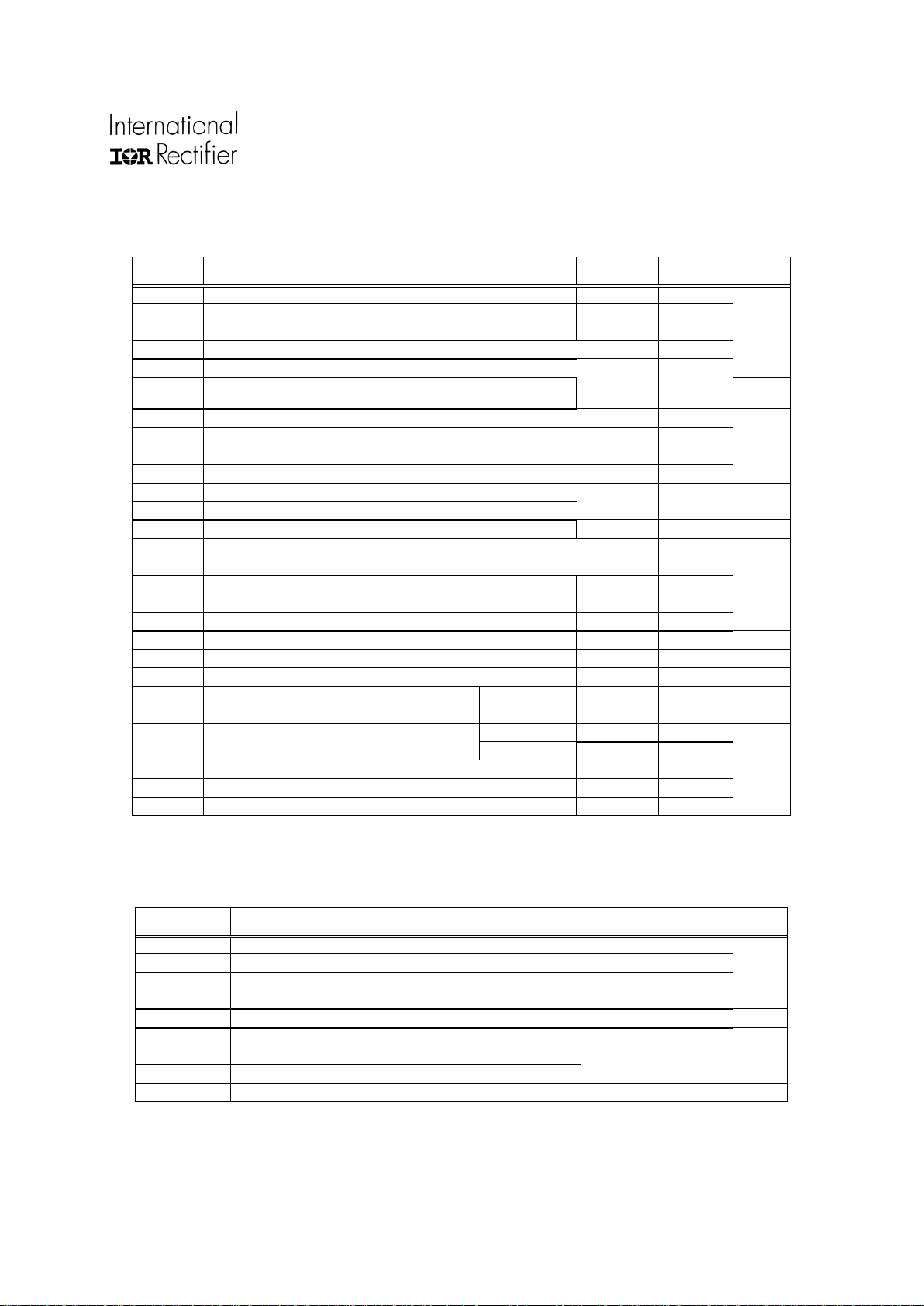

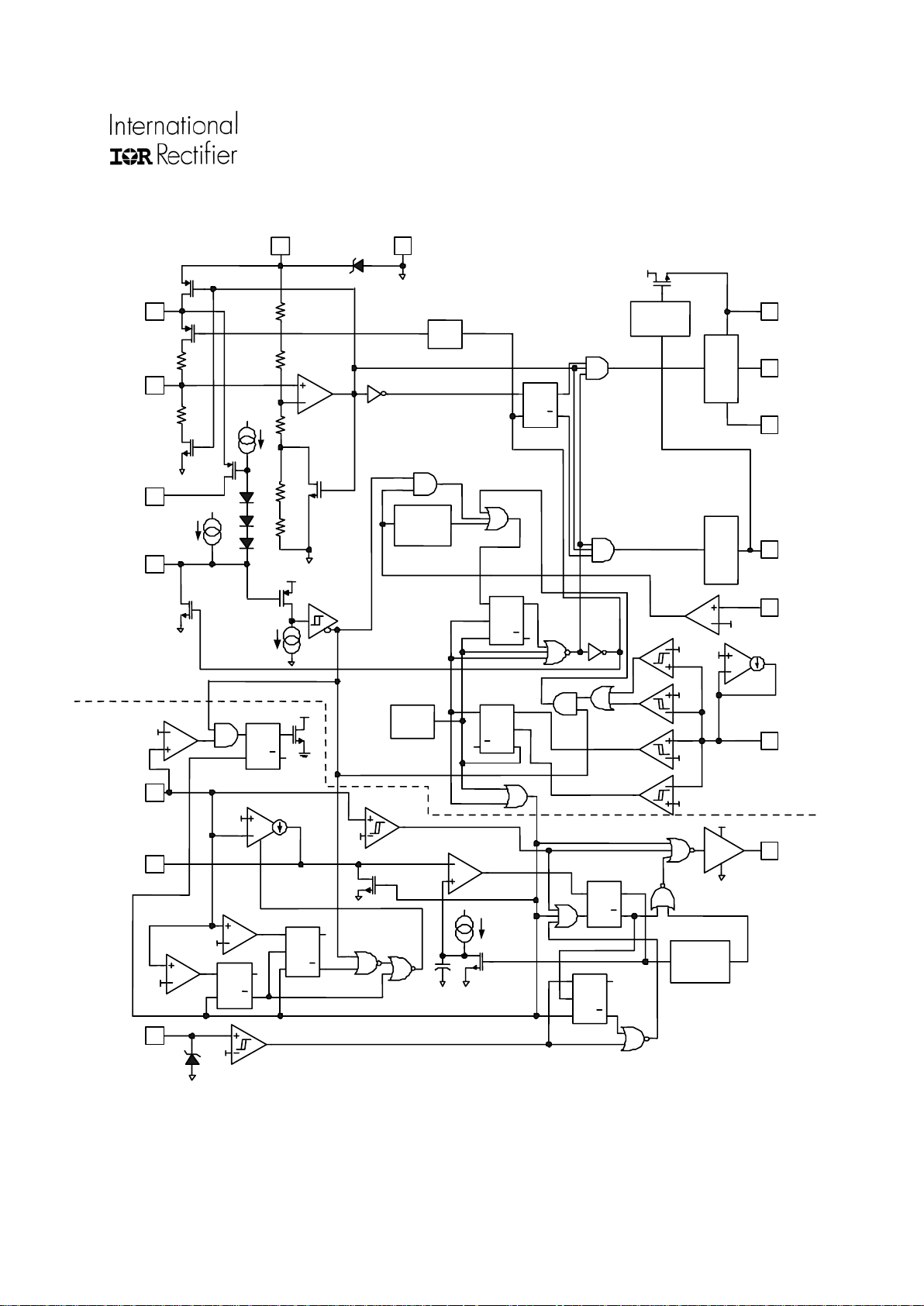

Application Diagram (Typical Only)

End-of-life window comparator pin

Internal up/down current-sense fault counter

DC bus undervoltage reset

Lamp removal/auto-restart shutdown pin

Internal bootstrap MOSFET

Internal 15.6 V zener clamp diode on V

CC

Micropower startup (250 µA)

Latch immunity and ESD protection

System Features

Improved V

BUS

regulation voltage tolerance

Increased SD pin shutdown voltage threshold hysteresis

Changed EOL pin internal 2.0 V bias to a +/-10 µA OTA

Internal bootstrap MOSFET

Packages

16-Lead PDIP 16-Lead SOIC

IRS2166DPbF IRS2166DSPbF

Note: Thick traces represent high-frequency, high-current paths.

Lead lengths should be minimized and power and IC grounds should be separated to avoid high-frequency

noise problems.

CRES

LRES

CDC

REOL1

REOL4

REOL3

REOL2

CEOL

RSUPPLY

RDC

L1

C1

BR1

C2

LPFC

MPFC

RPFC

DPFC

CBUS

L

N

RV1

GND

CY

F1

CSD1

RCS

ML

S

MHS

DCP2

RSD

CSNUB

RPU

CCS

DCP1

CVDC

RT

CT

RPH

CBOOT

RH

O

RL

O

CCOMP

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

IRS2166D

VBUS

CPH

RT

RPH

CT

COMP

ZX

PFC

LO

COM

VCC

VB

VS

HO

SD/EOL

CS

IC BALLAST

RVDC

CVCC1

CVCC2

RBUS

CPH

RZX

RLIM

CSD2

DSD

DCOMP

IRS2166D(S)PbF

www.irf.com Page 2

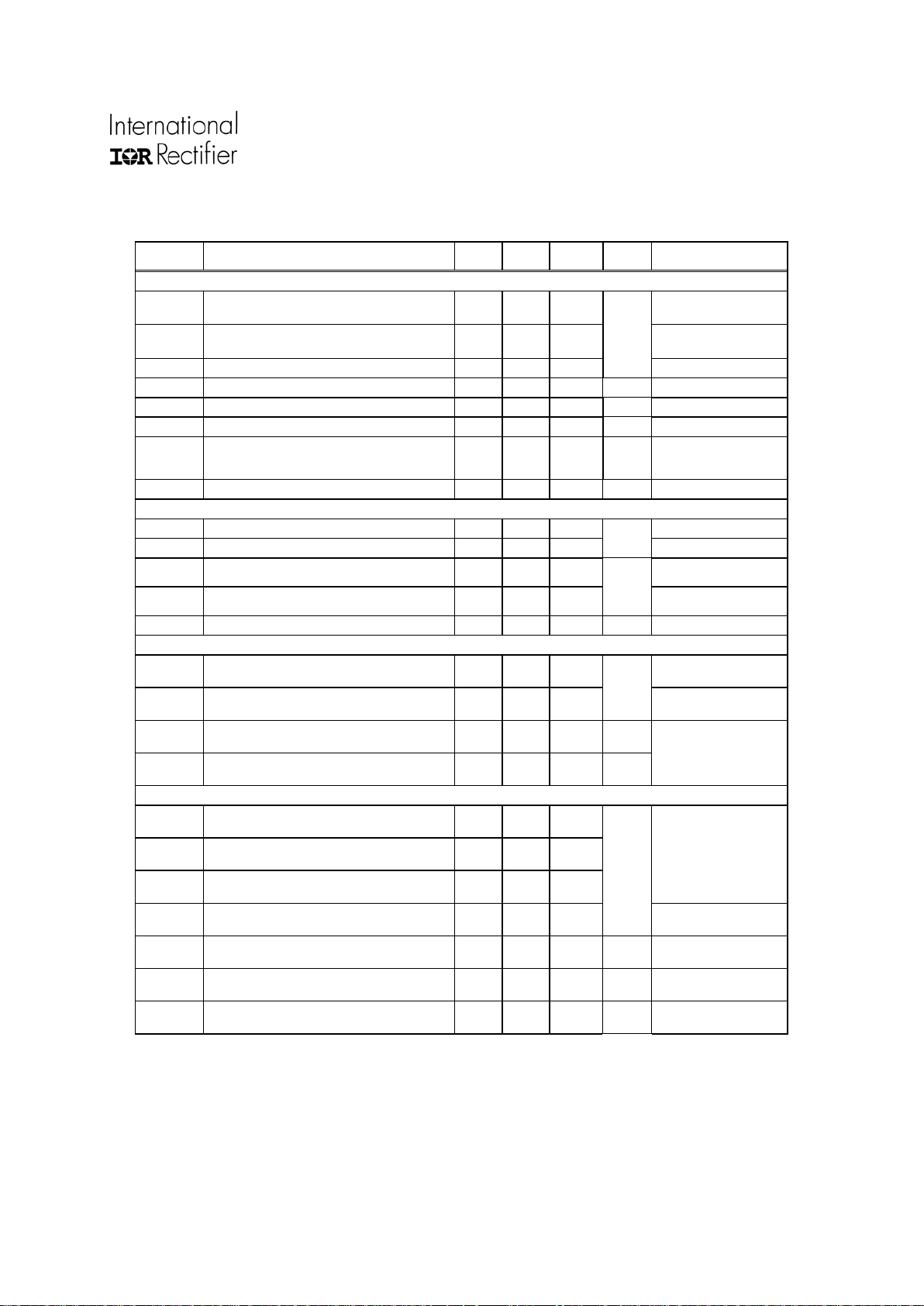

Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage

parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal

resistance and power dissipation ratings are measured under board mounted and still air conditions.

Symbol Definition Min. Max. Units

VB High-side floating supply voltage -0.3 625

VS High-side floating supply offset voltage VB – 25 VB + 0.3

VHO High-side floating output voltage VS - 0.3 VB + 0.3

VLO Low-side output voltage -0.3 VCC + 0.3

V

PFC

PFC gate driver output voltage -0.3 VCC + 0.3

V

I

O,MAX

Maximum allowable output current (HO, LO, PFC) due to external

power transistor miller effect

-500 500 mA

V

BUS

VBUS pin voltage -0.3 VCC + 0.3

V

CPH

CPH pin voltage -0.3 VCC + 0.3

VRT RT pin voltage -0.3 VCC + 0.3

V

RPH

RPH pin voltage -0.3 VCC + 0.3

V

IRT RT pin current -5 5

I

RPH

RPH pin current -5 5

mA

VCT CT pin voltage -0.3 VCC + 0.3 V

I

COMP

COM pin current -5 5

IZX ZX pin current -5 5

ICC VCC pin current (see Note 1) -25 25

mA

V

SD/EOL

SD/EOL pin voltage -0.3 VCC + 0.3 V

I

SD/EOL

SD/EOL pin current -5 5 mA

VCS CS pin voltage -0.3 VCC + 0.3 V

ICS CS pin current -5 5 mA

dV/dt Allowable VS offset voltage slew rate -50 50 V/ns

(16-Pin DIP) --- 1.8

PD

Package power dissipation @ T

A

≤ +25 ºC

PD = (T

JMAX-TA

)/R

θJA

(16-Pin SOIC) --- 1.4

W

(16-Pin DIP) --- 70

R

ΘJA

Thermal resistance, junction to ambient

(16-Pin SOIC) --- 82

ºC/W

TJ Junction temperature -55 150

TS Storage temperature -55 150

TL Lead temperature (soldering, 10 seconds) --- 300

ºC

Note 1: This IC contains a zener clamp structure between the chip VCC and COM which has a nominal breakdown

voltage of 15.6 V. This supply pin should not be driven by a DC, low impedance power source greater than the V

CLAMP

specified in the electrical characteristics section.

Recommended Operating Conditions

For proper operation the device should be used within the recommended conditions.

Symbol Definition Min. Max. Units

VB-VS High side floating supply voltage V

BSUV+

V

CLAMP

VS Steady state high-side floating supply offset voltage -1 600

VCC Supply voltage V

CCUV+

V

CLAMP

V

ICC V

CC

supply current (see Note 2) Note 2 20 mA

CT CT pin capacitance 220 --- pF

I

SD/EOL

SD/EOL pin current

ICS CS pin current

IZX ZX pin current

-1 1 mA

TJ Junction temperature -25 125 ºC

Note 2: Enough current should be supplied into the VCC pin to keep the internal 15.6 V zener clamp diode on this pin

regulating its voltage, V

CLAMP

.

IRS2166D(S)PbF

www.irf.com Page 3

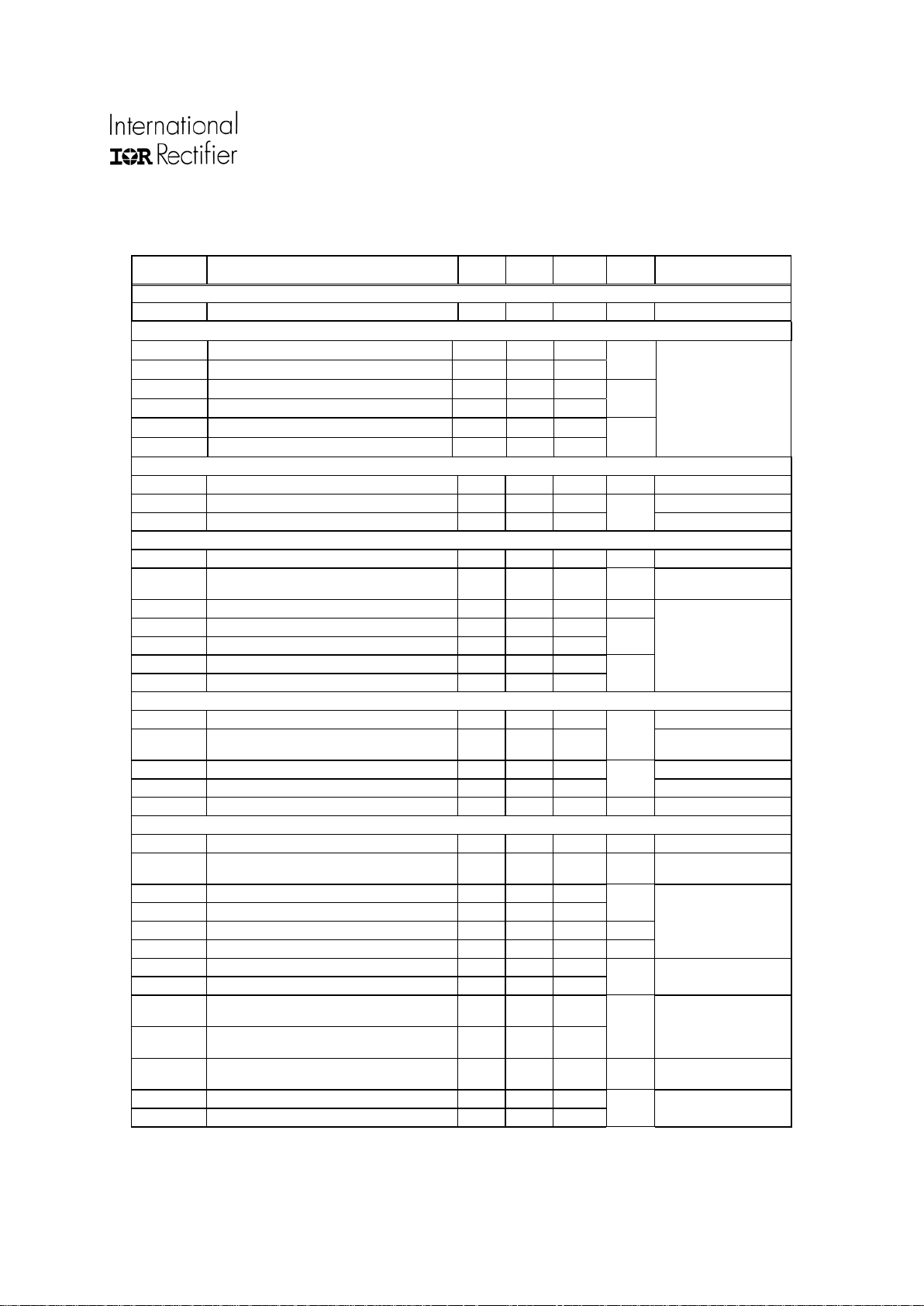

Electrical Characteristics

VCC = VBS = V

BIAS

=14 V +/- 0.25 V, V

CPH=VSD/EOL=VCOMP=VCS=VBUS=VZX

=0.0 V, RT = RPH = 39.2 kΩ, CLO = CHO = C

PFC

=

1000 pF, C

T

= 470 pF, TA =25 °C unless otherwise specified. See state diagram for MODE.

Symbol Definition Min Typ Max Units Test Conditions

Supply Characteristics

V

CCUV+

V

CC

supply undervoltage positive going

threshold

11.5 12.5 13.5

V

CC

rising from 0 V,

CT = COM

V

CCUV-

V

CC

supply undervoltage negative going

threshold

9.5 10.5 11.5

V

CC

falling from 14 V,

CT = COM

V

UVHYS

VCC supply undervoltage lockout hysteresis 1.5 2.0 3.0

V

CT = COM

I

QCCUV

UVLO mode VCC quiescent current --- 250 500 µA VCC = 8 V, CT = COM

I

QCC

Quiescent VCC supply current --- 4.3 5.1 mA CT = COM

I

QCCFLT

Fault quiescent VCC supply current --- 600 900 µA MODE = FAULT

I

CC,RUN

VCC current at RUN frequency --- 5.0 --- mA

MODE=RUN

COMP=2 V,

t

off,PFC

=2 µs

V

CLAMP

VCC zener clamp voltage 14.6 15.6 16.6 V ICC = 10 mA

Floating Supply Characteristics

I

QBS0

Quiescent VBS supply current --- 30 70 VHO = VS

I

QBS1

Quiescent VBS supply current --- 50 90

µA

VHO = VB

V

BSUV+

V

BS

supply undervoltage positive going

threshold

8.0 9.0 10.0 V

BS

rising from 0 V

V

BSUV-

V

BS

supply undervoltage negative going

threshold

7.0 8.0 9.0

V

V

BS

falling from 14 V

I

LKVS

VS offset supply leakage current --- --- 50 µA VB = VS = HO = 600 V

PFC Error Amplifier Characteristics

I

COMP,SOURCE

OTA error amplifier output current sourcing 20 30 40

MODE = RUN

V

VBUS

= 3.5 V

I

COMP,SINK

OTA error amplifier output current sinking -45 -35 -25

µA

MODE = RUN

V

VBUS

= 4.5 V

V

COMPOH

OTA error amplifier output voltage swing

(high state)

12.0 12.5 13.0 V

V

COMPOL

OTA error amplifier output voltage swing (low

state)

200 300 400 mV

PFC Control Characteristics

V

VBUSREG

V

BUS

internal reference voltage

(guaranteed by design)

3.9 4.0 4.1

V

VBUSOV+

V

BUS

over-voltage comparator positive going

threshold

4.1 4.3 4.5

V

VBUSOV-

V

BUS

over-voltage comparator negative going

hysteresis

4.0 4.15 4.3

V

COMP

=4.0 V

VZX

ZX pin positve edge triggered threshold

voltage

1.5 2.0 2.5

V

CT=COM

V

ZXHYS

ZX pin comparator hysterisis 100 300 500 mV

V

ZXclamp

ZX pin clamp voltage (high state) 5.7 6.7 7.7 V IZX = 5 mA, CT=COM

tWD PFC watch-dog pulse interval 150 400 500 µs

V

ZX

= 0 V, V

COMP

= 2.0 V

CT=COM

IRS2166D(S)PbF

www.irf.com Page 4

Electrical Characteristics (cont’d)

VCC = VBS = V

BIAS

=14 V +/- 0.25 V, V

CPH=VSD/EOL

= V

COMP

= VCS= V

BUS

= VZX =0.0 V, RT = RPH = 39.2 kΩ, CLO = CHO = C

PFC

=

1000 pF, C

T

= 470 pF, TA=25 °C unless otherwise specified. See state diagram for MODE.

Symbol Definition Min Typ Max Units Test Conditions

PFC Protection Circuitry Characteristics

V

VBUSUV-

V

BUS

pin undervoltage reset threshold 2.7 3.0 3.3 V CT=COM

Gate Driver Output Characteristics (HO, LO and PFC pins)

VOL Low-level output voltage, LO, HO, PFC --- COM ---

VOH High-level output voltage, LO, HO, PFC --- VCC ---

V

tr Turn-on rise time --- 120 220

tf Turn-off fall time --- 50 100

ns

I0+ Source current --- 180 ---

I0- Sink current --- 260 ---

mA

Bootstrap FET Characteristics

V

B,ON

VB when the bootstrap FET is on 13.2 13.7 --- V

I

B,CAP

VB source current when FET is on 40 55 --- CBS=0.1 µF

I

B,10V

VB source current when FET is on 9 12 ---

mA

VB=10 V

Ballast Control Oscillator Characteristics

fPH Preheat half-bridge oscillator frequency 73 76 81 kHz MODE=PREHEAT

f

RUN

Run half-bridge oscillator frequency 40 43 46

MODE=RUN,

CPH=13 V

D Oscillator duty cycle --- 50 --- %

t

d,LO

LO output deadtime 0.7 1.0 1.5

t

d,HO

HO output deadtime 0.7 1.0 1.5

µs

V

CT+

CT pin rising threshold voltage 7.8 8.4 9.0

V

CT-

CT pin falling threshold voltage 4.1 4.6 5.1

V

Ballast Control Preheat Characteristics

V

CPHEOP

CPH pin end of preheat threshold voltage --- 10.8 --- CT=COM, I

RPH

<2 µA

V

CPHRUN

CPH pin run mode threshold voltage --- 12.0 ---

V

V

BUS=VCC

, CT=COM,

V

SDEOL

=3.5 V,

I

RPHLK

RPH pin leakage current --- 0.1 --- MODE=RUN

I

CPH

CPH pin charging current 2.6 3.6 4.6

µA

CPH=5 V

V

CPHFLT

CPH pin voltage in fault mode --- 0 --- V MODE = FAULT

Ballast Control Protection Circuitry Characteristics

V

CSTH+

CS pin over-current sense threshold 1.075 1.20 1.325 V

n

EVENTS

CS pin fault counter number of events 70 100 140

MODE=PREHEAT,

V

BUS

=0 V

V

SDTH+

SD pin rising non-latched shutdown threshold

4.5 5.0 5.5

V

SDTH-

SD pin falling reset threshold voltage 2.7 3.0 3.3

V

V

SD,delay

Delay from V

SDTH+

until LO goes low --- 450 --- ns

V

EOLBIAS

EOL pin bias voltage 1.8 2.0 2.2 V

CT=COM

I

EOL,SRC

EOL pin internal OTA source current --- 10 ---

I

EOL,SNK

EOL pin internal OTA sink current --- 10 ---

µA SD = V

EOLBIAS

+ 0.5 V

V

EOLTH+

EOL pin rising latched shutdown threshold

(active during RUN MODE)

2.7 3.0 3.3

V

EOLTH-

EOL pin falling latched shutdown threshold

(active during RUN MODE)

0.9 1.0 1.1

V

MODE=RUN, CT=COM

V

BUS

=4.0 V, CPH=13 V

V

EOL,delay

Delay from V

EOLTH+

until LO goes low --- 1 --- µs

MODE=RUN,

CT=COM, CPH=13 V

V

CTFLT

CT pin fault mode voltage --- 0 ---

V

CPHFLT

CPH pin fault mode voltage --- 0 ---

V MODE=FAULT

IRS2166D(S)PbF

www.irf.com Page 5

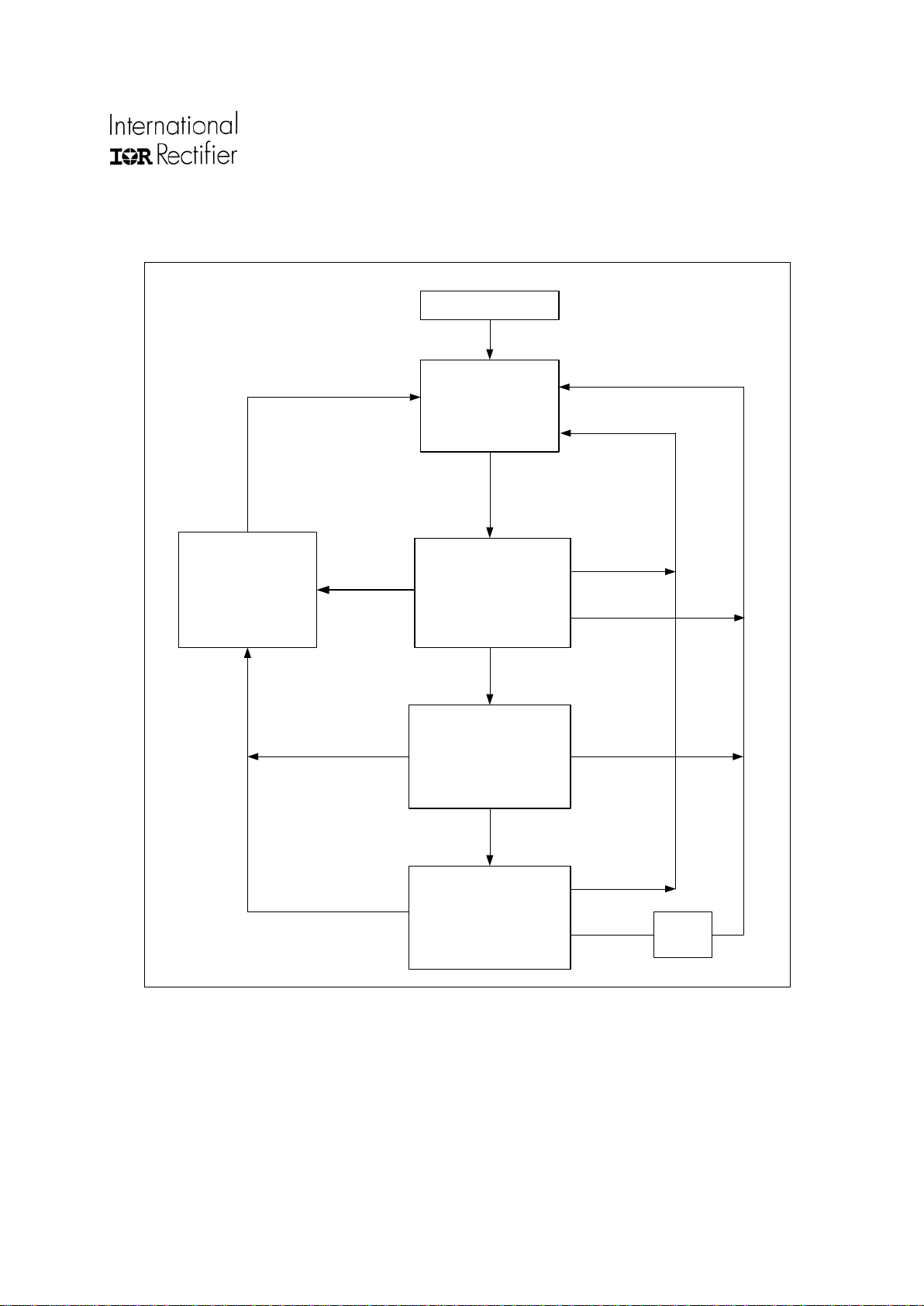

Schematic Block Diagram

PF

COM

Z

6.7 V

1.0 V

QS

R2 Q

R1

QS

R Q

VCC

RT

CP

VC

CT

RP

CO

R

V

TH

R

3 uA

R

Driver

Logic

SD/EO

R

R

RDT

3.0K

40 K

S1

S2

S3

S4

QT

R Q

S5

QS

R2 Q

R1

VBU

V

HO

V

LO

CS

High-

Side

Driver

LowSide

Driver

1.25 V

10

13

3

5

4

2

1

9

14

16

15

11

8

6

7

UVLO

400 us

Watch Dog

Timer

12

Soft

Start

OVP

4.3 V

Fault

Counter

2 V

5 V

1.0 V

3.0 V

4.0 V

3.5 V

Q S

R Q

RS2

Fault

Logic

Gain

Q S

R2 Q

R1

4.0 V

RS1

RS3

RS4

QS

R Q

VCC

3.0 V

Ballast

PFC

RUN

Bootstrap

Control

VCC

15.6 V

S6

VCC

3 V

Q S

R2Q

R1

Please Note: All values shown in block diagram are typical values only

IRS2166D(S)PbF

www.irf.com Page 6

State Diagram

SD/EOL > 5.0V (VSDTH+)

(Lamp Removal)

UVLO Mode

1

/2-Bridge Off

I

QCCUV

≅ 250µA

CPH = 0V

CT = 0V

PFC Off

PREHEAT Mode

1

/2-Bridge oscillating @ f

PH

RPH // RT

CPH Charging

PFC Enabled (High Gain)

CS Enabled

Fault Counter Enabled

VCC > 12.5 V (VCCUV+)

and

SD/EOL < 3.0 V (VSDTH-)

Power Turned On

FAULT Mode

Fault Latch Set

1

/2-Bridge Off

I

QCCFLT

≅ 600µA

CPH = 0 V

CT = 0 V

PFC Off

SD/EOL > 5.0 V (VSDTH+)

(Lamp Removal)

or

VCC < 10.5 V (VCCUV-)

(Power Turned Off)

CPH > 10.8 V (VCPHEOP)

IGNITION Mode

RPH>Open

f

PH

ramps to f

RUN

CPH charging

PFC = High Gain Mode

CS Enabled

Fault Counter Enabled

CS > 1.2 V (VCSTH+) (single event)

or

SD/EOL < 1.0 V (VEOLTH-)

or

SD/EOL > 3.0 V (VEOLTH+)

RUN Mode

RPH = Open

1/2-Bridge Oscillating @f

RUN

PFC = Low Gain Mode

VBUS UV Threshold Enabled

CS Enabled

Fault Counter Disabled

VBUS < 3.0 V

(VBUSUV)

CS > 1.2 V

(VCSTH+) for 100

events (nEVENTS)

Discharge

VCC to

UVLO

CPH > 12.0 V (VCPHRUN)

CS > 1.2 V (VCSTH+) for 100

events (nEVENTS)

VCC < 10.5 V (VCCUV-)

(Power Turned Off)

All values are typical. Applies to application diagram on page 1.

Loading...

Loading...