International CMOS Technology PEEL18CV8 User Manual

/

查询18CV8供应商

®

International

CMOS

Technology

CMOS Programmable Electrically Erasable Logic Device

Commercial

Industrial

PEEL™ 18CV8 -5/-7/-10/-15/-25

Features

■■■■

Multiple Speed Power, Temperature Options

CC

- V

= 5 Volts ±10%

- Speeds ranging from 5ns to 25 ns

- Power as low as 37mA at 25MHz

- Commercial and industrial versions available

■■■■

CMOS Electrically Erasable Technology

- Superior factory testing

- Reprogrammable in plastic package

- Reduces retrofit and development costs

■■■■

Development / Programmer Support

- Third party software and programmers

- ICT PLACE Development Software and PDS-3

programmer

- PLD-to-PEEL JEDEC file translator

General Description

The PEEL18CV8 is a Programmable Electrically Erasable

Logic (PEEL) device providing an attractive alternative to

ordinary PLDs. The PEEL18CV8 offers the performance,

flexibility , ease of design and production practicality needed

by logic designers today.

The PEEL18CV8 is available in 20-pin DIP, PLCC, SOIC

and TSSOP packages with speeds ranging from 5ns to

25ns with power consumption as low as 37mA. EE-Reprogrammability provides the convenience of instant reprogramming for development and reusable production

inventory minimizing the im pact of programming changes

or errors. EE-Reprogrammability also improves factory

testability, thus assuring the highest quality possible.

Architectural Flexibility

- Enhanced architecture fits in more logic

- 74 product terms x 36 input AND array

- 10 inputs and 8 I/O pins

- 12 possible macrocell configurations

- Asynchronous clear

- Independent output enables

-- 20 Pin DIP/SOIC/TSSOP and PLCC

■■■■

Application Versatility

- Replaces random logic

- Super sets PLDs (PAL, GAL, EPLD)

- Enhanced Architecture fits more logic than ordinary

PLDs

The PEEL18CV8 architecture allows it to replace over 20

standard 20-pin PLDs (PAL, GAL, EPLD etc.). It also provides additional architect ure features so more logic can be

put into every design. ICT’s JEDEC file translator instantly

converts to the PEEL18CV8 existing 20-pin PLDs without

the need to rework the existing design. Development and

programming support for the PEEL18CV8 is provided by

popular third-party programmers and development software.

ICT also offers free PLACE development software and a

low-cost development system (PDS-3).

Figure 1 Pin Configuration

I/CLK

I

I

I

I

I

I

I

I

GND

DIP

PLCC

TSSOP

SOIC

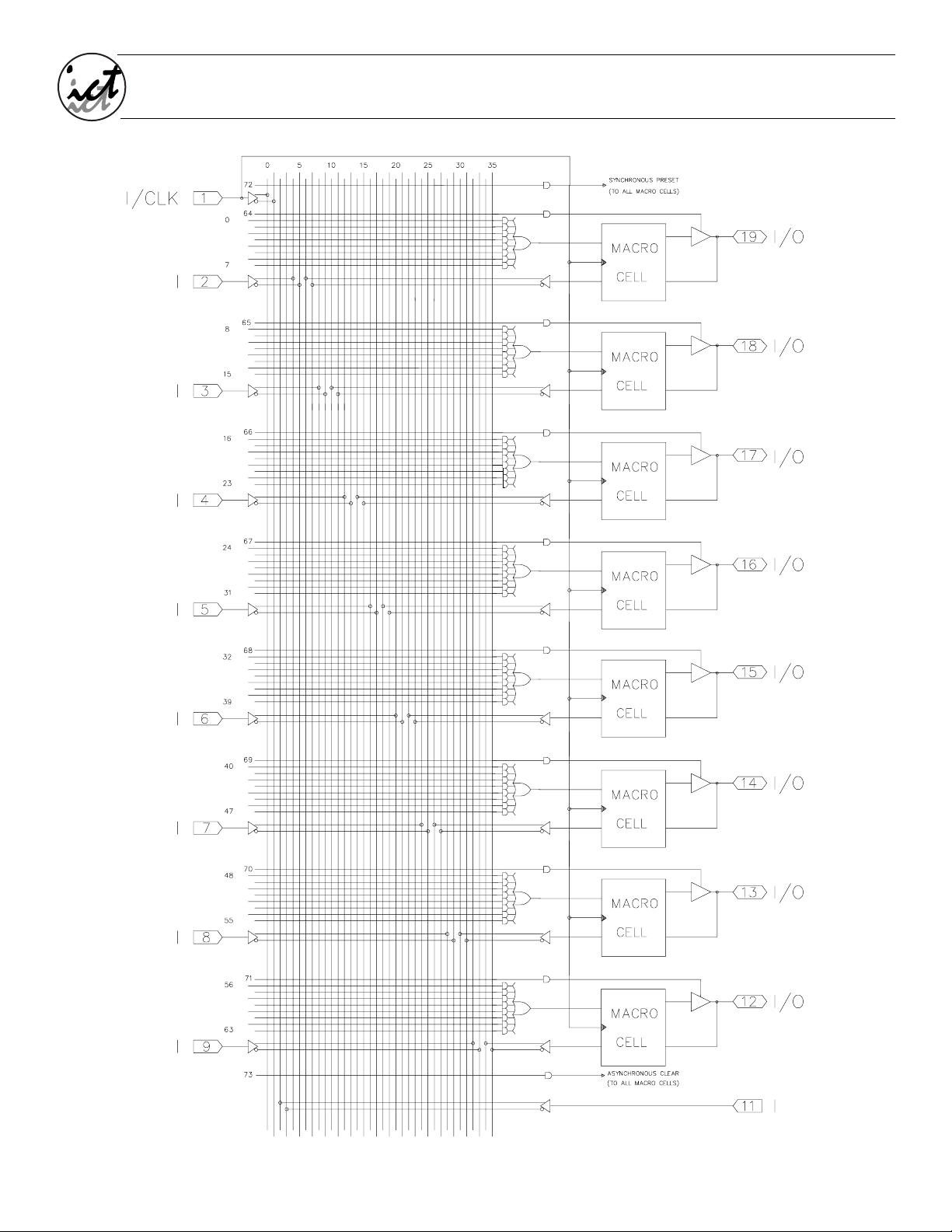

Figure 2 Block Diagram

1

2

3

4

5

6

7

8

9

10

VCC

20

I/O

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

I/O

12

I

11

1 04-02-004H

®

International

CMOS

Technology

PEELTM 18CV8

Figure 3 PEEL18CV8 Logic Array Diagra m

2 04-02-004H

®

International

CMOS

Technology

PEELTM 18CV8

Funct ion De scription

The PEEL18CV8 implements logic functions as sum-ofproducts expressions in a programmable-AND/fixed-OR

logic array. User-defined functions are created by programming the connections of input signals into the array. Userconfigurable output structures in the form of I/ O m acr ocells

further increase logic flexibility.

Architecture Overview

The PEE L18CV8 a rc h it ec t u r e is illustra te d in the bl o ck d iagram of Figure 2. Ten dedicated i nputs and 8 I/Os provide

up to 18 inputs and 8 outputs for creation of logic functions.

At the core of the device is a programmable electricallyerasable AND array which drives a fixed OR array. With

this structure, the PEEL18CV8 can implement up to 8 sumof-products logic expressions.

Associated with each of the 8 OR functions is an I/O macrocell which can be independently programmed to one of

12 different configurations. The programmable macrocells

allow each I/O to create sequential or combinatorial logic

functions of active-high or active-low polarity, while providing three different feedback paths into the AND array .

AND/OR LOGIC ARRAY

The programmable AND array of the PEEL18CV8 (s hown

in Figure 3) is formed by input lines intersecting product

terms. The input lines and product terms are used as follows:

array. (Note that PEE L device programmers automatically

program all of the connections on unused prod uct terms so

that they will h av e no effect on the outp ut fun c ti on ).

Programmable I/O Macrocell

The unique twelve-configuration out put macrocell provides

complete control over the architecture of each output. The

ability to configure each output independently permits

users to tailor the configurati on of the PEEL18CV8 to the

precise requirements of their designs.

Macrocell Architecture

Each I/O macrocell, as sho wn in Fig ure 4, consists of a Dtype flip-flop and two signal-select multiplexers. The configuration of each macrocell is determined by the four

EEPROM bits controlling these multiplexers. These bits

determine output polarity, output type (registered or nonregistered) and input-feedback path (bidirectional I/O, combinatorial feedback). Refer to Table 1 for details.

Equivalent circuits for the twelve macrocell configurations

are illustrated in Figure 5. In addition to emulating the f our

PAL-type output structures (configurations 3,4,9, and 10),

the macrocell provides eight additional configurations.

When creating a PEEL device design, the desired macrocell configuration generally is specified explicitly in the

design file. When the design is assem bled or com piled, the

macrocell configuration bits are defined in the last lines of

the JEDEC programming file.

■■■■

36 Input Line s :

- 20 input lines carry the true and complement of the

signals applied to the 10 input pins

- 16 additional lines carry the true and complement values of feedback or input signals from the 8 I/Os

■■■■

74 product terms:

- 64 product terms (arranged in groups of 8) are used

to form sum of product functions

- 8 output enable terms (one for each I/O)

- 1 global synchronous preset term

- 1 global asynchronous clear term

At each input-line/product-term intersection, there is an

EEPROM memory cell that determines whether or not

there is a logical connection at that intersection. Each product term is essentially a 36-input AND gate. A produ ct term

that is connected to b oth the t rue and complement of an

input signal will always be FALSE and thus will not affect

the OR function that it drives. When all the connections on

a product term are opened, a “don’t care” state exist s and

that term will a lways be TRU E .

When programming the PEEL18CV8, the device programmer first performs a bulk erase to remove the previo us pattern. The erase cycle opens every logical connection in the

array. The dev ice is c onfigu red t o p erform t he us er-defined

function by programming selected conn ections in the AND

Outp ut Type

The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flipflop (registered function). The D-type flip-flop latches data

on the rising edge of the clock and is controlled by the global preset and clear t erms. When the synch ronous preset

term is satisfied, the Q output of the register will be set

HIGH at the next rising edge of the clock input. Satisfying

the asynchronous clear will set Q LOW, regardless of the

clock state. If both terms are satisfied sim ultaneously, the

clear will override the preset.

Output Polarity

Each macrocell can be configured to implement active-high

or active-low logic. Programmable polarity eliminates the

need for external inverters.

Output Enable

The output of each I/O macrocell can be e nabled or disabled under the control of its associated programmable

output enable product term. When the logical conditions

programmed on the output enable term are satisfied, the

output signal is propagated to the I/O p in. Otherwise, the

output buffer is switched into the high-impedance state.

Under the control of the output enable term, the I/O pin can

3 04-02-004H

Loading...

Loading...