■

mu @

MCS@51

8-BIT CONTROL-ORIENTED MICROCONTROLLERS

Commercial/Express

8031AH18051AH18051AHP

8032N+18052N-I

8751W8751H-8

8751BW8752BI-I

■ High Performance HMOS Process ■

■

Internal Timers/Event Counters ■

■

2-Level interrupt Priority Structure

■

■

32 1/0 Lines (Four 8-Bit Ports)

■ 64K External Program Memory Space

■

■

Security Feature Protects EPROM Parts ■

Against Software Piracy

■

Boolean Processor

Bit-Addressable RAM

Programmable Full Duplex Serial

Channel

111 Instructions (64 Single-Cycle)

64K External Data Memory Space

Extended Temperature Range

(–40”C to +85”C)

The MCS@51 controllers are optimized for control applications. Byte-processing and numerical operations on

small data structures are facilitated by a variety of fast addressing modes for accessing the internal RAM. The

instruction set provides a convenient menu of 8-bit arithmetic instructions, including multiply and divide instruc-

tions. Extensive on-chip support is provided for one-bit variables as a separate data type, allowing direct bit

manipulation and testing in control and logic systems that require Boolean processing.

The 8751H is an EPROMversion of the 8051AH. It has 4 Kbytes of electrically programmable ROM which can

be erased with ultraviolet light. His fully compatible with the 8051AH but incorporates one additional feature: a

Program Memory Security bit that can be used to protect the EPROM against unauthorized readout. The

8751H-8 is identical to the 8751H but only operates up to 8 MHz.

The 8051AHP is identical to the 8051AH with the exception of the Protection Feature. To incorporate this

Protection Feature, program verification has been disabled and external memory accesses have been limited

to 4K.

The 8052AH is an enhanced version of the 8051AH. It is backwards compatible with the 8051AH and is

fabricated with HMOS II technology. The 8052AH enhancements are listed in the table below. Also refer to this

table for the ROM, ROMless and-EPROM versions of each product.

Device

Intsrnal Memory Timera/

Event Counters

Interrupts

Program Data

8031AH

none 128

X 8 RAM 2 x 18-Bit 5

8051AH 4K

X 8 ROM 128 X 8 RAM 2 x 16-Bit 5

6051AHP

4K

X 6 ROM 128 X 8 RAM 2 x 16-Bit

5

8751H

4K

X 8 EPROM 128 X 8 RAM 2 x 16-Bit 5

8751H-8 4K

X 8 EPROM 128X 6 RAM 2 x 16-Bit 5

6751BH

4K

X 8 EPROM 128X 8 RAM 2 x 16-Bit

5

8032AH

none 256

X 6 RAM 3 x 16-Bit 6

6052AH 8K

X 8 ROM 256 X 8 RAM 3 x 16-Bit 6

8752BH 8K

X 8 EPROM 256 X 8 RAM 3 x 16-Bit 6

I

IntelCorporationassumes noresponsibilityforthe use of any circuit~ otherthan circuitryembodiedinan Intel product.No othercircuitpatent

licenses are implied.Informationcontained hereinsupersedes previouslypublishedspecificationsontheaa davices from Intel.

O INTEL CORPORATION, 1994

October 1994 Order Numben 272318-002

MCS” 51 CONTROLLER

MO-M 7

P2.&P2 7

-

I

I

i fl 13 I I II ,, ,

JK2U

Acc

b

STACK

POINTER

~M‘f2#fi+-oN,TMoD,TJ

+1 L“ L-J

I

<>1 I

1

ml I

... ,, ,

I

7’7

1

. . . . .

9

PSEN

ALE

‘% “

TyG g~

E

RST-+

‘* II

I

1==4

119

P0nT3

h-+ T

LATCH

n

i-

,,(-1--%=2

w

PI O*1 7

5

Pm

LHvI!RS

———————————

P] O-P3 7

7

W3

I

————— —..

J

x

=

272318-1

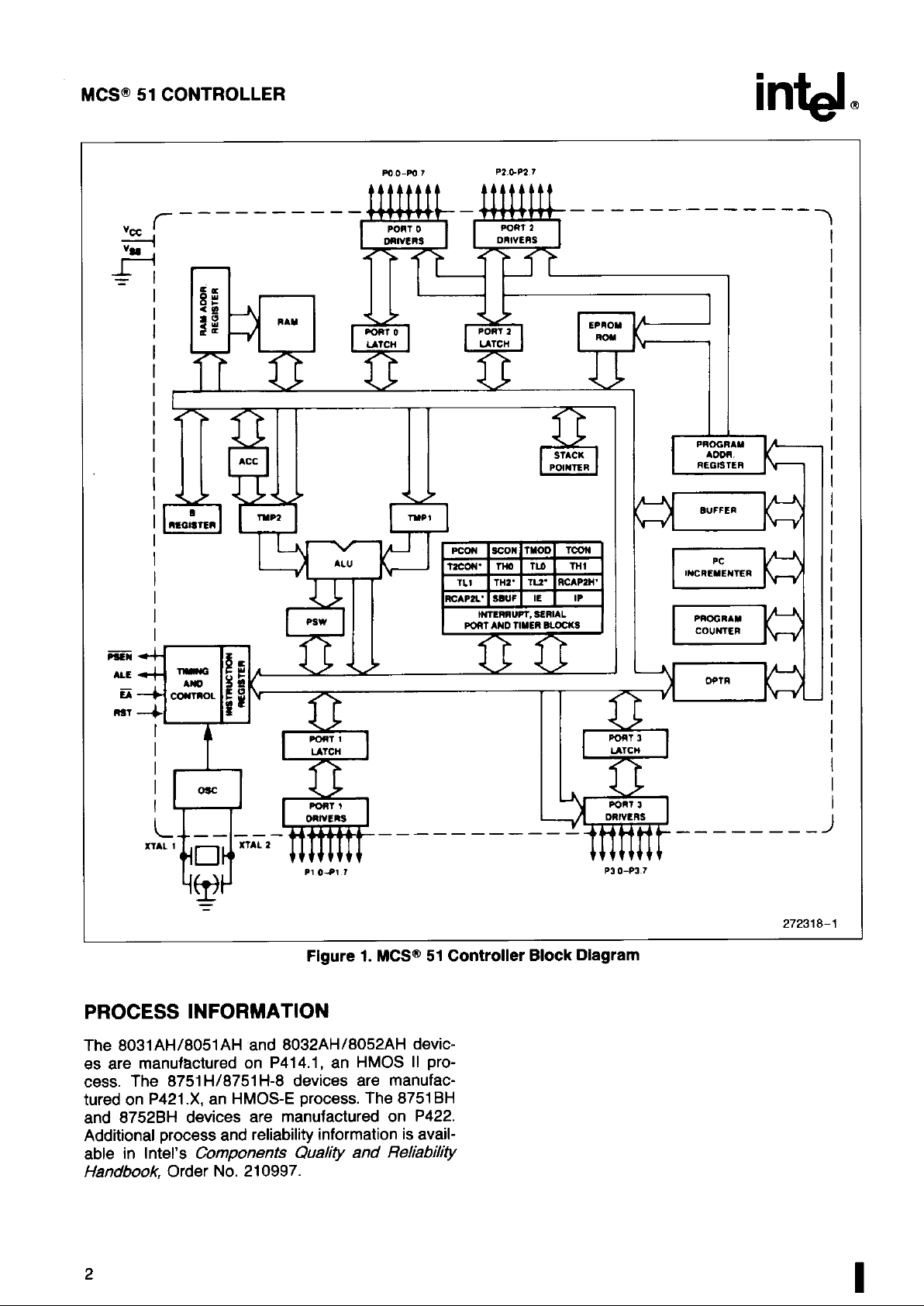

Figure 1. MCSI@51 Controller Block Diagram

PROCESS INFORMATION

The 8031AH/8051AH and 8032AH/8052AH devices are manufactured on P414.1, an HMOS II process. The 8751H/8751 H-8 devices are manufactured on P421.X, an HMOS-E process. The 8751BH

and 8752BH devices are manufactured on P422.

Additional process and reliability information isavailable in Intel’s

ComponentsQuality and Reliability

Handbook,

Order No, 210997.

MCS@ 51 CONTROLLER

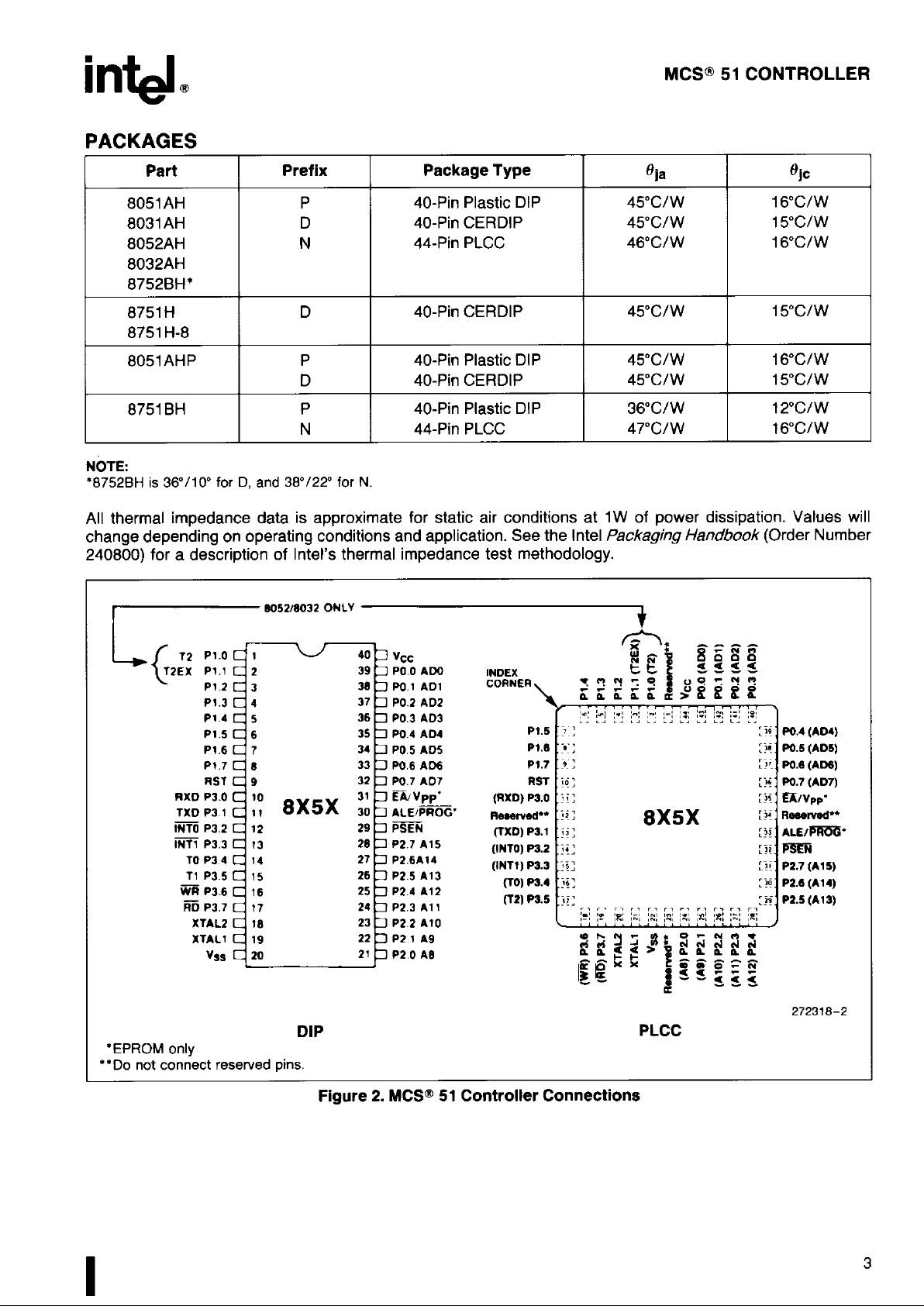

PACKAGES

Part Prefix

Package Type

‘ja Ojc

8051AH P

40-Pin Plastic DIP 45°chV 16“C/W

8031AH D 40-Pin CERDIP 4!5”CIW

15“CAIV

8052AH N

44-Pin PLCC 46°C/W 18°CfW

8032AH

6752BH*

8751H D 40-PinCERDIP 45”CIW 45“CIW

8751H-8

8051AHP P 40-Pin Plastic DIP

45”CIW 16°CfW

D 40-Pin CERDIP 45°c/w 15“cf w

8751BH P 40-Pin Plastic DIP 36”CIW

12°cf w

N 44-Pin PLCC 47”C1W

16”CfW

NOTE:

*8752BH

is 36”/10”for D,and38”/22”for N.

All thermal impedance data is approximate for static air conditions at IW of power dissipation. Values will

change depending on operating conditions and application. See the Intel Pac/raging

Handbook (Order Number

240800) for a description of Intel’s thermal impedance test methodology.

~“52’80320NL’ ~

L

{

T2

T2EX

I’__”ll

PI.’ 1 40

Vcc

P1.1 2 39 P’,’

P1.2 3 38

PO.1

P1.3 4 37

PO.2

P1.4 5 36

PO.3

P1.5 6 35 PO.4

P1,6 7 34

PO.5

P1.7 6 33

P06

‘1

RST 9

RU2 P3.O 10

TXD P3.1 11

INTOP3.2 12

INT1 P3,3 13

TOP3 4 14

11 P3.5 15

~ P3.6 16

t% P3.7 17

XTAL2 16

XTAL1 19

‘ss+!--

29

26

27

26

25

24

23

22

21

ADO

AD1

A02

A03

AD4

AD5

AD’

3 PO.7A07

3

EIJvpp”

Z

ALEIPROG”

3%FFI

3 P2.7 A15

2 P2.6A14

3 P2.5 A13

I P2.4 A12

1 P2.3 Al 1

> P2.2 AlO

3 P2 1 A9

X P20 A8

PI.6 ::8:;

P*,7 .:,.:

RST io;

(Rxo) P3.O

:ji:

neaslvsd**

.1:;

fTXD)P3.1

:ji;

(INTo)P3.2

:!;;

(INT1)P3.3

:j:;

fTo)P3.4 :>!:

8X5X

272318-2

DIP PLCC

●

EPROM only

“*Do not connect reserved pins.

Figure 2. MCS@51Controller Connections

3

MCS” 51 CONTROLLER

PIN DESCRIPTIONS

Vcc: Supply voltage.

Vss: Circuit ground.

Port O:Port Ois an 8-bit open drain bidirectional 1/0

port. As an output port each pin can sink 8 LS TTL

inputs.

Port O pins that have 1‘s written to them float, and in

that state can be used as high-impedance inputs.

Port Ois also the multiplexed low-order address and

data bus during accesses to external Program and

Data Memory. In this application it uses strong internal pullups when emitting 1‘s and can source and

sink 8 LS TTL inputs.

Port Oalso receives the code bytes during programming of the EPROM parts, and outputs the code

bytes during program verification of the ROM and

EPROM parts. External pullups are required during

program verification.

Port 1: Port 1 is an 8-bit bidirectional 1/0 port with

internal pullups, The Port 1 output buffers can sink/

source 4 LS TTL inputs. Port 1 pins that have 1‘s

written to them are pulled high by the internal pullUPS,and in that state can be used as inputs. As

inputs, Port 1 pins that are externally pulled low will

source current (IILon the data sheet) because of the

internal pullups.

Port 1 also receives the low-order address bytes

during programming of the EPROM parts and during

program verification of the ROM and EPROM parts.

In the 8032AH, 8052AH and 8752BH, Port 1 pins

P1.Oand P1.1 also serve the T2 and T2EX func-

tions, respectively.

w

Port 2 emits the high-order address byte during

fetches from external Program Memory and during

accesses to external Data Memory that use 16-bit

addresses (MOVX @DPTR). In this application it

uses strong internal pullups when emitting 1‘s. During accesses to external Data Memory that use 8-bit

addresses (MOVX @Ri),Port 2 emits the contents of

the P2 Special Function Register.

Port 2 also receives the high-order address bits during programming of the EPROM parts and during

program verification of the ROM and EPROM parts.

The protection feature of the 8051AHP causes bits

P2.4 through P2.7 to be forced to O,effectively limiting external Data and Code space to 4K each during

external accesses.

Port 3: Port 3 is an 8-bit bidirectional l/O port with

internal pullups. The Port 3 output buffers can sink/

source 4 LS TTL inputs. Port 3 pins that have 1‘s

written to them are pulled high by the internal pullUPS,and in that state can be used as inputs. As

inputs, Port 3 pins that are externally pulled low will

source current (IILon the data sheet) because of the

pullups.

Port 3 also serves the functions of various special

features of the MCS 51 Family, as listed below:

Port

Pin

P3,0

P3.1

P3.2

P3,3

P3.4

P3.5

P3.6

P3.7

Alternative Function

RXD (serial input port)

TXD (serial output port)

INTO(external interrupt O)

INT1 (external interrupt 1)

TO(Timer O external input)

T1 (Timer 1 external input)

WR (external data memory write strobe)

~ (external data memory read strobe)

I

Port

Pin

I

Alternative Function

I

P1.0

T2 (Timer/Counter 2 External Input)

P1.1

T2EX (Timer/Counter 2

Capture/Reload Trigger)

Port 2: Port 2 is an 8-bit bidirectional l/O port with

internal pullups. The Port 2 output buffers can sink/

source 4 LS TTL inputs. Porl 2 pins that have 1‘s

written to them are pulled high by the internal pullUPS,and in that state can be used as inputs. As

inputs, Port 2 pins that are externally pulled low will

source current (IILon the data sheet) because of the

internal pullups.

RST: Reset input. A high on this pin for two machine

cycles while the oscillator is running resets the device,

ALE/PROG: Address Latch Enable output pulse for

latching the low byte of the address during accesses

to external memory. This pin is also the program

pulse input (PROG) during programming of the

EPROM parts.

In normal operation ALE is emitted at a constant

rate of 1/6the oscillator frequency, and may be used

for external timing or clocking purposes. Note, how-

ever, that one ALE pulse is skipped during each ac-

cess to external Data Memory.

MCS” 51 CONTROLLER

w

PSEN: Program Store Enable is the read strobe to

external Program Memory.

When the device is executing code from external

Program Memory, PSEN is activated twice each machine cycle, except that two PSEN activations are

skipped during each access to external Data Memo-

ry

~/Vpp: External Access enable ~ must be

strapped to VSSin order to enable any MCS 51 device to fetch code from external Program memory

locations starting at OOOOHup to FFFFH. ~ must

be strapped to VCCfor internal program execution.

Note, however, that if the Security Bit in the EPROM

devices is programmed, the device will not fetch

code from any location in external Program Memory.

This pin also receives the programming supply voltage (VPP)during programming of the EPROM parts.

C2

I

El

XTAL2

n

XTAL1

cl

Vss

=

272318-3

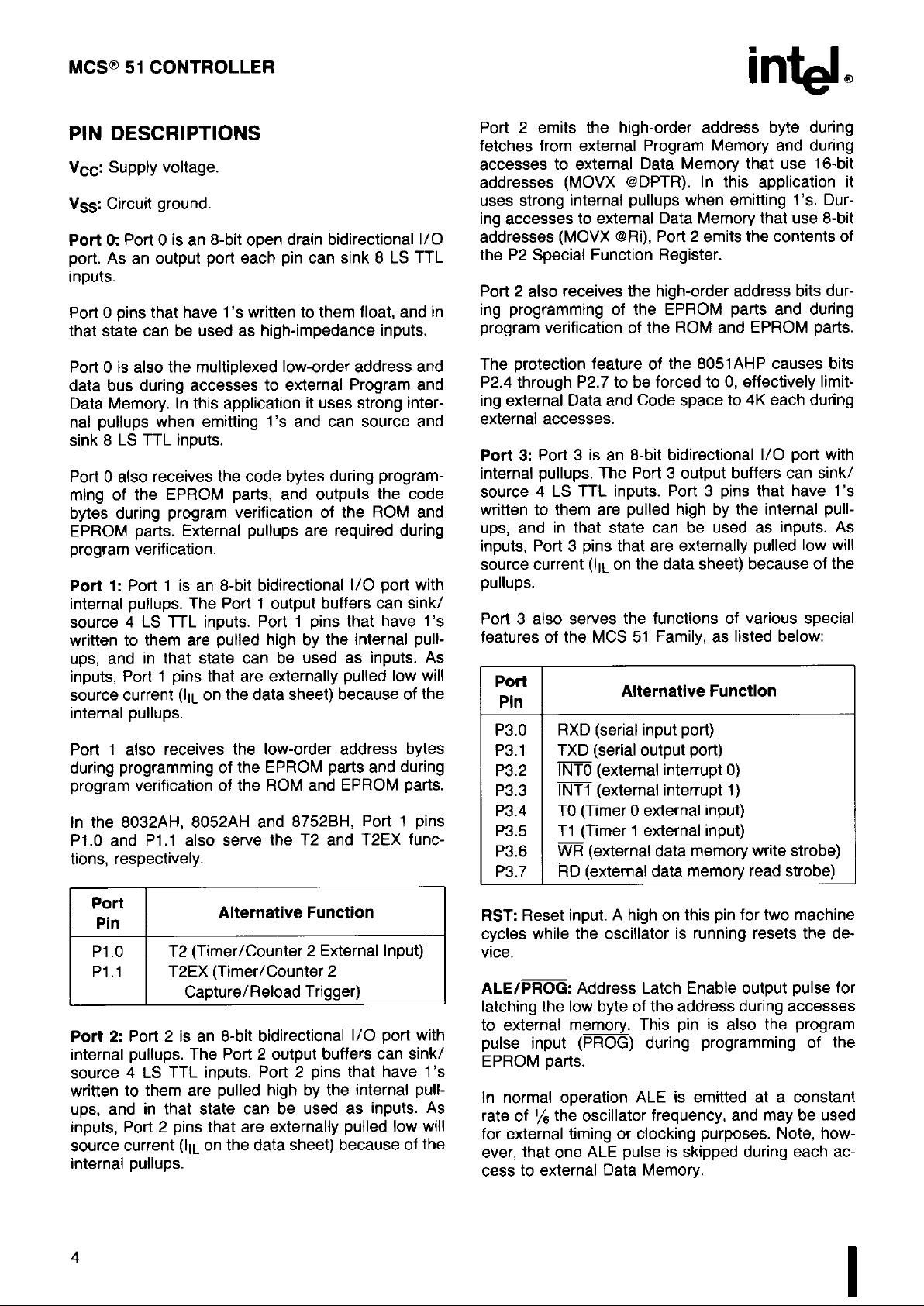

Cl, C2 = 30 PF +10 PFfor Crystals

ForCeramic Resonatorscontactresonatormanufacturer.

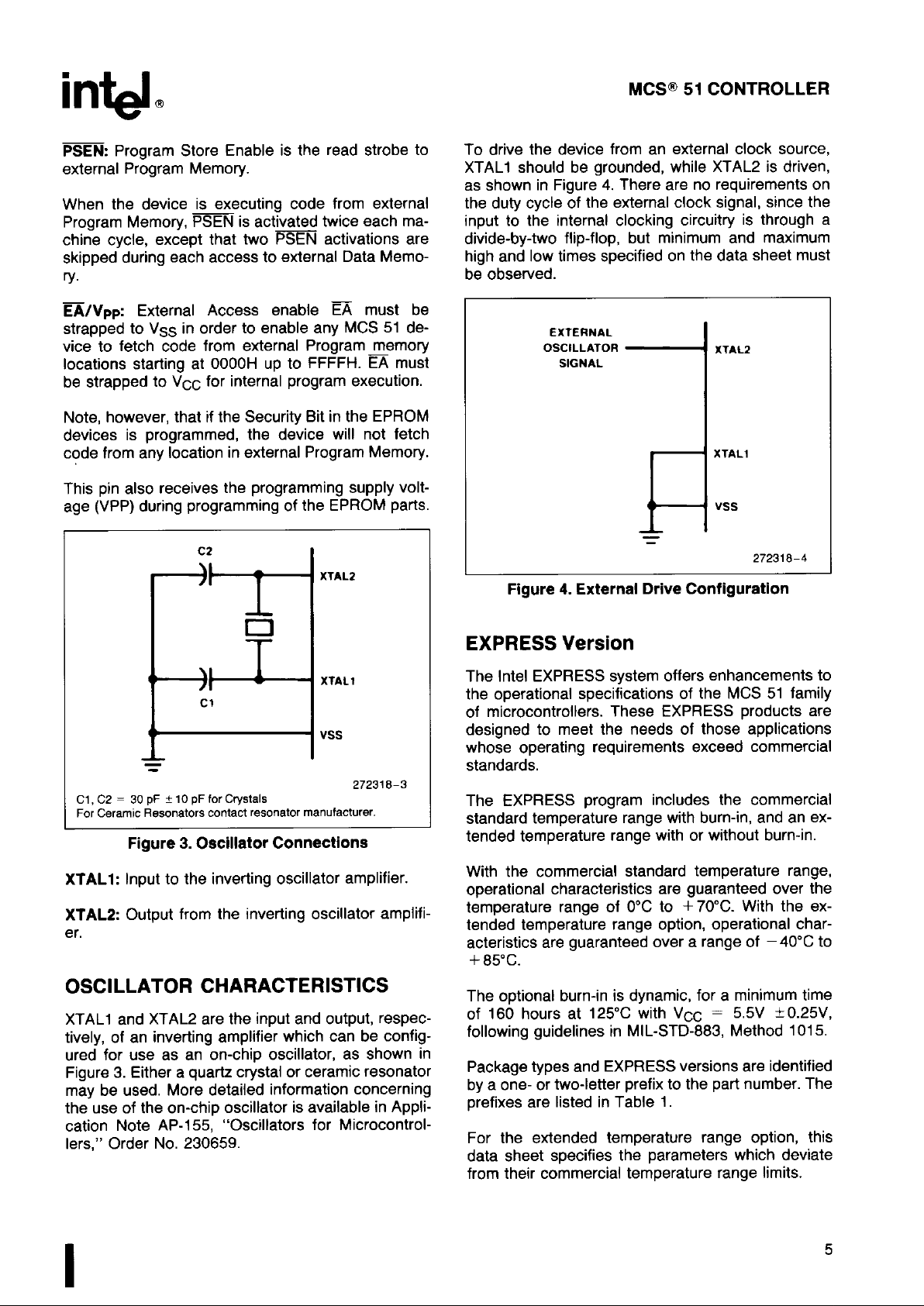

Figure 3. Oscillator Connections

XTAL1: Input to the inverting oscillator amplifier.

XTAL2: Output from the inverting oscillator amplifi-

er,

OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in

Figure 3. Either a quartz crystal or ceramic resonator

may be used. More detailed information concerning

the use of the on-chip oscillator is available in Application Note AP-155; “Oscillators

Iers,” Order No, 230659.

I

for Microcontrol-

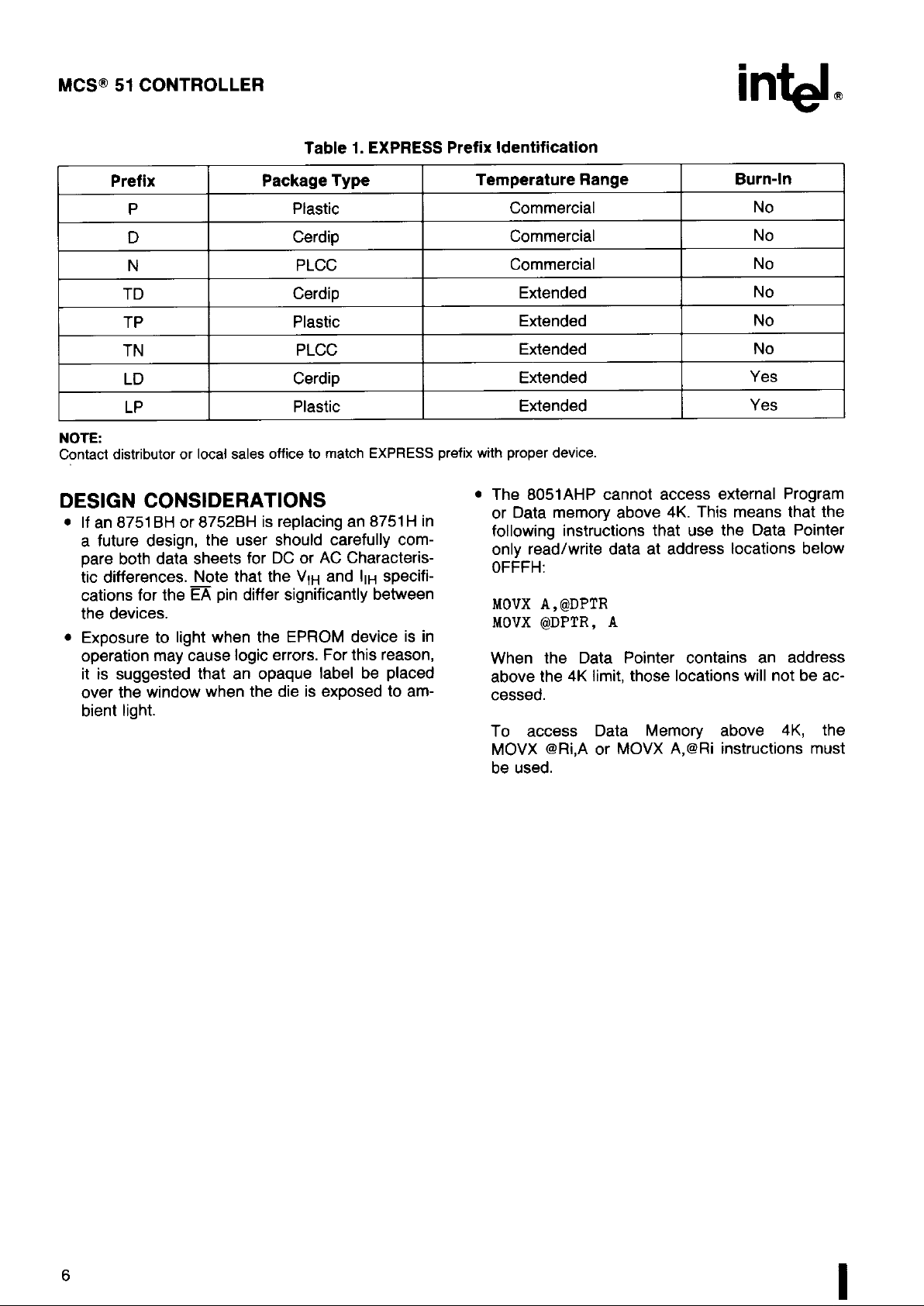

To drive the device from an external clock source,

XTAL1 should be grounded, while XTAL2 is driven,

as shown in Figure 4. There are no requirements on

the duty cycle of the external clock signal, since the

input to the internal clocking circuitry is through a

divide-by-two flip-flop, but minimum and maximum

high and low times specified on the data sheet must

be observed.

EXTERNAL

OSCILLATOR

SIGNAL

XTAL2

XTAL1

Vss

272318-4

Figure 4. External Drive Configuration

EXPRESS Version

The Intel EXPRESSsystem offers enhancements to

the operational specifications of the MCS 51 family

of microcontrollers. These EXPRESS products are

designed to meet the needs of those applications

whose operating requirements exceed commercial

standards.

The EXPRESS program includes the commercial

standard temperature range with burn-in, and an extended temperature range with or without burn-in.

With the commercial standard temperature range,

operational characteristics are guaranteed over the

temperature range of O“C to + 70”C. With the extended temperature range option, operational characteristics are guaranteed over a range of –40”C to

+ 85”C.

The optional burn-in is dynamic, for a minimum time

of 160 hours at 125°C with VCC = 5.5V * 0.25V,

following guidelines in MIL-STD-883, Method 1015.

Package types and EXPRESSversions are identified

by a one- or two-letter prefix to the part number. The

prefixes are listed in Table 1.

For the extended temperature range option, this

data sheet specifies the parameters which deviate

from their commercial temperature range limits.

5

MCS@51 CONTROLLER

Table 1.EXPRESSPrefix Identification

Prefix Package Type

Temperature Range

Burn-In

P Plastic

Commercial

No

D Cerdip Commercial

No

N PLCC Commercial

No

TD Cerdip Extended

No

TP Plastic Extended No

TN

PLCC Extended No

LD Cerdip Extended

Yes

LP Plastic Extended

Yes

NOTE:

Contactdistributoror localsalesofficeto matchEXPRESSprefixwithproperdevice.

DESIGN CONSIDERATIONS

If an 8751BH or 8752BH is replacing an 8751H in

a future design, the user should carefully compare both data sheets for DCor AC Characteris-

tic differences. Note that the VIH and IIHspecifi-

cations for the ~ pin differ significantly between

the devices.

Exposure to light when the EPROM device is in

operation may cause logic errors. For this reason,

it is suggested that an opaque label be placed

over the window when the die is exposed to ambient light.

●

The 8051AHP cannot access external Program

or Data memory above 4K. This means that the

following instructions that use the Data Pointer

only read/write data at address locations below

OFFFH:

MOVX A,@DPTR

MOVX (6JDPTR,A

When the Data Pointer contains an address

above the 4K limit, those locations will not be accessed.

To access Data Memory above 4K, the

MOVX @Ri,Aor MOVX A,@Ri instructions must

be used.

6

MCS” 51 CONTROLLER

ABSOLUTE MAXIMUM RATINGS*

Ambient Temperature Under Bias –40”C to + 85°C

Storage Temperature . –65°C to + 150°C

Voltage on EA/Vpp Pin to Vss

8751H . . . . . . . . . . . . . .. . . –0.5V to + 21.5V

8751BH/6752BH –0.5V

tO + 13.OV

Voltage on Any Other Pinto Vss . –0.5V to + 7V

Power Dissipation. . . ... 1.5W

OPERATING CONDITIONS

NOTICE:This is a productiondatasheet.It is validfor

the devices indicated in the revision history. The

specificationsare subjectto changewithout notice.

*WARNING:

Stressing the device beyond the “Absolute

Maximum Ratings” may cause permanent damage.

These are stress ratings orr~. Operation beyond the

“Operating Conditions” is not recommended and extended exposure beyond the “Operating Conditions”

may affect device reliabili~.

Symbol Description Min

Msx

Units

TA

Ambient Temperature Under Bias

Commercial o

+70

“c

Express –40 +65 “c

Vcc SupplyVoltage

4.5

5.5

v

Fosc

OscillatorFrequency

3.5 12 MHz

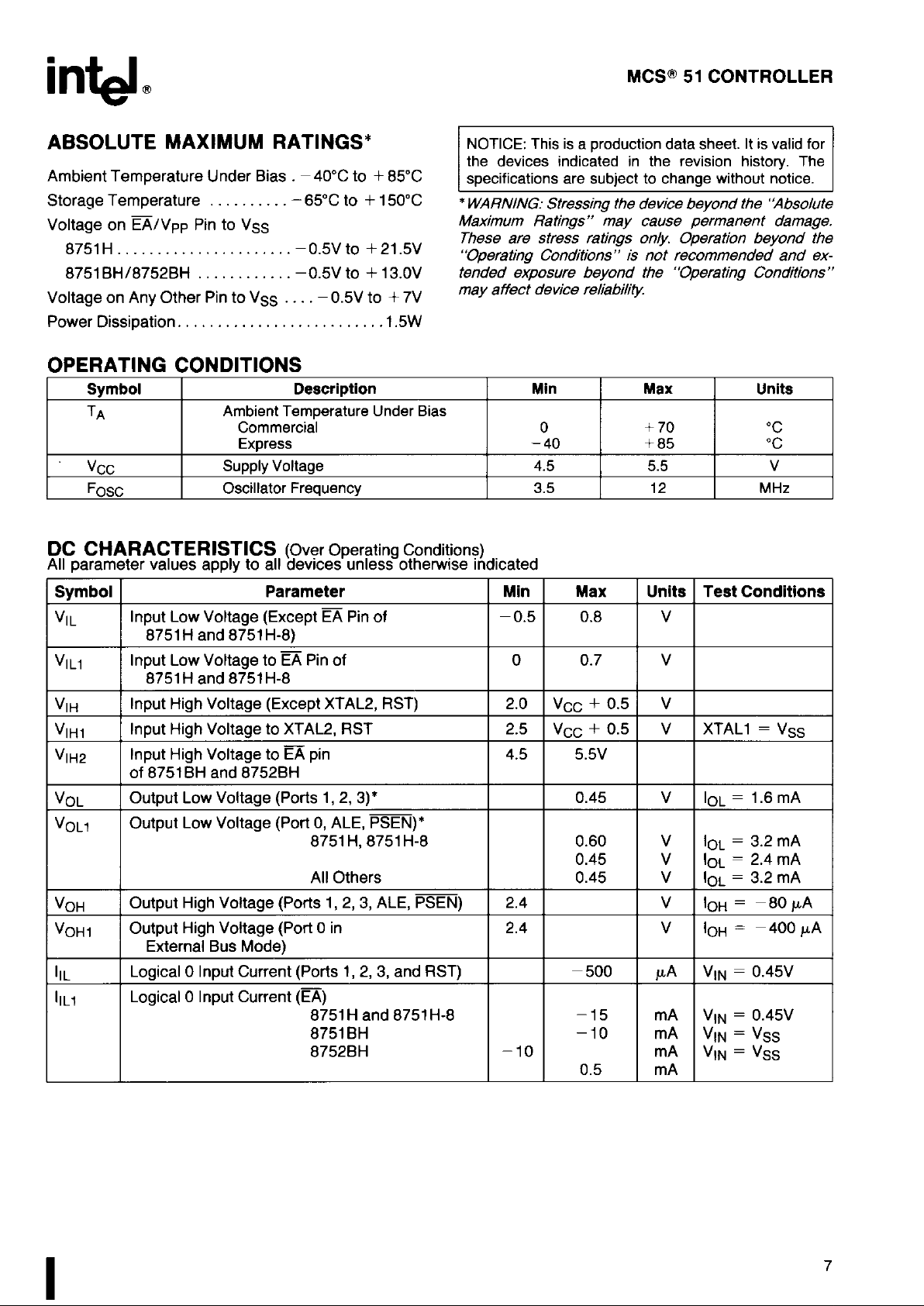

DC CHARACTERISTICS (OverOperating Conditions)

All parameter values apply to all devices unless otherwise indicated

Symbol

Parameter Min Max Units Test Conditions

VIL Input Low Voltage (Except~ Pin of –0.5 0.8 v

6751H and 8751H-8)

VIL1 Input Low Voltage to ~ Pinof o 0.7

v

6751H and 8751H-8

VIH Input High Voltage (Except XTAL2, RST) 2.0 Vcc + 0.5 v

VIH1 Input High Voltage to XTAL2, RST 2.5 Vcc + 0.5 v XTAL1 = Vss

VIH2 Input High Voltage to ~ pin 4.5 5.5V

of 6751BHand 8752BH

VoL Output Low Voltage (Ports 1,2, 3)*

0.45 v loL = 1.6 mA

VoLl

Output Low Voltage (Port O,ALE, PSEN)*

8751H, 8751H-8 0.60

v ioL = 3.2 mA

0.45 v !OL= 2.4 mA

All Others 0.45

v IOL= 3.2 mA

VOH Output High Voltage (Ports 1,2,3, ALE, PSEN)

2.4 v IOH= –80 PA

VOH1 Output High Voltage (Port Oin

2.4 v IOH= –400 pA

External Bus Mode)

IIL Logical OInput Current (Ports 1,2,3, and RST) –500

pA

VIN = 0.45V

IILI

Logical OInput Current (~)

8751H and 8751H-8

–15 mA VIN = 0.45V

8751BH –lo mA VIN = Vss

8752BH

–lo mA VIN = Vss

0.5 mA

7

Loading...

Loading...