Intel Corporation TE28F008SA-100, TB28F008SA-100 Datasheet

28F008SA

8-MBIT (1-MBIT x 8) FlashFileTMMEMORY

Extended Temperature Specifications Included

Y

High-Density Symmetrically-Blocked

Architecture

Ð Sixteen 64-Kbyte Blocks

Y

Extended Cycling Capability

Ð 100,000 Block Erase Cycles

Ð 1.6 Million Block Erase

Cycles per Chip

Y

Automated Byte Write and Block Erase

Ð Command User Interface

Ð Status Register

Y

System Performance Enhancements

Ð RY/BY

Ý

Status Output

Ð Erase Suspend Capability

Intel’s 28F008SA 8-Mbit FlashFileTMMemory is the highest density nonvolatile read/write solution for solid-state storage. The 28F008SA’s extended cycling, symmetrically blocked architecture, fast access time,

write automation and low power consumption provide a more reliable, lower power, lighter weight and higher

performance alternative to traditional rotating disk technology. The 28F008SA brings new capabilities to portable computing. Application and operating system software stored in resident flash memory arrays provide

instant-on, rapid execute-in-place and protection from obsolescence through in-system software updates.

Resident software also extends system battery life and increases reliability by reducing disk drive accesses.

For high density data acquisition applications, the 28F008SA offers a more cost-effective and reliable alternative to SRAM and battery. Traditional high density embedded applications, such as telecommunications, can

take advantage of the 28F008SA’s nonvolatility, blocking and minimal system code requirements for flexible

firmware and modular software designs.

The 28F008SA is offered in 40-lead TSOP (standard and reverse) and 44-lead PSOP packages. Pin assignments simplify board layout when integrating multiple devices in a flash memory array or subsystem. This

device uses an integrated Command User Interface and state machine for simplified block erasure and byte

write. The 28F008SA memory map consists of 16 separately erasable 64-Kbyte blocks.

Y

Deep Power-Down Mode

Ð 0.20 mAI

Y

Very High-Performance Read

CC

Typical

Ð 85 ns Maximum Access Time

Y

SRAM-Compatible Write Interface

Y

Hardware Data Protection Feature

Ð Erase/Write Lockout during Power

Transitions

Y

Industry Standard Packaging

Ð 40-Lead TSOP, 44-Lead PSOP

Y

ETOX III Nonvolatile Flash Technology

Ð 12V Byte Write/Block Erase

Intel’s 28F008SA employs advanced CMOS circuitry for systems requiring low power consumption and noise

immunity. Its 85 ns access time provides superior performance when compared with magnetic storage media.

A deep powerdown mode lowers power consumption to 1 mW typical thru V

handheld instrumentation and other low-power applications. The RP

absolute data protection during system powerup/down.

Manufactured on Intel’s 0.8 micron ETOX process, the 28F008SA provides the highest levels of quality,

reliability and cost-effectiveness.

*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

November 1995COPYRIGHT©INTEL CORPORATION, 1995 Order Number: 290429-005

, crucial in portable computing,

CC

Ý

power control input also provides

28F008SA

PRODUCT OVERVIEW

The 28F008SA is a high-performance 8-Mbit

(8,388,608 bit) memory organized as 1 Mbyte

(1,048,576 bytes) of 8 bits each. Sixteen 64-Kbyte

(65,536 byte) blocks are included on the 28F008SA.

A memory map is shown in Figure 6 of this specification. A block erase operation erases one of the sixteen blocks of memory in typically 1.6 seconds, independent of the remaining blocks. Each block can

be independently erased and written 100,000 cy-

cles. Erase Suspend mode allows system software

to suspend block erase to read data or execute

code from any other block of the 28F008SA.

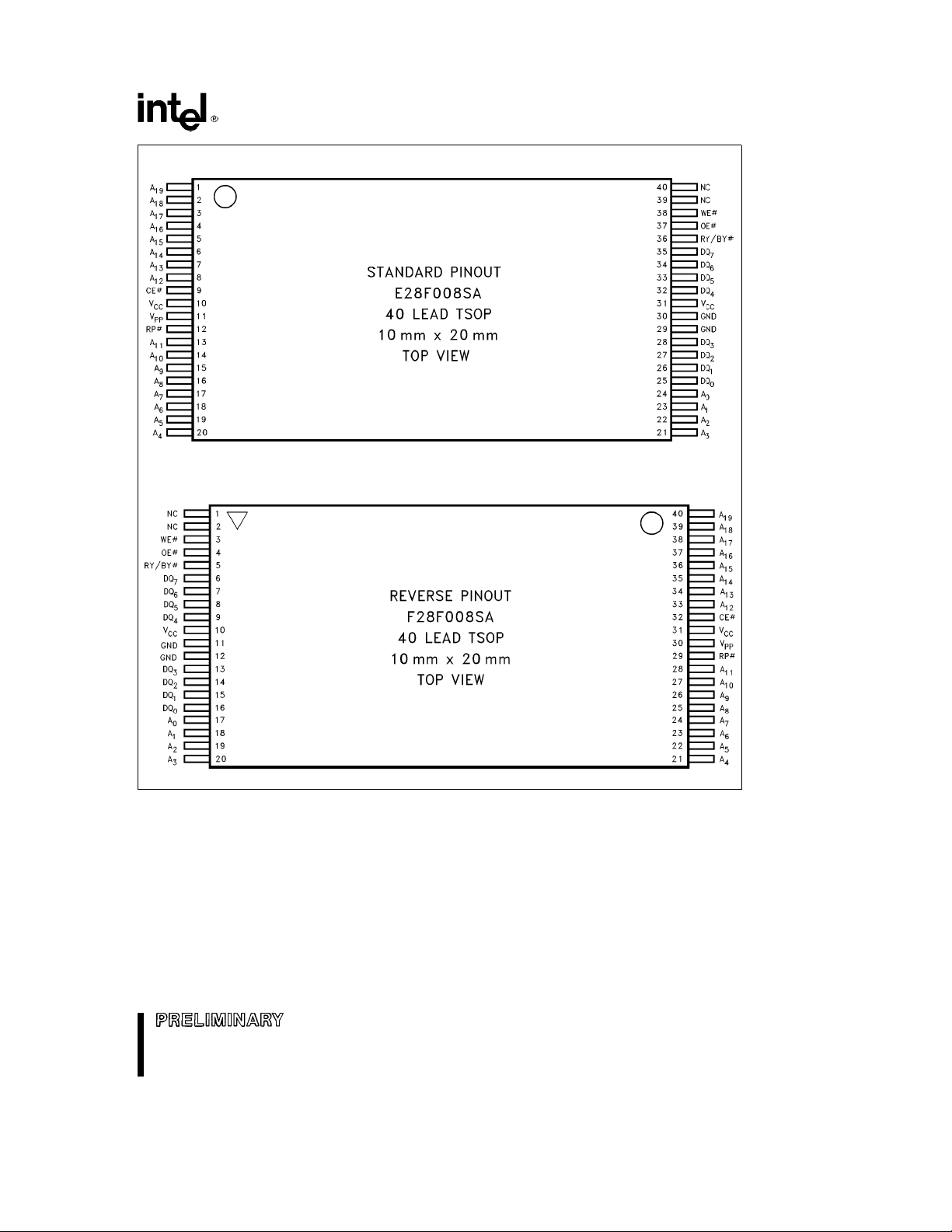

The 28F008SA is available in the 40-lead TSOP

(Thin Small Outline Package, 1.2 mm thick) and 44-

lead PSOP (Plastic Small Outline) packages. Pinouts are shown in Figures 2 and 4 of this specification.

The Command User Interface serves as the interface between the microprocessor or microcontroller

and the internal operation of the 28F008SA.

Byte Write and Block Erase Automation allow

byte write and block erase operations to be executed using a two-write command sequence to the

Command User Interface. The internal Write State

Machine (WSM) automatically executes the algorithms and timings necessary for byte write and

block erase operations, including verifications,

thereby unburdening the microprocessor or microcontroller. Writing of memory data is performed in

byte increments typically within 9 ms, an 80% improvement over current flash memory products. I

byte write and block erase currents are 10 mA

typical, 30 mA maximum. V

block erase voltage is 11.4V to 12.6V.

byte write and

PP

PP

The Status Register indicates the status of the

WSM and when the WSM successfully completes

the desired byte write or block erase operation.

Ý

The RY/BY

output gives an additional indicator of

WSM activity, providing capability for both hardware

signal of status (versus software polling) and status

masking (interrupt masking for background erase,

for example). Status polling using RY/BYÝminimizes both CPU overhead and system power consumption. When low, RY/BY

Ý

indicates that the

WSM is performing a block erase or byte write operation. RY/BY

Ý

high indicates that the WSM is ready

for new commands, block erase is suspended or the

device is in deep powerdown mode.

Maximum access time is 85 ns (t

mercial temperature range (0

supply voltage range (4.5V to 5.5V and 4.75V to

V

CC

5.25V). I

typical, 35 mA maximum at 8 MHz.

When the CE

active current (CMOS Read) is 20 mA

CC

Ý

and RPÝpins are at VCC, the I

CMOS Standby mode is enabled.

) over the com-

ACC

Ctoa70§C) and over

§

CC

A Deep Powerdown mode is enabled when the

Ý

RP

pin is at GND, minimizing power consumption

and providing write protection. I

powerdown is 0.20 mA typical. Reset time of 400 ns

is required from RP

Ý

switching high until outputs are

current in deep

CC

valid to read attempts. Equivalently, the device has a

wake time of 1 ms from RP

Ý

high until writes to the

Command User Interface are recognized by the

28F008SA. With RP

Ý

at GND, the WSM is reset

and the Status Register is cleared.

2

28F008SA

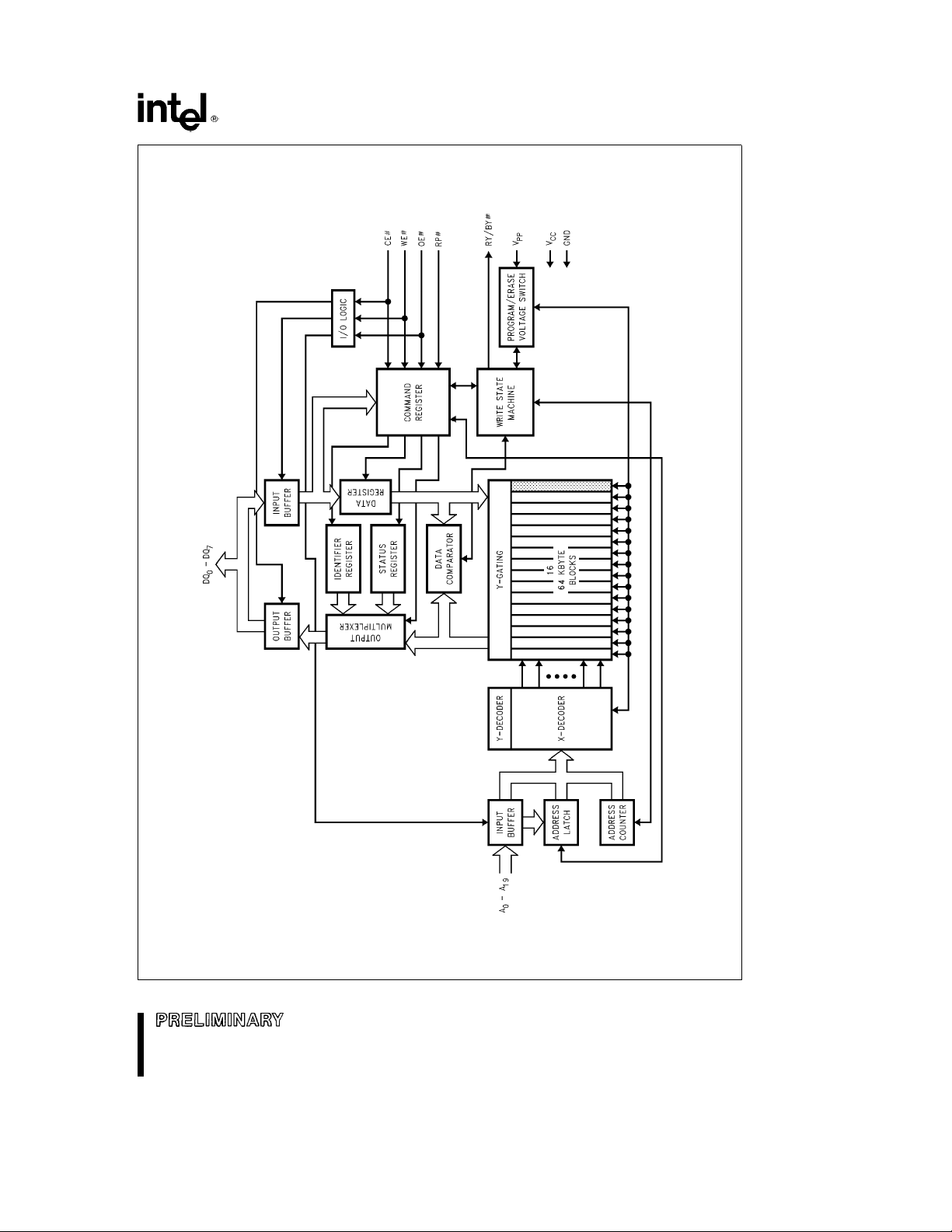

290429– 1

Figure 1. Block Diagram

3

28F008SA

Table 1. Pin Description

Symbol Type Name and Function

A0–A

19

DQ0–DQ7INPUT/OUTPUT DATA INPUT/OUTPUTS: Inputs data and commands during Command

Ý

CE

Ý

RP

Ý

OE

Ý

WE

Ý

RY/BY

V

PP

V

CC

GND GROUND

INPUT ADDRESS INPUTS for memory addresses. Addresses are internally

latched during a write cycle.

User Interface write cycles; outputs data during memory array, Status

Register and Identifier read cycles. The data pins are active high and

float to tri-state off when the chip is deselected or the outputs are

disabled. Data is internally latched during a write cycle.

INPUT CHIP ENABLE: Activates the device’s control logic, input buffers,

decoders, and sense amplifiers. CE

Ý

is active low; CEÝhigh deselects

the memory device and reduces power consumption to standby levels.

INPUT RESET/DEEP POWERDOWN: Puts the device in deep powerdown

Ý

mode. RP

is active low; RPÝhigh gates normal operation. RPÝalso

locks out block erase or byte write operations when active low, providing

data protection during power transitions. RP

Ý

active resets internal

automation. Exit from Deep Powerdown sets device to read-array mode.

INPUT OUTPUT ENABLE: Gates the device’s outputs through the data buffers

Ý

during a read cycle. OE

is active low.

INPUT WRITE ENABLE: Controls writes to the Command User Interface and

Ý

array blocks. WE

is active low. Addresses and data are latched on the

rising edge of the WEÝpulse.

OUTPUT READY/BUSYÝ: Indicates the status of the internal Write State

Machine. When low, it indicates that the WSM is performing a block

erase or byte write operation. RY/BY

Ý

high indicates that the WSM is

ready for new commands, block erase is suspended or the device is in

deep powerdown mode. RY/BY

Ý

is always active and does NOT float

to tri-state off when the chip is deselected or data outputs are disabled.

BLOCK ERASE/BYTE WRITE POWER SUPPLY for erasing blocks of

the array or writing bytes of each block.

NOTE:

PP

k

V

PPLMAX

, memory contents cannot be altered.

With V

DEVICE POWER SUPPLY (5Vg10%, 5Vg5%)

4

Standard Pinout

Reverse Pinout

28F008SA

290429– 2

Figure 2. TSOP Lead Configurations

290429– 3

5

28F008SA

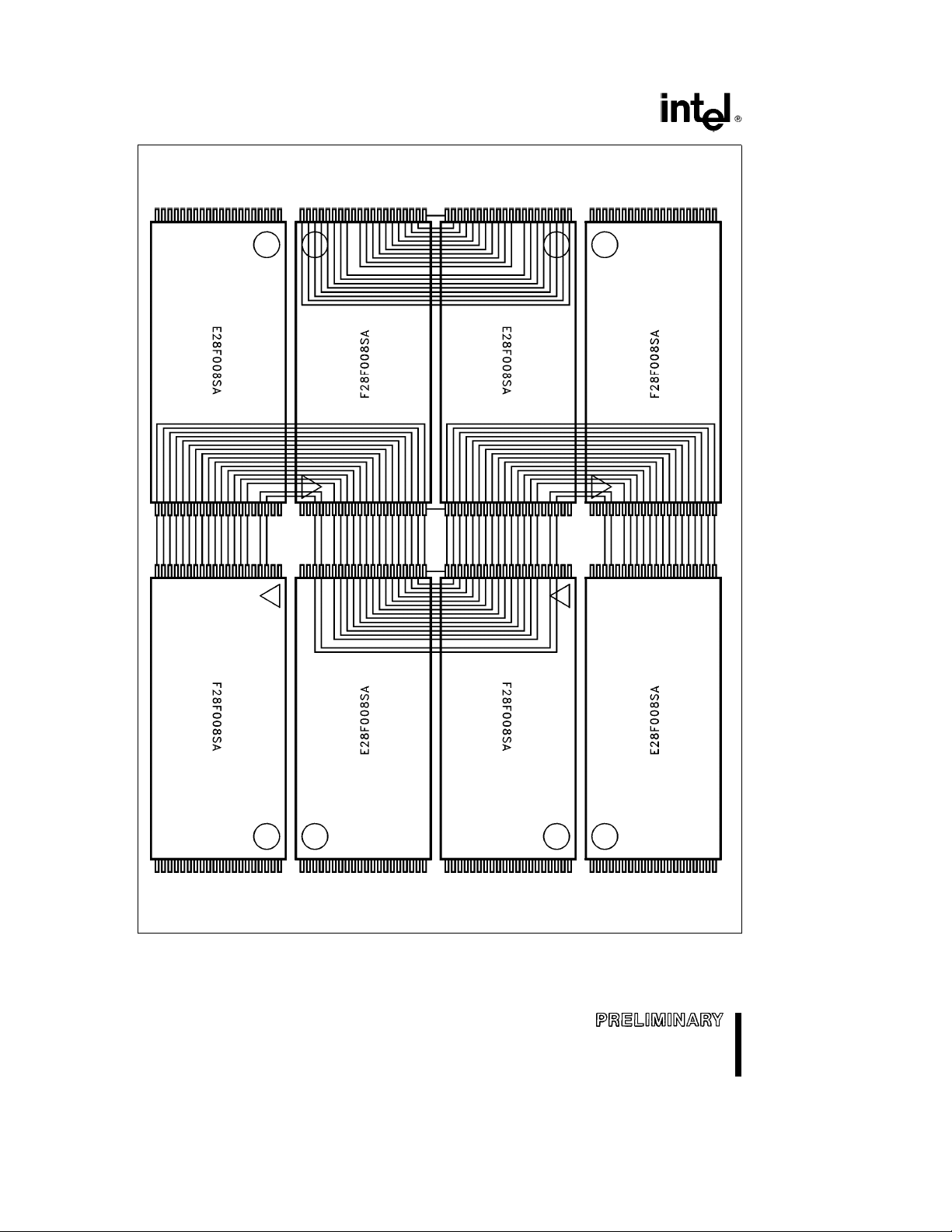

290429– 4

NOTE:

1. Connect all V

disconnected.

6

Figure 3. TSOP Serpentine Layout

and GND pins of each device to common power supply outputs. DO NOT leave VCCor GND inputs

CC

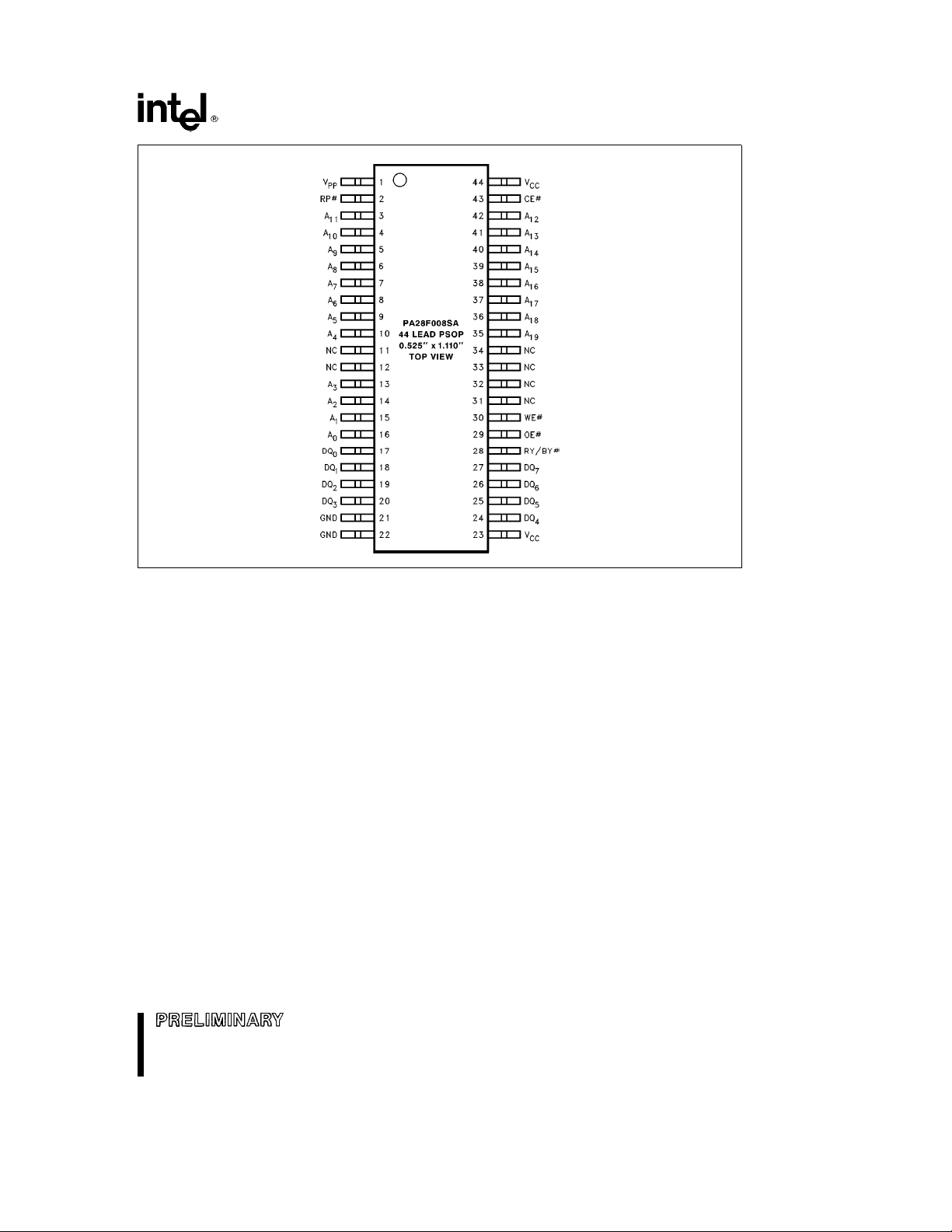

Figure 4. PSOP Lead Configuration

28F008SA

290429– 19

7

28F008SA

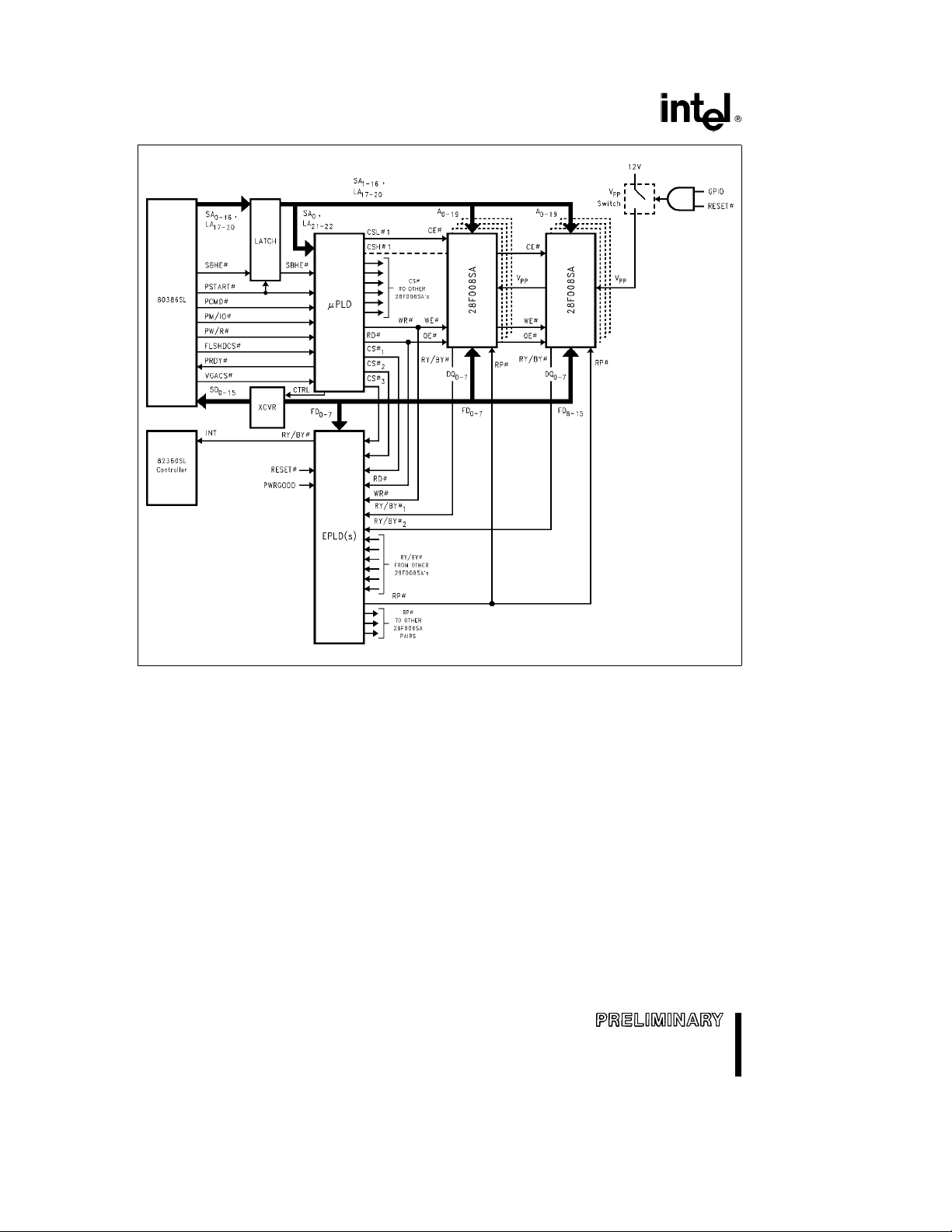

Figure 5. 28F008SA Array Interface to Intel386SL Microprocessor Superset through PI Bus

(Including RY/BY

Ý

Masking and Selective Powerdown), for DRAM Backup during System SUSPEND,

Resident O/S and Applications and Motherboard Solid-State Disk.

8

290429– 5

28F008SA

PRINCIPLES OF OPERATION

The 28F008SA includes on-chip write automation to

manage write and erase functions. The Write State

Machine allows for 100% TTL-level control inputs,

fixed power supplies during block erasure and byte

write, and minimal processor overhead with RAMlike interface timings.

After initial device powerup, or after return from

deep powerdown mode (see Bus Operations), the

28F008SA functions as a read-only memory. Manipulation of external memory-control pins allow array

read, standby and output disable operations. Both

Status Register and intelligent identifiers can also be

accessed through the Command User Interface

when V

This same subset of operations is also available

when high voltage is applied to the V

tion, high voltage on V

erasure and byte writing of the device. All functions

associated with altering memory contentsÐbyte

write, block erase, status and intelligent identifierÐ

are accessed via the Command User Interface and

verified thru the Status Register.

Commands are written using standard microprocessor write timings. Command User Interface contents

serve as input to the WSM, which controls the block

erase and byte write circuitry. Write cycles also internally latch addresses and data needed for byte write

or block erase operations. With the appropriate command written to the register, standard microprocessor read timings output array data, access the intelligent identifier codes, or output byte write and block

erase status for verification.

Interface software to initiate and poll progress of internal byte write and block erase can be stored in

any of the 28F008SA blocks. This code is copied to,

and executed from, system RAM during actual flash

memory update. After successful completion of byte

write and/or block erase, code/data reads from the

28F008SA are again possible via the Read Array

command. Erase suspend/resume capability allows

system software to suspend block erase to read

data and execute code from any other block.

PP

e

V

.

PPL

pin. In addi-

enables successful block

PP

PP

FFFFF

F0000

EFFFF

E0000

DFFFF

D0000

CFFFF

C0000

BFFFF

B0000

AFFFF

A0000

9FFFF

90000

8FFFF

80000

7FFFF

70000

6FFFF

60000

5FFFF

50000

4FFFF

40000

3FFFF

30000

2FFFF

20000

1FFFF

10000

0FFFF

00000

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

64-Kbyte Block

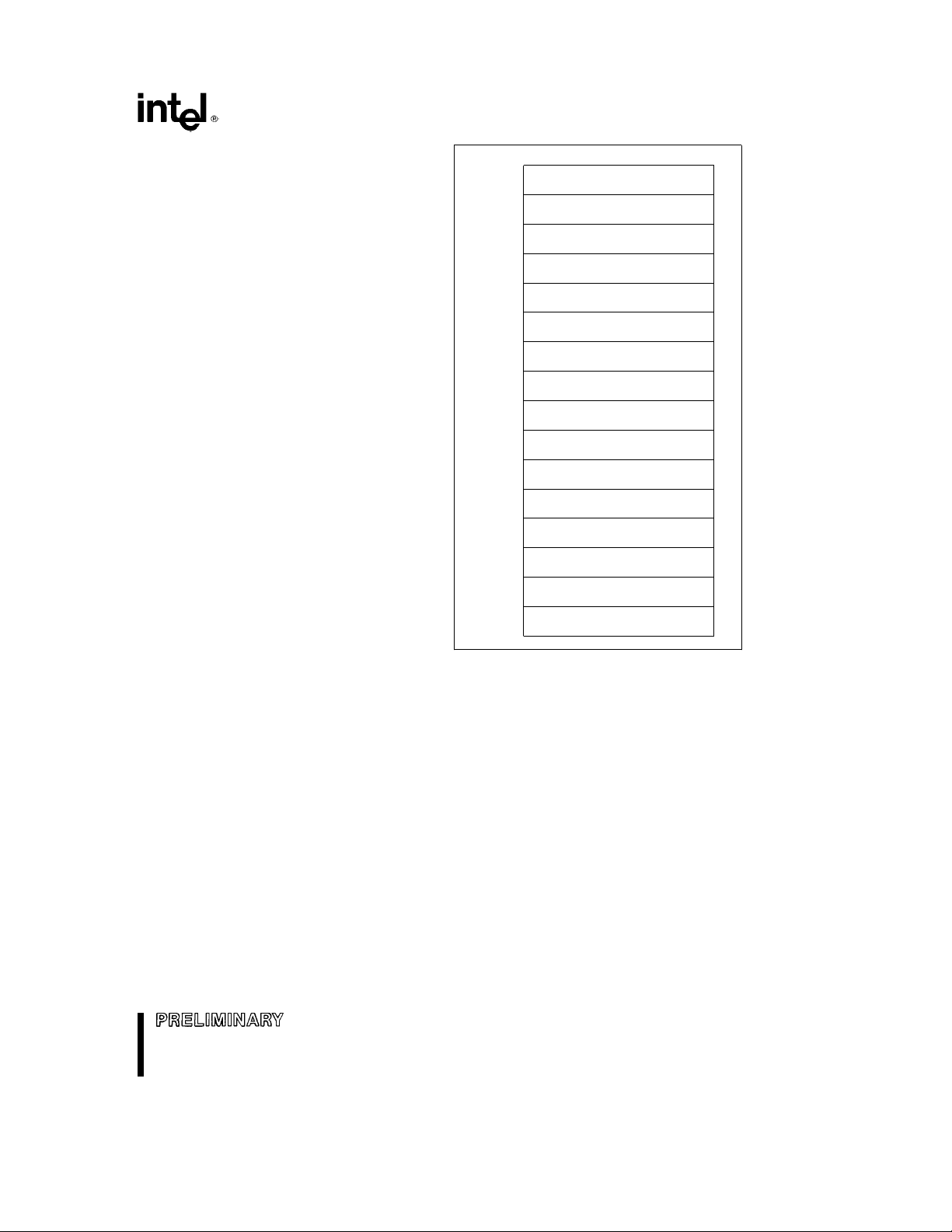

Figure 6. Memory Map

Command User Interface and Write

Automation

An on-chip state machine controls block erase and

byte write, freeing the system processor for other

tasks. After receiving the Erase Setup and Erase

Confirm commands, the state machine controls

block pre-conditioning and erase, returning progress

via the Status Register and RY/BY

write is similarly controlled, after destination address

and expected data are supplied. The program and

erase algorithms of past Intel flash memories are

now regulated by the state machine, including pulse

repetition where required and internal verification

and margining of data.

Ý

output. Byte

9

28F008SA

Data Protection

Depending on the application, the system designer

may choose to make the V

ble (available only when memory byte writes/block

erases are required) or hardwired to V

e

V

V

PP

The 28F008SA Command User Interface architec-

, memory contents cannot be altered.

PPL

ture provides protection from unwanted byte write or

block erase operations even when high voltage is

applied to VPP. Additionally, all functions are disabled whenever V

age V

accommodates either design practice and encour-

, or when RPÝis at VIL. The 28F008SA

LKO

is below the write lockout volt-

CC

power supply switcha-

PP

PPH

. When

The first task is to write the appropriate read mode

command to the Command User Interface (array, intelligent identifier, or Status Register). The

28F008SA automatically resets to Read Array mode

upon initial device powerup or after exit from deep

powerdown. The 28F008SA has four control pins,

two of which must be logically active to obtain data

at the outputs. Chip Enable (CE

lection control, and when active enables the selected memory device. Output Enable (OE

input/output (DQ

active drives data from the selected memory onto

the I/O bus. RP

–DQ7) direction control, and when

0

Ý

and WEÝmust also be at VIH.

Figure 10 illustrates read bus cycle waveforms.

ages optimization of the processor-memory interface.

Output Disable

The two-step byte write/block erase Command User

Interface write sequence provides additional software write protection.

BUS OPERATION

Flash memory reads, erases and writes in-system

via the local CPU. All bus cycles to or from the flash

memory conform to standard microprocessor bus

cycles.

Read

The 28F008SA has three read modes. The memory

can be read from any of its blocks, and information

can be read from the intelligent identifier or Status

Register. V

Read 1,2,3 V

Output Disable 1,2,3 V

Standby 1,2,3 V

Deep PowerDown 1,2 V

Intelligent Identifier (Mfr) 1,2 V

Intelligent Identifier (Device) 1,2 V

Write 1,2,3,4,5 V

NOTES:

1. Refer to DC Characteristics. When V

2. X can be V

voltages.

3. RY/BY

the WSM is not busy, in Erase Suspend mode or deep powerdown mode.

4. Command writes involving block erase or byte write are only successfully executed when V

5. Refer to Table 3 for valid D

can be at either V

PP

PPL

or V

PPH

.

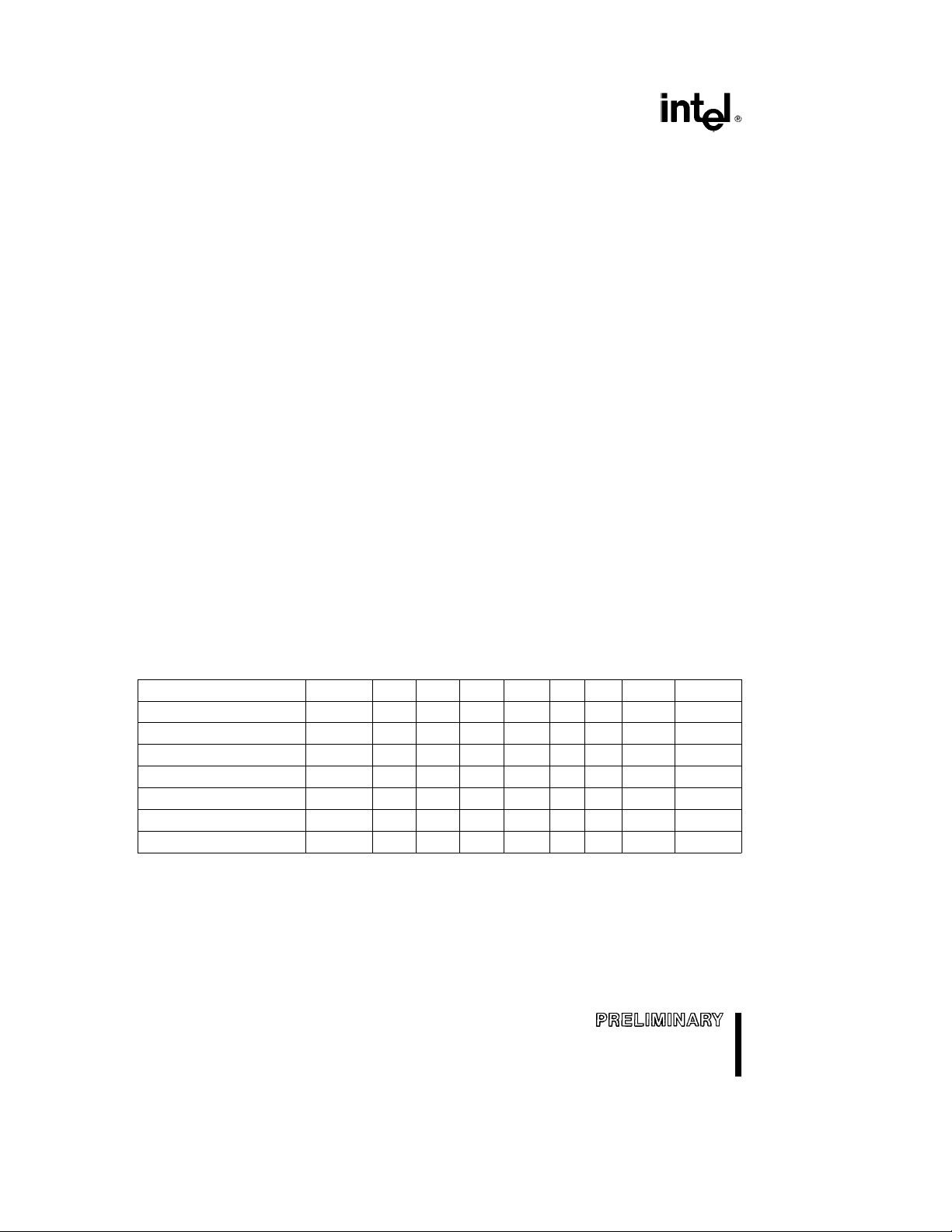

Table 2. Bus Operations

Mode Notes RPÝCEÝOEÝWEÝA0VPPDQ

IH

IH

IH

IL

IH

IH

IH

e

V

or VIHfor control pins and addresses, and V

IL

Ý

is VOLwhen the Write State Machine is executing internal block erase or byte write algorithms. It is VOHwhen

PP

during a write operation.

IN

, memory contents can be read but not written or erased.

PPL

With OEÝat a logic-high level (VIH), the device out-

puts are disabled. Output pins (DQ

placed in a high-impedance state.

Standby

CEÝat a logic-high level (VIH) places the 28F008SA

in standby mode. Standby operation disables much

of the 28F008SA’s circuitry and substantially reduc-

es device power consumption. The outputs (DQ

DQ

) are placed in a high-impedence state indepen-

7

dent of the status of OE

lected during block erase or byte write, the device

will continue functioning and consuming normal ac-

tive power until the operation completes.

V

V

V

IL

IL

V

V

IL

IH

V

X X X X High Z X

IH

X X X X X High Z V

V

V

IL

IL

V

V

IL

IL

V

V

IL

IH

or V

PPL

for VPP. See DC Characteristics for V

PPH

XXD

IH

V

X X High Z X

IH

V

IHVIL

V

IHVIH

V

XX DINX

IL

Ý

) is the device se-

Ý

) is the data

–DQ7) are

0

Ý

. If the 28F008SA is dese-

RY/BY

0–7

PPL

X

OH

OH

OH

and V

OUT

X 89H V

X A2H V

e

V

PPH

.

PP

0

Ý

PPH

–

10

Loading...

Loading...