Intel Corporation TA80960CA-25, TA80960CA-16 Datasheet

December 1994 Order Number: 271327-001

SPECIAL ENVIRONMENT 80960CA-25, -16

32-BIT HIGH-PERFORMANCE EMBEDDED PROCESSOR

#

Two Instructions/Clock Sustained Execution

#

Four 59 Mbytes/s DMA Channels with Data Chaining

#

Demultiplexed 32-bit Burst Bus with Pipelining

Y

32-bit Parallel Architecture

Ð Two Instructions/clock Execution

Ð Load/Store Architecture

Ð Sixteen 32-bit Global Registers

Ð Sixteen 32-bit Local Registers

Ð Manipulates 64-bit Bit Fields

Ð 11 Addressing Modes

Ð Full Parallel Fault Model

Ð Supervisor Protection Model

Y

Fast Procedure Call/Return Model

Ð Full Procedure Call in 4 Clocks

Y

On-Chip Register Cache

Ð Caches Registers on Call/Ret

Ð Minimum of 6 Frames Provided

Ð Up to 15 Programmable Frames

Y

On-Chip instruction Cache

Ð 1 Kbyte Two-Way Set Associative

Ð 128-bit Path to instruction Sequencer

Ð Cache-Lock Modes

Ð Cache-Off Mode

Y

High Bandwidth On-Chip Data RAM

Ð 1 Kbyte On-Chip Data RAM

Ð Sustains 128 bits per Clock Access

Y

Four On-Chip DMA Channels

Ð 59 Mbytes/s Fly-by Transfers

Ð 32 Mbytes/s Two-Cycle Transfers

Ð Data Chaining

Ð Data Packing/Unpacking

Ð Programmable Priority Method

Y

32-Bit Demultiplexed Burst Bus

Ð 128-bit internal Data Paths to

and

from Registers

Ð Burst Bus for DRAM Interfacing

Ð Address Pipelining Option

Ð Fully Programmable Wait States

Ð Supports 8-, 16- or 32-bit Bus Widths

Ð Supports Unaligned Accesses

Ð Supervisor Protection Pin

Y

Selectable Big or Little Endian Byte

Ordering

Y

High-Speed Interrupt Controller

Ð Up to 248 External interrupts

Ð 32 Fully Programmable Priorities

Ð Multi-mode 8-bit Interrupt Port

Ð Four internal DMA Interrupts

Ð Separate, Non-maskable interrupt Pin

Ð Context Switch in 750 ns Typical

Y

Product Grades Available

Ð SE3:

b

40§Ctoa110§C

SPECIAL ENVIRONMENT 80960CA-25, -16

32-BIT HIGH-PERFORMANCE EMBEDDED PROCESSOR

CONTENTS PAGE

1.0 PURPOSE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 5

2.0 80960CA OVERVIEW ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 5

2.1 The C-Series Core АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 6

2.2 Pipelined, Burst Bus АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 6

2.3 Flexible DMA Controller АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 6

2.4 Priority Interrupt Controller АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 6

2.5 Instruction Set Summary АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 7

3.0 PACKAGE INFORMATION ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 8

3.1 Package Introduction ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 8

3.2 Pin Descriptions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 8

3.3 80960CA Mechanical Data АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

3.3.1 80960CA PGA Pinout ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

3.4 Package Thermal Specifications ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 19

3.5 Stepping Register Information ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 21

3.6 Suggested Sources for 80960CA Accessories ААААААААААААААААААААААААААААААААААААААААА 21

4.0 ELECTRICAL SPECIFICATIONS АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 22

4.1 Absolute Maximum Ratings АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 22

4.2 Operating Conditions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 22

4.3 Recommended Connections ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 22

4.4 DC Specifications ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 23

4.5 AC Specifications ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 24

4.5.1 AC Test Conditions ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 28

4.5.2 AC Timing Waveforms АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 28

4.5.3 Derating Curves АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 32

5.0 RESET, BACKOFF AND HOLD ACKNOWLEDGE ААААААААААААААААААААААААААААААААААААААА 34

6.0 BUS WAVEFORMS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 35

7.0 REVISION HISTORY АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 62

2

CONTENTS PAGE

LIST OF FIGURES

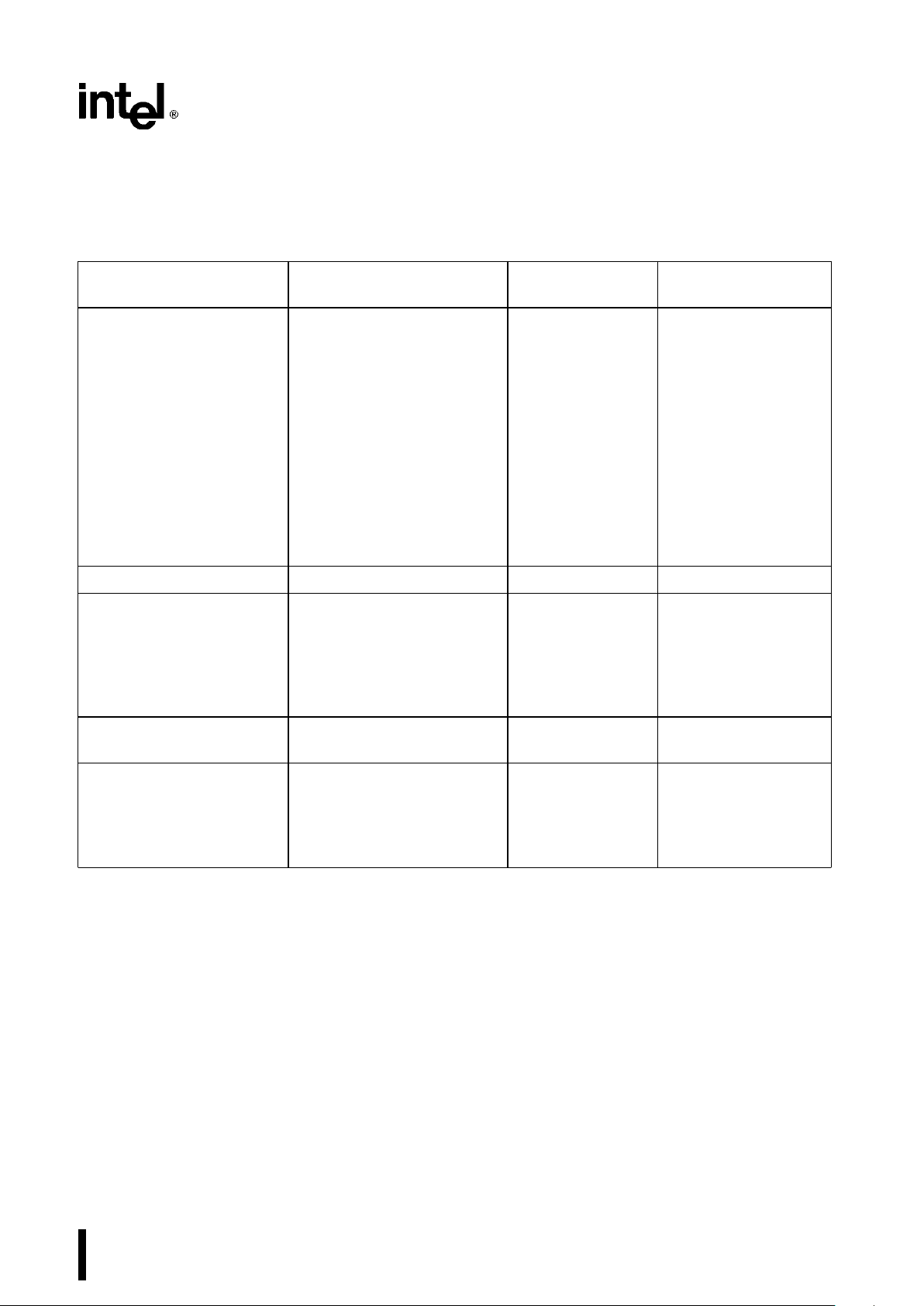

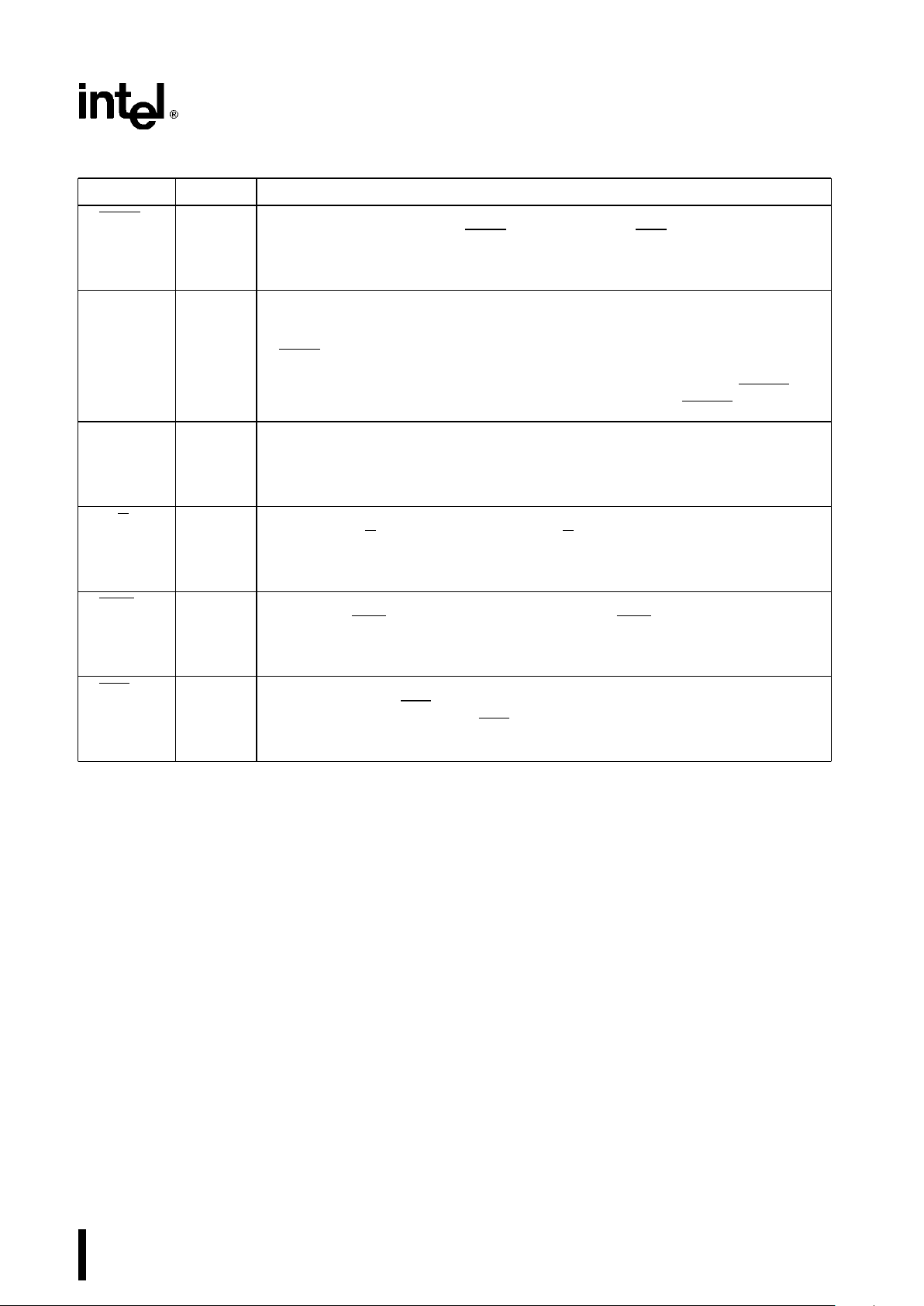

Figure 1 80960CA Block Diagram

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 5

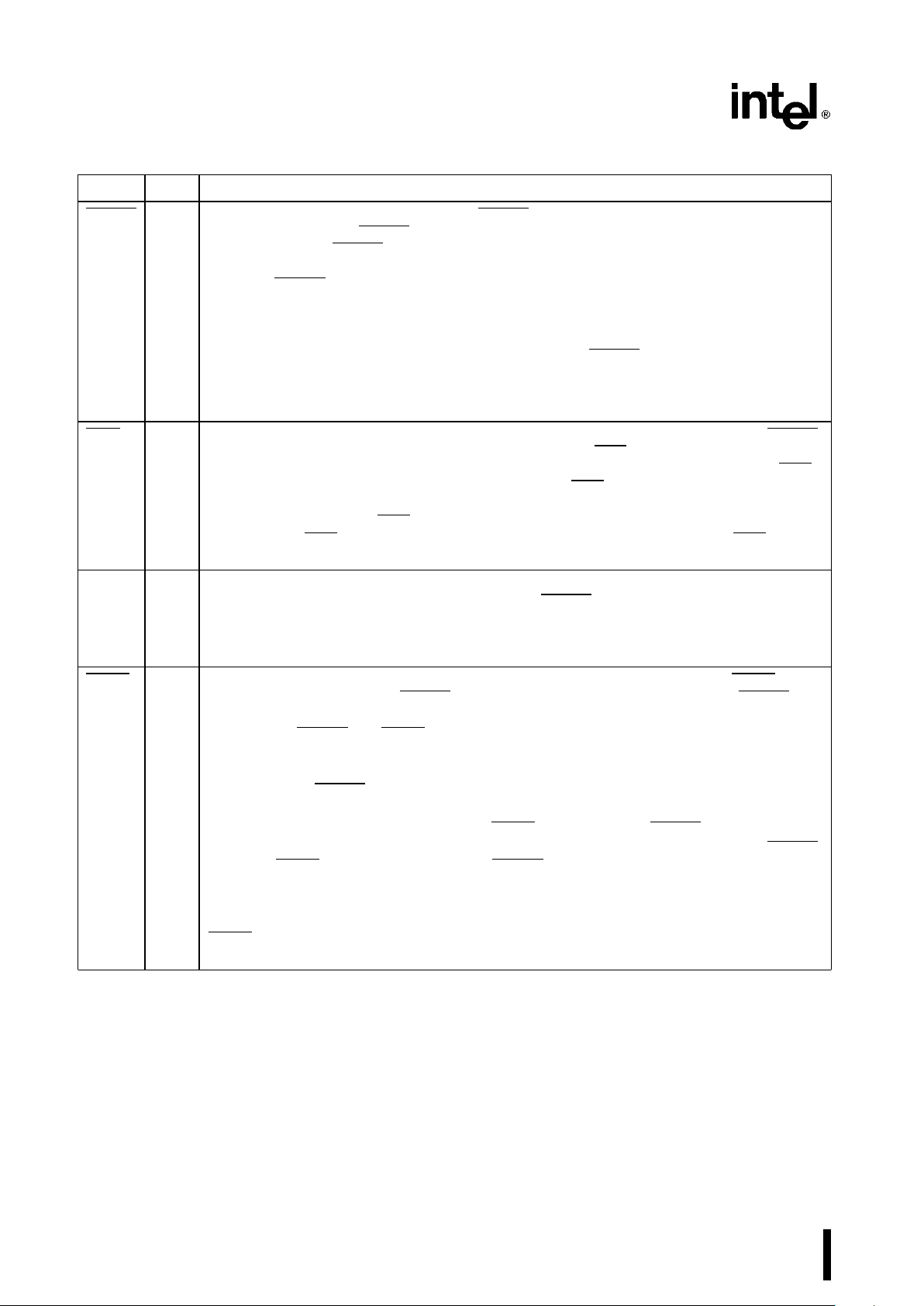

Figure 2 80960CA PGA PinoutÐView from Top (Pins Facing Down) АААААААААААААААААААААААА 17

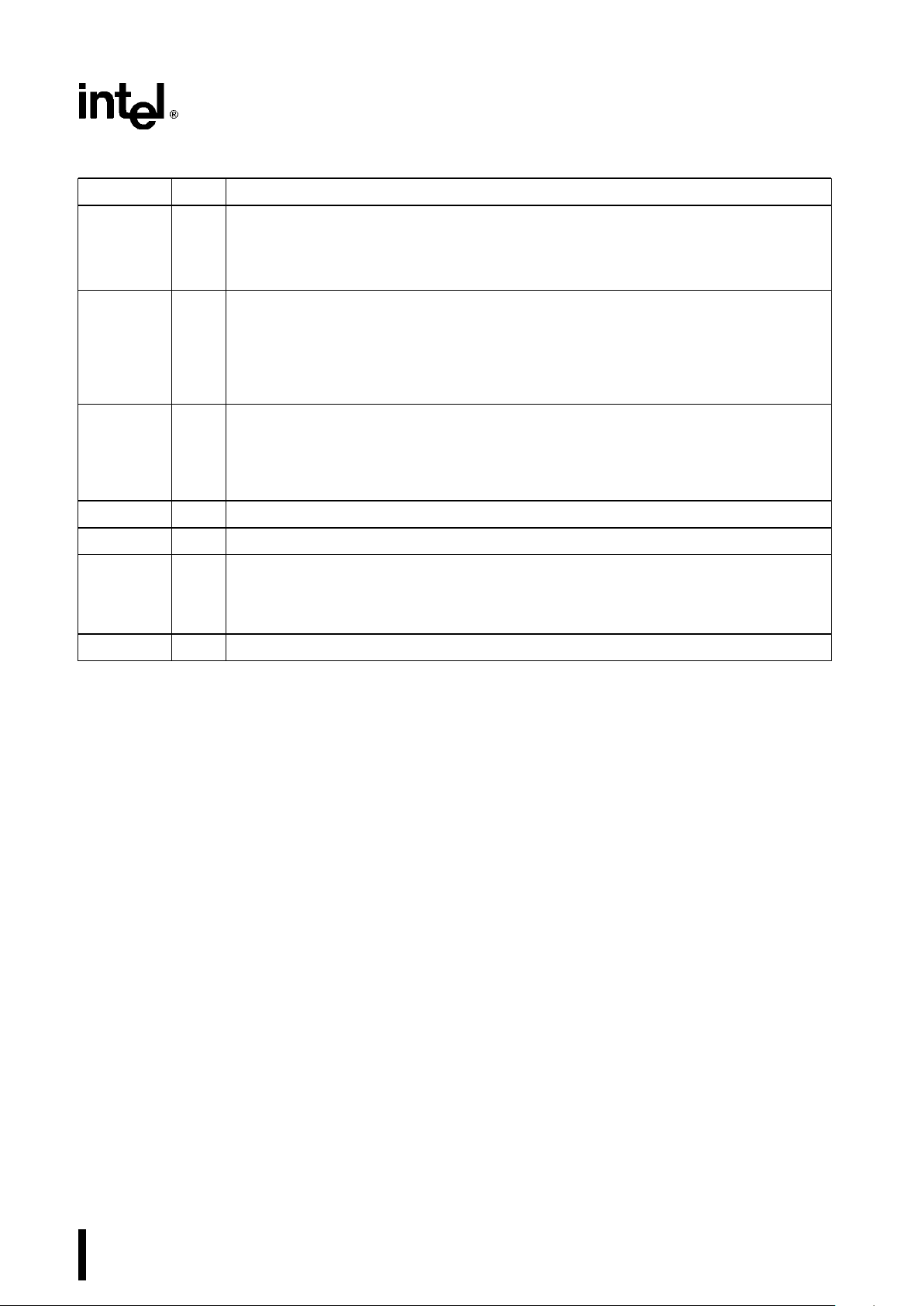

Figure 3 80960CA PGA PinoutÐView from Bottom (Pins Facing Up) АААААААААААААААААААААААА 18

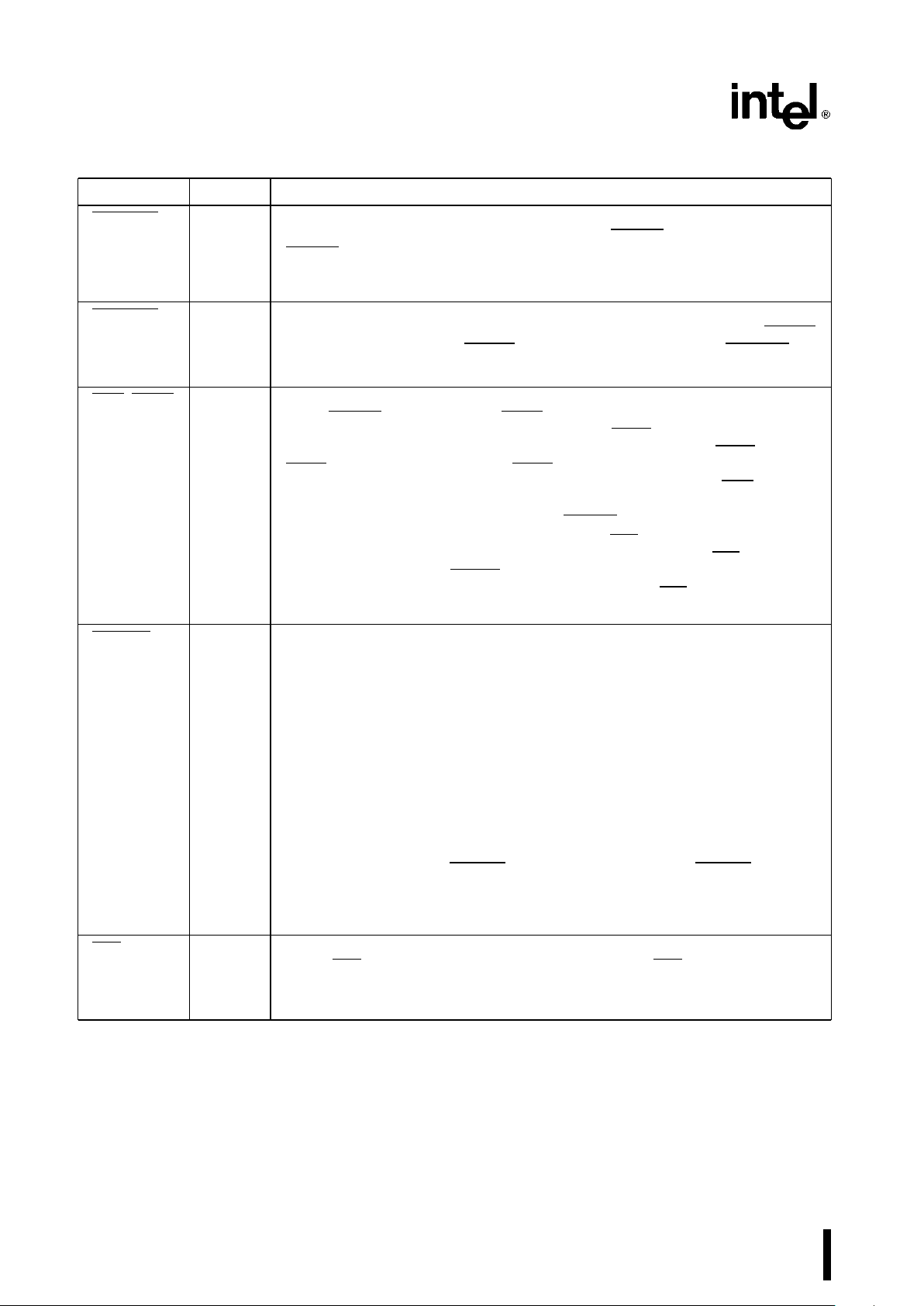

Figure 4 Measuring 80960CA PGA Case Temperature АААААААААААААААААААААААААААААААААААААА 19

Figure 5 Register g0 ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 21

Figure 6 AC Test Load ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 28

Figure 7 Input and Output Clocks Waveform АААААААААААААААААААААААААААААААААААААААААААААААА 28

Figure 8 CLKIN Waveform ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 28

Figure 9 Output Delay and Float Waveform ААААААААААААААААААААААААААААААААААААААААААААААААА 29

Figure 10 Input Setup and Hold Waveform ААААААААААААААААААААААААААААААААААААААААААААААААААА 29

Figure 11 NMI, XINT7:0 Input Setup and Hold Waveform ААААААААААААААААААААААААААААААААААААА 30

Figure 12 Hold Acknowledge Timings ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 30

Figure 13 Bus Backoff (BOFF) Timings АААААААААААААААААААААААААААААААААААААААААААААААААААААА 31

Figure 14 Relative Timings Waveforms АААААААААААААААААААААААААААААААААААААААААААААААААААААА 32

Figure 15 Output Delay or Hold vs Load Capacitance АААААААААААААААААААААААААААААААААААААААА 32

Figure 16 Rise and Fall Time Derating at Highest Operating Temperature

and Minimum V

CC

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 33

Figure 17 ICCvs Frequency and Temperature АААААААААААААААААААААААААААААААААААААААААААААААА 33

Figure 18 Cold Reset Waveform ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 35

Figure 19 Warm Reset Waveform ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 36

Figure 20 Entering the ONCE State АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 37

Figure 21 Clock Synchronization in the 2-x Clock Mode АААААААААААААААААААААААААААААААААААААА 38

Figure 22 Clock Synchronization in the 1-x Clock Mode АААААААААААААААААААААААААААААААААААААА 38

Figure 23 Non-Burst, Non-Pipelined Requests without Wait States ААААААААААААААААААААААААААА 39

Figure 24 Non-Burst, Non-Pipelined Read Request with Wait States АААААААААААААААААААААААААА 40

Figure 25 Non-Burst, Non-Pipelined Write Request with Wait States АААААААААААААААААААААААААА 41

Figure 26 Burst, Non-Pipelined Read Request without Wait States, 32-Bit Bus АААААААААААААААА 42

Figure 27 Burst, Non-Pipelined Read Request with Wait States, 32-Bit Bus ААААААААААААААААААА 43

Figure 28 Burst, Non-Pipelined Write Request without Wait States, 32-Bit Bus АААААААААААААААА 44

Figure 29 Burst, Non-Pipelined Write Request with Wait States, 32-Bit Bus ААААААААААААААААААА 45

Figure 30 Burst, Non-Pipelined Read Request with Wait States, 16-Bit Bus ААААААААААААААААААА 46

Figure 31 Burst, Non-Pipelined Read Request with Wait States, 8-Bit Bus АААААААААААААААААААА 47

Figure 32 Non-Burst, Pipelined Read Request without Wait States, 32-Bit Bus АААААААААААААААА 48

Figure 33 Non-Burst, Pipelined Read Request with Wait States, 32-Bit Bus ААААААААААААААААААА 49

Figure 34 Burst, Pipelined Read Request without Wait States, 32-Bit Bus ААААААААААААААААААААА 50

Figure 35 Burst, Pipelined Read Request with Wait States, 32-Bit Bus АААААААААААААААААААААААА 51

Figure 36 Burst, Pipelined Read Request with Wait States, 16-Bit Bus АААААААААААААААААААААААА 52

Figure 37 Burst, Pipelined Read Request with Wait States, 8-Bit Bus ААААААААААААААААААААААААА 53

3

CONTENTS PAGE

LIST OF FIGURES (Continued)

Figure 38 Using External READY

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 54

Figure 39 Terminating a Burst with BTERM АААААААААААААААААААААААААААААААААААААААААААААААААА 55

Figure 40 BOFF Functional Timing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 56

Figure 41 HOLD Functional Timing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 57

Figure 42 DREQ and DACK Functional Timing ААААААААААААААААААААААААААААААААААААААААААААААА 58

Figure 43 EOP Functional Timing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 58

Figure 44 Terminal Count Functional Timing ААААААААААААААААААААААААААААААААААААААААААААААААА 59

Figure 45 FAIL Functional Timing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 59

Figure 46 A Summary of Aligned and Unaligned Transfers for Little Endian Regions АААААААААА 60

Figure 47 A Summary of Aligned and Unaligned Transfers for Little Endian Regions

(Continued)

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 61

Figure 48 Idle Bus Operation АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 62

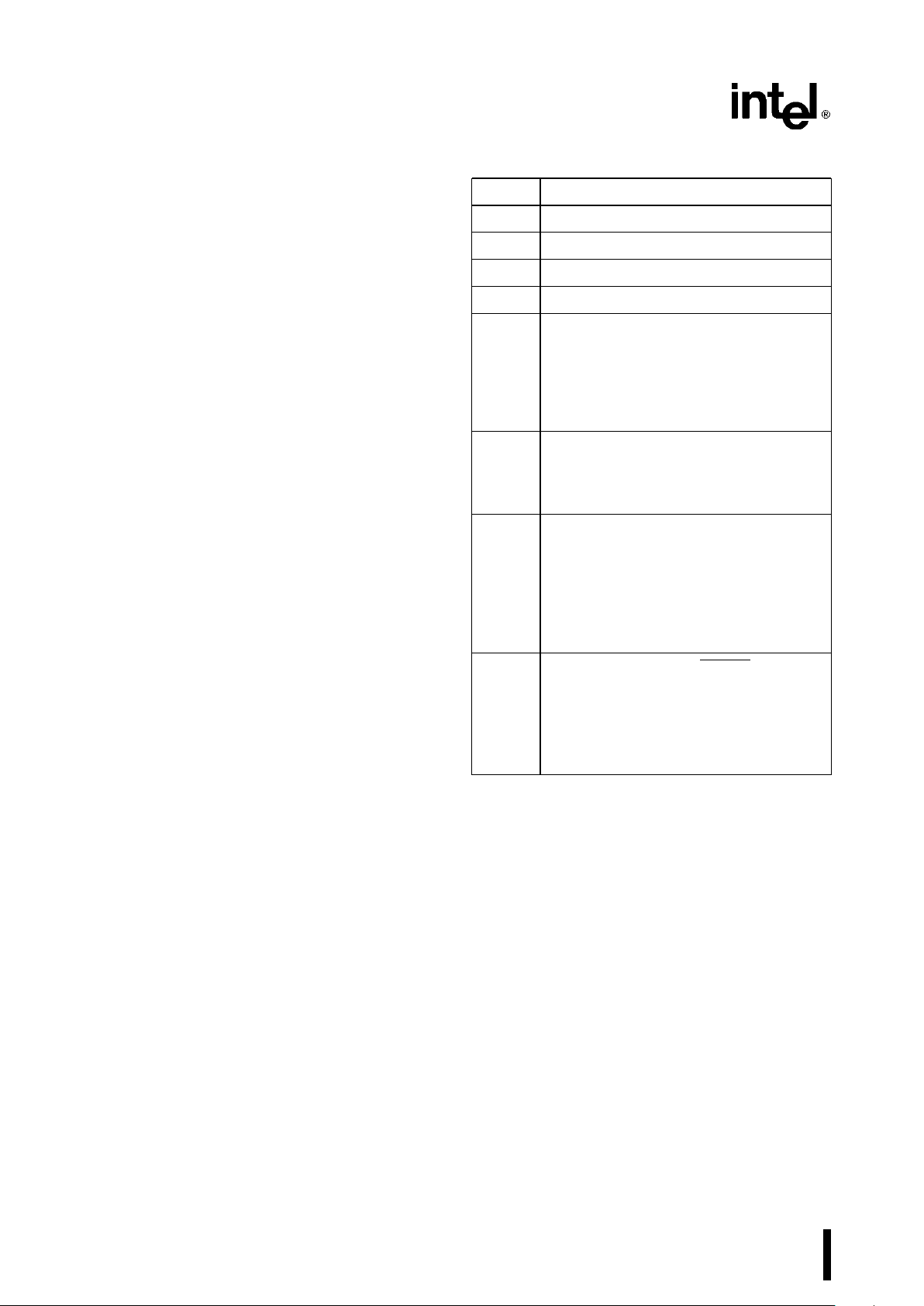

LIST OF TABLES

Table 1 80960CA Instruction Set

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 7

Table 2 Pin Description Nomenclature ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 8

Table 3 80960CA Pin DescriptionÐExternal Bus Signals ААААААААААААААААААААААААААААААААААААА 9

Table 4 80960CA Pin DescriptionÐProcessor Control Signals АААААААААААААААААААААААААААААА 12

Table 5 80960CA Pin DescriptionÐDMA and Interrupt Unit Control Signals ААААААААААААААААА 14

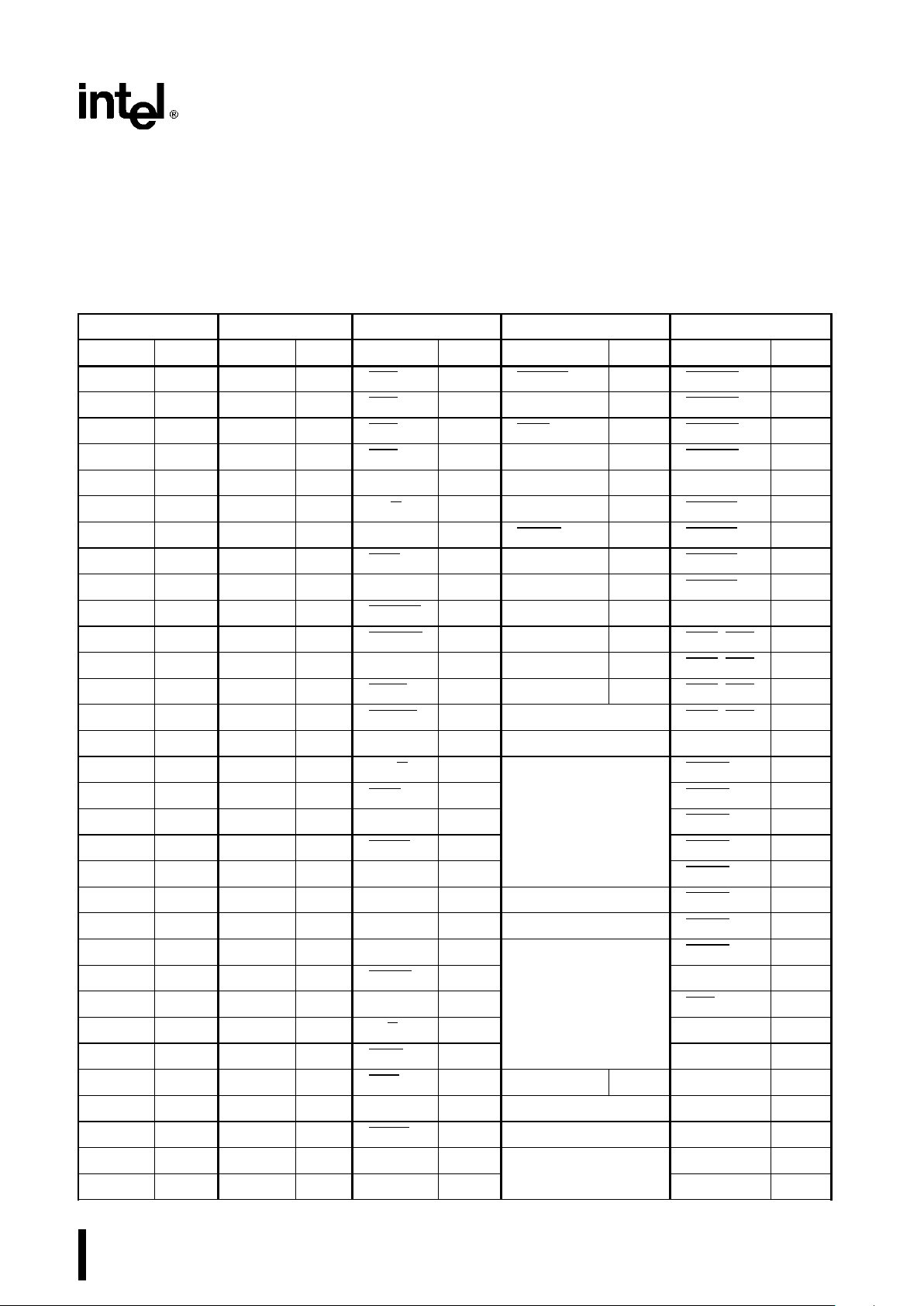

Table 6 80960CA PGA PinoutÐIn Signal Order ААААААААААААААААААААААААААААААААААААААААААААА 15

Table 7 80960CA PGA PinoutÐIn Pin Order АААААААААААААААААААААААААААААААААААААААААААААААА 16

Table 8 Maximum TAat Various Airflows in§C АААААААААААААААААААААААААААААААААААААААААААААА 19

Table 9 80960CA PGA Package Thermal Characteristics ААААААААААААААААААААААААААААААААААА 20

Table 10 Die Stepping Cross Reference ААААААААААААААААААААААААААААААААААААААААААААААААААААА 21

Table 11 Operating Conditions (80960CA-25, -16) ААААААААААААААААААААААААААААААААААААААААААА 22

Table 12 DC Characteristics ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 23

Table 13 80960CA AC Characteristics (25 MHz) ААААААААААААААААААААААААААААААААААААААААААААА 24

Table 14 80960CA AC Characteristics (16 MHz) ААААААААААААААААААААААААААААААААААААААААААААА 26

Table 15 Reset Conditions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 34

Table 16 Hold Acknowledge and Backoff Conditions ААААААААААААААААААААААААААААААААААААААААА 34

4

SPECIAL ENVIRONMENT 80960CA-25, -16

1.0 PURPOSE

This document provides electrical characteristics for

the 25 and 16 MHz versions of the 80960CA. For a

detailed description of any 80960CA functional

topicÐother than parametric performanceÐconsult

the

80960CA Product Overview

(Order No. 270669)

or the

i960ÉCA Microprocessor User’s Manual

(Order No. 270710). To obtain data sheet updates and

errata, please call Intel’s FaxBACK

É

data-on-demand system (1-800-628-2283 or 916-356-3105).

Other information can be obtained from Intel’s technical BBS (916-356-3600).

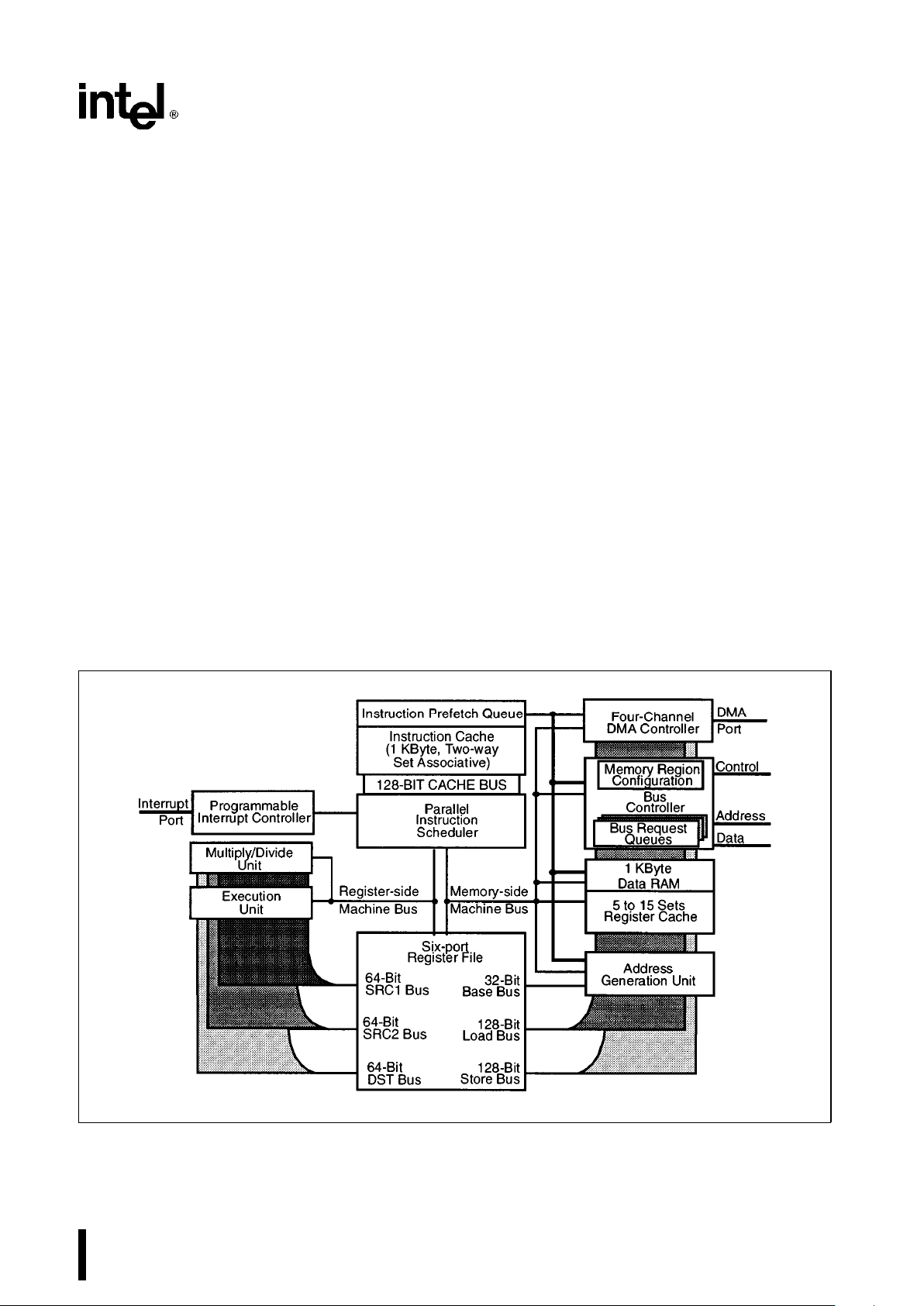

2.0 80960CA OVERVIEW

The 80960CA is the second-generation member of

the 80960 family of embedded processors. The

80960CA is object code compatible with the 32-bit

80960 Core Architecture while including Special

Function Register extensions to control on-chip peripherals and instruction set extensions to shift

64-bit operands and configure on-chip hardware.

Multiple 128-bit internal buses, on-chip instruction

caching and a sophisticated instruction scheduler allow the processor to sustain execution of two instructions every clock and peak at execution of

three instructions per clock.

A 32-bit demultiplexed and pipelined burst bus provides a 132 Mbyte/s bandwidth to a system’s highspeed external memory sub-system. In addition, the

80960CA’s on-chip caching of instructions, procedure context and critical program data substantially

decouple system performance from the wait states

associated with accesses to the system’s slower,

cost sensitive, main memory subsystem.

The 80960CA bus controller integrates full wait state

and bus width control for highest system performance with minimal system design complexity. Unaligned access and Big Endian byte order support

reduces the cost of porting existing applications to

the 80960CA.

The processor also integrates four complete datachaining DMA channels and a high-speed interrupt

controller on-chip. DMA channels perform: singlecycle or two-cycle transfers, data packing and unpacking and data chaining. Block transfersÐin addition to source or destination synchronized transfersÐare provided.

The interrupt controller provides full programmability

of 248 interrupt sources into 32 priority levels with a

typical interrupt task switch (‘‘latency’’) time of

750 ns.

271327–1

Figure 1. 80960CA Block Diagram

5

SPECIAL ENVIRONMENT 80960CA-25, -16

2.1 The C-Series Core

The C-Series core is a very high performance microarchitectural implementation of the 80960 Core Architecture. The C-Series core can sustain execution

of two instructions per clock (50 MIPs at 25 MHz).

To achieve this level of performance, Intel has incorporated state-of-the-art silicon technology and innovative microarchitectural constructs into the implementation of the C-Series core. Factors that contribute to the core’s performance include:

#

Parallel instruction decoding allows issuance of

up to three instructions per clock

#

Single-clock execution of most instructions

#

Parallel instruction decode allows sustained,

simultaneous execution of two single-clock instructions every clock cycle

#

Efficient instruction pipeline minimizes pipeline

break losses

#

Register and resource scoreboarding allow simultaneous multi-clock instruction execution

#

Branch look-ahead and prediction allows many

branches to execute with no pipeline break

#

Local Register Cache integrated on-chip caches

Call/Return context

#

Two-way set associative, 1 Kbyte integrated instruction cache

#

1 Kbyte integrated Data RAM sustains a fourword (128-bit) access every clock cycle

2.2 Pipelined, Burst Bus

A 32-bit high performance bus controller interfaces

the 80960CA to external memory and peripherals.

The Bus Control Unit features a maximum transfer

rate of 100 Mbytes per second (at 25 MHz). Internally programmable wait states and 16 separately configurable memory regions allow the processor to interface with a variety of memory subsystems with a

minimum of system complexity and a maximum of

performance. The Bus Controller’s main features include:

#

Demultiplexed, Burst Bus to exploit most efficient

DRAM access modes

#

Address Pipelining to reduce memory cost while

maintaining performance

#

32-, 16- and 8-bit modes for I/O interfacing ease

#

Full internal wait state generation to reduce system cost

#

Little and Big Endian support to ease application

development

#

Unaligned access support for code portability

#

Three-deep request queue to decouple the bus

from the core

2.3 Flexible DMA Controller

A four-channel DMA controller provides high speed

DMA control for data transfers involving peripherals

and memory. The DMA provides advanced features

such as data chaining, byte assembly and disassembly and a high performance fly-by mode capable of

transfer speeds of up to 45 Mbytes per second at

25 MHz. The DMA controller features a performance

and flexibility which is only possible by integrating

the DMA controller and the 80960CA core.

2.4 Priority interrupt Controller

A programmable-priority interrupt controller manages up to 248 external sources through the 8-bit

external interrupt port. The interrupt Unit also handles the four internal sources from the DMA controller and a single non-maskable interrupt input. The

8-bit interrupt port can also be configured to provide

individual interrupt sources that are level or edge

triggered.

Interrupts in the 80960CA are prioritized and signaled within 270 ns of the request. If the interrupt is

of higher priority than the processor priority, the context switch to the interrupt routine typically is complete in another 480 ns. The interrupt unit provides

the mechanism for the low latency and high throughput interrupt service which is essential for embedded

applications.

6

SPECIAL ENVIRONMENT 80960CA-25, -16

2.5 Instruction Set Summary

Table 1 summarizes the 80960CA instruction set by logical groupings. See the

i960ÉCA Microprocessor

User’s Manual

for a complete description of the instruction set.

Table 1. 80960CA Instruction Set

Data

Arithmetic Logical

Bit and Bit Field

Movement and Byte

Load Add And Set Bit

Store Subtract Not And Clear Bit

Move Multiply And Not Not Bit

Load Address Divide Or Alter Bit

Remainder Exclusive Or Scan For Bit

Modulo Not Or Span Over Bit

Shift Or Not Extract

*Extended Shift Nor Modify

Extended Multiply Exclusive Nor Scan Byte for Equal

Extended Divide Not

Add with Carry Nand

Subtract with Carry

Rotate

Comparison Branch Call/Return Fault

Compare Unconditional Branch Call Conditional Fault

Conditional Compare Conditional Branch Call Extended Synchronize Faults

Compare and Increment Compare and Branch Call System

Compare and Decrement Return

Test Condition Code Branch and Link

Check Bit

Debug

Processor

Atomic

Management

Modify Trace Controls Flush Local Registers Atomic Add

Mark Modify Arithmetic Controls Atomic Modify

Force Mark Modify Process Controls

*System Control

*DMA Control

NOTES:

Instructions marked by (*) are 80960CA extensions to the 80960 instruction set

7

SPECIAL ENVIRONMENT 80960CA-25, -16

3.0 PACKAGE INFORMATION

3.1 Package Introduction

This section describes the pins, pinouts and thermal

characteristics for the 80960CA in the 168-pin Ceramic Pin Grid Array (PGA) package. For complete

package specifications and information, see the

Packaging

Handbook (Order No. 240800).

3.2 Pin Descriptions

The 80960CA pins are described in this section. Table 2 presents the legend for interpreting the pin descriptions in the following tables. Pins associated

with the 32-bit demultiplexed processor bus are described in Table 3. Pins associated with basic processor configuration and control are described in Table 4. Pins associated with the 80960CA DMA Controller and Interrupt Unit are described in Table 5.

All pins float while the processor is in the ONCE

mode.

Table 2. Pin Description Nomenclature

Symbol Description

I Input only pin

O Output only pin

I/O Pin can be either an input or output

Ð Pins ‘‘must be’’ connected as described

S(...) Synchronous. Inputs must meet setup

and hold times relative to PCLK2:1 for

proper operation. All outputs are

synchronous to PCLK2:1.

S(E) Edge sensitive input

S(L) Level sensitive input

A(...) Asynchronous. Inputs may be

asynchronous to PCLK2:1.

A(E) Edge sensitive input

A(L) Level sensitive input

H(...) While the processor’s bus is in the Hold

Acknowledge or Bus Backoff state, the

pin:

H(1) is driven to V

CC

H(0) is driven to V

SS

H(Z) floats

H(Q) continues to be a valid input

R(...) While the processor’s RESET pin is low,

the pin:

R(1) is driven to V

CC

R(0) is driven to V

SS

R(Z) floats

R(Q) continues to be a valid output

8

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 3. 80960CA Pin DescriptionÐExternal Bus Signals

Name Type Description

A31:2 O ADDRESS BUS carries the physical address’ upper 30 bits. A31 is the most

significant address bit; A2 is the least significant. During a bus access, A31:2

S

identify all external addresses to word (4-byte) boundaries. The byte enable signals

H(Z)

indicate the selected byte in each word. During burst accesses, A3:2 increment to

R(Z)

indicate successive data cycles.

D31:0 I/O DATA BUS carries 32-, 16- or 8-bit data quantities depending on bus width

configuration. The least significant bit of the data is carried on D0 and the most

S(L)

significant on D31. When the bus is configured for 8-bit data, the lower 8 data lines,

H(Z)

D7:0 are used. For 16-bit data bus widths, D15:0 are used. For 32 bit bus widths the

R(Z)

full data bus is used.

BE3:0 O BYTE ENABLES select which of the four bytes addressed by A31:2 are active

during an access to a memory region configured for a 32-bit data-bus width. BE3

S

applies to D31:24; BE2

applies to D23:16; BE1 applies to D15:8; BE0 applies to

H(Z)

D7:0.

R(1)

32-bit bus: BE3

ÐByte Enable 3 Ðenable D31:24

BE2

ÐByte Enable 2 Ðenable D23:16

BE1

ÐByte Enable 1 Ðenable D15:8

BE0

ÐByte Enable 0 Ðenable D7:0

For accesses to a memory region configured for a 16-bit data-bus width, the

processor uses the BE3

, BE1 and BE0 pins as BHE, A1 and BLE respectively.

16-bit bus: BE3 ÐByte High Enable (BHE) Ðenable D15:8

BE2

ÐNot used (driven high or low)

BE1

ÐAddress Bit 1 (A1)

BE0

ÐByte Low Enable (BLE) Ðenable D7:0

For accesses to a memory region configured for an 8-bit data-bus width, the

processor uses the BE1

and BE0 pins as A1 and A0 respectively.

8-bit bus: BE3

ÐNot used (driven high or low)

BE2 ÐNot used (driven high or low)

BE1

ÐAddress Bit 1 (A1)

BE0

ÐAddress Bit 0 (A0)

W/R O WRITE/READ is asserted for read requests and deasserted for write requests. The

W/R

signal changes in the same clock cycle as ADS. It remains valid for the entire

S

access in non-pipelined regions. In pipelined regions, W/R

is not guaranteed to be

H(Z)

valid in the last cycle of a read access.

R(0)

ADS O ADDRESS STROBE indicates a valid address and the start of a new bus access.

ADS

is asserted for the first clock of a bus access.

S

H(Z)

R(1)

9

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 3. 80960CA Pin DescriptionÐExternal Bus Signals (Continued)

Name Type Description

READY I READY is an input which signals the termination of a data transfer. READY is

used to indicate that read data on the bus is valid or that a write-data transfer

S(L)

has completed. The READY

signal works in conjunction with the internally

H(Z)

programmed wait-state generator. If READY

is enabled in a region, the pin is

R(Z)

sampled after the programmed number of wait-states has expired. If the

READY

pin is deasserted, wait states continue to be inserted until READY

becomes asserted. This is true for the N

RAD,NRDD,NWAD

and N

WDD

wait

states. The N

XDA

wait states cannot be extended.

BTERM I BURST TERMINATE is an input which breaks up a burst access and causes

another address cycle to occur. The BTERM

signal works in conjunction with

S(L)

the internally programmed wait-state generator. If READY

and BTERM are

H(Z)

enabled in a region, the BTERM

pin is sampled after the programmed number

R(Z)

of wait states has expired. When BTERM

is asserted, a new ADS signal is

generated and the access is completed. The READY input is ignored when

BTERM

is asserted. BTERM must be externally synchronized to satisfy

BTERM

setup and hold times.

WAIT O WAIT indicates internal wait state generator status. WAIT is asserted when

wait states are being caused by the internal wait state generator and not by

S

the READY

or BTERM inputs. WAIT can be used to derive a write-data

H(Z)

strobe. WAIT

can also be thought of as a READY output that the processor

R(1)

provides when it is inserting wait states.

BLAST O BURST LAST indicates the last transfer in a bus access. BLAST is asserted

in the last data transfer of burst and non-burst accesses after the wait state

S

counter reaches zero. BLAST

remains asserted until the clock following the

H(Z)

last cycle of the last data transfer of a bus access. If the READY

or BTERM

R(0)

input is used to extend wait states, the BLAST

signal remains asserted until

READY

or BTERM terminates the access.

DT/R O DATA TRANSMIT/RECEIVE indicates direction for data transceivers. DT/R

is used in conjunction with DEN to provide control for data transceivers

S

attached to the external bus. When DT/R

is asserted, the signal indicates that

H(Z)

the processor receives data. Conversely, when deasserted, the processor

R(0)

sends data. DT/R

changes only while DEN is high.

DEN O DATA ENABLE indicates data cycles in a bus request. DEN is asserted at the

start of the bus request first data cycle and is deasserted at the end of the last

S

data cycle. DEN

is used in conjunction with DT/R to provide control for data

H(Z)

transceivers attached to the external bus. DEN remains asserted for

R(1)

sequential reads from pipelined memory regions. DEN

is deasserted when

DT/R

changes.

LOCK O BUS LOCK indicates that an atomic read-modify-write operation is in

progress. LOCK

may be used to prevent external agents from accessing

S

memory which is currently involved in an atomic operation. LOCK

is asserted

H(Z)

in the first clock of an atomic operation and deasserted in the clock cycle

R(1)

following the last bus access for the atomic operation. To allow the most

flexibility for memory system enforcement of locked accesses, the processor

acknowledges a bus hold request when LOCK

is asserted. The processor

performs DMA transfers while LOCK

is active.

HOLD I HOLD REQUEST signals that an external agent requests access to the

external bus. The processor asserts HOLDA after completing the current bus

S(L)

request. HOLD, HOLDA and BREQ are used together to arbitrate access to

H(Z)

the processor’s external bus by external bus agents.

R(Z)

10

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 3. 80960CA Pin DescriptionÐExternal Bus Signals (Continued)

Name Type Description

BOFF I BUS BACKOFF, when asserted, suspends the current access and causes

the bus pins to float. When BOFF

is deasserted, the ADS signal is asserted

S(L)

on the next clock cycle and the access is resumed.

H(Z)

R(Z)

HOLDA O HOLD ACKNOWLEDGE indicates to a bus requestor that the processor has

relinquished control of the external bus. When HOLDA is asserted, the

S

external address bus, data bus and bus control signals are floated. HOLD,

H(1)

BOFF

, HOLDA and BREQ are used together to arbitrate access to the

R(Q)

processor’s external bus by external bus agents. Since the processor grants

HOLD requests and enters the Hold Acknowledge state even while RESET

is

asserted, the state of the HOLDA pin is independent of the RESET

pin.

BREQ O BUS REQUEST is asserted when the bus controller has a request pending.

BREQ can be used by external bus arbitration logic in conjunction with HOLD

S

and HOLDA to determine when to return mastership of the external bus to the

H(Q)

processor.

R(0)

D/C O DATA OR CODE is asserted for a data request and deasserted for instruction

requests. D/C

has the same timing as W/R.

S

H(Z)

R(Z)

DMA O DMA ACCESS indicates whether the bus request was initiated by the DMA

controller. DMA

is asserted for any DMA request. DMA is deasserted for all

S

other requests.

H(Z)

R(Z)

SUP O SUPERVISOR ACCESS indicates whether the bus request is issued while in

supervisor mode. SUP

is asserted when the request has supervisor privileges

S

and is deasserted otherwise. SUP can be used to isolate supervisor code and

H(Z)

data structures from non-supervisor requests.

R(Z)

11

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 4. 80960CA Pin DescriptionÐProcessor Control Signals

Name Type Description

RESET I RESET causes the chip to reset. When RESET is asserted, all external signals return to

the reset state. When RESET

is deasserted, initialization begins. When the 2-x clock

A(L)

mode is selected, RESET

must remain asserted for 32 CLKIN cycles before being

H(Z)

deasserted to guarantee correct processor initialization. When the 1-x clock mode is

R(Z)

selected, RESET

must remain asserted for 10,000 CLKIN cycles before being deasserted

to guarantee correct processor initialization. The CLKMODE pin selects 1-x or 2-x input

clock division of the CLKIN pin.

The processor’s Hold Acknowledge bus state functions while the chip is reset. If the

processor’s bus is in the Hold Acknowledge state when RESET

is asserted, the processor

will internally reset, but maintains the Hold Acknowledge state on external pins until the

Hold request is removed. If a Hold request is made while the processor is in the reset

state, the processor bus will grant HOLDA and enter the Hold Acknowledge state.

FAIL O FAIL indicates failure of the processor’s self-test performed at initialization. When RESET

is deasserted and the processor begins initialization, the FAIL pin is asserted. An internal

S

self-test is performed as part of the initialization process. If this self-test passes, the FAIL

H(Q)

pin is deasserted; otherwise it remains asserted. The FAIL

pin is reasserted while the

R(0)

processor performs an external bus self-confidence test. If this self-test passes, the

processor deasserts the FAIL

pin and branches to the user’s initialization routine;

otherwise the FAIL

pin remains asserted. Internal self-test and the use of the FAIL pin can

be disabled with the STEST pin.

STEST I SELF TEST causes the processor’s internal self-test feature to be enabled or disabled at

initialization. STEST is read on the rising edge of RESET

. When asserted, the processor’s

S(L)

internal self-test and external bus confidence tests are performed during processor

H(Z)

initialization. When deasserted, only the bus confidence tests are performed during

R(Z)

initialization.

ONCE I ON CIRCUIT EMULATION, when asserted, causes all outputs to be floated. ONCE is

continuously sampled while RESET

is low and is latched on the rising edge of RESET.To

A(L)

place the processor in the ONCE state:

H(Z)

(1) assert RESET and ONCE (order does not matter)

R(Z)

(2) wait for at least 16 CLKIN periods in 2-x modeÐor 10,000 CLKIN periods in 1-x

modeÐafter V

CC

and CLKIN are within operating specifications

(3) deassert RESET

(4) wait at least 32 CLKIN periods

(The processor will now be latched in the ONCE

state as long as RESET is high.)

To exit the ONCE state. bring V

CC

and CLKIN to operating conditions, then assert RESET

and bring ONCE high prior to deasserting RESET.

CLKIN must operate within the specified operating conditions of the processor until Step 4

above has been completed. CLKIN may then be changed to DC to achieve the lowest

possible ONCE mode leakage current.

ONCE

can be used by emulator products or for board testers to effectively make an

installed processor transparent in the board.

12

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 4. 80960CA Pin DescriptionÐProcessor Control Signals (Continued)

Name Type Description

CLKIN I CLOCK INPUT is an input for the external clock needed to run the processor. The

external clock is internally divided as prescribed by the CLKMODE pin to produce

A(E)

PCLK2:1.

H(Z)

R(Z)

CLKMODE I CLOCK MODE selects the division factor applied to the external clock input (CLKIN).

When CLKMODE is high, CLKIN is divided by one to create PCLK2:1 and the

A(L)

processor’s internal clock. When CLKMODE is low, CLKIN is divided by two to create

H(Z)

PCLK2:1 and the processor’s internal clock. CLKMODE should be tied high or low in a

R(Z)

system as the clock mode is not latched by the processor. If left unconnected, the

processor will internally pull the CLKMODE pin low, enabling the 2-x clock mode.

PCLK2:1 O PROCESSOR OUTPUT CLOCKS provide a timing reference for all processor inputs

and outputs. All input and output timings are specified in relation to PCLK2 and

S

PCLK1. PCLK2 and PCLK1 are identical signals. Two output pins are provided to allow

H(Q)

flexibility in the system’s allocation of capacitive loading on the clock. PCLK2:1 may

R(Q)

also be connected at the processor to form a single clock signal.

V

SS

Ð GROUND connections must be connected externally to a VSSboard plane.

V

CC

Ð POWER connections must be connected externally to a VCCboard pane.

V

CCPLL

Ð V

CCPLL

is a separate VCCsupply pin for the phase lock loop used in 1-x clock mode.

Connecting a simple lowpass filter to V

CCPLL

may help reduce clock jitter (TCP)in

noisy environments. Otherwise, V

CCPLL

should be connected to VCC. This pin is

implemented starting with the D-stepping. See Table 13 for die stepping information.

NC Ð NO CONNECT pins must not be connected in a system.

13

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 5. 80960CA Pin DescriptionÐDMA and Interrupt Unit Control Signals

Name Type Description

DREQ3:0 I DMA REQUEST causes a DMA transfer to be requested. Each of the four

signals requests a transfer on a single channel. DREQ0

requests channel 0,

A(L)

DREQ1

requests channel 1, etc. When two or more channels are requested

H(Z)

simultaneously, the channel with the highest priority is serviced first. The

R(Z)

channel priority mode is programmable.

DACK3:0 O DMA ACKNOWLEDGE indicates that a DMA transfer is being executed.

Each of the four signals acknowledges a transfer for a single channel. DACK0

S

acknowledges channel 0, DACK1 acknowledges channel 1, etc. DACK3:0 are

H(1)

asserted when the requesting device of a DMA is accessed.

R(1)

EOP/TC3:0 I/O END OF PROCESS/TERMINAL COUNT can be programmed as either an

input (EOP3:0

) or as an output (TC3:0), but not both. Each pin is individually

A(L)

programmable. When programmed as an input, EOPx

causes the termination

H(Z/Q)

of a current DMA transfer for the channel corresponding to the EOPx pin.

R(Z)

EOP0

corresponds to channel 0, EOP1 corresponds to channel 1, etc. When

a channel is configured for source

and

destination chaining, the EOP pin for

that channel causes termination of only the current buffer transferred and

causes the next buffer to be transferred. EOP3:0

are asynchronous inputs.

When programmed as an output, the channel’s TCx

pin indicates that the

channel byte count has reached 0 and a DMA has terminated. TCx

is driven

with the same timing as DACKx

during the last DMA transfer for a buffer. If the

last bus request is executed as multiple bus accesses, TCx will stay asserted

for the entire bus request.

XINT7:0 I EXTERNAL INTERRUPT PINS cause interrupts to be requested. These pins

can be configured in three modes:

A(E/L)

Dedicated Mode: each pin is a dedicated external interrupt source.

H(Z)

Dedicated inputs can be individually programmed to

R(Z)

be level (low) or edge (falling) activated.

Expanded Mode: the eight pins act together as an 8-bit vectored

interrupt source. The interrupt pins in this mode are

level activated. Since the interrupt pins are active low,

the vector number requested is the one’s

complement of the positive logic value place on the

port. This eliminates glue logic to interface to

combinational priority encoders which output

negative logic.

Mixed Mode: XINT7:5 are dedicated sources and XINT4:0 act as

the five most significant bits of an expanded mode

vector. The least significant bits are set to 010

internally.

NMI I NON-MASKABLE INTERRUPT causes a non-maskable interrupt event to

occur. NMI

is the highest priority interrupt recognized. NMI is an edge (falling)

A(E)

activated source.

H(Z)

R(Z)

14

SPECIAL ENVIRONMENT 80960CA-25, -16

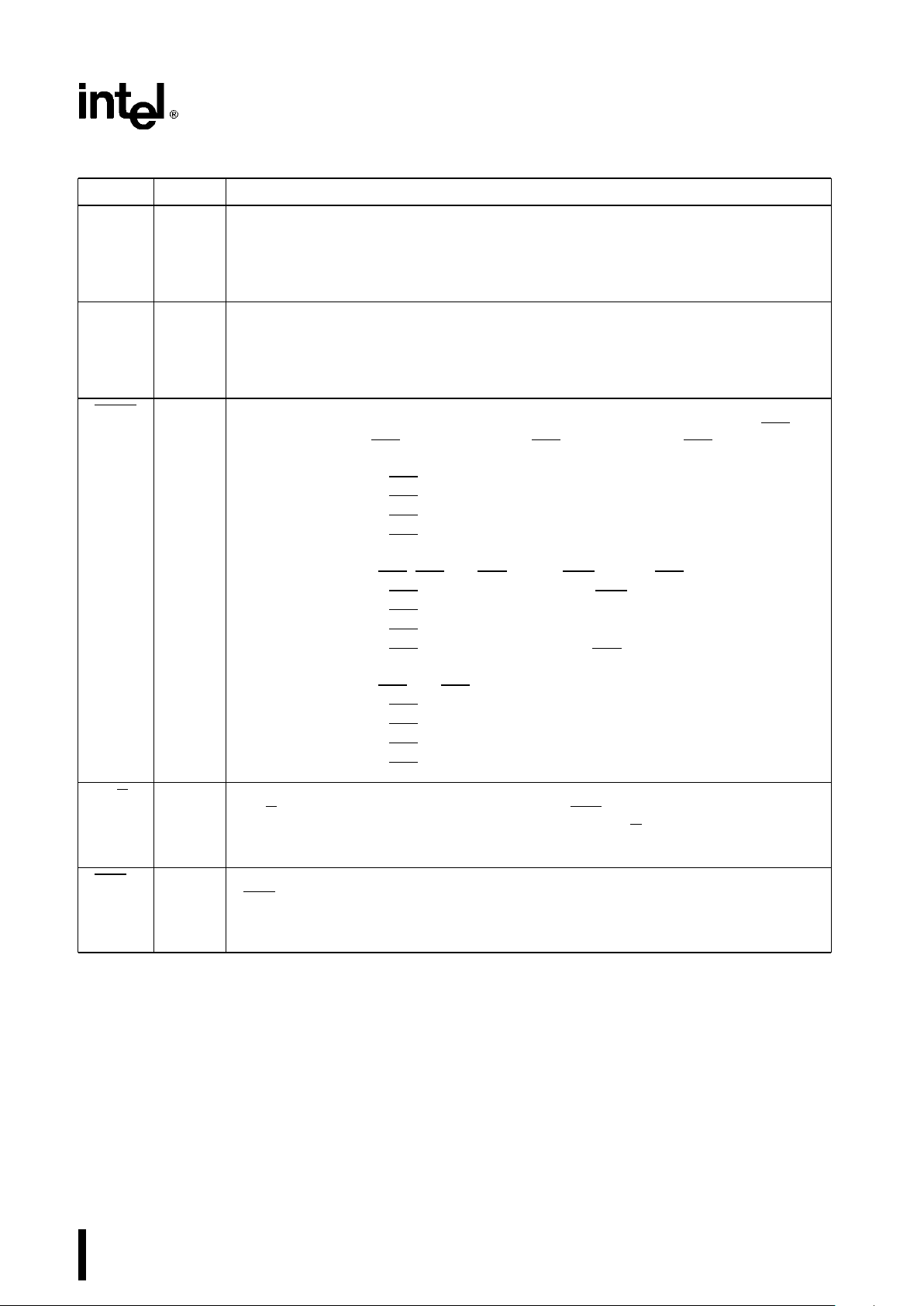

3.3 80960CA Mechanical Data

3.3.1 80960CA PGA Pinout

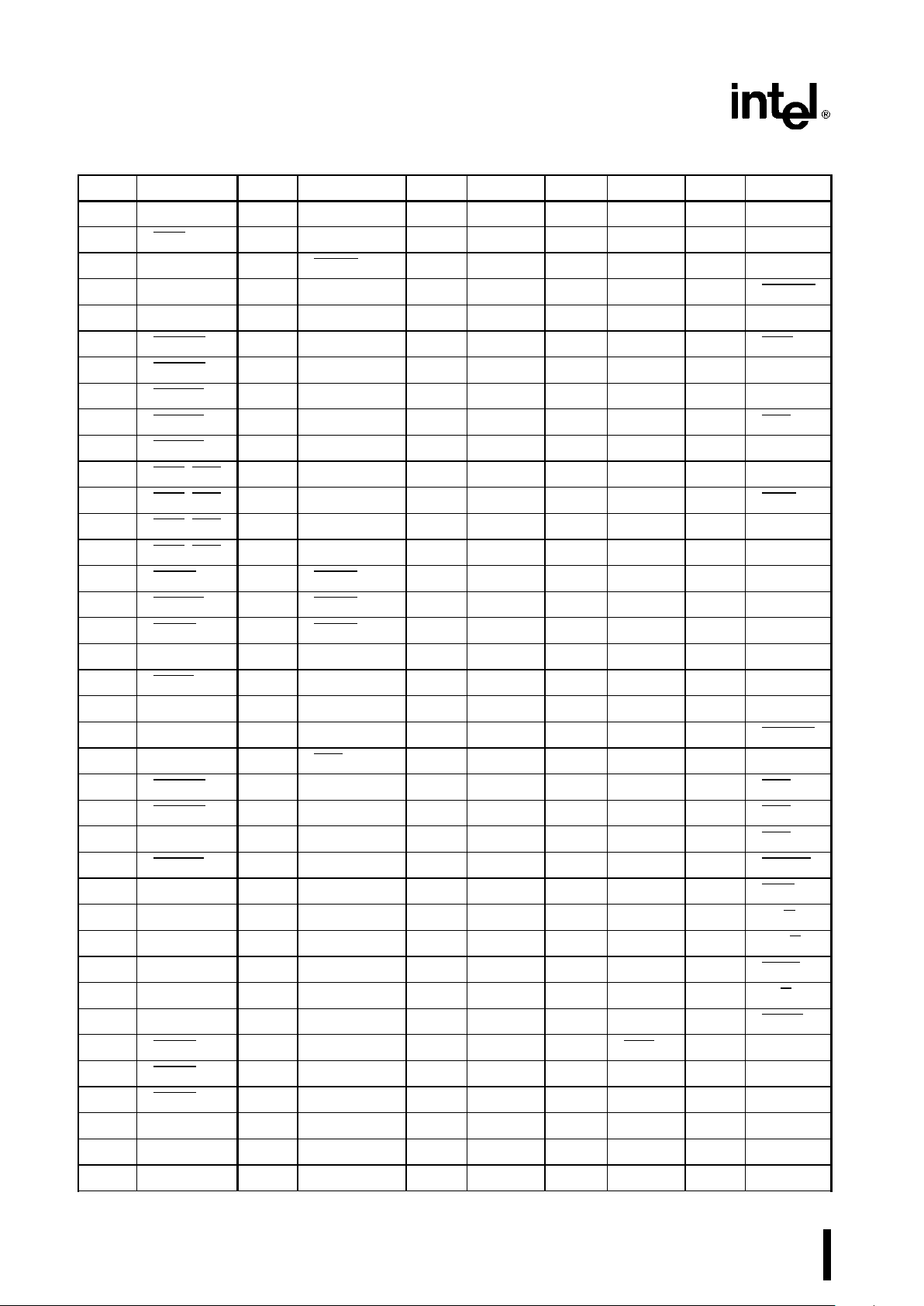

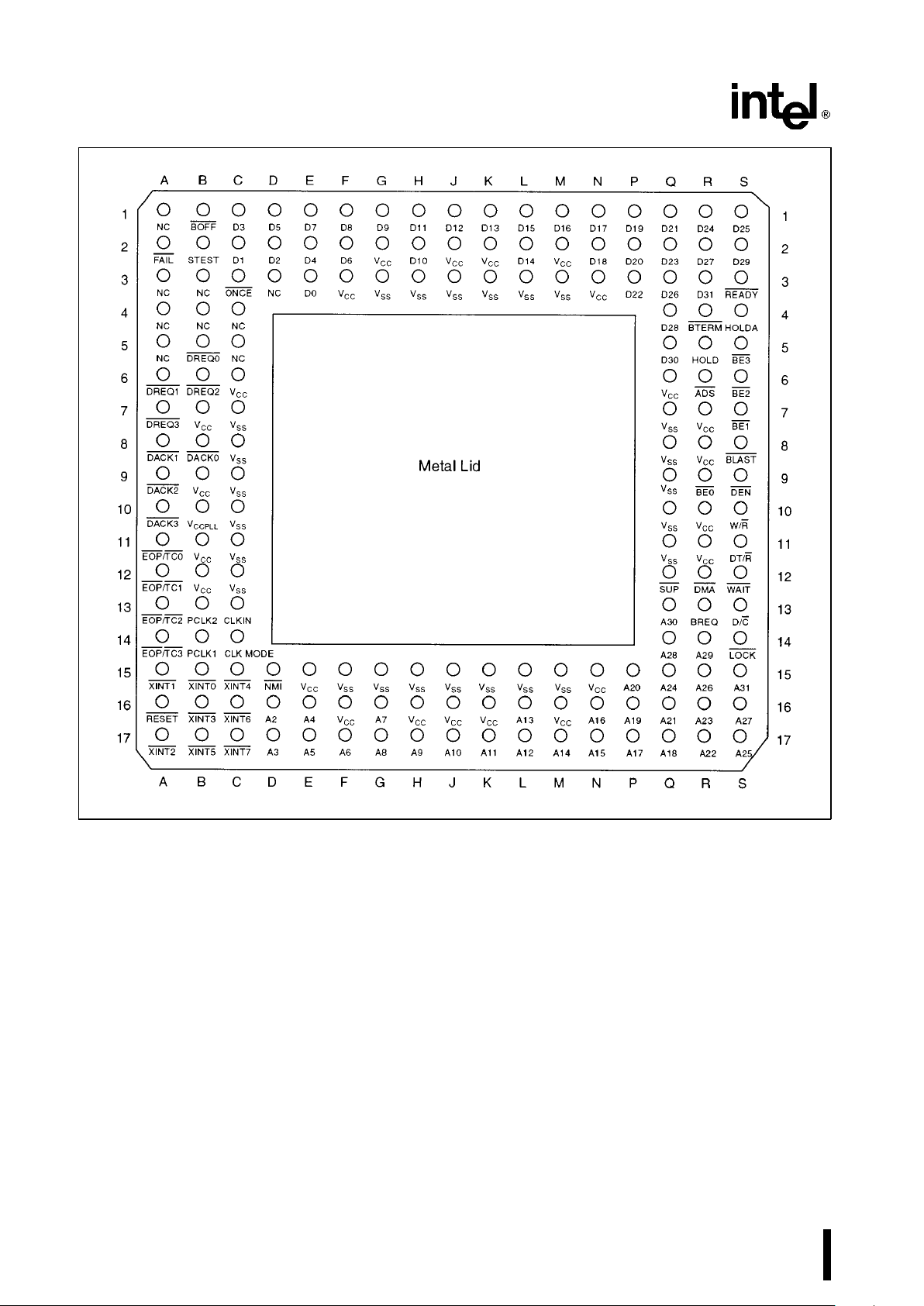

Tables 6 and 7 list the 80960CA pin names with

package location. Figure 2 depicts the complete

80960CA PGA pinout as viewed from the top side of

the component (i.e., pins facing down). Figure 3

shows the complete 80960CA PGA pinout as

viewed from the pin-side of the package (i.e., pins

facing up). See Section 4.0, ELECTRICAL SPECI-

FICATIONS for specifications and recommended

connections.

Table 6. 80960CA PGA PinoutÐIn Signal Order

Address Bus Data Bus Bus Control Processor Control I/O

Signal Pin Signal Pin Signal Pin Signal Pin Signal Pin

A31 S15 D31 R3 BE3 S5 RESET A16 DREQ3 A7

A30 Q13 D30 Q5 BE2 S6 DREQ2 B6

A29 R14 D29 S2 BE1 S7 FAIL A2 DREQ1 A6

A28 Q14 D28 Q4 BE0 R9 DREQ0 B5

A27 S16 D27 R2 STEST B2

A26 R15 D26 Q3 W/R S10 DACK3 A10

A25 S17 D25 S1 ONCE C3 DACK2 A9

A24 Q15 D24 R1 ADS R6 DACK1 A8

A23 R16 D23 Q2 CLKIN C13 DACK0 B8

A22 R17 D22 P3 READY S3 CLKMODE C14

A21 Q16 D21 Q1 BTERM R4 PLCK1 B14 EOP/TC3 A14

A20 P15 D20 P2 PLCK2 B13 EOP/TC2 A13

A19 P16 D19 P1 WAIT S12 EOP/TC1 A12

A18 Q17 D18 N2 BLAST S8 V

SS

EOP/TC0 A11

A17 P17 D17 N1

Location

A16 N16 D16 M1 DT/R S11

Q8, Q9, Q10, Q11

L15, M3, M15, Q7,

J15, K3, K15, L3,

G15, H3, H15, J3,

C11, C12, F15, G3,

C7, C8, C9, C10,

XINT7

C17

A15 N17 D15 L1 DEN S9 XINT6 C16

A14 M17 D14 L2 XINT5 B17

A13 L16 D13 K1 LOCK S14 XINT4 C15

A12 L17 D12 J1 XINT3 B16

A11 K17 D11 H1 V

CC

XINT2 A17

A10 J17 D10 H2 HOLD R5

Location

XINT1 A15

A9 H17 D9 G1 HOLDA S4

R8, R10, R11

N3, N15, Q6, R7,

K2, K16, M2, M16,

G2, H16, J2, J16,

C6, E15, F3, F16,

B7, B9, B11, B12,

XINT0

B15

A8 G17 D8 F1 BREQ R13

A7 G16 D7 E1 NMI D15

A6 F17 D6 F2 D/C S13

A5 E17 D5 D1 DMA R12

A4 E16 D4 E2 SUP Q12 V

CCPLL

B10

A3 D17 D3 C1 No Connect

A2 D16 D2 D2 BOFF B1

Location

D1 C2

B4, C4, C5, D3

A1, A3, A4, A5, B3,

D0 E3

15

SPECIAL ENVIRONMENT 80960CA-25, -16

Table 7. 80960CA PGA PinoutÐIn Pin Order

Pin Signal Pin Signal Pin Signal Pin Signal Pin Signal

A1 NC C1 D3 G1 D9 M1 D16 R1 D24

A2 FAIL C2 D1 G2 V

CC

M2 V

CC

R2 D27

A3 NC C3 ONCE G3 V

SS

M3 V

SS

R3 D31

A4 NC C4 NC G15 V

SS

M15 V

SS

R4 BTERM

A5 NC C5 NC G16 A7 M16 V

CC

R5 HOLD

A6 DREQ1 C6 V

CC

G17 A8 M17 A14 R6 ADS

A7 DREQ3 C7 V

SS

R7 V

CC

A8 DACK1 C8 V

SS

H1 D11 N1 D17 R8 V

CC

A9 DACK2 C9 V

SS

H2 D10 N2 D18 R9 BE0

A10 DACK3 C10 V

SS

H3 V

SS

N3 V

CC

R10 V

CC

A11 EOP/TC0 C11 V

SS

H15 V

SS

N15 V

CC

R11 V

CC

A12 EOP/TC1 C12 V

SS

H16 V

CC

N16 A16 R12 DMA

A13 EOP/TC2 C13 CLKIN H17 A9 N17 A15 R13 BREQ

A14 EOP/TC3 C14 CLKMODE R14 A29

A15 XINT1 C15 XINT4 J1 D12 P1 D19 R15 A26

A16 RESET C16 XINT6 J2 V

CC

P2 D20 R16 A23

A17 XINT2 C17 XINT7 J3 V

SS

P3 D22 R17 A22

J15 V

SS

P15 A20

B1 BOFF D1 D5 J16 V

CC

P16 A19 S1 D25

B2 STEST D2 D2 J17 A10 P17 A17 S2 D29

B3 NC D3 NC S3 READY

B4 NC D15 NMI K1 D13 Q1 D21 S4 HOLDA

B5 DREQ0 D16 A2 K2 V

CC

Q2 D23 S5 BE3

B6 DREQ2 D17 A3 K3 V

SS

Q3 D26 56 BE2

B7 V

CC

K15 V

SS

Q4 Q28 S7 BE1

B8 DACK0 E1 D7 K16 V

CC

Q5 D30 S8 BLAST

B9 V

CC

E2 D4 K17 A11 Q6 V

CC

S9 DEN

B10 V

CCPLL

E3 D0 Q7 V

SS

S10 W/R

B11 V

CC

E15 V

CC

L1 D15 Q8 V

SS

S11 DT/R

B12 V

CC

E16 A4 L2 D14 Q9 V

SS

S12 WAIT

B13 PCLK2 E17 A5 L3 V

SS

Q10 V

SS

S13 D/C

B14 PCLK1 L15 V

SS

Q11 V

SS

S14 LOCK

B15 XINT0 F1 D8 L16 A13 Q12 SUP S15 A31

B16 XINT3 F2 D6 L17 A12 Q13 A30 S16 A27

B17 XINT5 F3 V

CC

Q14 A28 S17 A25

F15 V

SS

Q15 A24

F16 V

CC

Q16 A21

F17 A6 Q17 A18

16

SPECIAL ENVIRONMENT 80960CA-25, -16

271327–2

Figure 2. 80960CA PGA PinoutÐView from Top (Pins Facing Down)

17

SPECIAL ENVIRONMENT 80960CA-25, -16

271327–3

Figure 3. 80960CA PGA PinoutÐView from Bottom (Pins Facing Up)

18

SPECIAL ENVIRONMENT 80960CA-25, -16

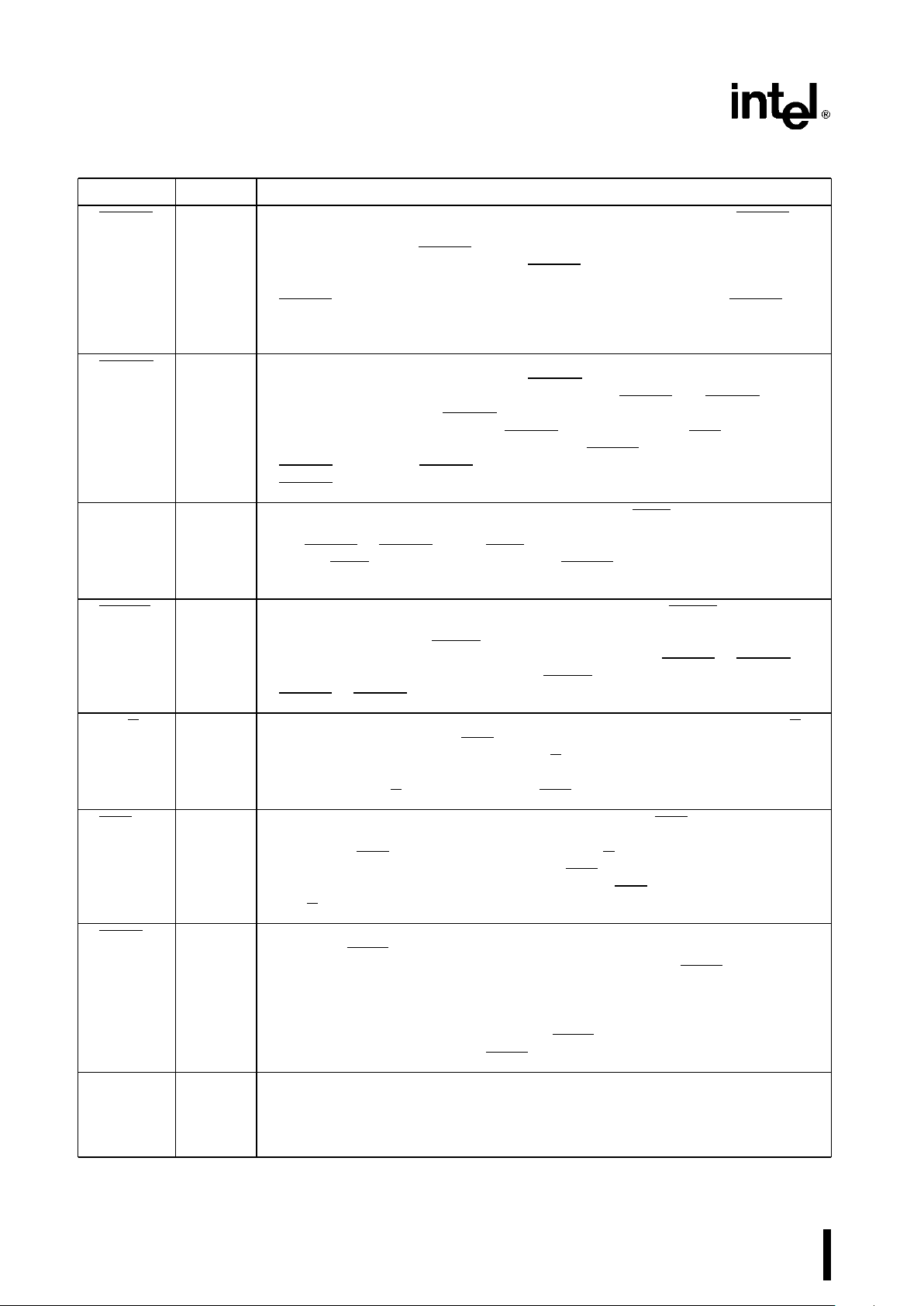

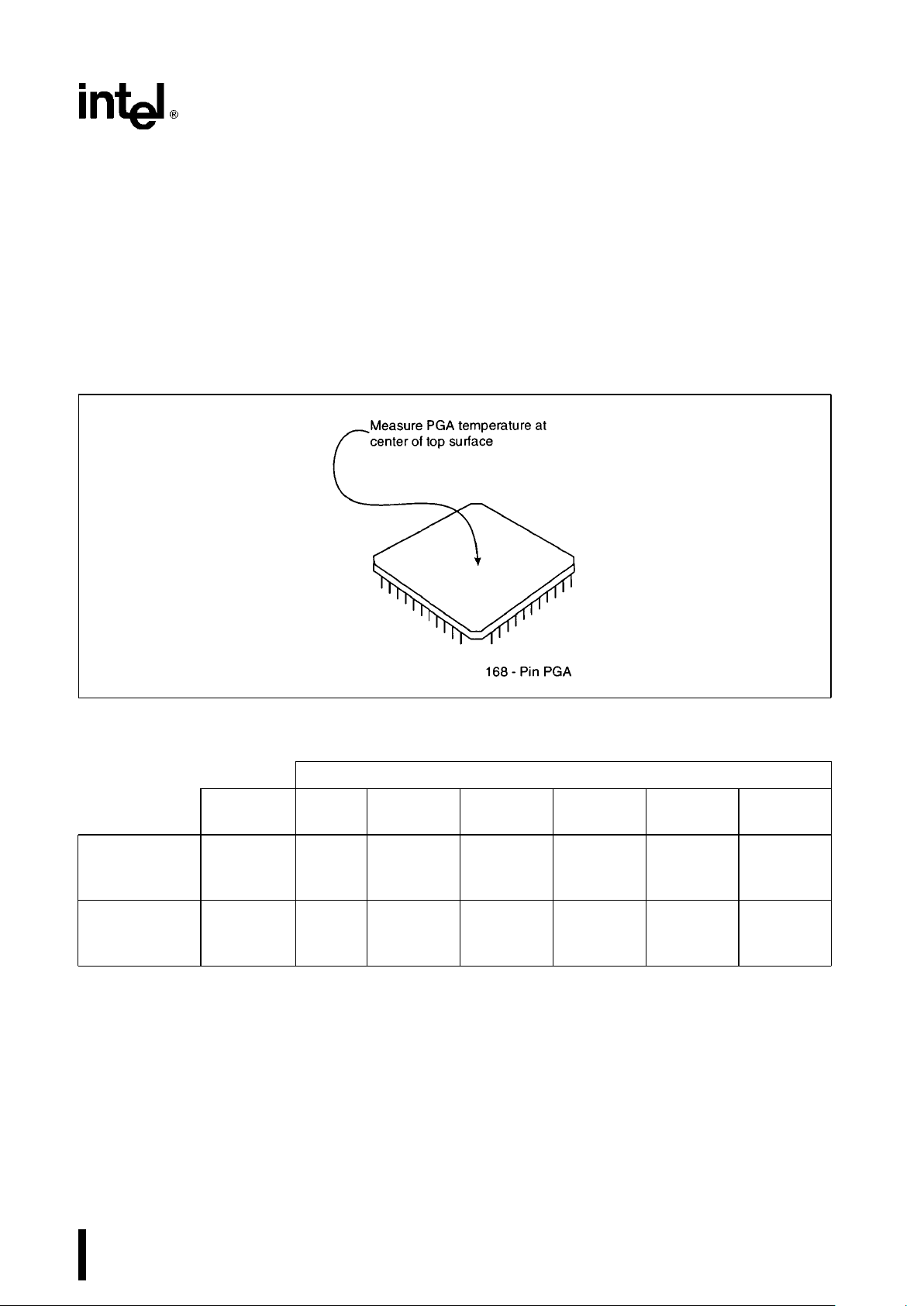

3.4 Package Thermal Specifications

The 80960CA is specified for operation when T

C

(case temperature) is within the range ofb40§C–

a

110§C. TCmay be measured in any environment

to determine whether the 80960CA is within specified operating range. Case temperature should be

measured at the center of the top surface, opposite

the pins. Refer to Figure 4.

T

A

(ambient temperature) can be calculated from

i

CA

(thermal resistance from case to ambient) using

the following equation:

T

A

e

T

C

b

P*i

CA

Table 8 shows the maximum TAallowable (without

exceeding T

C

) at various airflows and operating fre-

quencies (f

PCLK

).

Note that T

A

is greatly improved by attaching fins or

a heatsink to the package. P (maximum power consumption) is calculated by using the typical I

CC

as

tabulated in Section 4.4, DC Specifications and

V

CC

of 5V.

271327–4

Figure 4. Measuring 80960CA PGA Case Temperature

Table 8. Maximum T

A

at Various Airflows in§C

Airflow-ft/min (m/sec)

f

PCLK

0 200 400 600 800 1000

(MHz) (0) (1.01) (2.03) (3.04) (4.06) (5.07)

TAwith 33 51 66 79 81 85 87

Heatsink* 25 61 73 83 85 88 89

16 74 82 89 90 92 93

TAwithout 33 36 47 59 66 73 75

Heatsink* 25 49 58 67 73 78 80

16 66 72 78 82 86 87

NOTES:

0.285

×

high undirectional heatsink (Al alloy 6061, 50 mil fin width, 150 mil center-to-center fin spacing).

19

Loading...

Loading...