December 1994 Order Number: 290479-004

82434LX/82434NX PCI, CACHE AND MEMORY

CONTROLLER (PCMC)

Y

Supports the PentiumTMProcessor at

iCOMP

TM

Index 510T60 MHz and iCOMP

Index 567T66 MHz

Y

Supports the Pentium Processor at

iCOMP Index 735T90 MHz, iCOMP Index

815T100 MHz, and iCOMP Index 610T75

MHz

Y

Supports Pipelined Addressing

Capability of the Pentium Processor

Y

The 82430NX Drives 3.3V Signal Levels

on the CPU and Cache Interfaces

Y

High Performance CPU/PCI/Memory

Interfaces via Posted Write and Read

Prefetch Buffers

Y

Fully Synchronous PCI Interface with

Full Bus Master Capability

Y

Supports the Pentium Processor

Internal Cache in Either Write-Through

or Write-Back Mode

Y

Programmable Attribute Map of DOS

and BIOS Regions for System

Flexibility

Y

Integrated Low Skew Clock Driver for

Distributing Host Clock

Y

Integrated Second Level Cache

Controller

Ð Integrated Cache Tag RAM

Ð Write-Through and Write-Back Cache

Modes for the 82434LX

Ð Write-Back for the 82434NX

Ð 82434NX Supports Low-Power Cache

Standby

Ð Direct Mapped Organization

Ð Supports Standard and Burst SRAMs

Ð 256-KByte and 512-KByte Sizes

Ð Cache Hit Cycle of 3-1-1-1 on Reads

and Writes Using Burst SRAMs

Ð Cache Hit Cycle of 3-2-2-2 on Reads

and 4-2-2-2 on Writes Using

Standard SRAMs

Y

Integrated DRAM Controller

Ð Supports 2 MBytes to 192 MBytes of

Cacheable Main Memory for the

82434LX

Ð Supports 2 MBytes to 512 MBytes of

Cacheable Main Memory for the

82434NX

Ð Supports DRAM Access Times of

70 ns and 60 ns

Ð CPU Writes Posted to DRAM 4-1-1-1

Ð Refresh Cycles Decoupled from ISA

Refresh to Reduce the DRAM

Access Latency

Ð Six RAS

Ý

Lines (82434LX)

Ð Eight RAS

Ý

Lines (82434NX)

Ð Refresh by RAS

Ý

-Only, or CAS-

Before-RAS

Ý

, in Single or Burst

of Four

Y

Host/PCI Bridge

Ð Translates CPU Cycles into PCI Bus

Cycles

Ð Translates Back-to-Back Sequential

CPU Memory Writes into PCI Burst

Cycles

Ð Burst Mode Writes to PCI in Zero PCI

Wait-States (i.e. Data Transfer Every

Cycle)

Ð Full Concurrency Between CPU-to-

Main Memory and PCI-to-PCI

Transactions

Ð Full Concurrency Between CPU-to-

Second Level Cache and PCI-to-Main

Memory Transactions

Ð Same Cache and Memory System

Logic Design for ISA and EISA

Systems

Ð Cache Snoop Filter Ensures Data

Consistency for PCI-to-Main Memory

Transactions

Y

208-Pin QFP Package

*Other brands and names are the property of their respective owners.

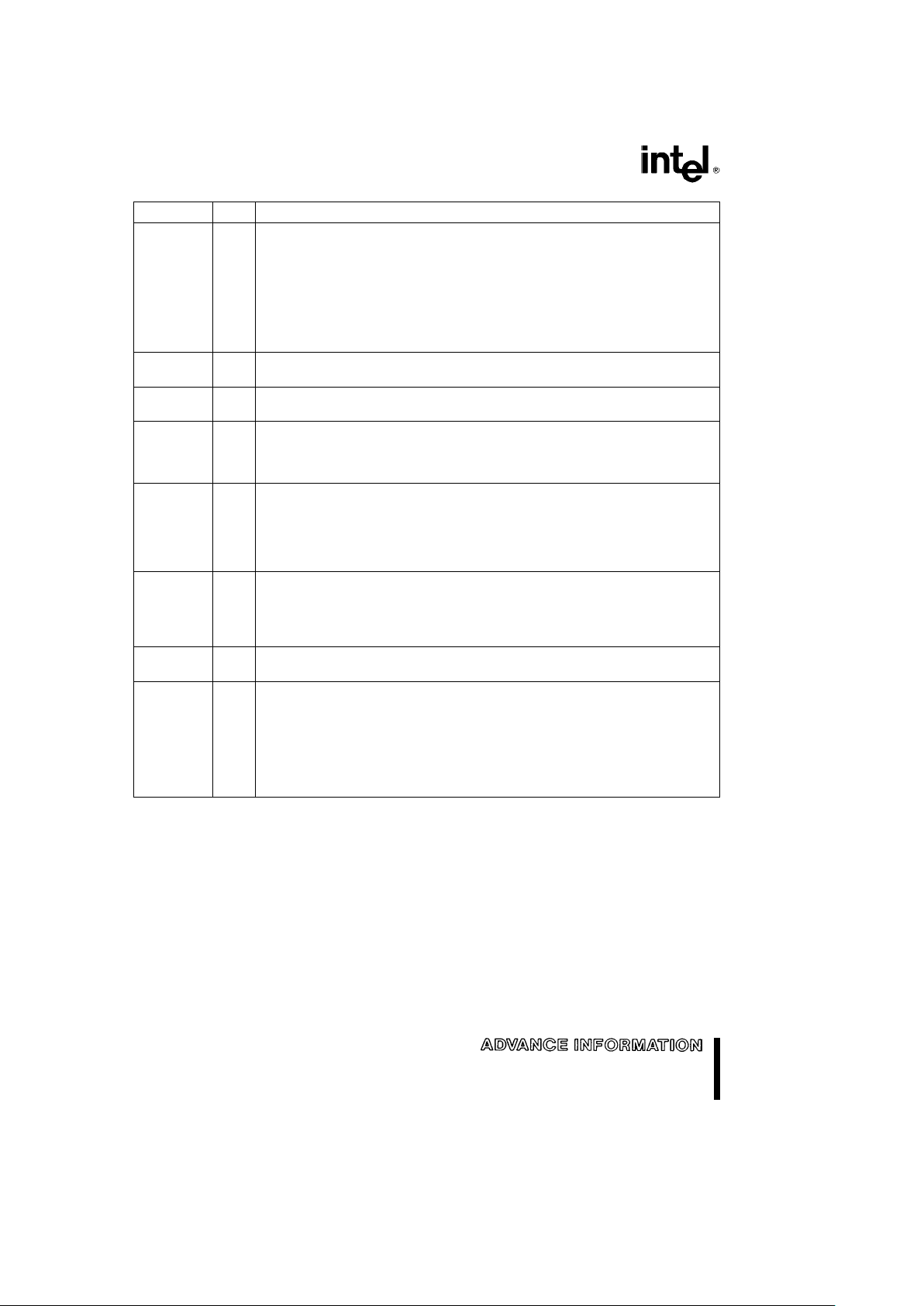

82434LX/82434NX

This document describes both the 82434LX and 82434NX. Unshaded areas describe the 82434LX.

Shaded areas, like this one, describe 82434NX operations that differ from the 82434LX.

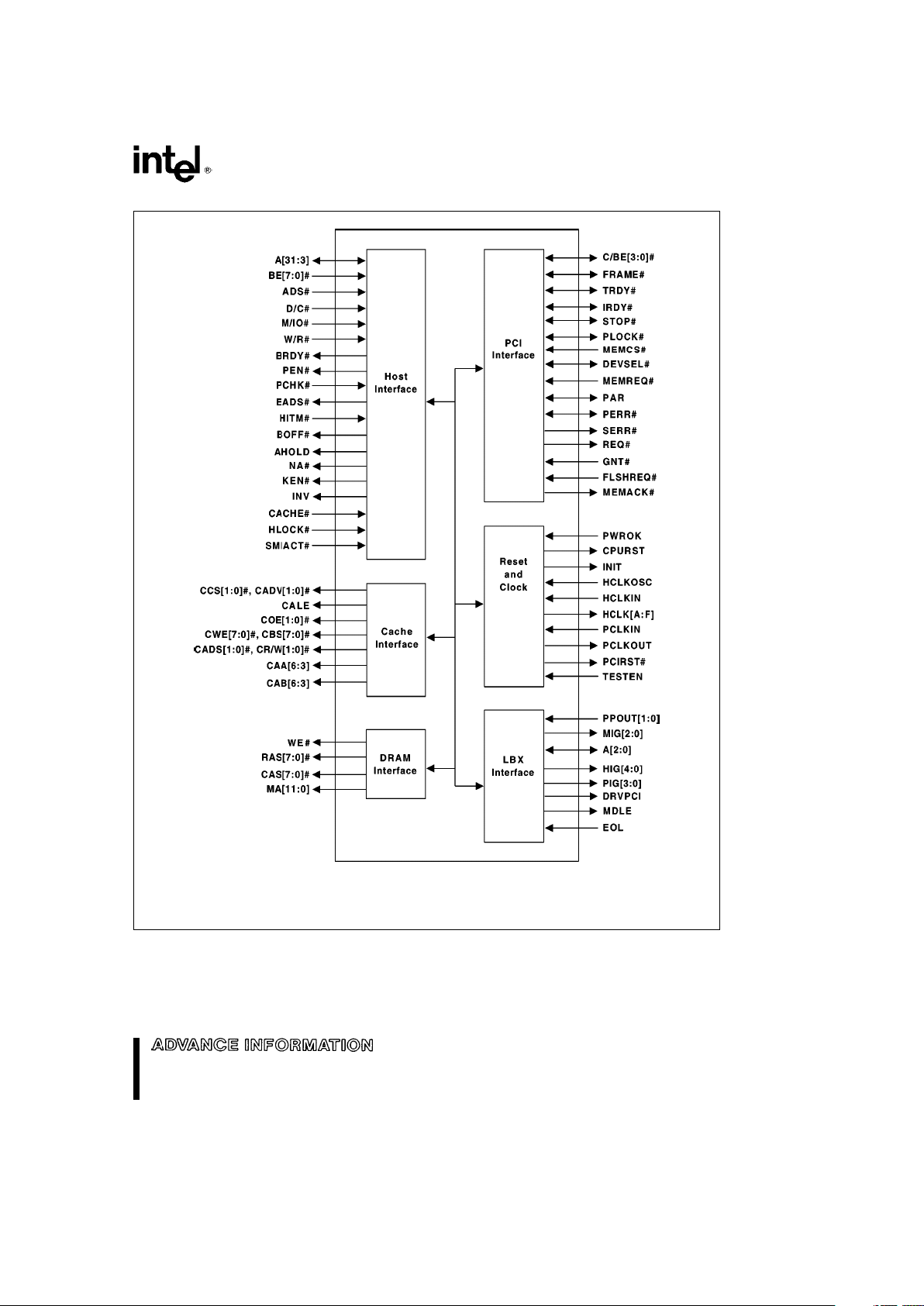

The 82434LX/82434NX PCI, Cache, Memory Controllers (PCMC) integrate the cache and main memory

DRAM control functions and provide bus control for transfers between the CPU, cache, main memory, and the

PCI Local Bus. The cache controller supports write-back (or write-through for 82434LX) cache policy and

cache sizes of 256-KBytes and 512-KBytes. The cache memory can be implemented with either standard or

burst SRAMs. The PCMC cache controller integrates a high-performance Tag RAM to reduce system cost.

2

82434LX/82434NX

290479– 1

NOTE:

RAS[7:6

]

Ý

and MA11 are only on the 82434NX. CCS[1:0]functionality is only on the 82434NX.

Simplified Block Diagram of the PCMC

3

82434LX/82434NX PCI, CACHE AND MEMORY

CONTROLLER (PCMC)

CONTENTS PAGE

1.0 ARCHITECTURAL OVERVIEW

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 10

1.1 System Overview АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 10

1.1.1 BUS HIERARCHYÐCONCURRENT OPERATIONS ААААААААААААААААААААААААААААААА 10

1.1.2 BUS BRIDGES ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 13

1.2 PCMC Overview ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 13

1.2.1 CACHE OPERATIONS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 14

1.2.1.1 Cache Consistency АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

1.2.2 ADDRESS/DATA PATHS АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

1.2.2.1 Read/Write Buffers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

1.2.3 HOST/PCI BRIDGE OPERATIONS ААААААААААААААААААААААААААААААААААААААААААААААА 15

1.2.4 DRAM MEMORY OPERATIONS АААААААААААААААААААААААААААААААААААААААААААААААААА 16

1.2.5 3.3V SIGNALS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 16

2.0 SIGNAL DESCRIPTIONS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 16

2.1 Host Interface ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 17

2.2 DRAM Interface ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 22

2.3 Cache Interface ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 23

2.4 PCI Interface АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 24

2.5 LBX Interface ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 28

2.6 Reset And Clock АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 28

3.0 REGISTER DESCRIPTION ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 30

3.1 I/O Mapped Registers ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 31

3.1.1 CONFADDÐCONFIGURATION ADDRESS REGISTER ААААААААААААААААААААААААААА 31

3.1.2 CSEÐCONFIGURATION SPACE ENABLE REGISTER ААААААААААААААААААААААААААА 32

3.1.3 TRCÐTURBO-RESET CONTROL REGISTER АААААААААААААААААААААААААААААААААААА 33

3.1.4 FORWÐFORWARD REGISTER АААААААААААААААААААААААААААААААААААААААААААААААААА 34

3.1.5 PMCÐPCI MECHANISM CONTROL REGISTER АААААААААААААААААААААААААААААААААА 34

3.1.6 CONFDATAÐCONFIGURATION DATA REGISTER ААААААААААААААААААААААААААААААА 34

3.2 PCI Configuration Space Mapped Registers АААААААААААААААААААААААААААААААААААААААААААА 35

3.2.1 CONFIGURATION SPACE ACCESS MECHANISM АААААААААААААААААААААААААААААААА 36

3.2.1.1 Access MechanismÝ1: АААААААААААААААААААААААААААААААААААААААААААААААААААААА 36

3.2.1.2 Access MechanismÝ2 АААААААААААААААААААААААААААААААААААААААААААААААААААААА 37

3.2.2 VIDÐVENDOR IDENTIFICATION REGISTER ААААААААААААААААААААААААААААААААААААА 40

3.2.3 DIDÐDEVICE IDENTIFICATION REGISTER АААААААААААААААААААААААААААААААААААААА 40

4

CONTENTS PAGE

3.2.4 PCICMDÐPCI COMMAND REGISTER

ААААААААААААААААААААААААААААААААААААААААААА 41

3.2.5 PCISTSÐPCI STATUS REGISTER ААААААААААААААААААААААААААААААААААААААААААААААА 42

3.2.6 RIDÐREVISION IDENTIFICATION REGISTER ААААААААААААААААААААААААААААААААААА 43

3.2.7 RLPIÐREGISTER-LEVEL PROGRAMMING INTERFACE REGISTER ААААААААААААА 43

3.2.8 SUBCÐSUB-CLASS CODE REGISTER АААААААААААААААААААААААААААААААААААААААААА 43

3.2.9 BASECÐBASE CLASS CODE REGISTER АААААААААААААААААААААААААААААААААААААААА 44

3.2.10 MLTÐMASTER LATENCY TIMER REGISTER ААААААААААААААААААААААААААААААААААА 44

3.2.11 BISTÐBIST REGISTER ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 44

3.2.12 HCSÐHOST CPU SELECTION REGISTER АААААААААААААААААААААААААААААААААААААА 45

3.2.13 DFCÐDETURBO FREQUENCY CONTROL REGISTER ААААААААААААААААААААААААА 46

3.2.14 SCCÐSECONDARY CACHE CONTROL REGISTER АААААААААААААААААААААААААААА 46

3.2.15 HBCÐHOST READ/WRITE BUFFER CONTROL АААААААААААААААААААААААААААААААА 48

3.2.16 PBCÐPCI READ/WRITE BUFFER CONTROL REGISTER ААААААААААААААААААААААА 49

3.2.17 DRAMCÐDRAM CONTROL REGISTER ААААААААААААААААААААААААААААААААААААААААА 50

3.2.18 DRAMTÐDRAM TIMING REGISTER АААААААААААААААААААААААААААААААААААААААААААА 51

3.2.19 PAMÐPROGRAMMABLE ATTRIBUTE MAP REGISTERS (PAM[6:0]) ААААААААААА 51

3.2.20 DRBÐDRAM ROW BOUNDARY REGISTERS ААААААААААААААААААААААААААААААААААА 54

3.2.20.1 82434LX Description ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 54

3.2.20.2 82434NX Description ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 56

3.2.21 DRBEÐDRAM ROW BOUNDARY EXTENSION REGISTER ААААААААААААААААААААА 58

3.2.22 ERRCMDÐERROR COMMAND REGISTER ААААААААААААААААААААААААААААААААААААА 58

3.2.23 ERRSTSÐERROR STATUS REGISTER АААААААААААААААААААААААААААААААААААААААА 60

3.2.24 SMRSÐSMRAM SPACE REGISTER АААААААААААААААААААААААААААААААААААААААААААА 61

3.2.25 MSGÐMEMORY SPACE GAP REGISTER АААААААААААААААААААААААААААААААААААААА 61

3.2.26 FBRÐFRAME BUFFER RANGE REGISTER АААААААААААААААААААААААААААААААААААА 62

4.0 PCMC ADDRESS MAP АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 64

4.1 CPU Memory Address Map АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 64

4.2 System Management RAMÐSMRAM АААААААААААААААААААААААААААААААААААААААААААААААААА 64

4.3 PC Compatibility Range АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 65

4.4 I/O Address Map АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 66

5

CONTENTS PAGE

5.0 SECOND LEVEL CACHE INTERFACE

ААААААААААААААААААААААААААААААААААААААААААААААААААА 67

5.1 82434LX Cache ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 67

5.1.1 CLOCK LATENCIES (82434LX) ААААААААААААААААААААААААААААААААААААААААААААААААААА 75

5.1.2 STANDARD SRAM CACHE CYCLES (82434LX) АААААААААААААААААААААААААААААААААА 76

5.1.2.1 Burst Read (82434LX) ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 76

5.1.2.2 Burst Write (82434LX) ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 78

5.1.2.3 Cache Line Fill (82434LX) АААААААААААААААААААААААААААААААААААААААААААААААААААА 80

5.1.3 BURST SRAM CACHE CYCLES (82434LX) ААААААААААААААААААААААААААААААААААААААА 84

5.1.3.1 Burst Read (82434LX) ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 84

5.1.3.2 Burst Write (82434LX) ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 86

5.1.3.3 Cache Line Fill (82434LX) АААААААААААААААААААААААААААААААААААААААААААААААААААА 88

5.1.4 SNOOP CYCLES ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 90

5.1.5 FLUSH, FLUSH ACKNOWLEDGE AND WRITE-BACK SPECIAL CYCLES ААААААААА 98

5.2 82434NX Cache ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 98

5.2.1 CYCLE LATENCY SUMMARY (82434NX) АААААААААААААААААААААААААААААААААААААААА 102

5.2.2 STANDARD SRAM CACHE CYCLES (82434NX) ААААААААААААААААААААААААААААААААА 103

5.2.3 SECOND LEVEL CACHE STANDBY ААААААААААААААААААААААААААААААААААААААААААААА 103

5.2.4 SNOOP CYCLES АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 103

5.2.5 FLUSH, FLUSH ACKNOWLEDGE, AND WRITE-BACK SPECIAL CYCLES АААААААА 103

6.0 DRAM INTERFACE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 104

6.1 82434LX DRAM Interface АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 104

6.1.1 DRAM CONFIGURATIONS АААААААААААААААААААААААААААААААААААААААААААААААААААААА 105

6.1.2 DRAM ADDRESS TRANSLATION ААААААААААААААААААААААААААААААААААААААААААААААА 105

6.1.3 CYCLE TIMING SUMMARY ААААААААААААААААААААААААААААААААААААААААААААААААААААА 108

6.1.4 CPU TO DRAM BUS CYCLES ААААААААААААААААААААААААААААААААААААААААААААААААААА 108

6.1.4.1 Read Page Hit АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 108

6.1.4.2 Read Page Miss АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 110

6.1.4.3 Read Row Miss ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 111

6.1.4.4 Write Page Hit АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 112

6.1.4.5 Write Page Miss АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 113

6.1.4.6 Write Row Miss ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 114

6.1.4.7 Read Cycle, 0-Active RASÝMode АААААААААААААААААААААААААААААААААААААААААА 115

6.1.4.8 Write Cycle, 0-Active RASÝMode АААААААААААААААААААААААААААААААААААААААААА 116

6

CONTENTS PAGE

6.1.5 REFRESH

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 117

6.1.5.1 RASÝ-Only Refresh-Single ААААААААААААААААААААААААААААААААААААААААААААААААА 117

6.1.5.2 CASÝ-Before-RASÝRefresh-Single АААААААААААААААААААААААААААААААААААААААА 119

6.1.5.3 Hidden Refresh-Single АААААААААААААААААААААААААААААААААААААААААААААААААААААА 120

6.2 82434NX DRAM Interface АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 121

6.2.1 DRAM ADDRESS TRANSLATION ААААААААААААААААААААААААААААААААААААААААААААААА 121

6.2.2 CYCLE TIMING SUMMARY ААААААААААААААААААААААААААААААААААААААААААААААААААААА 122

6.2.3 CPU TO DRAM BUS CYCLES ААААААААААААААААААААААААААААААААААААААААААААААААААА 122

6.2.3.1 Burst DRAM Read Page Hit ААААААААААААААААААААААААААААААААААААААААААААААААА 123

6.2.3.2 Burst DRAM Read Page Miss ААААААААААААААААААААААААААААААААААААААААААААААА 124

6.2.3.3 Burst DRAM Read Row Miss АААААААААААААААААААААААААААААААААААААААААААААААА 125

6.2.3.4 Burst DRAM Write Page Hit ААААААААААААААААААААААААААААААААААААААААААААААААА 126

6.2.3.5 Burst DRAM Write Page Miss ААААААААААААААААААААААААААААААААААААААААААААААА 127

6.2.3.6 Burst DRAM Write Row Miss АААААААААААААААААААААААААААААААААААААААААААААААА 128

6.2.4 REFRESH АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 129

6.2.4.1 RASÝ-Only RefreshÐSingle ААААААААААААААААААААААААААААААААААААААААААААААА 129

6.2.4.2 CASÝ-before-RASÝRefreshÐSingle АААААААААААААААААААААААААААААААААААААА 130

6.2.4.3 Hidden Refresh-Single АААААААААААААААААААААААААААААААААААААААААААААААААААААА 131

7.0 PCI INTERFACE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 132

7.1 PCI Interface Overview ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 132

7.2 CPU-to-PCI Cycles ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 132

7.2.1 CPU WRITE TO PCI ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 132

7.3 Register Access Cycles АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 133

7.3.1 CPU WRITE CYCLE TO PCMC INTERNAL REGISTER ААААААААААААААААААААААААААА 134

7.3.2 CPU READ FROM PCMC INTERNAL REGISTER АААААААААААААААААААААААААААААААА 135

7.3.3 CPU WRITE TO PCI DEVICE CONFIGURATION REGISTER ААААААААААААААААААААА 136

7.3.4 CPU READ FROM PCI DEVICE CONFIGURATION REGISTER ААААААААААААААААААА 138

7.4 PCI-to-Main Memory Cycles АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 141

7.4.1 PCI MASTER WRITE TO MAIN MEMORY ААААААААААААААААААААААААААААААААААААААА 141

7.4.2 PCI MASTER READ FROM MAIN MEMORY ААААААААААААААААААААААААААААААААААААА 143

7

CONTENTS PAGE

8.0 SYSTEM CLOCKING AND RESET

ААААААААААААААААААААААААААААААААААААААААААААААААААААА 144

8.1 Clock Domains ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 144

8.2 Clock Generation and Distribution АААААААААААААААААААААААААААААААААААААААААААААААААААА 144

8.3 Phase Locked Loop Circuitry ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 145

8.4 System Reset АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 147

8.5 82434NX Reset Sequencing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 149

9.0 ELECTRICAL CHARACTERISTICS ААААААААААААААААААААААААААААААААААААААААААААААААААААА 150

9.1 Absolute Maximum Ratings ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 150

9.2 Thermal Characteristics АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 150

9.3 82434LX DC Characteristics АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 150

9.4 82434NX DC Characteristics ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 152

9.5 82434LX AC Characteristics АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 154

9.5.1 HOST CLOCK TIMING, 66 MHz (82434LX) АААААААААААААААААААААААААААААААААААААА 154

9.5.2 CPU INTERFACE TIMING, 66 MHz (82434LX) ААААААААААААААААААААААААААААААААААА 155

9.5.3 SECOND LEVEL CACHE STANDARD SRAM TIMING, 66 MHz (82434LX) АААААААА 157

9.5.4 SECOND LEVEL CACHE BURST SRAM TIMING, 66 MHz (82434LX) АААААААААААА 158

9.5.5 DRAM INTERFACE TIMING, 66 MHz (82434LX) ААААААААААААААААААААААААААААААААА 158

9.5.6 PCI CLOCK TIMING, 66 MHz (82434LX) ААААААААААААААААААААААААААААААААААААААААА 158

9.5.7 PCI INTERFACE TIMING, 66 MHz (82434LX) АААААААААААААААААААААААААААААААААААА 159

9.5.8 LBX INTERFACE TIMING, 66 MHz (82434LX) ААААААААААААААААААААААААААААААААААА 160

9.5.9 HOST CLOCK TIMING, 60 MHz (82434LX) АААААААААААААААААААААААААААААААААААААА 160

9.5.10 CPU INTERFACE TIMING, 60 MHz (82434LX) АААААААААААААААААААААААААААААААААА 161

9.5.11 SECOND LEVEL CACHE STANDARD SRAM TIMING, 60 MHz (82434LX) АААААА 163

9.5.12 SECOND LEVEL CACHE BURST SRAM TIMING, 60 MHz (82434LX) ААААААААААА 164

9.5.13 DRAM INTERFACE TIMING, 60 MHz (82434LX) АААААААААААААААААААААААААААААААА 164

9.5.14 PCI CLOCK TIMING, 60 MHz (82434LX) АААААААААААААААААААААААААААААААААААААААА 165

9.5.15 PCI INTERFACE TIMING, 60 MHz (82434LX) ААААААААААААААААААААААААААААААААААА 165

9.5.16 LBX INTERFACE TIMING, 60 MHz (82434LX) АААААААААААААААААААААААААААААААААА 166

8

CONTENTS PAGE

9.6 82434NX AC Characteristics

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 167

9.6.1 HOST CLOCK TIMING, 66 MHz (82434NX), PRELIMINARY АААААААААААААААААААААА 167

9.6.2 CPU INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY АААААААААААААААААА 168

9.6.3 SECOND LEVEL CACHE STANDARD SRAM TIMING, 66 MHz (82434NX),

PRELIMINARY ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 170

9.6.4 SECOND LEVEL CACHE BURST SRAM TIMING, 66 MHz (82434NX),

PRELIMINARY ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 171

9.6.5 DRAM INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY АААААААААААААААА 171

9.6.6 PCI CLOCK TIMING, 66 MHz (82434NX), PRELIMINARY АААААААААААААААААААААААА 172

9.6.7 PCI INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY ААААААААААААААААААА 172

9.6.8 LBX INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY ААААААААААААААААААА 173

9.6.9 HOST CLOCK TIMING, 50 and 60 MHz (82434NX) ААААААААААААААААААААААААААААААА 173

9.6.10 CPU INTERFACE TIMING, 50 AND 60 MHz (82434NX) ААААААААААААААААААААААААА 174

9.6.11 SECOND LEVEL CACHE STANDARD SRAM TIMING, 50 AND 60 MHz

(82434NX) АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 176

9.6.12 SECOND LEVEL CACHE BURST SRAM TIMING, 50 AND 60 MHz

(82434NX) АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 177

9.6.13 DRAM INTERFACE TIMING, 50 AND 60 MHz (82434NX) ААААААААААААААААААААААА 177

9.6.14 PCI CLOCK TIMING, 50 AND 60 MHz (82434NX) ААААААААААААААААААААААААААААААА 178

9.6.15 PCI INTERFACE TIMING, 50 AND 60 MHz (82434NX) АААААААААААААААААААААААААА 178

9.6.16 LBX INTERFACE TIMING, 50 AND 60 MHz (82434NX) ААААААААААААААААААААААААА 179

9.6.17 TIMING DIAGRAMS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 179

10.0 PINOUT AND PACKAGE INFORMATION ААААААААААААААААААААААААААААААААААААААААААААА 182

10.1 Pin Assignment ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 182

10.2 Package Characteristics ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 189

11.0 TESTABILITY ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 190

9

82434LX/82434NX

1.0 ARCHITECTURAL OVERVIEW

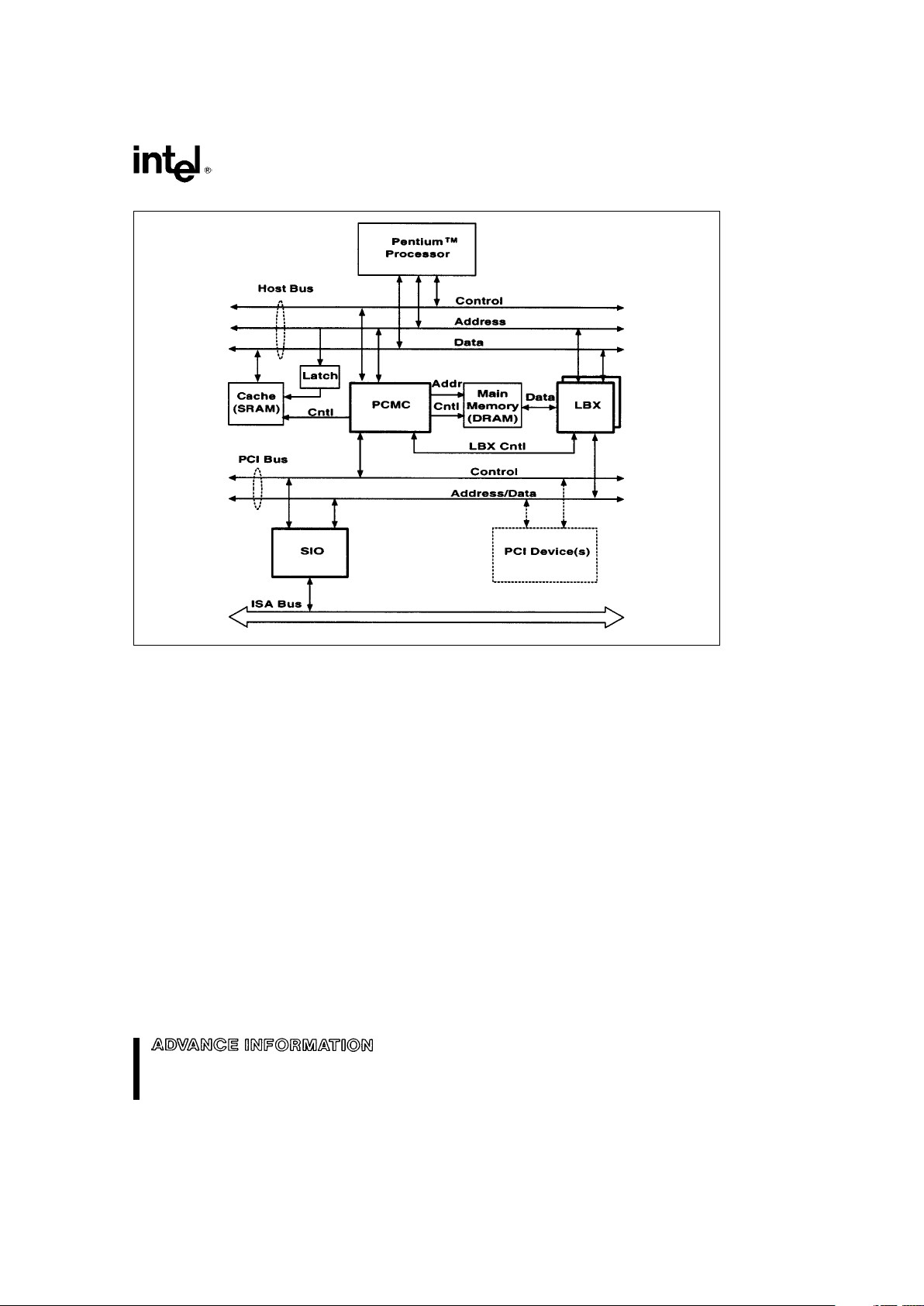

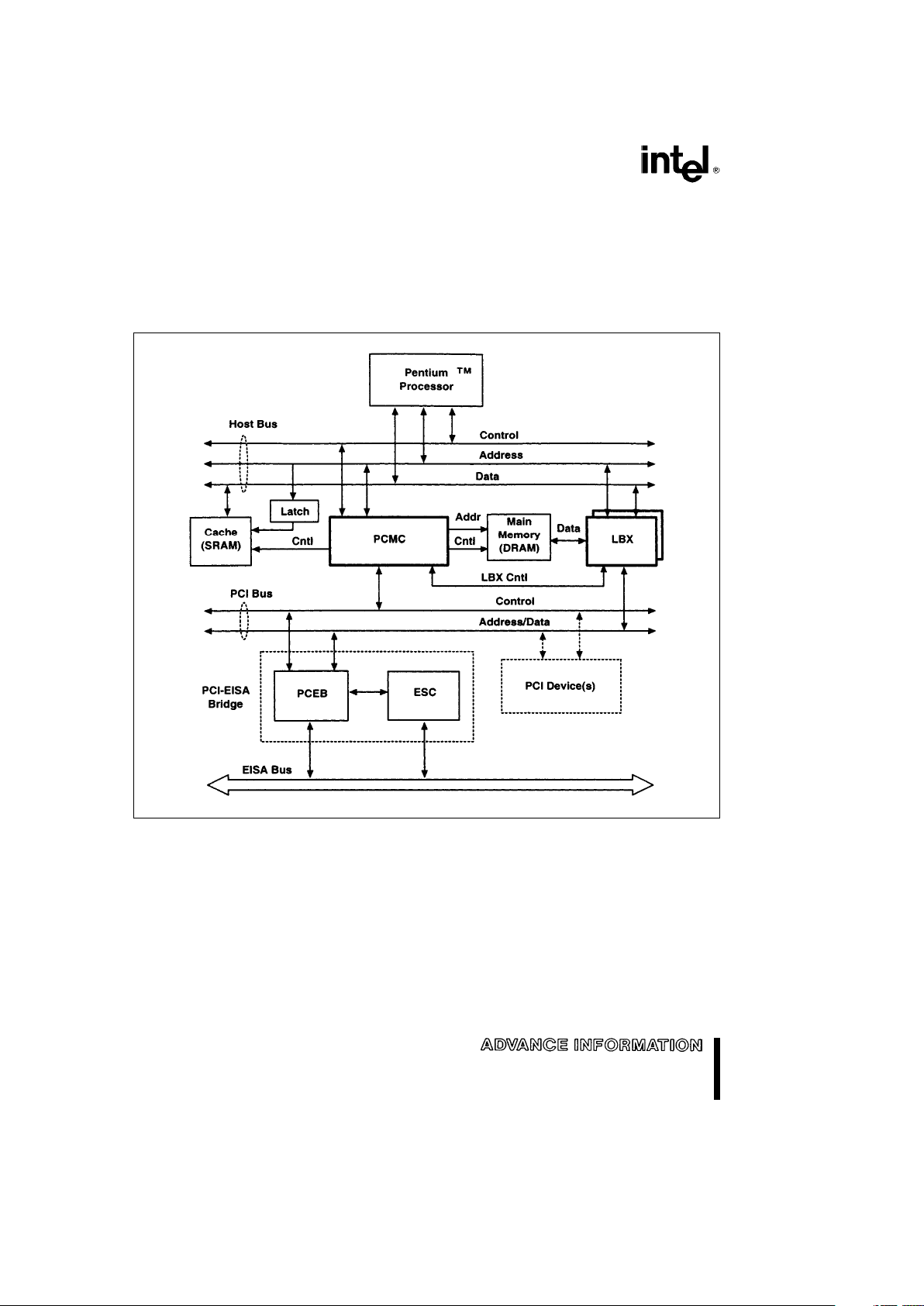

This section provides an 82430LX/82430NX PCIset

system overview that includes a description of the

bus hierarchy and bridges between the buses. The

82430LX PCIset consists of the 82434LX PCMC and

82433LX LBX components plus either a PCI/ISA

bridge or a PCI/EISA bridge. The 82430NX PCIset

consists of the 82434NX PCMC and 82433NX LBX

components plus either a PCI/ISA bridge or a PCI/

EISA bridge. The PCMC and LBX provide the core

cache and main memory architecture and serve as

the Host/PCI bridge. An overview of the PCMC follows the system overview section.

1.1 System Overview

The 82430LX/82430NX PCIset provides the Host/

PCI bridge, cache and main memory controller, and

an I/O subsystem core (either PCI/EISA or PCI/ISA

bridge) for the next generation of high-performance

personal computers based on the Pentium processor. System designers can take advantage of the

power of the PCI (Peripheral Component Interconnect) local bus while maintaining access to the large

base of EISA and ISA expansion cards. Extensive

buffering and buffer management within the bridges

ensures maximum efficiency in all three buses (Host

CPU, PCI, and EISA/ISA Buses).

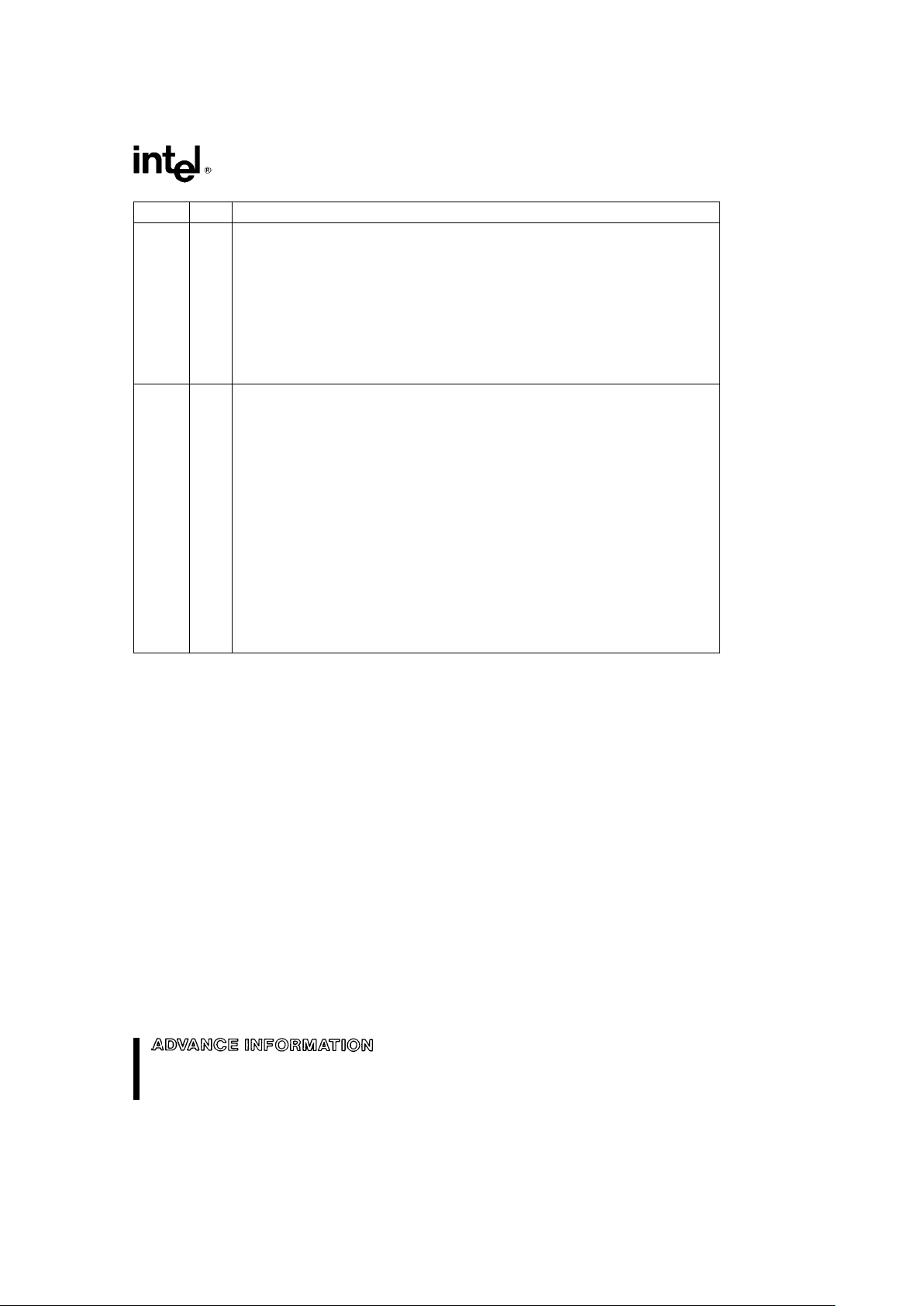

For an ISA-based system, the PCIset includes the

System I/O (82378IB SIO) component (Figure 1) as

the PCI/ISA bridge. For an EISA-based system (Figure 2), the PCIset includes the PCI-EISA bridge

(82375EB PCEB) and the EISA System Component

(82374EB ESC). The PCEB and ESC work in tandem to form the complete PCI/EISA bridge.

1.1.1. BUS HIERARCHYÐCONCURRENT

OPERATIONS

Systems based on the 82430LX/82430NX PCIset

contain three levels of buses structured in the following hierarchy:

#

Host Bus as the execution bus

#

PCI Bus as a primary I/O bus

#

ISA or EISA Bus as a secondary I/O bus.

This bus hierarchy allows concurrency for simultaneous operations on all three buses. Data buffering

permits concurrency for operations that crossover

into another bus. For example, the Pentium processor could post data destined to the PCI in the LBX.

This permits the Host transaction to complete in

minimum time, freeing up the Host Bus for further

transactions. The Pentium processor does not have

to wait for the transfer to complete to its final destination. Meanwhile, any ongoing PCI Bus transactions are permitted to complete. The posted data is

then transferred to the PCI Bus when the PCI Bus is

available. The LBX implements extensive buffering

for Host-to-PCI, Host-to-main memory, and PCI-tomain memory transactions. In addition, the PCEB/

ESC chip set and the SIO implement extensive buffering for transfers between the PCI Bus and the

EISA and ISA Buses, respectively.

Host Bus

Designed to meet the needs of high-performance

computing, the Host Bus features:

#

64-bit data path

#

32-bit address bus with address pipelining

#

Synchronous frequencies of 60 MHz and 66 MHz

#

Synchronous frequency of 50 MHz (82430NX)

#

Burst read and write transfers

#

Support for first level and second level caches

#

Capable of full concurrency with the PCI and

memory subsystems

#

Byte data parity

#

Full support for Pentium processor machine

check and DOS compatible parity reporting

#

Support for Pentium processor System Management Mode (SMM).

10

82434LX/82434NX

290479– 2

Figure 1. Block Diagram of a 82430LX/82430NX PCIset ISA System

PCI Bus

The PCI Bus is designed to address the growing industry needs for a standardized

local bus

that is not

directly dependent on the speed and the size of the

processor bus. New generations of personal computer system software such as Windows

TM

and

Win-NT

TM

with sophisticated graphical interfaces,

multi-tasking, and multi-threading bring new requirements that traditional PC I/O architectures cannot

satisfy. In addition to the higher bandwidth, reliability

and robustness of the I/O subsystem are becoming

increasingly important. PCI addresses these needs

and provides a future upgrade path. PCI features include:

#

Processor independent

#

Multiplexed, burst mode operation

#

Synchronous at frequencies up to 33 MHz

#

120 MByte/sec usable throughput

(132 MByte/sec peak) for a 32-bit data path

11

82434LX/82434NX

#

Low latency random access (60 ns write access

latency to slave registers from a master parked

on the bus)

#

Capable of full concurrency with the processor/

memory subsystem

#

Full multi-master capability allowing any PCI master peer-to-peer access to any PCI slave

#

Hidden (overlapped) central arbitration

#

Low pin count for cost effective component packaging (multiplexed address/data)

#

Address and data parity

#

Three physical address spaces: memory, I/O,

and configuration

#

Comprehensive support for autoconfiguration

through a defined set of standard configuration

functions.

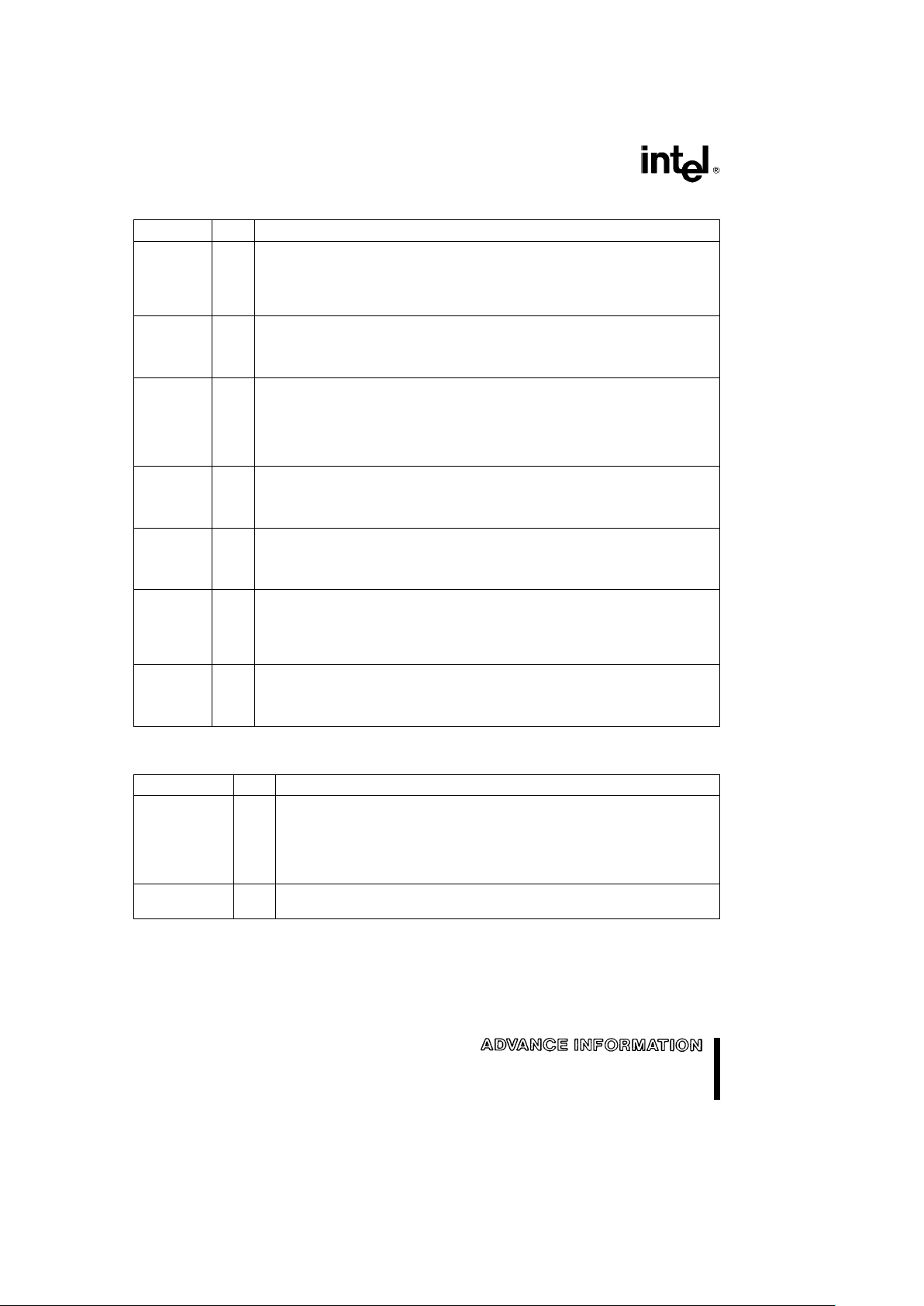

290479– 3

Figure 2. Block Diagram of the 82430LX/82430NX PCIset EISA System

12

82434LX/82434NX

ISA Bus

Figure 1 represents a system using the ISA Bus as

the second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O

bus to leverage the large ISA product base. The ISA

Bus has 24-bit addressing and a 16-bit data path.

EISA Bus

Figure 2 represents a system using the EISA Bus as

the second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O

bus to leverage the large EISA/ISA product base.

Combinations of PCI and EISA buses, both of which

can be used to provide expansion functions, will satisfy even the most demanding applications.

Along with compatibility for 16-bit and 8-bit ISA hardware and software, the EISA bus provides the following key features:

#

32-bit addressing and 32-bit data path

#

33 MByte/sec bus bandwidth

#

Multiple bus master support through efficient arbitration

#

Support for autoconfiguration.

1.1.2 BUS BRIDGES

Host/PCI Bridge Chip Set (PCMC and LBX)

The PCMC and LBX enhance the system performance by allowing for concurrency between the Host

CPU Bus and PCI Bus, giving each greater bus

throughput and decreased bus latency. The LBX

contains posted write buffers for Host-to-PCI, Hostto-main memory, and PCI-to-main memory transfers.

The LBX also contains read prefetch buffers for

Host reads of PCI, and PCI reads of main memory.

There are two LBXs per system. The LBXs are controlled by commands from the PCMC. The PCMC/

LBX Host/PCI bridge chip set is covered in more

detail in Section 1.2, PCMC Overview.

PCI-EISA Bridge Chip Set (PCEB and ESC)

The PCEB provides the master/slave functions on

both the PCI Bus and the EISA Bus. Functioning as

a bridge between the PCI and EISA buses, the

PCEB provides the address and data paths, bus

controls, and bus protocol translation for PCI-toEISA and EISA-to-PCI transfers. Extensive data buffering in both directions increase system perform-

ance by maximizing PCI and EISA Bus efficiency and

allowing concurrency on the two buses. The PCEB’s

buffer management mechanism ensures data coherency. The PCEB integrates central bus control functions including a programmable bus arbiter for the

PCI Bus and EISA data swap buffers for the EISA

Bus. Integrated system functions include PCI parity

generation, system error reporting, and programmable PCI and EISA memory and I/O address space

mapping and decoding. The PCEB also contains a

BIOS Timer that can be used to implement timing

loops. The PCEB is intended to be used with the

ESC to provide an EISA I/O subsystem interface.

The ESC integrates the common I/O functions

found in today’s EISA-based PCs. The ESC incorporates the logic for EISA Bus controller, enhanced

seven channel DMA controller with scatter-gather

support, EISA arbitration, 14 level interrupt controller, Advanced Programmable Interrupt Controller

(APIC), five programmable timer/counters, nonmaskable-interrupt (NMI) control, and power management. The ESC also integrates support logic to

decode peripheral devices (e.g., the flash BIOS, real

time clock, keyboard/mouse controller, floppy controller, two serial ports, one parallel port, and IDE

hard disk drive).

PCI/ISA Bridge (SIO):

The SIO component provides the bridge between

the PCI Bus and the ISA Bus. The SIO also integrates many of the common I/O functions found in

today’s ISA-based PCs. The SIO incorporates the

logic for a PCI interface (master and slave), ISA interface (master and slave), enhanced seven channel

DMA controller that supports fast DMA transfers and

scatter-gather, data buffers to isolate the PCI Bus

from the ISA Bus and to enhance performance, PCI

and ISA arbitration, 14 level interrupt controller, a

16-bit BIOS timer, three programmable timer/counters, and non-maskable-interrupt (NMI) control logic.

The SIO also provides decode for peripheral devices

(e.g., the flash BIOS, real time clock, keyboard/

mouse controller, floppy controller, two serial ports,

one parallel port, and IDE hard disk drive).

1.2 PCMC Overview

The PCMC (along with the LBX) provides three basic

functions: a cache controller, a main memory DRAM

controller, and a Host/PCI bridge. This section provides an overview of these functions. Note that, in

this document, operational descriptions assume that

the PCMC and LBX components are used together.

13

82434LX/82434NX

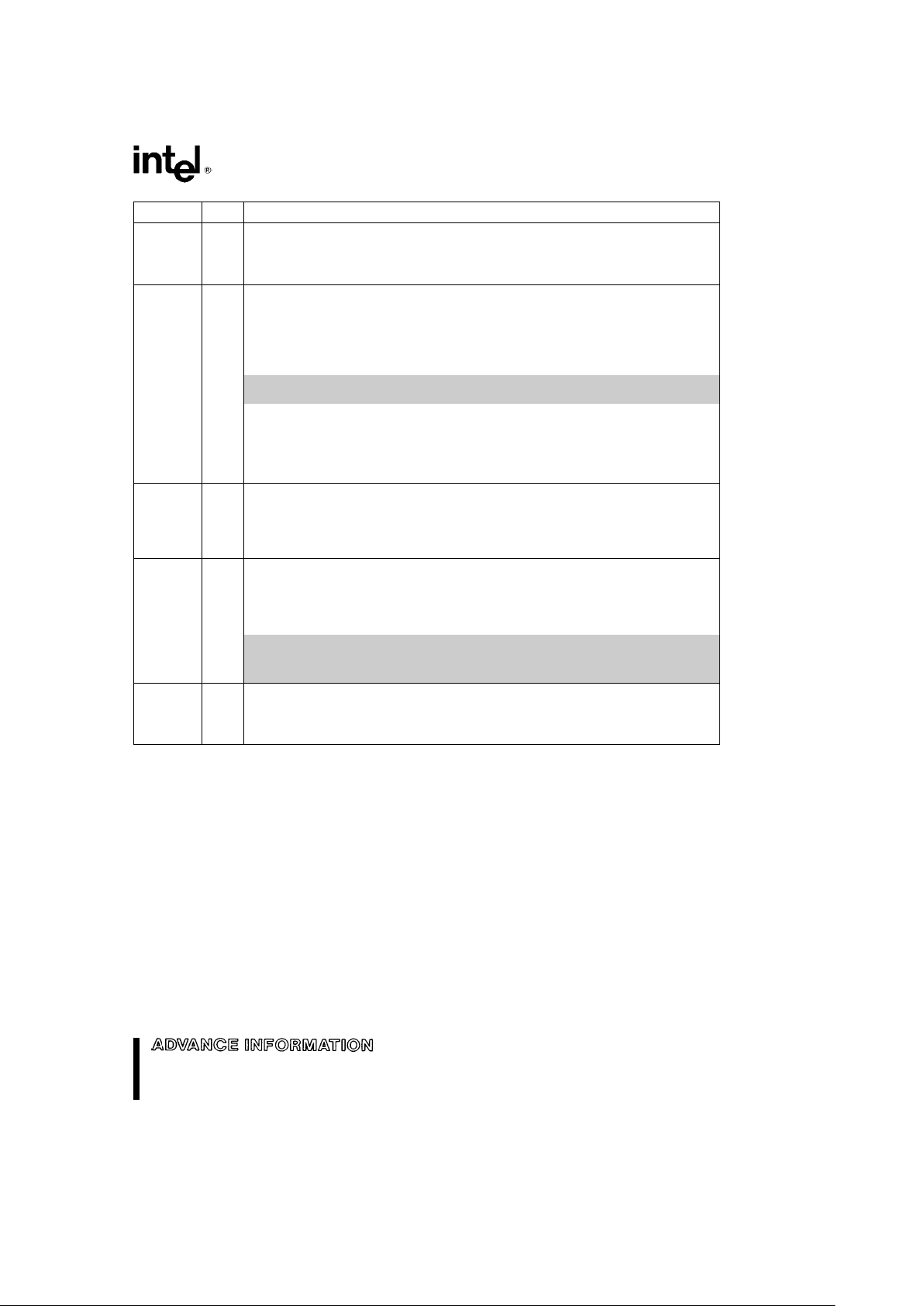

1.2.1 CACHE OPERATIONS

The PCMC provides the control for a second level

cache memory array implemented with either standard asynchronous SRAMs or synchronous burst

SRAMs. The data memory array is external to the

PCMC and located on the Host address/data bus.

Since the Pentium processor contains an internal

cache, there can be two separate caches in a Host

subsystem. The cache inside the Pentium processor

is referred to as the first level cache (also called

primary cache). A detailed description of the first level cache is beyond the scope of this document. The

PCMC cache control circuitry and associated external memory array is referred to as the second level

cache (also called secondary cache). The second

level cache is unified, meaning that both CPU data

and instructions are stored in the cache. The

82434LX PCMC supports both write-through and

write-back caching policies and the 82434NX supports write-back.

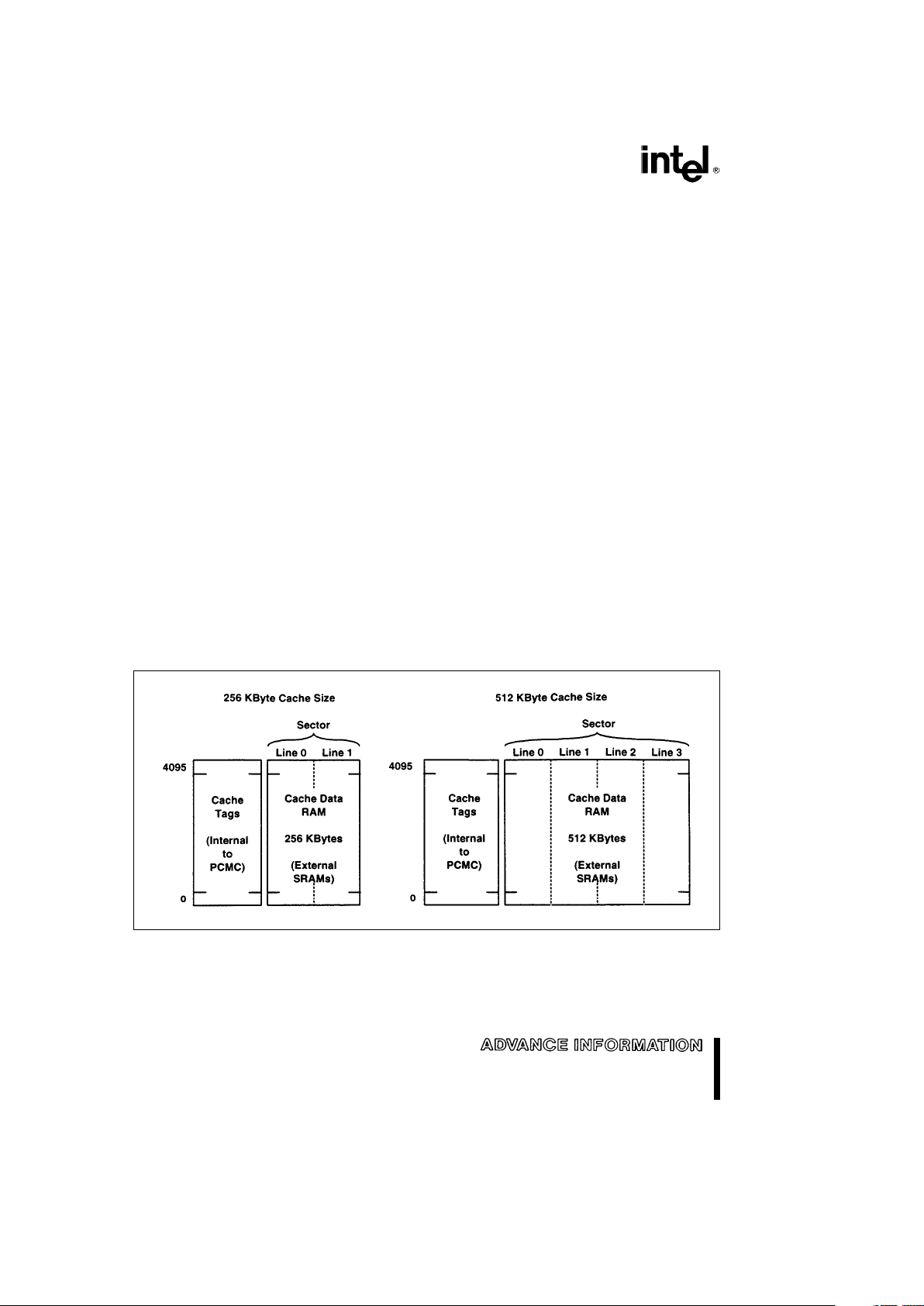

The optional second level cache memory array can

be either 256-KBytes or 512-KBytes in size. The

cache is direct-mapped and is organized as either

8K or 16K cache lines of 32 bytes per line.

In addition to the cache data RAM, the second level

cache contains a 4K set of cache tags that are internal to the PCMC. Each tag contains an address that

is associated with the corresponding data sector

(2 lines for a 256 KByte cache and 4 lines for a

512 KByte cache) and two status bits for each line in

the sector.

During a main memory read or write operation, the

PCMC first searches the cache. If the addressed

code or data is in the cache, the cycle is serviced by

the cache. If the addressed code or data is not in the

cache, the cycle is forwarded to main memory.

For the write-through (82434LX only) and write-back

(both 82434LX and 82434NX) policies, the cache

operation is determined by the CPU read or write

cycle as follows:

Write Cycle

If the caching policy is write-through and the write

cycle hits in the cache, both the cache and main

memory are updated. Upon a cache miss, only

main memory is updated. The cache is not updated (no write-allocate).

If the caching policy is write-back and the write

cycle hits in the cache, only the cache is updated;

main memory is not affected. Upon a cache miss,

only main memory is updated. The cache is not

updated (no write-allocate).

Read Cycle

Upon a cache hit, the cache operation is the same

for both write-through and write-back. In this case,

data is transferred from the cache to the CPU.

Main memory is not accessed.

290479– 4

Figure 3. Second Level Cache Organization

14

82434LX/82434NX

If the read cycle causes a cache miss, the line

containing the requested data is transferred from

main memory to the cache and to the CPU. In the

case of a write-back cache, if the cache line fill is

to a sector containing one or more modified lines,

the modified lines are written back to main memory

and the new line is brought into the cache. For a

modified line write-back operation, the PCMC

transfers the modified cache lines to main memory

via a write buffer in the LBX. Before writing the last

modified line from the write buffer to main memory,

the PCMC updates the first and second level

caches with the new line, allowing the CPU access

to the requested data with minimum latency.

1.2.1.1 Cache Consistency

The Snoop mechanism in the PCMC ensures data

consistency between cache (both first level and second level) and main memory. The PCMC monitors

PCI master accesses to main memory and when

needed, initiates an inquire (snoop) cycle to the first

and second level caches. The snoop mechanism

guarantees that consistent data is always delivered

to both the host CPU and PCI masters.

1.2.2 ADDRESS/DATA PATHS

Address paths between the CPU/cache and PCI

and data paths between the CPU/cache, PCI, and

main memory are supplied by two LBX components.

The LBX is a companion component to the PCMC.

Together, they form a Host/PCI bridge. The PCMC

(via the PCMC/LBX interface signals), controls the

address and data flow through the LBXs. Refer to

the LBX data sheet for more details on the address

and data paths.

Data is transferred to and from the PCMC internal

registers via the PCMC address lines. When the

Host CPU performs a write operation, the data is

sent to the LBXs. When the PCMC decodes the cycle as an access to one of its internal registers, it

asserts AHOLD to the CPU and instructs the LBXs

to copy the data onto the Host address lines. When

the PCMC decodes a Host read as an access to a

PCMC internal register, it asserts AHOLD to the

CPU. The PCMC then places the register data on its

address lines and instructs the LBX to copy the data

on the Host address bus to the Host data bus. When

the register data is on the Host data bus, the PCMC

negates AHOLD and completes the cycle.

1.2.2.1 Read/Write Buffers

The LBX provides an interface for the CPU address

and data buses, PCI Address/Data bus, and the

main memory DRAM data bus. There are three posted write buffers and one read-prefetch buffers implemented in the LBXs to increase performance and to

maximize concurrency. The buffers are:

#

CPU-to-Main Memory Posted Write Buffer

(4 Qwords)

#

CPU-to-PCI Posted Write Buffer (4 Dwords)

#

PCI-to-Main Memory Posted Write Buffer (2 x 4

Dwords)

#

PCI-to-Main Memory Read Prefetch Buffer (line

buffer, 4 Qwords).

Refer to the LBX data sheet for details on the operation of these buffers.

1.2.3 HOST/PCI BRIDGE OPERATIONS

The PCMC permits the Host CPU to access devices

on the PCI Bus. These accesses can be to PCI I/O

space, PCI memory space, or PCI configuration

space.

As a PCI device, the PCMC can be either a master

initiating a PCI Bus operation or a target responding

to a PCI Bus operation. The PCMC is a PCI Bus

master for Host-to-PCI cycles and a target for PCIto-main memory transfers. Note that the PCMC does

not permit peripherals to be located on the Host

Bus. CPU I/O cycles, other than to PCMC internal

registers, are forwarded to the PCI Bus and PCI Bus

accesses to the Host Bus are not supported.

When the CPU initiates a bus cycle to a PCI device,

the PCMC becomes a PCI Bus master and translates the CPU cycle into the appropriate PCI Bus

cycle. The Host/PCI Posted write buffer in the LBXs

permits the CPU to complete CPU-to-PCI Dword

memory writes in three CPU clocks (1 wait-state),

even if the PCI Bus is currently busy. The posted

data is written to the PCI device when the PCI Bus is

available.

When a PCI Bus master initiates a main memory access, the PCMC (and LBXs) become the target of

the PCI Bus cycle and responds to the read/write

access. During PCI-to-main memory accesses, the

PCMC automatically performs cache snoop operations on the Host Bus, when needed, to maintain

data consistency.

15

82434LX/82434NX

As a PCI device, the PCMC contains all of the required PCI configuration registers. The Host CPU

reads and writes these registers as described in

Section 3.0, Register Description.

1.2.4 DRAM MEMORY OPERATIONS

The PCMC contains a DRAM controller that supports CPU and PCI master accesses to main memory. The PCMC DRAM interface supplies the control

signals and address lines and the LBXs supply the

data path. DRAM parity is generated for main memory writes and checked for memory reads.

For the 82434LX, the memory array is 64-bits wide

and ranges in size from 2 MBytes– 192 MBytes. The

array can be implemented with either single-sided or

double-sided SIMMs. DRAM SIMM sizes of 256K x

36, 1M x 36, and 4M x 36 are supported.

For the 82434NX, the memory array is 64-bits wide

and ranges in size from 2 MBytes– 512 MBytes. The

array can be implemented with either single-sided or

double-sided SIMMs. DRAM SIMM sizes of 256K x

36, 1M x 36, 4M x 36, and 16M x 36 are supported.

To provide optimum support for the various cache

configurations, and the resultant mix of bus cycles,

the system designer can select between 0-active

RAS

Ý

and 1-active RASÝmodes. These modes af-

fect the behavior of the RAS

Ý

signal following either

CPU-to-main memory cycles or PCI-to-main memory

cycles.

The PCMC also provides programmable memory

and cacheability attributes on 14 memory segments

of various sizes in the ISA compatibility range

(512 KByte – 1 MByte address range). Access rights

to these memory segments from the PCI Bus are

controlled by the expansion bus bridge.

The PCMC permits a gap to be created in main

memory within the 1 MByte – 16 MBytes address

range, accommodating ISA devices which are

mapped into this range (e.g., ISA LAN card or an ISA

frame buffer).

1.2.5 3.3V SIGNALS

The 82434NX PCMC drives 3.3V signal levels on the

CPU and second level cache interfaces. Thus, no

extra logic (i.e. 5V/3.3V translation) is required when

interfacing to 3.3V processors and SRAMs. Six of

the power pins on the 82434NX are VDD3 pins.

These pins are connected to a 3.3V power supply.

The VDD3 pins power the output buffers on the CPU

and second level cache interfaces. The VDD3 pins

also power the output buffers for the HCLK[A-F

]

outputs.

2.0 SIGNAL DESCRIPTIONS

This section provides a detailed description of each

signal. The signals are arranged in functional groups

according to their associated interface. The states of

all of the signals during hard reset are provided in

Section 8.0, System Clocking and Reset.

The ‘‘

Ý

’’ symbol at the end of a signal name indicates that the active, or asserted state occurs when

the signal is at a low voltage level. When ‘‘

Ý

’’ is not

present after the signal name, the signal is asserted

when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working

with a mixture of ‘‘active-low’’ and ‘‘active-high’’ signals. The term assert,orassertion indicates that a

signal is active, independent of whether that level is

represented by a high or low voltage. The term ne-

gate,ornegation indicates that a signal is inactive.

The following notations are used to describe the signal type.

in Input is a standard input-only signal

out Totem pole output is a standard active driver

o/d Open drain

t/s Tri-State is a bi-directional, tri-state input/out-

put pin

s/t/s Sustained tri-state is an active low tri-state sig-

nal owned and driven by one and only one

agent at a time. The agent that drives a s/t/s

pin low must drive it high for at least one clock

before letting it float. A new agent can not

start driving a s/t/s signal any sooner than

one clock after the previous owner tri-states it.

An external pull-up is required to sustain the

inactive state until another agent drives it and

must be provided by the central resource.

16

82434LX/82434NX

2.1 Host Interface

Signal Type Description

A[31:0]t/s ADDRESS BUS: A[31:0]are the address lines of the Host Bus. A[31:3]are connected to

the CPU A[31:3]lines and to the LBXs. A[2:0]are only connected to the LBXs. Along with

the byte enable signals, the A[31:3]lines define the physical area of memory or I/O being

accessed. During CPU cycles, the A[31:3]lines are inputs to the PCMC. They are used for

address decoding and second level cache tag lookup sequences. Also during CPU cycles,

A[2:0]are outputs and are generated from BE[7:0

]

Ý

.A[27:24]provide hardware

strapping options for test features. For more details on theses options, refer to Section

11.0 Testability.

During inquire cycles, A[31:5]are inputs from the LBXs to the CPU and the PCMC to

snoop the first and the second level cache tags, respectively. In response to a Flush or

Flush Acknowledge Special Cycle, the PCMC asserts AHOLD and drives the addresses of

the second level cache lines to be written back to main memory on A[18:7].

During CPU to PCI configuration cycles, the PCMC drives A[31:0]with the PCI

configuration space address that is internally derived from the CPU physical I/O address.

All PCMC internal configuration registers are accessed via A[31:0]. During CPU reads

from PCMC internal configuration registers, the PCMC asserts AHOLD and drives the

contents of the addressed register on A[31:0]. The PCMC then signals the LBXs to copy

this value from the address lines onto the host data lines. During writes to PCMC internal

configuration registers, the PCMC asserts AHOLD and signals the LBXs to copy the write

data onto the A[31:0]lines.

Finally, when in deturbo mode, the PCMC periodically asserts AHOLD and then drives

A[31:0]to valid logic levels to keep these lines from floating for an extended period of

time.

A[31:28]provide hardware strapping options at powerup. For more details on strapping

options, refer to Section 8.0, System Clocking and Reset. A[27:24]provide hardware

strapping options for test features. For more details on these options, refer to Section

11.0 Testability.

17

82434LX/82434NX

Signal Type Description

BE[7:0

]

Ý

in BYTE ENABLES: The byte enables indicate which byte lanes on the CPU data bus

carry valid data during the current bus cycle. In the case of cacheable reads, all 8 bytes

of data are driven to the Pentium processor, regardless of the state of the byte enables.

The byte enable signals indicate the type of special cycle when M/IO

Ý

e

D/C

Ý

e

0 and

W/R

Ý

e

1. During special cycles, only one byte enable is asserted by the CPU. The

following table depicts the special cycle types and their byte enable encodings:

Special Cycle Type Asserted Byte Enable

Shutdown BE0

Ý

Flush BE1

Ý

Halt/Stop Grant BE2

Ý

Write Back BE3

Ý

Flush Acknowledge BE4

Ý

Branch Trace Message BE5

Ý

When the PCMC decodes a Shutdown Special Cycle, it asserts AHOLD, drives

000...000 (the PCI Shutdown Special Cycle Encoding) on the A[31:0]lines and signals

the LBXs to latch the host address bus. The PCMC then drives a Special Cycle on PCI,

signaling the LBXs to drive the latched address (00...00) on the AD[31:0]lines during

the data phase. The PCMC then asserts INIT for 16 HCLKs.

In response to Flush and Flush Acknowledge Special Cycles, the PCMC internally

inspects the Valid and Modified bits for each of the Second Level Cache Sectors. If a

line is both valid and modified, the PCMC drives the cache address of the line on the

A[18:7]and CAA/CAB[6:3]lines and writes the line back to main memory. The valid

and modified bits are both reset to 0. All valid and unmodified lines are simply marked

invalid.

In response to a write back special cycle, the PCMC simply returns BRDY

Ý

to the CPU.

The second level cache will be written back to main memory in response to the

following flush special cycle.

If BE2Ýis asserted during a special cycle, the 82434NX uses A4 to determine if the

cycle is a Halt or Stop Grant Special Cycle. If A4

e

0, the cycle is a Halt Special Cycle

and if A4

e

1, the cycle is a Stop Grant Special cycle.

In response to a halt special cycle, the PCMC asserts AHOLD, drives 000...001 (the PCI

halt special cycle encoding) on the A[31:0]lines, and signals the LBXs to latch the host

address bus. The PCMC then drives a special cycle on PCI, signaling the LBXs to drive

the latched address (00...01) on the AD[31:0]lines during the data phase.

When the 82434NX PCMC detects a CPU Stop Grant Special Cycle (M/IO

Ý

e

0,

D/C

Ý

e

0, W/R

Ý

e

1, A4e1, BE[7:0

]

Ý

e

FBh), it generates a PCI Stop Grant Special

cycle, with 0002h in the message field (AD[15:0]) and 0012h in the message dependent

data field (AD[31:16]) during the first data phase (IRDY

Ý

asserted).

ADS

Ý

in ADDRESS STROBE: The Pentium processor asserts ADSÝto indicate that a new bus

cycle is beginning. ADS

Ý

is driven active in the same clock as the address, byte enable,

and cycle definition signals. The PCMC ignores a floating low ADSÝthat may occur

when BOFF

Ý

is asserted as the CPU is asserting ADSÝ.

18

82434LX/82434NX

Signal Type Description

BRDYÝout BURST READY: BRDYÝindicates that the system has responded in one of three ways:

1. valid data has been placed on the Pentium processor data pins in response to a read,

2. CPU write data has been accepted by the system, or

3. the system has responded to a special cycle.

NA

Ý

out NEXT ADDRESS: The PCMC asserts NAÝfor one clock when the memory system is

ready to accept a new address from the CPU, even if all data transfers for the current

cycle have not completed. The CPU may drive out a pending cycle two clocks after NA

Ý

is asserted and has the ability to support up to two outstanding bus cycles.

AHOLD out ADDRESS HOLD: The PCMC asserts AHOLD to force the Pentium processor to stop

driving the address bus so that either the PCMC or LBXs can drive the bus. During PCI

master cycles, AHOLD is asserted to allow the LBXs to drive a snoop address onto the

address bus. If the PCI master locks main memory, AHOLD remains asserted until the

PCI master locked sequence is complete and the PCI master negates PLOCKÝ.

AHOLD is asserted during all accesses to PCMC internal configuration registers to allow

configuration register accesses to occur over the A[31:0]lines.

When in deturbo mode, the PCMC periodically asserts AHOLD to prevent the processor

from initiating bus cycles in order to emulate a slower system. The duration of AHOLD

assertion in deturbo mode is controlled by the Deturbo Frequency Control Register

(offset 51h). When PWROK is negated, the PCMC asserts AHOLD to allow the strapping

options on A[31:28]to be read. For more details on strapping options, see the System

Clocking and Reset section.

EADSÝout EXTERNAL ADDRESS STROBE: The PCMC asserts EADSÝto indicate to the Pentium

processor that a valid snoop address has been driven onto the CPU address lines to

perform an inquire cycle. During PCI master cycles, the PCMC signals the LBXs to drive a

snoop address onto the host address lines and then asserts EADS

Ý

to cause the CPU to

sample the snoop address.

INV out INVALIDATE: The INV signal specifies the final state (invalid or shared) that a first level

cache line transitions to in the event of a cache line hit during a snoop cycle. When

snooping the caches during a PCI master write, the PCMC asserts INV with EADS

Ý

.

When INV is asserted with EADS

Ý

, an inquire hit results in the line being invalidated.

When snooping the caches during a PCI master read, the PCMC does not assert INV with

EADS

Ý

. In this case, an inquire cycle hit results in a line transitioning to the shared state.

BOFF

Ý

out BACKOFF: The PCMC asserts BOFFÝto force the Pentium processor to abort all

outstanding bus cycles that have not been completed and float its bus in the next clock.

The PCMC uses this signal to force the CPU to re-order a write-back due to a snoop cycle

around a currently outstanding bus cycle. The PCMC also asserts BOFF

Ý

to obtain the

CPU data bus for write-back cycles from the secondary cache due to a snoop hit. The

CPU remains in bus hold until BOFF

Ý

is negated.

HITM

Ý

in HIT MODIFIED: The Pentium processor asserts HITMÝto inform the PCMC that the

current inquire cycle hit a modified line. HITM

Ý

is asserted by the Pentium processor two

clocks after the assertion of EADS

Ý

if the inquire cycle hits a modified line in the primary

cache.

19

82434LX/82434NX

Signal Type Description

M/IO

Ý

in BUS CYCLE DEFINITION (MEMORY/INPUT-OUTPUT, DATA/CONTROL, WRITE/

READ): M/IO, D/C

Ý

and W/RÝdefine Host Bus cycles as shown in the table below.

D/C

Ý

W/R

Ý

M/IOÝD/CÝW/RÝBus Cycle Type

Low Low Low Interrupt Acknowledge

Low Low High Special Cycle

Low High Low I/O Read

Low High High I/O Write

High Low Low Code Read

High Low High Reserved

High High Low Memory Read

High High High Memory Write

Interrupt acknowledge cycles are forwarded to the PCI Bus as PCI interrupt

acknowledge cycles (i.e. C/BE[3:0

]

Ý

e

0000 during the address phase). All I/O cycles

and any memory cycles that are not directed to memory controlled by the PCMC DRAM

controller are forwarded to PCI. The Pentium processor generates six different types of

special cycles. The special cycle type is encoded on the BE[7:0

]

Ý

lines.

HLOCK

Ý

in HOST BUS LOCK: The Pentium processor asserts HLOCKÝto indicate the current bus

cycle is locked. HLOCK

Ý

is asserted in the first clock of the first locked bus cycle and is

negated after the BRDYÝis returned for the last locked bus cycle. The Pentium

processor guarantees HLOCK

Ý

to be negated for at least one clock between back-toback locked operations. When a CPU locked cycle is directed to main memory, the

PCMC guarantees that once the locked operation begins in main memory, the CPU has

exclusive access to main memory (i.e., PCI master accesses to main memory will not be

initiated until the CPU locked operation completes). When a CPU locked cycle is

directed to PCI, the PCMC arbitrates for PLOCK

Ý

(PCI LOCKÝ) before initiating the

cycle on PCI, except when the cycle is to the memory range defined by the Frame

Buffer Range Register and the No Lock Requests bit in that register is set to 1.

CACHE

Ý

in CACHEABILITY: The Pentium processor asserts CACHEÝto indicate the internal

cacheability of a read cycle or that a write cycle is a burst write-back cycle. If the CPU

drives CACHE

Ý

inactive during a read cycle, the returned data is not cached,

regardless of the state of KEN

Ý

. The CPU asserts CACHEÝfor cacheable data reads,

cacheable code fetches, and cache line write-backs. CACHE

Ý

is driven along with the

cycle definition pins.

KEN

Ý

out CACHE ENABLE: The PCMC asserts KENÝto indicate to the CPU that the current

cycle is cacheable. KEN

Ý

is asserted for all accesses to memory ranges 0–512-KBytes

and 1024-KBytes to the top of main memory controlled by the PCMC when the Primary

Cache Enable bit is set to 1, except in the following case: KEN

Ý

is not asserted for

accesses to the top 64-KByte of main memory controlled by the PCMC when the

SMRAM Enable bit in the DRAM Control Register (Offset 57h) is set to 1 and the area is

not write protected. If the area is write protected and cacheable, KEN

Ý

is asserted for

code read cycles, but is not asserted during data read cycle. KENÝis asserted for any

CPU access within the range of 512-KBytes–1024-KBytes if the corresponding Cache

Enable bit in the PAM[6:0]Registers (offsets 59h–5Fh) is set to 1. When the Pentium

processor indicates that the current read cycle can be cached by asserting CACHE

Ý

and the PCMC responds with KENÝ, the cycle is converted into a burst cache line fill.

The CPU samples KEN

Ý

with the first of either BRDYÝor NAÝ.

20

82434LX/82434NX

Signal Type Description

SMIACT

Ý

in SYSTEM MANAGEMENT INTERRUPT ACTIVE: The Pentium processor asserts

SMIACT

Ý

to indicate that the processor is operating in System Management Mode

(SMM). When the SMRAM Enable bit in the DRAM Control Register (offset 57h) is set

to 1, the PCMC allows CPU accesses SMRAM as permitted by the SMRAM Space

Register at configuration space offset 72h.

PEN

Ý

out PARITY ENABLE: The PENÝsignal, along with the MCE bit in CR4 of the Pentium

processor, determines whether a machine check exception will be taken by the CPU as

a result of a parity error on a read cycle. The PCMC asserts PEN

Ý

during DRAM read

cycles if the MCHK on DRAM/L2 Cache Data Parity Error Enable bit in the Error

Command Register (offset 70h) is set to 1. The PCMC asserts PEN

Ý

during CPU

second level cache read cycles if the MCHK on DRAM/L2 Cache Data Parity Error

Enable and the L2 Cache Parity Enable bits in the Error Command Register (offset 70h)

are both set to 1.

PCHK

Ý

in DATA PARITY CHECK: PCHKÝis sampled by the PCMC to detect parity errors on

CPU read cycles from main memory if the Parity Error Mask Enable bit in the DRAM

Control Register (offset 57h) is reset to 0. PCHK

Ý

is sampled by the PCMC to detect

parity errors on CPU read cycles from the second level cache if the L2 Cache Parity

Enable bit in the Error Command Register (offset 70h) is set to 1. If incorrect parity was

detected on a data read, the PCHK

Ý

signal is asserted by the Pentium processor two

clocks after BRDY

Ý

is returned. PCHKÝis asserted for one clock for each clock in

which a parity error was detected.

21

82434LX/82434NX

2.2 DRAM Interface

Signal Type Description

RAS[5:0

]

Ý

out ROW ADDRESS STROBES: The RAS[5:0

]

Ý

signals are used to latch the row

address on the MA[10:0]lines into the DRAMs. Each RAS[5:0

]

Ý

signal corresponds

to one DRAM row. The 82434LX PCMC supports up to 6 rows in the DRAM array.

Each row is eight bytes wide. These signals drive the RAS

Ý

lines of the DRAM array

directly, without external buffers.

RAS[7:6

]

Ý

out ROW ADDRESS STROBES: The 82434NX supports up to eight rows of DRAM.

RAS[7:6

]

Ý

are used with RAS[5:0]to latch the row address on the MA[11:0]lines

into the DRAMs. Each row is eight bytes wide. These signals drive the RAS

Ý

lines of

the DRAM array directly, without external buffers.

CAS[7:0

]

Ý

out COLUMN ADDRESS STROBES: The CAS[7:0

]

Ý

signals are used to latch the

column address on the MA[10:0]lines into the DRAMs. Each CAS[7:0

]

Ý

signal

corresponds to one byte of the eight byte-wide array. These signals drive the CAS

Ý

lines of the DRAM array directly, without external buffers. In a minimum configuration,

each CAS[7:0

]

Ý

line only has one SIMM load, while the maximum configuration has 6

SIMM loads.

WE

Ý

out DRAM WRITE ENABLE: WEÝis asserted during both CPU and PCI master writes to

main memory. During burst writes to main memory, WE

Ý

is asserted before the first

assertion of CAS[7:0

]

Ý

and is negated with the last CAS[7:0

]

Ý

. The WEÝsignal is

externally buffered to drive the WE

Ý

inputs on the DRAMs.

MA[10:0

]

out DRAM MULTIPLEXED ADDRESS: MA[10:0]provide the row and column address to

the DRAM array. The 82434LX uses MA[10:0]for the complete DRAM address bus.

The MA[10:0]lines are externally buffered to drive the multiplexed address lines of

the DRAM array.

MA11 out DRAM MULTIPLEXED ADDRESS: MA11 provides the extra addressability for the

16M x 36 SiMMs that are supported by the 82434NX. MA[11:0]provide the row and

column address to the DRAM array. Like MA[10:0], MA11 is externally buffered to

drive the multiplexed address lines of the DRAM array.

22

82434LX/82434NX

2.3 Cache Interface

Signal Type Description

CALE out CACHE ADDRESS LATCH ENABLE: CALE controls the external latch between the

host address lines and the cache address lines. CALE is asserted to open the

external latch, allowing the host address lines to propagate to the cache address

lines. CALE is negated to latch the cache address lines.

CADS[1:0

]

Ý

, out This signal pin has two functions, depending on the type of SRAMs used for the

second level cache.

CR/W[1:0

]

Ý

CACHE ADDRESS STROBE: CADS[1:0

]

Ý

are used with burst SRAMs. When

asserted, CADS[1:0

]

Ý

cause the burst SRAMs to latch the cache address on the

rising edge of HCLK. CADS[1:0

]

Ý

are glitch-free synchronous signals. CADS[1:0

]

Ý

functionality is selected by the SRAM type bit in the Secondary Cache Control

Register. Two copies of this signal are provided for timing reasons only.

CACHE READ/WRITE: CR/W

Ý

provide read/write control to the second level

cache when using asynchronous dual-byte select SRAMs. This functionality is

selected by the SRAM Type and Cache Byte Control Bits in the Secondary Cache

Control Register. The two copies of this signal are always driven to the same logic

level.

CADV[1:0

]

Ý

, out This signal pin has two functions. The Cache Chip Select function is only enabled

when the SRAM connectivity bit (bit 2) in the SCC Register is set to 1.

CCS[1:0

]

Ý

CACHE ADVANCE: CADV[1:0

]

Ý

are used with burst SRAMs to advance the

internal two bit address counter inside the SRAMs to the next address of the burst

sequence. Two copies of this signal are provided for timing reasons only. The two

copies are always driven to the same logic level.

CACHE CHIP SELECT: CCS[1:0

]

Ý

are used with asynchronous SRAMs to deselect the SRAMs, placing them in a low power standby mode. When the CPU runs

a halt or stop grant special cycle, the 82434NX negates CCS[1:0

]

Ý

, placing the

second level cache in a power saving mode. The PCMC then asserts CCS[1:0

]

Ý

(activating the SRAMs) when the CPU asserts ADSÝ.

When using burst SRAMs, only CCS1Ýimplements the CCSÝfunction. CADV0

Ý

retains the address advance function. CCS1Ýserve two purposes with burst

SRAMs: 1) It is used (along with CADS[1:0

]

Ý

) to place the SRAMs in a low power

standby mode. When the CPU runs a halt or stop grant special cycle, the 82434NX

negates CCS1

Ý

and asserts CADS[1:0

]

Ý

for one clock, placing the SRAMs in a

power saving mode. The PCMC then asserts CCS1

Ý

so that the next ADSÝfrom

the CPU places the SRAMs in an active mode. 2) CCS1

Ý

is used to block pipelined

cycles from the SRAMs when the SRAMs are servicing a cycle. After NA

Ý

is

asserted, the PCMC negates CCS1Ýpreventing the SRAMs from sampling a new

address. CCS1

Ý

is asserted again when the SRAMs have completed the current

cycle.

CAA[6:3

]

out CACHE ADDRESS[6:3]: CAA[6:3]and CAB[6:3]are connected to address lines

A[3:0]on the second level cache SRAMs. CAA[4:3]and CAB[4:3]are used with

CAB[6:3

]

standard SRAMs to advance through the burst sequence. CAA[6:5]and CAB[6:5

]

are used during second level cache write-back cycles to address the modified lines

within the addressed sector. Two copies of these signals are provided for timing

reasons only. The two copies are always driven to the same logic level.

23

82434LX/82434NX

Signal Type Description

COE[1:0

]

Ý

out CACHE OUTPUT ENABLE: COE[1:0

]

Ý

are asserted when data is to be read from

the second level cache and are negated at all other times. Two copies of this signal

are provided for timing reasons only. The two copies are always driven to the same

logic level.

CWE[7:0

]

Ý

, out This signal pin has two functions, depending on the type of SRAMs used for the

second level cache.

CBS[7:0

]

Ý

CACHE WRITE ENABLES: CWE[7:0

]

Ý

are asserted to write data to the second

level cache SRAMs on a byte-by-byte basis. CWE7

Ý

controls the most significant

byte while CWE0

Ý

controls the least significant byte. These signals are cache write

enables when using burst SRAMs (SRAM Type bit in SCC Register is 1) or when

using asynchronous SRAMs (SRAM Type bit in SCC Register is 0) and the Cache

Byte Control Bit is 1.

CACHE BYTE SELECTS: The CBS[7:0

]

Ý

lines provide byte control to the

secondary cache when using dual-byte select asynchronous SRAMs. These signals

are Cache Byte select lines when the SRAM Type and Cache Byte Control Bits in the

SCC Register are both 0.

2.4 PCI Interface

Signal Type Description

C/BE[3:0

]

Ý

t/s PCI BUS COMMAND AND BYTE ENABLES: C/BE[3:0

]

Ý

are driven by the current

bus master during the address phase of a PCI cycle to define the PCI command, and

during the data phase as the PCI byte enables. The PCI commands indicate the

current cycle type, and the PCI byte enables indicate which byte lanes carry

meaningful data. C/BE[3:0

]

Ý

are outputs of the PCMC during CPU cycles that are

directed to PCI. C/BE[3:0

]

Ý

are inputs when the PCMC acts as a slave. The

command encodings and types are listed below.

C/BE[3:0

]

Ý

Command

0000 Interrupt Acknowledge

0001 Special Cycle

0010 I/O Read

0011 I/O Write

0100 Reserved

0101 Reserved

0110 Memory Read

0111 Memory Write

1000 Reserved

1001 Reserved

1010 Configuration Read

1011 Configuration Write

1100 Memory Read Multiple

1101 Reserved

1110 Memory Read Line

1111 Memory Write and Invalidate

24

82434LX/82434NX

Signal Type Description

FRAMEÝs/t/s CYCLE FRAME: FRAMEÝis driven by the current bus master to indicate the

beginning and duration of an access. FRAME

Ý

is asserted to indicate that a bus

transaction is beginning. While FRAME

Ý

is asserted, data transfers continue. When

FRAME

Ý

is negated, the transaction is in the final data phase. FRAMEÝis an output

of the PCMC during CPU cycles which are directed to PCI. FRAME

Ý

is an input to the

PCMC when the PCMC acts as a slave.

IRDY

Ý

s/t/s INITIATOR READY: The assertion of IRDYÝindicates the current bus master’s ability

to complete the current data phase. IRDY

Ý

works in conjunction with TRDYÝto

indicate when data has been transferred. On PCI, data is transferred on each clock

that both IRDY

Ý

and TRDYÝare asserted. During read cycles, IRDYÝis used to

indicate that the master is prepared to accept data. During write cycles, IRDY

Ý

is used

to indicate that the master has driven valid data on the AD[31:0]lines. Wait states are

inserted until both IRDY

Ý

and TRDYÝare asserted together. IRDYÝis an output of

the PCMC when the PCMC is the PCI master. IRDYÝis an input to the PCMC when

the PCMC acts as a slave.

TRDY

Ý

s/t/s TARGET READY: TRDYÝindicates the target device’s ability to complete the current

data phase of the transaction. It is used in conjunction with IRDY

Ý

. A data phase is

completed on each clock that TRDY

Ý

and IRDYÝare both sampled asserted. During

read cycles, TRDY

Ý

indicates that valid data is present on AD[31:0]lines. During write

cycles, TRDY

Ý

indicates the target is prepared to accept data. Wait states are

inserted on the bus until both IRDY

Ý

and TRDYÝare asserted together. TRDYÝis an

output of the PCMC when the PCMC is the PCI slave. TRDYÝis an input to the PCMC

when the PCMC is a master.

DEVSELÝs/t/s DEVICE SELECT: When asserted, DEVSELÝindicates that the driving device has

decoded its address as the target of the current access. DEVSEL

Ý

is an output of the

PCMC when PCMC is a PCI slave and is derived from the MEMCS

Ý

input. MEMCS

Ý

is generated by the expansion bus bridge as a decode to the main memory address

space. During CPU-to-PCI cycles, DEVSEL

Ý

is an input. It is used to determine if any

device has responded to the current bus cycle, and to detect a target abort cycle.

Master-Abort termination results if no subtractive decode agent exists in the system,

and no one asserts DEVSEL

Ý

within a programmed number of clocks.

STOP

Ý

s/t/s STOP: STOPÝindicates that the current target is requesting the master to stop the

current transaction. This signal is used in conjunction with DEVSEL

Ý

to indicate

disconnect, target-abort, and retry cycles. When PCMC is acting as a master on PCI, if

STOP

Ý

is sampled active on a rising edge of PCLKIN, FRAMEÝis negated within a

maximum of 3 clock cycles. STOPÝmay be asserted by the PCMC in three cases. If a

PCI master attempts to access main memory when another PCI master has locked

main memory, the PCMC asserts STOP

Ý

to signal retry. The PCMC detects this

condition when sampling FRAME

Ý

and LOCKÝboth active during an address phase.

When a PCI master is reading from main memory, the PCMC asserts STOP

Ý

when the

burst cycle is about to cross a cache line boundary. When a PCI master is writing to

main memory, the PCMC asserts STOP

Ý

upon filling either of the two PCI-to-main

memory posted write buffers. Once asserted, STOP

Ý

remains asserted until FRAME

Ý

is negated.

25

82434LX/82434NX

Signal Type Description

PLOCK

Ý

s/t/s PCI LOCK: PLOCKÝis used to indicate an atomic operation that may require

multiple transactions to complete. PCI provides a mechanism referred to as

‘‘resource lock’’ in which only the target of the PCI transaction is locked. The

assertion of GNT

Ý

on PCI does not guarantee control of the PLOCKÝsignal.

Control of PLOCK

Ý

is obtained under its own protocol. When the PCMC is the PCI

slave, PLOCK

Ý

is sampled as an input on the rising edge of PCLKIN when FRAME

Ý

is sampled active. If PLOCKÝis sampled asserted, the PCMC enters into a locked

state and remains in the locked state until PLOCK

Ý

is sampled negated on a

following rising edge of PCLKIN, when FRAME

Ý

is sampled asserted.

REQ

Ý

out REQUEST: The PCMC asserts REQÝto indicate to the PCI bus arbiter that the

PCMC is requesting use of the PCI Bus in response to a CPU cycle directed to PCI.

GNT

Ý

in GRANT: When asserted, GNTÝindicates that access to the PCI Bus has been

granted to the PCMC by the PCI Bus arbiter.

MEMCS

Ý

in MAIN MEMORY CHIP SELECT: When asserted, MEMCSÝindicates to the PCMC

that a PCI master cycle is targeting main memory. MEMCS

Ý

is generated by the

expansion bus bridge. MEMCS

Ý

is sampled by the PCMC on the rising edge of

PCLKIN on the first and second cycle after FRAME

Ý

has been asserted.

FLSHREQ

Ý

in FLUSH REQUEST: When asserted, FLSHREQÝinstructs the PCMC to flush the

CPU-to-PCI posted write buffer in the LBXs and to disable further posting to this

buffer as long as FLSHREQÝremains active. The PCMC acknowledges completion

of the CPU-to-PCI write buffer flush operation by asserting MEMACK

Ý

. MEMACK

Ý

remains asserted until FLSHREQÝis negated. FLSHREQÝis driven by the

expansion bus bridge and is used to avoid deadlock conditions on the PCI Bus.

MEMREQ

Ý

in MEMORY REQUEST: When asserted, MEMREQÝinstructs the PCMC to flush the

CPU-to-PCI and CPU-to-main memory posted write buffers and to disable posting in

these buffers as long as MEMREQ

Ý

is active. The PCMC acknowledges completion

of the flush operations by asserting MEMACK

Ý

. MEMACKÝremains asserted until

MEMREQÝis negated. MEMREQÝis driven by the expansion bus bridge.

MEMACK

Ý

out MEMORY ACKNOWLEDGE: When asserted, MEMACKÝindicates the completion

of the operations requested by an active FLSHREQ

Ý

and/or MEMREQÝ.

PAR t/s PARITY: PAR is an even parity bit across the AD[31:0]and C/BE[3:0

]

Ý

lines. Parity

is generated on all PCI transactions. As a master, the PCMC generates even parity

on CPU writes to PCI, based on the PPOUT[1:0]inputs from the LBXs. During CPU

read cycles from PCI, the PCMC checks parity by checking the value sampled on the

PAR input with the PPOUT[1:0]inputs from the LBXs. As a slave, the PCMC

generates even parity on PAR, based on the PPOUT[1:0]inputs during PCI master

reads from main memory. During PCI master writes to main memory, the PCMC

checks parity by checking the value sampled on PAR with the PPOUT[1:0]inputs.

26

82434LX/82434NX

Signal Type Description

PERRÝs/t/s PARITY ERROR: PERRÝmay be pulsed by any agent that detects a parity error during

an address phase, or by the master or the selected target during any data phase in which

the AD lines are inputs. The PERR

Ý

signal is enabled when the PERRÝon Receiving

Data Parity Error bit in the Error Command Register (offset 70h) and the Parity Error

Enable bit in the PCI Command Register (offset 04h) are both set to 1.

When enabled, CPU-to-PCI write data is checked for parity errors by sampling the

PERR

Ý

signal two PCI clocks after data is driven. Also, when enabled, PERRÝis

asserted by the PCMC when it detects a data parity error on CPU read data from PCI and

PCI master write data to main memory. PERR

Ý

is neither sampled nor driven by the

PCMC when either the PERR

Ý

on Receiving Data Parity Error bit in the Error Command

Register or the Parity Error Enable bit in the PCI Command Register is reset to 0.

SERRÝo/d SYSTEM ERROR: SERRÝmay be pulsed by any agent for reporting errors other than

parity. SERR

Ý

is asserted by the PCMC whenever a serious system error (not

necessarily a PCI error) occurs. The intent is to have the PCI central agent (for example,

the expansion bus bridge) assert NMI to the processor. Control over the SERR

Ý

signal is

provided via the Error Command Register (offset 70h) when the Parity Error Enable bit in

the PCI Command Register (offset 04h) is set to 1. When the SERR

Ý

DRAM/L2 Cache

Data Parity Error bit is set to 1, SERR

Ý

is asserted upon detecting a parity error on CPU

read cycles from DRAM. If the L2 Cache Parity bit is also set to 1, SERR

Ý

will be

asserted upon detecting a parity error on CPU read cycles from the second level cache.

The Pentium processor indicates these parity errors to the PCMC via the PCHK

Ý

signal.

When the SERRÝon PCI Address Parity Error bit is set to 1, the PCMC asserts SERRÝif

a parity error is detected during the address phase of a PCI master cycle.

When the SERR

Ý

on Received PCI Data Parity bit is set to 1, the PCMC asserts SERR

Ý

if a parity error is detected on PCI during a CPU read from PCI. During CPU to PCI write

cycles, when the SERR

Ý

on Transmitted PCI Data Parity Error bit is set to 1, the PCMC

asserts SERR

Ý

in response to sampling PERRÝactive. When the SERRÝon Received

Target Abort bit is set to 1, the PCMC asserts SERR

Ý

when the PCMC receives a target

abort on a PCMC initiated PCI cycle. If the Parity Error Enable bit in the PCI Command

Register is reset to 0, SERR

Ý

is disabled and is never asserted by the PCMC.

27

82434LX/82434NX

2.5 LBX Interface

Signal Type Description

HIG[4:0

]

out HOST INTERFACE GROUP: HIG[4:0]are outputs of the PCMC used to control the

LBX HA (Host Address) and HD (Host Data) buses. Commands driven on HIG[4:0

]

cause the host data and/or address lines to be either driven or latched by the LBXs.

See the 82433LX (LBX) Local Bus Accelerator Data Sheet for a listing of the

HIG[4:0]commands.

MIG[2:0

]

out MEMORY INTERFACE GROUP: MIG[2:0]are outputs of the PCMC and control the

LBX MD (Memory Data) bus. Commands driven on the MIG[2:0]lines cause the

memory data lines to be either driven or latched by the LBXs. See the 82433LX (LBX)

Local Bus Accelerator Data Sheet for a listing of the MIG[2:0]commands.

MDLE out MEMORY DATA LATCH ENABLE: During CPU reads from main memory, MDLE is

used to control the latching of memory read data on the CPU data bus. MDLE is

negated as CAS[7:0

]

Ý

are negated to close the latch between the memory data bus

and the host data bus. During CPU reads from main memory, the PCMC closes the

memory data to host data latch in the LBXs as BRDYÝis asserted and opens the

latch after the CPU has sampled the data.

PIG[3:0

]

out PCI INTERFACE GROUP: PIG[3:0]are outputs of the PCMC used to control the LBX

AD (PCI Address/Data) bus. Commands driven on the PIG[3:0]lines cause the AD

lines to be either driven or latched. See the 82433LX (LBX) Local Bus Accelerator

Data Sheet for a listing of the PIG[3:0]commands.

DRVPCI out DRIVE PCI: DRVPCI acts as an output enable for the LBX AD lines. When sampled

asserted, the LBXs begin driving the PCI AD lines. When negated, the AD lines on