Intel Corporation SB82378ZB, SB82379AB Datasheet

E

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of

any patent or copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor

variations to this specification known as errata. Other brands and names are the property of their respective owners.

© INTEL CORPORATION 1996 March 1996 Order Number: 290571-001

Provides the Bridge Between the PCI

Bus and ISA Bus

100% PCI and ISA Compatible

PCI and ISA Master/Slave Interface

Directly Drives 10 PCI Loads and 6

ISA Slots

PCI at 25 MHz and 33 MHz

ISA from 6 MHz to 8.33 MHz

Enhanced DMA Functions

Scatter/Gather (S/G) (82378ZB)

Fast DMA Type A, B and F (82378ZB)

Compatible DMA Transfers

32-bit Addressability(82378ZB)

27-bit Addressability(82379AB)

Seven Independently Programmable

Channels

Functionality of Two 82C37A DMA

Controllers

Data Buffers to Improve Performance

8-Byte DMA/ISA Master Line Buffer

32-bit Posted Memory Write Buffer to

ISA

Integrated 16-bit BIOS Timer

Non-Maskable Interrupts (NMI)

PCI System Errors

ISA Parity Errors

Arbitration for ISA Devices

ISA Masters

DMA and Refresh

Four Dedicated PCI Interrupts

Level Sensitive

Mapped to Any Unused Interrupt

Arbitration for PCI Devices

Six PCI Masters Supported

Fixed, Rotating, or a Combination

Utility Bus (X-Bus) Peripheral Support

Provides Chip Select Decode

Controls Lower X-Bus Data Byte

Transceiver

Functionality of One 82C54 Timer

System Timer

Refresh Request

Speaker Tone Output

Functionality of Two 82C59 Interrupt

Controllers

14 Interrupts Supported

Edge/Level Selectable Interrupts

I/O APIC (Advanced Programmable

Interrupt Controller (82379AB)

Support for Multi-Processor Systems

System Power Management (Intel SMM

Support)

Programmable System Management

Interrupt (SMI)

Hardware Events,

Software Events, EXTSMI#

Programmable CPU Clock Control

(STPCLK#)

Fast-On/Off Mode

208-Pin QFP Package

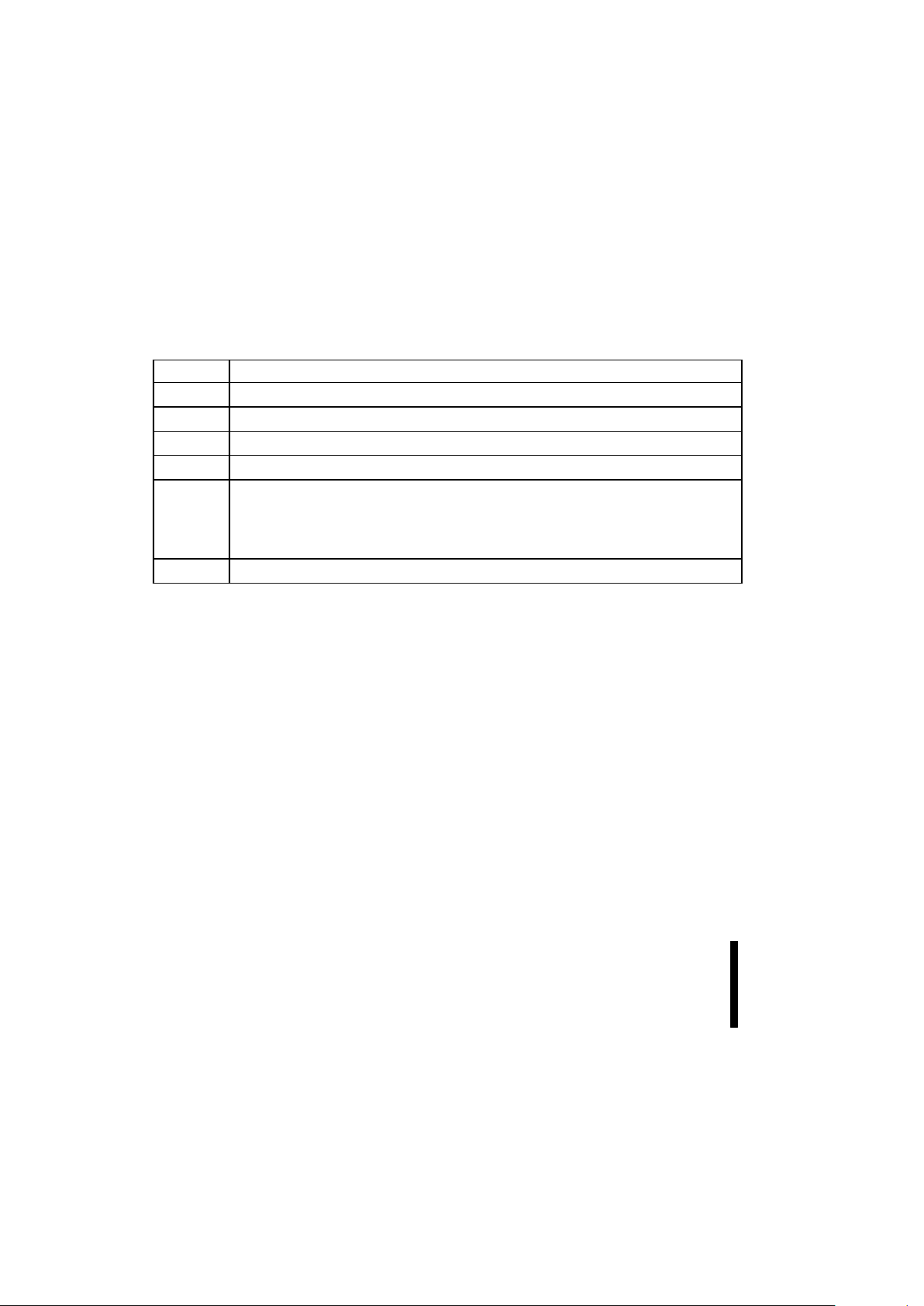

The 82378ZB System I/O (SIO) and 82379AB System I/O APIC (SIO.A) components are PCI-to-ISA Bus Bridge

devices. These devices integrate many of the common I/O functions found in today's ISA-based PC systems

a

seven channel DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, a BIOS timer, Intel SMM

power management support, and logic for NMI generation. In addition, the SIO and SIO.A each support a total of

six PCI Masters, and four PCI Interrupts. Decode is provided for peripheral devices such as the flash BIOS, real

time clock, keyboard/mouse controller, floppy controller, two serial ports, one parallel port, and IDE hard disk

drive.

For both the SIO and SIO.A, each DMA channel supports compatibility transfers. The SIO also supports types

A, B, and F transfers and scatter/gather. In addtion to the standard ISA-compatible interrupt controller that is in

both the SIO and SIO.A, the SIO.A contains an Advance Programmable Interrupt Controller (IO APIC) for use in

multi-processing systems.

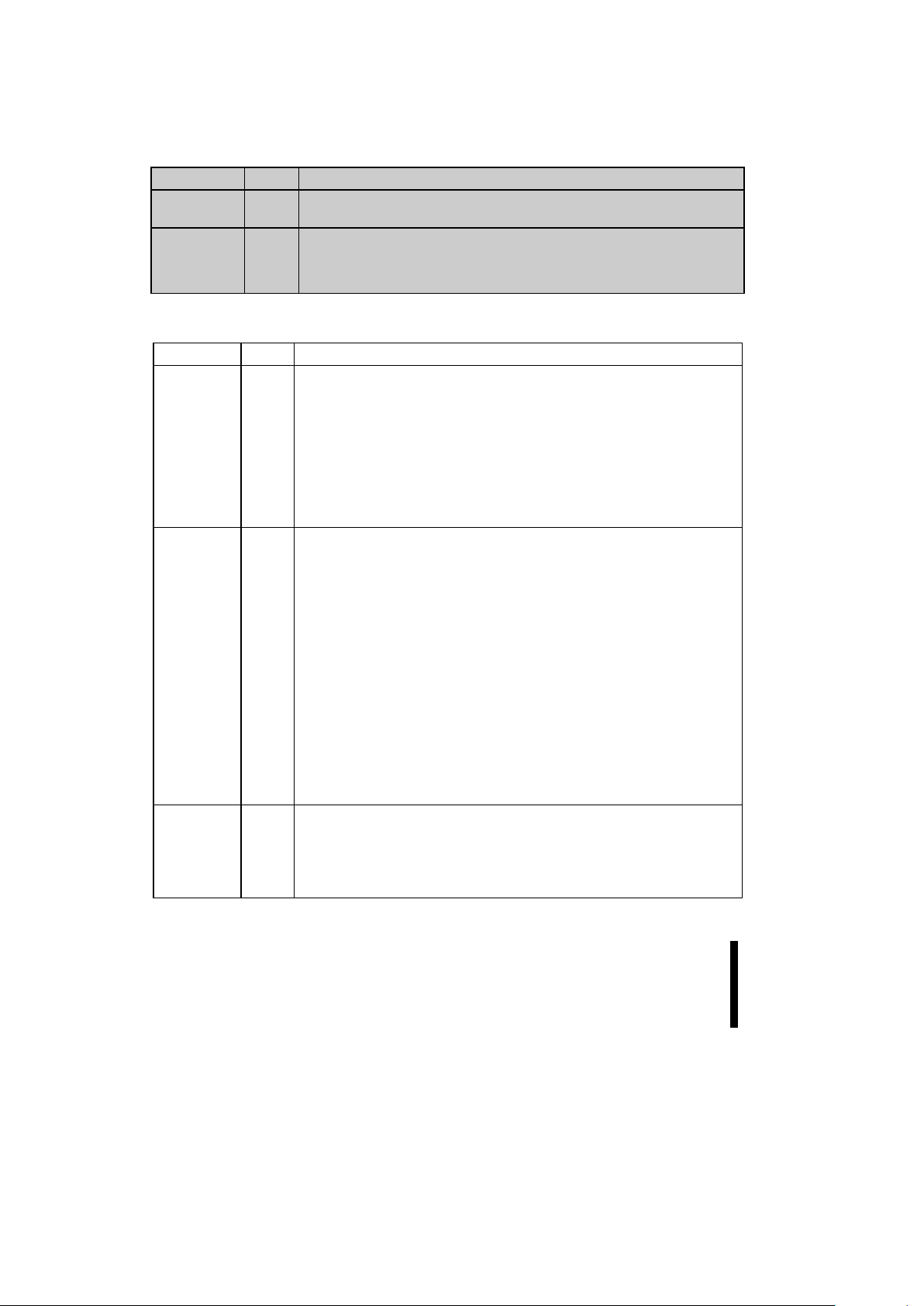

This document describes both the 82378ZB (SIO) and 82379AB (SIO.A) components. Unshaded areas describe

the 82378ZB. Shaded areas, like this one, describe differences between the 82379AB and 82378ZB.

82378ZB SYSTEM I/O (SIO) AND

82379AB SYSTEM I/O APIC (SIO.A)

82378ZB (SIO) AND 82379AB (SIO.A) E

2

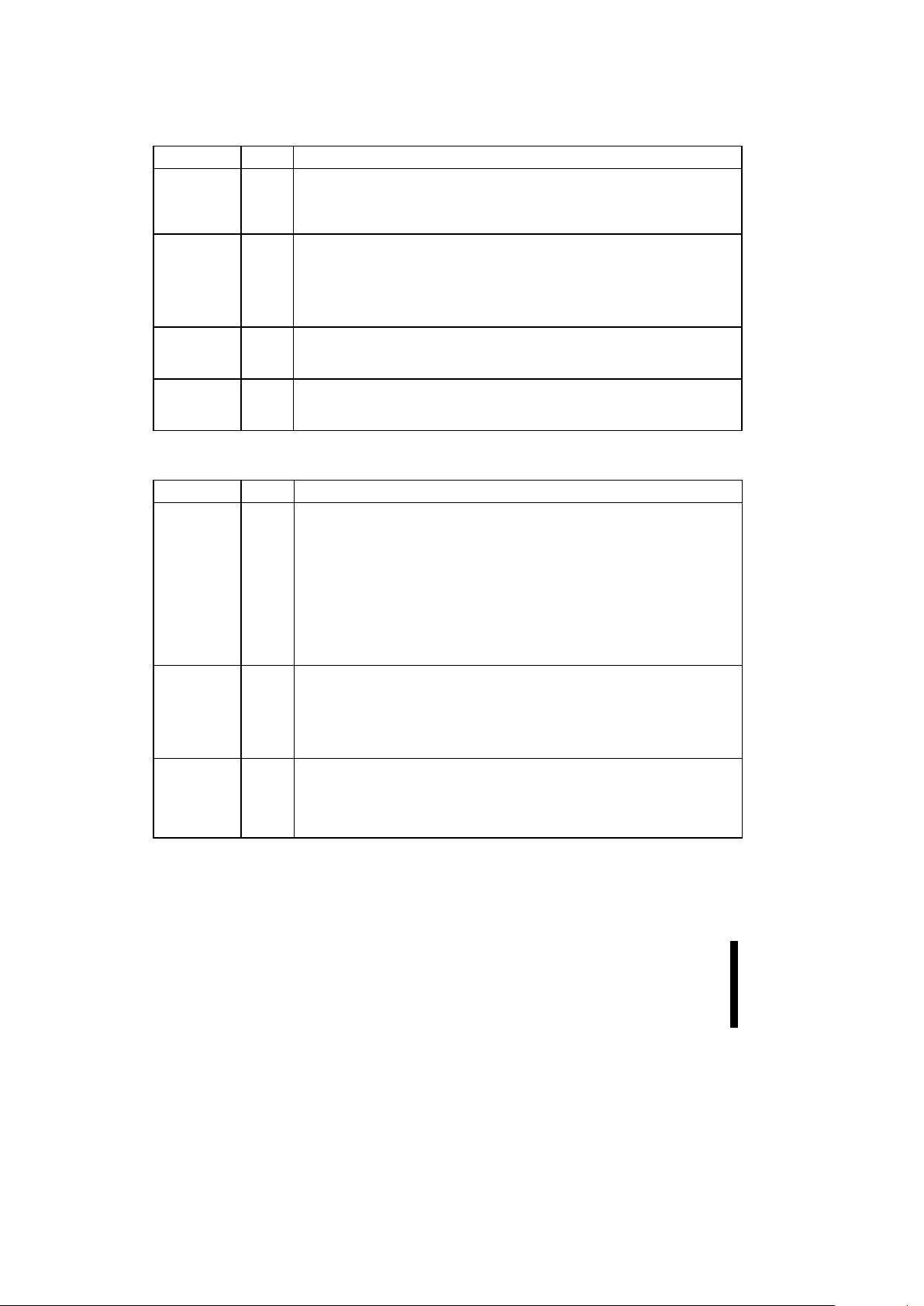

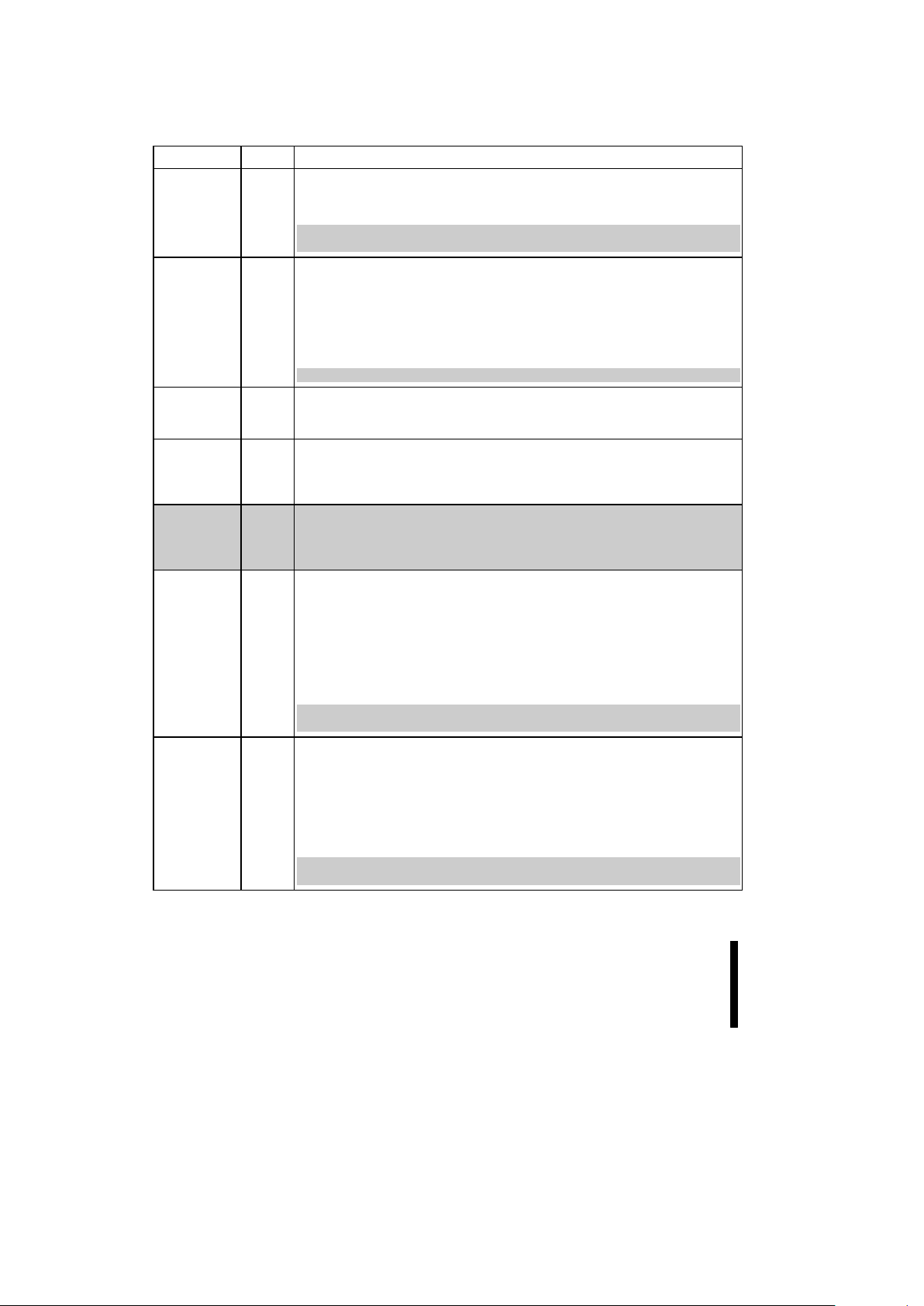

REQ0#/SIOGNT#

DREQ[7:5,3:0]

Data Buffers

PCI

Decode

ISA

Decode

PCI

Bus

Interface

ISA

Bus

Interface

PCI

Arbiter

Interrupt

Timers/

Counters

DMA

PCICLK

PCIRST#

AD[31:0]

C/BE#[3:0]

FRAME#

IRDY#

TRDY#

STOP#

LOCK#

DEVSEL#

SERR#

PAR

IDSEL

MEMCS#

REQ1#

CPUREQ#

GNT0#/SIOREQ#

GNT1#/RESUME#

CPUGNT#

MEMREQ#

MEMACK#

INT

NMI

IRQ[15,14,

11:9,7:3,1]

DA CK[7:5,3:0]#

TC (82379AB)

REFRESH#

SD[15:0]

SA[19:0]

LA[23:17]

IOCS16#

MEMCS16#

SBHE#

MASTER#

MEMR#

MEMW#

AEN

IOCHRDY

IOCHK#

SYSCLK

BALE

IOR#

IOW#

SMEMR#

SMEMW#

ZEROWS#

RSTDRV

SPKR/TESTO

UBUSTR

UBUSOE#

EC SAD D R[2:0]

ECSEN#

DSKCHG

ALT_RST#

ALT_A20

FERR#/IRQ13

IGNNE#

Utility

Bus

Support

Logic

OSC

FLSHREQ#

IRQ12/M

IRQ8#

Test

TEST

BIOS Timer

SPKR/TESTO

REQ[3:2]#

GNT[3:2]#

PIRQ[3:0]#

SMI#

STPCLK#

EXTSMI#

INIT

CPU

Interface

I/O

APIC

(8 2 37 9 AB

Only)

APICCLK

APICD[1:0]

EOP(82378ZB)

SIO_A_BK.DRW

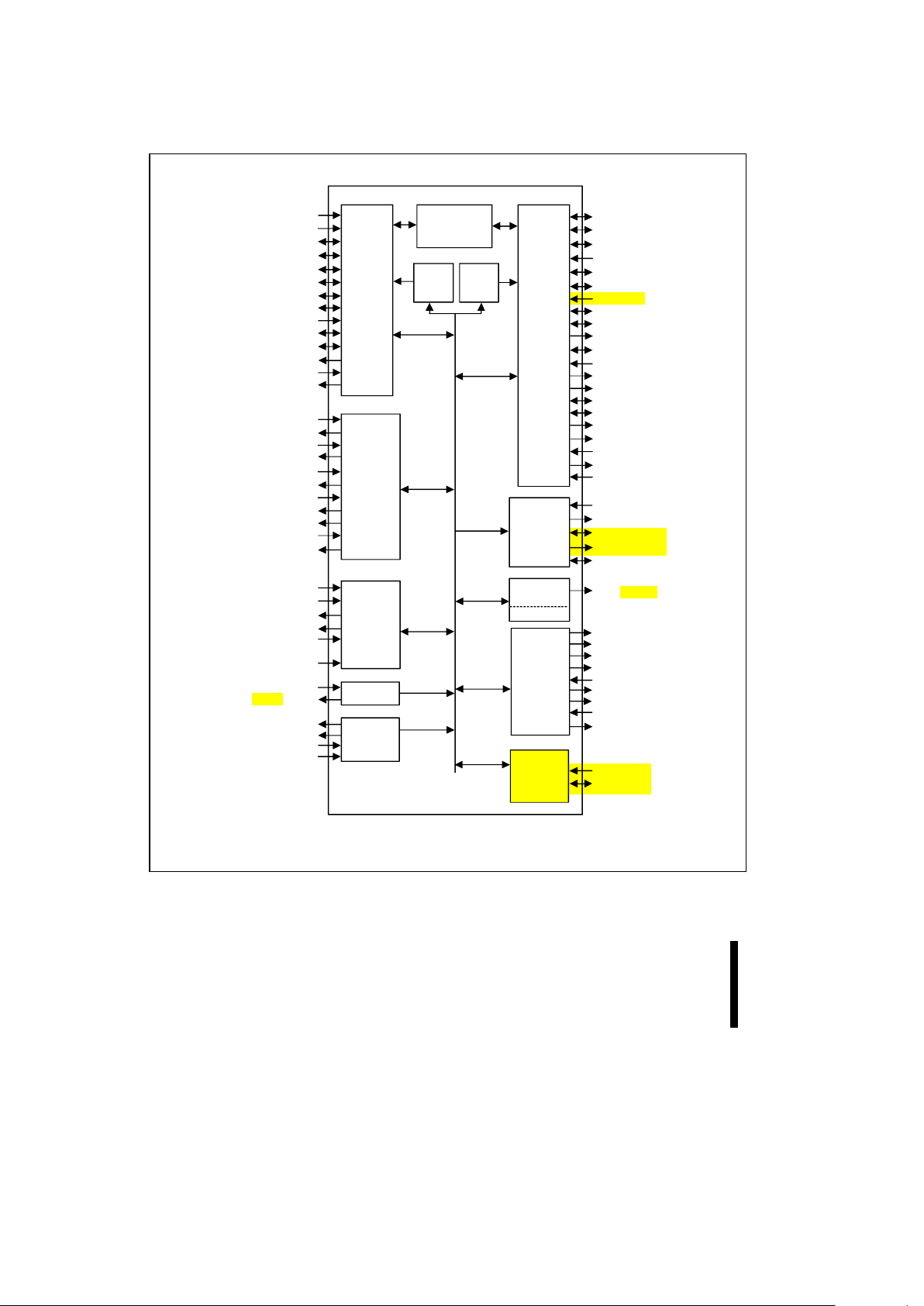

Note: I/O APIC signals are only on the 82379AB. Also, SPKR/TESTO are only multiplexed on the 82379AB and are separate

signals on the 82378ZB. The MASTER# signal is only on the 82378ZB.

82378ZB SIO and 82379AB SIO.A Component Block Diagram

E 82378ZB (SIO) AND 82379 (SIO.A)

3

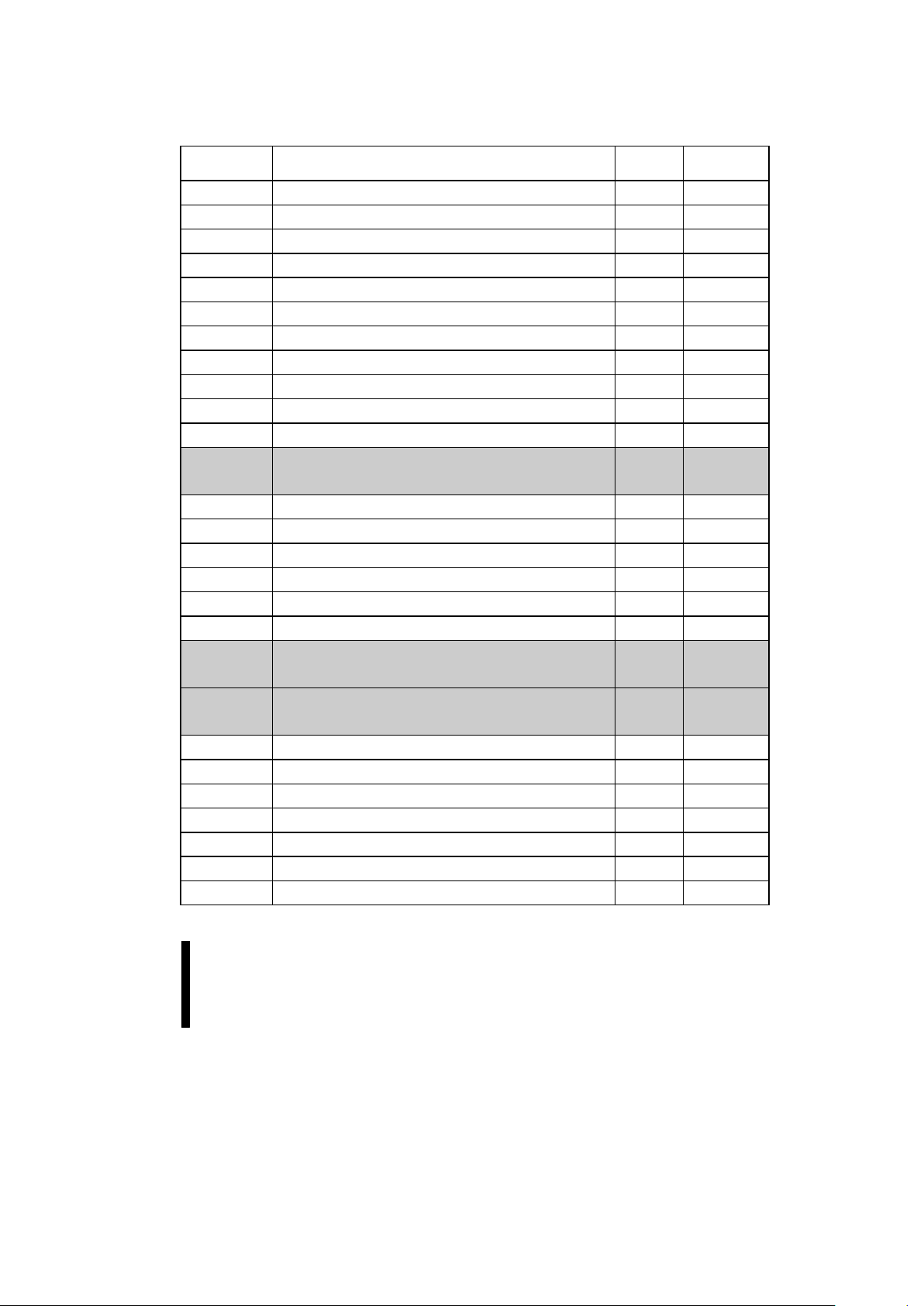

CONTENTS

PAGE

1.0. ARCHITECTURAL OVERVIEW....................................................................................................................9

2.0. SIGNAL DESCRIPTION................................................................................................ ...............................12

2.1. PCI BUS INTERFACE SIGNALS ................................ ................................ ................................ ............. 13

2.2. PCI ARBITER SIGNALS ................................ ................................ ................................ ........................... 14

2.3. ADDRESS DECODER SIGNAL ................................ ................................ ................................ ............... 16

2.4. POWER MANAGEMENT SIGNALS ................................ ................................ ................................ ........ 17

2.5. ISA INTERFACE SIGNALS ................................ ................................ ................................ ...................... 17

2.6. DMA SIGNALS ................................ ................................ ................................ ................................ .......... 19

2.7. TIMER SIGNAL ................................ ................................ ................................ ................................ ......... 20

2.8. INTERRUPT CONTROLLER SIGNALS ................................ ................................ ................................ ..21

2.9. APIC BUS SIGNALS (82379AB ONLY) ................................ ................................ ................................ .. 22

2.10. UTILITY BUS SIGNALS ................................ ................................ ................................ .......................... 22

2.11. TEST SIGNALS ................................ ................................ ................................ ................................ .......24

3.0. REGISTER DESCRIPTION..........................................................................................................................25

3.1. SIO CONFIGURATION REGISTER DESCRIPTION ................................ ................................ ............. 32

3.1.1. VID—VENDOR IDENTIFICATION REGISTER ................................ ................................ ............... 32

3.1.2. DID—DEVICE IDENTIFICATION REGISTER ................................ ................................ ................. 33

3.1.3. COM—COMMAND REGISTER ................................ ................................ ................................ ........ 33

3.1.4. DS—DEVICE STATUS REGISTER ................................ ................................ ................................ .34

3.1.5. RID—REVISION IDENTIFICATION REGISTER ................................ ................................ ............. 34

3.1.6. PCICON—PCI CONTROL REGISTER ................................ ................................ ............................ 35

3.1.7. PAC—PCI ARBITER CONTROL REGISTER ................................................................ ................. 36

3.1.8. PAPC—PCI ARBITER PRIORITY CONTROL REGISTER ................................ ............................ 37

3.1.9. ARBPRIX—PCI ARBITER PRIORITY CONTROL EXTENSION REGISTER ............................... 39

3.1.10. MCSCON-MEMCS# CONTROL REGISTER ................................ ................................ ................. 39

3.1.11. MCSBOH—MEMCS# BOTTOM OF HOLE REGISTER ................................ ............................... 40

3.1.12. MCSTOH—MEMCS# TOP OF HOLE REGISTER ................................ ................................ ........40

3.1.13. MCSTOM—MEMCS# TOP OF MEMORY REGISTER ................................ ................................ .41

3.1.14. IADCON—ISA ADDRESS DECODER CONTROL REGISTER ................................ ................... 41

3.1.15. IADRBE—ISA ADDRESS DECODER ROM BLOCK ENABLE REGISTER ............................... 42

3.1.16. IADBOH—ISA ADDRESS DECODER BOTTOM OF HOLE REGISTER ................................ ....42

3.1.17. IADTOH—ISA ADDRESS DECODER TOP OF HOLE REGISTER ................................ ............ 42

3.1.18. ICRT—ISA CONTROLLER RECOVERY TIMER REGISTER ................................ ..................... 43

3.1.19. ICD—ISA CLOCK DIVISOR REGISTER ................................ ................................ ....................... 44

3.1.20. UBCSA—UTILITY BUS CHIP SELECT A REGISTER ................................ ................................ . 45

3.1.21. UBCSB—UTILITY BUS CHIP SELECT B REGISTER ................................ ................................ . 46

3.1.22. MAR1—MEMCS# ATTRIBUTE REGISTER #1 ................................ ................................ ............ 47

82378ZB (SIO) AND 82379AB (SIO.A) E

4

3.1.23. MAR2—MEMCS# ATTRIBUTE REGISTER #2 ................................ ................................ ............. 47

3.1.24. MAR3—MEMCS# ATTRIBUTE REGISTER #3 ................................ ................................ ............. 48

3.1.25. PIRQ[3:0]#—PIRQ ROUTE CONTROL REGISTERS ................................ ................................ ...48

3.1.26. PACC—PIC/APIC CONFIGURATION CONTROL REGISTER (82379AB Only) ........................ 49

3.1.27. APICBASE—APIC BASE ADDRESS RELOCATION (82379AB Only) ................................ .......49

3.1.28. BIOS TIMER BASE ADDRESS REGISTER ................................ ................................ .................. 50

3.1.29. SMICNTL—SMI CONTROL REGISTER ................................ ................................ ........................ 50

3.1.30. SMIEN—SMI ENABLE REGISTER ................................ ................................ ................................ 51

3.1.31. SEE—SYSTEM EVENT ENABLE REGISTER ................................ ................................ .............. 51

3.1.32. FTMR—FAST OFF TIMER REGISTER ................................ ................................ ......................... 52

3.1.33. SMIREQ—SMI REQUEST REGISTER ................................ ................................ .......................... 53

3.1.34. CTLTMR—CLOCK SCALE STPCLK# LOW TIMER ................................ ................................ .....54

3.1.35. CTLTMRH—CLOCK SCALE STPCLK# HIGH TIMER ................................ ................................ .54

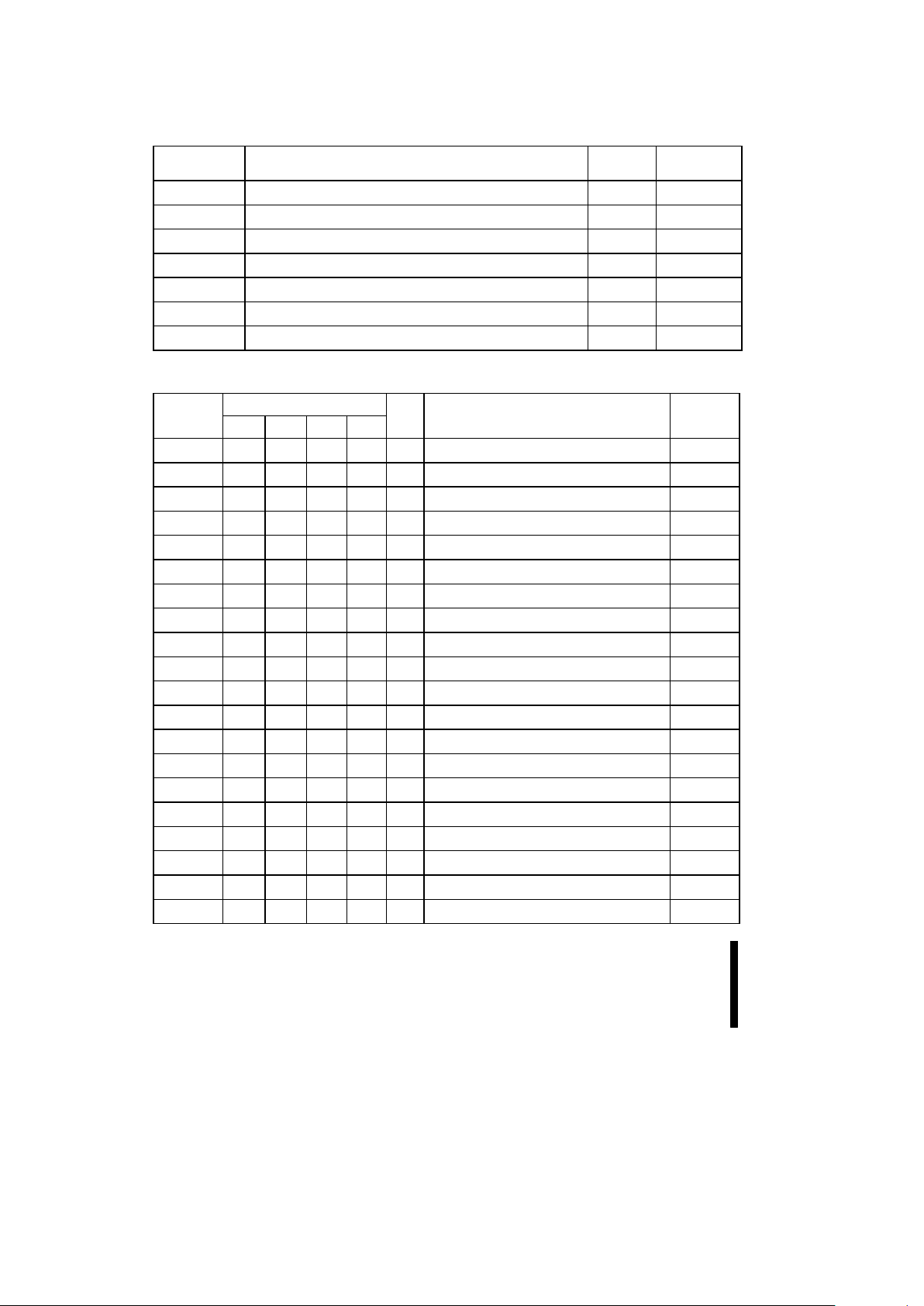

3.2. DMA REGISTER DESCRIPTION ................................ ................................ ................................ .............55

3.2.1. DCOM—DMA COMMAND REGISTER ................................ ................................ ............................ 55

3.2.2. DCM—DMA CHANNEL MODE REGISTER ................................ ................................ .................... 55

3.2.3. DCEM—DMA CHANNEL EXTENDED MODE REGISTER (82378ZB Only) ................................ 56

3.2.4. DR—DMA REQUEST REGISTER ................................ ................................ ................................ ....59

3.2.5. MASK REGISTER—WRITE SINGLE MASK BIT ................................ ................................ .............59

3.2.6. MASK REGISTER—WRITE ALL MASK BITS ................................ ................................ .................60

3.2.7. DS—DMA STATUS REGISTER ................................ ................................ ................................ .......60

3.2.8. DMA BASE AND CURRENT ADDRESS REGISTERS (8237 COMPATIBLE SEGMENT) .........61

3.2.9. DMA BASE AND CURRENT BYTE/WORD COUNT REGISTERS (8237 COMPATIBLE

SEGMENT)................................ ................................ ................................ ................................ ................61

3.2.10. DMA MEMORY BASE LOW PAGE AND CURRENT LOW PAGE REGISTERS ....................... 62

3.2.11. DMA MEMORY BASE HIGH PAGE AND CURRENT HIGH PAGE REGISTERS ...................... 62

3.2.12. DMA CLEAR BYTE POINTER REGISTER ................................ ................................ .................... 63

3.2.13. DMC—DMA MASTER CLEAR REGISTER ................................ ................................ ................... 64

3.2.14. DCM—DMA CLEAR MASK REGISTER ................................ ................................ ........................ 64

3.2.15. SCATTER/GATHER (S/G) COMMAND REGISTER (82378ZB Only) ................................ .........64

3.2.16. SCATTER/GATHER (S/G) STATUS REGISTER (82378ZB Only) ................................ ..............65

3.2.17. SCATTER/GATHER (S/G) DESCRIPTOR TABLE POINTER REGISTER (82378ZB Only) .....67

3.2.18. SCATTER/GATHER (S/G) INTERRUPT STATUS REGISTER (82378ZB Only) ....................... 67

3.3. TIMER REGISTER DESCRIPTION ................................ ................................ ................................ .........68

3.3.1. TCW—TIMER CONTROL WORD REGISTER ................................ ................................................68

3.3.2. INTERVAL TIMER STATUS BYTE FORMAT REGISTER ................................ ............................. 70

3.3.3. COUNTER ACCESS PORTS REGISTER ................................ ................................ ....................... 71

3.3.4. BIOS TIMER REGISTER ................................ ................................................................ ...................71

3.4. INTERRUPT CONTROLLER REGISTER DESCRIPTION ................................ ................................ ....72

3.4.1. ICW1—INITIALIZATION COMMAND WORD 1 REGISTER ................................ ........................... 72

3.4.2. ICW2—INITIALIZATION COMMAND WORD 2 REGISTER ................................ ........................... 73

3.4.3. ICW3—INITIALIZATION COMMAND WORD 3 REGISTER ................................ ........................... 73

E 82378ZB (SIO) AND 82379 (SIO.A)

5

3.4.4. ICW3—INITIALIZATION COMMAND WORD 3 REGISTER ................................ ........................... 73

3.4.5. ICW4—INITIALIZATION COMMAND WORD 4 REGISTER ................................ ........................... 74

3.4.6. OCW1—OPERATIONAL CONTROL WORD 1 REGISTER ................................ ........................... 74

3.4.7. OCW2—OPERATIONAL CONTROL WORD 2 REGISTER ................................ ........................... 75

3.4.8. OCW3—OPERATIONAL CONTROL WORD 3 REGISTER ................................ ........................... 76

3.5. CONTROL REGISTERS ................................ ................................ ................................ ........................... 77

3.5.1. NMISC—NMI STATUS AND CONTROL REGISTER ................................ ................................ ..... 77

3.5.2. NMI ENABLE AND REAL-TIME CLOCK ADDRESS REGISTER .................................................. 78

3.5.3. PORT 92 REGISTER ................................ ................................ ................................ ......................... 78

3.5.4. DIGITAL OUTPUT REGISTER ................................ ................................ ................................ ......... 79

3.5.5. RESET UBUS IRQ1/IRQ12 REGISTER ................................ ................................ .......................... 79

3.5.6. COPROCESSOR ERROR REGISTER ................................ ................................ ............................ 80

3.5.7. ELCR—EDGE/LEVEL CONTROL REGISTER ................................ ................................ ............... 80

3.6. POWER MANAGEMENT REGISTERS ................................ ................................ ................................ ... 80

3.6.1. APMC—ADVANCED POWER MANAGEMENT CONTROL PORT ................................ .............. 81

3.6.2. APMS—ADVANCED POWER MANAGEMENT STATUS PORT ................................ .................. 81

3.7. APIC REGISTERS (82379AB ONLY) ................................ ................................ ................................ ......81

3.7.1. IOREGSEL—I/O REGISTER SELECT REGISTER (82379AB Only) ................................ ............ 82

3.7.2. IOWIN—I/O WINDOW REGISTER (82379AB Only) ................................ ................................ .......82

3.7.3. APICID—I/O APIC IDENTIFICATION REGISTER (82379AB Only) ................................ .............. 82

3.7.4. APICID—I/O APIC VERSION REGISTER (82379AB Only) ................................ ........................... 83

3.7.5. APICARB—I/O APIC ARBITRATION REGISTER (82379AB Only) ................................ ............... 83

3.7.6. IOREDTBL[15:0]—I/O REDIRECTION TABLE REGISTERS (82379AB Only) ............................. 83

4.0. FUNCTIONAL DESCRIPTION....................................................................................................................86

4.1. MEMORY AND I/O ADDRESS MAP ................................ ................................ ................................ .......86

4.1.1. MEMORY ADDRESS MAP (GENERATING MEMCS#) ................................ ................................ . 86

4.1.2. BIOS MEMORY SPACE ................................ ................................ ................................ .................... 87

4.1.3. I/O ACCESSES ................................ ................................ ................................ ................................ ..87

4.1.4. SUBTRACTIVELY DECODED CYCLES TO ISA ................................ ................................ ............88

4.1.5. UTILITY BUS ENCODED CHIP SELECTS ................................ ................................ ..................... 88

4.2. PCI INTERFACE ................................ ................................ ................................ ................................ .......88

4.2.1. PCI COMMAND SET ................................ ................................ ................................ ......................... 88

4.2.2. TRANSACTION TERMINATION ................................ ................................ ................................ .......89

4.3. PCI ARBITRATION CONTROLLER ................................ ................................ ................................ ........90

4.3.1. ARBITRATION SIGNAL PROTOCOL ................................ ................................ .............................. 90

4.3.2. INTERNAL/EXTERNAL ARBITER CONFIGURATION ................................ ................................ ...91

4.3.3. Guaranteed Access Time Mode ................................ ................................ ................................ ........ 92

4.3.3.1. DMA LATENCIES IN GAT MODE ONLY (82378ZB ONLY) ................................ .................... 92

4.4. ISA INTERFACE ................................ ................................ ................................ ................................ ....... 92

4.4.1. ISA CLOCK GENERATION ................................ ................................ ................................ ............... 93

4.5. DMA CONTROLLER ................................ ................................ ................................ ................................ .93

82378ZB (SIO) AND 82379AB (SIO.A) E

6

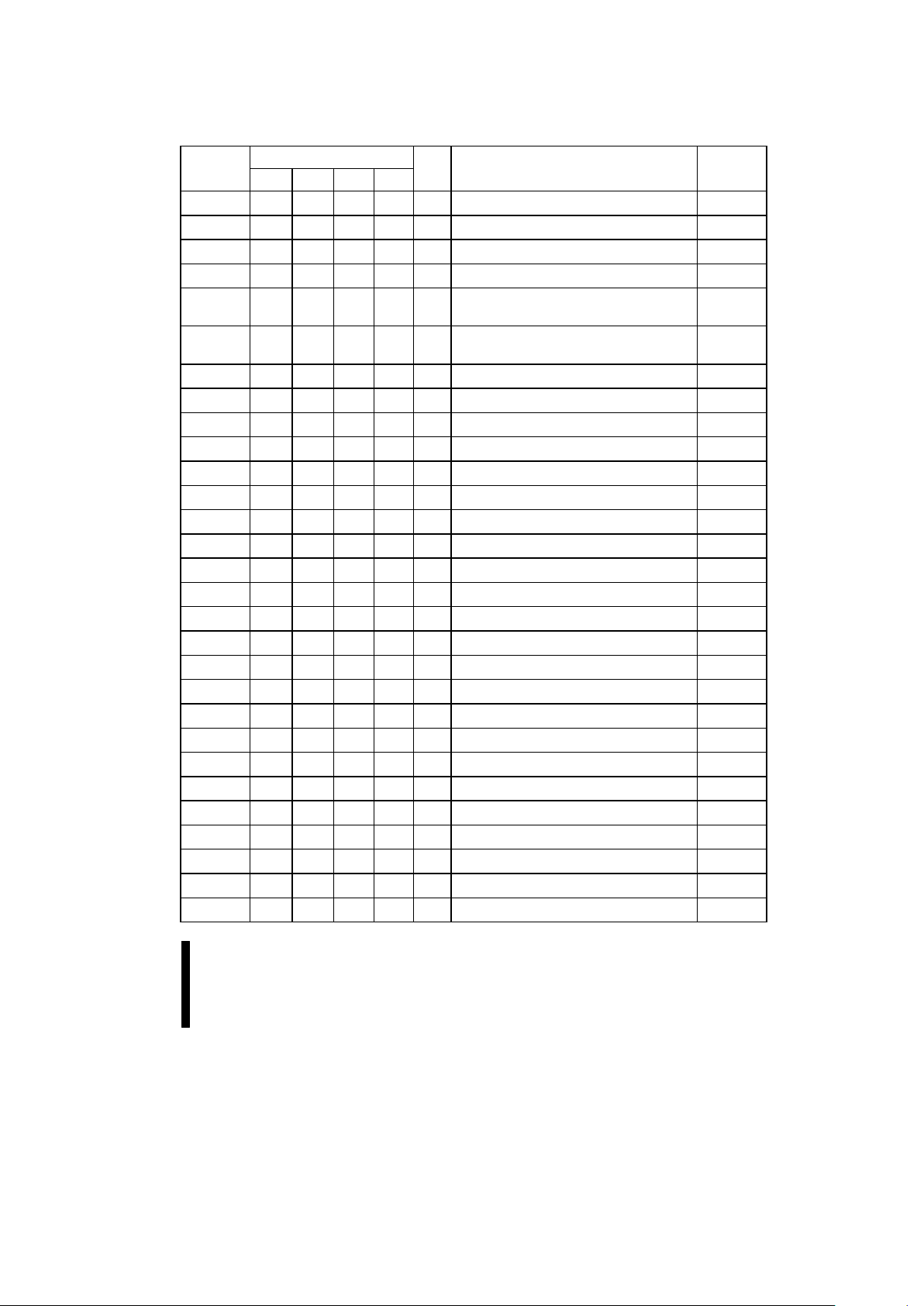

4.5.1. DMA TIMINGS ................................ ................................ ................................ ................................ ....94

4.5.1.1. COMPATIBLE TIMING (82378ZB AND 82379AB) ................................................................ ...95

4.5.1.2. TYPE "A" TIMING (82378ZB) ................................ ................................ ................................ .....95

4.5.1.3. TYPE "B" TIMING (82378ZB) ................................ ................................ ................................ .....95

4.5.1.4. TYPE "F" TIMING (82378ZB) ................................ ................................ ................................ .....95

4.5.1.5. DREQ AND DACK# LATENCY CONTROL (82378ZB AND 82379AB) ................................ ..95

4.5.2. ISA REFRESH CYCLES (82378ZB and 82379AB) ................................ ................................ ......... 95

4.5.3. SCATTER/GATHER (S/G) DESCRIPTION (82378ZB) ................................ ................................ ...95

4.6. DATA BUFFERING ................................ ................................ ................................ ................................ ...98

4.6.1. DMA/ISA MASTER LINE BUFFER ................................ ................................ ................................ ...98

4.6.2. PCI MASTER POSTED WRITE BUFFER ................................ ................................ ........................ 98

4.7. SIO TIMERS ................................ ................................ ................................ ................................ ............... 98

4.7.1. INTERVAL TIMERS ................................ ................................................................ ........................... 98

4.7.2. BIOS TIMER ................................ ................................ ................................ ................................ ........99

4.8. INTERRUPT CONTROLLER ................................ ................................ ................................ ..................100

4.8.1. EDGE AND LEVEL TRIGGERED MODES ................................ ................................ ....................101

4.8.2. NON-MASKABLE INTERRUPT (NMI) ................................ ................................ ............................ 101

4.9. ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC) (82379AB ONLY) ...............102

4.9.1. PHYSICAL CHARACTERISTICS OF APIC BUS (82379AB Only) ................................ ..............105

4.9.2. ARBITRATION FOR APIC BUS (82379AB Only) ................................ ................................ ..........105

4.9.3. INTR AND THE PENTIUM

PROCESSOR’S "THROUGH LOCAL MODE" (82379AB Only) ....105

4.9.4. PULSING OF APICD1 DURING CPU RESET (82379AB Only) ................................ ................... 107

4.9.5. SIO.A ASSERTING SIGNALS LOW DURING PCIRST# (82379AB ONLY) ................................ 111

4.10. UTILITY BUS PERIPHERAL SUPPORT ................................ ................................ ............................. 111

4.11. POWER MANAGEMENT ................................ ................................................................ ......................116

4.11.1. SMM MODE ................................ ................................ ................................ ................................ ....117

4.11.2. SMI SOURCES ................................ ................................ ................................ ............................... 117

4.11.3. SMI# AND INIT INTERACTION ................................ ................................ ................................ ....118

4.11.4. CLOCK CONTROL ................................ ................................ ................................ ......................... 119

4.11.5. DUAL-PROCESSOR POWER MANAGEMENT SUPPORT (82379AB Only) ........................... 120

4.11.5.1. SMI# DELIVERY MECHANISM ................................ ................................ ............................. 120

4.11.5.2. STPCLK# TIED TO BOTH SOCKETS ................................ ................................ ................... 120

4.11.5.3. SMI#/INTR (APIC MODE) ................................ ................................ ................................ .......121

4.11.6. INTERRUPT LEVELS AND SYSTEM EVENT GENERATION IN POWER MANAGED

SYSTEMS (82378ZB Only) ................................ ................................ ................................ .................... 121

4.12. DESIGN CONSIDERATIONS (82378ZB/82379AB) ................................ ................................ ...........121

4.12.1. Good Layout Practice ................................ ................................ ................................ .....................121

4.12.2. ASYNCHRONOUSLY SWITCHING SIGNALS ................................ ................................ ............121

5.0. ELECTRICAL CHARACTERISTICS................................ .........................................................................122

5.1. MAXIMUM RATINGS ................................ ................................ ................................ .............................. 122

6.0. PIN ASSIGNMENT................................................................................................ ......................................123

E 82378ZB (SIO) AND 82379 (SIO.A)

7

7.0. MECHANICAL SPECIFICATIONS...........................................................................................................127

7.1. PACKAGE DIAGRAM ................................ ................................ ................................ ............................. 127

7.2. THERMAL SPECIFICATIONS ................................ ................................ ................................ ............... 128

8.0. TESTABILITY ................................................................................................................................ .............128

8.1. GLOBAL TRI-STATE ................................ ................................ ................................ .............................. 128

8.2. NAND TREE ................................ ................................ ................................ ................................ ............ 128

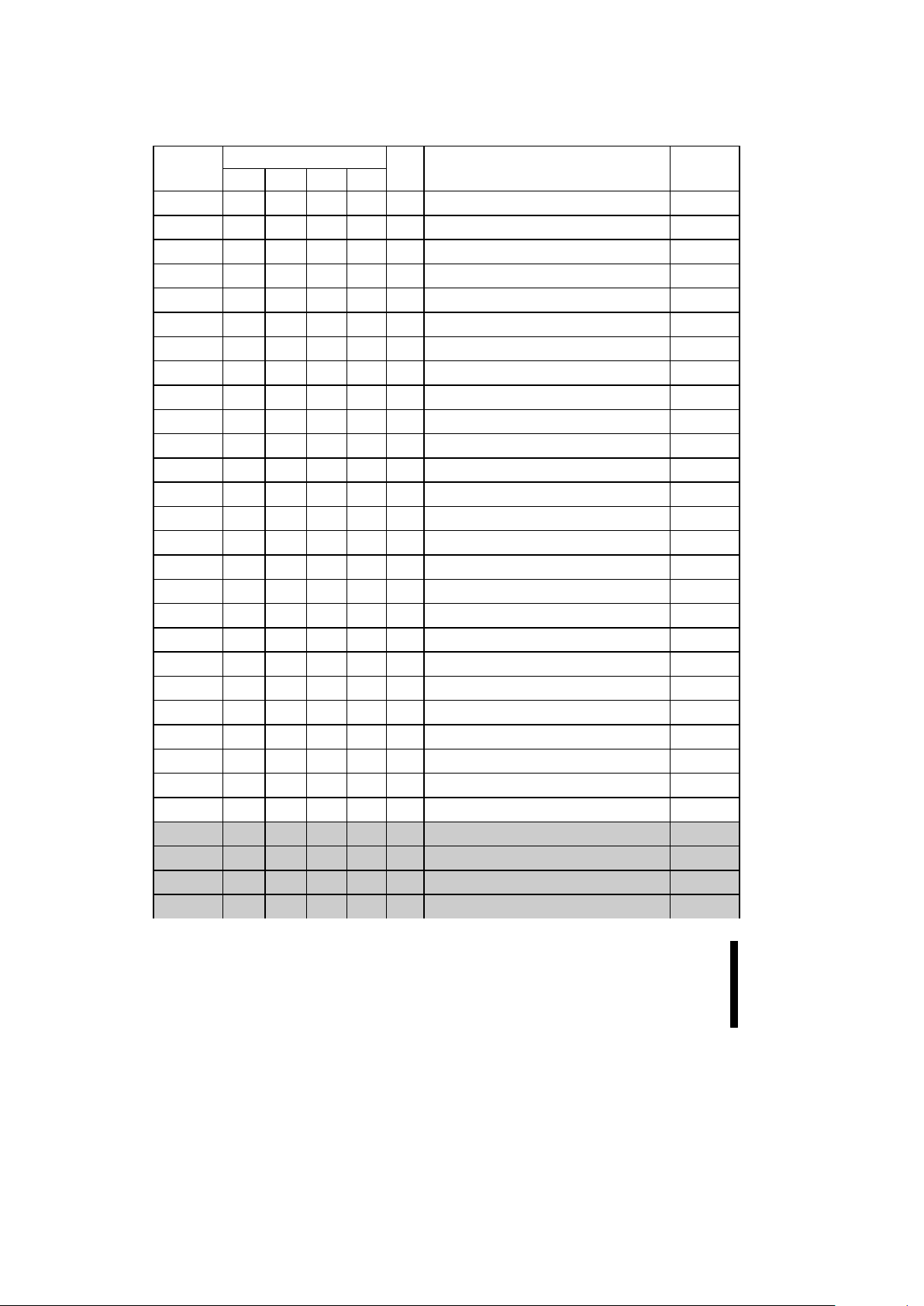

8.3. NAND TREE CELL ORDER ................................ ................................ ................................ ................... 129

8.4. NAND TREE DIAGRAM ................................ ................................ ................................ ......................... 137

82378ZB (SIO) AND 82379AB (SIO.A) E

8

E 82378ZB (SIO) AND 82379 (SIO.A)

9

1.0. ARCHITECTURAL OVERVIEW

The major functions of the SIO and SIO.A components are broken up into blocks as shown in the SIO and SIO.A

Component Block Diagrams. A description of each block is provided below.

PCI Bus Interface

The PCI Bus Interface provides the interface between the SIO/SIO.A and the PCI Bus. The SIO/SIO.A provides

both a master and slave interface to the PCI Bus. As a PCI master, the SIO/SIO.A runs cycles on behalf of

DMA, ISA masters, and the internal data buffer management logic when buffer flushing is required. The

SIO/SIO.A burstS a maximum of two Dwords when reading from PCI memory, and one Dword when writing to

PCI memory. The SIO/SIO.A does not generate PCI I/O cycles as a master. As a PCI slave, the SIO/SIO.A

accepts cycles initiated by PCI masters targeted for the SIO/SIO.A internal register set or the ISA Bus. The

SIO/SIO.A accepts a maximum of one data transaction before terminating the transaction. This supports the

Incremental Latency Mechanism as defined in the Peripheral Component Interconnect (PCI) Specification.

As a master, the SIO/SIO.A generates address and command signal (C/BE#) parity for read and write cycles,

and data parity for write cycles. As a slave, the SIO/SIO.A generates data parity for read cycles. Parity checking

is not supported. The SIO/SIO.A also provides support for system error reporting by generating a NonMaskable-Interrupt (NMI) when SERR# is driven active.

The SIO/SIO.A, as a resource, can be locked by any PCI master. In the context of locked cycles, the entire

SIO/SIO.A subsystem (including the ISA Bus) is considered a single resource.

The SIO/SIO.A directly supports the PCI Interface running at either 25 MHz or 33 MHz. If a frequency of less

than 33 MHz is required (not including 25 MHz), a SYSCLK divisor value (as indicated in the ISA Clock Divisor

Register) must be selected that guarantees that the ISA Bus frequency does not violate the 6 MHz to 8.33 MHz

SYSCLK range.

PCI Arbiter

The PCI arbiter provides support for six PCI masters; the Host Bridge, SIO/SIO.A, and four PCI masters. The

arbiter can be programmed for a purely rotating scheme, fixed, or a combination of the two. The Arbiter can also

be programmed to support bus parking. This gives the Host Bridge default access to the PCI Bus when no other

device is requesting service. The arbiter can be disabled if an external arbiter is used.

Data Buffers

To isolate the slower ISA Bus from the PCI Bus, the SIO/SIO.A provides two types of data buffers. One Dworddeep posted write buffer is provided for the posting of PCI initiated memory write cycles to the ISA Bus. The

second buffer is a bi-directional, 8-byte line buffer used for ISA master and DMA accesses to the PCI Bus. All

DMA and ISA master read and write cycles go through the 8-byte line buffer. The data buffers also provide the

data assembly or disassembly when needed for transactions between the PCI and ISA Buses. Buffering is

programmable and can be enabled or disabled through software.

ISA Bus Interface

The SIO/SIO.A incorporates a fully ISA-Bus compatible master and slave interface. The SIO/SIO.A directly

drives six ISA slots without external data or address buffering. The ISA interface also provides byte swap logic,

I/O recovery support, wait-state generation, and SYSCLK generation. The SIO/SIO.A supports ISA Bus

frequencies from 6 to 8.33 MHz.

82378ZB (SIO) AND 82379AB (SIO.A) E

10

As an ISA master, the SIO/SIO.A generates cycles on behalf of DMA, Refresh, and PCI master initiated cycles.

The SIO/SIO.A supports compressed cycles when accessing ISA slaves (i.e., ZEROWS# asserted). As an ISA

slave, the SIO/SIO.A accepts ISA master accesses targeted for the SIO/SIO.A internal register set or ISA

master memory cycles targeted for the PCI Bus. The SIO/SIO.A does not support ISA master initiated I/O cycles

targeted for the PCI Bus.

The SIO/SIO.A also monitors ISA master to ISA slave cycles to generate SMEMR# or SMEMW#, and to support

data byte swapping, if necessary.

DMA

The DMA controller in the SIO/SIO.A incorporates the functionality of two 82C37 DMA controllers with seven

independently programmable channels. Each channel can be programmed for 8- or 16-bit DMA device size. The

DMA controller is also responsible for generating ISA refresh cycles.

For the 82378ZB, ISA-compatible or fast DMA type "A", type "B", or type "F" timings are supported and 32-bit

addressing is supported as an extension of the ISA-compatible specification. The SIO supports an enhanced

feature called Scatter/Gather (S/G). This feature provides the capability of transferring multiple buffers between

memory and I/O without CPU intervention. In S/G mode, the DMA can read the memory address and word count

from an array of buffer descriptors, located in system memory, called the S/G Descriptor (SGD) Table. This

allows the DMA controller to sustain DMA transfers until all of the buffers in the SGD table are read.

For the SIO.A, the DMA supports 8-/16-bit device size using ISA-compatible timings and 27-bit addressing as an

extension of the ISA-compatible specification. Scatter/Gather is not supported.

Timer Block

The timer block contains three counters that are equivalent in function to those found in one 82C54

programmable interval timer. These three counters are combined to provide the System Timer function, Refresh

Request, and speaker tone. The three counters use the 14.31818 MHz OSC input for a clock source.

In addition to the three counters, the SIO/SIO.A provides a programmable 16-bit BIOS timer. This timer can be

used by BIOS software to implement timing loops. The timer uses the ISA system clock (SYSCLK) divided by 8

as a clock source. An 8:1 ratio between the SYSCLK and the BIOS timer clock is always maintained. The

accuracy of the BIOS timer is

± 1 ms.

Utility Bus (X-Bus) Logic

The SIO/SIO.A provides four encoded chip selects that are decoded externally to provide chip selects for flash

BIOS, real time clock, keyboard/Mouse Controller, floppy controller, two serial ports, one parallel port, and an

IDE hard disk drive. The SIO/SIO.A provides the control for the buffer that isolates the lower 8 bits of the Utility

Bus from the lower 8 bits of the ISA Bus. In addition to providing the encoded chip selects and Utility Bus buffer

control, the SIO/SIO.A also provides Port 92 functions (Alternate Reset and Alternate A20), Coprocessor error

reporting, the Floppy DSKCHG function, and a mouse interrupt input.

Interrupt Controller Block

The SIO/SIO.A provides an ISA compatible interrupt controller that incorporates the functionality of two 82C59

interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are

possible.

E 82378ZB (SIO) AND 82379 (SIO.A)

11

Advanced Programmable Interrupt Controller (APIC) (SIO.A Only)

In addition to the standard ISA-compatible interrupt controller described above, the SIO.A incorporates the

Advanced Programmable Interrupt Controller (APIC). While the standard interrupt controller is intended for use in

a uni-processor system, APIC can be used in either a uni-processor or multi-processor system. APIC provides

multi-processor interrupt management and incorporates both static and dynamic symmetric interrupt distribution

across all processors. In systems with multiple I/O subsystems, each subsystem can have its own set of

interrupts.

Power Management

Extensive power management capability permits a system to operate in a low power state without being

powered down. Once in the low power state (called 'Fast-Off' state), the computer appears to be off. For

example, the System Memory Management (SMM) code could turn off the CRT, line printer, hard disk drive's

spindle motor, and fans. In addition, the CPU's clock can be governed. To the user, the machine appears to be

in the off state. However, the system is actually in an extremely low power state that still permits the CPU to

function and maintain communication connections normally associated with today's desktops (e.g., LAN,

Modem, or FAX). Programmable options provide power management flexibility. For example, various system

events can be programmed to place the system in the low power state or break events can be programmed to

wake the system up.

Test

The test block provides the interface to the test circuitry within the SIO/SIO.A. The test input can be used to tristate all of the SIO/SIO.A outputs.

82378ZB (SIO) AND 82379AB (SIO.A) E

12

2.0. SIGNAL DESCRIPTION

This section contains a detailed description of each signal. The signals are arranged in functional groups

according to the interface.

Note that the '#' symbol at the end of a signal name indicates that the active, or asserted state occurs when the

signal is at a low voltage level. When '#' is not present after the signal name, the signal is asserted when at the

high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a

mixture of 'active-low' and 'active-high' signals. The term assert, or assertion indicates that a signal is active,

independent of whether that level is represented by a high or low voltage. The term negate, or negation

indicates that a signal is inactive.

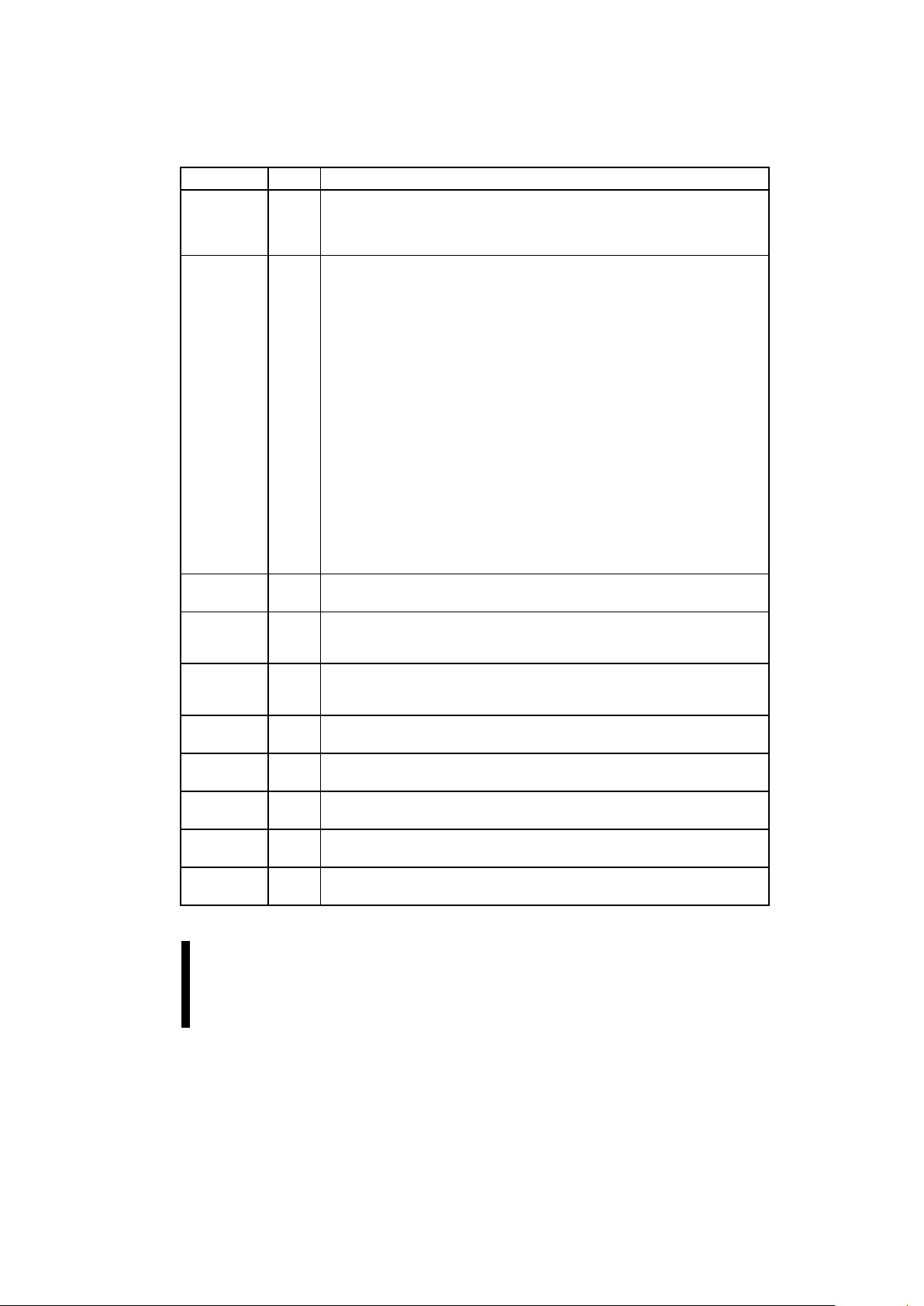

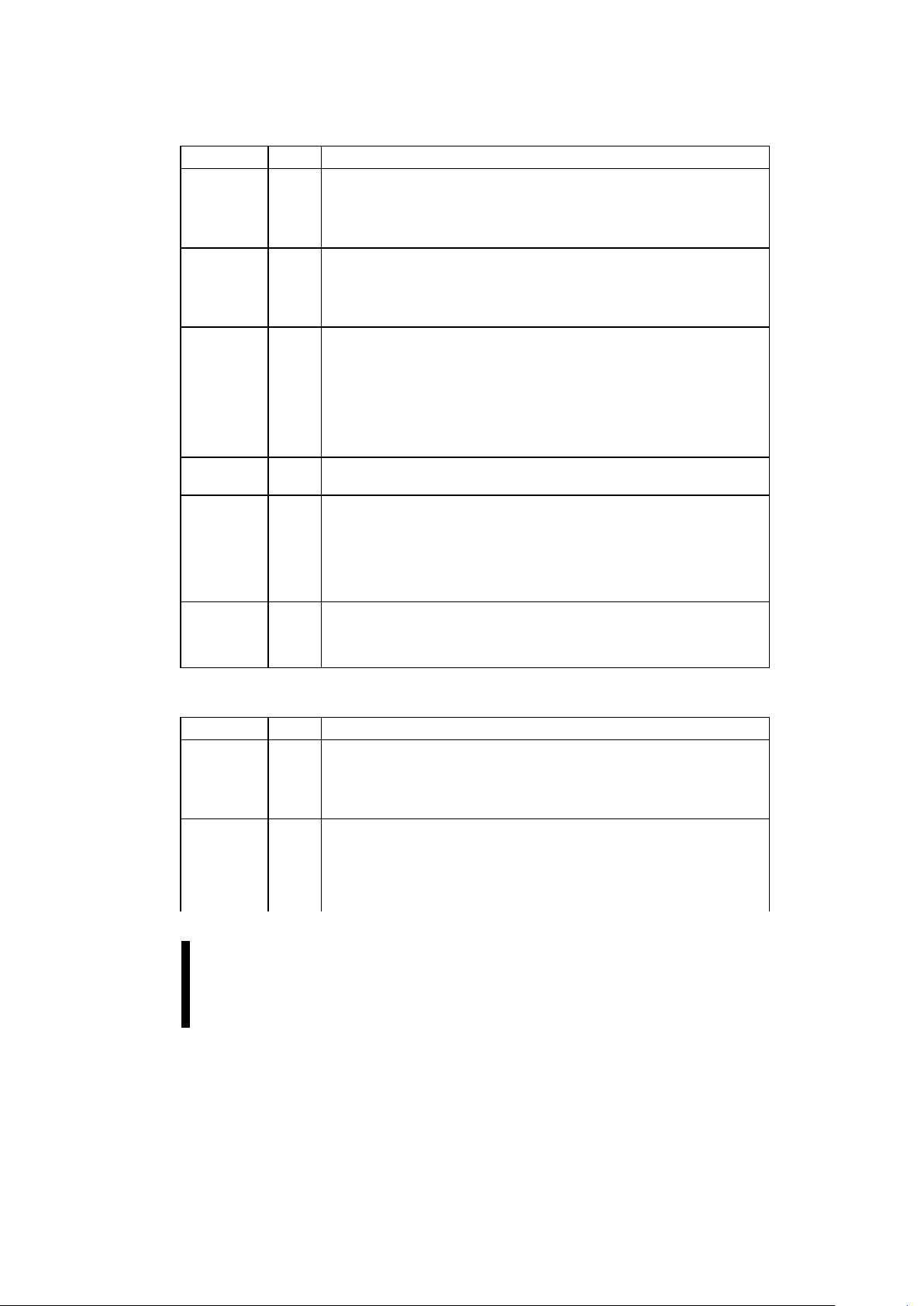

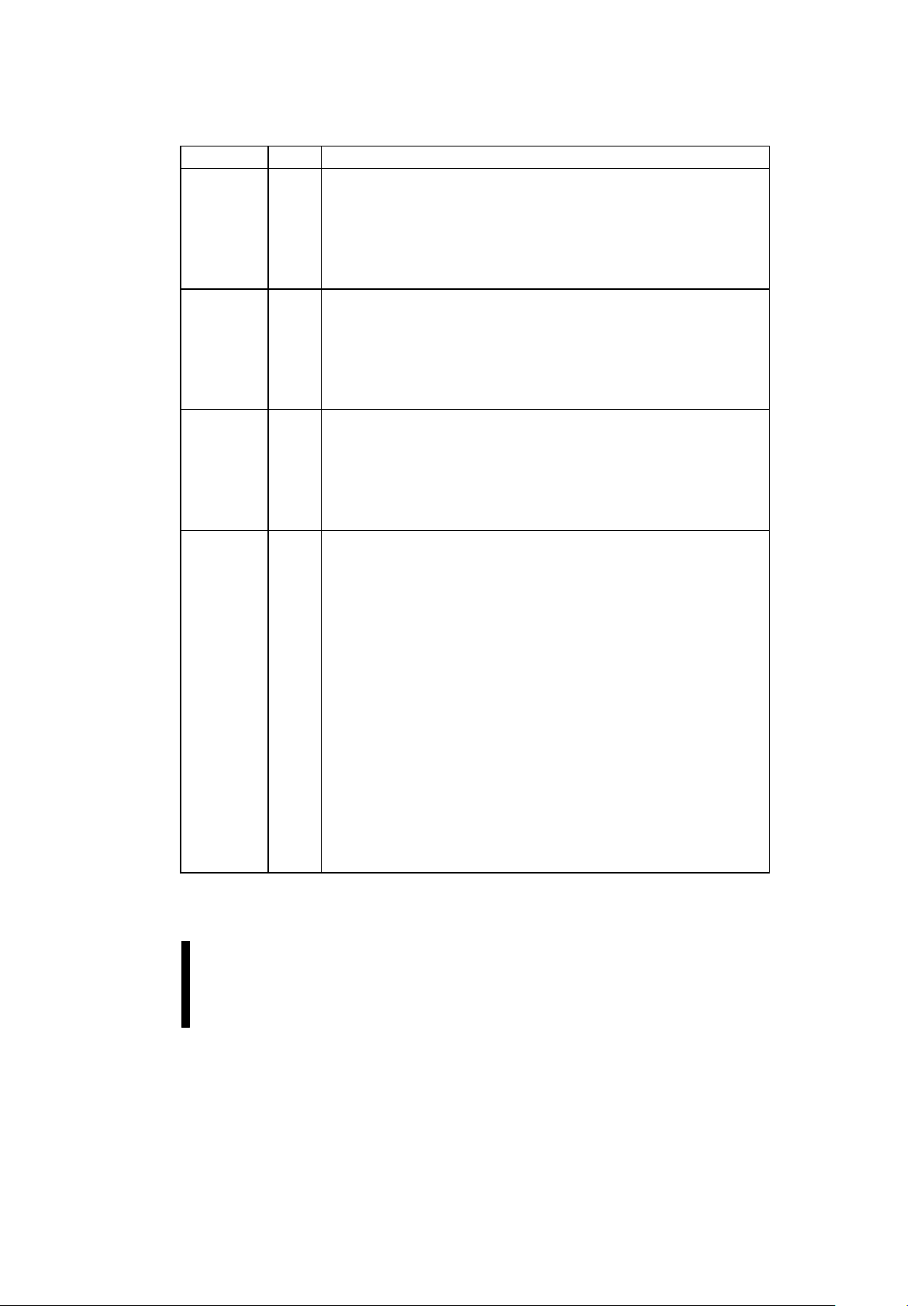

The following notations are used to described the signal type.

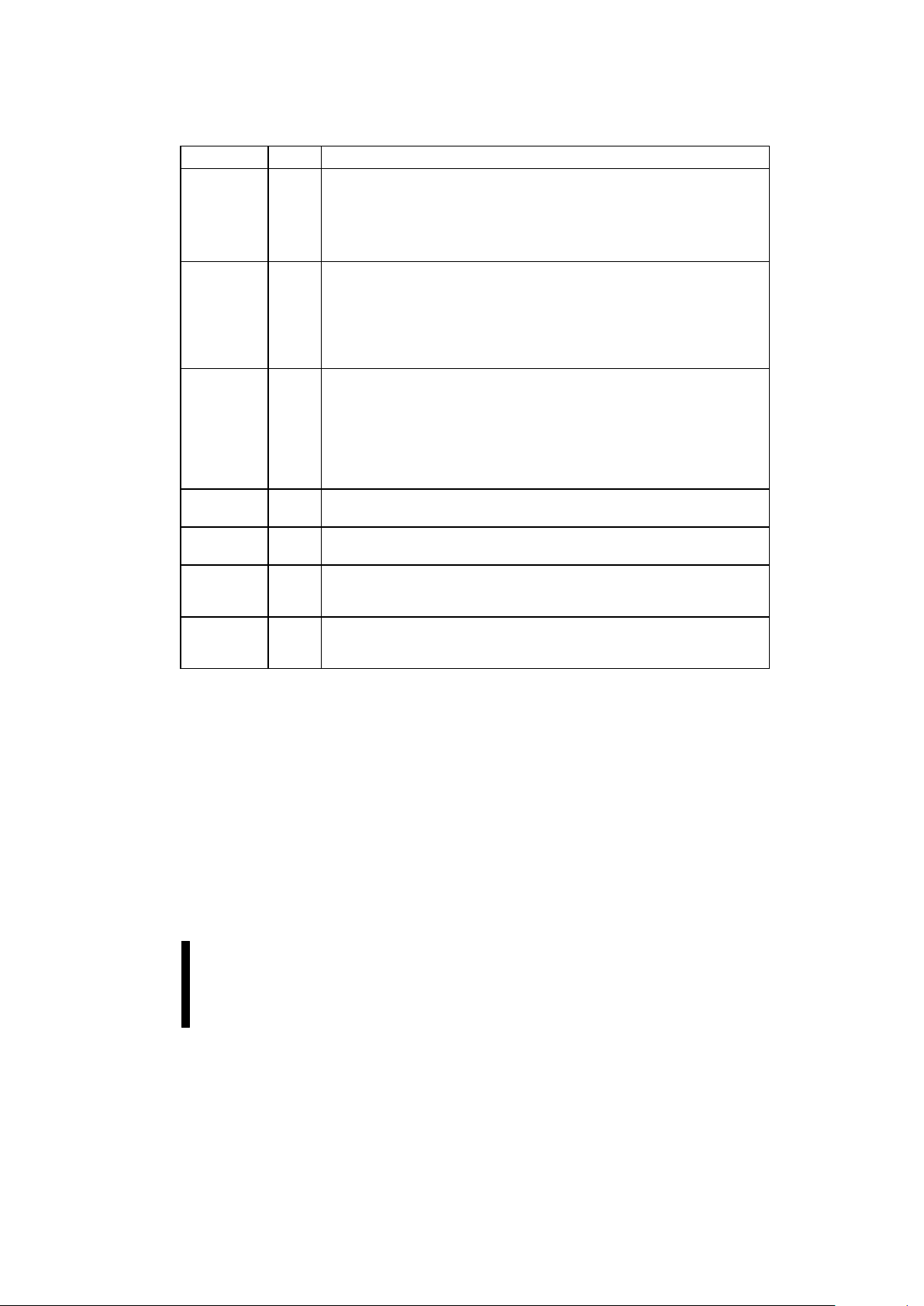

Signal Type

Description

I

Input is a standard input-only signal.

O

Totem Pole Output is a standard active driver.

OD

Open Drain Input/Output.

IO

Input/Output is a bidirectional, tri-state pin.

s/t/s

Sustained Tri-State is an active low tri-state signal owned and driven by one and only one

agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock

before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock

after the previous owner tri-states it. A pull-up sustains the inactive state until another agent

drives it and is provided by the central resource.

t/s/o

Tri-State Output

E 82378ZB (SIO) AND 82379 (SIO.A)

13

2.1. PCI Bus Interface Signals

Signal Name

Type

Description

PCICLK I

PCI CLOCK: PCICLK provides timing for all transactions on the PCI Bus. All other

PCI signals are sampled on the rising edge of PCICLK, and all timing parameters

are defined with respect to this edge. Frequencies supported by the SIO/SIO.A

include 25 and 33 MHz.

PCIRST# I

PCI RESET: PCIRST# forces the SIO/SIO.A to a known state. AD[31:0],

C/BE[3:0]#, and PAR are always driven low by the SIO/SIO.A synchronously from

the leading edge of PCIRST#. The SIO/SIO.A always tri-states these signals from

the trailing edge of PCIRST#. If the internal arbiter is enabled (CPUREQ# sampled

high on the trailing edge of PCIRST#), the SIO/SIO.A will drive these signals low

again (synchronously 2-5 PCICLKs later) until the bus is given to another master. If

the internal arbiter is disabled (CPUREQ# sampled low on the trailing edge of

PCIRST#), these signals remain tri-stated until the SIO/SIO.A is required to drive

them valid as a master or slave.

FRAME#, IRDY#, TRDY#, STOP#, DEVSEL#, MEMREQ#, FLSHREQ#,

CPUGNT#, GNT0#/SIOREQ#, and GNT1#/RESUME# are tri-stated from the

leading edge of PCIRST#. FRAME#, IRDY#, TRDY#, STOP#, and DEVSEL#

remain tri-stated until driven by the SIO/SIO.A as either a master or a slave.

MEMREQ#, FLSHREQ#, CPUGNT#, GNT0#/SIOREQ#, and GNT1#/RESUME#

are tri-stated until driven by the SIO/SIO.A. After PCIRST#, MEMREQ# and

FLSHREQ# are driven inactive asynchronously from PCIRST# inactive. CPUGNT#,

GNT0#/SIOREQ#, and GNT1#/RESUME# are driven based on the arbitration

scheme and the asserted REQx#'s.

All registers are set to their default values. PCIRST# may be asynchronous to

PCICLK when asserted or negated. Although asynchronous, negation must be a

clean, bounce-free edge. Note that PCIRST# must be asserted for more than 1 µs.

AD[31:0]

I/O

PCI ADDRESS/DATA. The standard PCI address and data lines. The address is

driven with FRAME# assertion and data is driven or received in following clocks.

C/BE[3:0]#

I/O

BUS COMMAND AND BYTE ENABLES: The command is driven with FRAME#

assertion. Byte enables corresponding to supplied or requested data are driven on

following clocks.

FRAME#

I/O

(s/t/s)

CYCLE FRAME: Assertion indicates the address phase of a PCI transfer. Negation

indicates that one more data transfer is desired by the cycle initiator. FRAME# is tri-

stated from the leading edge of PCIRST#.

TRDY#

I/O

(s/t/s)

TARGET READY: Asserted when the target is ready for a data transfer. TRDY# is

tri-stated from the leading edge of PCIRST#.

IRDY#

I/O

(s/t/s)

INITIATOR READY: Asserted when the initiator is ready for a data transfer. IRDY#

is tri-stated from the leading edge of PCIRST#.

STOP#

I/O

(s/t/s)

STOP: Asserted by the target to request the master to stop the current transaction.

STOP# is tri-stated from the leading edge of PCIRST#.

LOCK# I

LOCK: LOCK# indicates an atomic operation that may require multiple transactions

to complete. LOCK# is always an input to the SIO/SIO.A.

IDSEL I

INITIALIZATION DEVICE SELECT: IDSEL is used as a chip select during

configuration read and write transactions.

82378ZB (SIO) AND 82379AB (SIO.A) E

14

Signal Name

Type

Description

DEVSEL#

I/O

(s/t/s)

DEVICE SELECT: The SIO/SIO.A asserts DEVSEL# to claim a PCI transaction

through positive or subtractive decoding. DEVSEL# is tri-stated from the leading

edge of PCIRST#. DEVSEL# remains tri-stated until driven by the SIO/SIO.A as

either a master or a slave.

PIRQ[3:0]#

I

PCI INTERRUPT REQUEST: PIRQ#s are used to generate asynchronous

interrupts to the CPU via the Programmable Interrupt Controllers (82C59s)

integrated in the SIO/SIO.A. These signals are defined as level sensitive and are

asserted low. The PIRQx# interrupts can be steered into any unused IRQ interrupt.

The PIRQx# Route Control Register determines which IRQ interrupt each PCI

interrupt is steered into. These pins include a weak internal pull-up resistor.

PAR O

CALCULATED PARITY SIGNAL: A single parity bit is provided over AD[31:0] and

C/BE[3:0]. PAR is always driven low by the 82379AB synchronously from the

leading edge of PCIRST#.

SERR# I

SYSTEM ERROR: SERR# can be pulsed active by any PCI device that detects a

system error condition. Upon sampling SERR# active, the SIO/SIO.A generates a

non-maskable interrupt (NMI) to the CPU.

2.2. PCI Arbiter Signals

Signal Name

Type

Description

CPUREQ# I

CPU REQUEST: This signal provides the following functions:

1. If CPUREQ# is sampled high on the trailing edge of PCIRST#, the internal arbiter

is enabled. If CPUREQ# is sampled low on the trailing edge of PCIRST#, the

internal arbiter is disabled. This requires that the host bridge drive CPUREQ# high

during PCIRST#.

2. If the SIO/SIO.A internal arbiter is enabled, this pin is configured as CPUREQ#.

An active low assertion indicates that the CPU initiator desires the use of the PCI

Bus. If the internal arbiter is disabled, this pin is meaningless after reset.

This pin has a weak internal pull-up resistor.

REQ0#/

SIOGNT#

I

REQUEST 0/SIO GRANT: If the SIO/SIO.A internal arbiter is enabled, this pin is

configured as REQ0#. An active low assertion indicates that Initiator0 desires the

use of the PCI Bus. If the internal arbiter is disabled, this pin is configured as

SIOGNT#. When asserted, SIOGNT# indicates that the external PCI arbiter has

granted use of the bus to the SIO/SIO.A. This pin has a weak internal pull-up

resistor.

REQ1# I

REQUEST 1: If the SIO/SIO.A internal arbiter is enabled through the Arbiter

Configuration Register, then this signal is configured as REQ1#. An active low

assertion indicates that Initiator1 desires the use of the PCI Bus. If the internal

arbiter is disabled, the SIO/SIO.A ignores REQ1# after reset. This pin has a weak

internal pull-up resistor.

E 82378ZB (SIO) AND 82379 (SIO.A)

15

Signal Name

Type

Description

CPUGNT# t/s/o

CPU GRANT: If the SIO/SIO.A internal arbiter is enabled, this pin is configured as

CPUGNT#. The SIO/SIO.A internal arbiter asserts CPUGNT# to indicate that the

CPU initiator has been granted the PCI Bus. If the internal arbiter is disabled, this

signal is meaningless. CPUGNT# is tri-stated from the leading edge of PCIRST#.

CPUGNT# is tri-stated until driven by the SIO/SIO.A. CPUGNT# is driven based on

the arbitration scheme and the asserted REQx#s.

GNT0#/

SIOREQ#

t/s/o

GRANT 0/SIO REQUEST: If the SIO/SIO.A internal arbiter is enabled, this pin is

configured as GNT0#. The SIO/SIO.A internal arbiter asserts GNT0# to indicate

that Initiator0 has been granted the PCI Bus. If the internal arbiter is disabled, this

pin is configured as SIOREQ#. The SIO/SIO.A asserts SIOREQ# to request the

PCI Bus. GNT0#/SIOREQ# is tri-stated from the leading edge of PCIRST#.

GNT0#/SIOREQ# is tri-stated until driven by the SIO/SIO.A. GNT0#/SIOREQ# is

driven based on the arbitration scheme and the asserted REQx#'s.

GNT1#/

RESUME#

t/s/o

GRANT 1/RESUME: If the SIO's internal arbiter is enabled, this pin is configured as

GNT1#. The SIO/SIO.A internal arbiter asserts GNT1# to indicate that Initiator1 has

been granted the PCI Bus. If the internal arbiter is disabled, this pin is configured as

RESUME#. The SIO/SIO.A asserts RESUME# to indicate that the conditions

causing the SIO/SIO.A to retry the cycle has passed. GNT1#/RESUME# is tri-

stated from the leading edge of PCIRST#. GNT1#/RESUME# is tri-stated until

driven by the SIO/SIO.A. GNT1#/RESUME# is driven based on the arbitration

scheme and the asserted REQx#'s.

REQ2# I

REQUEST 2: This pin is an active low signal that indicates that Initiator2 desires the

use of the PCI Bus. This signal has a weak internal pull-up resistor.

REQ3# I

REQUEST 3: This pin is an active low signal that indicates that Initiator3 desires the

use of the PCI Bus. This signal has a weak internal pull-up resistor.

GNT2# t/s/o

GRANT 2: This pin is configured as GNT2#. The SIO/SIO.A internal arbiter asserts

GNT2# to indicate that Initiator2 has been granted the PCI Bus. GNT2# is high upon

reset.

GNT3# t/s/o

GRANT 3: This pin is configured as GNT3#. The SIO/SIO.A internal arbiter asserts

GNT3# to indicate that Initiator3 has been granted the PCI Bus. GNT3# is high upon

reset.

82378ZB (SIO) AND 82379AB (SIO.A) E

16

Signal Name

Type

Description

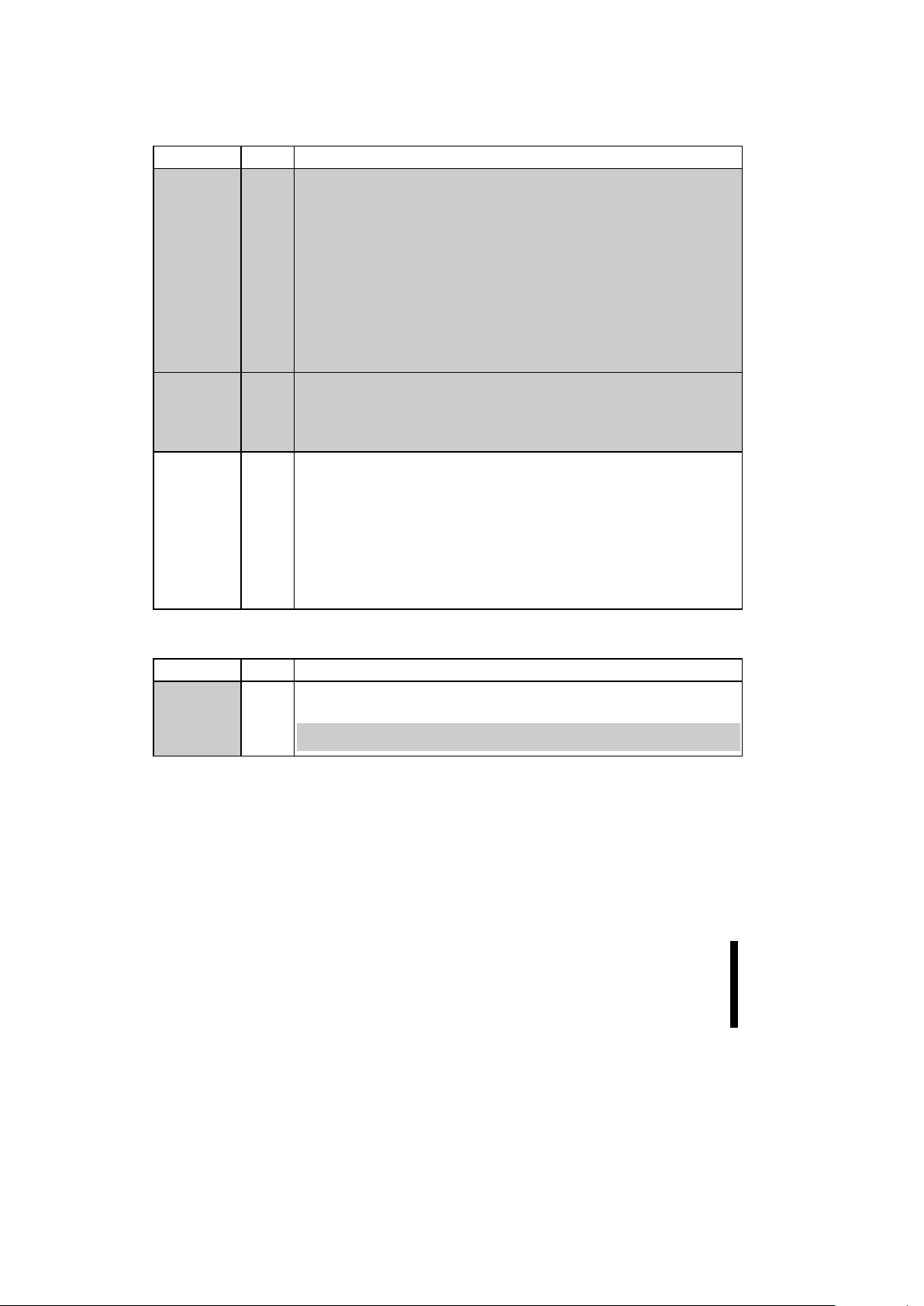

MEMREQ# t/s/o

MEMORY REQUEST: If the SIO/SIO.A is configured in Guaranteed Access Time

(GAT) Mode, MEMREQ# will be asserted when an ISA master or DMA is

requesting the ISA Bus (along with FLSHREQ#) to indicate that the SIO/SIO.A

requires ownership of the main memory. MEMREQ# is tri-stated from the leading

edge of PCIRST#. MEMREQ# remains tri-stated until driven by the SIO/SIO.A.

After PCIRST, MEMREQ# is driven inactive asynchronously from PCIRST#

inactive. The SIO/SIO.A asserts FLSHREQ# concurrently with asserting

MEMREQ#.

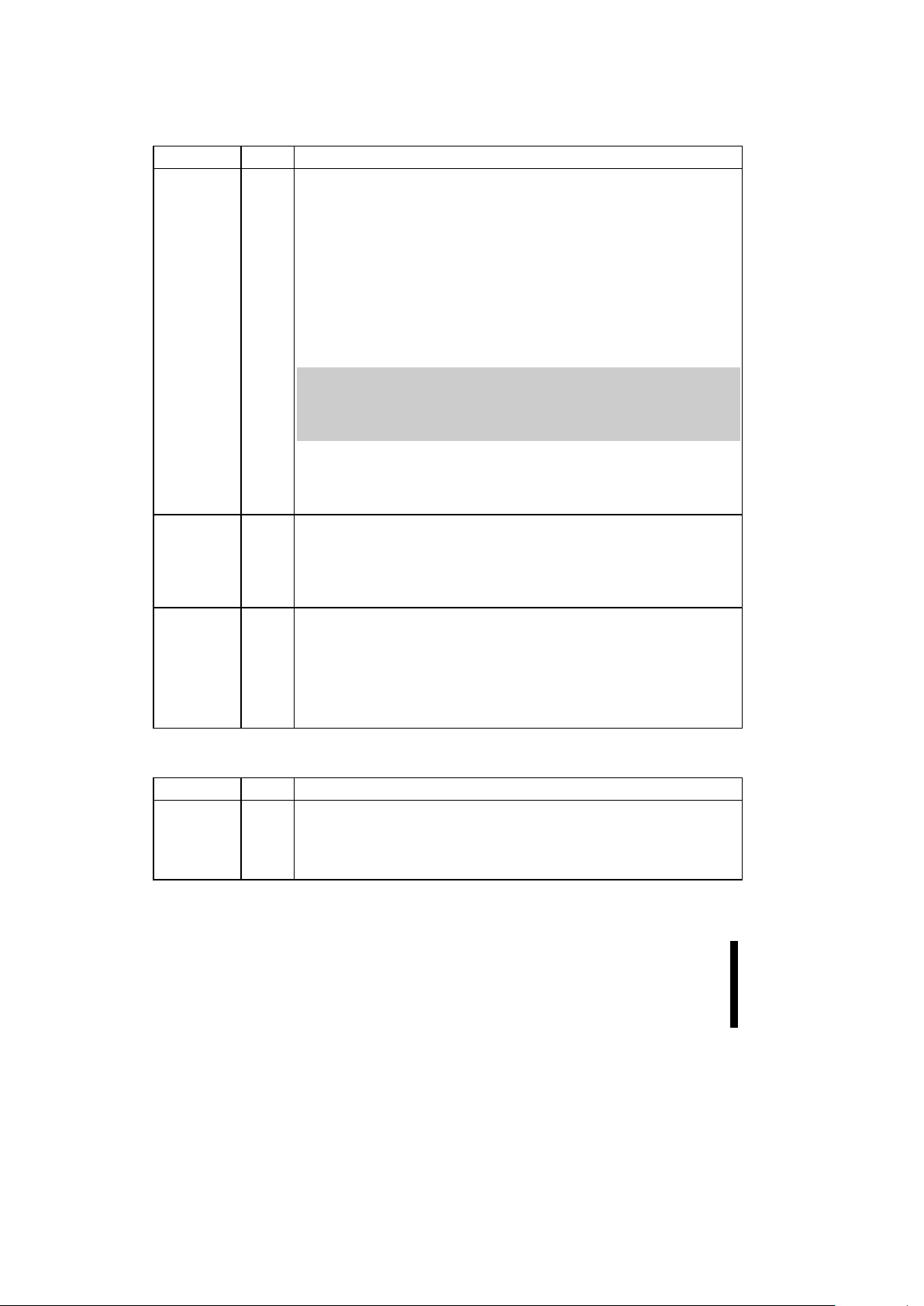

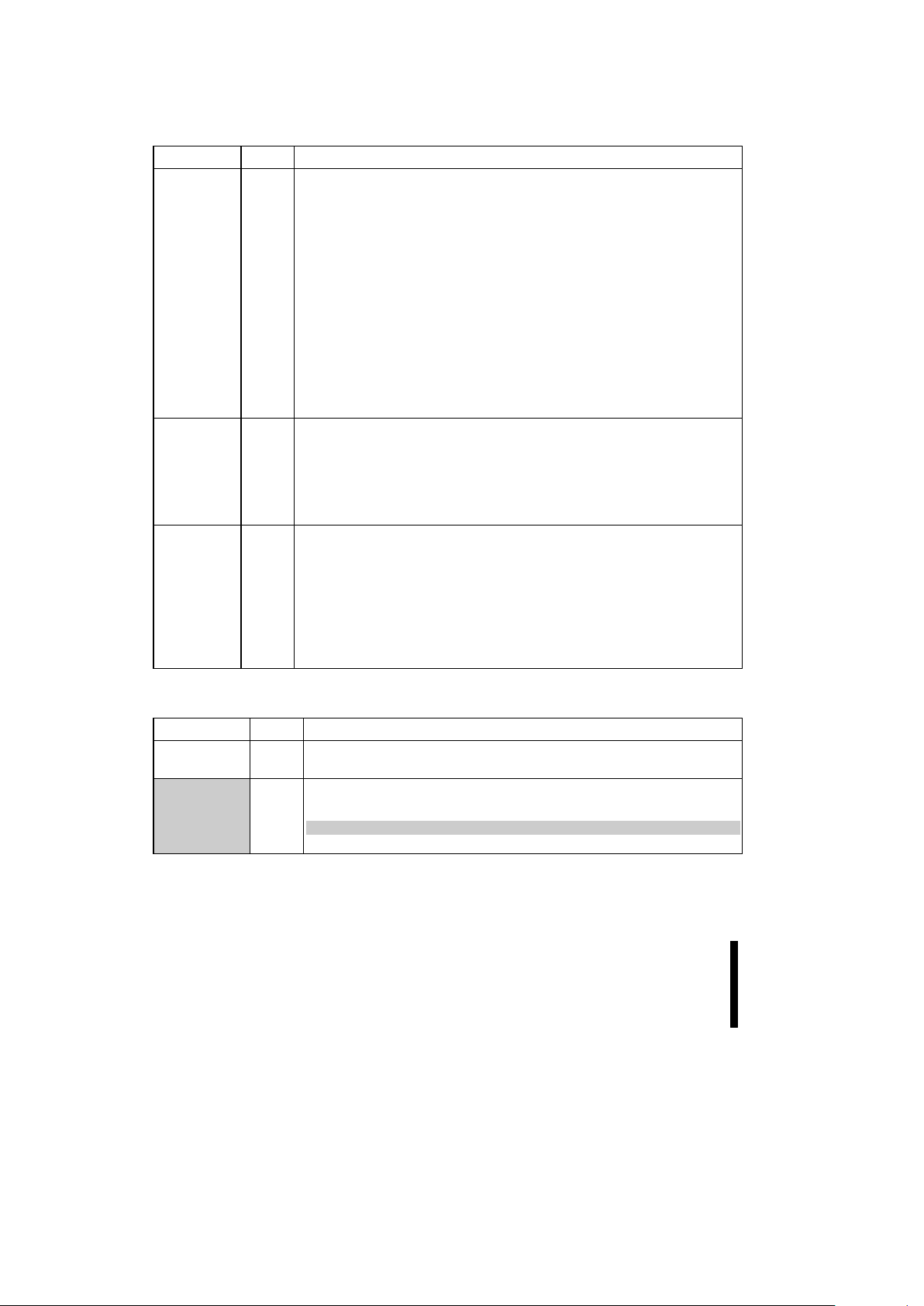

FLSHREQ# MEMREQ# Meaning

1 1 Idle

0 1 Flush buffers pointing towards PCI to

avoid ISA deadlock

1 0 82378ZB. Reserved

82379AB. GAT enabled or disabled: For buffer

coherency in APIC systems, the buffers

pointing to main memory must be flushed

and disabled for the duration of assertion.

0 0 GAT mode. Guarantee PCI Bus immediate

access to main memory (this may or may

not require the PCI-to-main memory

buffers to be flushed first depending on

the number of buffers).

FLSHREQ# t/s/o

FLUSH REQUEST: FLSHREQ# is generated by the SIO/SIO.A to command all of

the system's posted write buffers pointing towards the PCI Bus to be flushed. This is

required before granting the ISA Bus to an ISA master or the DMA. FLSHREQ# is

tri-stated from the leading edge of PCIRST#. FLSHREQ# remains tri-stated until

driven by the SIO/SIO.A. After PCIRST, FLSHREQ# is driven inactive

asynchronously from PCIRST# inactive.

MEMACK# I

MEMORY ACKNOWLEDGE: MEMACK# is the response handshake that indicates

to the SIO/SIO.A that the function requested over the MEMREQ# and/or

FLSHREQ# signals has been completed. In GAT mode (MEMREQ# and

FLSHREQ# asserted), the main memory bus is dedicated to the PCI Bus and the

system's posted write buffers pointing towards the PCI Bus have been flushed and

are disabled. In non-GAT mode (FLSHREQ# asserted alone), this means the

system's posted write buffers have been flushed and are disabled. In either case,

the SIO/SIO.A can now grant the ISA Bus to the requester.

2.3. Address Decoder Signal

Signal Name

Type

Description

MEMCS# O

MEMORY CHIP SELECT. MEMCS# is a programmable address decode signal

provided to a Host CPU bridge. A CPU bridge can use MEMCS# to forward a PCI

cycle to main memory behind the bridge. MEMCS# is driven one PCI clock after

FRAME# is sampled active (address phase) and is valid for one clock cycle before

going inactive. MEMCS# is high upon reset.

E 82378ZB (SIO) AND 82379 (SIO.A)

17

2.4. Power Management Signals

Signal Name

Type

Description

SMI# O

SYSTEM MANAGEMENT INTERRUPT: SMI# is asserted by the 82379AB in

response to one of many enableable hardware or software events. This signal is

driven low during a hard reset (PCIRST# asserted) and driven high when PCIRST#

is negated.

STPCLK# O

STOP CLOCK: STPCLK# is asserted by the 82379AB in response to one of many

enableable hardware or software events. STPCLK# connects directly to the CPU.

This signal is driven low during a hard reset (PCIRST# asserted) and driven high

when PCIRST# is negated.

EXTSMI# I

EXTERNAL SYSTEM MANAGEMENT INTERRUPT: EXTSMI# is a falling edge

triggered input to the 82379AB indicating that an external device is requesting the

system to enter SMM mode. This pin includes a weak internal pull-up resistor.

INIT I

INIT: INIT is an input to the SIO/SIO.A indicating that the CPU is actually being soft

reset. It is connected to the INIT pin of the CPU. This pin includes a weak internal

pull-up resistor.

2.5. ISA Interface Signals

Signal Name

Type

Description

AEN O

ADDRESS ENABLE: AEN is asserted during DMA cycles to prevent I/O slaves

from misinterpreting DMA cycles as valid I/O cycles. This signal is also driven high

during refresh cycles. AEN is driven low upon reset.

BALE O

BUS ADDRESS LATCH ENABLE: BALE is an active high signal asserted by the

SIO/SIO.A to indicate that the address (SA[19:0], LA[23:17]), AEN and SBHE#

signal lines are valid. The LA[23:17] address lines are latched on the trailing edge of

BALE. BALE remains asserted throughout DMA and ISA master cycles. BALE is

driven low upon reset.

SYSCLK O

SYSTEM CLOCK: SYSCLK is an output of the SIO/SIO.A component. The

frequencies supported are 6 to 8.33 MHz.

IOCHRDY I/O

I/O CHANNEL READY: Resources on the ISA Bus assert IOCHRDY to indicate

that additional time (wait states) is required to complete the cycle. IOCHRDY is tri-

stated upon reset.

IOCS16# I

16-BIT I/O CHIP SELECT: This signal is driven by I/O devices on the ISA Bus to

indicate that they support 16-bit I/O bus cycles.

IOCHK# I

I/O CHANNEL CHECK: IOCHK# can be driven by any resource on the ISA Bus.

When asserted, it indicates that a parity or an un-correctable error has occurred for

a device or memory on the ISA Bus. A NMI will be generated to the CPU if the NMI

generation is enabled.

IOR# I/O

I/O READ: IOR# is the command to an ISA I/O slave device that the slave may

drive data on to the ISA data bus (SD[15:0]). IOR# is driven high upon reset.

IOW# I/O

I/O WRITE: IOW# is the command to an ISA I/O slave device that the slave may

latch data from the ISA data bus (SD[15:0]). IOW# is driven high upon reset.

82378ZB (SIO) AND 82379AB (SIO.A) E

18

Signal Name

Type

Description

LA[23:17]

I/O

UNLATCHED ADDRESS: These address lines allow accesses to physical memory

on the ISA Bus up to 16 Mbytes. The LA[23:17] signals are at an unknown state

upon reset.

For the 82378ZB, these signals are undefined during DMA type "A", "B", and "F"

cycles.

SA[19:0]

I/O

SYSTEM ADDRESS BUS: These bi-directional address lines define the selection

with the granularity of one byte within the one Mbyte section of memory defined by

the LA[23:17] address lines. The address lines SA[19:17] that are coincident with

LA[19:17] are defined to have the same values as LA[19:17] for all memory cycles.

For I/O accesses, only SA[15:0] are used. SA[19:0] are outputs when the

SIO/SIO.A owns the ISA Bus. SA[19:0] are inputs when an external ISA Master

owns the ISA Bus. SA[19:0] are at an unknown state upon reset.

For the 82378ZB, SA[19:0] are undefined during DMA type "A", "B", or "F" cycles.

SBHE# I/O

SYSTEM BYTE HIGH ENABLE: SBHE# indicates, when asserted, that a byte is

being transferred on the upper byte (SD[15:8]) of the data bus. SBHE# is negated

during refresh cycles. SBHE# is at an unknown state upon reset.

MEMCS16# OD

MEMORY CHIP SELECT 16: MEMCS16# is a decode of LA[23:17] without any

qualification of the command signal lines. ISA slaves that are 16-bit memory devices

drive this signal low. The SIO/SIO.A drives this signal low during ISA master to PCI

memory cycles. MEMCS16# is at an unknown state upon reset.

MASTER#

(82378ZB

Only)

I

MASTER: An ISA Bus master asserts MASTER# to indicate that it has control of

the ISA Bus. Before the ISA master can assert MASTER#, it must first sample

DACK# active. Once MASTER# is asserted, the ISA master has control of the ISA

Bus until it negates MASTER#.

MEMR# I/O

MEMORY READ: MEMR# is the command to a memory slave that it may drive

data onto the ISA data bus. MEMR# is an output when the SIO/SIO.A is a master

on the ISA Bus. MEMR# is an input when an ISA master, other than the SIO/SIO.A,

owns the ISA Bus. This signal is also driven by the SIO/SIO.A during refresh

cycles.

For compatible timing mode DMA cycles, the SIO/SIO.A, as a master, asserts

MEMR# if the address is less than 16 Mbytes. This signal is not generated for

accesses to addresses greater than 16 Mbytes.

For the 82378ZB, MEMR# is not driven active during DMA type "A", "B", or "F"

cycles.

MEMW# I/O

MEMORY WRITE: MEMW# is the command to a memory slave that it may latch

data from the ISA data bus. MEMW# is an output when the SIO/SIO.A owns the ISA

Bus. MEMW# is an input when an ISA master, other than the SIO/SIO.A, owns the

ISA Bus.

For compatible timing mode DMA cycles, the SIO/SIO.A, as a master, asserts

MEMW# if the address is less than 16 Mbytes. This signal is not generated for

accesses to addresses greater than 16 Mbytes.

For the 82378ZB, MEMW# is not driven active during DMA type "A", "B", or "F"

cycles.

E 82378ZB (SIO) AND 82379 (SIO.A)

19

Signal Name

Type

Description

SMEMW# O

SYSTEM MEMORY WRITE: The SIO/SIO.A asserts SMEMW# to request a

memory slave to accept data from the data lines. If the access is below the 1 Mbyte

range (00000000−000FFFFFh) during DMA compatible, SIO/SIO.A master, or ISA

master cycles, the SIO/SIO.A asserts SMEMW#. SMEMW# is a delayed version of

MEMW#. SMEMW# is driven high upon reset.

SMEMR# O

SYSTEM MEMORY READ: The SIO/SIO.A asserts SMEMR# to request a memory

slave to accept data from the data lines. If the access is below the 1 Mbyte range

(00000000−000FFFFFh) during DMA compatible, SIO/SIO.A master, or ISA master

cycles, the SIO/SIO.A asserts SMEMR#. SMEMR# is a delay version of MEMR#.

Upon PCIRST# this signal is low. SMEMR# is driven high upon reset.

ZEROWS# I

ZERO WAIT STATES: An ISA slave asserts ZEROWS# after its address and

command signals have been decoded to indicate that the current cycle can be

shortened. A 16-bit ISA memory cycle can be reduced to two SYSCLKs. An 8-bit

memory or I/O cycle can be reduced to three SYSCLKs. ZEROWS# has no effect

during 16-bit I/O cycles.

If IOCHRDY and ZEROWS# are both asserted during the same clock, then

ZEROWS# is ignored and wait states are added as a function of IOCHRDY (i.e.,

IOCHRDY has precedence over ZEROWS#).

OSC I

OSCILLATOR: OSC is the 14.31818 MHz ISA clock signal. It is used by the

internal 8254 Timer, counters 0, 1, and 2.

RSTDRV O

RESET DRIVE: The SIO/SIO.A asserts RSTDRV to reset devices that reside on

the ISA Bus. The SIO/SIO.A asserts this signal when PCIRST# (PCI Reset) is

asserted. In addition, the SIO/SIO.A can be programmed to assert RSTDRV by

writing to the ISA Clock Divisor Register. Software should assert the RSTDRV

during configuration to reset the ISA Bus when changing the clock divisor. Note that

when RSTDRV is generated via the ISA Clock Divisor Register, software must

ensure that RSTDRV is driven active for a minimum of 1 µs.

SD[15:0]

I/O

SYSTEM DATA: SD[15:0] provide the 16-bit data path for devices residing on the

ISA Bus. SD[15:8] correspond to the high order byte and SD[7:0] correspond to the

low order byte. SD[15:0] are undefined during refresh. The SIO/SIO.A tri-states

SD[15:0] during reset.

2.6. DMA Signals

Signal Name

Type

Description

DREQ

[3:0,7:5]

I

DMA REQUEST: The DREQ lines are used to request DMA service from the

SIO/SIO.A DMA controller or for a 16-bit master to gain control of the ISA expansion

bus. The active level (high or low) is programmed via the DMA Command Register

(bit 6). The request must remain active until the appropriate DACK signal is

asserted.

DACK#

[3:0,7:5]

O

DMA ACKNOWLEDGE: The DACK output lines indicate that a request for DMA

service has been granted by the SIO/SIO.A or that a 16-bit master has been

granted the bus. The active level (high or low) is programmed via the DMA

Command Register (bit 7). These lines should be used to decode the DMA slave

device with the IOR# or IOW# line to indicate selection. Upon PCIRST#, these lines

are set inactive (high).

82378ZB (SIO) AND 82379AB (SIO.A) E

20

Signal Name

Type

Description

EOP

(82378ZB)

I/O

END OF PROCESS: EOP is bi-directional, acting in one of two modes, and is

directly connected to the TC line of the ISA Bus. DMA slaves assert EOP to the

SIO/SIO.A to terminate DMA cycles. The SIO/SIO.A asserts EOP to DMA slaves

as a terminal count indicator.

EOP-IN MODE: For all transfer types during DMA, the SIO/SIO.A samples EOP. If

it is sampled asserted, the transfer is terminated.

TC-OUT MODE: The SIO asserts EOP after a new address has been output, if the

byte count expires with that transfer. The EOP (TC) remains asserted until AEN is

negated, unless AEN is negated during an autoinitialization. EOP (TC) is negated

before AEN is negated during an autoinitialization.

When all the DMA channels are not in use, the EOP signal is in output mode and

negated (low). After PCIRST#, EOP is in output mode and inactive.

TC

(82379AB)

O

TERMINAL COUNT: The SIO.A asserts TC after a new address has been output, if

the byte count expires with that transfer. TC remains asserted until AEN is negated,

unless AEN is negated during an autoinitialization. TC is negated before AEN is

negated during an autoinitialization. After PCIRST#, EOP is in output mode and

inactive.

REFRESH# I/O

REFRESH: As an output, REFRESH# is used by the SIO/SIO.A to indicate when a

refresh cycle is in progress. It should be used to enable the SA[15:0] address to the

row address inputs of all banks of dynamic memory on the ISA Bus. Thus, when

MEMR# is asserted, the entire expansion bus dynamic memory is refreshed.

Memory slaves must not drive any data onto the bus during refresh. As an output,

this signal is driven directly onto the ISA Bus. This signal is an output only when the

SIO/SIO.A DMA refresh is a master on the bus responding to an internally

generated request for refresh.

As an input, REFRESH# is driven by 16-bit ISA Bus masters to initiate refresh

cycles. Upon PCIRST#, this signal is tri-stated.

2.7. Timer Signal

Signal Name

Type

Description

SPKR

(82378ZB)

SPKR/TESTO

(82379AB)

O

SPEAKER DRIVE: The SPKR signal, in the 82378ZB and 82379AB, is the output of

counter 2 and has a 24 mA drive capability. Upon reset, its output state is 0.

For the 82379AB in test mode, this pin is the output pin used during NAND tree

testing.

E 82378ZB (SIO) AND 82379 (SIO.A)

21

2.8. Interrupt Controller Signals

Signal Name

Type

Description

IRQ[15,14,11:

9, 7:3,1]

I

INTERRUPT REQUEST: The IRQ signals provide both system board components

and ISA Bus I/O devices with a mechanism for asynchronously interrupting the

CPU. The assertion mode of these inputs (edge or level triggered) is programmable

via the ELCR Register. Upon PCIRST#, the IRQ lines are placed in edge-triggered

mode.

NOTE:

1. For the 82378ZB, an active IRQ input must remain asserted until after the interrupt is

acknowledged. If the input goes inactive before this time, a DEFAULT IRQ7 occurs when

the CPU acknowledges the interrupt.

2. For the 82379AB, A low to high transition on IRQ1 is latched by the 82379AB. The latch is

cleared by a read of address 60h.

3. Refer to the Utility Bus Signal descriptions for IRQ12 and IRQ13 signal descriptions.

IRQ8# I

INTERRUPT REQUEST EIGHT SIGNAL: IRQ8# is an active low interrupt input.

The assertion mode of these inputs (edge or level triggered) is programmable via

the ELCR Register. Upon PCIRST#, the IRQ lines are placed in edge-triggered

mode.

NOTE:

1. For the 82378ZB, IRQ8# must remain asserted until after the interrupt is acknowledged. If

the input goes inactive before this time, a DEFAULT IRQ7 will occur when the CPU

acknowledges the interrupt.

2. For the 82379AB, this pin requires an external 8.2 KΩ pull-up resistor.

INT O

CPU INTERRUPT: INT is driven by the SIO/SIO.A to signal the CPU that an

interrupt request is pending and needs to be serviced. It is asynchronous with

respect to SYSCLK or PCICLK and is always an output. The interrupt controller

must be programmed following a reset to ensure that INT is at a known state. Upon

PCIRST#, INT is driven low.

NMI O

NON-MASKABLE INTERRUPT: NMI is used to force a non-maskable interrupt to

the CPU. The SIO/SIO.A generates an NMI when either SERR# or IOCHK# is

asserted, depending on how the NMI Status and Control Register is programmed.

The CPU detects an NMI when it detects a rising edge on NMI. After the NMI

interrupt routine processes the interrupt, the NMI status bits in the NMI Status and

Control Register are cleared by software. The NMI interrupt routine must read this

register to determine the source of the interrupt. The NMI is reset by setting the

corresponding NMI source enable/disable bit in the NMI Status and Control

Register. To enable NMI interrupts, the two NMI enable/disable bits in the register

must be set to 0, and the NMI mask bit in the NMI Enable/Disable and Real-Time

Clock Address Register must be set to 0. Upon PCIRST#, this signal is driven low.

82378ZB (SIO) AND 82379AB (SIO.A) E

22

2.9. APIC Bus Signals (82379AB Only)

Pin Name

Type

Description

APICCLK in

APIC BUS CLOCK: APICCLK provides the timing reference for the APIC Bus.

Changes on APICD[1:0]# are synchronous to the rising edge of APICCLK.

APICD[1:0]

od

APIC DATA: APICD1 and APICD0 are the APIC data bus signals. Interrupt

messages are sent/received over this bus. APICD1 has a weak pull-down resistor.

These signals require external pull-ups (330 Ω recommended) to the 3.3V rail.

These signals are tri-stated during a hard reset.

2.10. Utility Bus Signals

Signal Name

Type

Description

UBUSTR O

UTILITY DATA BUS TRANSMIT/RECEIVE: UBUSTR is tied directly to the

direction control of a 74F245 that buffers the utility data bus, UD[7:0]. UBUSTR is

asserted for all I/O read cycles (regardless if a utility bus device has been decoded).

UBUSTR is asserted for memory cycles only if BIOS space has been decoded. For

PCI and ISA master-initiated read cycles, UBUSTR is asserted from the falling edge

of either IOR# or MEMR#, depending on the cycle type (driven from MEMR# only if

BIOS space has been decoded). When the rising edge of IOR# or MEMR# occurs,

the SIO/SIO.A negates UBUSTR. For DMA read cycles from the Utility Bus,

UBUSTR is asserted when DACKx# is asserted and negated when DACKx# is

negated. At all other times, UBUSTR is negated. Upon PCIRST#, this signal is

driven low.

UBUSOE# O

UTILITY DATA BUS OUTPUT ENABLE: UBUSOE# is tied directly to the output

enable of a 74F245 that buffers the utility data bus, UD[7:0], from the system data

bus, SD[7:0]. UBUSOE# is asserted anytime a SIO/SIO.A supported Utility Bus

device is decoded, and the devices decode is enabled in the Utility Bus Chip Select

Enable Registers. UBUSOE# is asserted from the falling edge of the ISA

commands (IOR#, IOW#, MEMR#, or MEMW#) for PCI and ISA master-initiated

cycles. UBUSOE# is negated from the rising edge of the ISA command signals for

SIO/SIO.A-initiated cycles and the SA[16:0] and LA[23:17] address for ISA master-

initiated cycles. For DMA cycles, UBUSOE# is asserted when DACK2# is asserted

and negated when DACK2# negated. UBUSOE# is not driven active under the

following conditions:

NOTES:

1. During an I/O access to the floppy controller, if DSKCHG is sampled low at reset.

2. If the Digital Output Register is programmed to ignore DACK2#.

3. During an I/O read access to floppy location 3F7h (primary) or 377h (secondary), if theIDE

decode space is disabled (i.e., IDE is not resident on the Utility Bus).

4. During any access to a utility bus peripheral in which its decode space has been disabled.

Upon a PCIRST#, this signal is driven inactive (high).

ECSADDR

[2:0]

O

ENCODED CHIP SELECTS: ECSADDR[2:0] are the encoded chip selects and/or

control signals for the Utility Bus peripherals supported by the SIO/SIO.A. The

binary code formed by the three signals indicates which Utility Bus device is

selected. These signals tie to the address inputs of two external 74F138 decoder

chips and are driven valid/invalid from the SA[16:0] and LA[23:17] address lines.

Upon PCIRST#, these signals are driven high.

E 82378ZB (SIO) AND 82379 (SIO.A)

23

Signal Name

Type

Description

ECSEN# O

ENCODED CHIP SELECT ENABLE: ECSEN# is used to determine which of the

two external 74F138 decoders is to be selected. ECSEN# is driven low to select

decoder 1 and driven high to select decoder 2. This signal is driven valid/invalid

from the SA[16:0] and LA[23:17] address lines (except for the generation of

RTCALE#, in which case, ECSEN# is driven active based on IOW# falling, and

remains active for two SYSCLKs). During a non-valid address or during an access

not targeted for the Utility Bus, this signal is driven high. Upon PCIRST#, this signal

is driven high.

ALT_RST#

O

ALTERNATE RESET: ALT_RST# is used to reset the CPU under program control.

This signal is AND'ed together externally with the reset signal (KBDRST#) from the

keyboard controller to provide a software means of resetting the CPU. This provides

a faster means of reset than is provided by the keyboard controller. Writing a 1 to bit

0 in the Port 92 Register causes this signal to pulse low for approximately 4

SYSCLKs. Before another ALT_RST# pulse can be generated, bit 0 must be set to

0. Upon PCIRST#, this signal is driven inactive high (bit 0 in the Port 92 Register is

set to 0).

ALT_A20

O

ALTERNATE A20: ALT_A20 is used to force A20M# to the CPU low for support of

real mode compatible software. This signal is externally OR'ed with the A20GATE

signal from the keyboard controller and CPURST to control the A20M# input of the

CPU. Writing a 0 to bit 1 of the Port 92 Register forces ALT_A20 low. ALT_A20 low

drives A20M# to the CPU low, if A20GATE from the keyboard controller is also low.

Writing a 1 to bit 1 of the Port 92 Register force ALT_A20 high. ALT_A20 high drives

A20M# to the CPU high, regardless of the state of A20GATE from the keyboard

controller. Upon reset, this signal is driven low.

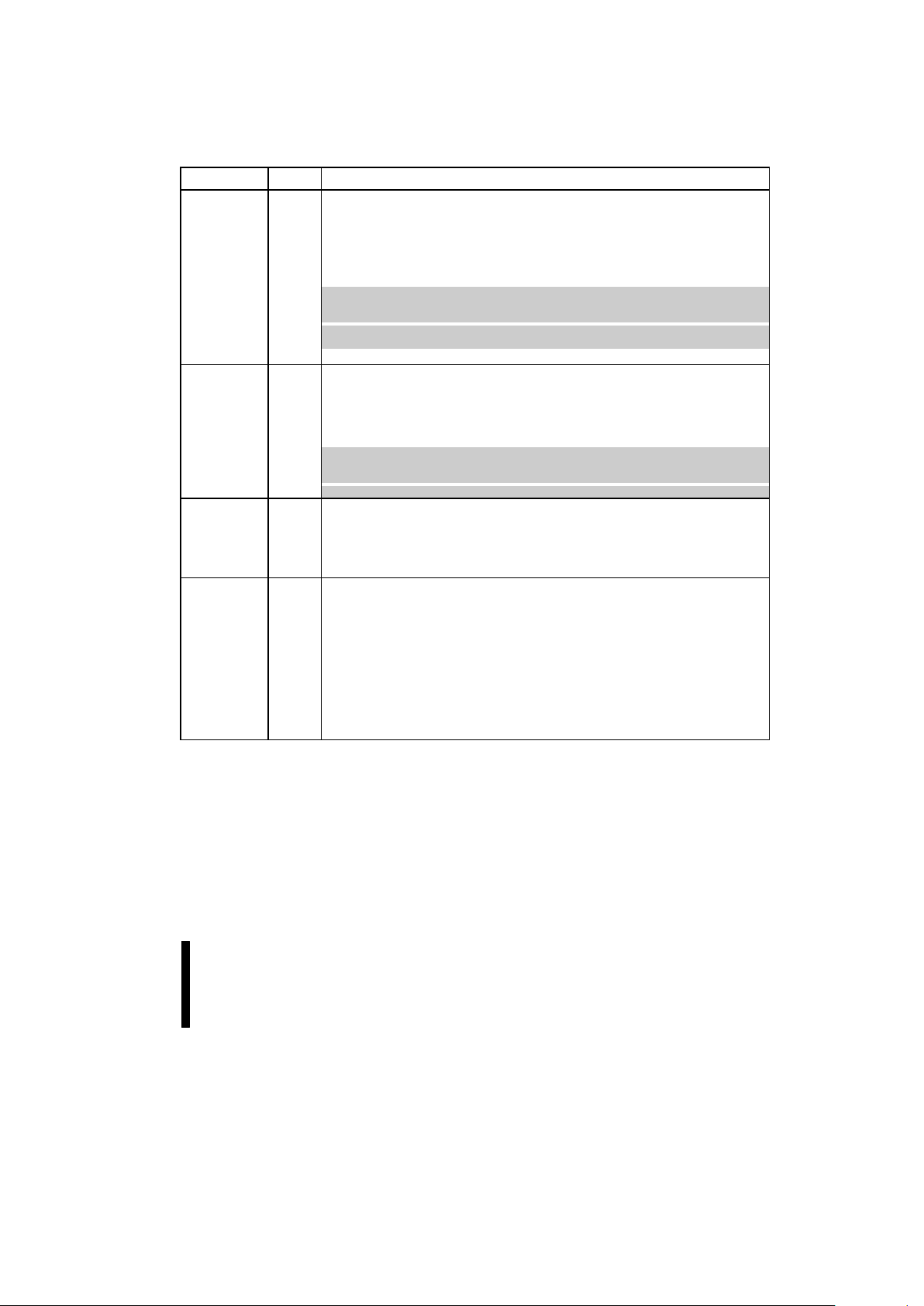

DSKCHG I

DISK CHANGE: DSKCHG is tied directly to the DSKCHG signal of the floppy

controller. This signal is inverted and driven on SD7 during I/O read cycles to floppy

address locations 3F7h (primary) or 377h (secondary) as shown in the table below.

Note that the primary and secondary locations are programmed in the Utility Bus

Address Decode Enable/Disable Register "A".

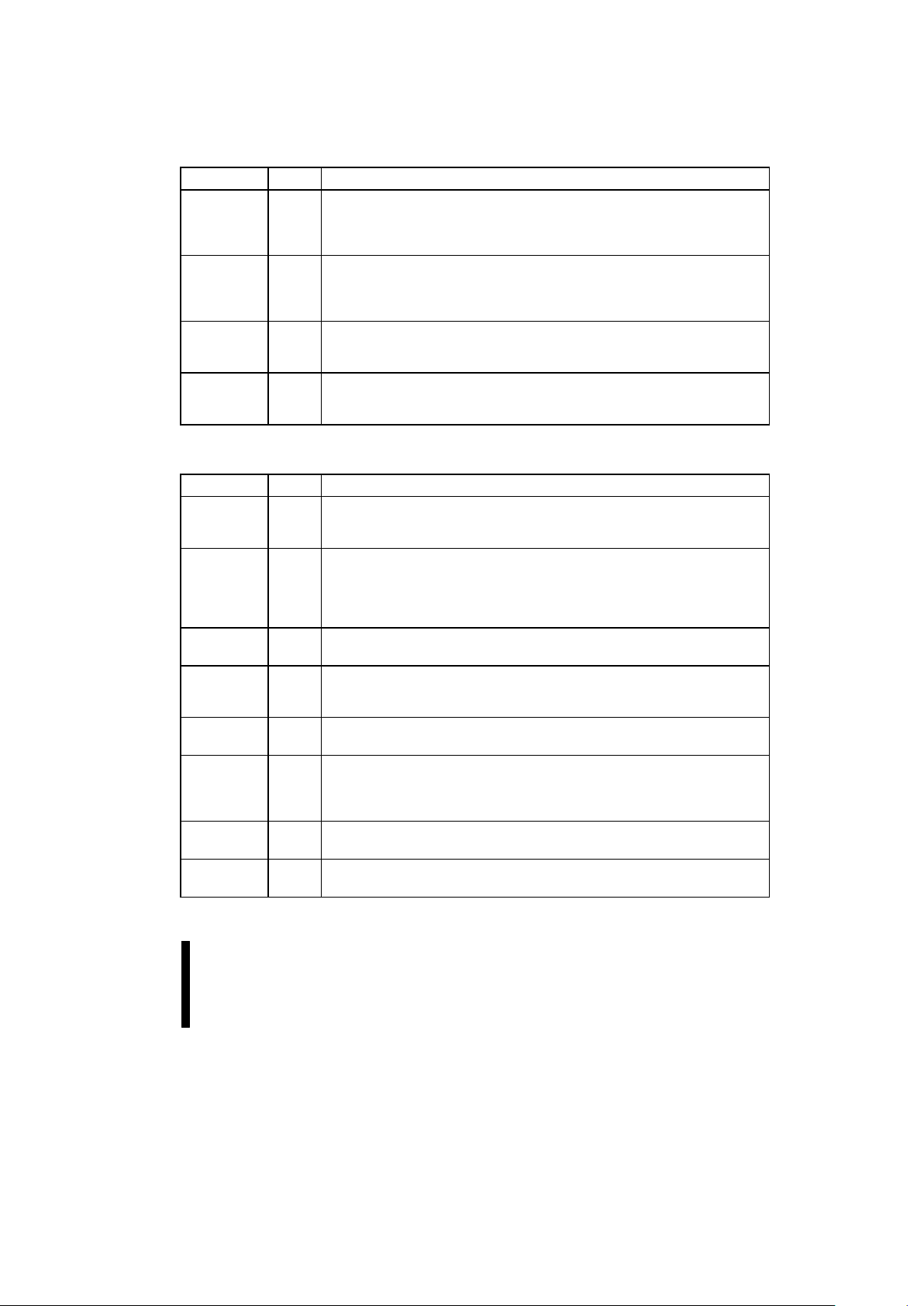

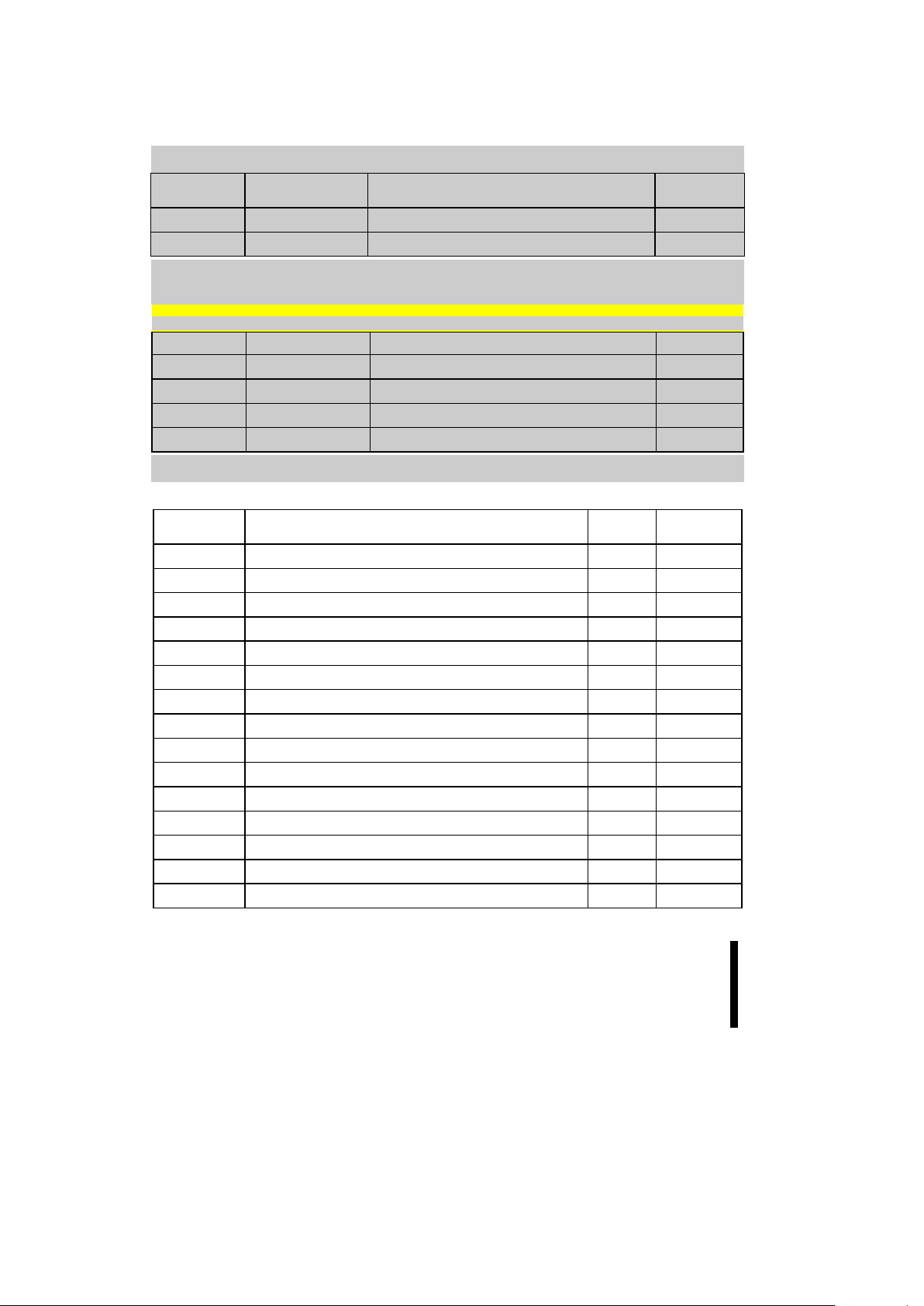

FLOPPYCS# IDECSx# State of SD7 (output) State of UBUSOE#

Decode Decode

Enabled Enabled Tri-stated Enabled

Enabled Disabled Driven via DSKCHG Disabled

Disabled Enabled Tri-stated Enabled (note)

Disabled Disabled Tri-stated Disabled

NOTE:

For this mode to be supported, extra logic is required to disable the U-Bus transceiver for

accesses to 3F7/377. This is necessary because of potential contention between the Utility

Bus buffer and a floppy on the ISA Bus driving the system bus at the same time during shared

I/O accesses.

This signal is also used to determine if the floppy controller is present on the Utility

Bus. It is sampled on the trailing edge of PCIRST#, and if high, the floppy is present.

For systems that do not support a floppy via the SIO/SIO.A, this pin should be

strapped low. If sampled low, the SD7 function, UBUSOE#, and ECSADDR[2:0]

signals will not be enabled for DMA or programmed I/O accesses to the floppy disk

controller. This condition overrides the floppy decode enable bits in the Utility Bus

Chip Select A.

82378ZB (SIO) AND 82379AB (SIO.A) E

24

Signal Name

Type

Description

FERR#/

IRQ13

I

NUMERIC COPROCESSOR ERROR/IRQ13: This signal has two separate

functions, depending on bit 5 in the ISA Clock Divisor Register. This pin functions as

a FERR# signal supporting coprocessor errors, if this function is enabled (bit 5=1),

or as an external IRQ13, if the coprocessor error function is disabled (bit 5=0).

If programmed to support coprocessor error reporting, this signal is tied to the

coprocessor error signal on the CPU. If FERR# is asserted by the coprocessor

inside the CPU, the SIO/SIO.A generates an internal IRQ13 to its interrupt controller

unit. The SIO/SIO.A then asserts the INT output to the CPU. Also, in this mode,

FERR# gates the IGNNE# signal to ensure that IGNNE# is not asserted to the CPU

unless FERR# is active. When FERR# is asserted, the SIO/SIO.A asserts INT to

the CPU as an IRQ13. IRQ13 continues to be asserted until a write to F0h has been

detected.

If the coprocessor error reporting is disabled, FERR# can be used by the system as

IRQ13. Upon PCIRST#, this signal provides the standard IRQ13 function. This

signal should be pulled high with an external 8.2K Ω pull-up resistor if the IRQ13

mode is used or the pin is left floating.

IGNNE# O

IGNORE ERROR: This signal is connected to the ignore error pin of the CPU.

IGNNE# is only used if the SIO/SIO.A coprocessor error reporting function is

enabled in the ISA Clock Divisor Register (bit 5=1). If FERR# is active, indicating a

coprocessor error, a write to the Coprocessor Error Register (F0h) causes the

IGNNE# to be asserted. IGNNE# remains asserted until FERR# is negated. If

FERR# is not asserted when the Coprocessor Error Register is written, the IGNNE#

is not asserted. IGNNE# is driven high upon a reset.

IRQ12/M I

INTERRUPT REQUEST/MOUSE INTERRUPT: In addition to providing the

standard interrupt function as described in the pin description for IRQ[15,14, 11:9,

7:3, 1], this pin also provides a mouse interrupt function. Bit 4 in the ISA Clock

Divisor Register determines the functionality of IRQ12/M.

When the mouse interrupt function is selected, a low-to-high transition on this signal

is latched by the SIO/SIO.A and an INT is generated to the CPU as IRQ12. An

interrupt will continue to be generated until a PCIRST# or an I/O read access to

address 60h (falling edge of IOR#) is detected. After a PCIRST#, this pin provides

the standard IRQ12 function.

2.11. Test Signals

Signal Name

Type

Description

TEST I

TEST: The TEST signal is used to tri-state all of the SIO/SIO.A outputs. During

normal operation, this input should be tied to ground.

TESTO

(82378ZB)

SPKR/TESTO

(82379AB)

O

TEST OUTPUT: For both the 82378ZB and 82379AB, this is the output pin used

during NAND tree testing.

For the 82379AB, when not in test mode, this pin is the speaker output.

E 82378ZB (SIO) AND 82379 (SIO.A)

25

3.0. REGISTER DESCRIPTION

The SIO/SIO.A contains PCI configuration Registers and ISA-Compatible Registers. In addition, the SIO.A

contains I/O APIC Registers. Some of the SIO/SIO.A configuration and ISA-Compatible Registers contain

reserved bits. These bits are labeled "Reserved". Software must take care to deal correctly with bit-encoded

fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely

on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit

positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new

values for other bit positions, and the data then written back.

In addition to reserved bits within a register, the SIO/SIO.A contains address locations in the PCI configuration

space that are marked "Reserved" (Table 3). The SIO/SIO.A responds to accesses to these address locations

by completing the PCI cycle. However, reads of reserved address locations yield all zeroes and writes have no

effect on the SIO/SIO.A.

The SIO/SIO.A, upon receiving a hard reset (PCIRST# signal), sets its internal registers to pre-determined

default states. The default values are indicated in the individual register descriptions.

Configuration Registers

The configuration registers (Table 3) are located in PCI configuration space and are only accessible from the

PCI Bus. Addresses for configuration registers are offset values that appear on AD[7:2] and C/BE#[3:0]. The

configuration registers can be accessed as Byte, Word (16-bit), or Dword (32-bit) quantities. All multi-byte

numeric fields use "little-endian" ordering (i.e., lower addresses contain the least significant parts of the fields).

ISA-Compatible Registers

The ISA-Compatible Registers include DMA Registers, Timer Registers, Interrupt Controller Registers, and NonMaskable Interrupt and Utility Bus Support Registers (Table 6). All of these registers are accessible from the PCI

Bus. In addition, some of the registers are accessible from the ISA Bus. Except for the BIOS timer Registers, the

ISA-Compatible Registers can only be accessed as byte quantities. If a PCI master attempts a multi-byte access

(i.e., more than one Byte Enable signal asserted), the SIO/SIO.A responds with a target-abort. The BIOS Timer