Intel Corporation SB82375EB, SB82375SB Datasheet

*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

March 1996COPYRIGHT©INTEL CORPORATION, 1996 Order Number: 290477-004

82375EB/82375SB PCI-EISA BRIDGE (PCEB)

Y

Provides the Bridge Between the PCI

Local Bus and EISA Bus

Y

100% PCI and EISA Compatible

Ð PCI and EISA Master/Slave Interface

Ð Directly Drives 10 PCI Loads and 8

EISA Slots

Ð Supports PCI from 25 to 33 MHz

Y

Data Buffers Improve Performance

Ð Four 32-bit PCI-to-EISA Posted Write

Buffers

Ð Four 16-byte EISA-to-PCI Read/Write

Line Buffers

Ð EISA-to-PCI Read Prefetch

Ð EISA-to-PCI and PCI-to-EISA Write

Posting

Y

Data Buffer Management Ensures Data

Coherency

Ð Flush Posted Write Buffers

Ð Flush or Invalidate Line Buffers

Ð System-Wide Data Buffer Coherency

Control

Y

Burst Transfers on both the PCI and

EISA Buses

Y

32-Bit Data Paths

Y

Integrated EISA Data Swap Buffers

Y

Arbitration for PCI Devices

Ð Supports Six PCI Masters

Ð Fixed, Rotating, or a Combination of

the Two

Ð Supports External PCI Arbiter and

Arbiter Cascading

Y

PCI and EISA Address Decoding and

Mapping

Ð Positive Decode of Main Memory

Areas (MEMCS

Ý

Generation)

Ð Four Programmable PCI Memory

Space Regions

Ð Four Programmable PCI I/O Space

Regions

Y

Programmable Main Memory Address

Decoding

Ð Main Memory Sizes up to

512 MBytes

Ð Access Attributes for 15 Memory

Segments in First 1 MByte of Main

Memory

Ð Programmable Main Memory Hole

Y

Integrated 16-bit BIOS Timer

Y

Only Available as Part of a Supported

Kit

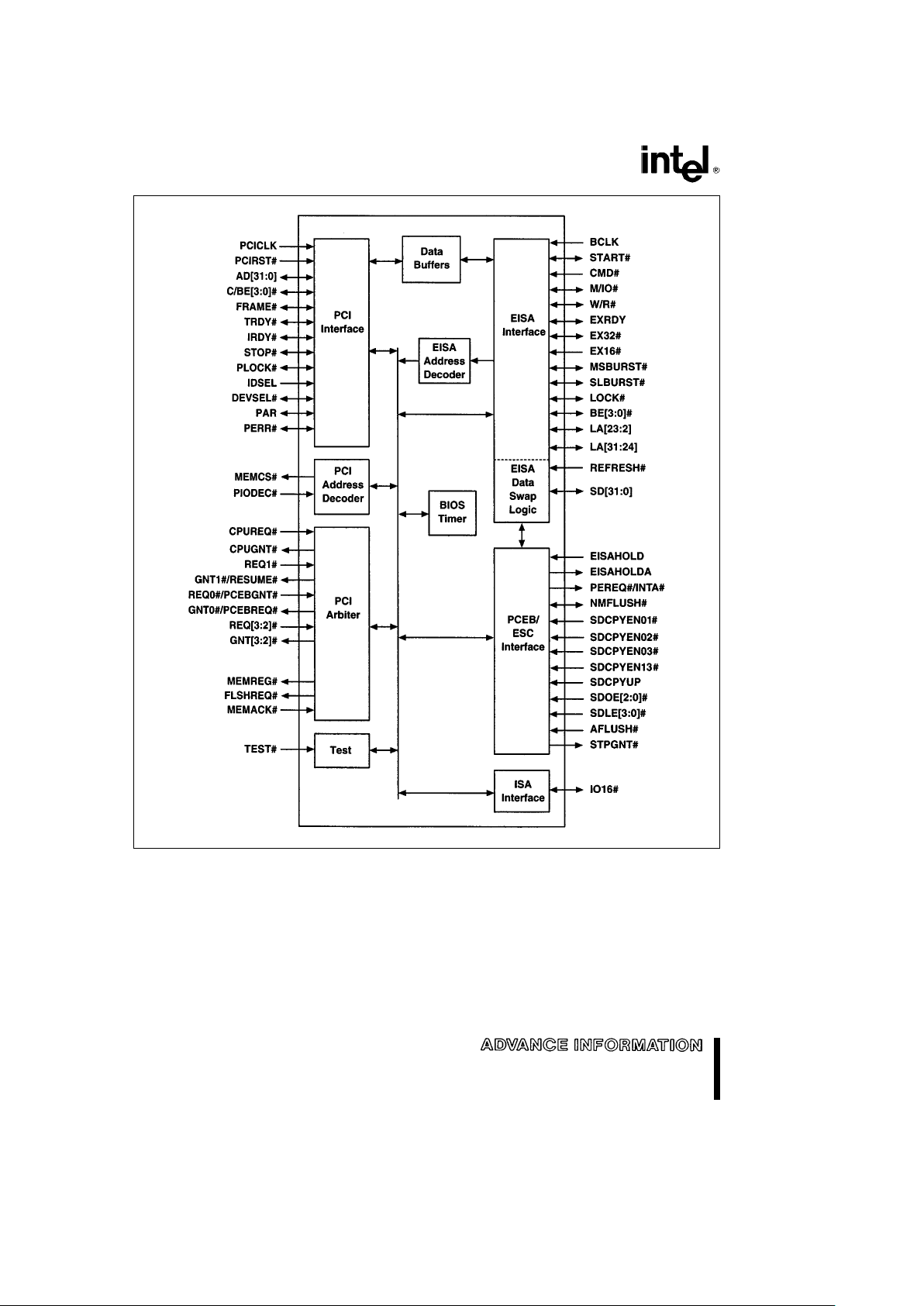

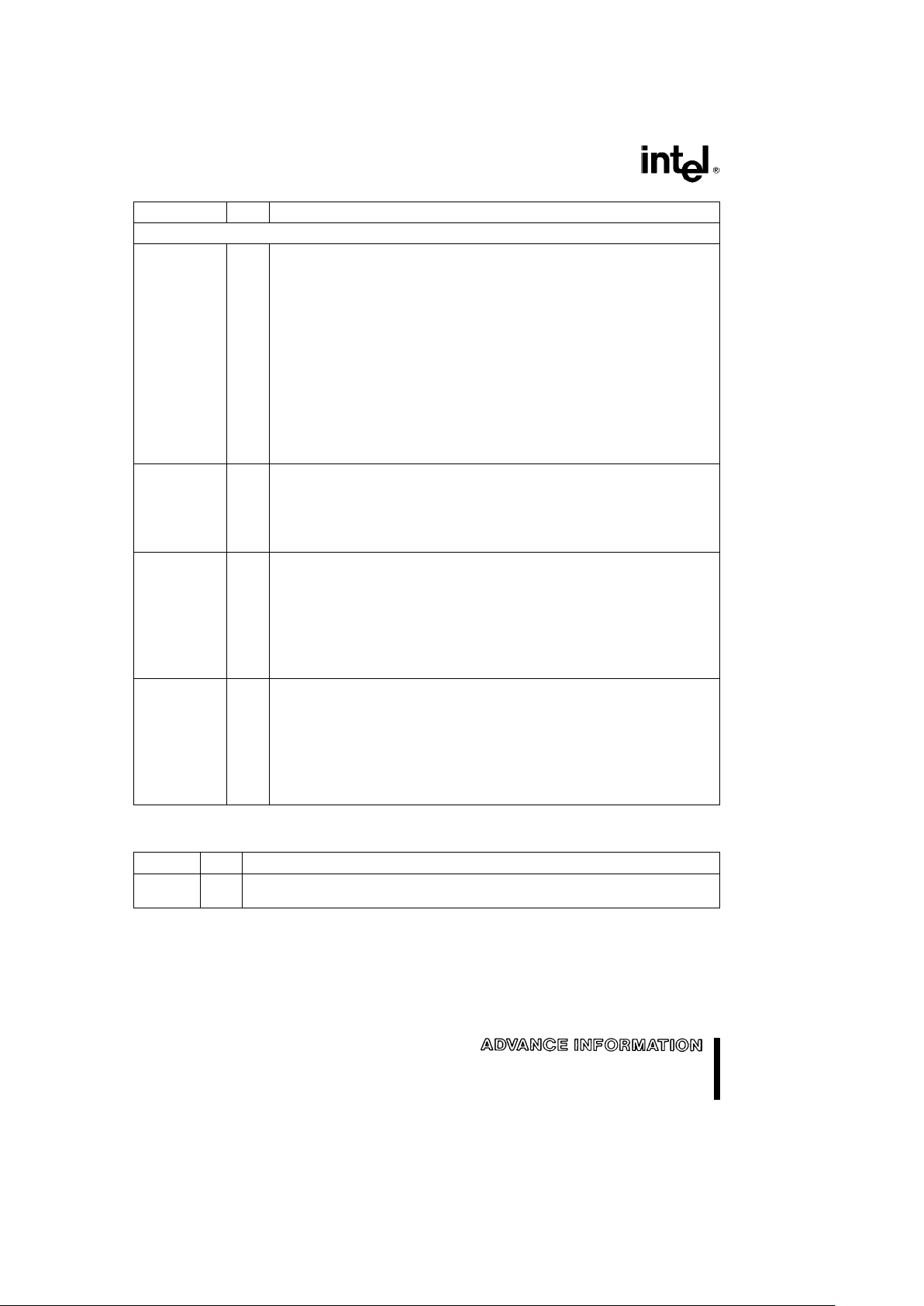

The 82375EB/SB PCI-EISA Bridge (PCEB) provides the master/slave functions on both the PCI Local Bus

and the EISA Bus. Functioning as a bridge between the PCI and EISA buses, the PCEB provides the address

and data paths, bus controls, and bus protocol translation for PCI-to-EISA and EISA-to-PCI transfers. Extensive data buffering in both directions increases system performance by maximizing PCI and EISA Bus efficiency and allowing concurrency on the two buses. The PCEB’s buffer management mechanism ensures data

coherency. The PCEB integrates central bus control functions including a programmable bus arbiter for the

PCI Bus and EISA data swap buffers for the EISA Bus. Integrated system functions include PCI parity generation, system error reporting, and programmable PCI and EISA memory and I/O address space mapping and

decoding. The PCEB also contains a BIOS Timer that can be used to implement timing loops. The PCEB is

intended to be used with the EISA System Component (ESC) to provide an EISA I/O subsystem interface.

This document describes both the 82375EB and 82375SB components. Unshaded areas describe the

82375EB. Shaded areas, like this one, describe the 82375SB operations that differ from the 82375EB.

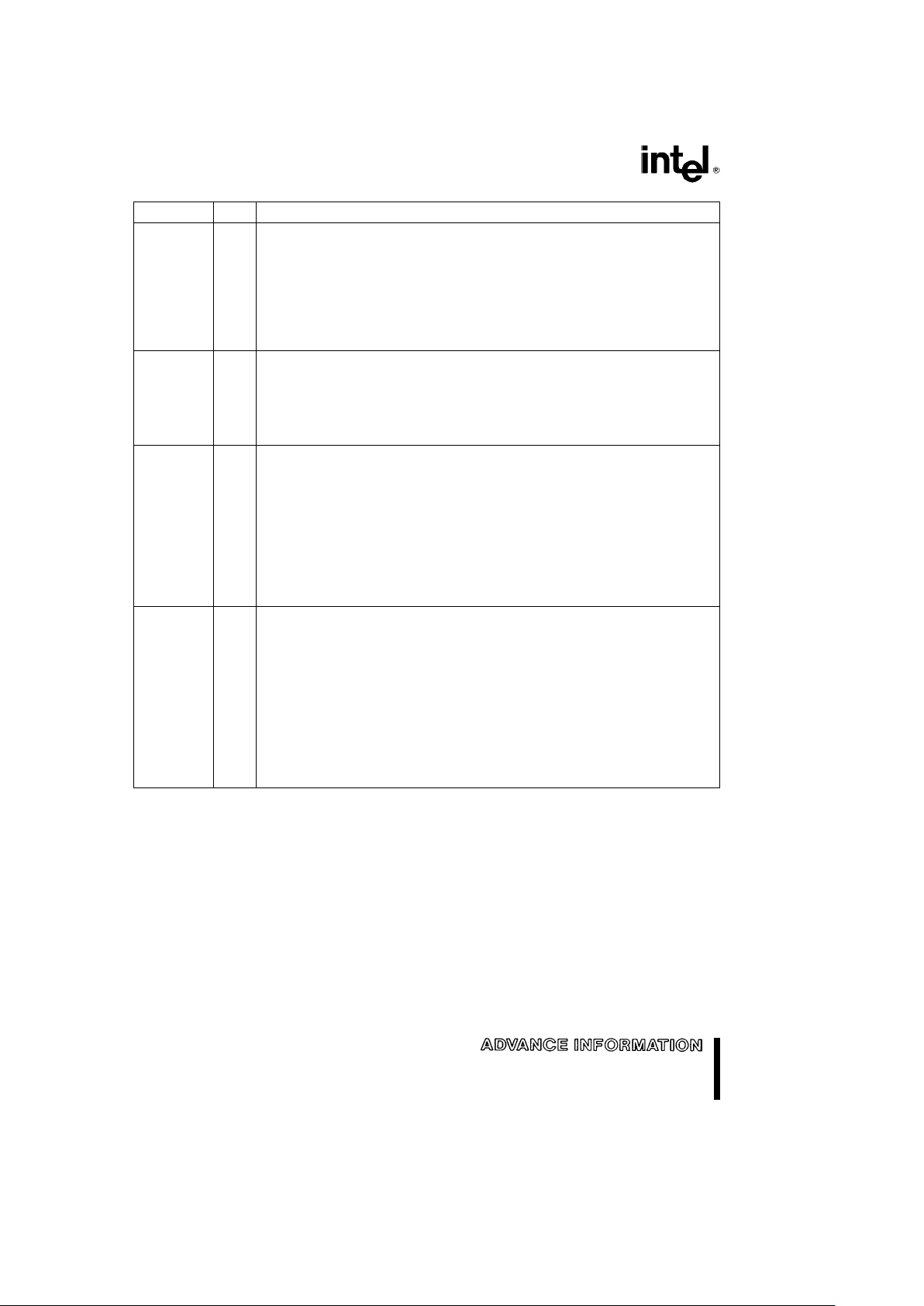

82375EB/SB

290477– 1

PCEB Simplified Block Diagram

2

82375EB/82375SB PCI-EISA BRIDGE (PCEB)

CONTENTS PAGE

1.0 ARCHITECTURAL OVERVIEW

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 8

1.1 PCEB Overview ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 10

1.2 ESC Overview ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 12

2.0 SIGNAL DESCRIPTION АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 14

2.1 PCI Bus Interface Signals АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

2.2 PCI Arbiter Signals АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 18

2.3 Address Decoder Signals АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 19

2.4 EISA Interface Signals ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 20

2.5 ISA Interface Signals АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 23

2.6 PCEB/ESC Interface Signals АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 24

2.7 Test Signal АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 26

3.0 REGISTER DESCRIPTION ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 27

3.1 Configuration Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 27

3.1.1 VIDÐVENDOR IDENTIFICATION REGISTER ААААААААААААААААААААААААААААААААААААА 29

3.1.2 DIDÐDEVICE IDENTIFICATION REGISTER АААААААААААААААААААААААААААААААААААААА 29

3.1.3 PCICMDÐPCI COMMAND REGISTER ААААААААААААААААААААААААААААААААААААААААААА 30

3.1.4 PCISTSÐPCI STATUS REGISTER ААААААААААААААААААААААААААААААААААААААААААААААА 31

3.1.5 RIDÐREVISION IDENTIFICATION REGISTER ААААААААААААААААААААААААААААААААААА 31

3.1.6 MLTÐMASTER LATENCY TIMER REGISTER АААААААААААААААААААААААААААААААААААА 32

3.1.7 PCICONÐPCI CONTROL REGISTER ААААААААААААААААААААААААААААААААААААААААААААА 32

3.1.8 ARBCONÐPCI ARBITER CONTROL REGISTER ААААААААААААААААААААААААААААААААА 33

3.1.9 ARBPRIÐPCI ARBITER PRIORITY CONTROL REGISTER ААААААААААААААААААААААА 34

3.1.10 ARBPRIXÐPCI ARBITER PRIORITY CONTROL EXTENSION REGISTER ААААААА 35

3.1.11 MCSCONÐMEMCSÝCONTROL REGISTER ААААААААААААААААААААААААААААААААААА 35

3.1.12 MCSBOHÐMEMCSÝBOTTOM OF HOLE REGISTER АААААААААААААААААААААААААА 36

3.1.13 MCSTOHÐMEMCSÝTOP OF HOLE REGISTER АААААААААААААААААААААААААААААААА 37

3.1.14 MCSTOMÐMEMCSÝTOP OF MEMORY REGISTER ААААААААААААААААААААААААААА 37

3.1.15 EADC1ÐEISA ADDRESS DECODE CONTROL 1 REGISTER АААААААААААААААААААА 38

3.1.16 IORTÐISA I/O RECOVERY TIMER REGISTER ААААААААААААААААААААААААААААААААА 39

3.1.17 MAR1ÐMEMCSÝATTRIBUTE REGISTERÝ1 ААААААААААААААААААААААААААААААААА 40

3.1.18 MAR2ÐMEMCSÝATTRIBUTE REGISTERÝ2 ААААААААААААААААААААААААААААААААА 40

3.1.19 MAR3ÐMEMCSÝATTRIBUTE REGISTERÝ3 ААААААААААААААААААААААААААААААААА 41

3.1.20 PDCONÐPCI DECODE CONTROL REGISTER АААААААААААААААААААААААААААААААААА 42

3.1.21 EADC2ÐEISA ADDRESS DECODE CONTROL EXTENSION REGISTER АААААААА 43

3

CONTENTS PAGE

3.1.22 EPMRAÐEISA-TO-PCI MEMORY REGION ATTRIBUTES REGISTER

ААААААААААА 44

3.1.23 MEMREGN[4:1]ÐEISA-TO-PCI MEMORY REGION ADDRESS REGISTERS ÀÀÀÀ 45

3.1.24 IOREGN[4:1]ÐEISA-TO-PCI I/O REGION ADDRESS REGISTERS АААААААААААААА 46

3.1.25 BTMRÐBIOS TIMER BASE ADDRESS REGISTER АААААААААААААААААААААААААААААА 46

3.1.26 ELTCRÐEISA LATENCY TIMER CONTROL REGISTER ААААААААААААААААААААААААА 47

3.2 I/O Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 47

3.2.1 BIOSTMÐBIOS TIMER REGISTER ААААААААААААААААААААААААААААААААААААААААААААААА 47

4.0 ADDRESS DECODING АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 48

4.1 PCI Cycle Address Decoding АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 50

4.1.1 MEMORY SPACE ADDRESS DECODING АААААААААААААААААААААААААААААААААААААААА 51

4.1.1.1 Main Memory Decoding (MEMCSÝ) ААААААААААААААААААААААААААААААААААААААААА 51

4.1.1.2 BIOS Memory Space АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 54

4.1.1.3 Subtractively And Negatively Decoded Cycles To EISA ААААААААААААААААААААААА 54

4.1.2 PCEB CONFIGURATION REGISTERS АААААААААААААААААААААААААААААААААААААААААААА 56

4.1.3 PCEB I/O REGISTERS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 56

4.1.4 POSITIVELY DECODED COMPATIBILITY I/O REGISTERS ААААААААААААААААААААААА 56

4.1.4.1 ESC Resident PIC Registers ААААААААААААААААААААААААААААААААААААААААААААААААА 57

4.1.4.2 EISA Resident IDE Registers ААААААААААААААААААААААААААААААААААААААААААААААААА 57

4.2. EISA Cycle Address Decoding АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 58

4.2.1 POSITIVELY DECODED MEMORY CYCLES TO MAIN MEMORY ААААААААААААААААА 58

4.2.2 PROGRAMMABLE EISA-TO-PCI MEMORY ADDRESS REGIONS ААААААААААААААААА 61

4.2.3 PROGRAMMABLE EISA-TO-PCI I/O ADDRESS REGIONS ААААААААААААААААААААААА 61

4.2.4 EXTERNAL EISA-TO-PCI I/O ADDRESS DECODER АААААААААААААААААААААААААААААА 62

4.3 Palette DAC Snoop Mechanism АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 62

5.0 PCI INTERFACE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 62

5.1 PCI Bus Transactions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 63

5.1.1 PCI COMMAND SET ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 63

5.1.2 PCI CYCLE DESCRIPTIONS АААААААААААААААААААААААААААААААААААААААААААААААААААААА 64

5.1.2.1 Interrupt Acknowledge ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 64

5.1.2.2 Special Cycle АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 65

5.1.2.3 I/O Read АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 65

5.1.2.4 I/O Write АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 65

5.1.2.5 Memory Read ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 66

5.1.2.6 Memory Write ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 67

5.1.2.7 Configuration Read, Configuration Write АААААААААААААААААААААААААААААААААААААА 67

5.1.2.8 Memory Read Multiple ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 68

4

CONTENTS PAGE

5.1.2.9 Memory Read Line

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 68

5.1.2.10 Memory Write And Invalidate ААААААААААААААААААААААААААААААААААААААААААААААА 68

5.1.3 PCI TRANSFER BASICS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 68

5.1.3.1 Turn-Around-Cycle Definition ААААААААААААААААААААААААААААААААААААААААААААААААА 69

5.1.3.2 Idle Cycle Definition АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 69

5.1.4 BASIC READ ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 71

5.1.5 BASIC WRITE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 72

5.1.6 CONFIGURATION CYCLES АААААААААААААААААААААААААААААААААААААААААААААААААААААА 73

5.1.7 INTERRUPT ACKNOWLEDGE CYCLE АААААААААААААААААААААААААААААААААААААААААААА 74

5.1.8 EXCLUSIVE ACCESS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 75

5.1.9 DEVICE SELECTION ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 77

5.1.10 TRANSACTION TERMINATION ААААААААААААААААААААААААААААААААААААААААААААААААА 78

5.1.10.1 Master Initiated Termination АААААААААААААААААААААААААААААААААААААААААААААААА 78

5.1.10.2 Target Initiated Termination ААААААААААААААААААААААААААААААААААААААААААААААААА 79

5.1.10.3 PCEB Target Termination Conditions ААААААААААААААААААААААААААААААААААААААА 81

5.1.10.4 PCEB Master Termination Conditions ААААААААААААААААААААААААААААААААААААААА 81

5.1.10.5 PCEB Responses/Results Of Termination АААААААААААААААААААААААААААААААААА 81

5.1.11 PCI DATA TRANSFERS WITH SPECIFIC BYTE ENABLE COMBINATIONS АААААА 82

5.2 PCI Bus Latency ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 82

5.2.1 MASTER LATENCY TIMER (MLT) АААААААААААААААААААААААААААААААААААААААААААААААА 82

5.2.2 INCREMENTAL LATENCY MECHANISM ААААААААААААААААААААААААААААААААААААААААА 83

5.3 PCI Bus Parity Support And Error Reporting АААААААААААААААААААААААААААААААААААААААААААА 83

5.3.1 PARITY GENERATION AND CHECKING ААААААААААААААААААААААААААААААААААААААААА 83

5.3.1.1 Address Phase АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 84

5.3.1.2 Data Phase АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 84

5.3.2 PARITY ERRORÐPERRÝSIGNAL АААААААААААААААААААААААААААААААААААААААААААААА 84

5.3.3 SYSTEM ERRORS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 84

5.4 PCI Bus Arbitration АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 85

5.4.1 PCI ARBITER CONFIGURATION ААААААААААААААААААААААААААААААААААААААААААААААААА 85

5.4.1.1 Fixed Priority Mode АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 87

5.4.1.2 Rotating Priority Mode ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 89

5.4.1.3 Mixed Priority Mode АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 89

5.4.1.4 Locking Masters ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 89

5.4.2 ARBITRATION SIGNALING PROTOCOL ААААААААААААААААААААААААААААААААААААААААА 89

5.4.2.1 REQÝand GNTÝRules ААААААААААААААААААААААААААААААААААААААААААААААААААААА 90

5.4.2.2 Back-to-Back Transactions АААААААААААААААААААААААААААААААААААААААААААААААААА 90

5

CONTENTS PAGE

5.4.3 RETRY THRASHING RESOLVE

АААААААААААААААААААААААААААААААААААААААААААААААААА 91

5.4.3.1 Resume Function АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 91

5.4.3.2 Master Retry Timer АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 92

5.4.4 BUS LOCK MODE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 92

5.4.5 MEMREQÝ, FLSHREQÝ, AND MEMACKÝPROTOCOL ААААААААААААААААААААААААА 92

5.4.5.1 Flushing System Posted Write Buffers АААААААААААААААААААААААААААААААААААААААА 93

5.4.5.2 Guaranteed Access Time Mode АААААААААААААААААААААААААААААААААААААААААААААА 94

5.4.5.3 Interrupt Synchronization-Buffer Flushing ААААААААААААААААААААААААААААААААААААА 95

5.4.6 BUS PARKING ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 95

5.4.7 PCI ARBITRATION AND PCEB/ESC EISA OWNERSHIP EXCHANGE ААААААААААААА 96

5.4.7.1 GAT Mode and PEREQÝSignaling АААААААААААААААААААААААААААААААААААААААААА 96

5.4.7.2 PCI Retry and EISA Latency Timer (ELT) Mechanism ААААААААААААААААААААААААА 96

6.0 DATA BUFFERING АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 97

6.1 Line Buffers ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 98

6.1.1 WRITE STATE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 98

6.1.2 READ STATE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 99

6.2 Buffer Management Summary АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 100

7.0 EISA INTERFACE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 101

7.1 PCEB As An EISA Master АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 102

7.1.1 STANDARD EISA MEMORY AND I/O READ/WRITE CYCLES ААААААААААААААААААА 102

7.1.2 EISA BACK-OFF CYCLE АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 103

7.2 PCEB As An EISA Slave АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 105

7.2.1 EISA MEMORY AND I/O READ/WRITE CYCLES АААААААААААААААААААААААААААААААА 106

7.2.2 EISA MEMORY BURST CYCLES АААААААААААААААААААААААААААААААААААААААААААААААА 107

7.3 I/O Recovery АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 108

8.0 EISA DATA SWAP BUFFERS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 109

8.1 Data Assembly And Disassembly ААААААААААААААААААААААААААААААААААААААААААААААААААААА 109

8.2 The Copy Operation (Up Or Down) АААААААААААААААААААААААААААААААААААААААААААААААААААА 110

8.3 The Re-Drive Operation АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 111

9.0 BIOS TIMER АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 114

9.1 Bios Timer Operations АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 114

6

CONTENTS PAGE

10.0 PCEB/ESC INTERFACE

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 115

10.1 Arbitration Control Signals ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 115

10.2 System Buffer Coherency Control-APIC ААААААААААААААААААААААААААААААААААААААААААААА 117

10.3 Power Management (82375SB) ААААААААААААААААААААААААААААААААААААААААААААААААААААА 117

10.4 EISA Data Swap Buffer Control Signals АААААААААААААААААААААААААААААААААААААААААААААА 117

10.5 Interrupt Acknowledge Control АААААААААААААААААААААААААААААААААААААААААААААААААААААА 118

11.0 ELECTRICAL CHARACTERISTICS ААААААААААААААААААААААААААААААААААААААААААААААААААА 118

11.1 Absolute Maximum Ratings ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 118

12.0 PINOUT AND PACKAGE INFORMATION ААААААААААААААААААААААААААААААААААААААААААААА 119

12.1 Pin Assignment ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 119

12.2 Package Characteristics ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 127

13.0 TESTABILITY ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 128

13.1 NAND Tree ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 128

7

82375EB/SB

1.0 ARCHITECTURAL OVERVIEW

The PCI-EISA bridge chip set provides an I/O subsystem core for the next generation of high-performance

personal computers (e.g., those based on the Intel486

TM

or PentiumÉprocessors). System designers can take

advantage of the power of the PCI local bus while maintaining access to the large base of EISA and ISA

expansion cards, and corresponding software applications. Extensive buffering and buffer management within

the PCI-EISA bridge ensures maximum efficiency in both bus environments.

The chip set consists of two componentsÐthe 82375EB PCI-EISA Bridge (PCEB) and the 82374EB EISA

System Component (ESC). These components work in tandem to provide an EISA I/O subsystem interface for

personal computer platforms based on the PCI standard. This section provides an overview of the PCI and

EISA Bus hierarchy followed by an overview of the PCEB and ESC components.

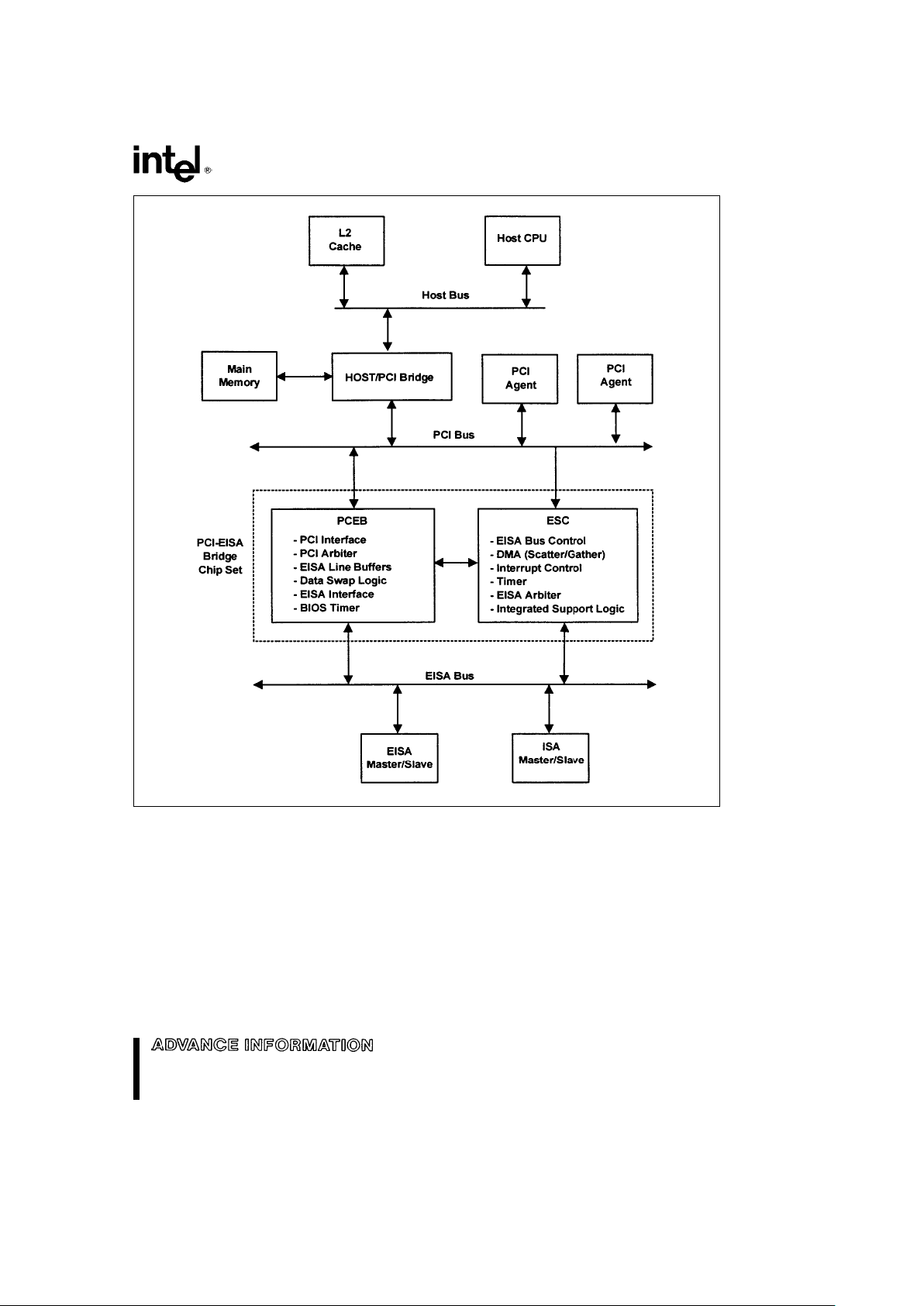

Bus HierarchyÐConcurrent Operations

Figure 1 shows a block diagram of a typical system using the PCI-EISA Bridge chip set. The system contains

three levels of buses structured in the following hierarchy:

#

Host Bus as the execution bus

#

PCI Bus as a primary I/O bus

#

EISA Bus as a secondary I/O bus

PCI Bus

The PCI Bus has been defined to address the growing industry needs for a standardized

local bus

that is not

directly dependent on the speed and the size of the processor bus. New generations of personal computer

system software such as Windows

TM

and Win-NTTMwith sophisticated graphical interfaces, multi-tasking and

multi-threading bring new requirements that traditional PC I/O architectures can not satisfy. In addition to the

higher bandwidth, reliability and robustness of the I/O subsystem are becoming increasingly important. The

PCI environment addresses these needs and provides an upgrade path for the future. PCI features include:

#

Processor independent

#

Multiplexed, burst mode operation

#

Synchronous up to 33 MHz

#

120 MByte/sec usable throughput (132 MByte/sec peak) for 32-bit data path

#

240 MByte/sec usable throughput (264 MByte/sec peak) for 64-bit data path

#

Optional 64-bit data path with operations that are transparent with the 32-bit data path

#

Low latency random access (60 ns write access latency to slaves from a master parked on the bus)

#

Capable of full concurrency with processor/memory subsystem

#

Full multi-master capability allowing any PCI master peer-to-peer access to any PCI slave

#

Hidden (overlapped) central arbitration

#

Low pin count for cost effective component packaging (multiplexed address/data)

#

Address and data parity

#

Three physical address spaces: memory, I/O, and configuration

#

Comprehensive support for autoconfiguration through a defined set of standard configuration functions

8

82375EB/SB

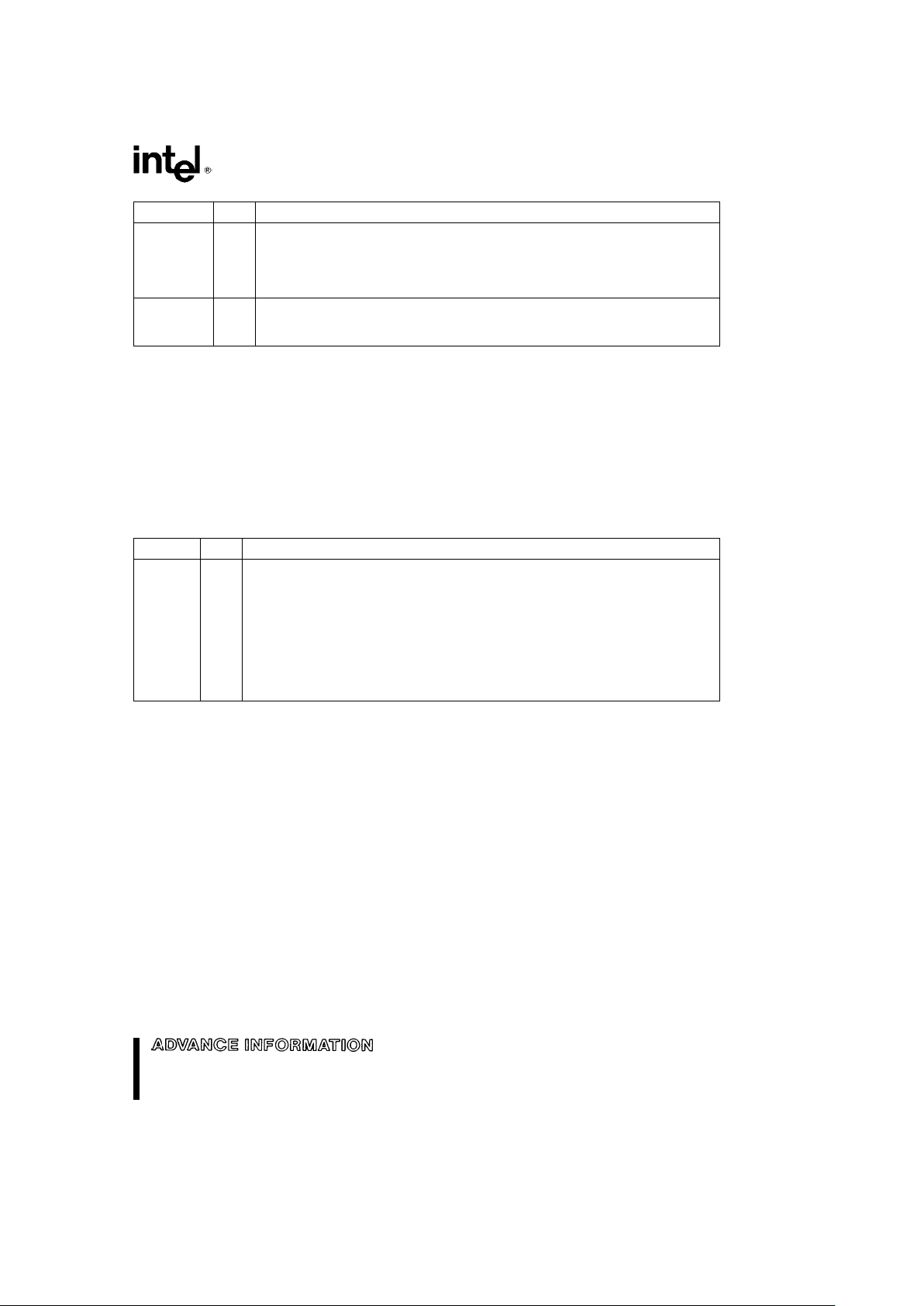

290477– 2

Figure 1. PCI-EISA System Diagram

System partitioning shown in Figure 1 illustrates how the PCI can be used as a common interface between

different portions of a system platform that are typically supplied by the chip set vendor. These portions are the

Host/PCI Bridge (including a main memory DRAM controller and an optional secondary cache controller) and

the PCI-EISA Bridge. Thus, the PCI allows a system I/O core design to be decoupled from the processor/

9

82375EB/SB

memory treadmill, enabling the I/O core to provide maximum benefit over multiple generations of processor/

memory technology. For this reason, the PCI-EISA Bridge can be used with different processors (i.e. derivatives of the Intel486 CPU or the new generation processors, such as the Pentium processor.) Regardless of

the new requirements imposed on the processor side of the Host/PCI Bridge (e.g. 64-bit data path, 3.3V

interface, etc.) the PCI side remains unchanged. This standard PCI environment allows reusability, not only of

the rest of the platform chip set (i.e. PCI-EISA Bridge), but also of all other I/O functions interfaced at the PCI

level. These functions typically include graphics, SCSI, and LAN.

EISA Bus

The EISA bus in the system shown in the Figure 1 represents a second level I/O bus. It allows personal

computer platforms built around the PCI as a primary I/O bus to leverage the large EISA/ISA product base.

Combinations of PCI and EISA buses, both of which can be used to provide expansion functions, will satisfy

even the most demanding applications.

Along with compatibility for 16-bit and 8-bit ISA hardware and software, the EISA bus provides the following

key features:

#

32-bit addressing and 32-bit data path

#

33 MByte/sec bus bandwidth

#

Multiple bus master support through efficient arbitration

#

Support for autoconfiguration

Integrated Bus Central Control Functions

The PCI-EISA Bridge chip set integrates central bus functions on both the PCI and EISA Buses. For PCI, the

functions include PCI bus arbitration and the default bus driver. For the EISA Bus, central functions include the

EISA Bus controller and EISA arbiter that are integrated in the ESC and EISA data swap buffers that are

integrated in the PCEB.

Integrated System Functions

The PCI-EISA Bridge chip set integrates system functions including PCI parity and system error reporting,

buffer management, PCI and EISA memory and I/O address space mapping and decoding. For maximum

flexibility, all of these functions are programmable allowing for variety of optional features.

1.1 PCEB Overview

The PCEB and ESC form a PCI-EISA Bridge chip set. The PCEB/ESC interface provides the inter-chip communications between these two devices. The major functions provided by the PCEB are described in this

section.

PCI Bus Interface

The PCEB can be either a master or slave on the PCI Bus and supports bus frequencies from 25-to-33 MHz.

The PCEB becomes a slave when it positively decodes a PCI cycle. The PCEB also becomes a slave for

unclaimed cycles on the PCI Bus. These unclaimed cycles are subtractively decoded by the PCEB and

forwarded to the EISA Bus. As a slave, the PCEB supports single cycle transfers for memory, I/O, and

configuration operations.

10

82375EB/SB

For EISA-initiated transfers to the PCI Bus, the PCEB is a PCI master. The PCEB permits EISA devices to

access either PCI memory or I/O. While all PCI I/O transfers are single cycle, PCI memory cycles can be

either single cycle or burst, depending on the status of the PCEB’s Line Buffers. During EISA reads of PCI

memory, the PCEB uses a burst read cycle of four Dwords to prefetch data into a Line Buffer. During EISA-toPCI memory writes, the PCEB uses PCI burst cycles to flush the Line Buffers. The PCEB contains a programmable Master Latency Timer that provides the PCEB with a guaranteed time slice on the PCI Bus, after which it

surrenders the bus.

As a master on the PCI Bus, the PCEB generates address and command signals (C/BE[3:0

]

Ý

), address parity

for read and write cycles, and data parity for write cycles. As a slave, the PCEB generates data parity for read

cycles. Parity checking is not supported.

The PCEB, as a resource, can be locked by any PCI master. In the context of locked cycles, the entire PCEB

subsystem (including the EISA Bus) is considered a single resource.

PCI Bus Arbitration

The PCI arbiter supports six PCI mastersÐthe Host/PCI bridge, PCEB, and four other PCI masters. The arbiter

can be programmed for twelve fixed priority schemes, a rotating scheme, or a combination of the fixed and

rotating schemes. The arbiter can be programmed for bus parking that permits the Host/PCI Bridge default

access to the PCI Bus when no other device is requesting service. The arbiter also contains an efficient PCI

retry mechanism to minimize PCI Bus thrashing when the PCEB generates a retry.

EISA Bus Interface

The PCEB contains a fully EISA-compatible master and slave interface. The PCEB directly drives eight EISA

slots without external data or address buffering. The PCEB is only a master or slave on the EISA Bus for

transfers between the EISA Bus and PCI Bus. For transfers contained to the EISA Bus, the PCEB is never a

master or slave. However, the data swap buffers contained in the PCEB are involved in these transfers, if data

size translation is needed. The PCEB also provides support for I/O recovery.

EISA/ISA masters and DMA can access PCI memory or I/O. The PCEB only forwards EISA cycles to the PCI

Bus if the address of the transfer matches one of the address ranges programmed into the PCEB for EISA-toPCI positive decode. This includes the main memory segments used for generating MEMCS

Ý

from the EISA

Bus, one of the four programmable memory regions, or one of the four programmable I/O regions. For EISAinitiated accesses to the PCI Bus, the PCEB is a slave on the EISA Bus. I/O accesses are always non-buffered

and memory accesses can be either non-buffered or buffered via the Line Buffers. For buffered accesses,

burst cycles are supported.

During PCI-initiated cycles to the EISA Bus, the PCEB is an EISA master. Single cycle transfers are used for I/

O and memory read/write cycles from PCI to EISA.

PCI/EISA Address Decoding

The PCEB contains two address decodersÐone to decode PCI-initiated cycles and the other to decode EISAinitiated cycles. The two decoders permit the PCI and EISA Buses to operate concurrently.

The PCEB can also be programmed to provide main memory address decoding on behalf of the Host/PCI

bridge. When programmed, the PCEB monitors the PCI and EISA bus cycle addresses, and generates a

memory chip select signal (MEMCS

Ý

) indicating that the current cycle is targeted to main memory residing

behind the Host/PCI bridge. Programmable features include, read/write attributes for specific memory segments and the enabling/disabling of a memory hole. If not used, the MEMCS

Ý

feature can be disabled.

11

82375EB/SB

In addition to the main memory address decoding, there are four programmable memory regions and four

programmable I/O regions for EISA-initiated cycles. EISA/ISA master or DMA accesses to one of these

regions are forwarded to the PCI Bus.

Data Buffering

The PCEB contains four 16-byte wide Line Buffers for EISA-initiated cycles to the PCI Bus. The Line Buffers

permit prefetching of read data from PCI memory and posting of data being written to PCI memory.

By using burst transactions to fill or flush these buffers, when appropriate, the PCEB maximizes bus efficiency.

For example, an EISA device could fill a Line Buffer with byte, word, or Dword transfers and the PCEB would

use a PCI burst cycle to flush the filled line to PCI memory.

BIOS Timer

The PCEB has a 16-bit BIOS Timer. The timer can be used by BIOS software to implement timing loops. The

timer count rate is derived from the EISA clock (BCLK) and has an accuracy of

g

1 ms.

1.2 ESC Overview

The PCEB and ESC form a PCI-EISA bridge. The PCEB/ESC interface provides the inter-chip communications

between these two devices. The major functions provided by the ESC are described in this section.

EISA Controller

The ESC incorporates a 32-bit master and an 8-bit slave. The ESC directly drives eight EISA slots without

external data or address buffering. EISA system clock (BCLK) generation is integrated by dividing the PCI

clock (divide by 3 or divide by 4) and wait state generation is provided. The AENx and MACKx signals provide

a direct interface to four EISA slots and supports eight EISA slots with encoded AENx and MACKx signals.

The ESC contains an 8-bit data bus (lower 8 bits of the EISA data bus) that is used to program the ESC’s

internal registers. Note that for transfers between the PCI and EISA Buses, the PCEB provides the data path.

Thus, the ESC does not require a full 32-bit data bus. A full 32-bit address bus is provided and is used during

refresh cycles and for DMA operations.

The ESC performs cycle translation between the EISA Bus and ISA Bus. For mis-matched master/slave

combinations, the ESC controls the data swap buffers that are located in the PCEB. This control is provided

through the PCEB/ESC interface.

DMA Controller

The ESC incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels. Each channel can be programmed for 8- or 16-bit DMA device size, and ISA-compatible, type

‘‘A’’, type ‘‘B’’, or type ‘‘C’’ timings. Full 32-bit addressing is provided. The DMA controller also generates

refresh cycles.

12

82375EB/SB

The DMA controller supports an enhanced feature called scatter/gather. This feature provides the capability

of transferring multiple buffers between memory and I/O without CPU intervention. In scatter/gather mode,

the DMA can read the memory address and word count from an array of buffer descriptors, located in main

memory, called the scatter/gather descriptor (SGD) table. This allows the DMA controller to sustain DMA

transfers until all of the buffers in the SGD table are handled.

Interrupt Controller

The ESC contains an EISA compatible interrupt controller that incorporates the functionality of two 82C59

Interrupt Controllers. The two interrupt controllers are cascaded providing 14 external and two internal interrupts.

Advanced Programmable Interrupt Controller (APIC)

In addition to the standard EISA compatible interrupt controller described above, the ESC incorporates the

Advanced Programmable Interrupt Controller (APIC). While the standard interrupt controller is intended for use

in a uni-processor system, APIC can be used in either a uni-processor or multi-processor system. APIC

provides multi-processor interrupt management and incorporates both static and dynamic symmetric interrupt

distribution across all processors. In systems with multiple I/O subsystems, each subsystem can have its own

set of interrupts.

Timer/Counter

The ESC provides two 82C54 compatible timers (Timer 1 and Timer 2). The counters in Timer 1 support the

system timer interrupt (IRQ0

Ý

), refresh request, and a speaker tone output (SPKR). The counters in Timer 2

support fail-safe time-out functions and the CPU speed control.

Integrated Support Logic

To minimize the chip count for board designs, the ESC incorporates a number of extended features. The ESC

provides support for ALTA20 (Fast A20GATE) and ALTRST with I/O Port 92h. The ESC generates the control

signals for SA address buffers and X-Bus buffer. The ESC also provides chip selects for BIOS, the keyboard

controller, the floppy disk controller, and three general purpose devices. Support for generating chip selects

with an external decoder is provided for IDE, a parallel port, and a serial port. The ESC provides support for a

PC/AT compatible coprocessor interface and IRQ13 generation.

Power Management

Extensive power management capability permits a system to operate in a low power state without being

powered down. Once in the low power state (called ‘‘Fast Off’’ state), the computer appears to be off. For

example, the SMM code could turn off the CRT, line printer, hard disk drive’s spindle motor, and fans. In

addition, the CPU’s clock can be governed. To the user, the machine appears to be in the off state. However,

the system is actually in an extremely low power state that still permits the CPU to function and maintain

communication connections normally associated with today’s desktops (e.g., LAN, Modem, or FAX). Programmable options provide power management flexibility. For example, various system events can be programmed

to place the system in the low power state or break events can be programmed to wake the system up.

13

82375EB/SB

2.0 SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups

according to their associated interface.

The ‘‘

Ý

’’ symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal

is at a low voltage level. When ‘‘

Ý

’’ is not present after the signal name, the signal is asserted when at the high

voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a

mixture of ‘‘active-low’’ and ‘‘active-high’’ signals. The term assert,orassertion indicates that a signal is

active, independent of whether that level is represented by a high or low voltage. The term negate,or

negation indicates that a signal is inactive.

The following notations are used to describe the signal type.

in Input is a standard input-only signal

out Totem Pole output is a standard active driver

o/d Open Drain input/output

t/s Tri-State is a bi-directional, tri-state input/output pin

s/t/s Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a

time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float.

A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tristates it. An external pull-up is required to sustain the inactive state until another agent drives it and

must be provided by the central resource.

14

82375EB/SB

2.1 PCI Bus Interface Signals

Pin Name Type Description

PCICLK in PCI CLOCK: PCICLK provides timing for all transactions on the PCI Bus. All other PCI

signals are sampled on the rising edge of PCICLK and all timing parameters are defined

with respect to this edge. Frequencies supported by the PCEB range from 25 to

33 MHz.

PCIRSTÝin PCI RESET: PCIRSTÝforces the PCEB into a known state. All t/s and s/t/s signals

are forced to a high impedance state, and the s/o/d signals are allowed to float high.

The PCEB negates all GNT

Ý

lines to the PCI Bus and the PCEB negates its internal

request. The PCEB drives AD[31:0], C/BE[3:0

]

Ý

, and PAR during reset to keep these

signals from floating (depending on the state of CPUREQ

Ý

and REQ1ÝÐas described

in the following paragraph).

As long as PCIRST

Ý

is asserted, the PCEB drives the AD[31:0]signals to keep them

from floating. Note that CPUREQ

Ý

must be sampled high when PCIRSTÝis asserted.

All PCEB registers are set to their default values. PCIRSTÝmay be asynchronous to

PCICLK when asserted or negated. Although asynchronous, the negation of PCIRST

Ý

must be a clean, bounce-free edge. PCIRSTÝmust be asserted for a minimum 1 ms,

and PCICLK must be active during the last 100 ms of the PCIRST

Ý

pulse.

AD[31:0]t/s ADDRESS AND DATA: AD[31:0]is a multiplexed address and data bus. During the

first clock of a transaction, AD[31:0]contain a physical address. During subsequent

clocks, AD[31:0]contain data.

A PCEB bus transaction consists of an address phase followed by one or more data

phases. Little-endian byte ordering is used. AD[7:0]define the least significant byte

(LSB) and AD[31:24]the most significant byte (MSB). The information contained in the

two low order address bits varies by address space. In the I/O address space, AD[1:0

]

are used to provide full byte address. In the memory and configuration address space,

AD[1:0]are driven ‘‘00’’ during the address phase. The other three encodings are

reserved. See Section 5.0, PCI Interface for more details.

When the PCEB is a target, AD[31:0]are inputs during the address phase of a

transaction. During the following data phase(s), the PCEB may be asked to supply data

on AD[31:0

]

as for a PCI read, or accept data as for a PCI write. As an Initiator, the

PCEB drives a valid address on AD[31:0

]

(with exceptions related to AD[1:0]) during

the address phase, and drives write or latches read data on AD[31:0]during the data

phase.

When PCIRST

Ý

is asserted, the PCEB drives the AD[31:0]signals to keep them from

floating. In addition, the PCEB acts as the central resource responsible for driving the

AD[31:0]signals when no device owns the PCI Bus and the bus is idle.

15

82375EB/SB

Pin Name Type Description

C/BE[3:0

]

Ý

t/s BUS COMMAND AND BYTE ENABLES: The command and byte enable signals are

multiplexed on the same PCI pins. During the address phase of a transaction,

C/BE[3:0

]

Ý

define the bus command for bus command definitions. During the data

phase, C/BE[3:0

]

Ý

are used as Byte Enables. The Byte Enables determine which

byte lanes carry meaningful data. C/BE[0

]

Ý

applies to byte 0 and C/BE[3

]

Ý

to byte

3. C/BE[3:0

]

Ý

are not used for address decoding.

The PCEB drives C/BE[3:0

]

Ý

as an initiator of a PCI Bus cycle and monitors

C/BE[3:0

]

Ý

as a target.

When PCIRST

Ý

is asserted, the PCEB drives C/BE[3:0

]

Ý

to keep them from

floating. In addition, the PCEB acts as the central resource responsible for driving the

C/BE[3:0

]

Ý

signals when no device owns the PCI Bus and the bus is idle

FRAME

Ý

s/t/s FRAME: FRAMEÝis driven by the current initiator to indicate the beginning and

duration of an access. FRAMEÝis asserted to indicate that a bus transaction is

beginning. During a transaction, data transfers continue while FRAME

Ý

is asserted.

When FRAME

Ý

is negated, the transaction is in the final data phase. FRAMEÝis an

input when the PCEB is the target. FRAME

Ý

is an output when the PCEB is the

initiator. During reset, this signal is tri-stated.

TRDY

Ý

s/t/s TARGET READY: TRDYÝ, as an output, indicates the target’s ability to complete

the current data phase of the transaction. TRDY

Ý

is used in conjunction with

IRDY

Ý

. A data phase is completed on any clock that both TRDYÝand IRDYÝare

sampled asserted. When PCEB is the target during a read cycle, TRDYÝindicates

that the PCEB has valid data present on AD[31:0]. During a write, it indicates that the

PCEB, as a target, is prepared to latch data. TRDY

Ý

is an input to the PCEB when

the PCEB is the initiator. During reset, this signal is tri-stated.

IRDY

Ý

s/t/s INITIATOR READY: IRDYÝ, as an output, indicates the initiator’s ability to complete

the current data phase of the transaction. IRDY

Ý

is used in conjunction with

TRDY

Ý

. A data phase is completed on any clock that both IRDYÝand TRDYÝare

sampled asserted. When PCEB is the initiator of a write cycle, IRDYÝindicates that

the PCEB has valid data present on AD[31:0]. During a read, it indicates the PCEB is

prepared to latch data. IRDY

Ý

is an input to the PCEB when the PCEB is the target.

During reset, this signal is tri-stated.

STOP

Ý

s/t/s STOP: As a target, the PCEB asserts STOPÝto request that the master stop the

current transaction. When the PCEB is an initiator, STOP

Ý

is an input. As an initiator,

the PCEB stops the current transaction when STOP

Ý

is asserted. Different

semantics of the STOPÝsignal are defined in the context of other handshake

signals (TRDY

Ý

and DEVSELÝ). During reset, this signal is tri-stated.

PLOCK

Ý

s/t/s PCI LOCK: PLOCKÝindicates an atomic operation that may require multiple

transactions to complete. PLOCK

Ý

is an input when PCEB is the target and output

when PCEB is the initiator. When PLOCK

Ý

is sampled negated during the address

phase of a transaction, a PCI agent acting as a target will consider itself a locked

resource until it samples PLOCK

Ý

and FRAMEÝnegated. When other masters

attempt accesses to the PCEB (practically to the EISA subsystem) while the PCEB is

locked, the PCEB responds with a retry termination. During reset, this signal is tristated.

16

82375EB/SB

Pin Name Type Description

IDSEL in INITIALIZATION DEVICE SELECT: IDSEL is used as a chip select during

configuration read and write transactions. The PCEB samples IDSEL during the

address phase of a transaction. If the PCEB samples IDSEL asserted during a

configuration read or write, the PCEB responds by asserting DEVSEL

Ý

on the next

cycle.

DEVSELÝs/t/s DEVICE SELECT: The PCEB asserts DEVSELÝto claim a PCI transaction as a result

of positive or subtractive decode. As an output, the PCEB asserts DEVSEL

Ý

when it

samples IDSEL asserted during configuration cycles to PCEB configuration registers.

As an input, DEVSEL

Ý

indicates the response to a PCEB-initiated transaction. The

PCEB, when not a master, samples this signal for all PCI transactions to decide

whether to subtractively decode the cycle (except for configuration and special cycles).

During reset, this signal is tri-stated.

PAR t/s PARITY: PAR is even parity across AD[31:0]and C/BE[3:0

]

Ý

. When acting as a

master, the PCEB drives PAR during the address and write data phases. As a target,

the PCEB drives PAR during read data phases.

When PCIRST

Ý

is asserted, the PCEB drives the PAR signal to keep it from floating.

The PCEB acts as the central resource responsible for driving the PAR signal when no

other device is granted the PCI Bus and the bus is idle.

Note that the driving and tri-stating of the PAR signal is always one clock delayed from

the corresponding driving and tri-stating of the AD[31:0]and C/BE[3:0

]

Ý

signals.

PERR

Ý

s/t/s PARITY ERROR: PERRÝreports data parity errors on all transactions, except special

cycles. This signal can only be asserted (by the agent receiving data) two clocks

following the data (which is one clock following the PAR signal that covered the data).

The duration of PERR

Ý

is one clock for each data phase that a data parity error is

detected. (If multiple data errors occur during a single transaction the PERR

Ý

signal is

asserted for more than a single clock.) PERR

Ý

must be driven high for one clock

before being tri-stated. During reset, this signal is tri-stated.

17

82375EB/SB

2.2 PCI Arbiter Signals

Pin Name Type Description

CPUREQÝin CPU REQUEST: CPUREQÝasserted indicates that the Host CPU requests use of

the PCI Bus. During PCIRST

Ý

, this signal must be sampled high by the PCEB. When

PCIRST

Ý

is asserted (and CPUREQÝis sampled high), the PCEB drives the AD,

C/BE

Ý

, and PAR signals to keep them from floating.

REQ[3:0

]

Ý

in REQUEST: A bus master asserts the corresponding request signal to request the

PCI Bus.

CPUGNTÝout CPU GRANT: The PCEB asserts CPUGNTÝto indicate that the CPU master (Host

Bridge) has been granted the PCI Bus. During PCI reset, CPUGNT

Ý

is tri-stated.

GNT[3:0

]

Ý

out GRANT: The PCEB asserts one of the GNT[3:0]signals to indicate that the

corresponding PCI master has been granted the PCI Bus. During PCI reset, these

signals are tri-stated.

MEMREQÝout MEMORY REQUEST: If the PCEB is configured in Guaranteed Access Time (GAT)

Mode, MEMREQ

Ý

is asserted when an EISA device or DMA requests the EISA Bus.

The PCEB asserts this signal (along with FLSHREQ

Ý

) to indicate that the PCEB

requires ownership of main memory. The PCEB asserts FLSHREQ

Ý

concurrently

with asserting MEMREQ

Ý

. This signal is synchronous to the PCI clock. During reset,

this signal is driven high.

FLSHREQ

Ý

MEMREQÝMeaning

1 1 Idle

0 1 Flush buffers pointing towards PCI

to avoid ISA deadlock

1 0 GAT enabled or disabled: For buffer

coherency in APIC systems, the

buffers pointing to main memory

must be flushed and disabled for the

duration of assertion.

0 0 GAT mode: Guarantee PCI Bus

immediate access to main memory

(this may or may not require the

PCI-to-main memory buffers to be

flushed first, depending on the

number of buffers).

FLSHREQÝout FLUSH REQUEST: FLSHREQÝis asserted by the PCEB to command all of the

system’s posted write buffers pointing towards PCI to be flushed. This is required

before granting the EISA Bus to an EISA master or the DMA. Note that, for APIC

related buffer flush requests, this signal is negated. This signal is synchronous to the

PCI clock. During reset, this signal is driven high.

18

82375EB/SB

Pin Name Type Description

MEMACKÝin MEMORY ACKNOWLEDGE: MEMACKÝis the response handshake that indicates

to the PCEB that the function requested over the MEMREQ

Ý

and/or FLSHREQ

Ý

signals has been completed.

If the PCEB is configured for Guaranteed Access Time Mode through the Arbiter

Control Register, and both MEMREQ

Ý

and FLSHREQÝare asserted, the assertion

of MEMACKÝindicates to the PCEB that ownership of main memory has been

granted and that all system buffers have been flushed and temporarily disabled.

If MEMACK

Ý

is asserted in response to assertion of MEMREQÝ(GAT either

enabled or disabled), it indicates that the system’s buffers pointing towards the main

memory are flushed and temporarily disabled so that APIC can proceed with the

interrupt message sequence.

If FLSHREQ

Ý

is asserted and MEMREQÝis not asserted (with GAT mode being

either enabled or disabled), the assertion of MEMACKÝindicates that the system’s

posted write buffers pointing towards PCI are flushed and temporarily disabled, and

the EISA Bus can be granted to an EISA master or DMA.

This signal is synchronous to the PCI clock.

2.3 Address Decoder Signals

Pin Name Type Description

MEMCSÝout MEMORY CHIP SELECT: MEMCSÝis a programmable address decode signal

provided to a Host CPU bridge. A Host bridge can use MEMCS

Ý

to forward a PCI cycle

to the main memory behind the bridge. MEMCS

Ý

is asserted one PCI clock after

FRAME

Ý

is sampled asserted (address phase) and is valid for one clock cycle before

being negated. MEMCS

Ý

is driven high during reset.

PIODECÝin PCI I/O SPACE DECODER: PIODECÝcan be used to provide arbitrarily complex

EISA-to-PCI I/O address space mapping. This signal can be connected to the decode

select output of an external I/O address decoder. When PIODEC

Ý

is asserted during

an EISA I/O cycle, that cycle is forwarded to the PCI Bus.

Note that an external pull-up resistor is required if this input signal is not used (i.e., not

driven by the external logic).

19

82375EB/SB

2.4 EISA Interface Signals

Pin Name Type Description

BCLK in BUS CLOCK: BCLK is the system clock used to synchronize events on the EISA Bus.

The ESC device generates BCLK (BCLKOUT), which is a divided down clock from a

PCICLK. BCLK runs at a frequency that is dependent on PCICLK and a selected

division factor (within the ESC). For example, a 25 MHz PCICLK and a division factor of

3 results in an 8.33 MHz BCLK.

STARTÝt/s START: STARTÝprovides timing control at the start of the cycle and remains asserted

for one BCLK period.

When the PCEB is an EISA master, START

Ý

is an output signal. STARTÝis asserted

after LA[31:24

]

Ý

,LA[23:2]and M/IOÝbecome valid. STARTÝis negated on the

rising edge of the BCLK, one BCLK after it was asserted. The trailing edge of START

Ý

is always delayed from the rising edge of BCLK.

When the PCEB is an EISA master, for cycles to a mismatched slave (see note at the

end of this section), STARTÝbecomes an input signal at the end of the first START

Ý

phase and remains an input until the negation of the last CMDÝ. The ESC gains the

control of the transfer and generates START

Ý

.

When the PCEB is an EISA slave, START

Ý

is an input signal. It is sampled on the rising

edge of BCLK.

Upon PCIRST

Ý

, this signal is tri-stated and placed in output mode.

CMD

Ý

in COMMAND: CMDÝprovides timing control within the cycle. In all cases, CMDÝis an

input to the PCEB from the ESC. CMDÝis asserted from the rising edge of BCLK,

simultaneously with the negation of START

Ý

, and remains asserted until the end of the

cycle.

M/IO

Ý

t/s MEMORY OR I/O: M/IOÝidentifies the current cycle as a memory or an I/O cycle.

M/IO

Ý

is pipelined from one cycle to the next and must be latched by the slave.

M/IO

Ý

e

1 indicates a memory cycle and M/IO

Ý

e

0 indicates an I/O cycle.

When the PCEB is an EISA master, the M/IO

Ý

is an output signal. When the PCEB is

an EISA slave, M/IOÝis an input signal. The PCEB responds as an EISA slave for both

memory and I/O cycles. Upon PCIRST

Ý

, this signal is tri-stated and is placed in output

mode.

W/R

Ý

t/s WRITE OR READ: W/RÝidentifies the cycle as a write or a read cycle. The W/R

Ý

signal is pipelined from one cycle to the next and must be latched by the slave. W/R

Ý

e

1 indicates a write cycle and W/R

Ý

e

0 indicates a read cycle.

When the PCEB is an EISA master, W/R

Ý

is an output signal. When the PCEB is an

EISA slave, W/RÝis an input signal. Upon PCIRSTÝ, this signal is tri-stated and

placed in output mode.

20

82375EB/SB

Pin Name Type Description

EXRDY od EISA READY: EXRDY is used by EISA I/O and memory slaves to request wait

states during a cycle. Each wait state is a BCLK period.

The PCEB, as an EISA master or slave, samples EXRDY. As an input, the EXRDY is

sampled on the falling edge of BCLK after the CMD

Ý

has been asserted, and if

inactive, each falling edge thereafter.

When PCEB is an EISA slave, it may drive EXRDY low to introduce wait states.

During reset, this signal is not driven.

EX32

Ý

od EISA 32 BIT: EX32Ýis used by the EISA slaves to indicate support of 32 bit

transfers. When the PCEB is an EISA master, it samples EX32

Ý

on the same rising

edge of BCLK that START

Ý

is negated.

During mismatched cycles (see note at the end of this section), EX32

Ý

(and EX16Ý)

is used to transfer the control back to the PCEB. EX32

Ý

(along with EX16Ý)is

asserted by the ESC on the falling edge of BCLK before the rising edge of the BCLK

when the last CMD

Ý

is negated. This indicates that the cycle control is transferred

back to the PCEB.

As an EISA slave, the PCEB always drives EX32

Ý

to indicate 32 bit support for EISA

cycles. During reset, this signal is not driven.

EX16

Ý

in EISA 16 BIT: EX16Ýis used by the EISA slaves to indicate their support of 16 bit

transfers. As an EISA master, the PCEB samples EX16

Ý

on the same rising edge of

BCLK that STARTÝis negated.

During mismatched cycles (see note at the end of this section), EX16

Ý

(and EX32Ý)

is used to transfer the control back to the PCEB. EX16

Ý

(along with EX32Ý)is

asserted by the ESC on the falling edge of the BCLK before the rising edge of the

BCLK when the last CMD

Ý

is negated. This indicates that the cycle control is

transferred back to the PCEB.

As an EISA slave, the PCEB never asserts EX16

Ý

.

MSBURSTÝt/s MASTER BURST: MSBURSTÝis an output when the PCEB is an EISA master and

an input when the PCEB is a slave.

As a master, the PCEB asserts MSBURST

Ý

to indicate to the slave that the next

cycle is a burst cycle. If the PCEB samples SLBURST

Ý

asserted on the rising edge

of BCLK after START

Ý

is asserted, the PCEB asserts MSBURSTÝon the next

BCLK edge and proceeds with the burst cycle.

As a slave, the PCEB monitors this signal in response to the PCEB asserting

SLBURST

Ý

. The EISA master asserts MSBURSTÝto the PCEB to indicate that the

next cycle is a burst cycle. As a slave, the PCEB samples MSBURST

Ý

on the rising

edge of BCLK after the rising edge of BCLK that CMD

Ý

is asserted by the ESC.

MSBURST

Ý

is sampled on all subsequent rising edges of BCLK until the signal is

sampled negated. The burst cycle is terminated on the rising edge of BCLK when

MSBURST

Ý

is sampled negated, unless EXRDY is sampled negated on the

previous falling edge of BCLK. During reset, this signal is tri-stated.

21

82375EB/SB

Pin Name Type Description

SLBURSTÝt/s SLAVE BURST: SLBURSTÝis an input when the PCEB is an EISA master and an

output when the PCEB is a slave.

When the PCEB is a master, the slave indicates that it supports burst cycles by

asserting SLBURST

Ý

to the PCEB. The PCEB samples SLBURSTÝon the rising

edge of BCLK at the end of START

Ý

for EISA master cycles.

When the PCEB is an EISA slave, this signal is an output. As a slave, the PCEB

asserts this signal to the master indicating that the PCEB supports EISA burst cycles.

During reset, this signal is tri-stated.

LOCK

Ý

t/s LOCK: When asserted, LOCKÝguarantees exclusive memory access. This signal is

asserted by the PCEB when the PCI master is running locked cycles to EISA slaves.

When asserted, this signal locks the EISA subsystem.

LOCK

Ý

can also be activated by a device on the EISA Bus. This condition is

propagated to the PCI Bus via the PLOCKÝsignal. During reset, this signal is tristated.

BE[3:0

]

Ý

t/s BYTE ENABLES: BE[3:0

]

Ý

identify the specific bytes that are valid during the

current EISA Bus cycles. When the PCEB is an EISA master and the cycles are

directed to a matched slave (slave supports 32-bit transfers), the BE[3:0

]

Ý

are

outputs from the PCEB.

When the cycles are directed to a mis-matched slave (slave does not support 32-bit

transfers - see note), the BE[3:0

]

Ý

are floated one and half BCLKs after STARTÝis

asserted. These signals become inputs (driven by the ESC) for the rest of the cycle.

BE[3:0

]

Ý

are pipelined signals and must be latched by the addressed slave. When

the PCEB is an EISA/ISA/DMA slave, BE[3:0

]

Ý

are inputs to the PCEB.

Upon PCIRST

Ý

, these signals are tri-stated and placed in output mode.

LA[31:24

]

Ý

, t/s LATCHABLE ADDRESS: LA[31:24

]

Ý

and LA[23:2]are the EISA address signals.

When the PCEB is an EISA master, these signals are outputs from the PCEB. These

LA[23:2

]

addresses are pipelined and must be latched by the EISA slave. LA[31:24

]

Ý

and

LA[23:2]are valid on the falling edge of START

Ý

. Note that the upper address bits

are inverted before being driven on LA[31:24

]

Ý

. The timing for LA[31:24]and

LA[23:2]are the same.

When the PCEB is an EISA slave, these signals are inputs and are latched by the

PCEB.

For I/O cycles, the PCEB, as an EISA master, floats LA[31:24

]

Ý

to allow for ESC’s

address multiplexing (during I/O cycle to configuration RAM). LA[23:2]are actively

driven by the PCEB. For memory cycles, the PCEB as an EISA master, drives the LA

address lines. During reset, these signals are tri-stated.

22

82375EB/SB

Pin Name Type Description

SD[31:0

]

t/s SYSTEM DATA: SD[31:0]are bi-directional data lines that transfer data between the

PCEB and other EISA devices. Data transfer between EISA and PCI devices use

these signals. The data swapping logic in the PCEB ensures that the data is available

on the correct byte lanes for any given transfer. During reset, these signals are tristated.

REFRESHÝin REFRESH: When asserted, REFRESHÝindicates to the PCEB that the current cycle

on the EISA Bus is a refresh cycle. It is used by the PCEB decoder to distinguish

between EISA memory read cycles and refresh cycles.

NOTE:

Mis-matched Cycles. When the PCEB is an EISA master, cycles to the slaves, other than 32 bits transfers, are considered

a mis-matched cycle. For mis-matched cycles, the PCEB backs off the EISA Bus one and half BCLKs after it asserted

START

Ý

by releasing (floating) STARTÝ,BE[3:0

]

Ý

and the SD[31:0]lines. The ESC device then takes control of the

transfer. The ESC controls the transfer until the last transfer. At the end of the last transfer, the control is transferred back to

the PCEB. The ESC transfers control back to the PCEB by asserting EX32

Ý

and EX16Ýon the falling edge of BCLK before

the rising edge of BCLK when the last CMD

Ý

is negated.

2.5 ISA Interface Signals

An ISA interface signal is included to improve the PCEB’s handling of I/O cycles on the EISA side of the

bridge. This signal permits ISA masters to address PCI I/O slaves using the full 16-bit bus size. The signal also

allows the PCEB to identify 8-bit I/O slaves for purposes of generating the correct amount of I/O recovery.

Pin Name Type Description

IO16

Ý

o/d 16-BIT I/O CHIP SELECT: As an EISA slave, the PCEB asserts IO16Ýwhen

PIODEC

Ý

is asserted or an I/O cycle to PCI is detected.

As an EISA master, the PCEB uses IO16

Ý

as an input to determine the correct amount

of I/O recovery time from the I/O Recovery Time (IORT) Register. This register

contains bit-fields that are used to program recovery times for 8-bit and 16-bit I/O.

When IO16Ýis asserted, the recovery time programmed into the 16-bit I/O field (bits

[

1:0

]

) , if enabled, is used. When IO16

Ý

is negated, the recovery time programmed into

the 8-bit I/O field (bits[5:3

]

), if enabled, is used.

This signal must have an external pull-up resistor. During reset, this signal is not driven.

23

82375EB/SB

2.6 PCEB/ESC Interface Signals

Pin Name Type Description

ARBITRATION AND INTERRUPT ACKNOWLEDGE CONTROL

EISAHOLD in EISA HOLD: EISAHOLD is used by the ESC to request control of the EISA Bus from

the PCEB. This signal is synchronous to PCICLK and is driven inactive when

PCIRST

Ý

is asserted.

EISAHLDA out EISA HOLD ACKNOWLEDGE: The PCEB asserts EISAHLDA to inform the ESC that

it has been granted ownership of the EISA Bus. This signal is synchronous to the

PCICLK.

PEREQÝ/ out PCI-TO-EISA REQUEST OR INTERRUPT ACKNOWLEDGE: PEREQÝ/INTAÝis a

dual-function signal. The signal function is determined by the state of EISAHLDA

INTA

Ý

signal.

When EISAHLDA is negated, this signal is an interrupt acknowledge (i.e., PEREQ

Ý

/

INTA

Ý

asserted indicates to the ESC that the current cycle on the EISA is an interrupt

acknowledge).

When EISAHLDA is asserted, this signal is a PCI-to-EISA request (i.e. PEREQ

Ý

/

INTAÝasserted indicates to the ESC that the PCEB needs to obtain the ownership of

the EISA Bus on behalf of a PCI agent).

This signal is synchronous to the PCICLK and it is driven inactive when PCIRST

Ý

is

asserted.

STPGNTÝout STOP GRANT ACKNOWLEDGE: STPGNTÝis asserted when the PCEB receives a

STOP GRANT PCI special cycle for one PCICLK period. This signal is only asserted

when the PCI AD[31:0]signals equal 00120002h during the first data phase of the PCI

special cycle. Data of 00120002h on AD[31:0]in subsequent data phases during a

PCI special cycle does not result in the assertion of STPGNT

Ý

.

24

82375EB/SB

PIN NAME Type Description

PCEB BUFFER COHERENCY CONTROL

NMFLUSHÝt/s NEW MASTER FLUSH: The bi-directional NMFLUSHÝsignal provides handshake

between the PCEB and ESC to control flushing of PCI system buffers on behalf of

EISA masters.

During an EISA Bus ownership change, before the ESC can grant the bus to the

EISA master (or DMA), the ESC must ensure that system buffers are flushed and the

buffers pointing towards the EISA subsystem are disabled. The ESC asserts

NMFLUSH

Ý

for one PCI clock to request system buffer flushing. (After asserting

NMFLUSHÝfor 1 PCI clock, the ESC tri-states NMFLUSHÝ.) When the PCEB

samples NMFLUSH

Ý

asserted, it starts immediately to assert NMFLUSHÝand

begins flushing its internal buffers, if necessary. The PCEB also requests PCI system

buffer flushing via the MEMREQ

Ý

, FLSHREQÝ, and MEMACKÝsignals.

When the PCEB completes its internal buffer flushing and MEMACKÝis asserted

(indicating that the PCI system buffer flushing is complete), the PCEB negates

NMFLUSH

Ý

for 1 PCI clock and stops driving it. When the ESC samples

NMFLUSHÝnegated, it grants the EISA Bus to an EISA master (or DMA). The ESC

resumes responsibility of the default NMFLUSH

Ý

driver and starts driving

NMFLUSH

Ý

negated until the next time a new EISA master (or DMA) wins

arbitration.

This signal is synchronous with PCICLK and is negated by the ESC at reset.

AFLUSH

Ý

t/s APIC FLUSH: AFLUSHÝis bi-directional signal between the PCEB and ESC that

controls system buffer flushing on behalf of the APIC. After a reset the ESC negates

AFLUSHÝuntil the APIC is initialized and the first interrupt request is recognized.

25

82375EB/SB

Pin Name Type Description

DATA SWAP BUFFER CONTROL

SDCPYEN01Ýin COPY ENABLE: These active Low signals perform byte copy operation on the

EISA data bus (SD[31:0]). The Copy Enable signals are asserted during mis-

SDCPYEN02

Ý

matched cycles and are used by the PCEB to enable byte copy operations

SDCPYEN03

Ý

between the SD data byte lanes 0, 1, 2, and 3 as follows:

SDCPYEN13

Ý

SDCPYEN01Ý: Copy between Byte Lane 0 (SD[7:0]) and Byte Lane 1

(SD[15:8])

SDCPYEN02Ý: Copy between Byte Lane 0 (SD[7:0]) and Byte Lane 2

(SD[23:16])

SDCPYEN03

Ý

: Copy between Byte Lane 0 (SD[7:0]) and Byte Lane 3

(SD[31:24])

SDCPYEN13Ý: Copy between Byte Lane 1 (SD[15:8]) and Byte Lane 3

(SD[31:24])

Note that the direction of the copy is controlled by SDCPYUP.

SDCPYUP in SYSTEM DATA COPY UP: SDCPYUP controls the direction of the byte copy

operation. A high on SDCPYUP indicates a COPY UP operation where the lower

byte(s) of the SD data bus are copied onto the higher byte(s) of the bus. A low on

the signal indicates a COPY DOWN operation where the higher byte(s) of the data

bus are copied on to the lower byte(s) of the bus. The PCEB uses this signal to

perform the actual data byte copy operation during mis-matched cycles.

SDOE[2:0

]

Ý

in SYSTEM DATA OUTPUT ENABLE: These active Low signals enable the SD data

output onto the EISA Bus. The ESC only activates these signals during mismatched cycles. The PCEB uses these signal to enable the SD data buffers as

follows:

SDOE0

Ý

Enables byte lane 0 SD[7:0

]

SDOE1

Ý

Enables byte lane 1 SD[15:8

]

SDOE2

Ý

Enables byte lane 3 SD[31:24]and byte lane 2

SD[23:16

]

SDLE[3:0

]

Ý

in SYSTEM DATA LATCH ENABLE: SDLE[3:0

]

Ý

enable the latching of data on the

EISA Bus. These signals are activated only during mis-matched cycles, except

PCEB-initiated write cycles. The PCEB uses these signals to latch the SD data bus

as follows:

SDLE0

Ý

Latch byte lane 0 SD[7:0

]

SDLE1

Ý

Latch byte lane 1 SD[15:8

]

SDLE2

Ý

Latch byte lane 2 SD[23:16

]

SDLE3

Ý

Latch byte lane 3 SD[31:24

]

2.7 Test Signal

Pin Name Type Description

TEST

Ý

in TEST: This pin is used to tri-state all PCEB outputs. During normal operations, this pin

must be tied high.

26

82375EB/SB

3.0 REGISTER DESCRIPTION

The PCEB contains both PCI configuration registers and I/O registers. The configuration registers (Table 1)

are located in PCI configuration space and are only accessible from the PCI Bus. The addresses shown in the

table for each register are offset values that appear on AD[7:2]and C/BE[3:0

]

Ý

. The configuration registers

can be accessed as Byte, Word (16-bit), or Dword (32-bit) quantities. All multi-byte numeric fields use ‘‘little-endian’’ ordering (i.e., lower addresses contain the least significant parts of the fields).

The BIOS Timer is the only non-configuration register (Section 3.2, I/O Registers). This register, like the

configuration registers, is only accessible from the PCI Bus. The BIOS Timer Register can be accessed as

byte, word, or Dword quantities.

Some of the PCEB registers contain reserved bits. These bits are labeled ‘‘Reserved’’. Software must take

care to deal correctly with bit-encoded fields that are reserved. On reads, software must use appropriate

masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software

must ensure that the values of reserved bits are preserved. That is, the values of reserved bit positions must

first be read, merged with the new values for other bit positions and the data then written back.

In addition to reserved bits within a register, the PCEB contains address locations in the PCI configuration

space that are marked ‘‘Reserved’’ (Table 1). The PCEB responds to accesses to these address locations by

completing the PCI cycle. When a reserved register location is read, 0000h is returned. Writes have no affect

on the PCEB.

During a hard reset (PCIRST

Ý

asserted), the PCEB registers are set to pre-determined default states. The

default values are indicated in the individual register descriptions.

During the address phase of a configuration cycle, Bits[10:8]encode one of eight possible functions on a

device. The PCEB only supports one function; that of a bridge between the PCI and EISA/ISA Busses. This

function has the code of 000. Thus, for accessing PCEB configuration registers, Bits[10:8

]

e

000 of the address. If the PCEB IDSEL is asserted and any of the above three bits is 1, the PCEB returns all zeros for a read

and does not respond to a write.

3.1 Configuration Registers

Table 1 summarizes the PCEB configuration space registers. Following the table, is a detailed description of

each register and register bit. The register descriptions are arranged in the order that they appear in Table 1.

The following nomenclature is used for access attributes.

RO Read Only. If a register is read only, writes to this register have no effect.

R/W Read/Write. A register with this attribute can be read and written.

R/WC Read/Write Clear. A register bit with this attribute can be read and written. However, a write of a 1

clears (sets to 0) the corresponding bit and a write of a 0 has no effect.

NOTE:

Some register fields are used to program address ranges for various PCEB functions. The register

contents represent the address bit value and not the signal level on the bus. For example, the upper

address lines on the EISA Bus have inverted signals (LA[31:24

]

Ý

). However, this inversion is auto-

matically handled by the PCEB hardware and is transparent to the programmer.

27

82375EB/SB

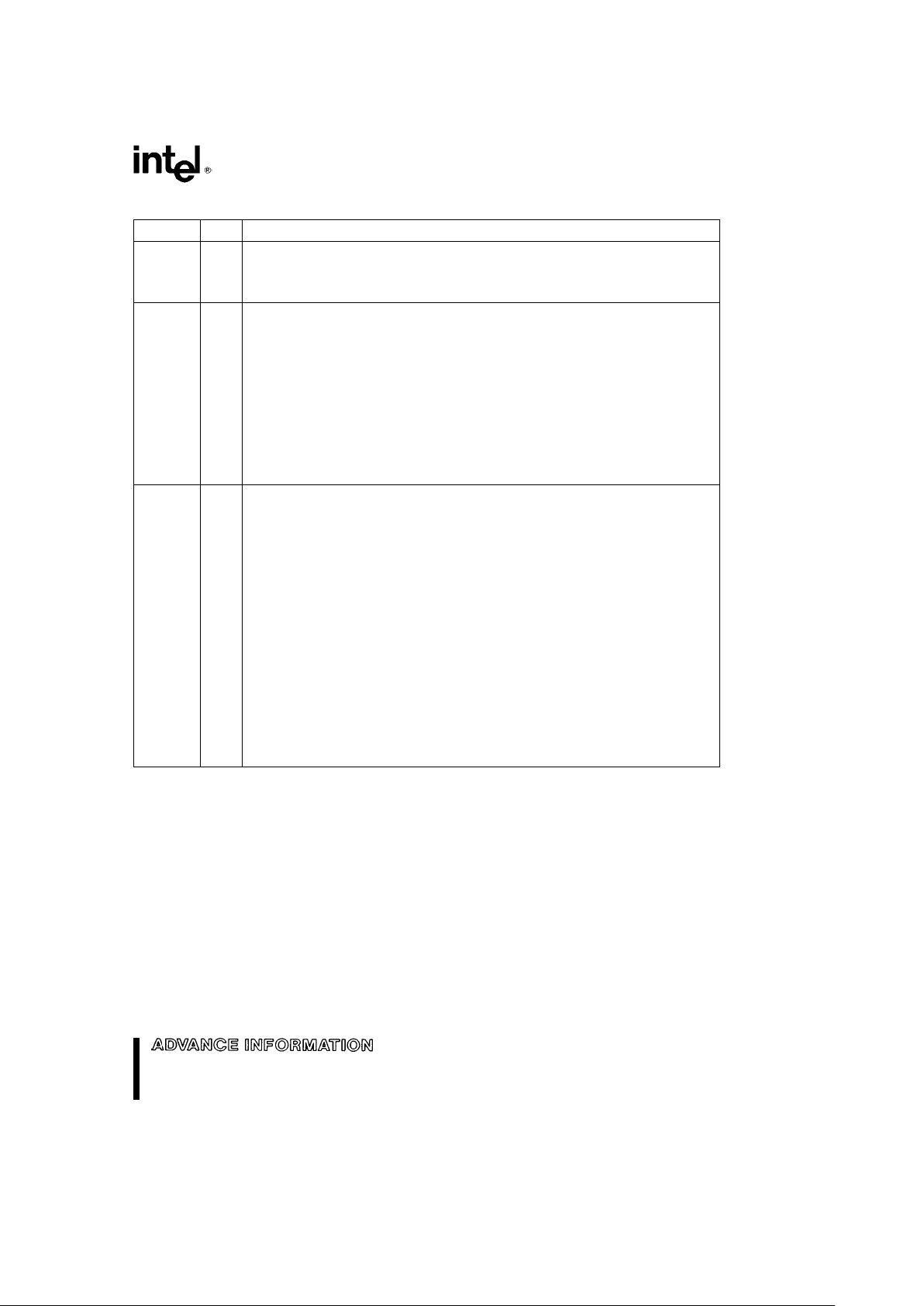

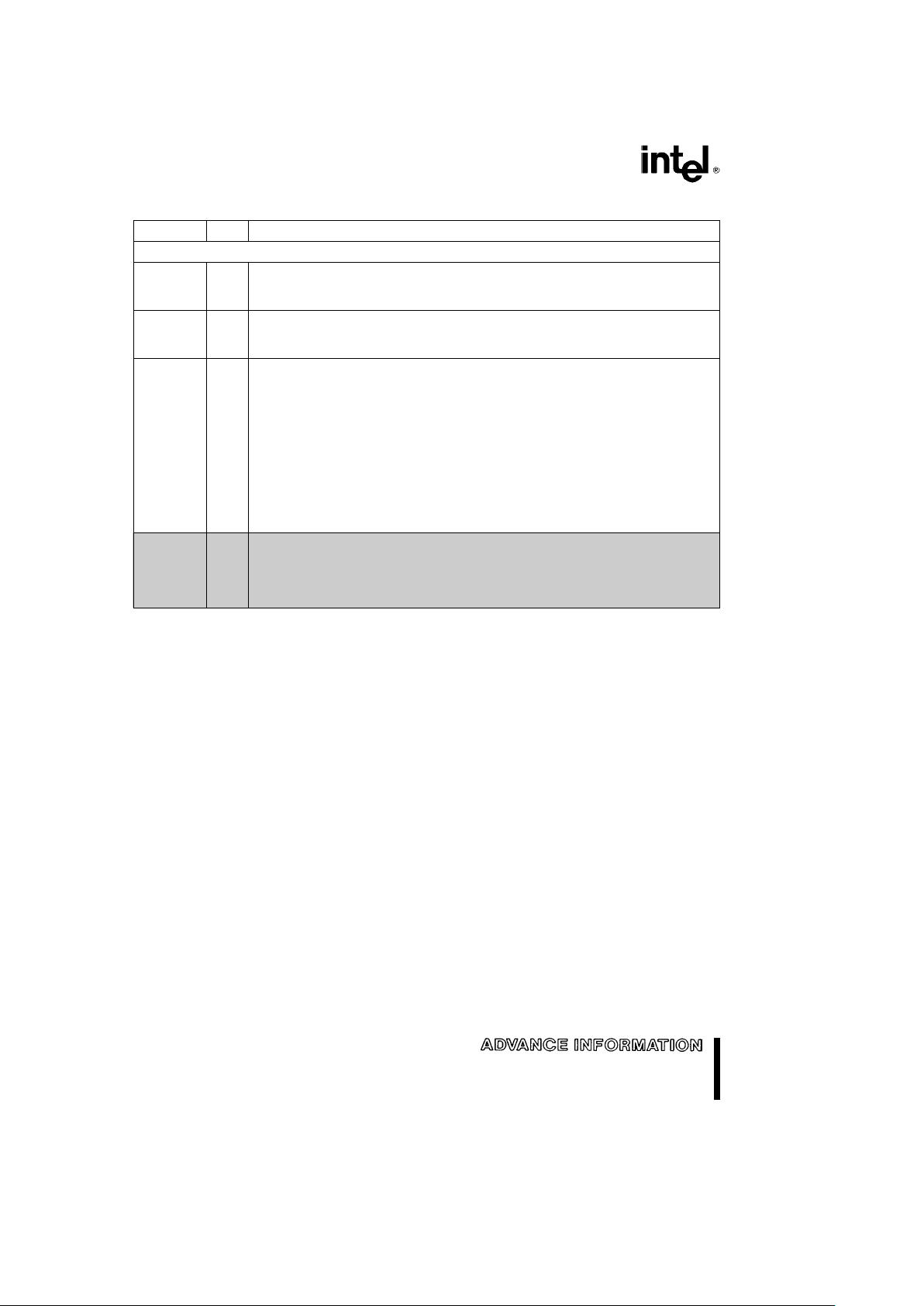

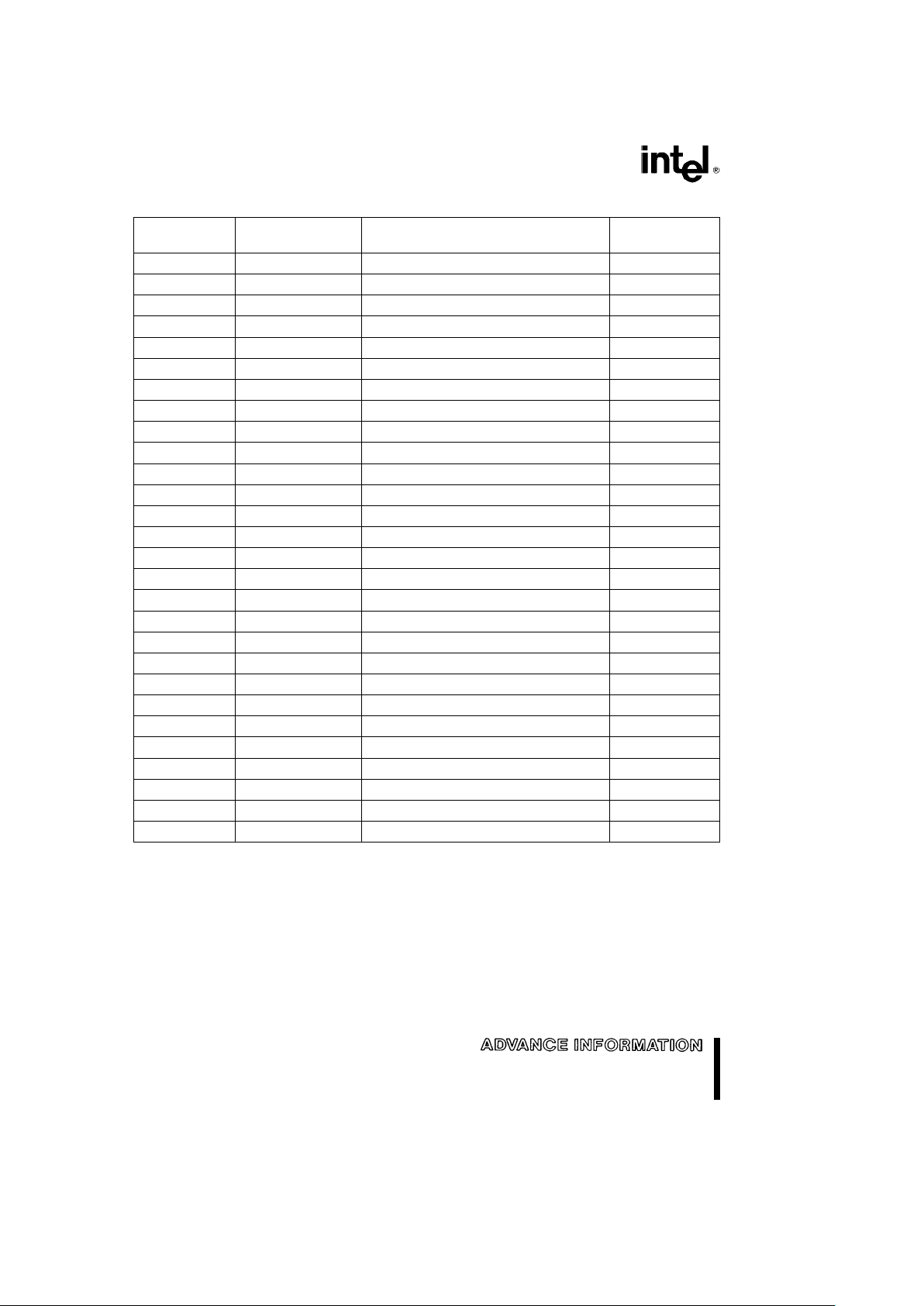

Table 1. Configuration Registers

Address

Abbreviation Register Name Access

Offset

00–01h VID Vendor Identification RO

02–03h DID Device Identification RO

04–05h PCICMD Command Register R/W

06–07h PCISTS Status Register RO, R/WC

08h RID Revision Identification RO

09–0Ch Ð Reserved Ð

0Dh MLTIM Master Latency Timer R/W

0E–3Fh Ð Reserved Ð

40h PCICON PCI Control R/W

41h ARBCON PCI Arbiter Control R/W

42h ARBPRI PCI Arbiter Priority Control R/W

43h ARBPRIX PCI Arbiter Priority Control Extension R/W

44h MCSCON MEMCSÝControl R/W

45h MCSBOH MEMCSÝBottom of Hole R/W

46h MCSTOH MEMCSÝTop of Hole R/W

47h MCSTOM MEMCSÝTop of Memory R/W

48–49h EADC1 EISA Address Decode Control 1 R/W

4A–4Bh Ð Reserved Ð

4Ch IORTC ISA I/O Recovery Time Control R/W

4Dh–53h Ð Reserved Ð

54h MAR1 MEMCSÝAttribute RegisterÝ1 R/W

55h MAR2 MEMCSÝAttribute RegisterÝ2 R/W

56h MAR3 MEMCSÝAttribute RegisterÝ3 R/W

57h Ð Reserved Ð

58h PDCON PCI Decode Control R/W

59h Ð Reserved Ð

5Ah EADC2 EISA Address Decode Control 2 R/W

5Bh Ð Reserved Ð

28

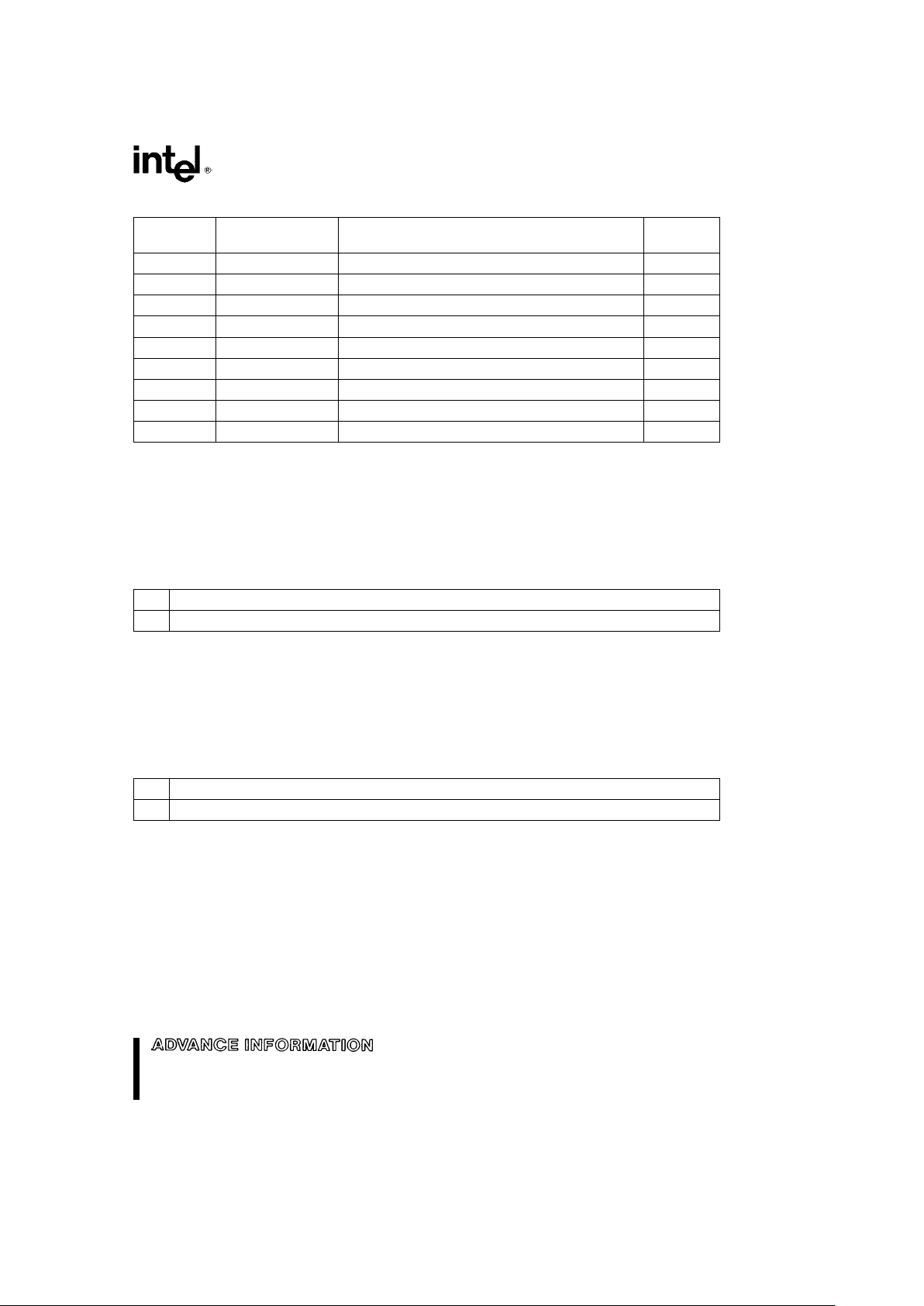

82375EB/SB

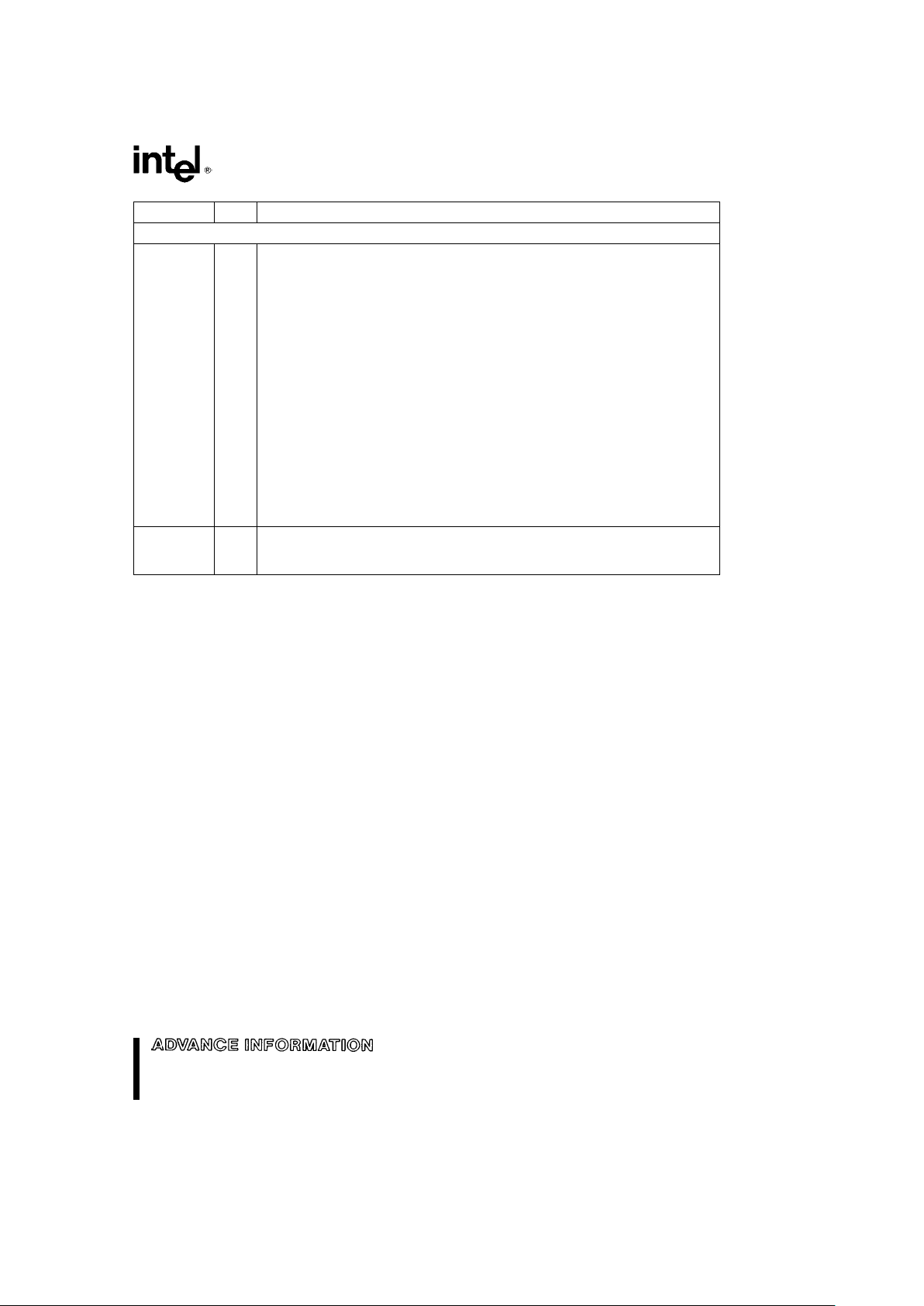

Table 1. Configuration Registers (Continued)

Address

Abbreviation Register Name Access

Offset

5Ch EPMRA EISA-to-PCI Memory Region Attributes R/W

5D–5Fh Ð Reserved Ð

60–6Fh MEMREGN[4:1

]

EISA-to-PCI Memory Region Address (4 Registers) R/W

70–7Fh IOREGN[4:1

]

EISA-to-PCI I/O Region Address (4 Registers) R/W

80–81h BTMR BIOS Timer Base Address R/W

84h ELTCR EISA Latency Timer Control Register R/W

85–87h Ð Reserved Ð

88–8Bh PTCR PCEB Test Control RegisterÐDO NOT WRITE Ð

8C–FFh Ð Reserved Ð

3.1.1 VIDÐVENDOR IDENTIFICATION REGISTER

Address Offset: 00– 01h

Default Value: 8086h

Attribute: Read Only

Size: 16 bits

The VID Register contains the vendor identification number. This register, along with the Device Identification

Register, uniquely identify any PCI device. Writes to this register have no effect.

Bit Description

15:0 Vendor Identification Number: This is a 16-bit value assigned to Intel.

3.1.2 DIDÐDEVICE IDENTIFICATION REGISTER

Address Offset: 02– 03h

Default Value: 0482h

Attribute: Read Only

Size: 16 bits

The DID Register contains the device identification number. This register, along with the VID Register, define

the PCEB. Writes to this register have no effect.

Bit Description

15:0 Device Identification Number: This is a 16-bit value assigned to the PCEB.

29

82375EB/SB

3.1.3 PCICMDÐPCI COMMAND REGISTER

Address Offset: 04– 05h

Default Value: 0007h

Attribute: Read/Write, Read Only

Size: 16 bits

This 16-bit register contains PCI interface control information. This register enables/disables PCI parity error

checking, enables/disables PCEB bus master capability, and enables/disables the PCEB to respond to PCIoriginated memory and I/O cycles. Note that, for certain PCI functions that are not implemented within the

PCEB, the control bits are still shown (labeled ‘‘not supported’’).

Bit Description

15:9 Reserved

8 SERRÝEnable (SERRE)ÐNot SupportedÐRO: Function of this bit is to control the SERRÝsignal.

Since the PCEB does not implement the SERR

Ý

signal, this bit always reads as 0 (disabled).

7 Wait State Control (WSC)ÐNot SupportedÐRO: This bit controls insertion of wait-states for

devices that do not meet the 33-10 PCI specification. Since PCEB meets the 33-10 specification, this

control function is not implemented. WSC is always read as 0.

6 Parity Error Enable (PERRE)ÐR/W: PERRE controls the PCEB’s response to PCI parity errors.

When PERRE

e

1, the PCEB asserts the PERRÝsignal when a parity error is detected. When

PERRE

e

0, the PCEB ignores any parity errors that it detects. After PCIRSTÝ, PERREe0 (parity

checking disabled).

5 VGA Palette Snoop (VGPS)ÐNot SupportedÐRO: This bit is intended only for specific control of

PCI-based VGA devices and it is not applicable to the PCEB. This bit is not implemented and always

reads as 0.

4 Memory Write and Invalidate Enable (MWIE)ÐNot SupportedÐRO: This is an enable bit for using

the Memory Write and Invalidate command. The PCEB doesn’t support this command as a master.

As a slave the PCEB aliases this command to a memory write. This bit always reads as 0 (disabled).

3 Special Cycle Enable (SCE)ÐNot SupportedÐRO: Since this capability is not implemented, the

PCEB does not respond to any type of special cycle. This bit always reads as 0.

2 Bus Master Enable (BME)ÐR/W: ME enables/disables the PCEB’s PCI Bus master capability.

When BME

e

0, the PCEB bus master capability is disabled. This prevents the PCEB from requesting

the PCI Bus on behalf of EISA/ISA masters, the DMA, or the Line Buffers. When BME

e

1, the bus

master capability is enabled. This bit is set to 1 after PCIRST

Ý

.

1 Memory Space Enable (MSE)ÐR/W: This bit enables the PCEB to accept PCI-originated memory

cycles. When MSE

e

1, the PCEB responds to PCI-originated memory cycles to the EISA Bus. When

MSE

e

0, the PCEB does not respond to PCI-originated memory cycles to the EISA Bus (DEVSELÝis

inhibited). This bit is set to 1 (enabled for BIOS access) after PCIRSTÝ.

0 I/O Space Enable (IOSE)ÐR/W: This bit enables the PCEB to accept PCI-originated I/O cycles.

When IOSE

e

1, the PCEB responds to PCI-originated I/O cycles. When IOSEe0, the PCEB does

not respond to a PCI I/O cycle (DEVSEL

Ý

is inhibited), including I/O cycles bound for the EISA Bus.

This bit is set to 1 (I/O space enabled) after PCIRST

Ý

.

30

Loading...

Loading...