E

© INTEL CORPORATION 1996, 1997 April 1997 Order Number: 290550-002

n

Bridge Between the PCI Bus and ISA Bus

n

PCI and ISA Master/Slave Interface

PCI from 25–33 MHz

ISA from 7.5–8.33 MHz

5 ISA Slots

n

Fast IDE Interface

Supports PIO and Bus Master IDE

Supports up to Mode 4 Timings

Transfer Rates to 22 MB/Sec

8 x 32-Bit Buffer for Bus Master IDE PCI

Burst Transfers

Separate Master/Slave IDE Mode

Support (PIIX3)

n

Plug-n-Play Port for Motherboard Devices

2 Steerable DMA Channels (PIIX Only)

Fast DMA with 4-Byte Buffer (PIIX Only)

2 Steerable Interrupts Lines on the PIIX

and 1 Steerable Interrupt Line on the

PIIX3

1 Programmable Chip Select

n

Steerable PCI Interrupts for PCI Device Plugn-Play

n

PCI Specification Revision 2.1 Compliant

(PIIX3)

n

Functionality of One 82C54 Timer

System Timer; Refresh Request;

Speaker Tone Output

n

Two 82C59 Interrupt Controller Functions

14 Interrupts Supported

Independently Programmable for

Edge/Level Sensitivity

n

Enhanced DMA Functions

Two 8237 DMA Controllers

Fast Type F DMA

Compatible DMA Transfers

7 Independently Programmable

Channels

n

X-Bus Peripheral Support

Chip Select Decode

Controls Lower X-Bus Data Byte

Transceiver

n

I/O Advanced Programmable Interrupt

Controller (IOAPIC) Support (PIIX3)

n

Universal Serial Bus (USB) Host Controller

(PIIX3)

Compatible with Universal Host

Controller Interface (UHCI)

Contains Root Hub with 2 USB Ports

n

System Power Management (Intel SMM

Support)

Programmable System Management

Interrupt (SMI)—Hardware Events,

Software Events, EXTSMI#

Programmable CPU Clock Control

(STPCLK#)

Fast On/Off Mode

n

Non-Maskable Interrupts (NMI)

PCI System Error Reporting

n

NAND Tree for Board-Level ATE Testing

n

208-Pin QFP

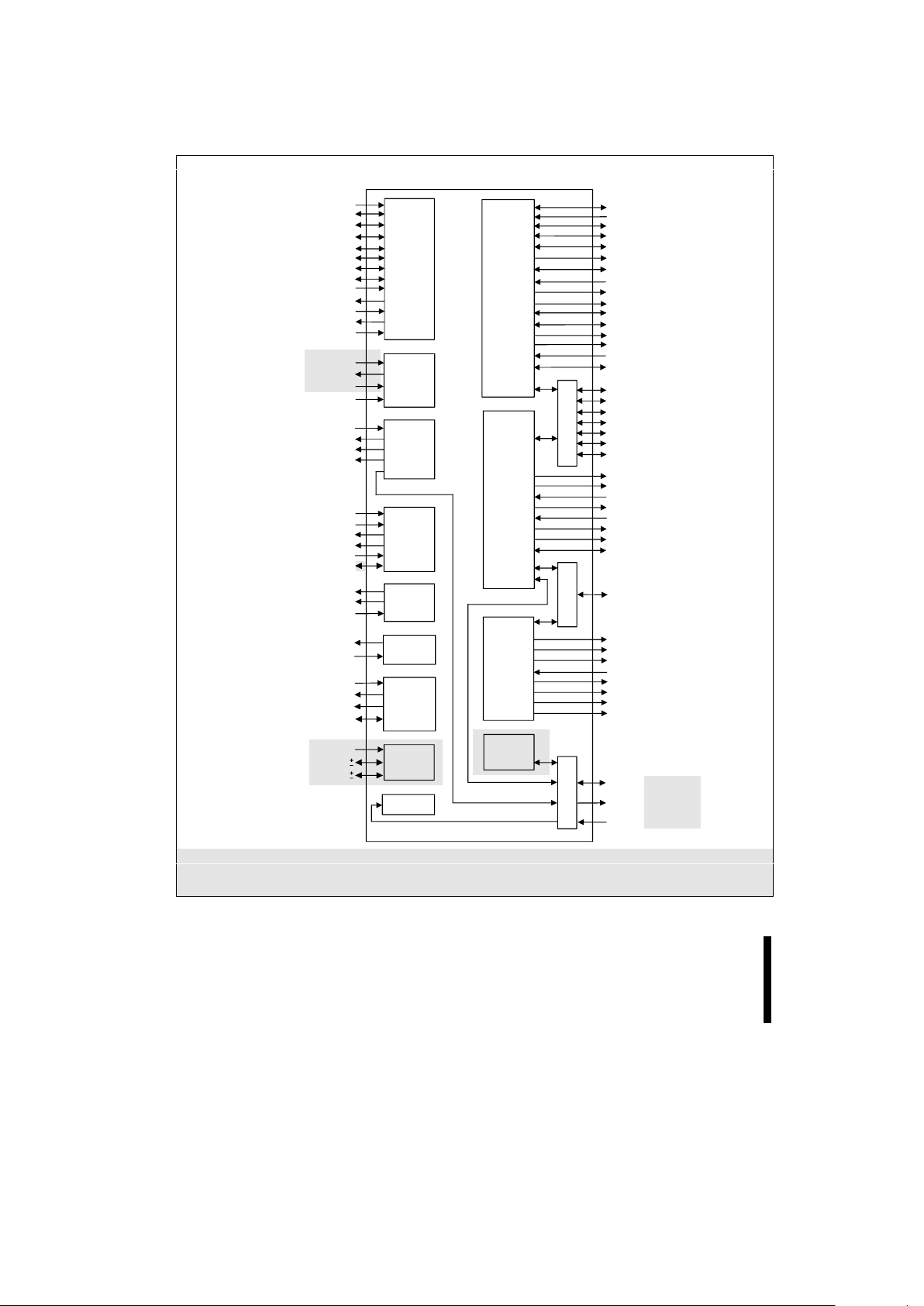

The 82371FB (PIIX) and 82371SB (PIIX3) PCI ISA IDE Xcelerators are multi-function PCI devices

implementing a PCI-to-ISA bridge function and an PCI IDE function. In addition, the PIIX3 implements a

Universal Serial Bus hos t/hub function. As a PCI-to-IS A bridge, the PII X/PIIX3 int egrates many com mon I/O

functions found in ISA -based PC systems—a seven-c hannel DMA c ontroller, two 82C59 int errupt c ontrollers ,

an 8254 timer/counter, and power management support. In addition to compatible transfers, each DMA

channel supports type F trans fers. Chip selec t decoding is provi ded for BIOS, real ti me clock, and k eyboard

controller. Edge/Level interrupts and interrupt steering are supported for PCI plug and play c ompatibility. The

PIIX/PIIX 3 supports two IDE c onnectors for up to f our IDE devices prov iding an interfac e for IDE hard disks

and CD ROMs. The PIIX/PIIX3 provides motherboard plug and play compatibility. PIIX implements two

steerable DMA channels (inc l udi ng type F transfers) and up to two steerable interrupt lines. PIIX 3 implements

one steerable interrupt line. The interrupt lines can be routed t o any of the available ISA interrupts. Both

PIIX/PIIX3 implement a programmable chip select.

PIIX3 contains a Uni versal Serial Bus (USB) Host Controller t hat is UHCI compatible. The Host Control ler’s

root hub has two programmable USB ports. PIIX3 also provides support for an external IOAPIC.

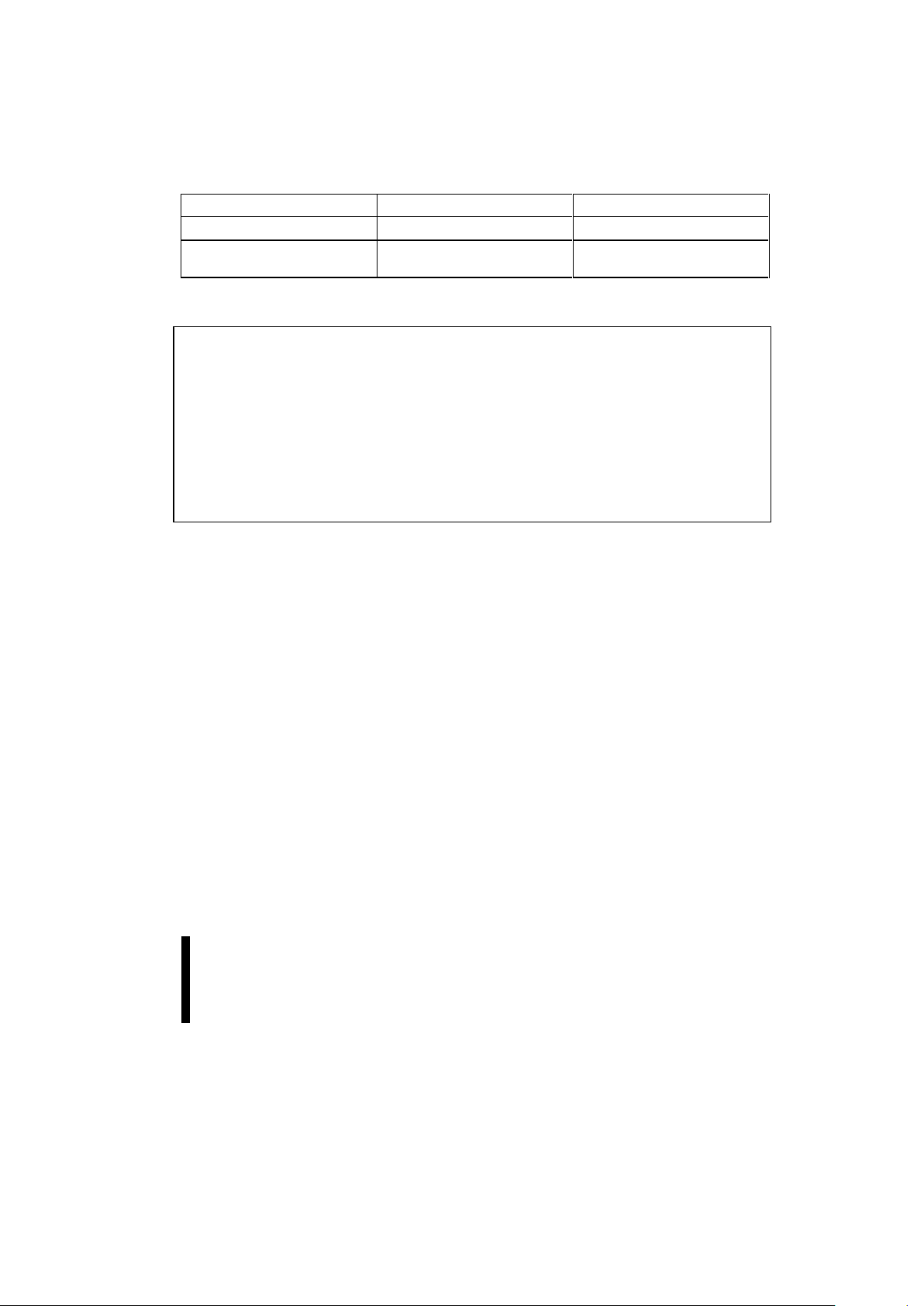

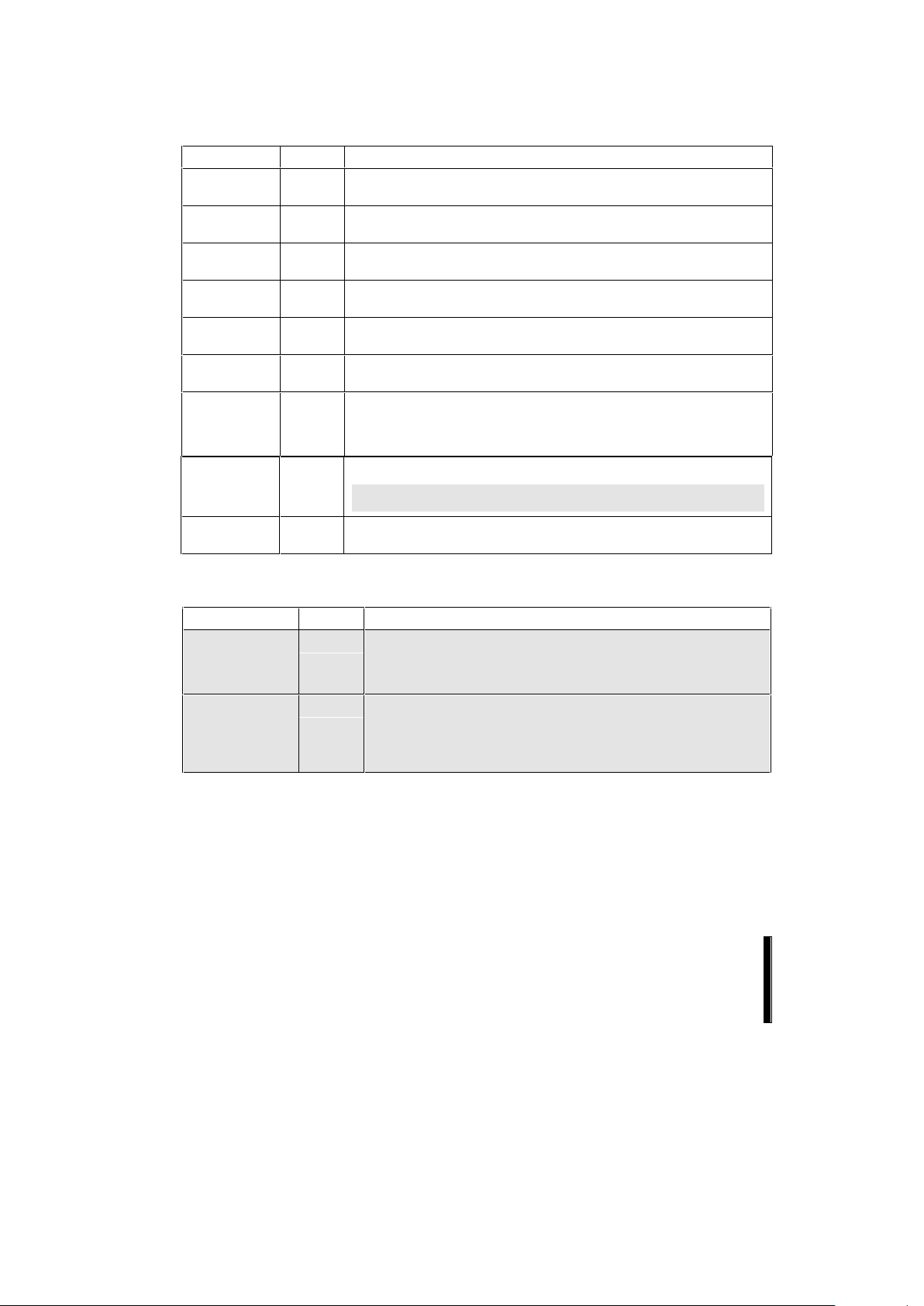

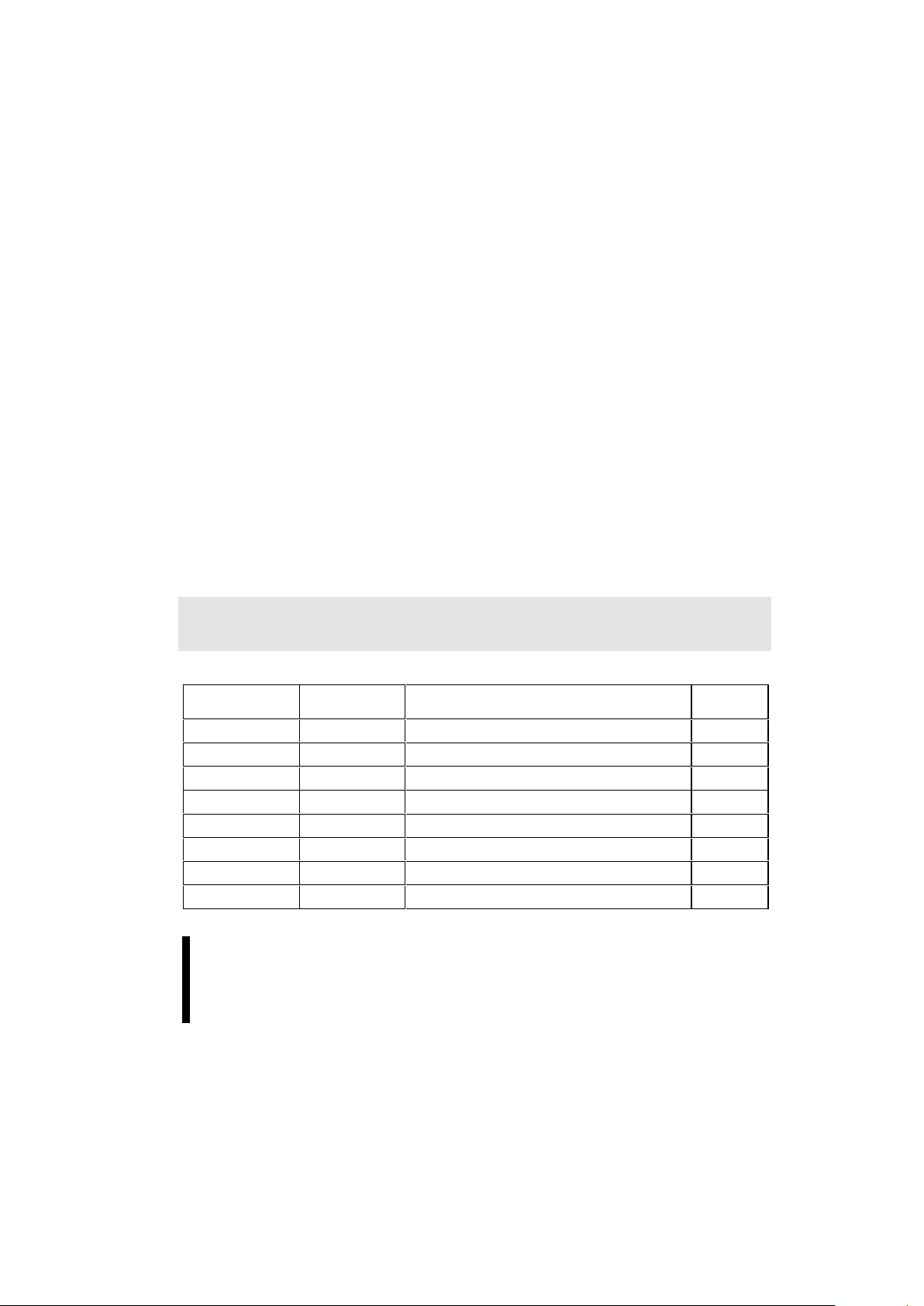

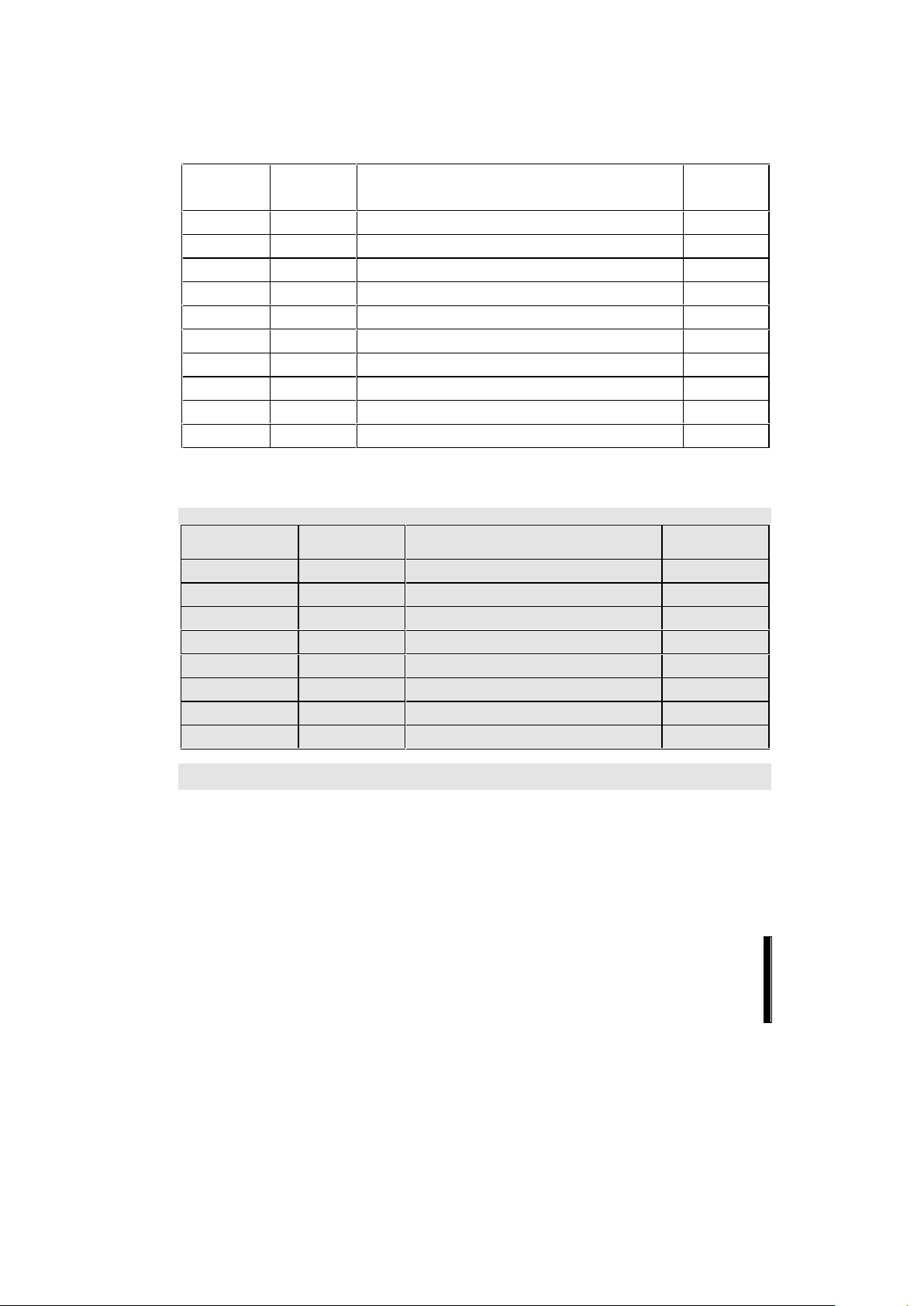

This document describes the PIIX 3 Component. Uns haded areas desc ribe the 82371FB P IIX. Shaded areas,

like this one, describe the PIIX3 operations that differ from the 82371FB PIIX.

82371FB (PIIX) AND 82371SB (PIIX3)

PCI ISA IDE XCELERATOR

82371FB (PIIX) AND 82371SB (PIIX3) E

2

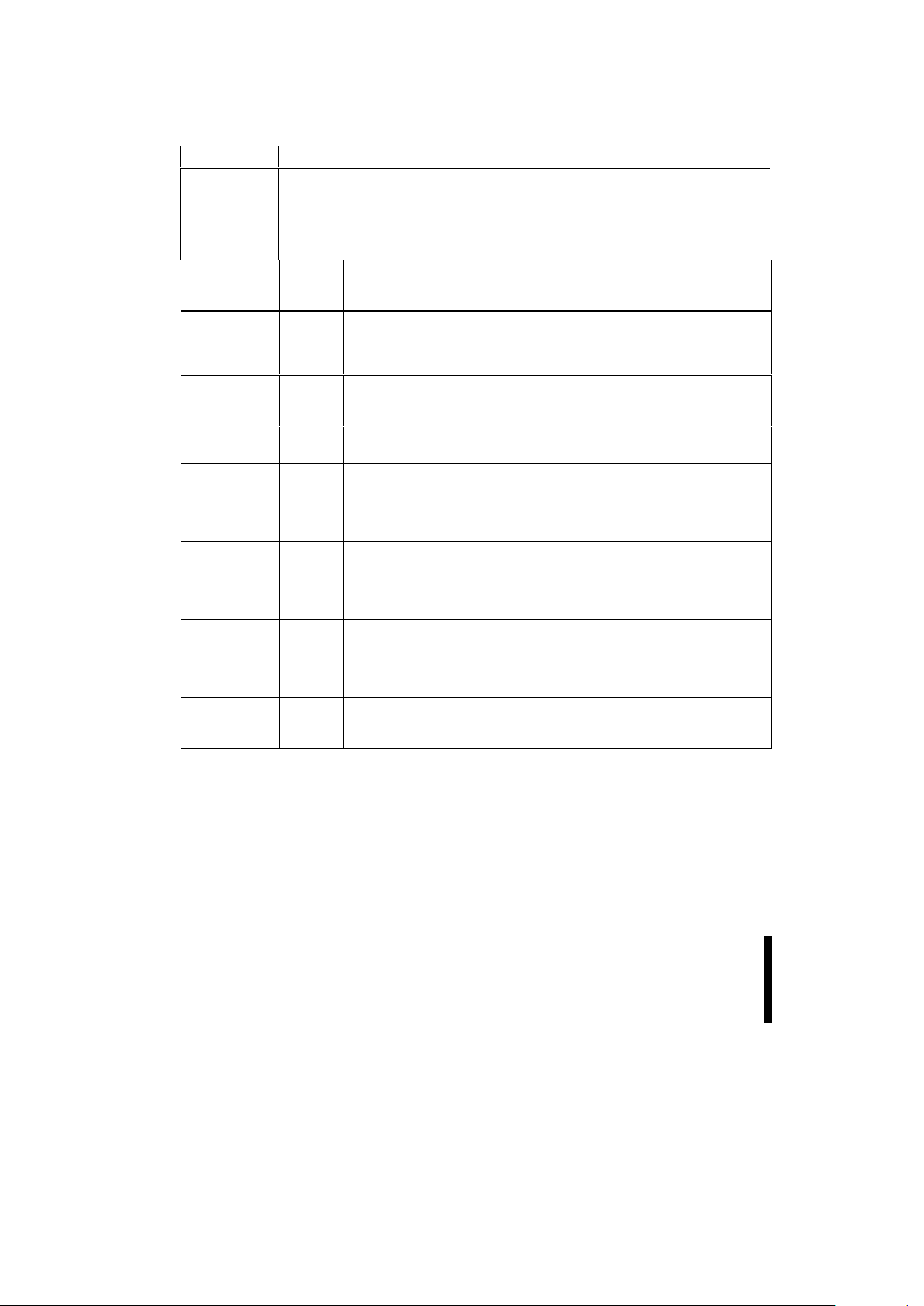

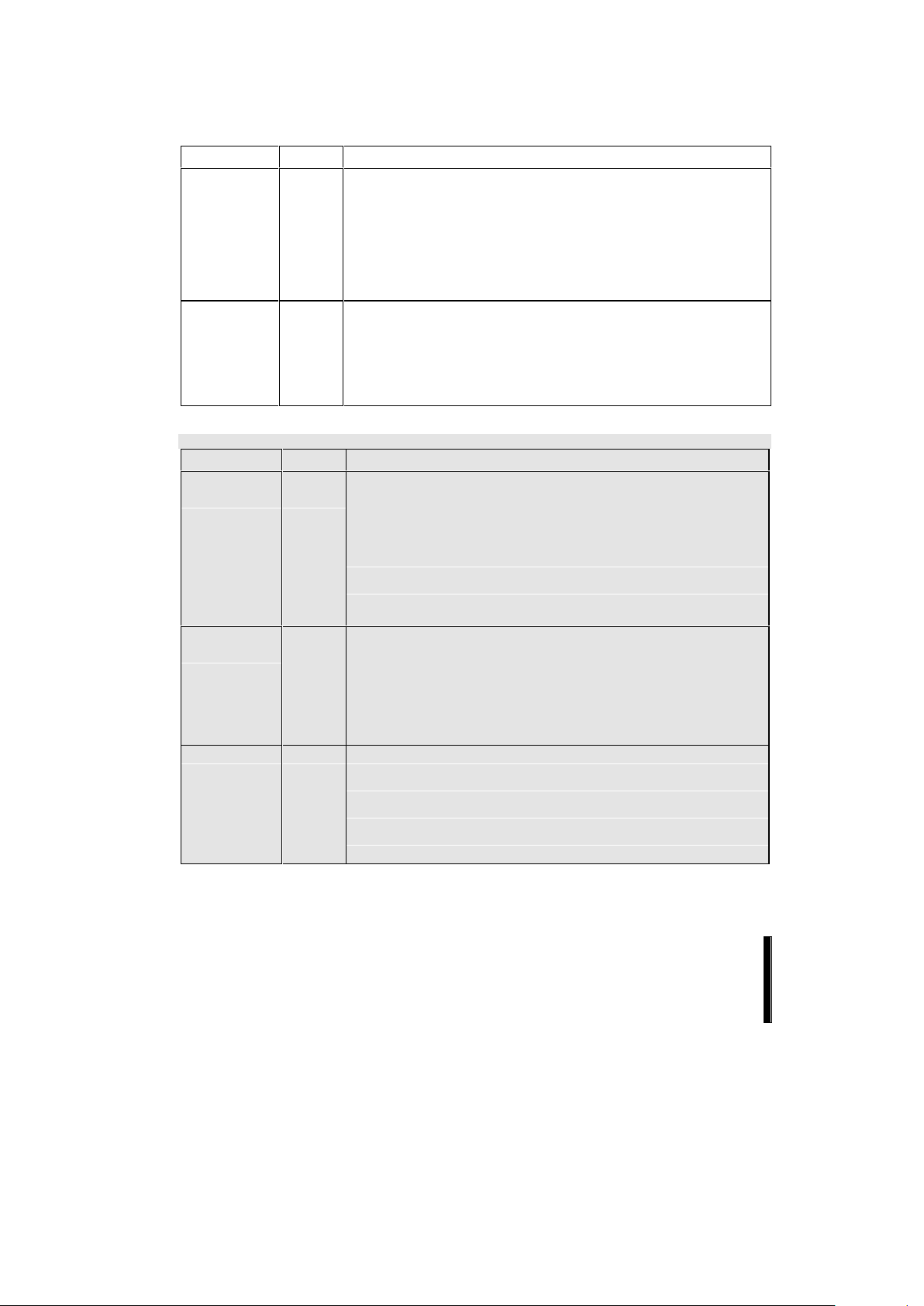

USBP1

USBP0

PCI

Bus

Interface

ISA

Bus

Interface

Mother

Board

Interface

Interrupt

Timers/

Counters

DMA

PCICLK

AD[31:0]

C/BE [3 :0 ]#

FRAME#

IRDY #

TRDY#

STOP#

DEVSEL#

SERR#

PAR

IDSEL

MIRQ1

MD R Q[1:0]

MDAK[1:0]#

INTR

NMI

IRQ(15,14,11:9,7:3,1)

DACK[7:5,3:0]#

TC

REFRESH#

SD[15:0]

LA23/CS1S

IOCS16#

MEMCS16#

DD12/SBHE#

MEMR#

MEMW#

AEN

IOCHRDY

IOCHK#

SYSCLK

BALE

IOR#

IOW #

SMEMR#

SMEMW#

ZEROWS#

blkdia.drw

SPKR

FERR#

IGNN E #

X-Bus

Support

Logic

OSC

IRQ12/M

IRQ8 #

Test

TESTIN# or APICREQ#

PIRQ[A:D]#

SMI#

STPCLK#

EXTSMI#

System

Power

Mgmt

PHOLD#

PHOLDA#

System

Reset

PWROK

CPURST

PCIRST# or APICACK#

RSTDRV

INIT

IDE

Interface

SA[7:0]

DD[11:0]/SA[19:8]

M

U

X

LA22/CS3S

LA21/CS1P

LA20/CS3P

LA19:17]/DA[2:0]

DIOR#

DIOW#

DDRQ[1:0]

DDAK[1:0]#

IORDY

SOE#

SDIR

DD15/PCS#

M

U

X

XDIR#

XOE#

RTCALE

BIOSCS#

RTCCS#

KBCS#

DD13

DREQ[7:5,3:0]

I/O AP IC

Support

Logic

M

U

X

DD14

PCIRST#

TESTIN#

DD14 or A PICCS #

Universial

Serial

Interfac e

USBCLK

PIIX O n ly

(Not On PIIX3 )

MIRQ0

PIIX3 O nly

(Not On PIIX)

PIIX3 Only

(Not On PIIX )

Note:

1. IOAPIC signals are multiplexed with signals from the System Reset, Test, and IDE Interface blocks

2. PIRQD# is an input on the PIIX and bi-directional on PIIX3.

PIIX/PIIX3 Simplified Block Diagram

E 82371FB (PIIX) AND 82371SB (PIIX3)

3

CONTENTS

PAGE

REVISION HISTORY...................................................................................................................................... 7

1.0. SIGNAL DESCRIPTION.......................................................................................................................... 9

1.1. PCI Interface Signals ........................................................................................................................... 9

1.2. Motherboard I/O Device Interface Signals.......................................................................................... 10

1.3. IDE Interface Signals ......................................................................................................................... 11

1.4. ISA Interface Signals.......................................................................................................................... 13

1.5. DMA Signals...................................................................................................................................... 15

1.6. Timer/Counter Signals........................................................................................................................ 15

1.7. Interrupt Controller Signals................................................................................................................. 16

1.8. System Power Management (SMM) Signals......................................................................................16

1.9. X-Bus Signals .................................................................................................................................... 17

1.10. APIC Bus Signals (PIIX3 Only) ........................................................................................................ 18

1.11. Universal Serial Bus Signals (PIIX3 Only)........................................................................................19

1.12. System Reset Signals...................................................................................................................... 19

1.13. Test Signals.....................................................................................................................................20

1.14. Power and Ground Signals............................................................................................................... 20

1.15. Signal State During Reset................................................................................................................ 21

2.0. REGISTER DESCRIPTION...................................................................................................................22

2.1. Register Access................................................................................................................................. 22

2.2. PCI Configuration Registers—PCI To ISA Bridge (Function 0)........................................................... 31

2.2.1. VID—VENDOR IDENTIFICATION REGISTER (Function 0)........................................................ 31

2.2.2. DID—DEVICE IDENTIFICATION REGISTER (Function 0) .........................................................31

2.2.3. PCICMD—COMMAND REGISTER (Function 0)......................................................................... 31

2.2.4. PCISTS—PCI DEVICE STATUS REGISTER (Function 0).......................................................... 32

2.2.5. RID—REVISION IDENTIFICATION REGISTER (Function 0)...................................................... 33

2.2.6. CLASSCCLASS CODE REGISTER (Function 0)..................................................................... 33

2.2.7. HEDT—HEADER TYPE REGISTER (Function 0)....................................................................... 33

2.2.8. IORT—ISA I/O RECOVERY TIMER REGISTER (Function 0)..................................................... 33

2.2.9. XBCS—X-BUS CHIP SELECT REGISTER (Function 0)............................................................. 34

2.2.10. PIRQRC[A:D]—PIRQx ROUTE CONTROL REGISTERS (Function 0)...................................... 36

2.2.11. TOM—TOP OF MEMORY REGISTER (Function 0).................................................................. 36

2.2.12. MSTAT—MISCELLANEOUS STATUS REGISTER (Function 0)............................................... 37

2.2.13. MBIRQ[1:0]—MOTHERBOARD DEVICE IRQ ROUTE CONTROL REGISTERS (Function 0).. 39

2.2.14. MBDMA[1:0]—MOTHERBOARD DEVICE DMA CONTROL REGISTERS (Function 0) ............40

2.2.15. PCSC—PROGRAMMABLE CHIP SELECT CONTROL REGISTER (Function 0) .....................40

2.2.16. APICBASE—APIC BASE ADDRESS RELOCATION REGISTER (Function 0) (PIIX3 Only)..... 41

2.2.17. DLC—DETERMINISTIC LATENCY CONTROL REGISTER (Function 0) (PIIX3 Only) ............. 42

2.2.18. SMICNTL—SMI CONTROL REGISTER (Function 0)................................................................ 43

82371FB (PIIX) AND 82371SB (PIIX3) E

4

2.2.19. SMIEN—SMI ENABLE REGISTER (Function 0) .......................................................................43

2.2.20. SEE—SYSTEM EVENT ENABLE REGISTER (Function 0) ...................................................... 44

2.2.21. FTMR—FAST OFF TIMER REGISTER (Function 0)................................................................. 45

2.2.22. SMIREQ—SMI REQUEST REGISTER (Function 0) ................................................................. 45

2.2.23. CTLTMR—CLOCK SCALE STPCLK# LOW TIMER (Function 0).............................................. 46

2.2.24. CTHTMR—CLOCK SCALE STPCLK# HIGH TIMER (Function 0)............................................. 47

2.3. PCI Configuration Registers—IDE Interface (Function 1)................................................................... 47

2.3.1. VID—Vendor Identification Register (Function 1) ........................................................................ 47

2.3.2. DID—DEVICE IDENTIFICATION REGISTER (Function 1) ......................................................... 47

2.3.3. PCICMD—COMMAND REGISTER (Function 1)......................................................................... 48

2.3.4. PCISTS—PCI DEVICE STATUS REGISTER (Function 1).......................................................... 48

2.3.5. RID—REVISION IDENTIFICATION REGISTER (Function 1)...................................................... 49

2.3.6. CLASSCCLASS CODE REGISTER (Function 1)..................................................................... 49

2.3.7. MLT—MASTER LATENCY TIMER REGISTER (Function 1) ...................................................... 49

2.3.8. HEDT—HEADER TYPE REGISTER (Function 1)....................................................................... 50

2.3.9. BMIBA—BUS MASTER INTERFACE BASE ADDRESS REGISTER (Function 1) ......................50

2.3.10. IDETIM—IDE TIMING REGISTER (Function 1) ........................................................................ 51

2.3.11. SIDETIM—SLAVE IDE TIMING REGISTER (Function 1) (PIIX3 Only) ..................................... 52

2.4. PCI Configuration RegistersUniversal Serial Bus (Function 2) (PIIX3 Only).................................... 53

2.4.1. VID—VENDOR IDENTIFICATION REGISTER (Function 2) (PIIX3)............................................ 53

2.4.2. DIDDEVICE IDENTIFICATION REGISTER (Function 2) (PIIX3) ............................................. 54

2.4.3. PCICMDCOMMAND REGISTER (Function 2) (PIIX3)............................................................. 54

2.4.4. DSDEVICE STATUS REGISTER (Function 2) (PIIX3)............................................................. 55

2.4.5. RIDREVISION IDENTIFICATION REGISTER (Function 2) (PIIX3).......................................... 55

2.4.6. CLASSCCLASS CODE REGISTER (Function 2) (PIIX3)......................................................... 56

2.4.7. MLTMASTER LATENCY TIMER REGISTER (Function 2) (PIIX3) .......................................... 56

2.4.8. HEDTHEADER TYPE REGISTER (Function 2) (PIIX3)........................................................... 57

2.4.9. BASEADD

I/O SPACE BASE ADDRESS (Function 2) (PIIX3) ................................................57

2.4.10. ILInterrupt Line Register (Function 2) (PIIX3)......................................................................... 57

2.4.11. INTRPINTERRUPT PIN (Function 2) (PIIX3)......................................................................... 58

2.4.12. SBRNUMSERIAL BUS RELEASE NUMBER (Function 2) (PIIX3)......................................... 58

2.4.13. MSTATMISCELLANEOUS STATUS REGISTER (Function 2) (PIIX3)................................... 58

2.4.14. LEGSUPLEGACY SUPPORT REGISTER (FUNCTION 2) (PIIX3) ........................................59

2.5. ISA-Compatible Registers.................................................................................................................. 61

2.5.1. DMA REGISTERS....................................................................................................................... 61

2.5.1.1. DCOM—DMA Command Register........................................................................................ 61

2.5.1.2. DCM—DMA Channel Mode Register.................................................................................... 61

2.5.1.3. DR—DMA Request Register................................................................................................. 62

2.5.1.4. Mask Register—Write Single Mask Bit ................................................................................. 63

2.5.1.5. Mask Register—Write All Mask Bits...................................................................................... 63

2.5.1.6. DS—DMA Status Register.................................................................................................... 64

2.5.1.7. DMA Base And Current Address Registers (8237 Compatible Segment).............................. 64

2.5.1.8. DMA Base And Current Byte/Word Count Registers (Compatible Segment) ........................ 65

E 82371FB (PIIX) AND 82371SB (PIIX3)

5

2.5.1.9. DMA Memory Low Page Registers....................................................................................... 65

2.5.1.10. DMA Clear Byte Pointer Register........................................................................................ 66

2.5.1.11. DMC—DMA Master Clear Register..................................................................................... 66

2.5.1.12. DCLM—DMA Clear Mask Register..................................................................................... 66

2.5.2. TIMER/COUNTER REGISTER DESCRIPTION .......................................................................... 66

2.5.2.1. TCW—Timer Control Word Register..................................................................................... 66

2.5.2.2. Interval Timer Status Byte Format Register .......................................................................... 68

2.5.2.3. Counter Access Ports Register............................................................................................. 69

2.5.3. INTERRUPT CONTROLLER REGISTERS .................................................................................69

2.5.3.1. ICW1—Initialization Command Word 1 Register................................................................... 70

2.5.3.2. ICW2—Initialization Command Word 2 Register................................................................... 70

2.5.3.3. ICW3—Initialization Command Word 3 Register................................................................... 71

2.5.3.4. ICW3—Initialization Command Word 3 Register................................................................... 71

2.5.3.5. ICW4—Initialization Command Word 4 Register................................................................... 71

2.5.3.6. OCW1—Operational Control Word 1 Register...................................................................... 72

2.5.3.7. OCW2—Operational Control Word 2 Register...................................................................... 72

2.5.3.8. OCW3—Operational Control Word 3 Register...................................................................... 73

2.5.3.9. ELCR1—Edge/Level Triggered Register............................................................................... 74

2.5.3.10. ELCR2—Edge/Level Triggered Register............................................................................. 74

2.5.4. X-BUS, COPROCESSOR, and RESET REGISTERS ................................................................. 75

2.5.4.1. Reset X-Bus IRQ12 And IRQ1 Register................................................................................ 75

2.5.4.2. Coprocessor Error Register ..................................................................................................75

2.5.4.3. RC—Reset Control Register................................................................................................. 75

2.5.5. NMI REGISTERS........................................................................................................................ 76

2.5.5.1. NMISC—NMI Status And Control Register...........................................................................76

2.5.5.2. NMI Enable and Real-Time Clock Address Register............................................................. 77

2.6. System Power Management Registers .............................................................................................. 77

2.6.1. APMC—ADVANCED POWER MANAGEMENT CONTROL PORT............................................. 77

2.6.2. APMS—ADVANCED POWER MANAGEMENT STATUS PORT ................................................ 78

2.7. PCI BUS Master IDE Registers.......................................................................................................... 78

2.7.1. BMICOM—BUS MASTER IDE COMMAND REGISTER ............................................................. 78

2.7.2. BMISTA—BUS MASTER IDE STATUS REGISTER ................................................................... 79

2.7.3. BMIDTP—BUS MASTER IDE DESCRIPTOR TABLE POINTER REGISTER ............................. 80

2.8. USB I/O Registers.............................................................................................................................. 80

2.8.1. USBCMDUSB Command Register........................................................................................... 80

2.8.2. USBSTSUSB Status Register.................................................................................................. 82

2.8.3. USBINTRUSB Interrupt Enable Register ................................................................................. 83

2.8.4. FRNUMFrame Number Register.............................................................................................. 83

2.8.5. FLBASEADDFrame List Base Address Register...................................................................... 84

2.8.6. Start Of Frame (SOF) Modify Register ........................................................................................ 84

2.8.7. PORTSCPort Status and Control Register............................................................................... 85

3.0. FUNCTIONAL DESCRIPTION ..............................................................................................................89

82371FB (PIIX) AND 82371SB (PIIX3) E

6

3.1. Memory and I/O Address Map ........................................................................................................... 89

3.1.1. I/O Accesses............................................................................................................................... 89

3.1.2. Memory Address Map ................................................................................................................. 89

3.1.3. BIOS MEMORY........................................................................................................................... 90

3.2. PCI Interface...................................................................................................................................... 90

3.2.1. TRANSACTION TERMINATION .................................................................................................90

3.2.2. PARITY SUPPORT..................................................................................................................... 91

3.2.3. PCI ARBITRATION .....................................................................................................................91

3.3. ISA Interface...................................................................................................................................... 92

3.4. DMA Controller...................................................................................................................................93

3.4.1. TYPE F TIMING..........................................................................................................................94

3.4.2. ISA REFRESH CYCLES .............................................................................................................94

3.5. PCI Local Bus IDE ............................................................................................................................. 95

3.5.1. ATA REGISTER BLOCK DECODE............................................................................................. 96

3.5.2. ENHANCED TIMING MODES..................................................................................................... 97

3.5.2.1. Back-To-Back PIO IDE Transactions.................................................................................... 98

3.5.2.2. IORDY Masking .................................................................................................................... 98

3.5.2.3. PIO 32 Bit IDE Data Port Mode ............................................................................................ 98

3.5.3. BUS MASTER FUNCTION.......................................................................................................... 98

3.6. Universal Serial Bus Host Controller (PIIX3 only)............................................................................. 100

3.7. Interval Timer................................................................................................................................... 102

3.8. Interrupt Controller...........................................................................................................................103

3.8.1. PROGRAMMING THE ICWs/OCWs ......................................................................................... 104

3.8.2. EDGE AND LEVEL TRIGGERED MODE.................................................................................. 104

3.8.3. INTERRUPT STEERING........................................................................................................... 104

3.9. Stand-Alone IOAPIC Support (PIIX3)............................................................................................... 105

3.10. INTR Signaling with Pentium® processor Local APIC in Virtual Wire Mode ................................... 106

3.11. X-Bus Peripheral Support............................................................................................................... 107

3.12. Power Management....................................................................................................................... 108

3.12.1. SMM MODE............................................................................................................................ 109

3.12.2. SMI SOURCES.......................................................................................................................109

3.12.3. CLOCK CONTROL.................................................................................................................. 110

3.13. Reset Support................................................................................................................................ 110

3.13.1. HARDWARE STRAPPING OPTIONS.....................................................................................111

4.0. PINOUT AND PACKAGE INFORMATION.......................................................................................... 112

4.1. Pinout............................................................................................................................................... 112

4.2. PACKAGE DIMENSIONS................................................................................................................117

5.0. TESTABILITY (PIIX/PIIX3).................................................................................................................. 118

5.1. Test Mode Description .....................................................................................................................118

5.2. NAND Tree Mode............................................................................................................................. 118

5.3. Tri-state Mode.................................................................................................................................. 122

E 82371FB (PIIX) AND 82371SB (PIIX3)

7

REVISION HISTORY

Revision Date Version Description

May 1996 -001 Initial Release

April 1997 -002 Included information from

Specification Update

Information in this document is provided in connection with Intel products. No l icense, express or impli ed,

by estoppel or otherwise, to any intellectual property right s is granted by this document or by the s ale of

Intel products. Except as provided in Int el’s Term s and Condit ions of S ale f or suc h product s, Intel assum es

no liability whatsoever, and Intel disclaims any express or im plied warranty, relating to sale and/or use of

Intel products including liability or warranties relating t o fitness for a particular purpose, merchant ability, or

infringement of any patent, copyright or other intellec tual property right. Intel products are not intended for

use in medical, life saving, or life sustaining applications. Intel retains the right to make changes to

specifications and product desc riptions at any time, without not ice. The Intel 82371FB and 82371SB m ay

contain design defects or errors known as errata. W hich may c ause the products to deviate from published

specifications . Suc h errata are not c overed by Intel ’s warranty. Current c haracte rized errata are avai lable i n

“Intel 430FX TSC/TDP/PIIX Specification Update (Order#297733)and I ntel 82371SB (PIIX3) PCI ISA IDE

Xcelerator Specification Update (Order#297658). Third-party brands and names are the property of their

respective owners.

82371FB (PIIX) AND 82371SB (PIIX3) E

8

E 82371FB (PIIX) AND 82371SB (PIIX3)

9

1.0. SIGNAL DESCRIPTION

This section contains a detailed description of each signal. The signals are arranged in functional groups

according to their interface.

Note that the ’#’ symbol at the end of a signal name indic ates t hat the active, or ass erted stat e occurs when

the signal is at a low volt age level. When ’#’ is not present after t he signal name, the s ignal i s as serted when

at the high voltage level.

The terms assertion and negation are us ed extens ively . This i s done t o avoid conf usion when working with a

mixture of ’active-low’ and ’active-high’ signals. The t erm assert, or assertion indicat es t hat a s ignal is ac tiv e,

independent of whether that level is represented by a high or low voltage. The term negate, or negation

indicates that a signal is inactive.

Note that certain signal pins provide two separate functions. At the system level, these pins drive other

signals with different functions through ex ternal buffers or trans ceivers. These pins hav e two diff erent signal

names depending on the function. These s ignal names hav e been noted in t he signal desc ription t ables, wi th

the signal whose function is being described in bold font. (For example, LA23/CS1S is in the section

describing CS1S and LA23/CS1S is in the section describing LA23).

The following notations are used to describe the signal type.

I

Input

is a standard input-only signal.

O

Totem Pole Output

is a standard active driver.

I/O

Input/Output

is a bi-directional, tri-state signal.

od

Open Drain

allows multiple devices to share as a wire-OR.

st Schmitt Trigger input.

t/s

Tri-State

is a bi-directional, tri-state input/output pin.

s/t/s

Sustained Tri-state

is an active low tri-s tate signal owned and driv en by one and only one agent at a

time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float.

A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tristates it. An external pull-up is required to sustain t he inactive state unt il another agent drives it and

must be provided by the central resource.

1.1. PCI Interface Signals

Signal Name Type Description

PCICLK I PCI CLOCK: PCICLK provides timing for all transactions on the PCI Bus.

All other PCI signals are sampled on the rising edge of PCICLK, and all

timing parameters are defined with respect to this edge. PCI frequencies of

25–33 MHz are supported.

AD[31:0] I/O PCI ADDRESS/DATA: The standard PCI address and data lines. The

address is driven with FRAME# assertion and data is driven or received in

following clocks

C/BE[3:0]# I/O BUS COMMAND AND BYTE ENABLES: The command is driven with

FRAME# assertion. Byte enables corresponding to supplied or requested

data is driven on following clocks.

FRAME# I/O

(s/t/s)

FRAME: Assertion indicates the address phase of a PCI transfer.

Negation indicates that one more data transfer is desired by the cycle

initiator.

82371FB (PIIX) AND 82371SB (PIIX3) E

10

Signal Name Type Description

TRDY# I/O

(s/t/s)

TARGET READY: Asserted when the target is ready for a data transfer.

IRDY# I/O

(s/t/s)

INITIATOR READY: Asserted when the initiator is ready for a data

transfer.

STOP# I/O

(s/t/s)

STOP: Asserted by the target to request the master to stop the current

transaction.

IDSEL I INITIALIZATION DEVICE SELECT: IDSEL is used as a chip select during

configuration read and write transactions.

DEVSEL# I/O

(s/t/s)

DEVICE SELECT: The PIIX/PIIX3 asserts DEVSEL# to claim a PCI

transaction through positive or subtractive decoding.

PAR O CALCULATED PARITY SIGNAL: PAR is "even" parity and is calculated

on 36 bits—AD[31:0] plus C/BE[3:0]#.

SERR# I SYSTEM ERROR: SERR# can be pulsed active by any PCI device that

detects a system error condition. Upon sampling SERR# active, the

PIIX/PIIX3 can be programmed to generate a non-maskable interrupt

(NMI) to the CPU.

PHOLD# O PCI HOLD: The PIIX/PIIX3 asserts this signal to request the PCI Bus.

The PIIX3 implements the passive release mechanism by toggling PHOLD#

inactive for one PCICLK.

PHLDA# I PCI HOLD ACKNOWLEDGE: This signal is asserted to grant the PCI bus

to the PIIX/PIIX3.

1.2. Motherboard I/O Device Interface Signals

Signal Name Type Description

MDRQ[1:0]

(PIIX Only)

I MOTHERBOARD DEVICE DMA REQUEST: These signals can be

connected internally to any of DREQ[3:0,7:5]. Each pair of request/

acknowledge signals is controlled by a separate register. Each signal

can be configured as steerable interrupts for motherboard devices.

MDAK[1:0]#

(PIIX Only)

O MOTHERBOARD DEVICE DMA ACKNOWLEDGE: These signals

can be connected internally to any of DACK[3:0,7:5]. Each pair of

request/ acknowledge signals is controlled by a separate register.

Each signal can be configured as steerable interrupts for motherboard

devices.

E 82371FB (PIIX) AND 82371SB (PIIX3)

11

Signal Name Type Description

MIRQ0/IRQ0

(PIIX3 Only)

MIRQ[1:0]

(PIIX Only)

I/O

I

MOTHERBOARD DEVICE INTERRUPT REQUEST: The MIRQx

signals can be internally connected to interrupts IRQ[15,14,12:9,7:3].

Each MIRQx line has a separate Route Control Register. If MIRQx and

PIRQx# are steered to the same ISA interrupt, the device connected to

the MIRQx should produce active high, level interrupts. The

MIRQ0/IRQ0 signal has two functions (for PIIX3 only), depending on

the programming of the IRQ0 Enable bit (MIRQ0 Register). In the

systems that include the PIIX3 and IOAPIC, the MIRQ0/IRQ0 pin will

function as the IRQ0 output and should be connected to the INTIN2

input of the IOAPIC. The interrupt from the Secondary IDE Channel

should be connected to the IRQ15 input on PIIX3 and to the INTIN15

input on the IOAPIC. In the systems that include the PIIX3 only, the

interrupt from the Secondary IDE Channel should be connected to the

MIRQ0/IRQ0 input.

If an MIRQ line is steered to a given IRQ input to the internal 8259, the

corresponding ISA IRQ is masked, unless the Route Control register is

programmed to allow the interrupts to be shared. This should only be

done if the device connected to the MIRQ line and the device

connected to the ISA IRQ line both produce active high, level

interrupts.

MIRQ0 can be configured as an output to connect the internal IRQ0

signal to an external IO-APIC.

1.3. IDE Interface Signals

Signal Name Type Description

DD[15:0]/

PCS#,

SBHE#,

SA[19:8]

APICCS#

(PIIX3)

I/O

O

I/O

I/O

O

DISK DATA: These signals directly drive the corresponding signals on

up to two IDE connectors (primary and secondary). In addition, these

signals are buffered (using 2xALS245’s on the motherboard) to produce

the SA[19:8], PCS#, and SBHE# signals (see separate descriptions).

For the PIIX3, DD14 is buffered to produce APICCS#

DIOR# O DISK I/O READ: This signal directly drives the corresponding signal on

up to two IDE connectors (primary and secondary).

DIOW# O DISK I/O WRITE: This signal directly drives the corresponding signal on

up to two IDE connectors (primary and secondary).

DDRQ[1:0] I DISK DMA REQUEST: These input signals are directly driven from the

DRQ signals on the primary (DDRQ0) and secondary (DDRQ1) IDE

connectors. They are used in conjunction with the PCI Bus master IDE

function and are not associated with any ISA-Compatible DMA channel.

DDAK[1:0]# O DISK DMA ACKNOWLEDGE: These signals directly drive the DAK#

signals on the primary (DDAK0# ) and secondary (DDAK1#) IDE

connectors. These signals are used in conjunction with the PCI Bus

master IDE function and are not associated with any ISA-Compatible

DMA channel.

82371FB (PIIX) AND 82371SB (PIIX3) E

12

Signal Name Type Description

IORDY I IO CHANNEL READY: This input signal is directly driven by the

corresponding signal on up to two IDE connectors (primary and

secondary).

SOE# O SYSTEM ADDRESS TRANSCEIVER OUTPUT ENABLE: This signal

controls the output enables of the ’245 transceivers that interface the

DD[15:0] signals to the SA[19:8], SBHE#, PCS# and APICCS# (PIIX3

only) signals.

SDIR O SYSTEM ADDRESS TRANSCEIVER DIRECTION: This signal controls

the direction of the ’245 transceivers that interface the DD[15:0] signals

to the SA[19:8], SBHE#, PCIS, and APICCS# (PIIX3 only), signals.

Default condition is high (transmit). When an ISA Bus master is granted

use of the bus, the transceivers are turned around to drive the ISA

address [19:8] on DD[15:3]. The address can then be latched by the

PIIX/PIIX3. In this case, the SDIR signal is low (receive). The SOE# and

SDIR signals taken together as a group can assume one of three states:

SOE# SDIR State

0 1 PCI to ISA transaction

1 1 PCI to IDE

0 0 ISA Bus master

Signals Buffered from LA[23:17]

These signals are buffered from the LA[23:17] lines by an ALS244 tri-stat e buffer. The output enable of thi s

buffer is tied asserted. These signals are set up with respect to the IDE command strobes (DIO R# and IOW#)

and are valid throughout I/O transactions targeting the ATA register block(s).

Signal Name Type Description

LA23/

CS1S

I/O CHIP SELECT: CS1S is for the ATA command register block and

corresponds to the inverted CS1FX# on the secondary IDE connector.

CS1S is inverted externally (see PCI Local Bus IDE section).

LA22/

CS3S

I/O CHIP SELECT: CS3S is for the ATA control register block and

corresponds to the inverted CS3FX# on the secondary IDE connector.

CS3S is inverted externally (see PCI Local Bus IDE section).

LA21/

CS1P

I/O CHIP SELECT: CS1P is for the ATA command register block and

corresponds to the inverted CS1FX# on the primary IDE connector. CS1P

is inverted externally (see PCI Local Bus IDE section).

LA20/

CS3P

I/O CHIP SELECT: CS3P is for the ATA control register block and

corresponds to the inverted CS3FX# on the primary IDE connector. CS3P

is inverted externally (see PCI Local Bus IDE section).

LA[19:17]

DA[2:0]

I/O DISK ADDRESS: DA[2:0] are used to indicate which byte in either the

ATA command block or control block is being addressed.

E 82371FB (PIIX) AND 82371SB (PIIX3)

13

1.4. ISA Interface Signals

Signal Name Type Description

BALE O BUS ADDRESS LATCH ENABLE: BALE is an active high signal asserted

by the PIIX/PIIX3 to indicate that the address (SA[19:0], LA[23:17]) and

SBHE# signal lines are valid.

AEN O ADDRESS ENABLE: AEN is asserted during DMA cycles to prevent I/O

slaves from misinterpreting DMA cycles as valid I/O cycles. This signal is

also driven high during PIIX/PIIX3 initiated refresh cycles.

For the PIIX, when TC is sampled low on the assertion of PWORK (External

DMA mode), the PIIX tri-states this signal.

SYSCLK O ISA SYSTEM CLOCK: SYSCLK is the reference clock for the ISA Bus and

drives the bus directly. SYSCLK is generated by dividing PCICLK by 3 or 4.

The SYSCLK frequencies supported are 7.5 MHz and 8.33 MHz. SYSCLK

is a divided down version of PCICLK.

Hardware Strapping Option

SYSCLK is tri-stated when PWROK is negated. The value of SYSCLK is

sampled on the assertion of PWROK: If sampled high, the ISA clock divisor

is 3 (for 25 MHz PCI). If sampled low, the divisor is 4 (for 30 and 33 MHz

PCI).

IOCHRDY I/O I/O CHANNEL READY: Resources on the ISA Bus negate IOCHRDY to

indicate that additional time (wait states) is required to complete the cycle.

This signal is normally high on the ISA Bus. IOCHRDY is an input when the

PIIX/PIIX3 owns the ISA Bus and the CPU or a PCI agent is accessing an

ISA slave or during DMA transfers. IOCHRDY is output when an external

ISA Bus Master owns the ISA Bus and is accessing DRAM or a PIIX/PIIX3

register.

IOCS16# I 16-BIT I/O CHIP SELECT: This signal is driven by I/O devices on the ISA

Bus to indicate that they support 16-bit I/O bus cycles.

IOCHK# I I/O CHANNEL CHECK: IOCHK# can be driven by any resource on the ISA

Bus. When asserted, it indicates that a parity or an uncorrectable error has

occurred for a device or memory on the ISA Bus. If enabled, a NMI is

generated to the CPU.

IOR# I/O I/O READ: IOR# is the command to an ISA I/O slave device that the slave

may drive data on to the ISA data bus (SD[15:0]).

IOW# I/O I/O WRITE: IOW# is the command to an ISA I/O slave device that the slave

may latch data from the ISA data bus (SD[15:0]).

LA[23:17]/

CS1S

CS3S

CS1P

CS3P

DA[2:0]

I/O/

O

O

O

O

O

UNLATCHED ADDRESS: The LA[23:17] address lines are bi-directional.

These address lines allow accesses to physical memory on the ISA Bus up

to 16 Mbytes.

The LA[23:17] are also used to drive the IDE interface chip selects and

address lines via an external ALS244 buffer. See the IDE Interface signal

descriptions.

82371FB (PIIX) AND 82371SB (PIIX3) E

14

Signal Name Type Description

SA[7:0],

SA[19:8]/

DD[11:0]

I/O

I/O

I/O

SYSTEM ADDRESS BUS: These bi-directional address lines define the

selection with the granularity of one byte within the one-Mbyte section of

memory defined by the LA[23:17] address lines. The address lines

SA[19:17] that are coincident with LA[19:17] are defined to have the same

values as LA[19:17] for all memory cycles. For I/O accesses, only SA[15:0]

are used.

SBHE#/

DD12

I/O

I/O

SYSTEM BYTE HIGH ENABLE: SBHE# indicates, when asserted, that a

byte is being transferred on the upper byte (SD[15:8]) of the data bus.

SBHE# is negated during refresh cycles.

MEMCS16# od MEMORY CHIP SELECT 16: MEMCS16# is a decode of LA[23:17]

without any qualification of the command signal lines. ISA slaves that are

16-bit memory devices drive this signal low. The PIIX/PIIX3 drives this

signal low during ISA master to DRAM Cycles.

MEMR# I/O MEMORY READ: MEMR# is the command to a memory slave that it may

drive data onto the ISA data bus. This signal is also driven by the

PIIX/PIIX3 during refresh cycles.

MEMW# I/O MEMORY WRITE: MEMW# is the command to a memory slave that it

may latch data from the ISA data bus.

SMEMR# O STANDARD MEMORY READ: The PIIX/PIIX3 asserts SMEMR# to

request an ISA memory slave to drive data onto the data lines. If the

access is below 1 Mbyte (00000000–000FFFFFh) during DMA compatible,

PIIX/PIIX3 master, or ISA master cycles, the PIIX/PIIX3 asserts SMEMR#.

SMEMR# is a delayed version of MEMR#.

SMEMW# O STANDARD MEMORY WRITE: The PIIX/PIIX3 asserts SMEMW# to

request an ISA memory slave to accept data from the data lines. If the

access is below 1 Mbyte (00000000–000FFFFFh) during DMA compatible,

PIIX/PIIX3 master, or ISA master cycles, the PIIX/PIIX3 asserts

SMEMW#. SMEMW# is a delayed version of MEMW#.

ZEROWS# I ZERO WAIT-STATES: An ISA slave asserts ZEROWS# after its address

and command signals have been decoded to indicate that the current

cycle can be shortened. A 16-bit ISA memory cycle can be reduced to two

SYSCLKs. An 8-bit memory or I/O cycle can be reduced to three

SYSCLKs. ZEROWS# has no effect during 16-bit I/O cycles.

SD[15:0] I/O SYSTEM DATA: SD[15:0] provide the 16-bit data path for devices residing

on the ISA Bus. SD[15:8] correspond to the high order byte and SD[7:0]

correspond to the low order byte. SD[15:0] are undefined during refresh.

E 82371FB (PIIX) AND 82371SB (PIIX3)

15

1.5. DMA Signals

Signal Name Type Description

DREQ

[7:5,3:0]

I DMA REQUEST: The DREQ lines are used to request DMA service from

the PIIX/PIIX3 ’s DMA controller or for a 16-bit master to gain control of the

ISA expansion bus. The active level (high or low) is programmed via the

DMA Command Register. The request must remain active until the

appropriate DACKx# signal is asserted.

DACK

[7:5,3:0]#

O DMA ACKNOWLEDGE: The DACK output lines indicate that a request

for DMA service has been granted by the PIIX/PIIX3 or that a 16-bit master

has been granted the bus. The active level (high or low) is programmed via

the DMA Command Register. These lines should be used to decode the

DMA slave device with the IOR# or IOW# line to indicate selection. If used

to signal acceptance of a bus master request, this signal indicates when it

is legal to assert MASTER#.

For the PIIX, when TC is sampled low on the assertion of PWORK

(External DMA mode), the PIIX tri-states these signals. This mode is not

available on PIIX3.

TC O TERMINAL COUNT: The PIIX/PIIX3 asserts TC to DMA slaves as a

terminal count indicator. When all the DMA channels are not in use, TC is

negated (low).

Hardware Strapping Option (PIIX Only)

This strapping option selects between the internal ISA DMA mode and

External DMA mode. When TC is sampled high on the assertion of

PWROK (ISA DMA mode), the PIIX drives the AEN, TC, and DACK#[7:5,

3:0] normally. When TC is sampled low on the assertion of PWROK

(External DMA mode), the PIIX tri-states the AEN, TC, and DACK[7:5,

3:0]# signals, and also forwards PCI masters I/O accesses to location

0000h to ISA. TC has an internal pull-up resistor. To tie TC low, an

external 1 KΩ pull-down resistor should be used. For the PIIX3, this signal

should not be pulled down.

REFRESH# I/O REFRESH: As an output, REFRESH# indicates when a refresh cycle is in

progress. It should be used to enable the SA[7:0] address to the row

address inputs of all banks of dynamic memory on the ISA Bus. Thus,

when MEMR# is asserted, the entire expansion bus dynamic memory is

refreshed. Memory slaves must not drive any data onto the bus during

refresh. As an output, this signal is driven directly onto the ISA Bus. This

signal is an output only when the PIIX/PIIX3 DMA refresh controller is a

master on the bus responding to an internally generated request for

refresh. As an input, REFRESH# is driven by 16-bit ISA Bus masters to

initiate refresh cycles.

1.6. Timer/Counter Signals

Signal Name Type Description

SPKR O SPEAKER DRIVE: The SPKR signal is the output of counter 2.

OSC I OSCILLATOR: OSC is the 14.31818 MHz ISA clock signal. It is used by

the internal 8254 Timer.

82371FB (PIIX) AND 82371SB (PIIX3) E

16

1.7. Interrupt Controller Signals

Signal Name Type Description

IRQ[15,14,

11:9, 7:3,1]

I INTERRUPT REQUEST: The IRQ signals provide both system board

components and ISA Bus I/O devices with a mechanism for

asynchronously interrupting the CPU. The assertion mode of these

inputs depends on the programming of the two ELCR registers. The

IRQ14 signal must be used by the Bus Master IDE interface function

to signal interrupts on the primary IDE channel.

IRQ8# I INTERRUPT REQUEST EIGHT SIGNAL: IRQ8# is always an active

low edge triggered interrupt input (i.e., this interrupt can not be

modified by software). Upon PCIRST#, IRQ8# is placed in active low

edge sensitive mode.

IRQ12/M I INTERRUPT REQUEST/MOUSE INTERRUPT: In addition to

providing the standard interrupt function (see IRQ[15,14,11:9,7:3,1]

signal description), this pin can be programmed (via X-Bus Chip

Select Register) to provide a mouse interrupt function.

PIRQ[D:A]# I

I/O For

PIRQD#

(PIIX3

only)

PROGRAMMABLE INTERRUPT REQUEST: The PIRQx# signals

can be shared with interrupts IRQ[15,14,12:9,7:3] as described in the

Interrupt Steering section. Each PIRQx# line has a separate Route

Control Register. These signals require external pull-up resisters.

For the PIIX3, the USB interrupt is output on PIRQD#.

INTR od CPU INTERRUPT: INTR is driven by the PIIX/PIIX3 to signal the CPU

that an interrupt request is pending and needs to be serviced. The

interrupt controller must be programmed following PCIRST# to ensure

that INTR is at a known state.

NMI od NON-MASKABLE INTERRUPT: NMI is used to force a non-maskable

interrupt to the CPU. The PIIX/PIIX3 generates an NMI when either

SERR# or IOCHK# is asserted, depending on how the NMI Status

and Control Register is programmed.

1.8. System Power Management (SMM) Signals

Signal Name Type Description

SMI# od SYSTEM MANAGEMENT INTERRUPT: SMI# is an active low

synchronous output that is asserted by the PIIX/PIIX3 in response to one

of many enabled hardware or software events.

STPCLK# od STOP CLOCK: STPCLK# is an active low synchronous output that is

asserted by the PIIX/PIIX3 in response to one of many hardware or

software events. STPCLK# connects directly to the CPU and is

synchronous to PCICLK.

EXTSMI# I EXTERNAL SYSTEM MANAGEMENT INTERRUPT: EXTSMI# is a

falling edge triggered input to the PIIX/PIIX3 indicating that an external

device is requesting the system to enter SMM mode. This signal contains

a weak internal pullup.

E 82371FB (PIIX) AND 82371SB (PIIX3)

17

1.9. X-Bus Signals

Signal Name Type Description

XDIR# O X-BUS DIRECTION: XDIR# is tied directly to the direction control of a

74F245 that buffers the X-Bus data (XD[7:0]). XDIR# is asserted for all I/O

read cycles, regardless if the accesses are to a PIIX/PIIX3 supported

device. XDIR# is only asserted for memory cycles if BIOS sapce (PIIX and

PIIX3) or APIC space (PIIX3 only) has been decoded. For PCI master

inititated read cycles, XDIR# is asserted from the falling edge of either

IOR# or MEMR# (from MEMR# only if BIOS space (PIIX and PIIX3) or

APIC (PIIX3 only)

space has been decoded), depending on the cycle type.

For ISA master-initiated read cycles, XDIR# is asserted from the falling

edge of either IOR# or MEMR# (from MEMR# only if BIOS space has been

decoded), depending on the cycle type. When the rising edge of IOR# or

MEMR# occurs, the PIIX/PIIX3 negates XDIR#. For DMA read cycles from

the X-Bus, XDIR# is asserted from DACKx# falling and negated from

DACKx# rising. At all other times, XDIR# is negated.

XOE# O X-BUS OUTPUT ENABLE: XOE# is tied directly to the output enable of a

74F245 that buffers the X-Bus data (XD[7:0]) from the system data bus

(SD[7:0]). XOE# is asserted when a PIIX/PIIX3 supported X-Bus device is

decoded, and the devices decode is enabled in the X-Bus Chip Select

Enable Register (XBCS Register). XOE# is asserted from the falling edge

of the ISA commands (IOR#, IOW#, MEMR#, or MEMW#) for PCI Master

and ISA master-initiated cycles. XOE# is negated from the rising edge of

the ISA command signals for CPU and PCI Master-initiated cycles and the

SA[16:0] and LA[23:17] address for ISA master-initiated cycles. XOE# is

not generated during any access to an X-Bus peripheral in which its

decode space has been disabled.

DD15/ PCS# O PROGRAMMABLE CHIP SELECT: PCS# is asserted for ISA I/O cycles

that are generated by PCI masters and subtractively decoded to ISA, if the

access hits the address range programmed into the PCSC Register. The

X-Bus buffer signals are enabled when the chip select is asserted (i.e., it is

assumed that the peripheral that is selected via this pin resides on the XBus).

BIOSCS# O BIOS CHIP SELECT: BIOSCS# is asserted during read or write accesses

to BIOS. BIOSCS# is driven combinatorially from the ISA addresses

SA[16:0] and LA [23:17], except during DMA. During DMA cycles,

BIOSCS# is not generated.

KBCS# O KEYBOARD CONTROLLER CHIP SELECT: KBCS# is asserted during

I/O read or write accesses to KBC locations 60h and 64h. This signal is

driven combinatorially from the ISA addresses SA[16:0] and LA [23:17].

For DMA cycles, KBCS# is never asserted.

RTCCS# O REAL TIME CLOCK CHIP SELECT: RTCCS# is asserted during read or

write accesses to RTC location 71h. RTCCS# can be tied to a pair of

external OR gates to generate the real time clock read and write command

signals.

RTCALE O REAL TIME CLOCK ADDRESS LATCH: RTCALE is used to latch the

appropriate memory address into the RTC. A write to port 70h with the

appropriate RTC memory address that will be written to or read from,

causes RTCALE to be asserted. RTCALE is asserted based on IOW#

falling and remains asserted for two SYSCLKs.

82371FB (PIIX) AND 82371SB (PIIX3) E

18

Signal Name Type Description

FERR# I NUMERIC COPROCESSOR ERROR: This signal is tied to the

coprocessor error signal on the CPU. IGNNE# is only used if the

PIIX/PIIX3 coprocessor error reporting function is enabled in the XBCSA

Register. If FERR# is asserted, the PIIX/PIIX3 generates an internal

IRQ13 to its interrupt controller unit. The PIIX/PIIX3 then asserts the INTR

output to the CPU. FERR# is also used to gate the IGNNE# signal to

ensure that IGNNE# is not asserted to the CPU unless FERR# is active.

FERR# has a weak internal pull-up used to ensure a high level when the

coprocessor error function is disabled.

IGNNE# od IGNORE ERROR: This signal is connected to the ignore error pin on the

CPU. IGNNE# is only used if the PIIX/PIIX3 coprocessor error reporting

function is enabled in the XBCSA Register. If FERR# is asserted,

indicating a coprocessor error, a write to the Coprocessor Error Register

(F0h) causes the IGNNE# to be asserted. IGNNE# remains asserted until

FERR# is negated. If FERR# is not asserted when the Coprocessor Error

Register is written, the IGNNE# signal is not asserted.

1.10. APIC Bus Signals (PIIX3 Only)

Signal Name Type Description

DD14/

APICCS#

I/O

O

APIC CHIP SELECT (PIIX3 only). This active low output signal is

asserted when the APIC Chip Select is enabled and a PCI originated

cycle is positively decoded within the programmed IOAPIC address

space. The default addresses of the IOAPIC are Memory FEC0_0000h

and FEC0_0010h.

System Design Note: The DD[14]/APICCS# signal is demuxed externally

with a 245 transceiver. The output of the transceiver drives the IOAPIC’s

CS# signal. At certain times the transceiver floats its outputs, therefore a

pullup resistor on the output of the tranceiver is required to keep this

signal negated.

TESTIN#/

APICREQ#

I APIC REQUEST (PIIX3 only). This signal has two functions, depending

on the programming of the APIC Chip Select bit (XBCS Register). See the

Test SIgnal Description for the TESTIN# function. APICREQ# is asserted

by an external APIC device prior to sending an interrupt over the APIC

serial bus. When the PIIX3 samples this pin active it flushes its F-type

DMA buffers pointing towards PCI. Once the buffers are flushed, the

PIIX3 asserts APICACK# to inform the external APIC that it can proceed

to send the APIC interrupt. APICREQ# must be synchronous to PCICLK.

PCIRST#/

APICACK#

O

O

APIC ACKNOWLEDGE (PIIX3 only). This signal has two functions,

depending on the programming of the APIC Chip Select bit (XBCS

Register). See the System Reset Signal Description for the PCIRST#

function. The PIIX3 asserts APICACK# after its internal buffers are

flushed in response to the APICREQ# signal. When the IOAPIC samples

this signal asserted it knows that the PIIX3’s buffers are flushed and that

it can proceed to send the APIC interrupt. The signal is driven from the

rising edge of PCICLK and is negated while PCIRST# is asserted.

E 82371FB (PIIX) AND 82371SB (PIIX3)

19

1.11. Universal Serial Bus Signals (PIIX3 Only)

Signal Name Type Description

USBCLK I UNIVERSAL SERIAL BUS CLOCK. This signal clocks the universial serial

bus clock.

USBP0+

USBP0-

I/O UNIVERSAL SERIAL BUS PORT 0. These signals are the differential data

pair for Serial Port 0.

USBP1+

USBP1-

I/O UNIVERSIAL SERIAL BUS PORT 1. These signals are the differential data

pair for Serial Port 1.

1.12. System Reset Signals

Signal Name Type Description

PWROK I POWER OK: When asserted, PWROK is an indication to the PIIX/PIIX3

that power and PCICLK have been stable for at least 1 ms. PWROK can be

driven asynchronously. When PWROK is negated, the PIIX/PIIX3 asserts

CPURST, PCIRST# and RSTDRV. When PWROK is asserted, the

PIIX/PIIX3 negates CPURST, PCIRST#, and RSTDRV.

CPURST od CPU RESET: The PIIX/PIIX3 asserts CPURST to reset the CPU. The

PIIX/PIIX3 asserts CPURST during power-up and when a hard reset

sequence is initiated through the RC register. CPURST is driven

synchronously to the rising edge of PCICLK. If a hard reset is initiated

through the RC register, the PIIX/PIIX3 resets it’s internal registers to the

default state.

PCIRST#/

APICACK#

(PIIX3 Only)

O

O

PCI RESET: This signal has two functions, depending on the programming

of the APIC Chip Select bit (XBCS Register). See the APIC SIgnal

Description for the APICACK# function. The PIIX/PIIX3 asserts PCIRST# to

reset devices that reside on the PCI Bus. The PIIX/PIIX3 asserts PCIRST#

during power-up and when a hard reset sequence is initiated through the

RC register. PCIRST# is driven inactive a minimum of 1 ms after PWROK

is driven active. PCIRST# is driven active for a minimum of 1ms when

initiated through the RC register. PCIRST# is driven asynchronously

relative to PCICLK.

INIT OD INITIALIZATION: The PIIX/PIIX3 asserts INIT if it detects a shut down

special cycle on the PCI Bus or if a soft reset is initiated via the RC

Register.

RSTDRV O RESET DRIVE: The PIIX/PIIX3 asserts this signal during a hard reset and

during power-up to reset ISA Bus devices. RSTDRV is also asserted for a

minimum of 1 ms if a hard reset has been programmed in the RC Register.

82371FB (PIIX) AND 82371SB (PIIX3) E

20

1.13. Test Signals

Signal Name Type Description

TESTIN#/

APICREQ#

(PIIX3 Only)

I

I

TEST INPUT: This signal has two functions, depending on the

programming of the APIC Chip Select bit (XBCS Register). See the APIC

SIgnal Description for the APICREQ# function. The TESTIN# signal is used

in conjunction with the IRQ signals to select the various test modes of the

PIIX/PIIX3. This input contains an internal pull up resistor. After a hard

reset, this pin functions as a TESTIN# signal. An external weak pull-up

resistor (4.7k to 20k ohms) is required to 5V.

1.14. Power and Ground Signals

Signal Name Type Description

VCC Power (5 Volts): This pin is connected to the 5 volt power supply.

VCC3

(PIIX3)

Power (3.3 Volts): This pin is connected to the 3.3 volt power supply.

Note that, if the the Universal Serial Bus function is not used, this pin can

be connected to the 5 volt power supply.

GND Ground: This pin is connected to the ground plane.

E 82371FB (PIIX) AND 82371SB (PIIX3)

21

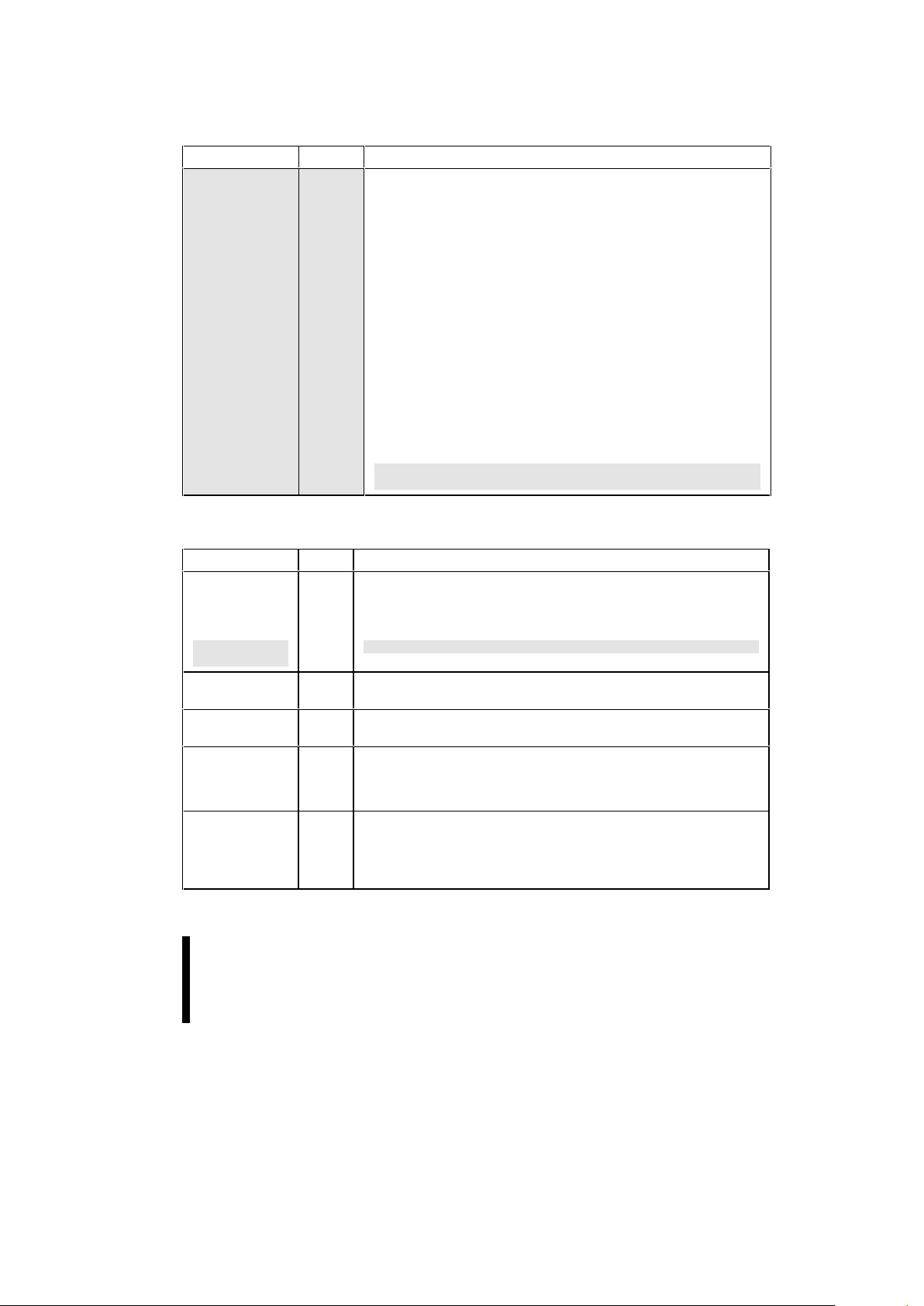

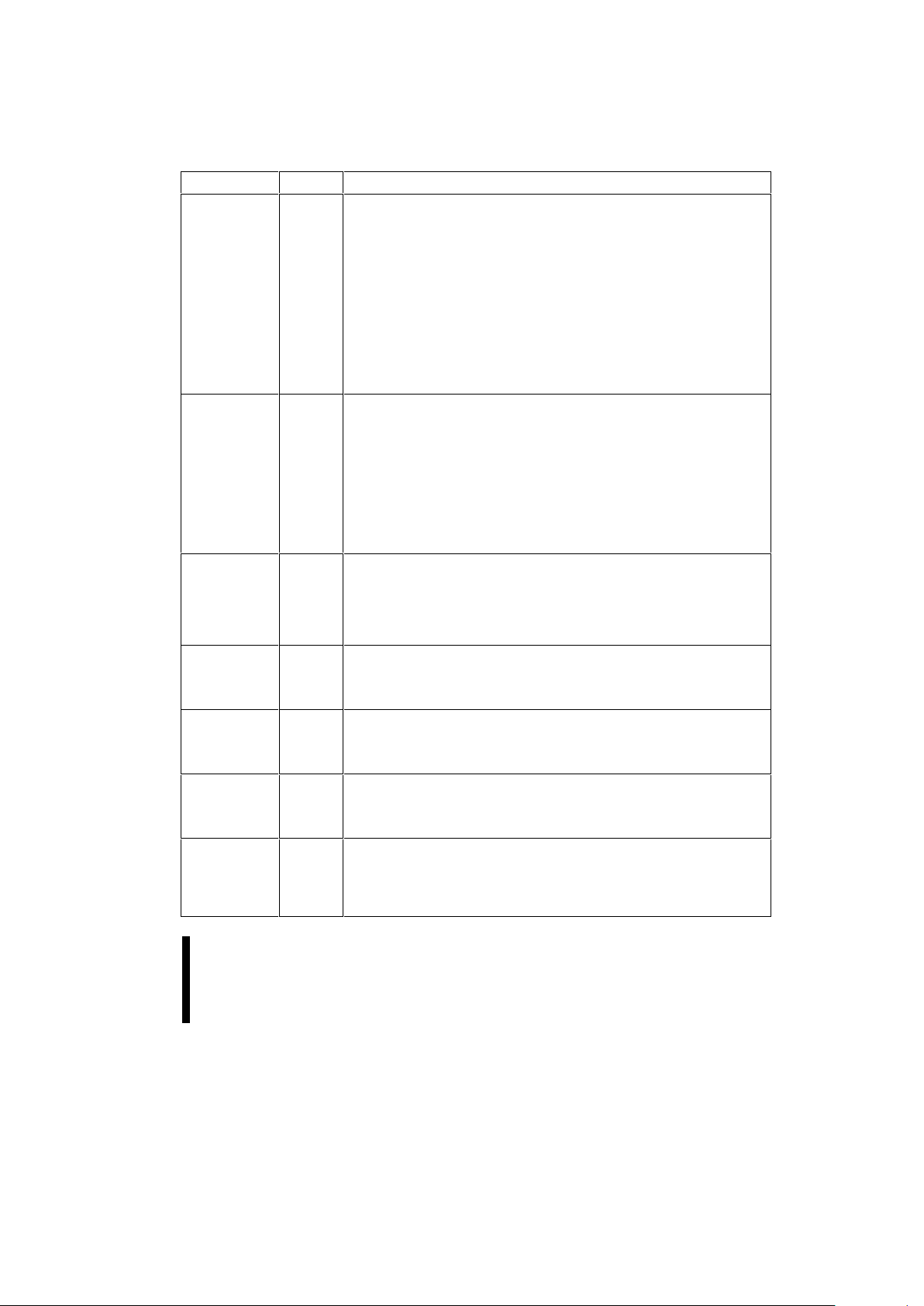

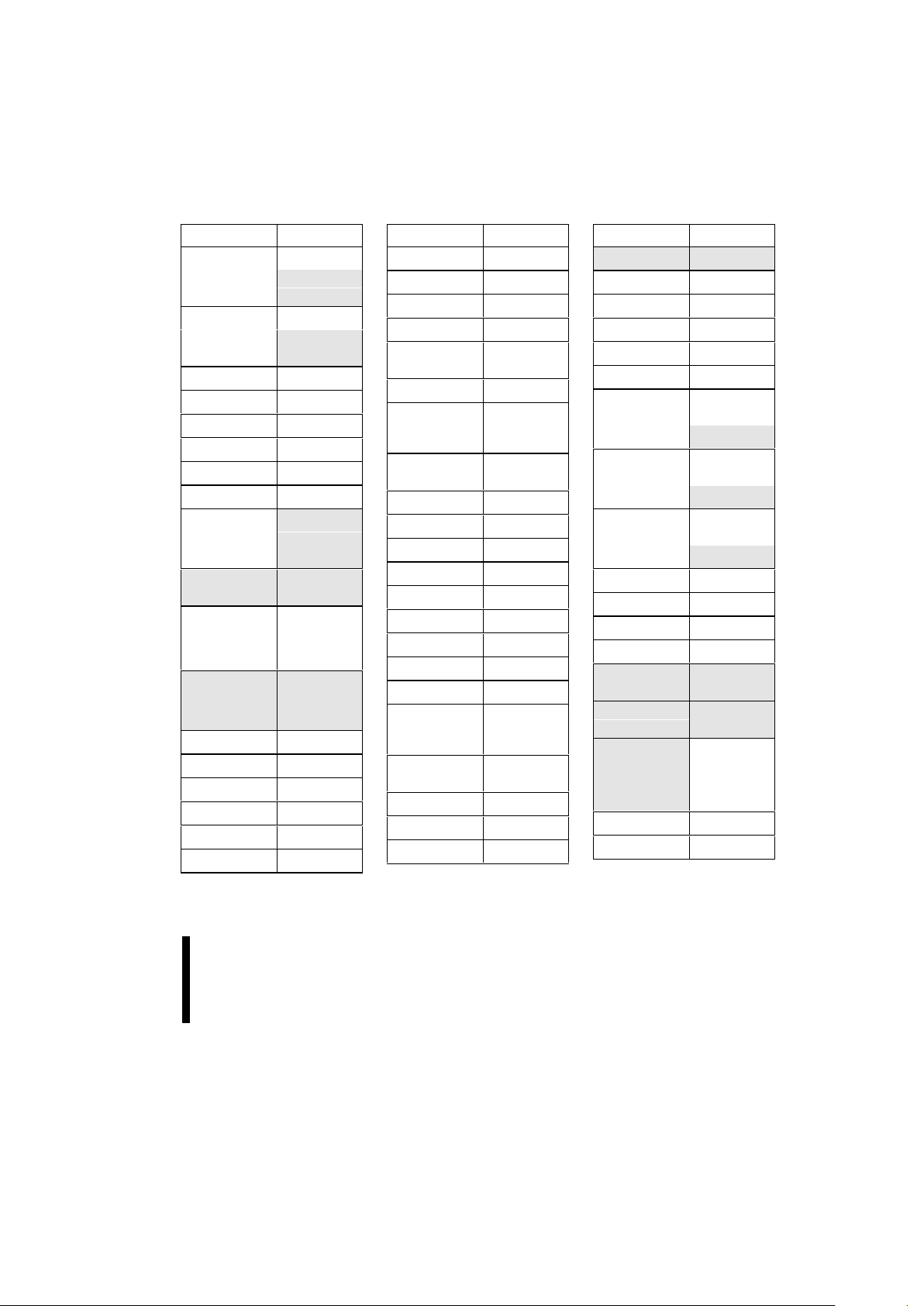

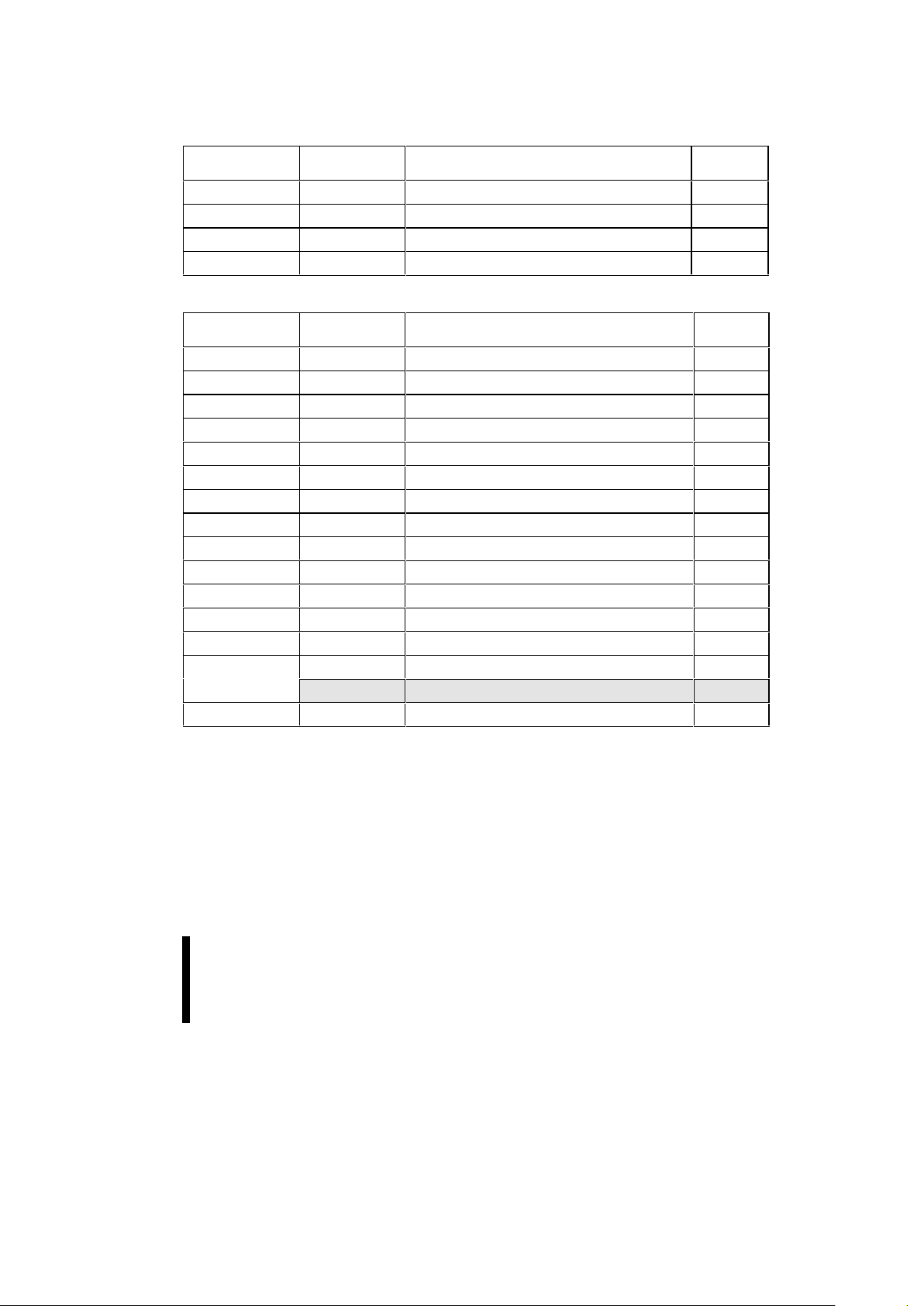

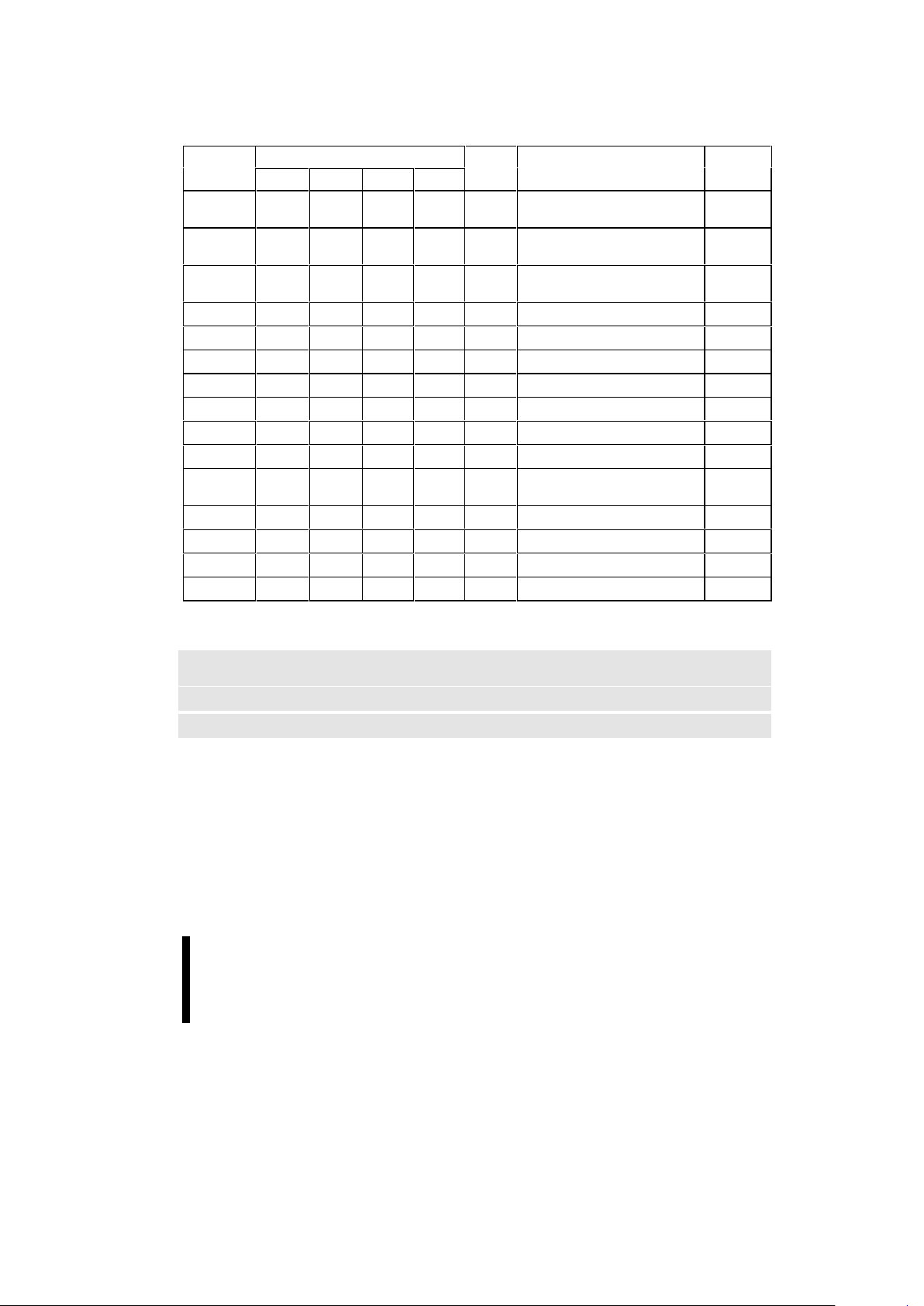

1.15. Signal State During Reset

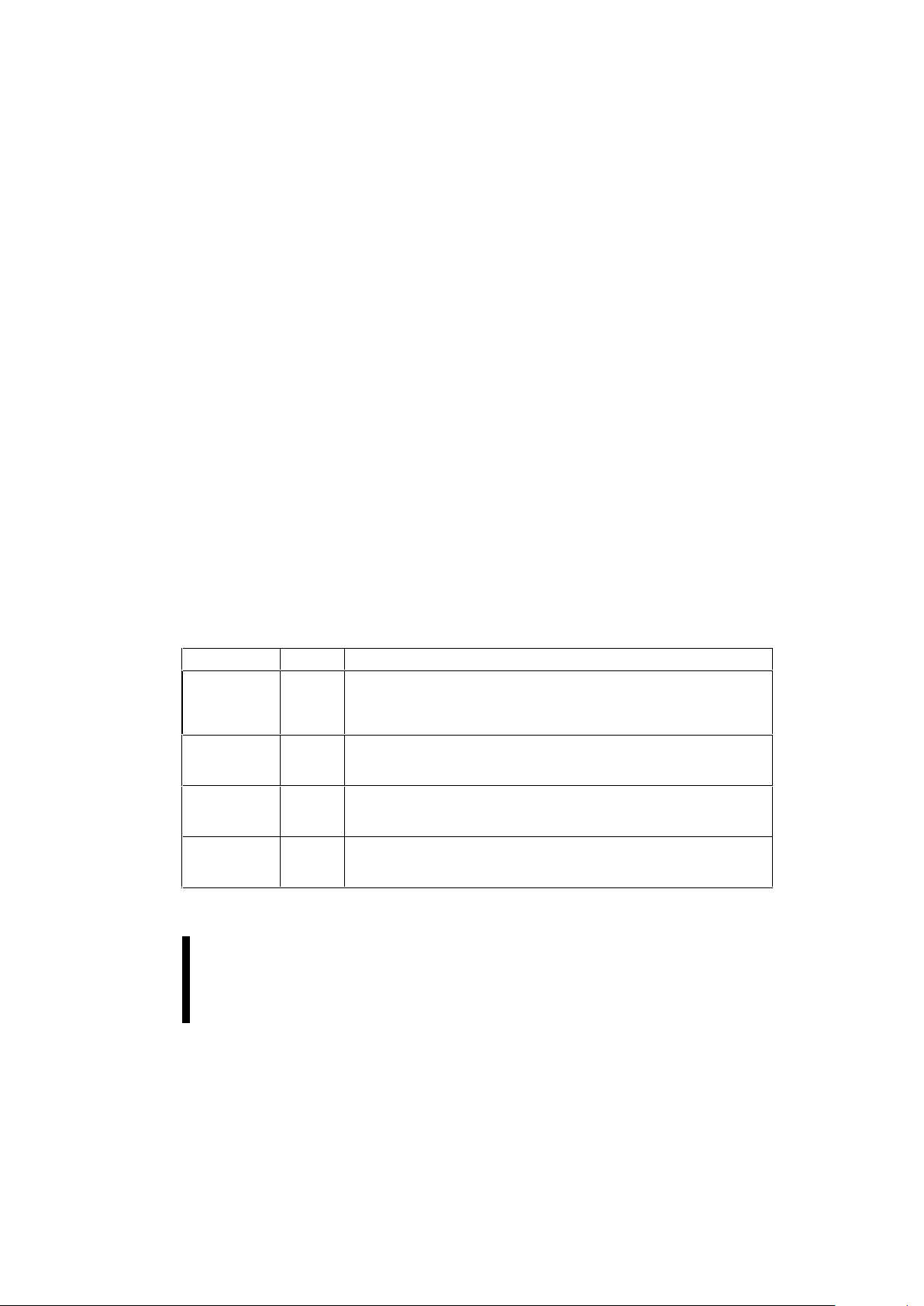

Table 1 shows the state of all PII X/PI IX3 out put and bi-direct ional si gnals during a hard res et. A hard reset is

initiated when PWROK is asserted or by programming a hard reset through the RC Register.

Table 1. Output and I/O Signal States During Hard Reset

Signal State

AD[31:0] Low (PIIX)

Tri-State

(PIIX3)

C/BE[3:0]# Low (PIIX)

Tri-State

(PIIX3)

FRAME# Tri-state

TRDY# Tri-state

IRDY# Tri-state

STOP# Tri-state

DEVSEL# Tri-state

PAR Input

PHOLD# High (PIIX)

Tri-state

(PIIX3)

MDAK[1:0]#

(PIIX)

High

DD[15,13:0]/

PCS#,SBHE#,

SA[19:8],

DD14 (PIIX)

Tri-state

DD14 (PIIX)

DD14/APICCS#

(PIIX3)

Tri-state

High

SA[7:0] Undefined

DIOR# High

DIOW# High

DDAK[1:0]# High

SOE# High

SDIR High

Signal State

LA23/CS1S Undefined

LA22/CS3S Undefined

LA21/CS1P Undefined

LA20/CS3P Undefined

LA[19:17]/

DA[2:0]

Undefined

BALE Low

AEN Depends on

strapping

option

SYSCLK Strapping

Option

IOCHRDY Tri-state

IOR# High

IOW# High

MEMCS16# Open drain

MEMR# Tri-state

MEMW# Tri-state

SMEMR# High

SMEMW# High

SD[15:0] Tri-state

DACK[7:5,3:0]# Depends on

strapping

option

TC Strapping

Option

REFRESH# Tri-state

SPKR Low

INTR Open drain

Signal State

PIRQD# (PIIX3) Tri-state

NMI Open drain

SMI# Open drain

STPCLK# Open drain

XDIR# High

XOE# High

BIOSCS# Undefined

(PIIX)

High (PIIX3)

KBCS# Undefined

(PIIX)

High (PIIX3)

RTCCS# Undefined

(PIIX)

High (PIIX3)

RTCALE Low

FERR# Open drain

IGNNE# Open drain

CPURST Open drain

USBP0+

USBP0-

Tri-state

USBP1+

USBP1-

Tri-state

PCIRST# (PIIX)

PCIRST#/

APICACK#

(PIIX3)

Low

INIT Low

RSTDRV High

82371FB (PIIX) AND 82371SB (PIIX3) E

22

2.0. REGISTER DESCRIPTION

The 82371FB PIIX internal regis ters are organized i nto f ive groups —P CI Conf igurati on Regist ers (f unct ion 0),

PCI Configuration Registers (function 1), ISA-Compatible Registers, PCI Bus Master IDE Registers, and

System Power Management Registers. These registers are discussed in this section.

The PIIX3 internal registers contain the same register sets as t he PI IX plus t wo addit ional regis ter s ets for t he

Universal Serial Bus (USB) function—PCI Configuration Registers (function 2) and the USB I/O Registers.

Some of the PIIX/PIIX3 registers contain reserved bits. Software must deal correctly with fields that are

reserved. On reads, software must use appropriat e masks to extract the defined bits and not rely on reserved

bits being any particular value. On writes , software must ensure that the values of reserved bit pos itions are

preserved. That is, the values of reserved bit pos itions must first be read, merged wi th the new values for

other bit positions and then written back.

In addition to reserved bits within a register, the PIIX/PIIX3 contains address locations in the PCI

configuration space that are marked "Reserved". The PIIX/PIIX3 responds to accesses to these address

locations by completing the host cycle. Software should not write to reserved PIIX/PIIX3 configuration

locations in the device-specific region (above address offset 3Fh).

During a hard reset, the PIIX/ PIIX3 sets its internal regis ters to predetermined default states. The default

values are indicated in the individual register descriptions.

The following notation is used to describe register access attributes:

RO Read Only. If a register is read only, writes have no effect.

WO Write Only. If a register is write only, reads have no effect.

R/W Read/Write. A register with this attribute can be read and written. Note that indivi dual bits in som e

read/write registers may be read only.

R/WC Read/Write Clear. A register bi t with t his att ribute can be read and wri tten. However, a writ e of a 1

clears (sets to 0) the corresponding bit and a write of a 0 has no effect.

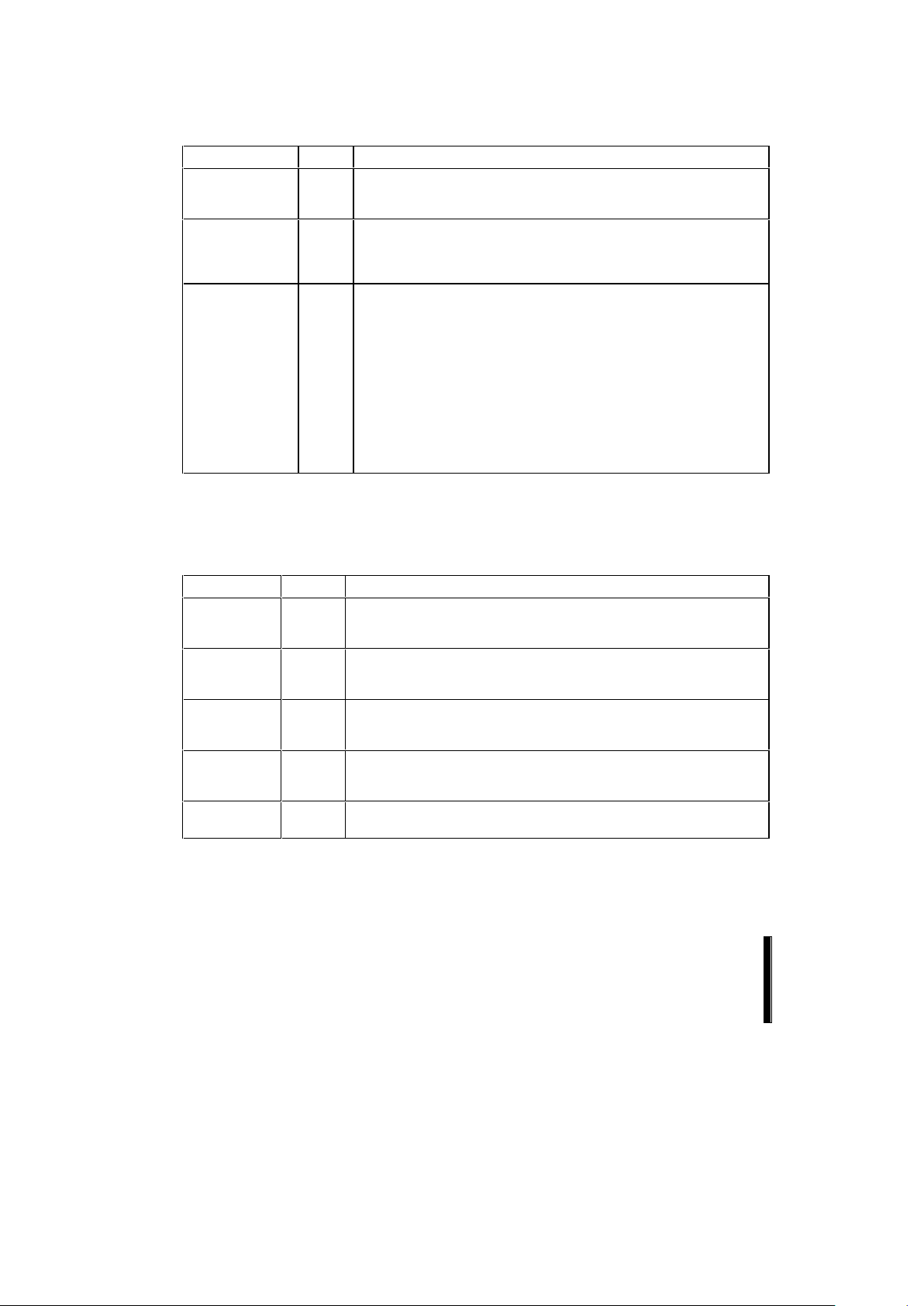

2.1. Register Access

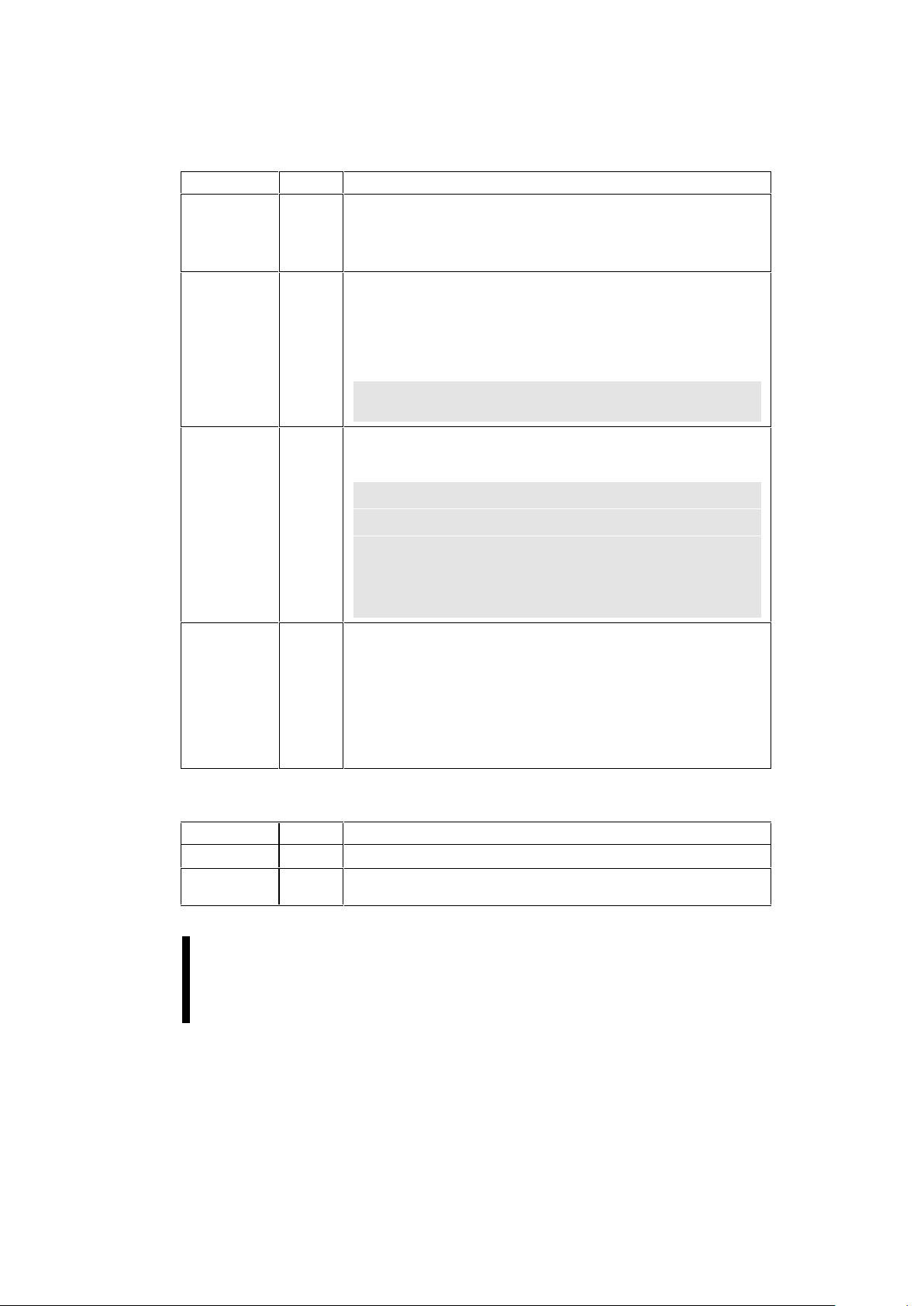

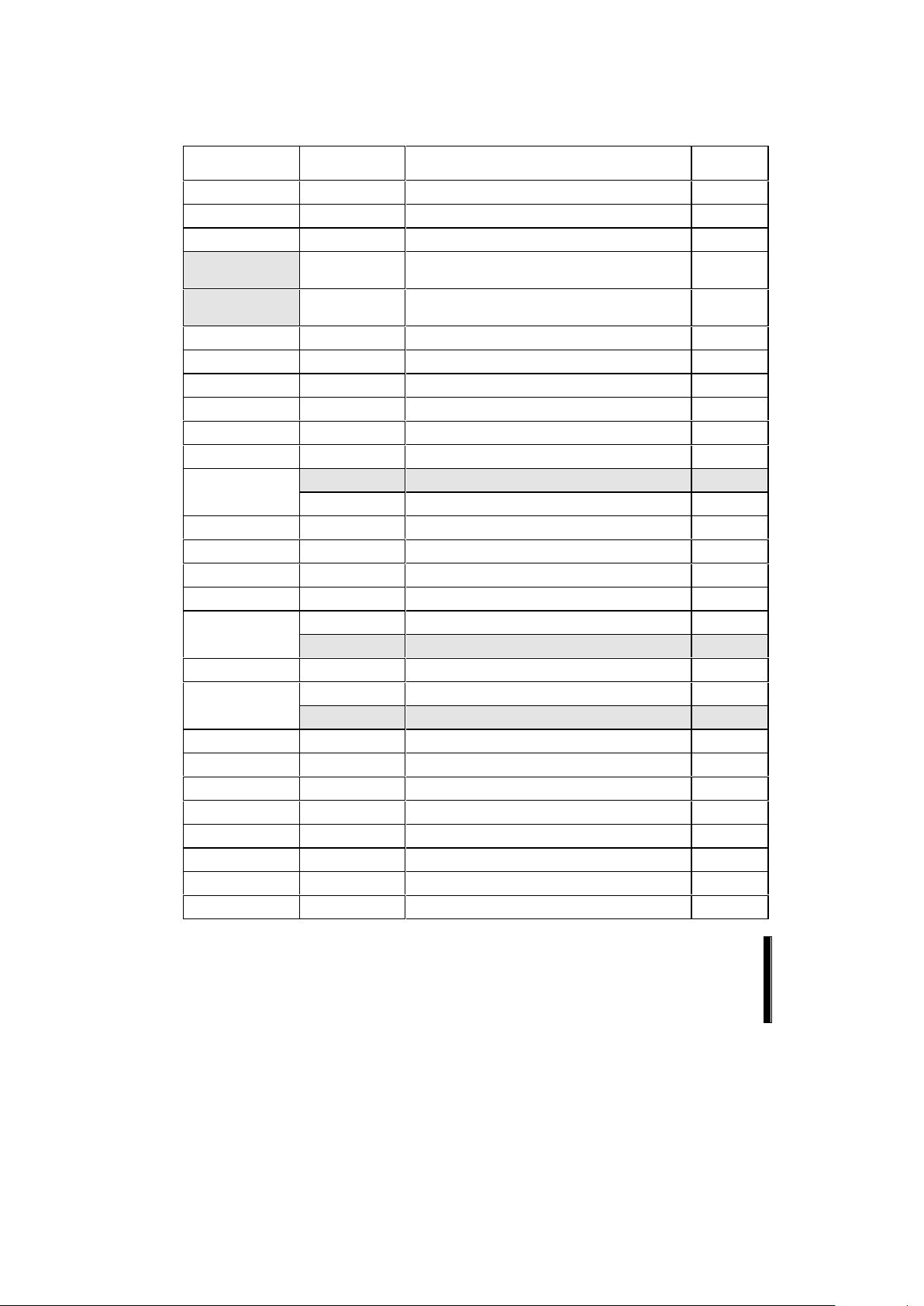

Table 2, Table 3, and Table 4 show the I/O assignments for the PCI Configuration Registers (function 0, 1,

and 2). Table 5 shows the I/O assignments for the ISA Compatible Registers. Table 6 shows the I/O

assignments for the Bus Master IDE Interface regi sters. Tabl e 7 shows the I /O ass ignments for the USB I/ O

registers. PCI masters have acc ess to all PIIX/P IIX3 int ernal registers. In addition, I SA mast ers have acces s

to some of the ISA-Compatible registers (see Table 5).

PCI Configuration Registers (functions 0, 1, and 2)

The 82371FB PIIX is a mult i-function dev ice on the PCI B us implement ing two f unctions—P CI-to-ISA Bridge

(function 0) and IDE Interface (function 1). Thes e functions can be independently c onfigured with t wo sets of

PCI configuration regist ers in com pliance wit h the PCI Loc al Bus S pecif ication, Revis ion 2.0. The two sets of

configuration registers are accessed by the CPU through a mechanism defined for multi-functional PCI

devices. The PIIX does not assert DEVSEL# for PCI configuration cycles that target functions 2 through 7.

The PIIX3 implements an addi tional PCI bus functionUniv ersial Serial Bus Interfac e. The PIIX3 does not

assert DEVSEL# for PCI configuration cycles that target functions 3 through 7.

E 82371FB (PIIX) AND 82371SB (PIIX3)

23

ISA Compatible Registers

The ISA-Compatible registers (e.g., DMA registers, timer/counter registers, X-Bus registers, and NMI

registers) are accessed through normal I/ O space. Except for the DMA regist ers, the PIIX/PIIX3 posi tively

decodes accesses t o the ISA -Compatible regi sters . The PII X/PI IX3 s ubtracti vely dec odes acc esses to al l I/ O

space registers contained within the ISA-Compatible DMA function. This permits another device in the

system to implement the compatible DMA function.

PCI master access es to the ISA-Compati ble registers can be 8, 16, 24, or 32 bits. However, the PIIX/P IIX3

only responds to the least significant byt e. On writes the other bytes are not loaded and on reads the other

bytes have invalid data. The PIIX/PII X3 responds as an 8-bit ISA I/ O sl ave when ac ces sed by an IS A m ast er.

See the PCI Local Bus IDE section for accesses to the IDE register blocks located in the IDE device

In general, accesses from CPU or PCI masters to t he internal PIIX/PI IX3 registers are not broadcast to the

ISA Bus. Exc eptions to t his are read/writ e acc es ses to 70h and F0h and writ e acc ess es t o 80h, 84 –86h, 88h,

8C–8Eh, 90h, 94–96h, 98h, and 9C–9Eh. These accesses are broadcast to the I SA Bus . Not e that al ias ing of

the 90–9Fh to 80–8Fh can be enabled/disabled via the ISA Controller Recovery Timer Register.

Power Management Registers

There are two power management registers loc ated in normal I/ O space. Thes e regist ers are ac cessed (by

PCI Bus masters) with 8-bit accesses. The other power management registers are located in PCI

configuration space for function 0.

PCI Bus Master IDE Registers

The PCI Bus master IDE function uses 16 bytes located in normal I/O space, allocated via the BMIBA

register (a PCI base address regis ter). All bus m aster IDE I/O s pace registers c an be accessed as 8, 16, or

32-bit quantities.

Universal Serial Bus Registers

A set of USB registers provide control and status information for the Host Controller and two USB ports

(Table 7). This block of regis ters is I/O mapped into PCI I/O s pace and control variouos operations of the

USB Host Controller. The registers are relocateable via the USBBASE Register which is located in function 0

PCI configuration space.

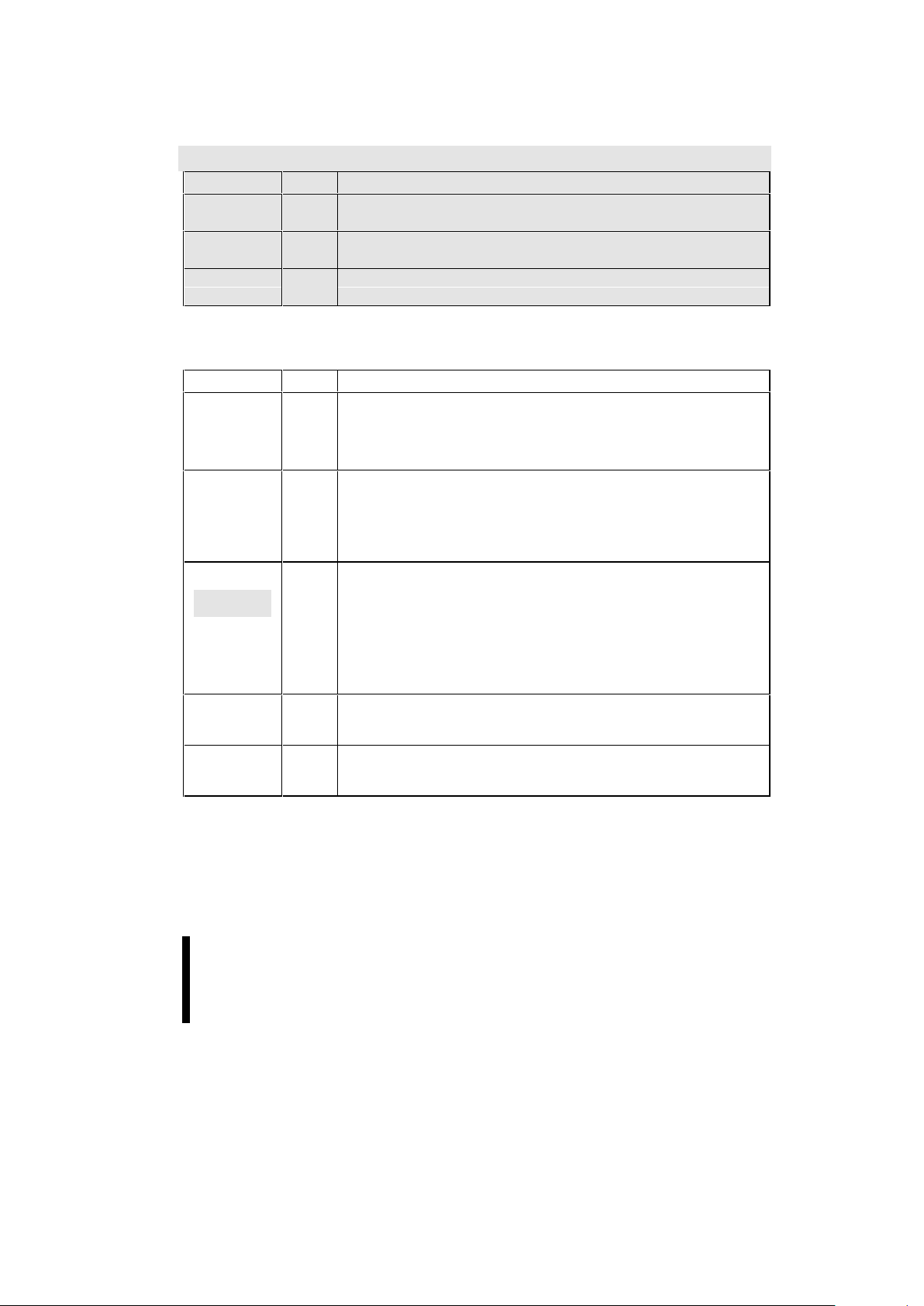

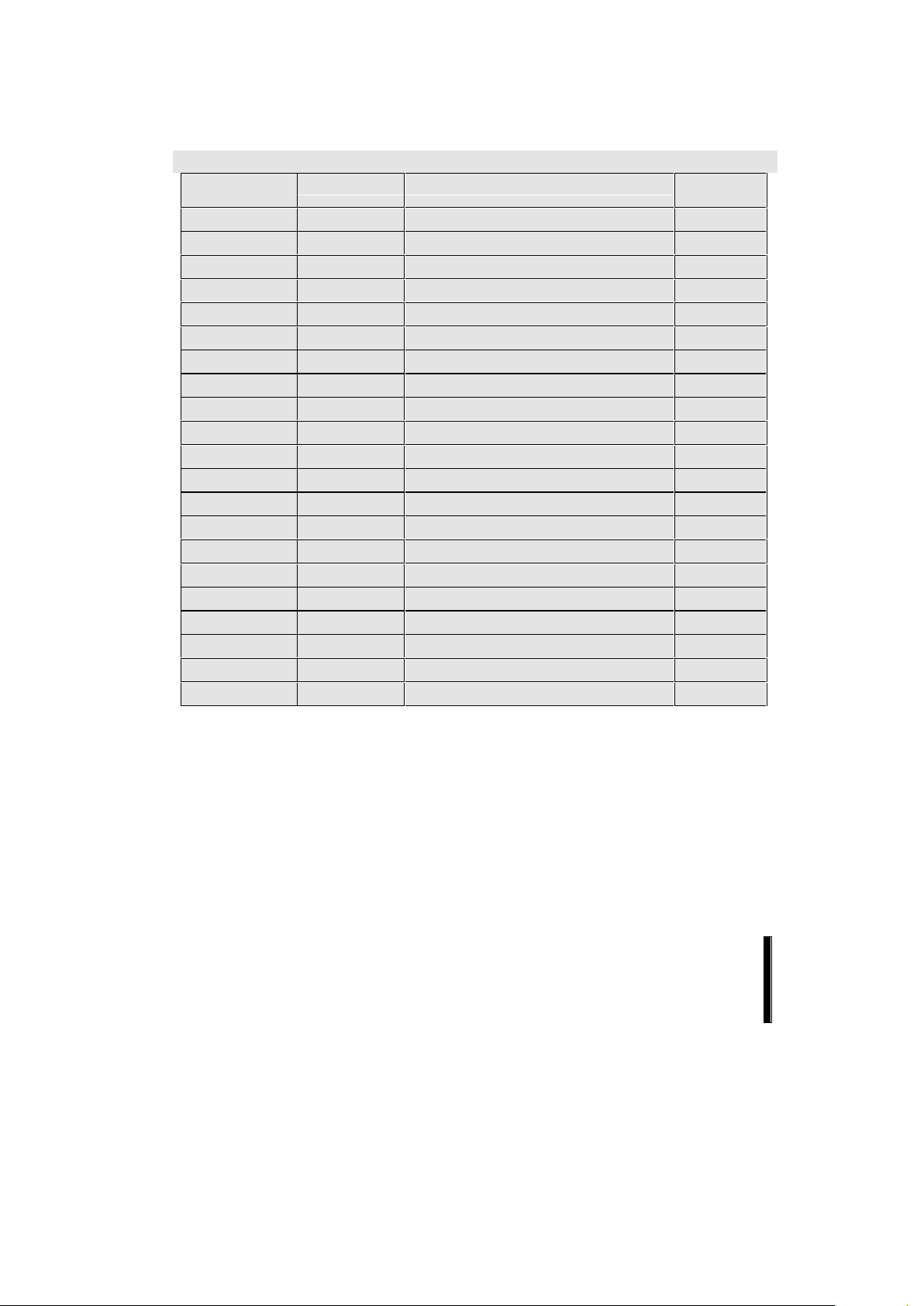

Table 2. PCI Configuration Registers—Function 0 (PCI to ISA Bridge)

Configuration

Offset

Mnemonic Register Register

Access

00–01h VID Vendor Identification RO

02–03h DID Device Identification RO

04–05h PCICMD PCI Command R/W

06–07h PCISTS PCI Device Status R/WC

08h RID Revision Identification RO

09−0Bh CLASSC Class Code RO

0C–0Dh — Reserved —

0Eh HEDT Header Type RO

82371FB (PIIX) AND 82371SB (PIIX3) E

24

Configuration

Offset

Mnemonic Register Register

Access

0F–4Bh — Reserved —

4Ch IORT ISA I/O Controller Recovery Timer R/W

4Dh — Reserved —

4Eh (PIIX)

4E–4Fh (PIIX3)

XBCS X-Bus Chip Select Enable R/W

4F–5Fh (PIIX)

50–5Fh (PIIX3)

— Reserved —

60–63h PIRQRC[A:D] PCI IRQ Route Control R/W

64–68h — Reserved —

69h TOM Top of Memory R/W

6A–6Bh MSTAT Miscellaneous Status R/W

6C–6Fh — Reserved —

70h MBIRQ0 Motherboard IRQ Route Control 0 R/W

71h MBIRQ1 Motherboard IRQ Route Control 1 (PIIX) R/W

— Reserved (PIIX3) —

72–75h — Reserved —

76–77h MBDMA[1:0] Motherboard DMA Control R/W

78–79h PCSC Programmable Chip Select Control R/W

7A–7Fh — Reserved —

80h — Reserved (PIIX) —

APICBASE APIC Base Address Relocation (PIIX3) R/W

81h — Reserved —

82h — Reserved (PIIX) —

DLC Deterministic Latency Control (PIIX3) R/W

83–9Fh — Reserved —

A0h SMICNTL SMI Control R/W

A1h — Reserved —

A2–A3h SMIEN SMI Enable R/W

A4–A7h SEE System Event Enable R/W

A8h FTMR Fast Off Timer R/W

A9h — Reserved —

AA–ABh SMIREQ SMI Request R/W

E 82371FB (PIIX) AND 82371SB (PIIX3)

25

Configuration

Offset

Mnemonic Register Register

Access

ACh CTLTMR Clock Scale STPCLK# Low Timer R/W

ADh — Reserved —

AEh CTHTMR Clock Scale STPCLK# High Timer R/W

AF–FFh — Reserved —

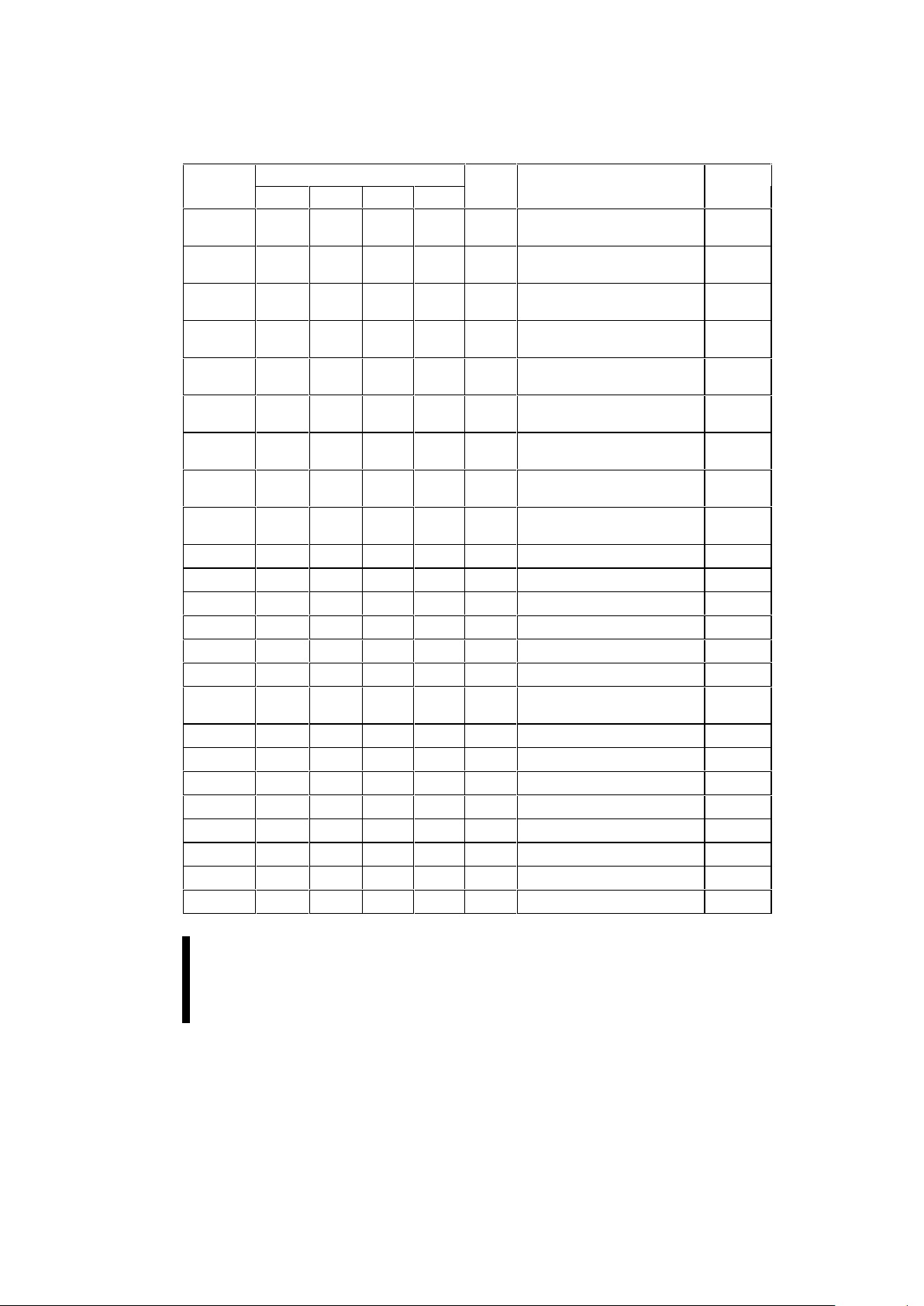

Table 3. PCI Configuration Registers—Function 1 (IDE Interface)

Configuration

Offset

Mnemonic Register Register

Access

00–01h VID Vendor Identification RO

02–03h DID Device Identification RO

04–05h PCICMD Command R/W

06–07h PCISTS PCI Device Status R/WC

08h RID Revision Identification RO

09−0Bh CLASSC Class Code RO

0Ch — Reserved —

0Dh MLT Master Latency Timer R/W

0Eh HEDT Header Type RO

0F–1Fh — Reserved —

20–23h BMIBA Bus Master Interface Base Address R/W

24–3Fh — Reserved —

40–43h IDETIM IDE Timing Modes R/W

44h — Reserved (PIIX) —

SIDETIM Slave IDE Timing Modes (PIIX3) R/W

45–FFh — Reserved —

82371FB (PIIX) AND 82371SB (PIIX3) E

26

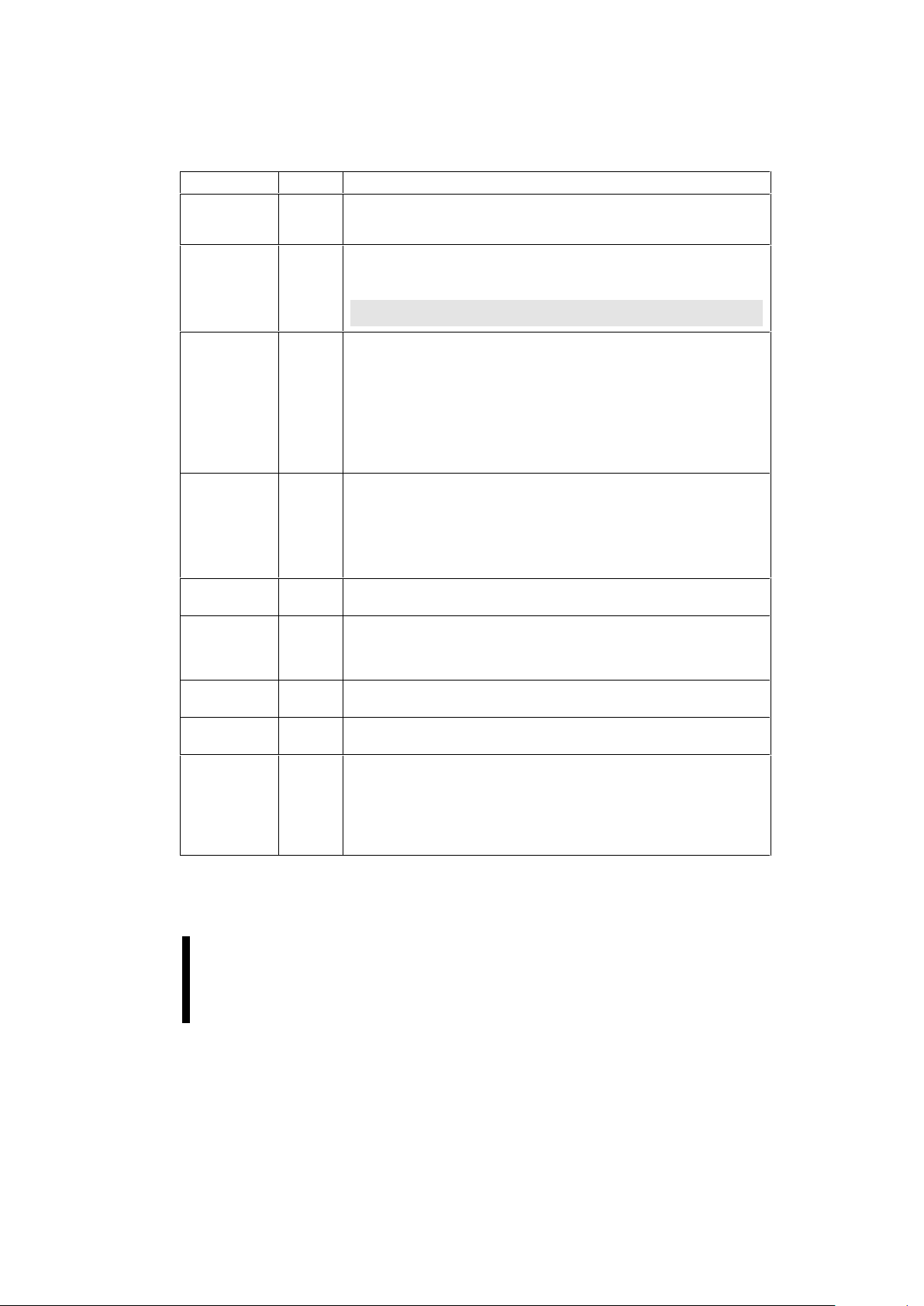

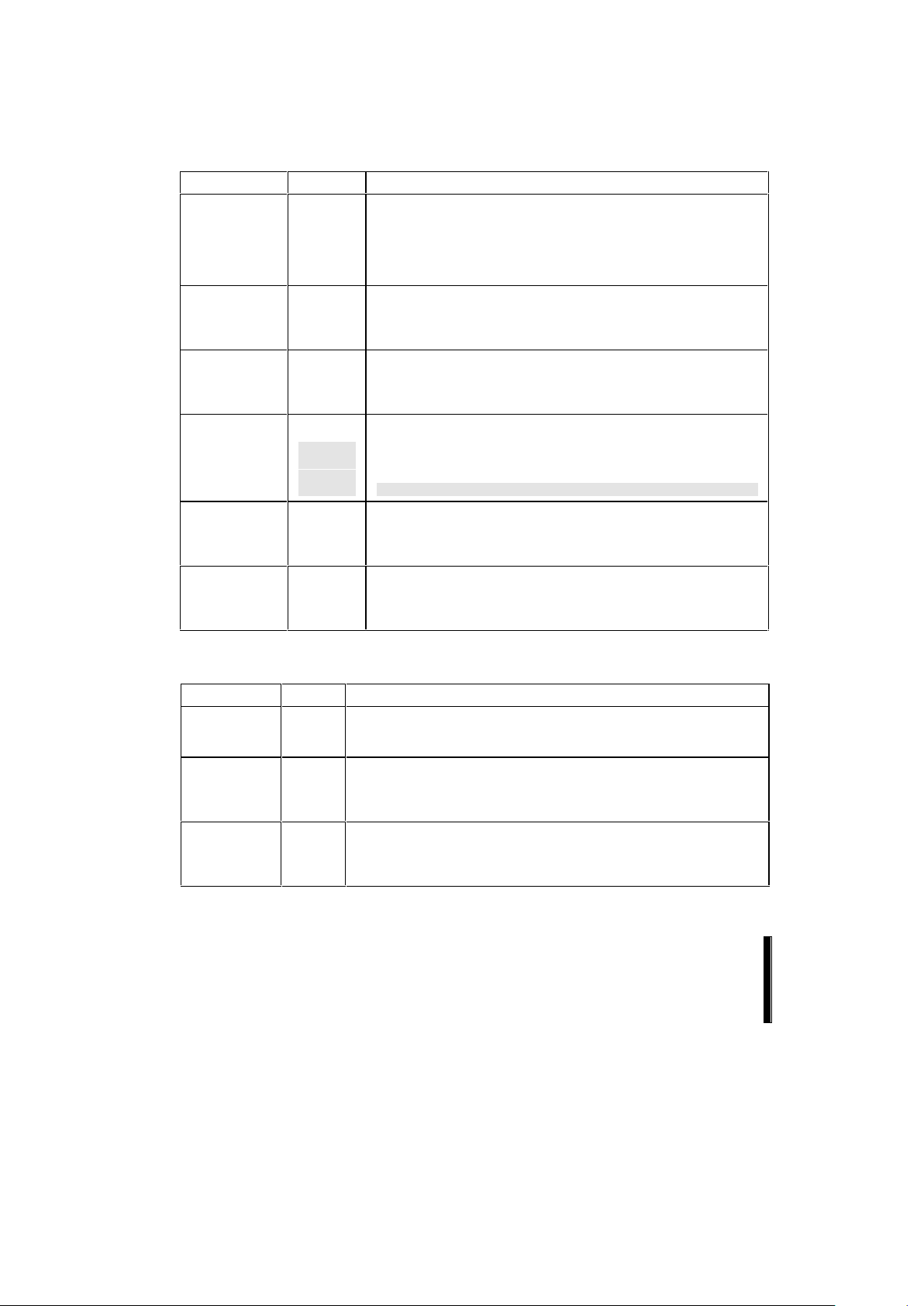

Table 4. PCI Configuration Registers—Function 2 (Universial Serial Bus Interface) (PIIX3 Only)

Configuration

Offset

Mnemonic Register Register

Access

00–01h VID Vendor Identification RO

02–03h DID Device Identification RO

04–05h PCICMD Command R/W

06–07h PCISTS Device Status R/WC

08h RID Revision Identification RO

09−0Bh CLASSC Class Code RO

0Ch — Reserved —

0Dh LATTMR Latency Timer R/W

0Eh HEDT Header Type RO

0F–19h — Reserved —

20–23h BASEADD IO Space Base Address R/W

24–3Bh — Reserved —

3Ch IL Interrupt Line R/W

3Dh INTRP Interrupt Pin RO

3E–5Fh — Reserved. —

60h SBRNUM Serial Bus Release Number RO

61–69h — Reserved —

6A–6Bh MSTAT Miscellaneous Status R/W

6C–BFh — Reserved —

C0–C1h LEGSUP Legacy Support R/WC

C2–FFh — Reserved —

E 82371FB (PIIX) AND 82371SB (PIIX3)

27

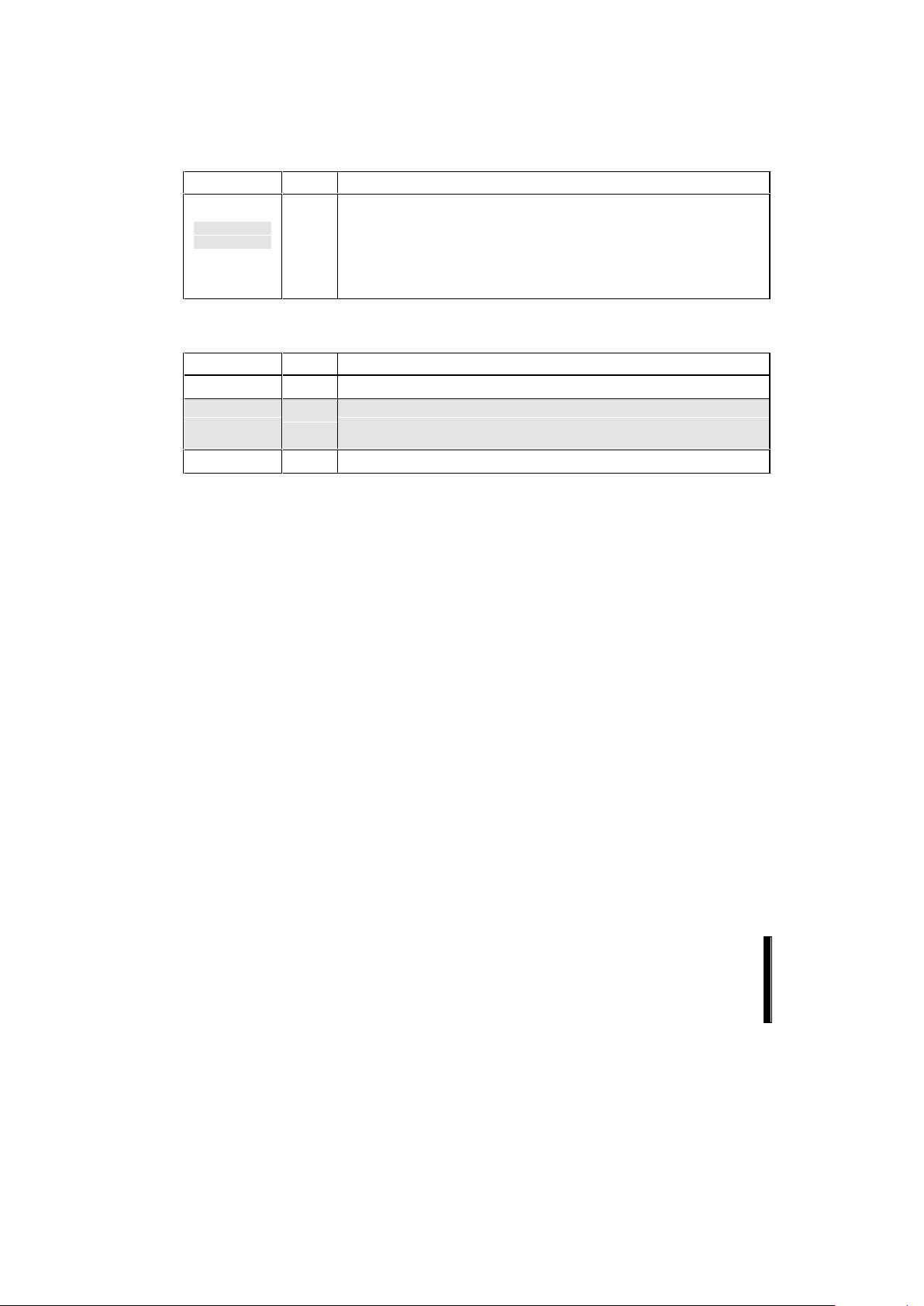

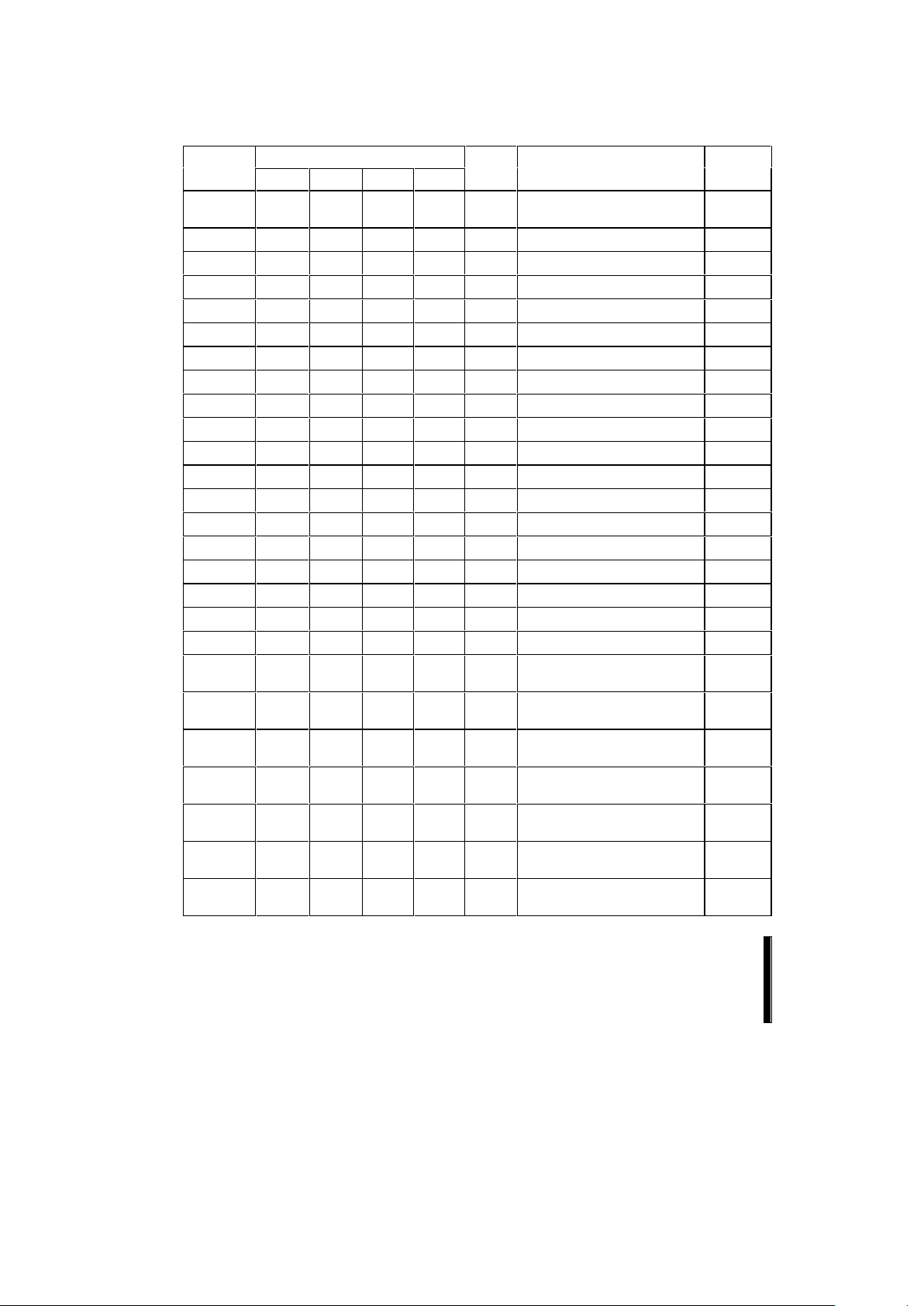

Table 5. ISA-Compatible and Power Management Registers

Address Address (bits) Type Name Access

(hex) FEDC BA98 7654 3210

0000h

3

0000 0000 000x 0000 r/w DMA1 CH0 Base and Current

Address

PCI

0001h

3

0000 0000 000x 0001 r/w DMA1 CH0 Base and Current

Count

PCI

0002h

3

0000 0000 000x 0010 r/w DMA1 CH1 Base and Current

Address

PCI

0003h

3

0000 0000 000x 0011 r/w DMA1 CH1 Base and Current

Count

PCI

0004h

3

0000 0000 000x 0100 r/w DMA1 CH2 Base and Current

Address

PCI

0005h

3

0000 0000 000x 0101 r/w DMA1 CH2 Base and Current

Count

PCI

0006h

3

0000 0000 000x 0110 r/w DMA1 CH3 Base and Current

Address

PCI

0007h

3

0000 0000 000x 0111 r/w DMA1 CH3 Base and Current

Count

PCI

0008h

3

0000 0000 000x 1000 r/w DMA1 Status(r) Command(w)

Register

PCI

0009h

3

0000 0000 000x 1001 wo DMA1 Write Request PCI

000Ah

3

0000 0000 000x 1010 wo DMA1 Write Single Mask Bit PCI

000Bh

3

0000 0000 000x 1011 wo DMA1 Write Mode PCI

000Ch

3

0000 0000 000x 1100 wo DMA1 Clear Byte Pointer PCI

000Dh

3

0000 0000 000x 1101 wo DMA1 Master Clear PCI

000Eh

3

0000 0000 000x 1110 wo DMA1 Clear Mask PCI

000Fh

3

0000 0000 000x 1111 r/w DMA1 Read/Write All Mask

Register Bits

PCI

0020h 0000 0000 001x xx00 r/w INT 1 Control PCI/ISA

0021h 0000 0000 001x xx01 r/w INT 1 Mask PCI/ISA

0040h 0000 0000 010x 0000 r/w Timer Counter 1 - Counter 0 Count PCI/ISA

0041h 0000 0000 010x 0001 r/w Timer Counter 1 - Counter 1 Count PCI/ISA

0042h 0000 0000 010x 0010 r/w Timer Counter 1 - Counter 2 Count PCI/ISA

0043h 0000 0000 010x 0011 wo Timer Counter 1 Command Mode PCI/ISA

0060h

1

0000 0000 0110 0000 r Reset XBus IRQ12/M and IRQ1 PCI/ISA

0061h 0000 0000 0110 0001 r/w NMI Status and Control PCI/ISA

82371FB (PIIX) AND 82371SB (PIIX3) E

28

Address Address (bits) Type Name Access

(hex) FEDC BA98 7654 3210

0070h

1

0000 0000 0111 0xx0 wo CMOS RAM Address and NMI

Mask Reg

PCI/ISA

0080h

2,3

0000 0000 100x 0000 r/w DMA Page (Reserved) PCI/ISA

0081h

3

0000 0000 100x 0001 r/w DMA Channel 2 Page PCI/ISA

0082h

3

0000 0000 1000 0010 r/w DMA Channel 3 Page PCI/ISA

0083h

3

0000 0000 100x 0011 r/w DMA Channel 1 Page PCI/ISA

0084h

2,3

0000 0000 100x 0100 r/w DMA Page (Reserved) PCI/ISA

0085h

2,3

0000 0000 100x 0101 r/w DMA Page (Reserved) PCI/ISA

0086h

2,3

0000 0000 100x 0110 r/w DMA Page (Reserved) PCI/ISA

0087h

3

0000 0000 100x 0111 r/w DMA Channel 0 Page PCI/ISA

0088h

2,3

0000 0000 100x 0100 r/w DMA Page (Reserved) PCI/ISA

0089h

3

0000 0000 100x 1001 r/w DMA Channel 6 Page PCI/ISA

008Ah

3

0000 0000 100x 1010 r/w DMA Channel 7 Page PCI/ISA

008Bh

3

0000 0000 100x 1011 r/w DMA Channel 5 Page PCI/ISA

008Ch

2,3

0000 0000 100x 1100 r/w DMA Page (Reserved) PCI/ISA

008Dh

2,3

0000 0000 100x 1101 r/w DMA Page (Reserved) PCI/ISA

008Eh

2,3

0000 0000 100x 1110 r/w DMA Page (Reserved) PCI/ISA

008Fh

3

0000 0000 100x 1111 r/w DMA low page Register Refresh PCI/ISA

00A0h 0000 0000 101x xx00 r/w INT 2 Control PCI/ISA

00A1h 0000 0000 101x xx01 r/w INT 2 Mask PCI/ISA

00B2h 0000 0000 1011 0010 r/w Advanced Power Management

Control

PCI

00B3h 0000 0000 1011 0011 r/w Advanced Power Management

Status

PCI

00C0h

3

0000 0000 1100 000x r/w DMA2 CH0 Base and Current

Address

PCI

00C2h

3

0000 0000 1100 001x r/w DMA2 CH0 Base and Current

Count

PCI

00C4h

3

0000 0000 1100 010x r/w DMA2 CH1 Base and Current

Address

PCI

00C6h

3

0000 0000 1100 011x r/w DMA2 CH1 Base and Current

Count

PCI

00C8h

3

0000 0000 1100 100x r/w DMA2 CH2 Base and Current

Address

PCI

E 82371FB (PIIX) AND 82371SB (PIIX3)

29