*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

December 1995COPYRIGHT©INTEL CORPORATION, 1996 Order Number: 290486-003

82091AA

ADVANCED INTEGRATED PERIPHERAL (AIP)

Y

Single-Chip PC Compatible I/O Solution

for Notebook and Desktop Platforms:

Ð 82078 Floppy Disk Controller Core

Ð Two 16550 Compatible UARTs

Ð One Multi-Function Parallel Port

Ð IDE Interface

Ð Integrated Back Power Protection

Ð Integrated Game Port Chip Select

Ð 5V or 3.3V Supply Operation with 5V

Tolerant Drive Interface

Ð Full Power Management Support

Ð Supports Type F DMA Transfers for

Faster I/O Performance

Ð No Wait-State Host I/O Interface

Ð Programmable Interrupt Interfaces

Ð Single Crystal/Oscillator Clock

(24 MHz)

Ð Software Detectable Device ID

Ð Comprehensive Powerup

Configuration

Y

The 82091AA is 100 Percent

Compatible with EISA, ISA and AT

Y

Host Interface Features

Ð 8-Bit Zero Wait-State ISA Bus

Interface

Ð DMA with Type F Transfers

Ð Five Programmable ISA Interrupt

Lines

Ð Internal Address Decoder

Y

Parallel Port Features

Ð All IEEE Standard 1284 Protocols

Supported (Compatibility, Nibble,

Byte, EPP, and ECP)

Ð Peak Bi-Directional Transfer Rate of

2 MB/sec

Ð Provides Interface for Low-Cost

Engineless Laser Printer

Ð 16-Byte FIFO for ECP

Ð Interface Backpower Protection

Y

Floppy Disk Controller Features

Ð 100 Percent Software Compatible

with Industry Standard 82077SL and

82078

Ð Integrated Analog Data Separator

250K, 300K, 500K, and 1 MBits/sec

Ð Programmable Powerdown

Command

Ð Auto Powerdown and Wakeup

Modes

Ð Integrated Tape Drive Support

Ð Perpendicular Recording Support for

4 MB Drives

Ð Programmable Write Pre-

Compensation Delays

Ð 256 Track Direct Address, Unlimited

Track Support

Ð 16-Byte FIFO

Ð Supports 2 or 4 Drives

Y

16550 Compatible UART Features

Ð Two Independent Serial Ports

Ð Software Compatible with 8250 and

16450 UARTs

Ð 16-Byte FIFO per Serial Port

Ð Two UART Clock Sources, Supports

MIDI Baud Rate

Y

IDE Interface Features

Ð Generates Chip Selects for IDE

Drives

Ð Integrated Buffer Control Logic

Ð Dual IDE Interface Support

Y

Power Management Features

Ð Transparent to Operating Systems

and Applications Programs

Ð Independent Power Control for Each

Integrated Device

Y

100-Pin QFP Package

(See Packaging Spec. 240800)

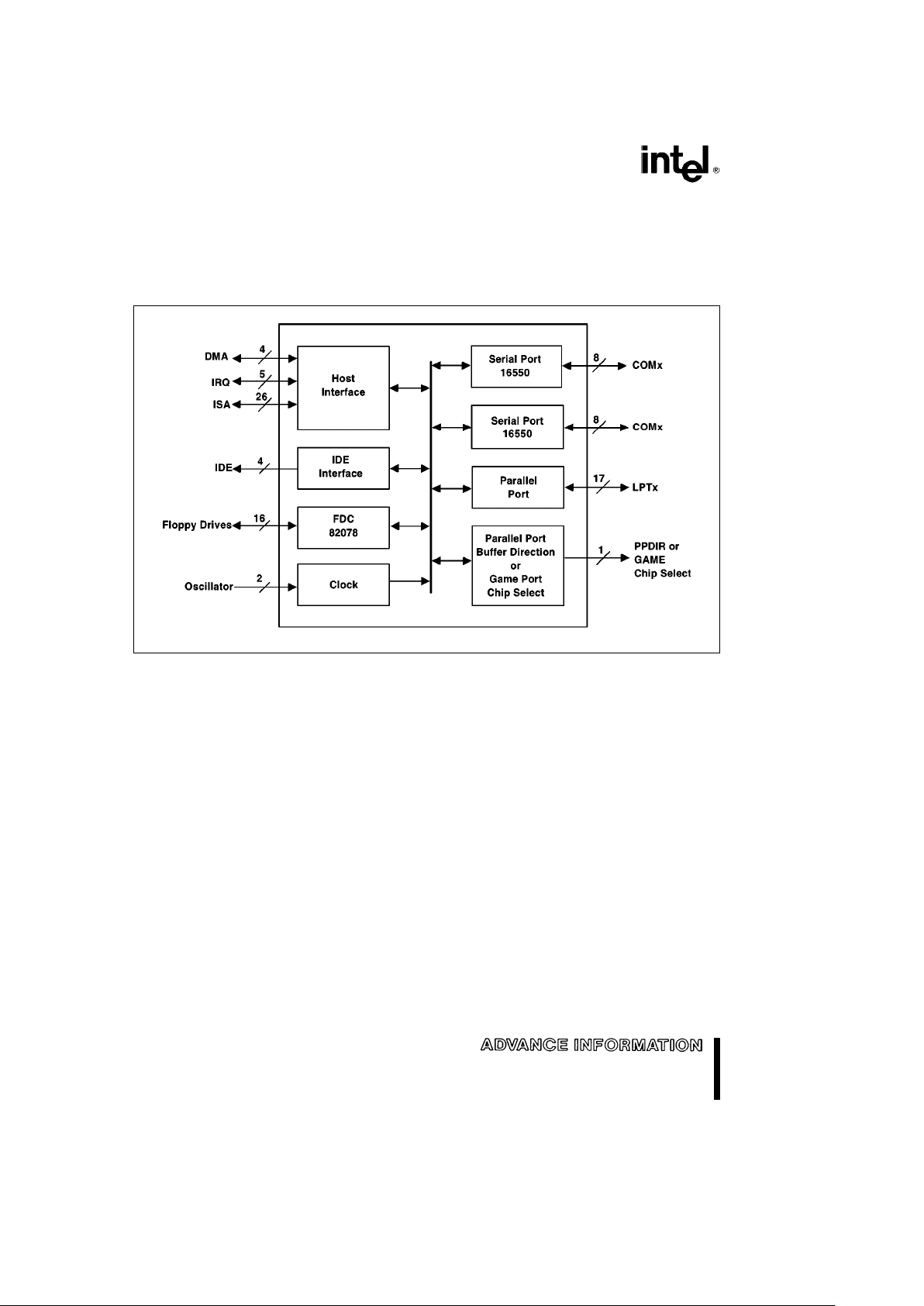

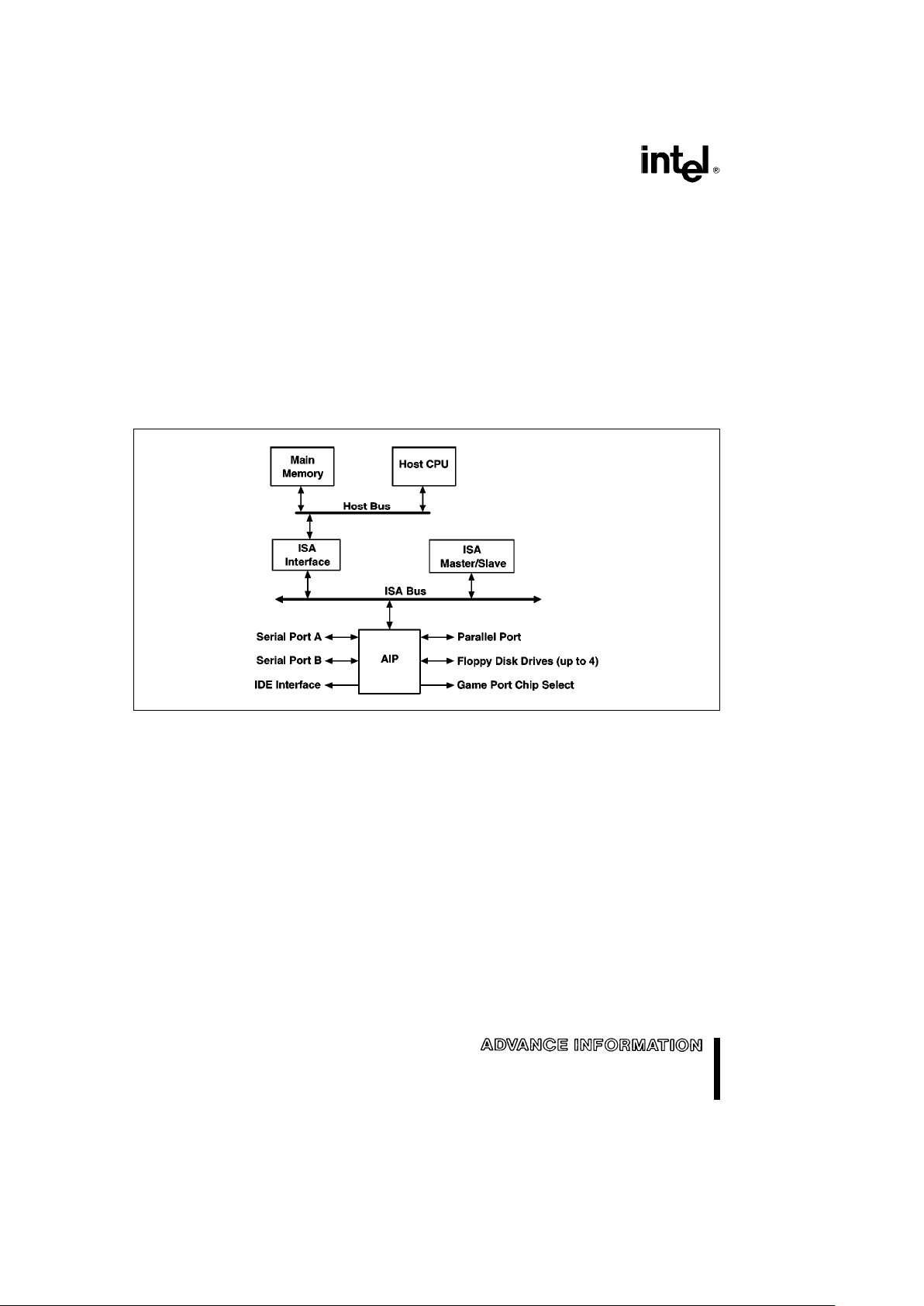

The 82091AA Advanced Integrated Peripheral (AIP) is an integrated I/O solution containing a floppy disk

controller, 2 serial ports, a multi-function parallel port, an IDE interface, and a game port on a single chip. The

integration of these I/O devices results in a minimization of form factor, cost and power consumption. The

82091AA

floppy disk controller is the 82078 core. The serial ports are 16550 compatible. The parallel port supports all of

the IEEE Standard 1284 protocols (ECP, EPP, Byte, Compatibility, and Nibble). The IDE interface supports

8- or 16-bit programmed I/O and 16-bit DMA. The Host Interface is an 8-bit ISA interface optimized for type

‘‘F’’ DMA and no wait-state I/O accesses. Improved throughput and performance, the 82091AA contains six

16-byte FIFOs –two for each serial port, one for the parallel port, and one for the floppy disk controller. The

82091AA also includes power management and 3.3V capability for power sensitive applications such as

notebooks. The 82091AA supports both motherboard and add-in card configurations.

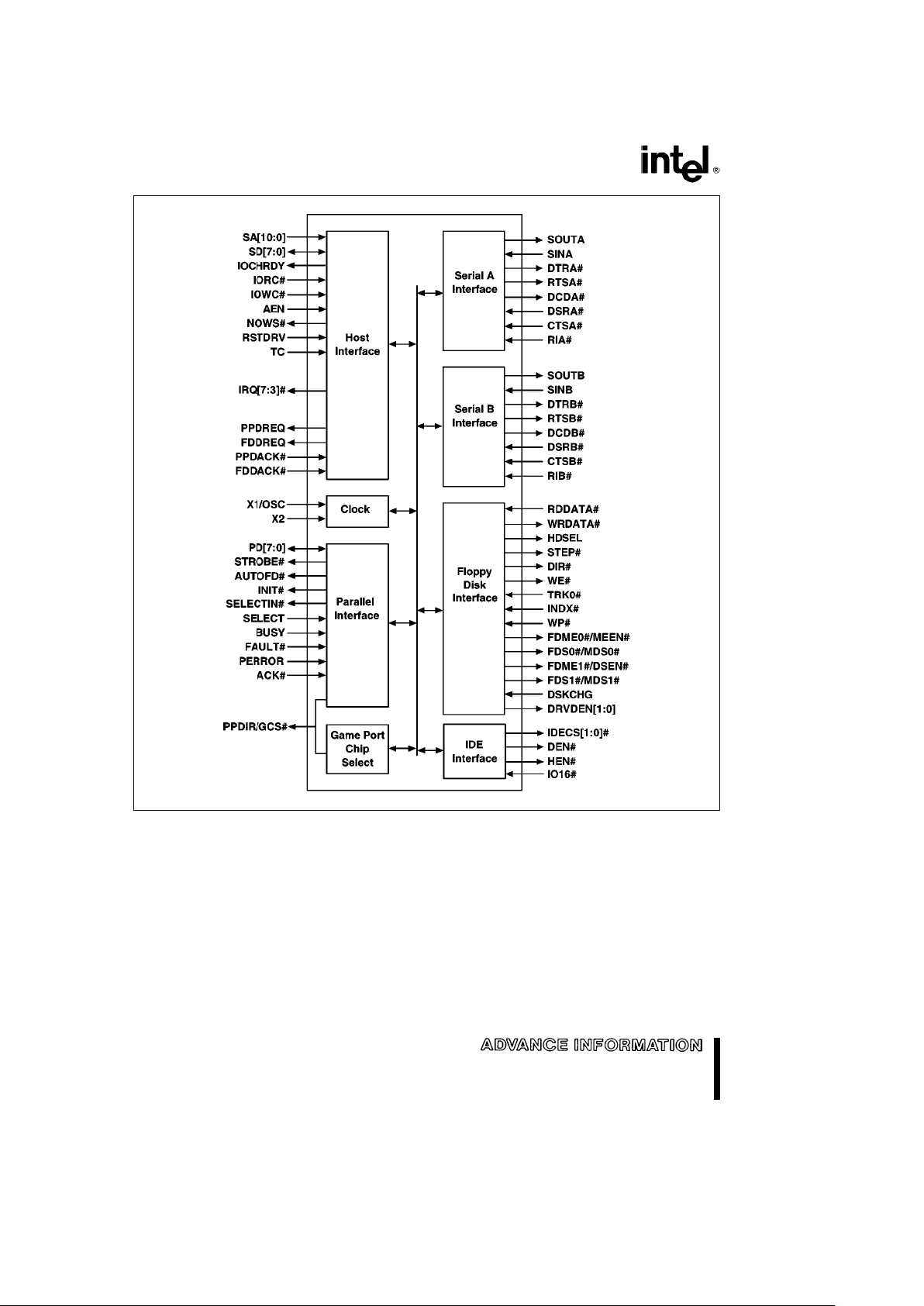

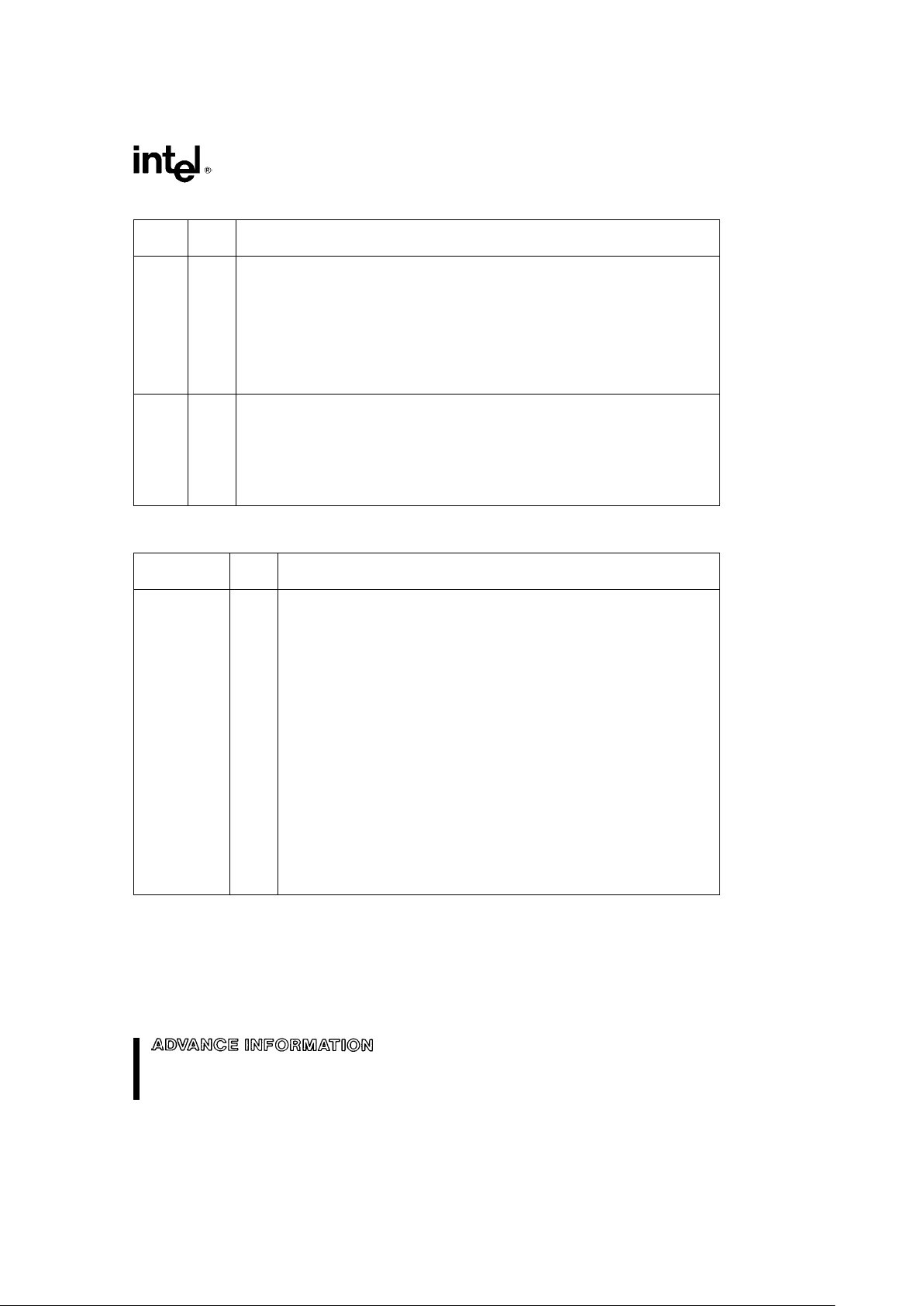

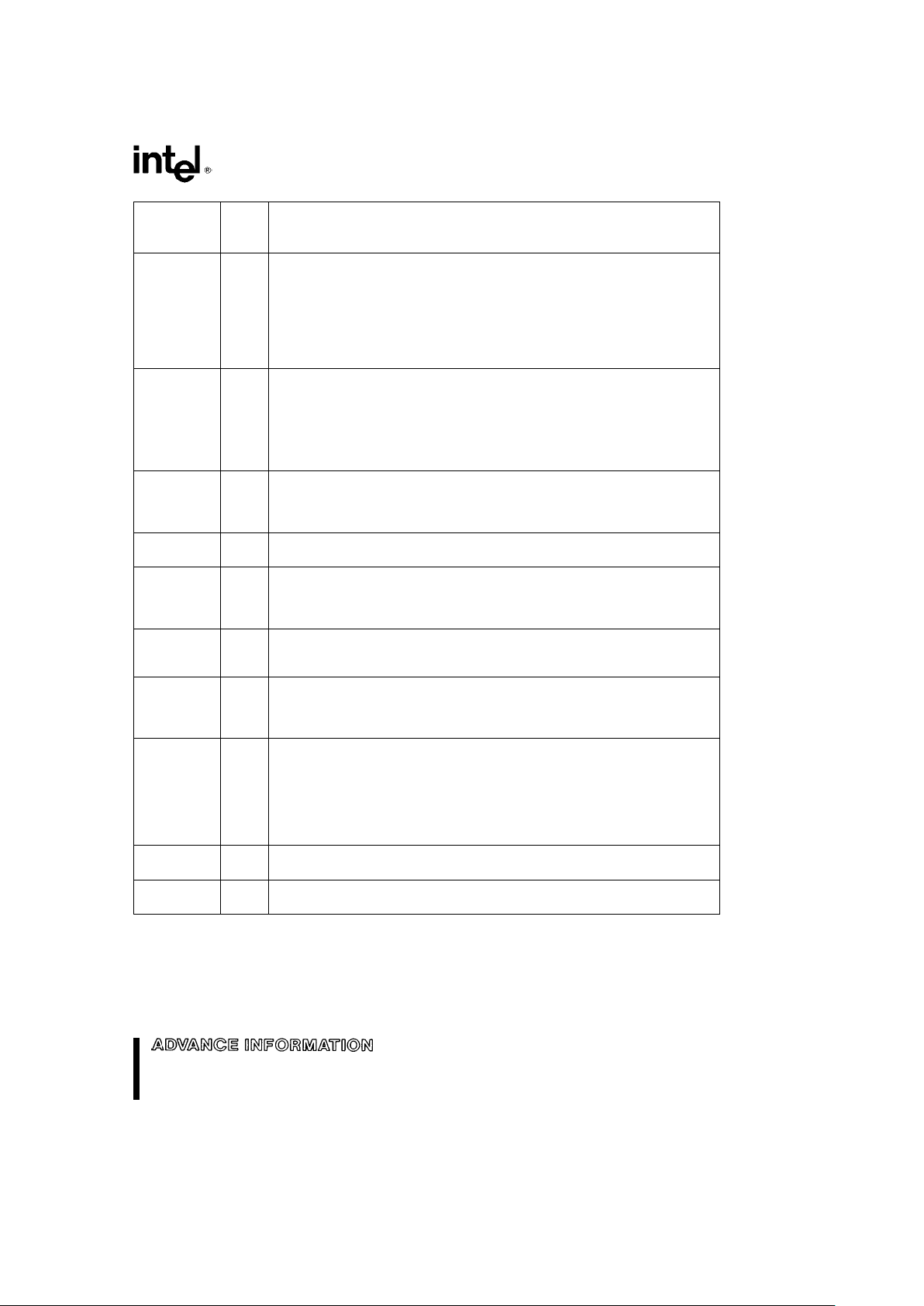

290486– 1

Figure 1. 82091AA Advanced Integrated Peripheral Block Diagram

2

82091AA

ADVANCED INTEGRATED PERIPHERAL (AIP)

CONTENTS PAGE

1.0 OVERVIEW

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 8

1.1 3.3/5V Operating Modes АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 11

2.0 SIGNAL DESCRIPTION АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 11

2.1 Host Interface Signals ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 13

2.2 Floppy Disk Controller Interface АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 15

2.3 Serial Port Interface ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 17

2.4 IDE Interface АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 18

2.5 Parallel Port External Buffer Control/Game Port АААААААААААААААААААААААААААААААААААААААА 19

2.6 Parallel Port Interface ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 20

2.6.1 COMPATIBILITY PROTOCOL SIGNAL DESCRIPTION АААААААААААААААААААААААААААА 21

2.6.2 NIBBLE PROTOCOL SIGNAL DESCRIPTION ААААААААААААААААААААААААААААААААААААА 22

2.6.3 BYTE MODE SIGNAL DESCRIPTION ААААААААААААААААААААААААААААААААААААААААААААА 23

2.6.4 ENHANCED PARALLEL PORT (EPP) PROTOCOL SIGNAL DESCRIPTION ААААААА 24

2.6.5 EXTENDED CAPABILITIES PORT (ECP) PROTOCOL SIGNAL DESCRIPTION ÀÀÀÀ 24

2.7 Hard Reset Signal Conditions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 26

2.8 Power And Ground АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 27

3.0 I/O ADDRESS ASSIGNMENTS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 27

4.0 AIP CONFIGURATION ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 29

4.1 Configuration Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 29

4.1.1 CFGINDX, CFGTRGTÐCONFIGURATION INDEX REGISTER AND TARGET

PORT ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 30

4.1.2 AIPIDÐAIP IDENTIFICATION REGISTER ААААААААААААААААААААААААААААААААААААААААА 32

4.1.3 AIPREVÐAIP REVISION IDENTIFICATION ААААААААААААААААААААААААААААААААААААААА 32

4.1.4 AIPCFG1ÐAIP CONFIGURATION 1 REGISTER АААААААААААААААААААААААААААААААААА 33

4.1.5 AIPCFG2ÐAIP CONFIGURATION 2 REGISTER АААААААААААААААААААААААААААААААААА 34

4.1.6 FCFG1ÐFDC CONFIGURATION REGISTER ААААААААААААААААААААААААААААААААААААА 36

4.1.7 FCFG2ÐFDC POWER MANAGEMENT AND STATUS REGISTER АААААААААААААААА 37

4.1.8 PCFG1ÐPARALLEL PORT CONFIGURATION REGISTER ААААААААААААААААААААААА 38

4.1.9 PCFG2ÐPARALLEL PORT POWER MANAGEMENT AND STATUS

REGISTER АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 40

4.1.10 SACFG1ÐSERIAL PORT A CONFIGURATION REGISTER АААААААААААААААААААААА 42

4.1.11 SACFG2ÐSERIAL PORT A POWER MANAGEMENT AND STATUS

REGISTER АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 43

4.1.12 SBCFG1ÐSERIAL PORT B CONFIGURATION REGISTER АААААААААААААААААААААА 46

3

CONTENTS PAGE

4.1.13 SBCFG2ÐSERIAL PORT B POWER MANAGEMENT AND STATUS

REGISTER

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 48

4.1.13.1 Serial Port A/B Configuration Registers SxEN and SxDPDN Bits ААААААААААААА 49

4.1.14 IDECFGÐIDE CONFIGURATION REGISTER АААААААААААААААААААААААААААААААААААА 50

4.2 Hardware Configuration ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 51

4.2.1 SELECTING THE HARDWARE CONFIGURATION MODE АААААААААААААААААААААААА 52

4.2.2 SELECTING HARDWARE CONFIGURATION MODE OPTIONS ААААААААААААААААААА 53

4.2.3 HARDWARE CONFIGURATION TIMING RELATIONSHIPS ААААААААААААААААААААААА 55

4.2.4 HARDWARE BASIC CONFIGURATION ААААААААААААААААААААААААААААААААААААААААААА 57

4.2.5 HARDWARE EXTENDED CONFIGURATION MODE АААААААААААААААААААААААААААААА 58

4.2.6 SOFTWARE ADD-IN CONFIGURATION АААААААААААААААААААААААААААААААААААААААААА 59

4.2.7 SOFTWARE MOTHERBOARD CONFIGURATION АААААААААААААААААААААААААААААААА 60

5.0 HOST INTERFACE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 61

6.0 PARALLEL PORT ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 62

6.1 Parallel Port Registers ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 62

6.1.1 ISA-COMPATIBLE AND PS/2-COMPATIBLE MODES ААААААААААААААААААААААААААААА 63

6.1.1.1 PDATAÐParallel Port Data Register (ISA-Compatible and PS/2-Compatible

Modes) ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 64

6.1.1.2 PSTATÐStatus Register (ISA-Compatible and PS/2-Compatible Modes) ААААА 64

6.1.1.3 PCONÐControl Register (ISA-Compatible and PS/2-Compatible Mode) АААААА 67

6.1.2 EPP MODE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 69

6.1.2.1 PDATAÐParallel Port Data Register (EPP Mode) ААААААААААААААААААААААААААААА 69

6.1.2.2 PSTATÐStatus Register (EPP Mode) АААААААААААААААААААААААААААААААААААААААА 70

6.1.2.3 PCONÐControl Register (EPP Mode) АААААААААААААААААААААААААААААААААААААААА 72

6.1.2.4 ADDSTRÐEPP Auto Address Strobe Register (EPP Mode) ААААААААААААААААААА 73

6.1.2.5 DATASTRÐAuto Data Strobe Register (EPP Mode) АААААААААААААААААААААААААА 74

6.1.3 ECP MODE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 74

6.1.3.1 ECPAFIFOÐECP Address/RLE FIFO Register (ECP Mode) АААААААААААААААААА 75

6.1.3.2 PSTATÐStatus Register (ECP Mode) АААААААААААААААААААААААААААААААААААААААА 76

6.1.3.3 PCONÐControl Register (ECP Mode) АААААААААААААААААААААААААААААААААААААААА 78

6.1.3.4 SDFIFOÐStandard Parallel Port Data FIFO АААААААААААААААААААААААААААААААААА 80

6.1.3.5 DFIFOÐData FIFO (ECP Mode) ААААААААААААААААААААААААААААААААААААААААААААА 81

6.1.3.6 TFIFOÐECP Test FIFO Register (ECP Mode) АААААААААААААААААААААААААААААААА 82

6.1.3.7 ECPCFGAÐECP Configuration A Register (ECP Mode) АААААААААААААААААААААА 83

6.1.3.8 ECPCFGBÐECP Configuration B Register (ECP Mode) АААААААААААААААААААААА 84

6.1.3.9 ECR ECPÐExtended Control Register (ECP Mode) АААААААААААААААААААААААААА 85

6.2 Parallel Port Operations ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 88

6.2.1 ISA-COMPATIBLE AND PS/2-COMPATIBLE MODES ААААААААААААААААААААААААААААА 88

6.2.2 EPP MODE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 90

6.2.3 ECP MODE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 92

4

CONTENTS PAGE

6.2.3.1 FIFO Operations

ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 95

6.2.3.2 DMA Transfers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 95

6.2.3.3 Reset FIFO and DMA Terminal Count Interrupt ААААААААААААААААААААААААААААААА 95

6.2.3.4 Programmed I/O Transfers АААААААААААААААААААААААААААААААААААААААААААААААААА 95

6.2.3.5 Data Compression ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 96

6.2.4 PARALLEL PORT EXTERNAL BUFFER CONTROL ААААААААААААААААААААААААААААААА 96

6.2.5 PARALLEL PORT SUMMARY АААААААААААААААААААААААААААААААААААААААААААААААААААА 96

7.0 SERIAL PORT ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 97

7.1 Register Description ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 97

7.1.1 THR(A,B)ÐTRANSMITTER HOLDING REGISTER АААААААААААААААААААААААААААААААА 99

7.1.2 RBR(A,B)ÐRECEIVER BUFFER REGISTER АААААААААААААААААААААААААААААААААААААА 99

7.1.3 DLL(A,B), DLM(A,B)ÐDIVISOR LATCHES (LSB AND MSB) REGISTERS АААААААААА 99

7.1.4 IER(A,B)ÐINTERRUPT ENABLE REGISTER АААААААААААААААААААААААААААААААААААА 101

7.1.5 IIR(A,B)ÐINTERRUPT IDENTIFICATION REGISTER АААААААААААААААААААААААААААА 102

7.1.6 FCR(A,B)ÐFIFO CONTROL REGISTER ААААААААААААААААААААААААААААААААААААААААА 104

7.1.7 LCR(A,B)ÐLINE CONTROL REGISTER ААААААААААААААААААААААААААААААААААААААААА 106

7.1.8 MCR(A,B)ÐMODEM CONTROL REGISTER ААААААААААААААААААААААААААААААААААААА 108

7.1.9 LSR(A,B)ÐLINE STATUS REGISTER ААААААААААААААААААААААААААААААААААААААААААА 109

7.1.10 MSR(A,B)ÐMODEM STATUS REGISTER АААААААААААААААААААААААААААААААААААААА 112

7.1.11 SCR(A,B)ÐSCRATCHPAD REGISTER ААААААААААААААААААААААААААААААААААААААААА 113

7.2 FIFO Operations ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 114

7.2.1 FIFO INTERRUPT MODE OPERATION АААААААААААААААААААААААААААААААААААААААААА 114

7.2.2 FIFO POLLED MODE OPERATION АААААААААААААААААААААААААААААААААААААААААААААА 114

8.0 FLOPPY DISK CONTROLLER АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 115

8.1 Floppy Disk Controller Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААА 115

8.1.1 SRBÐSTATUS REGISTER B (EREG ENe1) АААААААААААААААААААААААААААААААААААА 117

8.1.2 DORÐDIGITAL OUTPUT REGISTER АААААААААААААААААААААААААААААААААААААААААААА 118

8.1.3 TDRÐENHANCED TAPE DRIVE REGISTER АААААААААААААААААААААААААААААААААААА 119

8.1.4 MSRÐMAIN STATUS REGISTER ААААААААААААААААААААААААААААААААААААААААААААААА 121

8.1.5 DSRÐDATA RATE SELECT REGISTER ААААААААААААААААААААААААААААААААААААААААА 122

8.1.6 FDCFIFOÐFDC FIFO (DATA) ААААААААААААААААААААААААААААААААААААААААААААААААААА 125

8.1.7 DIRÐDIGITAL INPUT REGISTER ААААААААААААААААААААААААААААААААААААААААААААААА 126

8.1.8 CCRÐCONFIGURATION CONTROL REGISTER АААААААААААААААААААААААААААААААА 127

8.2 Reset АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 128

8.2.1 HARD RESET AND CONFIGURATION REGISTER RESET АААААААААААААААААААААА 128

8.2.2 DOR RESET vs DSR RESET АААААААААААААААААААААААААААААААААААААААААААААААААААА 128

8.3 DMA Transfers ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 128

8.4 Controller Phases АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 128

8.4.1 COMMAND PHASE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 128

8.4.2 EXECUTION PHASE АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 129

5

CONTENTS PAGE

8.4.2.1 Non-DMA Mode Transfers from the FIFO to the Host

АААААААААААААААААААААААА 129

8.4.2.2 Non-DMA Mode Transfers from the Host to the FIFO АААААААААААААААААААААААА 129

8.4.2.3 DMA Mode Transfers from the FIFO to the Host ААААААААААААААААААААААААААААА 129

8.4.2.4 DMA Mode Transfers from the Host to the FIFO ААААААААААААААААААААААААААААА 129

8.4.3 DATA TRANSFER TERMINATION АААААААААААААААААААААААААААААААААААААААААААААА 130

8.5 Command Set/Descriptions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 130

8.5.1 STATUS REGISTER ENCODING АААААААААААААААААААААААААААААААААААААААААААААААА 144

8.5.1.1 Status Register 0 ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 145

8.5.1.2 Status Register 1 ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 145

8.5.1.3 Status Register 2 ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 146

8.5.1.4 Status Register 3 ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 146

8.5.2 DATA TRANSFER COMMANDS ААААААААААААААААААААААААААААААААААААААААААААААААА 147

8.5.2.1 Read Data АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 147

8.5.2.2 Read Deleted Data ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 148

8.5.2.3 Read Track ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 149

8.5.2.4 Write Data АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 149

8.5.2.5 Verify ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 150

8.5.2.6 Format Track ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 151

8.5.2.7 Format Field АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 152

8.5.3 CONTROL COMMANDS АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 153

8.5.3.1 READ ID Command АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 153

8.5.3.2 RECALIBRATE Command АААААААААААААААААААААААААААААААААААААААААААААААААА 153

8.5.3.3 DRIVE SPECIFICATION Command ААААААААААААААААААААААААААААААААААААААААА 153

8.5.3.4 SEEK Command ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 154

8.5.3.5 SENSE INTERRUPT STATUS Command ААААААААААААААААААААААААААААААААААА 155

8.5.3.6 SENSE DRIVE STATUS Command ААААААААААААААААААААААААААААААААААААААААА 155

8.5.3.7 SPECIFY Command АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 155

8.5.3.8 CONFIGURE Command АААААААААААААААААААААААААААААААААААААААААААААААААААА 156

8.5.3.9 VERSION Command ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 157

8.5.3.10 RELATIVE SEEK Command ААААААААААААААААААААААААААААААААААААААААААААААА 157

8.5.3.11 DUMPREG Command ААААААААААААААААААААААААААААААААААААААААААААААААААААА 157

8.5.3.12 PERPENDICULAR MODE Command АААААААААААААААААААААААААААААААААААААА 157

8.5.3.13 POWERDOWN MODE Command ААААААААААААААААААААААААААААААААААААААААА 158

8.5.3.14 PART ID Command ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 159

8.5.3.15 OPTION Command АААААААААААААААААААААААААААААААААААААААААААААААААААААААА 159

8.5.3.16 SAVE Command АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 159

8.5.3.17 RESTORE Command ААААААААААААААААААААААААААААААААААААААААААААААААААААА 159

8.5.3.18 FORMAT AND WRITE Command АААААААААААААААААААААААААААААААААААААААААА 160

6

CONTENTS PAGE

9.0 IDE INTERFACE

АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 160

9.1 IDE Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 160

9.2 IDE Interface Operation АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 161

10.0 POWER MANAGEMENT АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 163

10.1 Power Management Registers ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 163

10.2 Clock Power Management АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 163

10.3 FDC Power Management АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 163

10.4 Serial Port Power Management АААААААААААААААААААААААААААААААААААААААААААААААААААААА 164

10.5 Parallel Port Power Management АААААААААААААААААААААААААААААААААААААААААААААААААААА 164

11.0 ELECTRICAL CHARACTERISTICS ААААААААААААААААААААААААААААААААААААААААААААААААААА 165

11.1 Absolute Maximum Ratings ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 165

11.2 DC Characteristics АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 165

11.3 Oscillator ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 168

11.4 AC Characteristics АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 169

11.4.1 CLOCK TIMINGS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 176

11.4.2 HOST TIMINGS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 176

11.4.3 FDC TIMINGS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 179

11.4.4 PARALLEL PORT TIMINGS АААААААААААААААААААААААААААААААААААААААААААААААААААА 180

11.4.5 IDE TIMINGS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 184

11.4.6 GAME PORT TIMINGS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 184

11.4.7 SERIAL PORT TIMINGS ААААААААААААААААААААААААААААААААААААААААААААААААААААААА 185

12.0 PINOUT AND PACKAGE INFORMATION ААААААААААААААААААААААААААААААААААААААААААААА 186

12.1 Pin Assignment ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 186

12.2 Package Characteristics ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 190

13.0 DATA SEPARATOR CHARACTERISTICS FOR FLOPPY DISK MODE АААААААААААААААА 192

13.1 Write Data Timing ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 194

13.2 Drive Control АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 194

13.3 Internal PLL ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА 195

APPENDIX AÐFDC FOUR DRIVE SUPPORT АААААААААААААААААААААААААААААААААААААААААААААА A-1

A.1 Floppy Disk Controller Interface Signals ААААААААААААААААААААААААААААААААААААААААААААААА A-1

A.2 DORÐDigital Output Register АААААААААААААААААААААААААААААААААААААААААААААААААААААААА A-2

A.3 TDRÐEnhanced Tape Drive Register ААААААААААААААААААААААААААААААААААААААААААААААААА A-5

A.4 MSRÐMain Status Register АААААААААААААААААААААААААААААААААААААААААААААААААААААААААА A-7

7

82091AA

1.0. OVERVIEW

The major functions of the 82091AA are shown in Figure 1. A brief description of each of these functions is

presented in this section.

Host Interface

The 82091AA host interface is an 8-bit direct-drive (24 mA) ISA Bus/X-Bus interface that permits the CPU to

access its registers through read/write operations in I/O space. These registers may be accessed by programmed I/O and/or DMA bus cycles. With the exception of the IDE Interface, all functions on the 82091AA

require only 8-bit data accesses. The 16-bit access required for the IDE Interface is supported through the

appropriate chip selects and data buffer enables from the 82091AA.

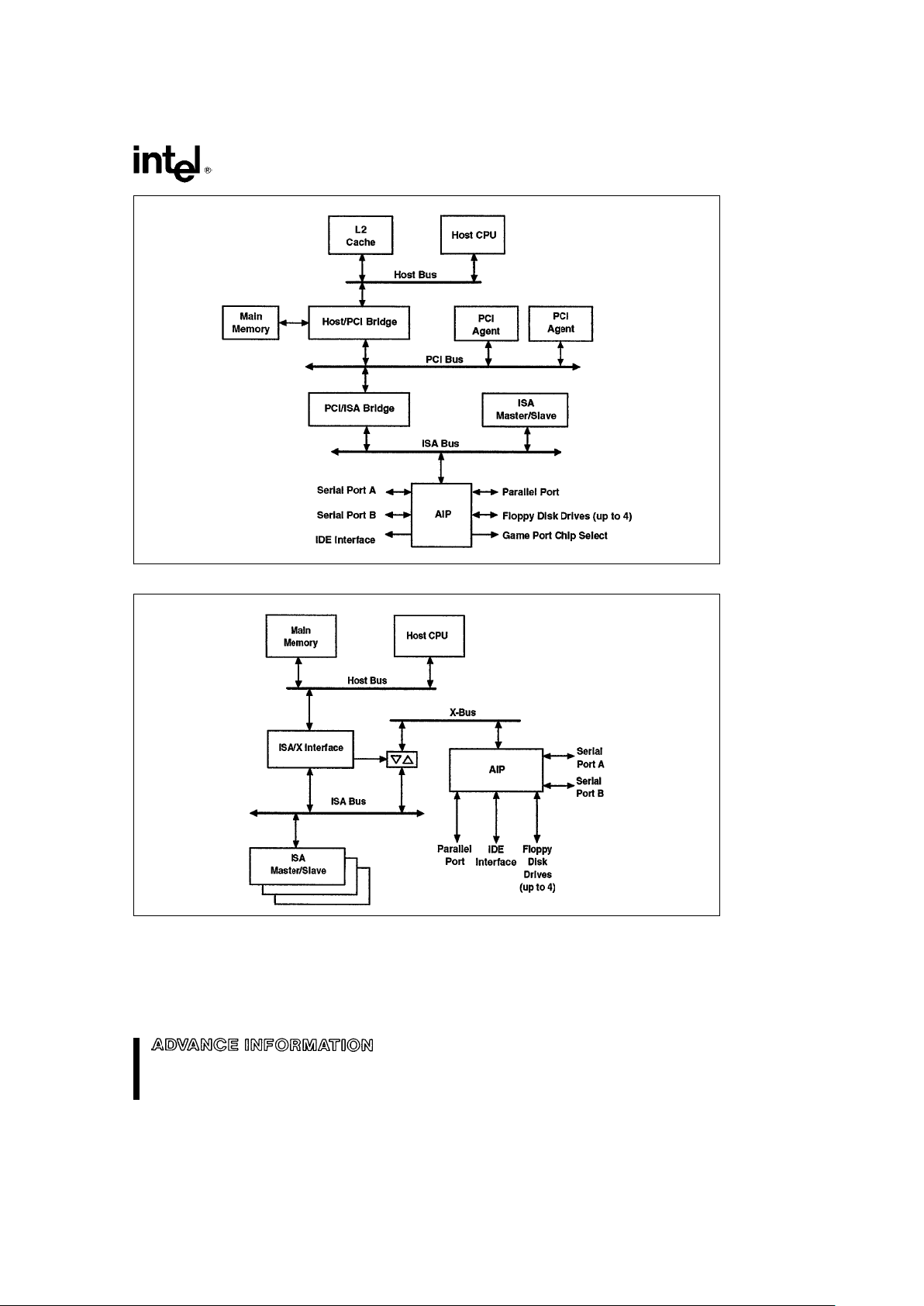

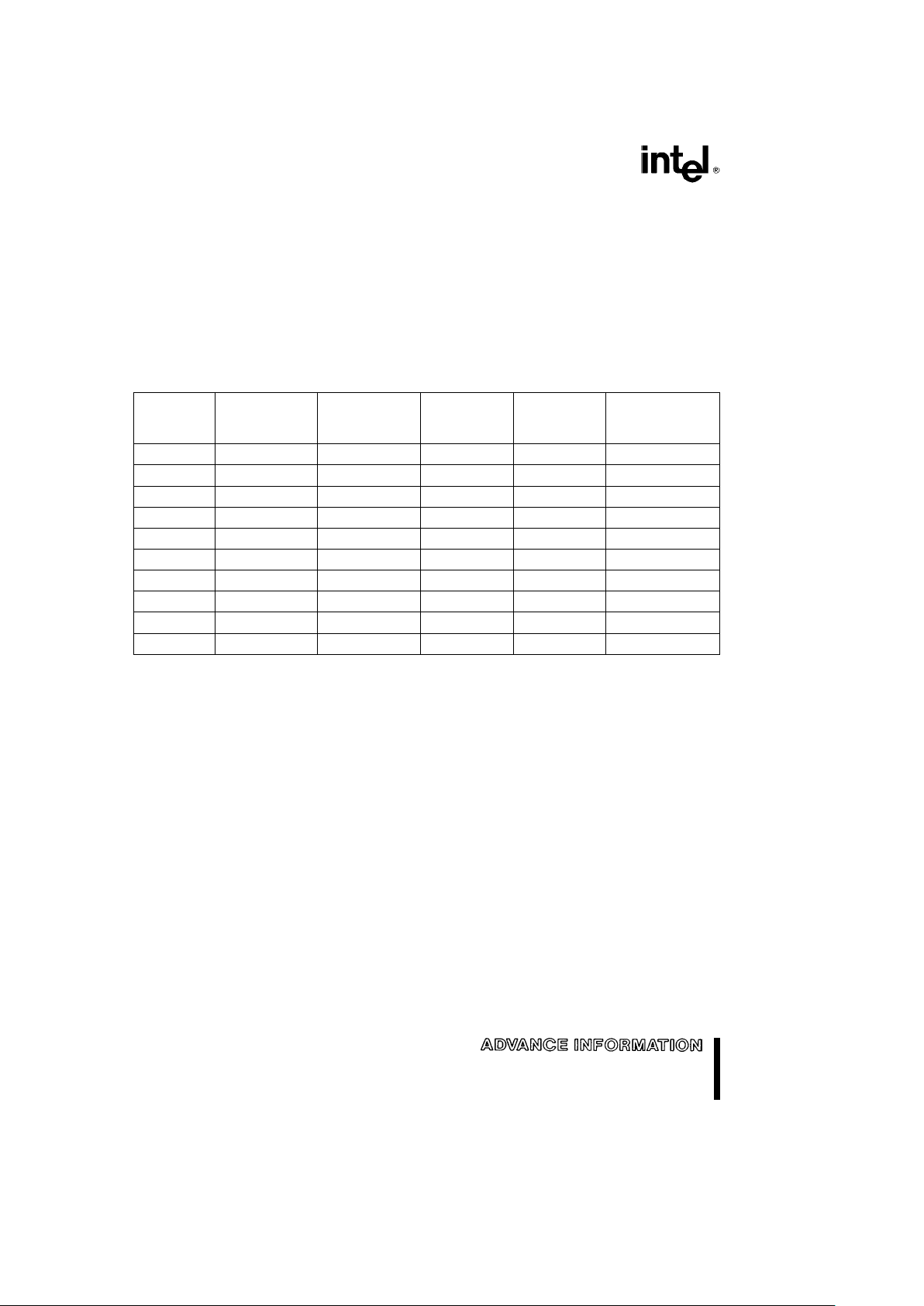

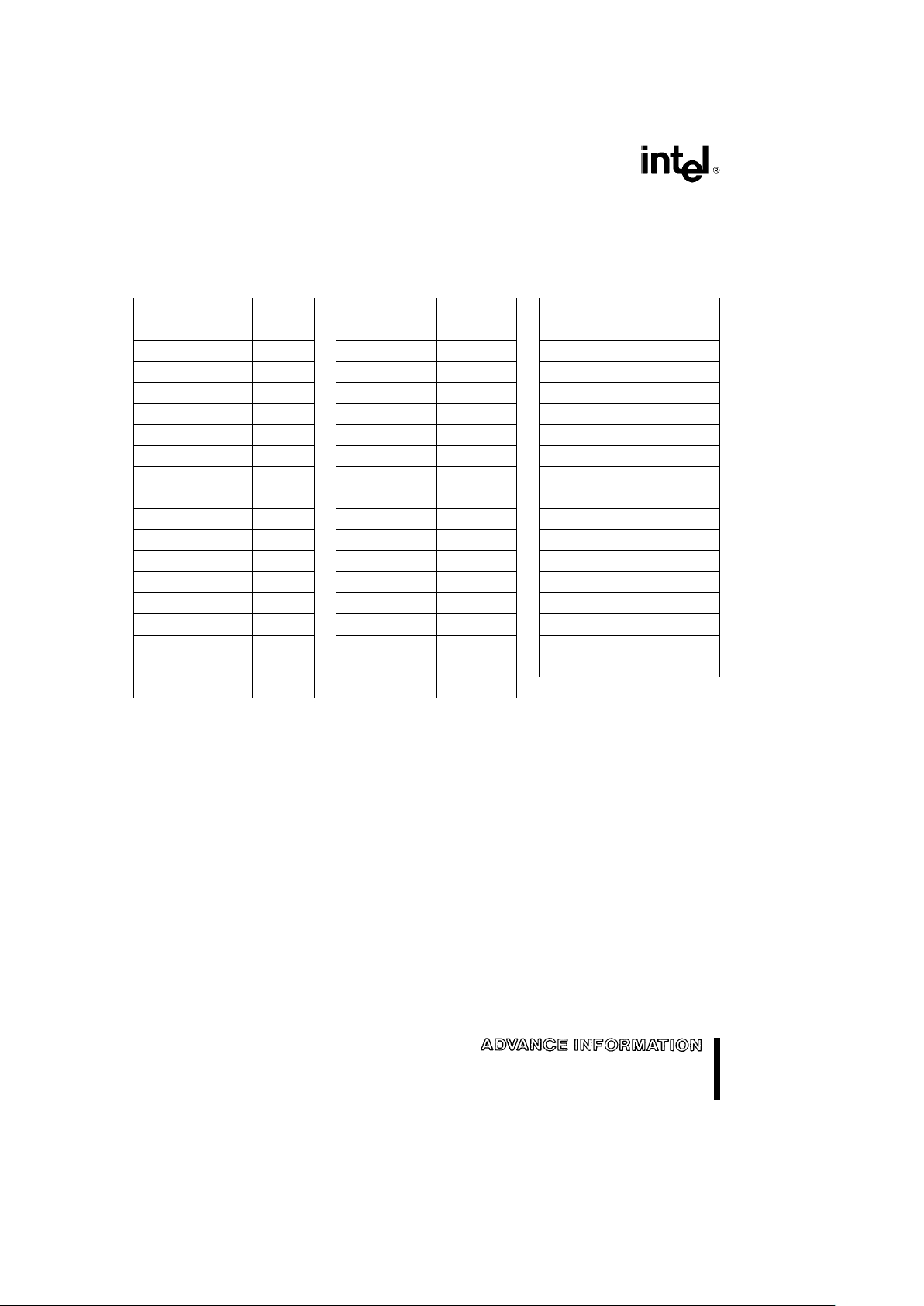

Figure 2 shows an example system implementation with the 82091AA located on an ISA Bus add-in card. This

add-in card could also be used in a PCI-based system as shown in Figure 3. For motherboard implementations, the 82091AA can be located on the X-Bus as shown in Figure 4.

290486– 2

Figure 2. Block Diagram of the 82091AA on the ISA Bus

8

82091AA

290486– 3

Figure 3. Block Diagram of the 82091AA in a PCI System

290486– 4

Figure 4. Block Diagram of the 82091AA on the X-Bus

9

82091AA

Floppy Disk Controller

The 82091AA’s enhanced floppy disk controller

(FDC) incorporates several new features allowing for

easy implementation in both the portable and desktop markets. It provides a low cost, small form factor

solution targeted for 5.0V and 3.3V platforms. The

FDC supports up to four drives.

The 82091AA’s FDC implements these new features

while remaining functionally compatible with 82078/

82077SL/82077AA/8272A floppy disk controllers.

Together, with a 24-MHz crystal, a resistor package

and a device chip select, these devices allow for the

most integrated solution available. The integrated

analog PLL data separator has better performance

than most board level discrete PLL implementations

and can be operated at 1 Mbps/500 Kbps/

300 Kbps/250 Kbps. A 16-byte FIFO substantially

improves system performance and is ideal for multimaster systems (e.g., EISA).

Serial Ports

The 82091AA contains two independent serial ports

that provide asynchronous communications that are

equivalent to two 16550 UARTs. The serial ports

have identical circuitry and provide the serial communication interface to a peripheral device or modem via Serial Port A and Serial Port B. Each serial

port can be configured for one of eight address assignments. The standard PC/AT compatible logical

address assignments for COM1, COM2, COM3, and

COM4 are supported.

The serial ports perform serial-to-parallel conversion

on data characters received from a peripheral device or modem, and parallel-to-serial conversion on

data characters received from the host. The serial

ports can operate in either FIFO mode or non-FIFO

mode. In FIFO mode, a 16-byte transmit FIFO holds

data from the host to be transmitted on the serial

link and a 16-byte receive FIFO that buffers data

from the serial link until read by the host.

The serial ports contain programmable baud rate

generators that divide the internal reference clock

by divisors of 1 to (2

16

b

1), and produce a 16x

clock for driving the transmitter and receiver logic.

The internal reference clock can be programmed to

support MIDI. The serial ports have complete modem-control capability and a prioritized interrupt system.

Parallel Port

The 82091AA provides a multi-function parallel port

that transfers information between the host and peripheral device (e.g., printer). The parallel port interface contains nine control/status lines and an 8-bit

data bus. The standard PC/AT compatible logical

address assignments for LPT1, LPT2, and LPT3 are

supported. The parallel port can be configured for

one of four modes and supports the following IEEE

Standard 1284 parallel interface protocol standards:

Parallel Port Parallel Interface

Mode Protocol

ISA-Compatible Mode Compatibility, Nibble

PS/2-Compatible Mode Byte

EPP Mode EPP

ECP Mode ECP

For ISA-Compatible and PS/2-Compatible modes,

software controls the handshake signals on the parallel port interface to transfer data between the host

and peripheral device. Status and Control registers

permit software to monitor the state of the peripheral

device and generate handshake sequences.

The EPP parallel port interface protocol increases

throughput by specifying an automatic handshake

sequence. In EPP mode, the 82091AA parallel port

automatically generates this handshake sequence in

hardware to transfer data between the host and

peripheral device.

10

82091AA

In addition to a hardware handshake on the parallel

port interface, the ECP protocol specification also

defines DMA and FIFO capability. To minimize processor overhead data transfer to/from a peripheral

device, the 82091AA parallel port, in ECP mode,

provides a 16-byte FIFO with DMA capability.

IDE Interface

The 82091AA supports the IDE (Integrated Drive

Electronics) interface by providing chip selects and

lower data byte control. Two chip selects are used to

access registers on the IDE device. Separate lower

and upper byte data control signals are provided.

With these control signals, minimal external logic is

needed to implement 16-bit IDE I/O and DMA interfaces.

Game Port

The 82091AA provides a game port chip select signal for use when the 82091AA is in an add-in card

application. This function is assigned to I/O address

location 201h. Note that when the 82091AA is located on the motherboard, this feature is not available.

Power Management

82091AA power management provides a mechanism for saving power when the device or a portion

of the device is not being used. By programming the

appropriate 82091AA registers, software can invoke

power management to the entire 82091AA or selected modules within the 82091AA (e.g., floppy disk

controller, serial port, or parallel port). There are two

methods for applying power managementÐdirect

powerdown or auto powerdown. Direct powerdown

turns off the clock to a particular module immediately placing that module into a powerdown state. This

method removes the clock regardless of the activity

or status of the module. When auto powerdown is

invoked, the module enters a powerdown state

(clock is turned off) after certain conditions are met

and the module is in an idle state.

1.1. 3.3V/5V Operating Modes

The 82091AA can operate at a power supply of

3.3V, 5V or a mix of 3.3V and 5V. The mixed power

supply mode provides 5V interfaces for the floppy

disk controller and parallel port while all other

82091AA interfaces and internal logic (including the

floppy disk controller and parallel port internal circuitry) operate at 3.3V. The mixed mode permits 5V

floppy disk drives and parallel port peripherals to be

used in a 3.3V system without external buffering.

NOTE:

3.3V operation is available only in the

82091AA.

2.0. SIGNAL DESCRIPTION

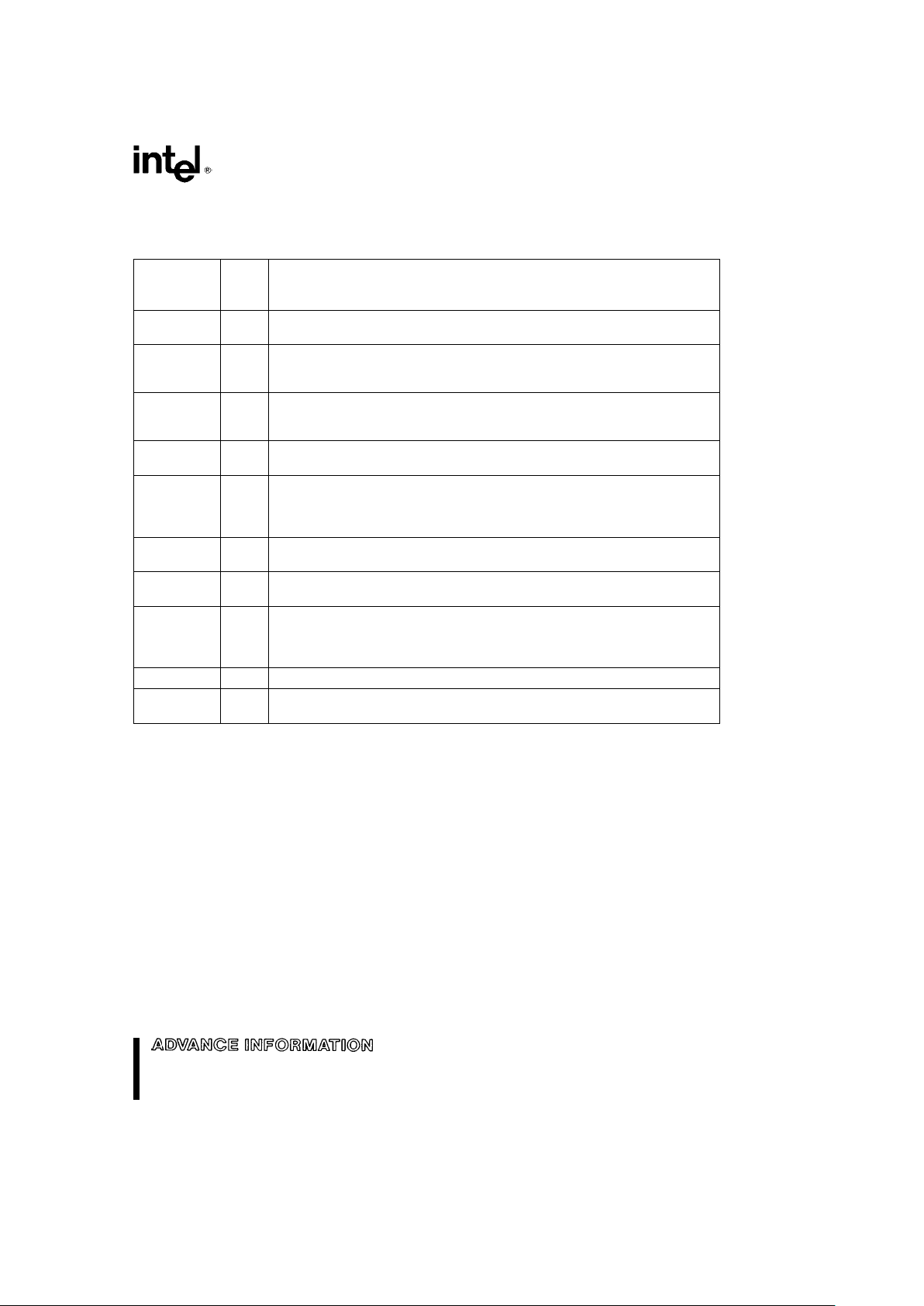

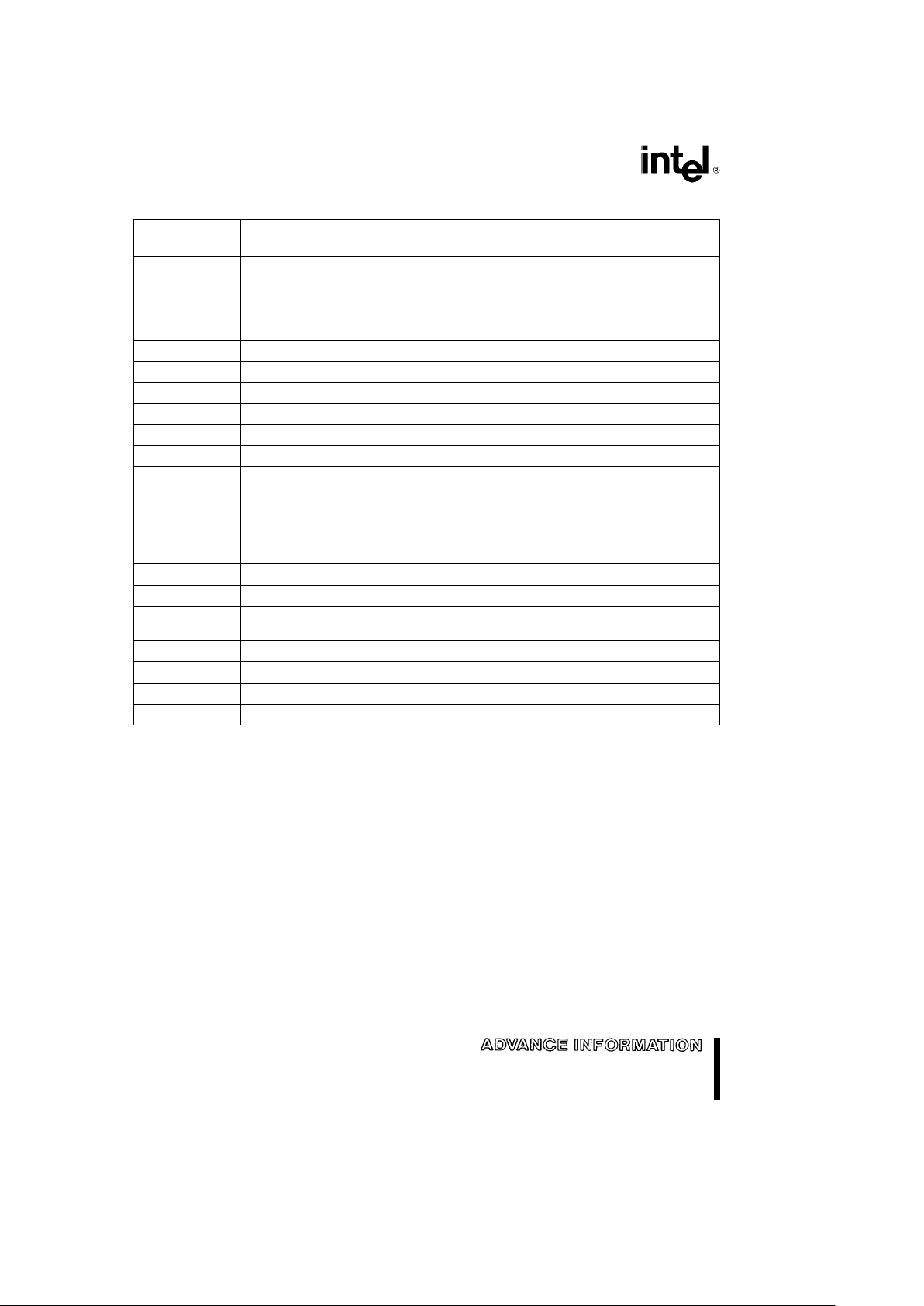

This section describes the 82091AA signals. The interface signals are shown in Figure 5 and described

in the following tables. Signal descriptions are organized by functional group.

Note that the ‘‘

Ý

’’ symbol at the end of a signal

name indicates the active, or asserted, state occurs

when the signal is at a low voltage level. When ‘‘

Ý

’’

is not present after the signal name, the signal is

asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working

with a mixture of ‘‘active-low’’ and ‘‘active-high’’ signals. The term assert,orassertion, indicates that a

signal is active, independent of whether that level is

represented by a high or low voltage. The term ne-

gate,ornegation, indicates that a signal is inactive.

The following notations are used to describe pin

types:

I Input Pin

O Output Pin

I/O Bi-Directional Pin

11

82091AA

290486– 5

Figure 5. 82091AA Signals

12

82091AA

2.1 Host Interface Signals

Signal

Type Description

Name

ISA SIGNALS

SA[10:0

]

I SYSTEM ADDRESS BUS: The 82091AA decodes the standard ISA I/O address

space using SA[9:0]. SA10 is used along with SA[9:0]to decode the extended

register set of the ECP parallel port. SA[10:0]connects directly to the ISA system

address bus.

SD[7:0

]

I/O SYSTEM DATA BUS: SD[7:0]is a bi-directional data bus. Data is written to and

read from the 82091AA on these signal lines. SD[7:0]connect directly to the ISA

system data bus.

IORC

Ý

I I/O READ COMMAND STROBE: IORCÝis an I/O access read control signal.

When a valid internal address is decoded by the 82091AA and IORC

Ý

is asserted,

data at the decoded address location is driven onto the SD[7:0]signal lines.

IOWC

Ý

I I/O WRITE COMMAND STROBE: IOWCÝis an I/O access write control signal.

When a valid internal address is decoded by the 82091AA and IOWC

Ý

is asserted,

data on the SD[7:0]signal lines is written into the decoded address location at the

rising edge of IOWC

Ý

.

NOWS

Ý

O NO WAIT-STATES: End data transfer signal. The 82091AA asserts NOWSÝwhen

a valid internal address is decoded by the 82091AA and the IORC

Ý

or IOWC

Ý

signal is asserted. This reduces the total bus cycle time by eliminating the waitstates associated with the default 8-bit I/O cycles. NOWSÝis not asserted for IDE

accesses or DMA accesses. This is an open drain output pin.

IOCHRDY O I/O CHANNEL READY: The 82091AA uses this signal for parallel port data

transfers when the parallel port is in EPP mode. In this case, the 82091AA negates

IOCHRDY to extend the cycle to allow for completion of transfers to/from the

peripheral attached to the parallel port. When the parallel port is in EPP mode, the

82091AA negates IOCHRDY to lengthen the ISA Bus cycle if the parallel port BUSY

signal is asserted.

The 82091AA also uses IOCHRDY during hardware configuration time (see Section

4.0, AIP Configuration). If IOWC

Ý

/IORCÝis asserted to the 82091AA during

hardware configuration time, the 82091AA negates IOCHRDY until hardware

configuration time is completed. This is an open drain output pin.

AEN I ADDRESS ENABLE: AEN is used during DMA cycles to prevent the 82091AA from

misinterpreting DMA cycles from valid I/O cycles. When negated, AEN indicates

that the 82091AA may respond to address and I/O commands addressed to the

82091AA. When asserted, AEN informs the 82091AA that a DMA transfer is

occurring. When AEN is asserted and a xDACK

Ý

signal is asserted, the 82091AA

responds to the cycle as a DMA cycle.

RSTDRV I RESET DRIVE: RSTDRV forces the 82091AA to a known state. All 82091AA

registers are set to their default state.

X1/OSC I CRYSTAL1/OSCILLATOR: Main clock input signal can be a 24 MHz crystal

connected across X1 and X2 or a 24 MHz TTL level clock input connected to X1.

X2 I CRYSTAL2: This signal pin is connected to one side of the crystal when a crystal

oscillator is used to provide the main clock. If an external oscillator/clock is

connected to X1, this pin is not used and left unconnected.

13

82091AA

2.1 Host Interface Signals (Continued)

Signal

Type Description

Name

DMA SIGNALS

FDDREQ O FLOPPY DISK CONTROLLER DMA REQUEST: The 82091AA asserts FDDREQ

to request service from a DMA controller for the FDC module. This signal is

enabled/disabled by bit 3 of the Digital Output Register (DOR). When disabled,

FDDREQ is tri-stated.

FDDACK

Ý

I FLOPPY DISK CONTROLLER DMA ACKNOWLEDGE: The DMA controller

asserts this signal to acknowledge the FDC DMA request. When asserted, the

IORC

Ý

and IOWCÝinputs are enabled during DMA transfers. This signal is

enabled/disabled by bit 3 of the DOR.

PPDREQ O PARALLEL PORT DMA REQUEST: Parallel port DMA service request to the

system DMA controller. This signal is only used when the parallel port is in ECP

hardware mode and is always negated when the parallel port is not in this mode. In

ECP hardware mode DMA requests are enabled/disabled by bit 3 of the ECP

Extended Control Register (ECR). When disabled, PPDREQ is tri-stated.

PPDACK

Ý

I PARALLEL PORT DMA ACKNOWLEDGE: The DMA controller asserts this signal

to acknowledge the parallel port DMA request. When asserted the IORCÝand

IOWC

Ý

inputs are enabled during DMA transfers. This signal is enabled/disabled

by bit 3 of the ECR Register.

TC I TERMINAL COUNT: The system DMA controller asserts TC to indicate it has

reached the last programmed data transfer. TC is accepted only when FDDACK

Ý

or PPDACKÝis asserted.

INTERRUPT SIGNALS

IRQ3, IRQ4 O INTERRUPT 3 AND 4: IRQ3 and IRQ4 are associated with the serial ports and

can be programmed (via the AIPCFG2 Register) to be either active high or active

low. These signals can be configured for a particular serial channel via hardware

configuration (at powerup) or by software configuration.

Under Hardware Configuration

IRQ3 is used as a serial port interrupt if the serial port is configured at address

locations 2F8h –2FFh or 2E8h–2EFh. IRQ4 is used as a serial port interrupt if the

serial port is configured at address locations 3F8h – 3FFh or 3E8h – 3EFh.

Under Software configuration

IRQ3 and IRQ4 are independently configured (i.e., the IRQ does not automatically

track the communication port address assignment).

These interrupts are enabled/disabled globally via bit 3 of the serial port Modem

Control Register (MCR) and for specific conditions via the Interrupt Enable

Register (IER). IRQ3 and IRQ4 are tri-stated when not enabled.

IRQ5, IRQ7 O INTERRUPT REQUEST 5: IRQ5 and IRQ7 are associated with the parallel port

and can be programmed (via AIPCFG2 Register) to be either active high or active

low. Either IRQ5 or IRQ7 is enabled/disabled via PCFG1 Register to signal a

parallel port interrupt. The interrupt not selected is disabled and tri-stated.

During hardware configuration (see Section 4.0, AIP Configuration), IRQ5 is used if

the parallel port is assigned to 278h –27Fh and IRQ7 is used if the parallel port

interrupt is assigned to either 3BCh– 3BFh or 378h –37Fh.

14

82091AA

2.1 Host Interface Signals (Continued)

Signal

Type Description

Name

INTERRUPT SIGNALS (Continued)

IRQ6 O INTERRUPT REQUEST 6: IRQ6 is associated with the floppy disk controller and can

be programmed (via the AIPCFG2 Register) to be either active high or active low. In

non-DMA mode this signal is asserted to signal when a data transfer is ready. IRQ6 is

also asserted to signal the completion of the execution phase for certain FDC

commands. This signal is enabled/disabled by the DMAGATE bit in the Digital Output

Register of the FDC. The signal is tri-stated when disabled.

2.2 Floppy Disk Controller Interface

Signal

Type Description

Name

RDDATA

Ý

I READ DATA: Serial data from the disk drive.

WRDATA

Ý

O WRITE DATA: MFM serial data to the disk drive. Precompensation value is

selectable through software.

HDSEL O HEAD SELECT: Selects which side of a disk is to be accessed. When asserted

(low), side 1 is selected. When negated (high), side 0 is selected.

STEP

Ý

O STEP: STEPÝsupplies step pulses (asserted) to the drive to move the head

between the tracks during a seek operation.

DIR

Ý

O DIRECTION: Controls the direction the head moves when a step signal is present.

The head moves toward the center when DIR

Ý

is asserted and away from the

center when negated.

WE

Ý

O WRITE ENABLE: WEÝis a disk drive control signal. When asserted, WE

Ý

enables the head to write to the disk.

TRK0

Ý

I TRACK0: The disk drive asserts this signal to indicate that the head is on track 0.

INDX

Ý

I INDEX: The disk drive asserts this signal to indicate the beginning of the track.

WP

Ý

I WRITE PROTECT: The disk drive asserts this signal to indicate that the disk drive

is write-protected.

DSKCHG I DISK CHANGE: The disk drive asserts this signal to indicate that the drive door

has been opened. The state of this signal input is available in the Digital Input

Register (DIR

Ý

).

DRIVDEN0 O DRIVE DENSITY: These signals are used by the disk drive to configure the drive

for the appropriate media density. These signals are controlled by the FDC’s Drive

DRIVDEN1

Specification Command.

15

82091AA

2.2 Floppy Disk Controller Interface (Continued)

Signal

Type Description

Name

FDME1Ý/OFLOPPY DRIVE MOTOR ENABLE 1, IDLE, OR DRIVE SELECT ENABLE: This

signal pin has two functions

(1)

. FDME1Ýis the motor enable for drive 1. FDME1

Ý

DSEN

Ý

(1)

is directly controlled via the Digital Output Register (DOR) and is a function of the

mapping based on the BOOTSEL bits in the Tape Drive Register (TDR).

The Drive Select Enable (DSENÝ) function is only used in a four floppy drive

system (see Appendix A, FDC Four Drive Support).

FDS1Ý/OFLOPPY DRIVE SELECT1, POWERDOWN, OR MOTOR DRIVE SELECT 1: This

signal pin has two functions

(1)

. FDS1Ýis the floppy drive select for drive 1. FDS1

Ý

MDS1

(1)

is controlled by the select bits in the DOR and is a function of the mapping based

on the BOOTSEL bits in the TDR.

The Motor Drive Select 1 (MDS1) function is only used in a four floppy drive system

(see Appendix A, FDC Four Drive Support).

FDME0Ý/OFLOPPY DRIVE MOTOR ENABLE 0 OR MOTOR ENABLE ENABLE: This signal

pin has two functions

(1)

. FDME0Ýis the motor enable for drive 0. FDME0Ýis

MEEN

Ý

(1)

directly controlled via the Digital Output Register (DOR) and is a function of the

mapping based on the BOOTSEL bits in the Tape Drive Register (TDR).

The Motor Enable Enable (MEEN

Ý

) function is only used in a four floppy drive

system (see Appendix A, FDC Four Drive Support).

FDS0Ý/OFLOPPY DRIVE SELECT 0 OR MOTOR DRIVE SELECT 0: This signal pin has two

functions

(1)

. FDS0Ýis the floppy drive select for drive 0. This output is controlled

MDS0

(1)

by the drive select bits in the DOR and is a function of the mapping based on

BOOTSEL bits in the TDR.

The Motor Drive Select 0 (MDS0) function is only used in a four floppy drive system

(see Appendix A, FDC Four Drive Support).

NOTE:

1. The function selected for these pins is based on the FDDQTY bit in the FCFG1 Register as shown in the following table.

Signal Pin

2 Drive System 4 Drive System

(FDDQTY

e

0) (FDDQTYe1)

FDME1Ý/DSEN

Ý

FDME1

Ý

DSEN

Ý

FDS1Ý/MDS1

Ý

FDS1

Ý

MDS1

FDME0Ý/MEEN

Ý

FDME0

Ý

MEEN

Ý

FDS0Ý/MDS0 FDS0

Ý

MDS0

When FDDQTYe1, these signal pins are used to control an external decoder for a four floppy disk

drive system as described in Appendix A, FDC Four Drive Support.

16

82091AA

2.3 Serial Port Interface

Serial Port A signal names end in the letter A and Serial Port B signal names end in the letter B. Serial Port A

and B signals have the same functionality.

Signal

Type Description

Name

CTSAÝ,ICLEAR TO SEND: When asserted, this signal indicates that the modem or data

set is ready to exchange data. The CTS

Ý

signal is a modem status input whose

CTSB

Ý

condition the CPU can determine by reading the CTS bit in Modem Status

Register (MSR) for the appropriate serial port. The CTS bit is the compliment of

the CTS

Ý

signal. The DCTS bit in the MSR indicates whether the CTSÝinput

has changed state since the previous reading of the MSR. CTSÝhas no effect on

the transmitter.

DCDAÝ,IDATA CARRIER DETECT: When asserted, this signal indicates that the data

carrier has been detected by the modem or data set. The DCD

Ý

signal is a

DCDB

Ý

modem status whose condition the CPU can determine by reading the DCD bit in

the MSR for the appropriate serial port. The DCD bit is the compliment of the

DCD

Ý

signal. The DDCD bit in the MSR indicates whether the DCDÝinput has

changed state since the previous reading of the MSR. DCDÝhas no effect on the

transmitter.

DSRAÝ,IDATA SET READY: When asserted, this signal indicates that the modem or data

set is ready to establish the communications link with the serial port module. The

DSRB

Ý

DSRÝsignal is a modem status whose condition the CPU can determine by

reading the DSR bit in the MSR for the appropriate serial channel. The DSR bit is

the compliment of the DSR

Ý

signal. The DSR bit in the MSR indicates whether

the DSRÝinput has changed state since the previous reading of the MSR. DSR

Ý

has no effect on the transmitter.

DTRAÝ, I/O DATA TERMINAL READY: DTRAÝ/DTRBÝare outputs during normal system

operations. When asserted, this signal indicates to the modem or data set that

DTRB

Ý

the serial port module is ready to establish a communications link. The DTR

Ý

signal can be asserted via the Modem Control Register (MCR). A hard reset

negates this signal.

Hardware Configuration

These signals are only inputs during hardware configuration time (RSTDRV

asserted and for a short time after RSTDRV is negated). (See Section 4.0, AIP

Configuration.)

RIAÝ, RIB

Ý

I RING INDICATOR: When asserted, this signal indicates that a telephone ringing

signal has been received by the modem or data set. The RI

Ý

signal is a modem

status input whose condition the CPU can determine by reading the RI bit in the

MSR for the appropriate serial channel. The RI bit is the compliment of the RI

Ý

signal. The TERI bit in the MSR indicates whether the RIÝinput has changed

from low to high since the previous reading of the MSR.

17

82091AA

2.3 Serial Port Interface (Continued)

Signal

Type Description

Name

RTSAÝ, I/O REQUEST TO SEND: RTSAÝ/RTSBÝare outputs during normal system

operations. When asserted, this signal informs the modem or data set that the

RTSB

Ý

serial port module is ready to exchange data. The RTSÝsignal can be asserted

via the RTS bit in the Modem Control Register. A hard reset negates this signal.

Hardware Configuration

These signals are only inputs during hardware configuration time (RSTDRV

asserted and for a short time after RSTDRV is negated). (See Section 4.0, AIP

Configuration.)

SINA, SINB I SERIAL INPUT: Serial data input from the communications link. (Peripheral

device, modem, or data set.)

SOUTA, I/O SERIAL OUTPUT: SOUTA/SOUTB are serial data outputs to the communications

link during normal system operations. (Peripheral device, modem, or data set.) The

SOUTB

SOUT signal is set to a marking state (logic 1) after a hard reset.

Test Mode

In test mode (selected via the SACFG2 or SBCFG2 Registers), the baudout from

the baud rate generator is output on SOUTx.

Hardware Configuration

These signals are only inputs during hardware configuration time (RSTDRV

asserted and for a short time after RSTDRV is negated). (See Section 4.0, AIP

Configuration.)

2.4 IDE Interface

Signal

Type Description

Name

IO16

Ý

I 16-BIT I/O: This signal is driven by I/O devices on the ISA Bus to indicate

support for 16-bit I/O bus cycles. The IDE interface asserts this signal to the

82091AA to indicate support for 16-bit transfers. For IDE transfers, the 82091AA

asserts HEN

Ý

when IO16Ýis asserted.

IDECS[1:0

]

Ý

I/O IDE CHIP SELECT: IDECS[1:0

]

Ý

are outputs during normal system operation

and are chip selects for the IDE interface. IDECS[1:0

]

Ý

select the Command

Block Registers of the IDE device and are decoded from SA[9:3]and AEN.

Hardware Configuration

These signals are only inputs during hardware configuration time (RSTDRV

asserted). (See Section 4.0, AIP Configuration.)

18

82091AA

2.4 IDE Interface (Continued)

Signal

Type Description

Name

DEN

Ý

I/O DATA ENABLE: DENÝis an output during normal system operations and is a data

enable for an external data buffer for all 82091AA and IDE accesses. The SD[7:0

]

signals can be connected directly to the ISA. In this case, the DEN

Ý

signal is not used.

However, an external buffer can be used to isolate the SD[7:0]signals from the 240 pF

loading of the ISA Bus. With an external buffer implementation, DEN

Ý

controls the

external buffers for transfers to/from the ISA Bus.

Hardware Configuration

This signal is only an input during hardware configuration time (RSTDRV asserted).

(See Section 4.0, AIP Configuration.)

HENÝI/O IDE UPPER DATA TRANSCEIVER ENABLE: HENÝis an output during normal system

operations and is a high byte data transceiver enable signal for the IDE hard disk drive

interface. HENÝis asserted for I/O accesses to the IDE data register when the drive

asserts IO16

Ý

.

Hardware Configuration

This signal is only an input during hardware configuration time (RSTDRV asserted).

(See Section 4.0, AIP Configuration.)

2.5 Parallel Port External Buffer Control/Game Port

Signal

Type Description

Name

PPDIR/GCS

Ý

I/O PARALLEL PORT DIRECTION (PPDIR) or GAME PORT CHIP SELECT

(GCS

Ý

): This signal is an output during normal operations and provides the

PPDIR and GCS

Ý

functions as follows:

PPDIR

This signal pin functions as a parallel port direction control output when the

82091AA is configured for software motherboard mode (SWMB). For

configuration details, see Section 4.0, AIP Configuration. If external buffers are

used on PD[7:0], PPDIR can be used to control the buffer direction. The

82091AA drives this signal low when PD[7:0]are outputs and the 82091AA

drives this signal high when PD[7:0]are inputs. Note that if a configuration

mode other than SWMB is selected, this signal pin is a game port chip select

and does not track the PD[7:0]signal direction.

GCS

Ý

This signal pin functions as a game port chip select output when 82091AA

configuration is set for Software Add-In (SWAI), Hardware Basic (HWB), or

Hardware Extended (HWE) modes. When the host accesses I/O address 201h,

GCS

Ý

is asserted.

Hardware Configuration

This signal is only an input during hardware configuration time (RSTDRV

asserted). (See Section 4.0, AIP Configuration.)

19

82091AA

2.6 Parallel Port Interface

The 82091AA parallel port is a multi-function interface that can be configured for one of four hardware

modes (see Section 4.0, AIP Configuration). The

hardware modes are ISA-Compatible, PS/2-Compatible, EPP, and ECP modes. These parallel port

modes support the compatibility, nibble, byte, EPP

and ECP parallel interface protocols described in the

IEEE 1284 standard. The operation and use of the

interface signal pins are a function of the parallel

port hardware mode selected and the protocol used.

Table 1 shows a matrix of the 82091AA parallel port

signal names and corresponding signal names for

each of the protocols. Sections 2.6.1–2.6.5 provide

a signal description for the five interface protocols.

Note that the 82091AA hardware operations are the

same for Compatibility and Nibble protocols. The

signals, however, are controlled and used differently

via software and the peripheral device.

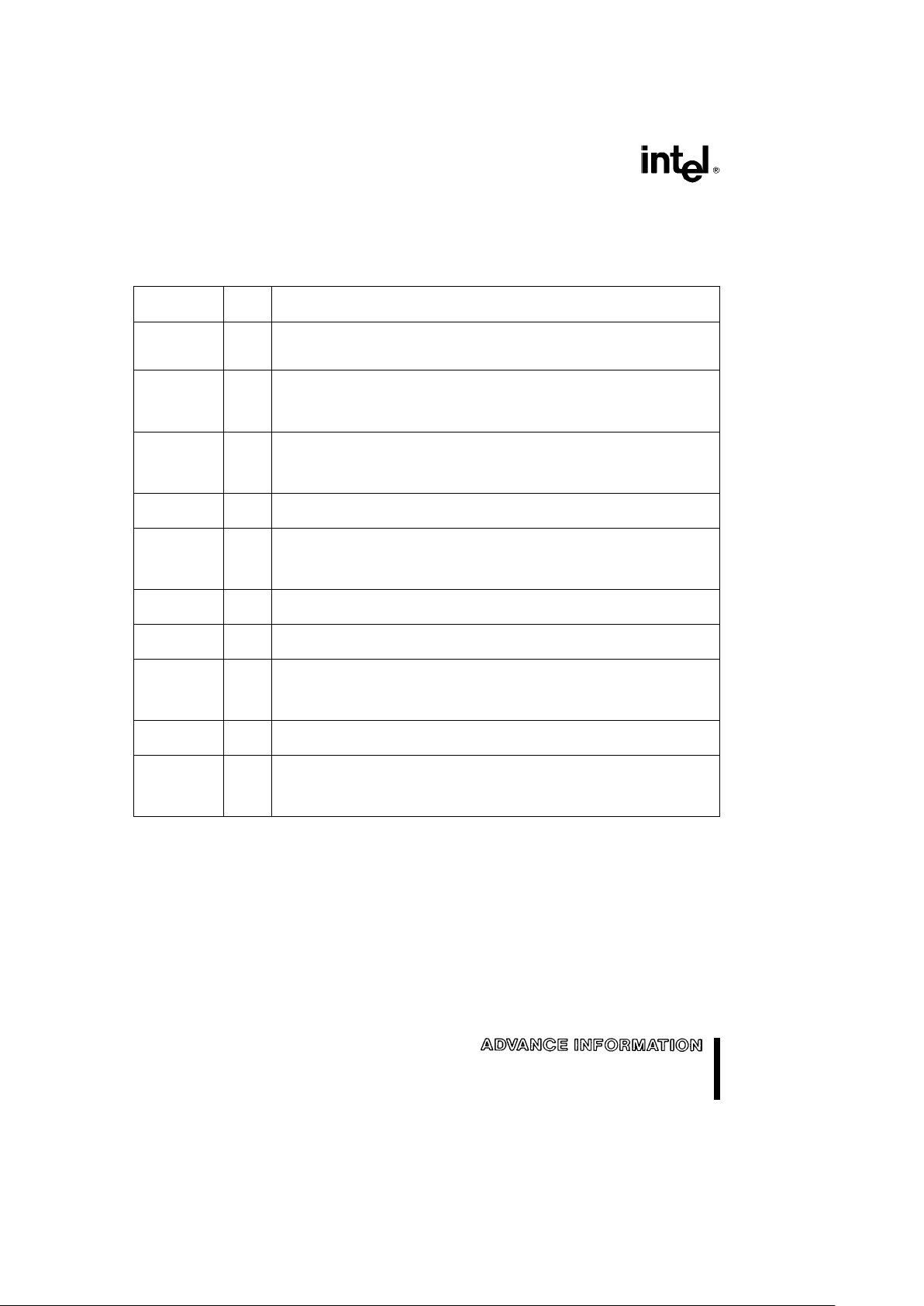

Table 1. Parallel Port Signal Name Cross Reference

82091AA Compatibility

Nibble Protocol Byte Protocol EPP Protocol ECP Protocol

Signal Protocol Signal

Signal Names Signal Names Signal Names Signal Names

Names Names

STROBE

Ý

Strobe

Ý

Ð HostCLK Write

Ý

HostClk

BUSY Busy PtrBusy PtrBusy Wait

Ý

PeriphAck

ACK

Ý

Ack

Ý

PtrClk PtrClk Intr PeriphClk

Ý

SELECT Select Xflag Xflag Xflag Xflag

PERROR PError AckDataReq AckDataReq AckDataReq AckReverse

Ý

FAULT

Ý

Fault

Ý

DataAvail

Ý

DataAvail

Ý

DataAvail

Ý

PeriphRequest

Ý

INIT

Ý

Init

Ý

Ð Ð Init

Ý

ReverseRequest

Ý

AUTOFD

Ý

AutoFd

Ý

HostBusy HostBusy DStrb

Ý

HostAck

PD[7:0

]

Data[8:1

]

Ð Data[8:1

]

Data[8:1

]

Data[8:1

]

SELECTINÝSelectIn

Ý

Ð Ð AStrb

Ý

ECP Mode

NOTE:

Not all parallel port signal pins are used for certain parallel port interface protocols. These signals are labeled ‘‘Ð’’.

20

82091AA

2.6.1 COMPATIBILITY PROTOCOL SIGNAL DESCRIPTION

Except for the data bus, the 82091AA and compatibility protocol signal names are the same. For the data bus,

the 82091AA signal names PD[7:0]corresponds to the compatibility protocol signal names Data[8:1].

82091AA

Signal Type Compatibility Protocol Signal Name and Description

Name

STROBE

Ý

O STROBE: The host asserts STROBEÝto latch data into the peripheral device’s

input latch. This signal is controlled via the PCON Register.

BUSY I BUSY: BUSY is asserted by the peripheral to indicate that the peripheral device

is not ready to receive data. The status of this signal line is reported in the PSTAT

Register.

ACK

Ý

I ACKNOWLEDGE: The printer asserts this signal to indicate that it has received

the data and is ready for new data. The status of this signal line is reported in the

PSTAT Register.

SELECT I SELECT: SELECT is asserted by the peripheral device to indicate that the device

is on line. The status of this signal line is reported in the PSTAT Register.

PERROR I PAPER ERROR: The peripheral device asserts PERROR to indicate that it has

encountered an error in the paper path. The exact meaning varies from peripheral

device to peripheral device. The status of this signal line is reported in the PSTAT

Register.

FAULT

Ý

I FAULT: FAULTÝis asserted by the peripheral device to indicate that an error

has occurred. The status of this signal line is reported in the PSTAT Register.

INIT

Ý

O INITIALIZE: The host asserts INITÝto issue a hardware reset to the peripheral

device. This signal is controlled via the PCON Register.

AUTOFD

Ý

O AUTO FEED: AUTOFDÝis asserted by the host to put the peripheral device into

auto-line feed mode. This means that when software asserts this signal, the

printer is instructed to advance the paper one line for each carriage return

encountered. This signal is controlled via the PCON Register.

PD[7:0

]

O DATA: Forward channel data.

SELECTIN

Ý

O SELECT INPUT: SELECTINÝis asserted by the host to select a peripheral

device. This signal is controlled via the PCON Register.

21

82091AA

2.6.2 NIBBLE PROTOCOL SIGNAL DESCRIPTION

The Nibble protocol assigns the following signal operation to the parallel port pins. The name in bold at the

beginning of the signal description column is the Nibble protocol signal name. The terms assert and negate

are used in accordance with the 82091AA signal name as described at the beginning of Section 2.0. For

example, AUTOFD

Ý

(HostBusy) asserted refers to AUTOFDÝ(HostBusy) at a low level.

82091AA

Signal Type Nibble Protocol Signal Name and Description

Name

STROBE

Ý

O STROBE: The host controls this signal via the PCON Register and STROBE

Ý

should be held negated by the host.

BUSY I PRINTER BUSY (PtrBusy): The peripheral drives this signal to transfer data bits

3 and 7 sequentially. The status of this signal line is reported in the PSTAT

Register.

ACK

Ý

I PRINTER CLOCK (PtrClk): The peripheral device asserts ACKÝ(PtrClk) to

indicate to the host that data is available. The signal is subsequently asserted to

qualify data being sent to the host. The status of this signal line is reported in the

PSTAT Register. If interrupts are enabled via the PCON Register, the assertion of

this signal causes a host interrupt to be generated.

SELECT I XFLAG: The peripheral device drives this signal to transfer data bits 1 and 5

sequentially. The status of this signal line is reported in the PSTAT Register.

PERROR I ACKNOWLEDGE DATA REQUEST (AckDataReq): This signal is initially high.

The peripheral device drives this signal low to acknowledge HostBusy assertion.

PERROR is subsequently used to transfer data bits 2 and 6 sequentially. The

status of this signal line is reported in the PSTAT Register.

FAULT

Ý

I DATA AVAILABLE (DataAvail): The peripheral device asserts FAULT

Ý

(DataAvail) to indicate data availability. Subsequently used to transfer data bits 0

and 4 sequentially. The status of this signal line is reported in the PSTAT

Register.

INIT

Ý

O INITIALIZE: The host controls this signal via the PCON Register.

AUTOFD

Ý

O HOST BUSY (HostBusy): The host negates AUTOFDÝ(HostBusy) in response

to ACK

Ý

being asserted. This signal is subsequently driven low to enable the

peripheral to transfer data to the host. AUTOFDÝis then driven high to

acknowledge receipt of byte data. This signal is controlled via the PCON

Register.

PD[7:0

]

O DATA: This 8-bit output data path to the peripheral Host data is written to the

peripheral attached to the parallel port interface on these signal lines.

SELECTIN

Ý

O SELECT INPUT: This signal is controlled by the PCON Register.

22

82091AA

2.6.3 BYTE MODE SIGNAL DESCRIPTION

The Byte protocol assigns the following signal operation to the parallel port pins. The name in bold at the

beginning of the signal description column is the Byte protocol signal name. The terms assert and negate are

used in accordance with the 82091AA signal name as described at the beginning of Section 2.0. For example,

STROBE

Ý

(HostClk) asserted refers to STROBEÝ(HostClk) at a low level.

82091AA

Type Byte Protocol Signal Name and Description

Signal Name

STROBE

Ý

O HOST CLOCK (HostClk): This signal is strobed low by the host to acknowledge

receipt of data. Note that the peripheral must not interpret this as a latch strobe

for forward channel data.

BUSY I PRINTER BUSY (PtrBusy): The peripheral device asserts BUSY (PtrBusy) to

provide forward channel peripheral busy status. The status of this signal line is

reported in the PSTAT Register.

ACK

Ý

I PRINTER CLOCK (PtrClk): The peripheral device asserts ACKÝ(PtrClk) to

indicate to the host that data is available. The signal is subsequently asserted to

qualify data being sent to the host. The status of this signal line is reported in the

PSTAT Register. If interrupts are enabled via the PCON Register, the assertion

of this signal causes a host interrupt to be generated.

SELECT I XFLAG: SELECT (XFLAG) is asserted by the peripheral device to indicate that

the device is on line. The status of this signal line is reported in the PSTAT

Register.

PERROR I ACKNOWLEDGE DATA REQUEST (AckDataReq): This signal is initially high.

The peripheral device drives this signal low to acknowledge HostBusy assertion.

The status of this signal line is reported in the PSTAT Register.

FAULT

Ý

I DATA AVAILABILITY (DataAvail): The peripheral device asserts FAULT

Ý

(DataAvail) to indicate data availability. The status of this signal line is reported in

the PSTAT Register.

INIT

Ý

O INITIALIZE: The host controls this signal via the PCON Register and INIT

Ý

should be held in the negated state.

AUTOFD

Ý

O HOST BUSY (HostBusy): The host negates AUTOFDÝ(HostBusy) in response

to ACK

Ý

being asserted.The signal is subsequently driven low to enable the

peripheral to transfer data to the host. AUTOFD

Ý

is then driven high to

acknowledge receipt of nibble data. This signal is controlled via the PCON

Register.

PD[7:0

]

O DATA: This 8-bit data bus is used for bi-directional data transfer.

SELECTIN

Ý

I/O SELECT INPUT: This signal is controlled by the PCON Register.

23

82091AA

2.6.4 ENHANCED PARALLEL PORT (EPP) PROTOCOL SIGNAL DESCRIPTION

EPP protocol assigns the following signal operation to the parallel port pins. The name in bold at the beginning

of the signal description column is the EPP mode signal name. The terms assert and negate are used in

accordance with the 82091AA signal name as described at the beginning of Section 2.0. For example, BUSY

(Wait

Ý

) asserted refers to BUSY (WaitÝ) being high.

82091AA

Type EPP Protocol Signal Name and Description

Signal Name

STROBE

Ý

O WRITE (WriteÝ): STROBEÝ(WriteÝ) indicates an address or data read/write

operation to the peripheral. The 82091AA drives this signal low for a write and

high for a read.

BUSY I WAIT (WaitÝ): The peripheral sets BUSY (WaitÝ) low to indicate that the device

is not ready. When BUSY signal is low, the 82091AA negates IOCHRDY on the

ISA Bus to lengthen the I/O cycles. The peripheral device sets BUSY (Wait

Ý

)

high to indicate that transfer of data or address is completed.

ACK

Ý

I INTERRUPT REQUEST (Intr): The peripheral asserts ACKÝ(Intr) to generate

an interrupt the host. When this signal is low and interrupts are enabled via bit 4

of the PCON Register, the 82091AA generates an interrupt request (via either

IRQ5 or IRQ7) to the host.

SELECT I SELECT: SELECT is asserted by the peripheral device to indicate that the

device is on line. The status of this signal line is reported in the PSTAT Register.

PERROR I PAPER ERROR: The peripheral device asserts PERROR to indicate that it has

encountered an error in the paper path. The exact meaning varies from

peripheral device to peripheral device. The status of this signal line is reported in

the PSTAT Register.

FAULT

Ý

I FAULT: FAULTÝis asserted by the peripheral device to indicate that an error

has occurred. The status of this signal line is reported in the PSTAT Register.

INIT

Ý

O INITIALIZE: The host asserts INITÝto issue a hardware reset to the peripheral

device. This signal is controlled via the PCON Register.

AUTOFD

Ý

O DATA STROBE (DStrbÝ): The 82091AA asserts AUTOFDÝ(DStrbÝ)to

indicate that valid data is present on PD[7:0

]

and is used by the peripheral to

latch data during write cycles. For reads, the 82091AA reads in data from

PD[7:0]when this signal is asserted.

PD[7:0

]

I/O DATA: This 8-bit bi-directional bus provides addresses or data during the write

cycles and supplies addresses or data to the 82091AA during the read cycles.

SELECTIN

Ý

O ADDRESS STROBE (AStrbÝ): The 82091AA asserts SELECTINÝ(AStrbÝ)to

indicate that a valid address is present on PD[7:0]and is used by the peripheral

to latch addresses during write cycles. For reads, the 82091AA reads in an

address from PD[7:0]when this signal is asserted.

2.6.5 EXTENDED CAPABILITIES PORT (ECP) PROTOCOL SIGNAL DESCRIPTION

ECP protocol assigns the following signal operation to the parallel port pins. The name in bold at the beginning

of the signal description column is the ECP protocol signal name. The terms assert and negate are used in

accordance with the 82091AA signal name as described at the beginning of Section 2.0. For example,

STROBE

Ý

(HostClk) asserted refers to STROBEÝ(HostClk) being low.

24

82091AA

82091AA

Signal Type ECP Protocol Signal Name and Description

Name

STROBE

Ý

O HOST CLOCK (HostClk): In the forward direction, the 82091AA asserts

STROBE

Ý

(HostClk) to instruct the peripheral to latch the data on PD[7:0].

During write operations, the peripheral should latch data on the rising edge of

STROBE

Ý

(HostClk). STROBEÝ(HostClk) handshakes with BUSY (PeriphAck)

during write operations and is negated after the 82091AA detects BUSY

(PeriphAck) asserted. STROBE

Ý

(HostClk) is not asserted by the 82091AA again

until BUSY (PeriphAck) is detected negated. For read operations (reverse

direction), STROBE

Ý

(HostClk) is not used.

BUSY I PERIPHERAL ACKNOWLEDGE (PeriphAck): The peripheral device asserts this

signal during a host write operation to acknowledge receipt of data. The

peripheral device then negates the signal after STROBE

Ý

is detected high to

terminate the transfer. For host write operations (forward direction), this signal

handshakes with STROBE

Ý

(HostClk). During a host read operation (reverse

direction), BUSY (PeriphAck) is normally low and is driven high by the peripheral

to identify Run Length Encoded (RLE) data.

ACK

Ý

I PERIPHERAL CLOCK (PeriphClk): During a peripheral to host transfer (reverse

direction), ACK

Ý

(PeriphClk) is asserted by the peripheral to indicate data is valid

on the data bus and then negated after AUTOFD

Ý

is detected high. This signal

handshakes with AUTOFDÝto transfer data.

SELECT I XFLAG (Xflag): This signal is asserted by the peripheral to indicate that it is on-

line. The status of this signal line is reported in the PSTAT Register.

PERROR I ACKNOWLEDGE REVERSE (AckReverseÝ): PERROR (AckReverseÝ)is

driven low by the peripheral to acknowledge a reverse transfer request by the

host. This signal handshakes with INIT

Ý

(ReverseRequestÝ). The status of this

signal line is reported in the PSTAT Register.

FAULT

Ý

I PERIPHERAL REQUEST (PeriphRequestÝ): The peripheral asserts FAULT

Ý

(PeriphRequestÝ) to request a reverse transfer. The status of this signal line is

reported in the PSTAT Register.

INIT

Ý

O REVERSE REQUEST (ReverseRequestÝ): The host controls this signal via the

PCON Register to indicate the transfer direction. The host asserts this signal to

request a reverse transfer direction and negates the signal for a forward transfer

direction.

AUTOFD

Ý

O HOST ACKNOWLEDGE (HostAck): The 82091AA asserts AUTOFD

Ý

(HostAck) to request data from the peripheral (reverse direction). This signal

handshakes with ACK

Ý

(PeriphClk). AUTOFDÝ(HostAck) is negated when the

peripheral indicates valid state of the data bus (i.e., ACK

Ý

is detected asserted).

In the forward direction, AUTOFDÝ(HostAck) indicates whether PD[7:0]contain

an address/RLE or data. The 82091AA asserts this signal to identify an address/

RLE transfer and negates it to identify a data transfer.

PD[7:0

]

I/O DATA: PD[7:0]is a bi-directional data bus that transfers data, addresses, or RLE

data.

SELECTIN

Ý

O ECP MODE (ECPmode): The host (via the PCON Register) negates this signal

during ECP mode operation.

25

82091AA

2.7 Hard Reset Signal Conditions

Table 1 shows the state of all 82091AA output and bi-directional signals during hard reset (RSTDRV asserted).

The strapping options described in Section 4.0, AIP Configuration are sampled when the 82091AA is hard

reset.

Table 2. Output and I/O Signal States During a Hard Reset

Signal Name State

ACK

Ý

Ð

AEN Ð

AUTOFD

Ý

Tri-state

BUSY Ð

CTS[A,B

]

Ý

Ð

DCD[A,B

]

Ý

High

DEN

Ý

High

(1)

DIR

Ý

High

DRVDEN[1:0]0 Low

DSKCHG

Ý

Ð

DTR[A,B

]

Ý

High

(1)

FAULT

Ý

Ð

FDDACK

Ý

Ð

FDDREQ Tri-state

FDME0Ý/MEEN

Ý

High

FDME1Ý/DSEN

Ý

High

FDS0Ý/MDS0 High

FDS1Ý/MDS1 High

Signal Name State

HDSEL High

HEN

Ý

High

(1)

IDECS[1,0

]

Ý

High

(1)

INDX

Ý

Ð

INIT

Ý

Low

IO16

Ý

Ð

IOCHRDY Tri-state

(2)

IORC

Ý

Ð

IOWC

Ý

Ð

IRQ[7:3

]

Tri-state

NOWS

Ý

Tri-state

PD[7:0

]

Low

PERROR Ð

PPDACK

Ý

Ð

PPDREQ Tri-state

PPDIR/GCS

Ý

High

(1)

RDDATA Ð

RI[A,B

]

Ý

Ð

Signal Name State

RSTDRV Ð

RTS[A,B

]

Ý

High

(1)

SA[10,0

]

Ð

SD[7:0

]

Tri-state

SELECT Ð

SELECTIN

Ý

Tri-state

SIN[A,B

]

Ð

SOUT[A,B

]

High

(1)

STEP

Ý

High

STROBE

Ý

Tri-state

TC Ð

TRK0

Ý

Ð

WE

Ý

High

WP

Ý

Ð

WRDATA

Ý

High

X1/OSC Ð

X2 Ð

NOTES:

1. During and immediately after a hard reset, this signal is an input for hardware configuration. After the hardware configuration time, these signals go to the state specified in the table.

2. If IORC

Ý

or IOWCÝis asserted, IOCHRDY will be asserted by the IOCHRDY.

3. Dashes represent input signals.

26

82091AA

2.8 Power And Ground

Signal

Type Description

Name

V

SS

I GROUND: The ground reference for the 82091AA.

V

CC

I POWER: The 5V/3.3V

(1)

modes are selected via strapping options at power-up (see

Section 4.2, hardware Configuration). When strapping options (V

SEL

) are set to 5V, the

V

CC

pins must be connected to 5V. When strapping options are set to 3.3V, the V

CC

pins must be connected to 3.3V.

V

CCF

I POWER: The 5V/3.3V

(1)

power supply for the 82091AA. In 5V or 3.3V power supply

modes (non-mixed mode), the voltage applied to V

CCF

is the same voltage as applied

to V

CC

.

For mixed mode operations, 5V is applied to V

CCF

. This voltage provides 5V reference

for the parallel port and floppy disk controller interfaces. Note that in mixed mode, 3.3V

is applied to V

CC

.

NOTE:

1. 3.3V operation is available only in the 82091AA.

3.0 I/O ADDRESS ASSIGNMENTS

The 82091AA assigns CPU I/O address locations to

its game port chip select, IDE interface, serial ports,

parallel port, floppy disk controller, and the 82091AA

configuration registers as indicated in Table 3. Except for the game port chip select (address 201h),

address assignments are configurable. For example,

the serial port can be assigned to one of eight address blocks. The parallel port can be assigned to

one of three address blocks, and the IDE interface

and floppy disk controller can be assigned to one of

two address blocks. These address assign-

ments are made during 82091AA configuration (either hardware configuration at powerup or a hard

reset, or software configuration by programming the

82091AA configuration registers). In addition, the

82091AA configuration registers can be located at

one of two address blocks during hardware configuration.

All of the 82091AA address locations are located in

the host I/O address space. The address block assignments are shown in Table 3. The first hex address in the Address Block column represents the

base address for that particular block.

27

82091AA

Table 3. AIP Address Assignments

Address

Assignment

Block (ISA Bus)

170–177h IDE InterfaceÐSecondary Address Block

1F0–1F7h IDE InterfaceÐPrimary Address Block

201h Game Port Chip Select

220–227h Serial Port

228–22Fh Serial Port

238–23Fh Serial Port

26E–26Fh 82091AA Configuration RegistersÐPrimary Address Block (022–023h on X-Bus)

278–27Fh Parallel Port

2E8–2EFh Serial Port

2F8–2FFh Serial Port

338–33Fh Serial Port

370–377h Floppy Disk ControllerÐSecondary Address Block (376h and 377h are Shared with

the IDE Drive Interface Secondary Address)

378–37Fh Parallel Port

398–399h 82091AA Configuration RegistersÐSecondary Address Block (024– 025h on X-Bus)

3BC–3BFh Parallel Port (All Mopes Except EPP)

3E8–3EFh Serial Port

3F0–3F7h Floppy Disk ControllerÐPrimary Address (3F6h and 3F7h are Shared with the IDE

Drive Interface Primary Address)

3F8–3FFh Serial Port

678–67Ah Parallel Port (ECP Mode Peripheral Interface Protocol)

778–77Ah Parallel Port (ECP Mode Peripheral Interface Protocol)

7BC–7BEh Parallel Port (ECP Mode Peripheral Interface Protocol)

NOTES:

1. The 82091AA does not contain IDE registers. However, the 82091AA provides the address block assignments for accessing the IDE registers that are located in the IDE device.

2. The standard PC/AT* compatible logical I/O address assignments are supported. For example, COM1 (3F8 –3FFh) and

COM2 (2F8–2FFh) are part of the serial port assignments and LPT1 (3BC–3BFh), LPT2 (378 – 37Fh), and LPT3

(278–27Fh) are part of the parallel port assignments.

*Other brands and names are the property of their respective owners.

28

82091AA

4.0 AIP CONFIGURATION

82091AA configuration consists of setting up overall

device operations along with certain functions

pertaining to the individual 82091AA modules

(parallel port, serial ports, floppy disk controller, and

IDE interface). Overall device operations include

selecting the clock frequency, power supply voltage,

and address assignment for the configuration

registers. Overall device operations also enable/

disable access to the configuration registers and

provide interrupt signal level control. For the

individual modules, 82091AA configuration includes

module address assignment, interrupt control,

module enable/disable, powerdown control, test

mode control, module reset, and certain functions

specific to each module. The remainder of the

functions unique to each module are handled via the

individual module registers.

Two methods are provided for configuring the

82091AAÐhardware configuration via strapping options at powerup (or whenever RSTDRV is asserted)

and software configuration by programming the configuration registers. (For information on hardware

configuration, see Section 4.2, Hardware Configuration. For information on software configuration, see

Section 4.1, Configuration Registers.)

NOTE:

1. There are four hardware configuration

modesÐSWMB (Software Motherboard),

SWAI (Software Add-In), HWB (Hardware

Basic), and HWE (Hardware Extended).

Some of these modes can be used without

the need for programming the 82091AA

configuration registers. Other modes use

both hardware configuration strapping options and programming the configuration

registers to set up the 82091AA.

2. The 82091AA’s operating power supply

voltage level, 82091AA clock frequency,

and address assignment for the 82091AA

configuration registers can only be configured by hardware configuration.

4.1 Configuration Registers

82091AA Configuration Space contains 13 configuration registers. Four of the registers (Product and

Revision Identification Registers and the 82091AA

Configuration 1 and 2 Registers) provide control and

status information for the entire chip. In addition, two

registers each for the floppy disk controller, parallel

port, serial port A, and serial port B and one register

for the IDE interface provide certain module status

and control information. The 82091AA configuration

registers are indirectly addressed by first writing to

the 82091AA Configuration Index Register as described in Section 4.1.1. Thus, the 13 configuration

registers occupy two address locations in the host’s

I/O address spaceÐone for indirectly selecting the

specific configuration register and the other for

transfering register data. All 82091AA configuration

registers are 8-bits wide and are accessed as byte

quantities.

Some of the 82091AA Configuration registers described in this section contain reserved bits. These

bits are labeled ‘‘R’’. Software must deal correctly

with fields that are reserved. On reads, software

must use appropriate masks to extract the defined

bits and not rely on reserved bits being any particular value. On writes, software must ensure that the

values of reserved bit positions are preserved. That

is, the value of reserved bit positions must first be

read, merged with the new values for other bit positions, and then written back.

In addition to reserved bits within a register, the

82091AA configuration space contains address locations that are labeled ‘‘Reserved’’ (Table 5). While

the 82091AA responds to accesses to these I/O addresses by completing the host cycle, writing to a

reserved I/O address can result in unintended device operations. Values read from a reserved I/O

address should not be used to permit future expansion and upgrades.

During a hard reset (RSTDRV asserted), the

82091AA sets its configuration registers to pre-determined default states. The default values are indicated in the individual register descriptions. The following nomenclature is used for register access attributes:

RO Read Only. If a register is read only, writes

have no effect.

R/W Read/Write. A register with this attribute can

be read and written. Note that individual bits in

some read/write registers may be read only.

29

82091AA

4.1.1 CFGINDX, CFGTRGTÐCONFIGURATION INDEX REGISTER AND TARGET PORT

I/O Address: Hardware Configurable (see Table 4)

Default Value: 00h

Attribute: Read/Write

Size: 8 bits