Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent

licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel.

© INTEL CORPORATION, 1995 September 1995 Order Number: 272543-001

®

8XC196MH INDUSTRIAL MOTOR CONTROL

CHMOS MICROCONTROLLER

The 8XC196MH is a member of Intel’s family of 16-bit MCS® 96 microcontrollers. It is designed primarily to

control three-phase AC induction and DC brushless motors. It features an enhanced three-phase waveform

generator specifically designed for use in “inverter” motor-control applications. This peripheral provides pulsewidth modulation and three-phase sine wave generation with minimal CPU intervention. It generates three

complementary non-overlapping PWM pulses with resolutions of 0.125 µs (edge triggered) or 0.250 µs

(centered).

The 8XC196MH has two dedicated serial port peripherals, allowing less software overhead. The watchdog timer

can be programmed with one of four time options.

The 8XC196MH is available without internal memory (80C196MH), with 32 Kbytes of factory programmed

OTPROM* (83C196MH), or with 32 Kbytes of user programmable OTPROM* (87C196MH). It is available in

three packages: 84-lead PLCC, 80-lead Shrink EIAJ/QF P, and 64-lead SDIP. The 64-lead package does not

contain pins for the P5.1/INST and P6.7/PWM1 signals.

Operational characteristics are guaranteed over the temperat ure range of

– 40°C to + 85°C.

*One-Time Programmable Read-Only Memory (OTPROM) is similar to EPROM but comes in an unwindowed package and

cannot be erased. It is user programmable.

n

High Performance CHMOS 16-bit CPU

n

16 MHz Operating Frequency

n

32 Kbytes of On-chip OTPROM/RO M

n

744 Bytes of On-chip Register RAM

n

Register-to-register Archi tectu re

n

16 Prioritized Interrupt Sources

n

Peripheral Transaction Server (PTS) with 15

Prioritized Sources

n

Up to 52 I/O Lines

n

3-phase Complementary Waveform Generator

n

8-channel 8- or 10-bit A/D with Samp l e and

Hold

n

2-channel UART

n

Event Processor Array (EPA) with 2 Highspeed Capture/Com pare Mo d ules an d 4 Highspeed Compare-only Modules

n

Two Programmable 16-bit Timers with

Quadrature Countin g Input s

n

Two Pulse-width Modulator (PWM) Outputs

with High Drive Capability

n

Flexible 8- or 16-bit External Bus

n

1.75 µs 16 × 16 Multipl y

n

3 µs 32/16 Divide

n

Extended Temperature Avai lab le

n

Idle and Powerdo w n Mod es

n

Watchdog Timer

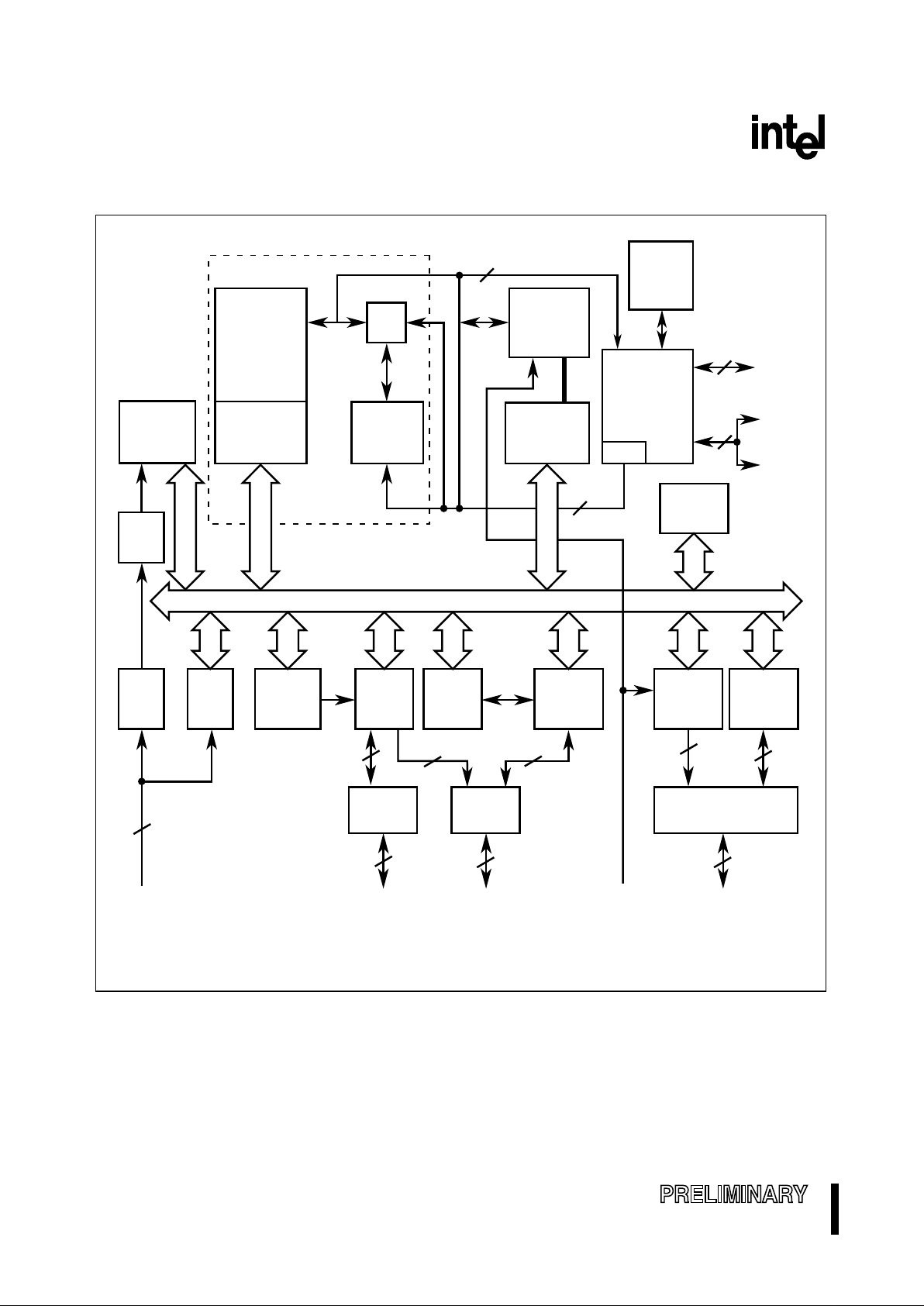

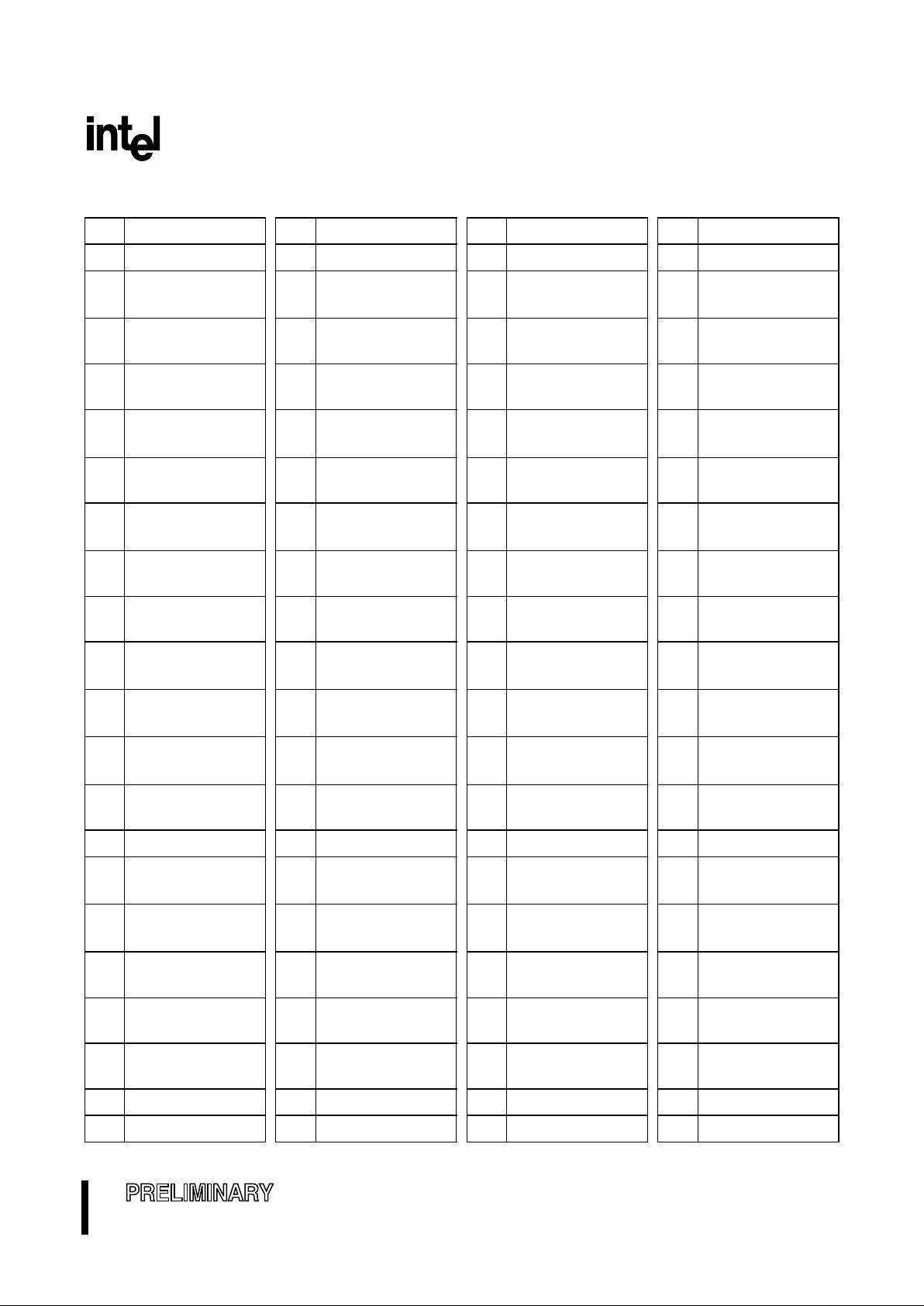

8XC196MH INDUSTRIAL MOTO R CONTRO L CHMO S MICRO CO NTR OLL ER

®

2

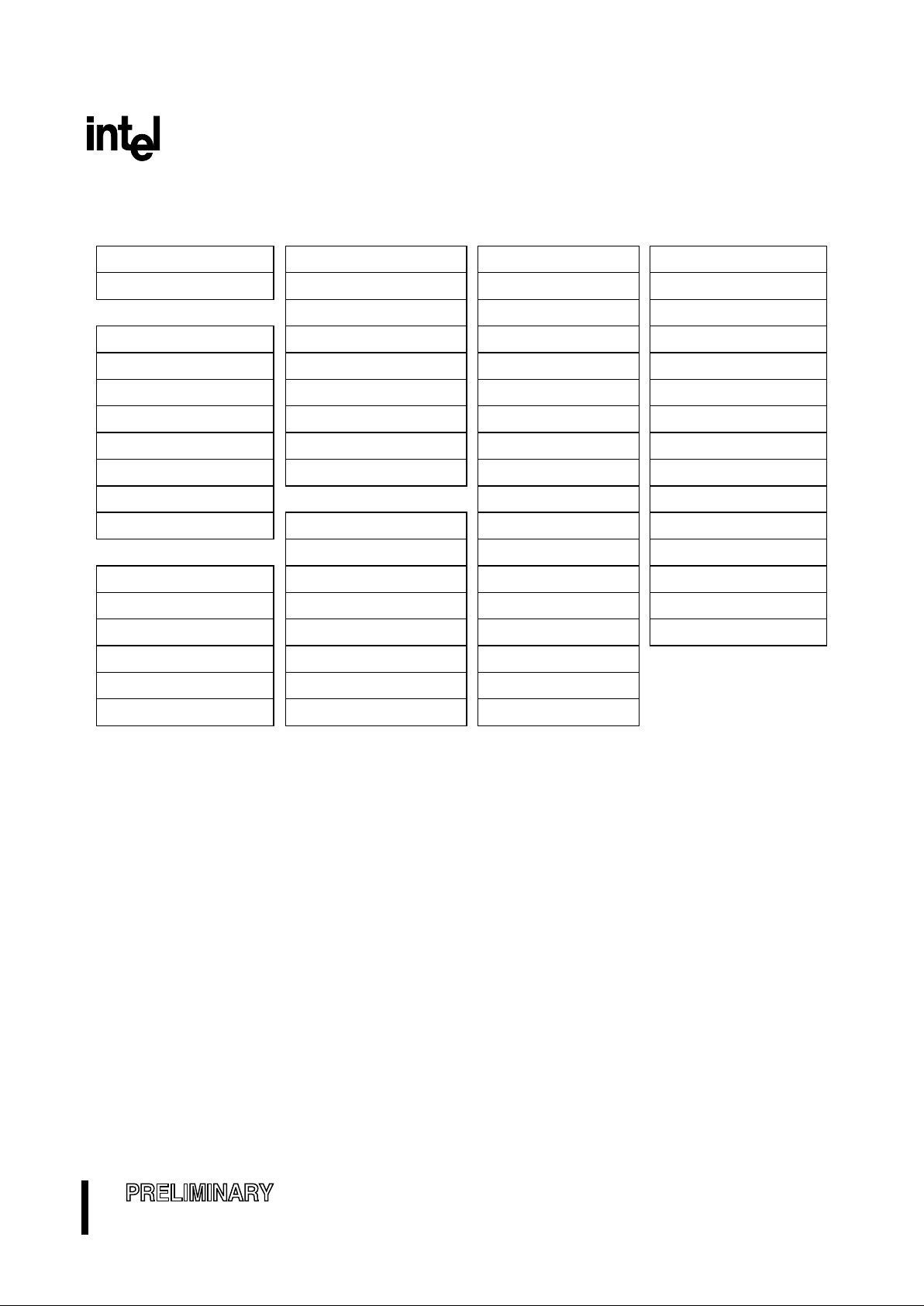

Figure 1. 8XC196MH Block Diagram

Timer 1

Timer 2

Event

Processor

Array

3-Phase

Waveform

Generator

Port 2

Microcode

Engine

RALU

CPU

Peripheral

Transaction

Server

32K

On-chip

ROM/

OTPROM

Port 4

AD15:8

Port 3

AD7:0

Port 5

Control

Signals

Interrupt

Controller

16

8

744

Byte

Register

File

Memory

Controller

Queue

Port 6

Port 6

Waveform

Generator

A2542-01

Port 2

SIO, EPA

2 Capture/Compare

4 Compare

Port 1

SIO 0

SIO 1

Port 1

Serial I/O

Baud

Rate

Generator

Port 0

A/D

Port 0

8/10-Bit

A/D

Converter

Mux

S/H

24 Bytes

CPU SFRs

Watchdog

Timer

EXTINT

PWM0

PWM1

88

4

4

26

8

6

2

8

8

8XC196MH INDUSTRIAL MOTOR CONT ROL CHM OS MICRO CO NTR OLL ER

®

3

PROCESS INFORMATION

This device is manufactured on PX29.5, a CHMOS IV

process. Additional process and reliability information

is available in Intel’s

Components Quality and

Reliability

Handbook (order number 210997).

All thermal impedance data is approximate for static

air conditions at 1 watt of power dissipation. Values

will change depending on operating conditions and

the application. The Intel

Packaging

Handbook (order

number 240800) describes I ntel’s thermal impedance

test methodology.

Table 1. Thermal Characteristics

Package Type θ

JA

θ

JC

84-lead PLCC 33°C/W 11°C/W

80-lead QFP 56°C/W 12°C/W

64-lead SDIP 56°C/W N/A

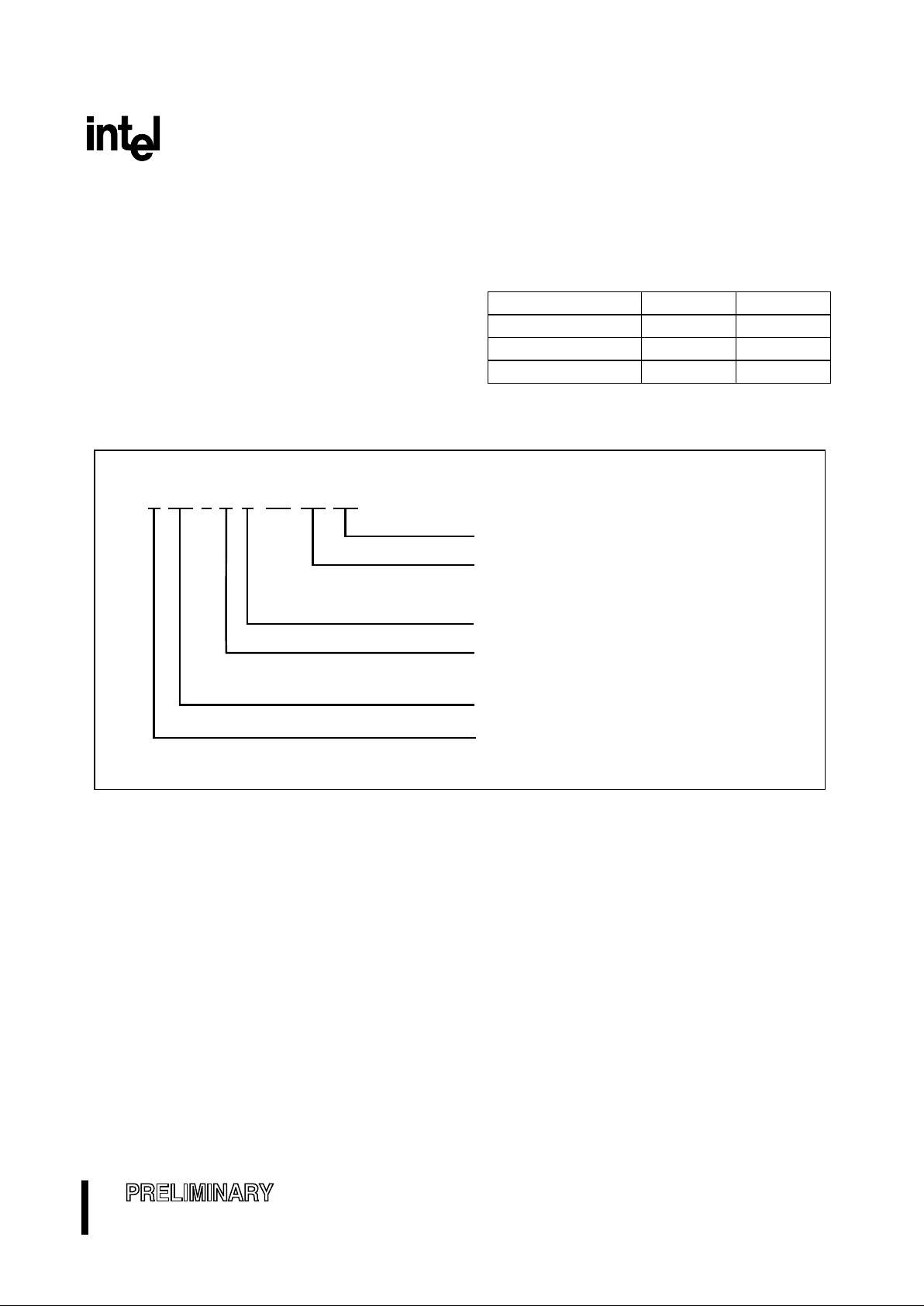

Figure 2. The 8XC196MH Family Nomenclat ure

X XX 8 X C 196 XX XX

Device Speed:

Product Family:

No Mark = 16 MHz

K

x

, Mx, N

x

CHMOS Technology

Program Memory Options:

0 = ROMless, 3 = ROM, 7 = OTPROM

Package - Type Options:

Temperature and Burn In Options:

A2759-01

D = SDIP, N = PLCC, S = QFP

No Mark = –40˚C – +85˚C Ambient

with Intel Standard Burn-In

8XC196MH INDUSTRIAL MOTO R CONTRO L CHMO S MICRO CO NTR OLL ER

®

4

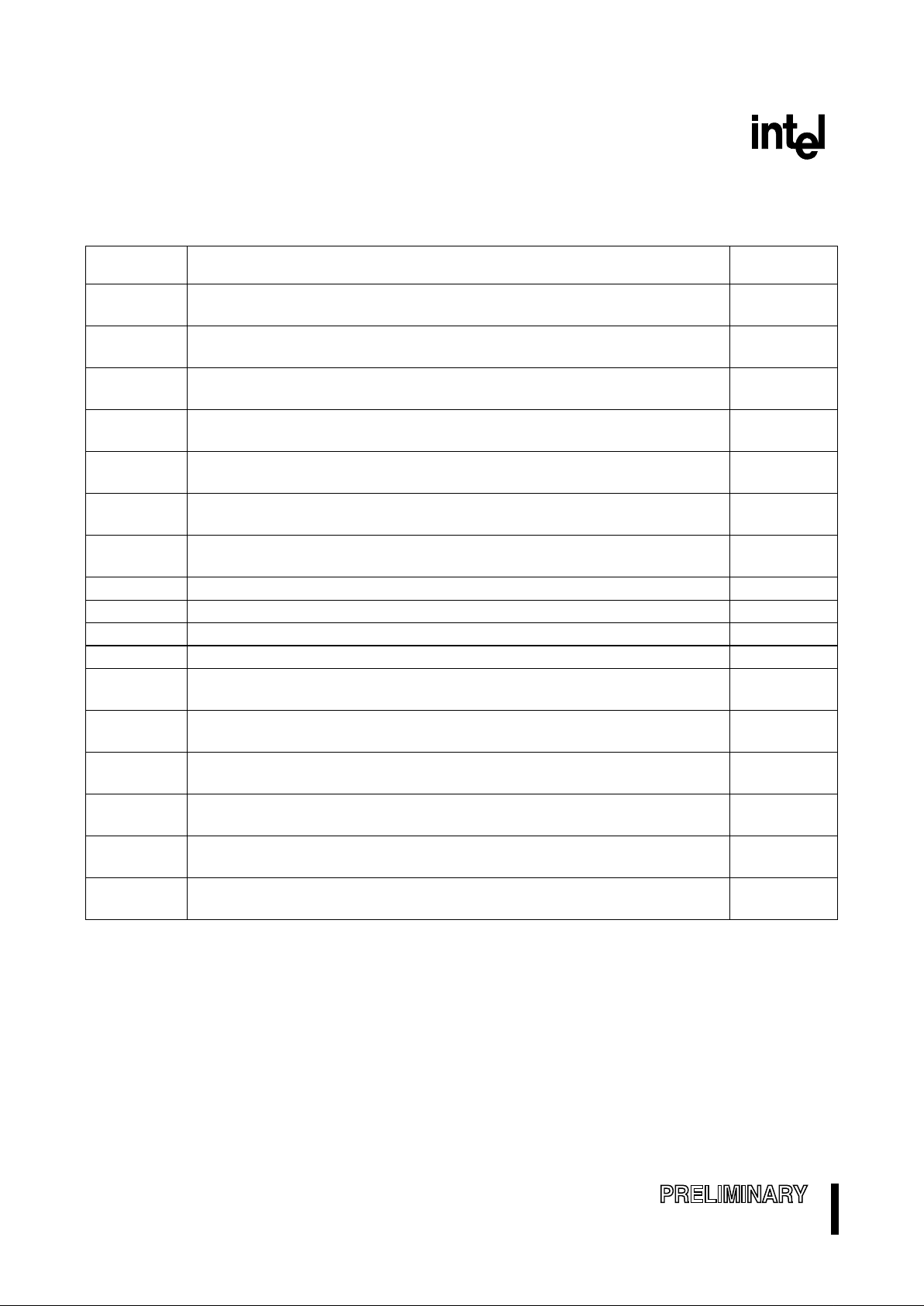

Table 2. 8XC196MH Memory Map

Address

(1)

Description Notes

0FFFFH

0A000H

External Memory

09FFFH

02080H

Internal ROM/OTPROM or External Mem ory

0207FH

0205EH

Reserved 1, 2

0205DH

02040H

PTS Vectors

0203FH

02030H

Interrupt Vectors (upper)

0202FH

02020H

ROM/OTPROM Security Key

0201FH

0201CH

Reserved 1, 2

0201BH Reserved (must contain 20H)

0201AH CCB1

02019H Reserved (must contain 20H)

02018H CCB0

02017H

02014H

Reserved

02013H

02000H

Interrupt Vectors (lower)

01FFFH

01F00H

Internal SFRs 1

1EFFH

300H

External Memory

2FFH

18H

Register RAM 3

17H

00H

CPU SFRs 1

NOTES:

1. Unless otherwise noted, write 0FFH to reserved mem ory locations and write 0 to reserved SFR bits.

2. WARNING: The contents and/or func tion of reserved locations may change with future revisions of the

device.

3. Code executed in locations 0000H to 02FFH will be forced external.

8XC196MH INDUSTRIAL MOTOR CONT ROL CHM OS MICRO CO NTR OLL ER

®

5

Table 3. Signals Arranged by Fun cti onal Categ ori e s

Address & Data Programming Control Input/Output Input/Output (Cont’d)

AD15:0 AINC# P0.0/ACH0 P2.5/COMP1

CPVER P0.1/ACH1 P2.6/COMP2

Bus Control & Status PACT# P0.2/ACH2 P2.7/SCLK1#/BCLK1

ALE/ADV# PALE# P0.3/ACH3 P3.7:0

BHE#/WRH# PBUS15:0 P0.4/ACH4 P4.7:0

BUSWIDTH PMODE.3:0 P0.5/ACH5 P5.7:0

INST PROG# P0.6/ACH6/T1CLK P6.0/WG1#

READY PVER P0.7/ACH7/T1DIR P6.1/WG1

RD# P1.0/TXD0 P6.2/WG2#

WR#/WRL# Processor Control P1.1/RXD0 P6.3/WG2

EA# P1.2/TXD1 P6.4/WG3#

Power & Ground EXTINT P1.3/RXD1 P6.5/WG3

ANGND NMI P2.0/EPA0 P6.6/PWM0

V

CC

ONCE# P2.1/SCLK0#/BCLK0 P6.7/PWM1

V

PP

RESET# P2.2/EPA1

V

REF

XTAL1 P2.3/COMP3

V

SS

XTAL2 P2.4/COMP0

NOTE: The following signals are not available in the 64-pin package: P5.1, P6.7, INST, and PWM1.

8XC196MH INDUSTRIAL MOTO R CONTRO L CHMO S MICRO CO NTR OLL ER

®

6

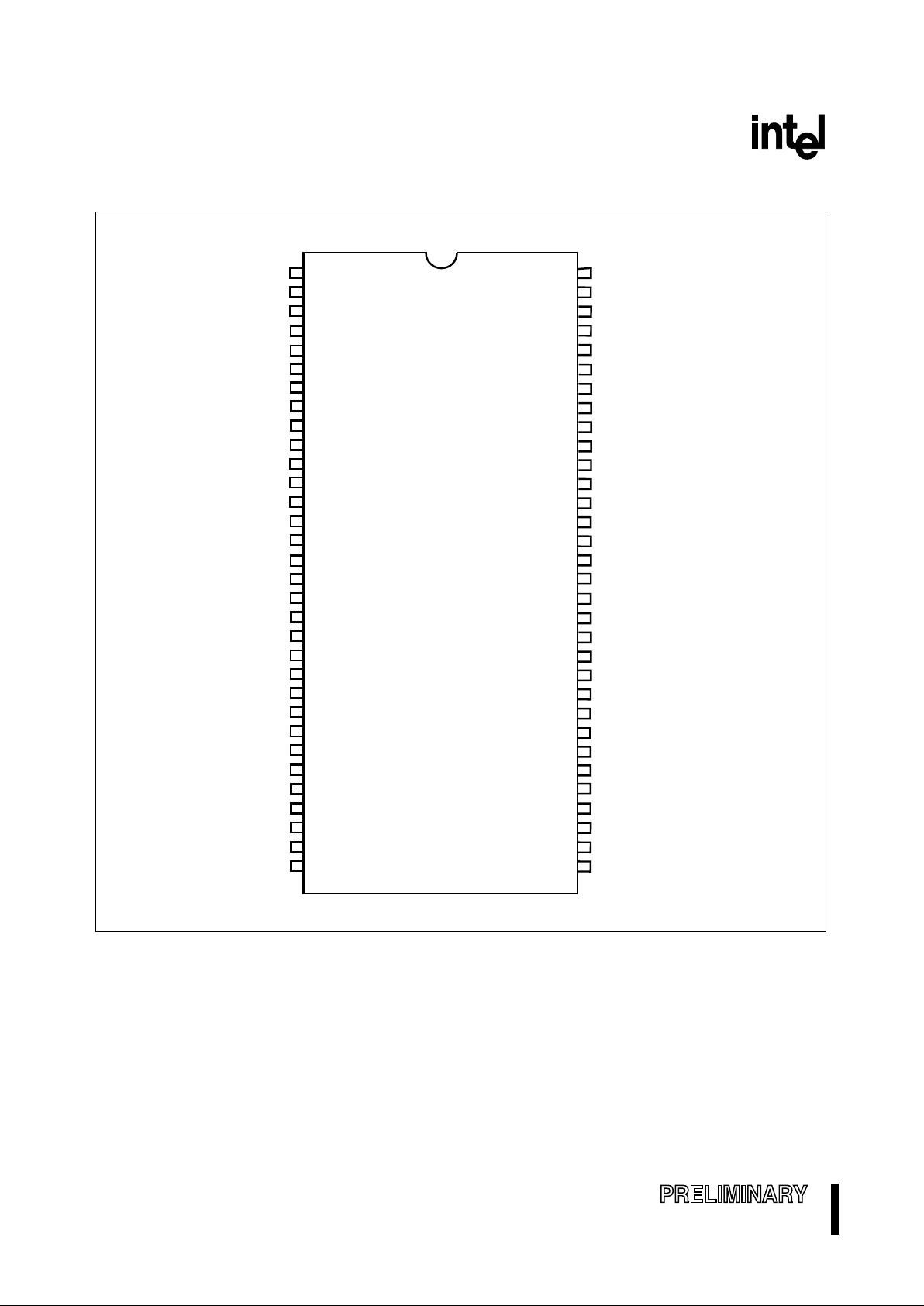

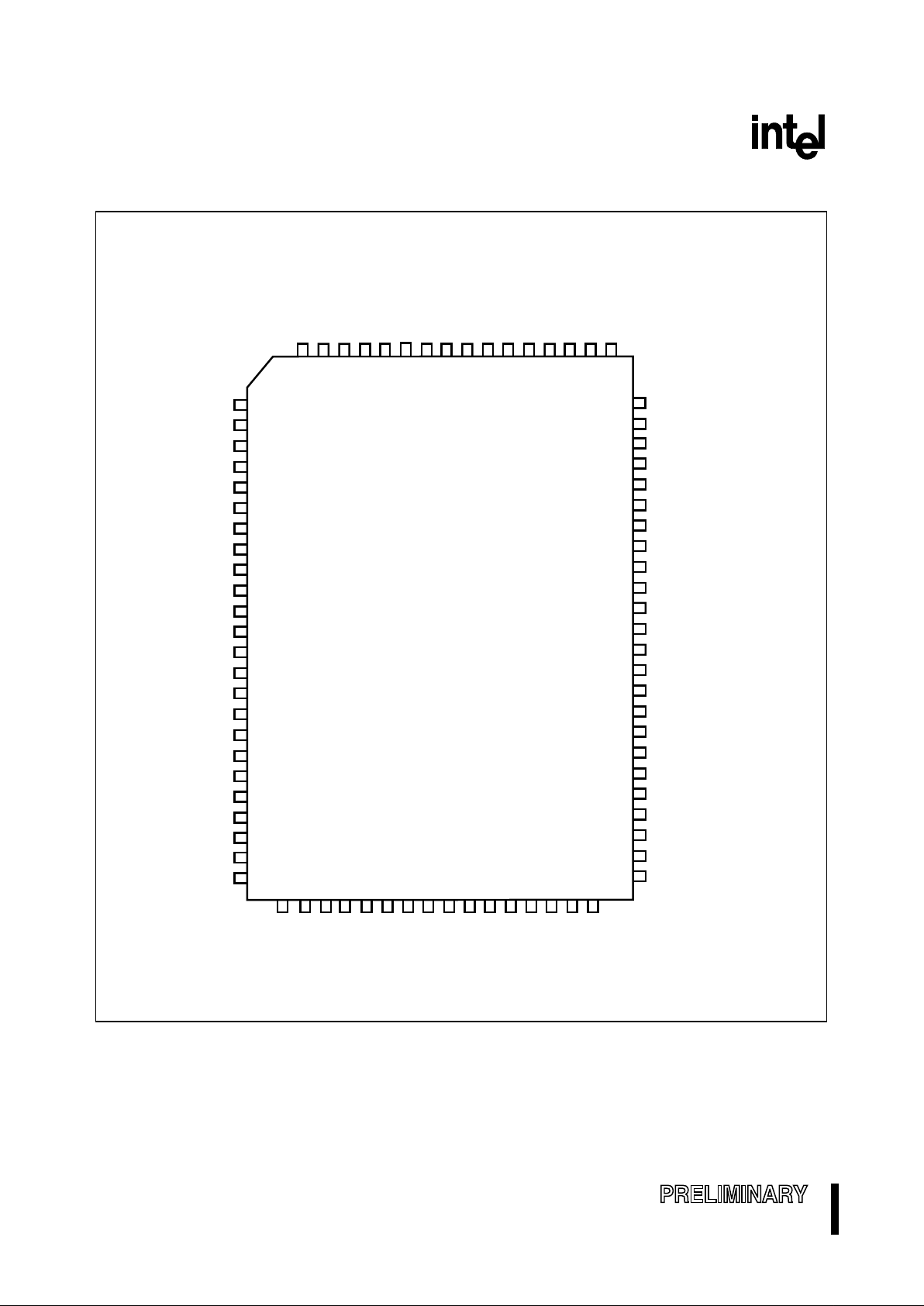

Figure 3. 8XC196MH 64-lead Shrink DIP (SDIP) Package

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

U8XC196MH

TOP VIEW

(Looking down

on component side of

PC board)

P5.6/READY

P5.4/ONCE#

EXTINT

V

SS

XTAL1

XTAL2

P6.6/PWM0

P2.7/SCLK1#/BCLK1

P2.6/COMP2/CPVER

P2.5/COMP1/PACT#

P2.4/COMP0/AINC#

P2.3/COMP3

P2.2/EPA1/PROG#

P2.1/SCLK0#/BCLK0/PALE#

P2.0/EPA0/PVER

P0.0/ACH0

P0.1/ACH1

P0.2/ACH2

P0.3/ACH3

P0.4/ACH4/PMODE.0

P0.5/ACH5/PMODE.1

V

REF

ANGND

P0.6/ACH6/T1CLK/PMODE.2

P0.7/ACH7/T1DIR/PMODE.3

P1.0/TXD0

P1.1/RXD0

P1.2/TXD1

P1.3/RXD1

P6.0/WG1#

P6.1/WG1

P6.2/WG2#

V

SS

P5.0/ALE/ADV#

V

PP

P5.3/RD#

P5.5/BHE#/WRH#

P5.2/WR#/WRL#

P5.7/BUSWIDTH

P4.6/AD14/PBUS.14

P4.5/AD13/PBUS.13

P4.7/AD15/PBUS.15

V

CC

P4.4/AD12/PBUS.12

P4.3/AD11/PBUS.11

P4.2/AD10/PBUS.10

P4.1/AD9/PBUS.9

P4.0/AD8/PBUS.8

P3.7/AD7/PBUS.7

P3.6/AD6/PBUS.6

P3.5/AD5/PBUS.5

P3.4/AD4/PBUS.4

P3.3/AD3/PBUS.3

P3.2/AD2/PBUS.2

P3.1/AD1/PBUS.1

P3.0/AD0/PBUS.0

RESET#

NMI

EA#

V

SS

V

CC

P6.5/WG3

P6.4/WG3#

P6.3/WG2

A2572-01

8XC196MH INDUSTRIAL MOTOR CONT ROL CHM OS MICRO CO NTR OLL ER

®

7

Table 4. 64-lead Shrink DIP (SDI P) Pi n Assi gnme nt

Pin Name Pin Name Pin Name Pin Name

1V

SS

17 P3.7/AD7

/PBUS.7

33 P6.2/WG2# 49 P0.0/A C H0

2 P5.0/A LE/ADV# 18 P3.6/AD6

/PBUS.6

34 P6.1/WG1 50 P2.0/EPA0/PVER

3V

PP

19 P3.5/AD5

/PBUS.5

35 P6.0/WG1# 51 P2.1/SCLK0#

/BCLK0/PALE#

4 P5.3/RD# 20 P3.4/AD4

/PBUS.4

36 P1.3/RXD1 52 P2.2/EPA1

/PROG#

5 P5.5/B HE#/WRH# 21 P3.3/AD3

/PBUS.3

37 P1.2/TXD1 53 P2. 3/CO M P3

6 P5.2/W R#/WRL# 22 P3.2/AD2

/PBUS.2

38 P1.1/RXD0 54 P2.4/COMP0

/AINC#

7 P5.7/B USW I DTH 23 P3.1/AD1

/PBUS.1

39 P1.0/TXD0 55 P2. 5/CO M P1

/PACT#

8 P4.6/A D 14

/PBUS.14

24 P3.0/AD0

/PBUS.0

40 P0.7/ACH7/T1DIR

/PMODE.3

56 P2.6/COMP2

/CPVER

9 P4.5/A D 13

/PBUS.13

25 RESET# 41 P0.6/ACH6

/T1CLK/PMODE .2

57 P2.7/SCLK1#

/BCLK1

10 P4.7/AD15

/PBUS.15

26 NMI 42 ANGND 58 P6.6/PWM0

11 V

CC

27 EA# 43 V

REF

59 XTAL2

12 P4.4/AD12

/PBUS.12

28 V

SS

44 P0.5/ACH5

/PMODE.1

60 XTAL1

13 P4.3/AD11

/PBUS.11

29 V

CC

45 P0.4/ACH4

/PMODE.0

61 V

SS

14 P4.2/AD10

/PBUS.10

30 P6.5/WG3 46 P0.3/ACH3 62 EXTINT

15 P4.1/AD9/PBUS.9 31 P6.4/WG3# 47 P0.2/ACH2 63 P5.4/ONCE#

16 P4.0/AD8/PBUS.8 32 P6.3/WG2 48 P0.1/ACH1 64 P5.6/READY

8XC196MH INDUSTRIAL MOTO R CONTRO L CHMO S MICRO CO NTR OLL ER

®

8

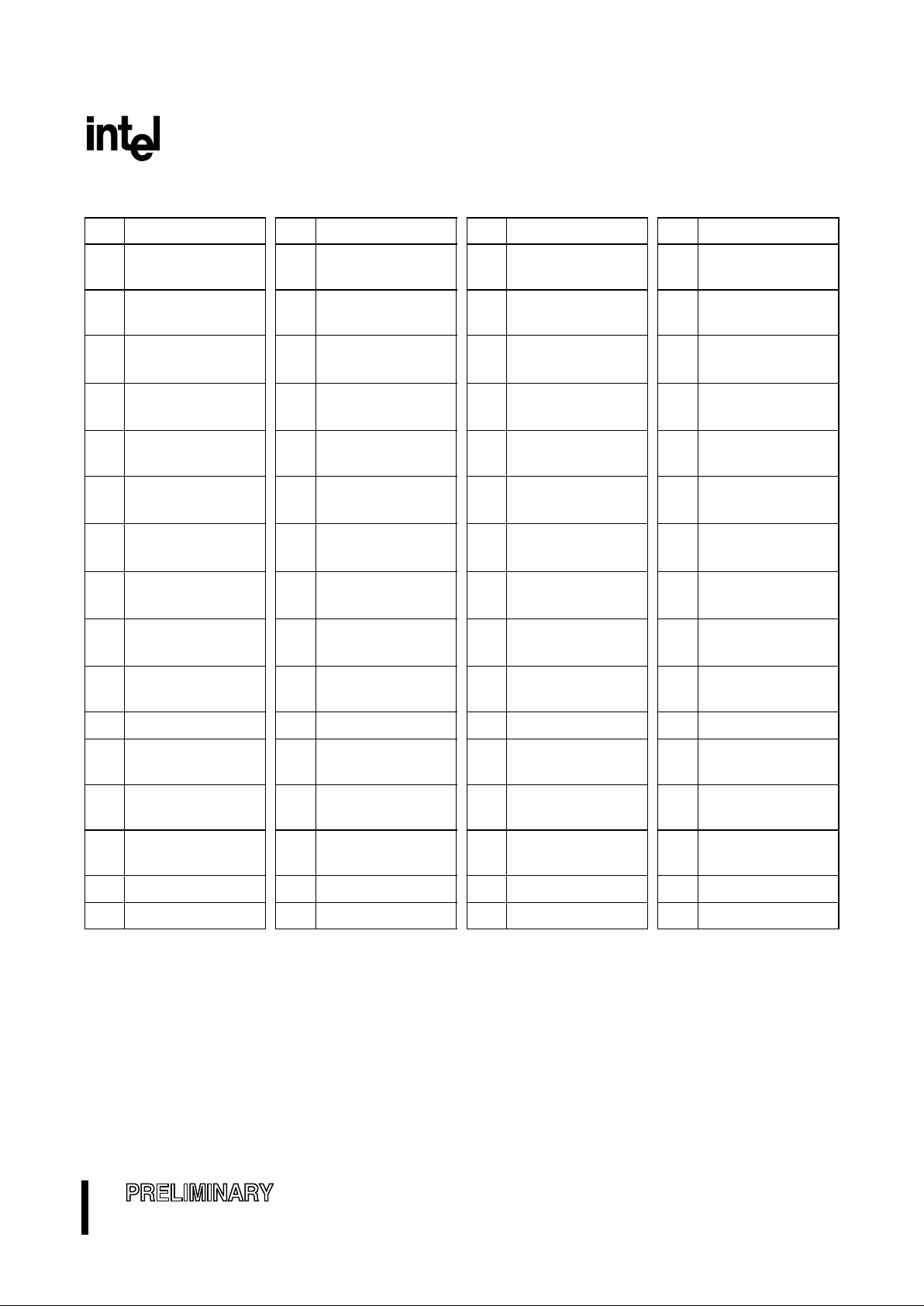

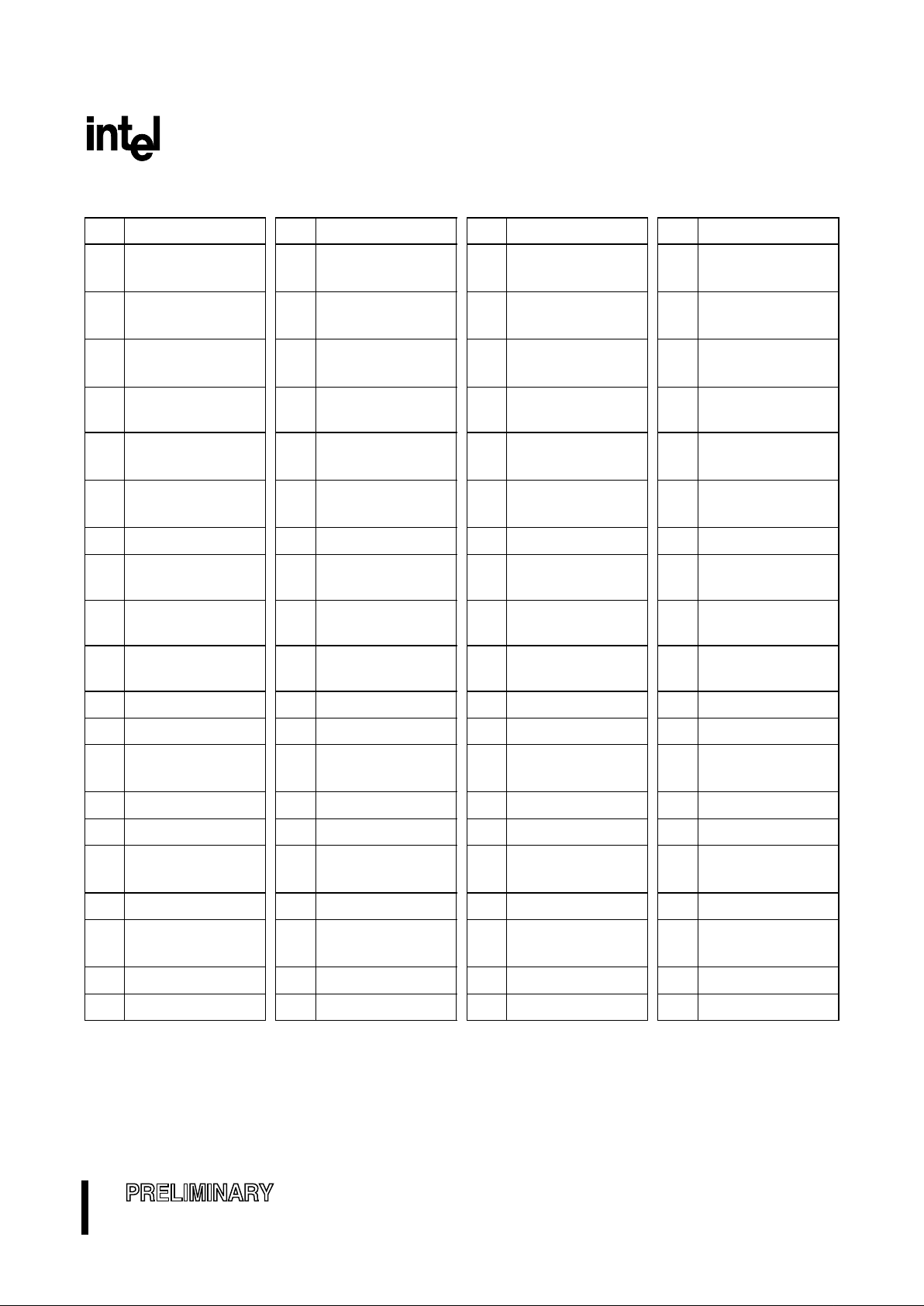

Figure 4. 8XC196MH 84-lead PLCC Package

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

11

10

987654321

84

83

82

81

80

79

78

77

76

75

P2.5/COMP1/PACT#

P2.4/COMP0/AINC#

NC

NC

P2.7/SCLK1#/BCLK1

P2.3/COMP3

P2.2/EPA1/PROG#

NC

NC

P2.1/SCLK0#/BCLK0/PALE#

P2.0/EPA0/PVER

NC

P0.0/ACH0

P0.1/ACH1

P0.2/ACH2

P0.3/ACH3

P0.4/ACH4/PMODE.0

P0.5/ACH5/PMODE.1

V

REF

ANGND

P0.6/ACH6/T1CLK/PMODE.2

P4.7/AD15/PBUS.15

P4.6/AD14/PBUS.14

VCC

P4.5/AD13/PBUS.13

NC

P4.4/AD12/PBUS.12

P4.3/AD11/PBUS.11

P4.2/AD10/PBUS.10

P4.1/AD9/PBUS.9

P4.0/AD8/PBUS.8

NC

NC

P3.7/AD7/PBUS.7

P3.6/AD6/PBUS.6

P3.5.AD5/PBUS.5

P3.4/AD4/PBUS.4

P3.3/AD3/PBUS.3

P3.2/AD2/PBUS.2

P3.1/AD1/PBUS.1

P3.0/AD0/PBUS.0

NC

P5.7/BUSWIDTH

P5.2/WR#/WRL#

NC

P5.5/BHE#/WRH#

P5.3/RD#

V

PP

P5.0/ALE/ADV#

V

SS

P5.1/INST

P5.6/READY

P5.4/ONCE#

EXTINT

V

SS

XTAL1

XTAL2

NC

NC

NC

P6.6/PWM0

P6.7/PWM1

P2.6/COMP2/CPVER

RESET#

NMI

NC

EA#

V

SS

NCVCC

P6.5/WG3

P6.4/WG3#

P6.3/WG2

V

SS

P6.2/WG2#

P6.1/WG1

P6.0/WG1#

P1.3/RXD1

P1.2/TXD1

NC

NC

P1.1/RXD0

P1.0/TXD0

P0.7/ACH7/T1DIR/PMODE.3

N8XC196MH

TOP VIEW

(Looking down

on component side of

PC board)

A2573-02

8XC196MH INDUSTRIAL MOTOR CONT ROL CHM OS MICRO CO NTR OLL ER

®

9

Table 5. 84-lead PLCC Pin Assig nme nt

Pin Name Pin Name Pin Name Pin Name

1 P5.4/ONCE# 22NC 43V

SS

64 P2.0/EPA0/PVER

2 P5.6/RE ADY 23 NC 44 P6.2/WG2# 65 P2.1/SCLK0#

/BCLK0/PALE#

3 P5.1/INST 24 P3.7/AD7

/PBUS.7

45 P6.1/WG1 66 NC

4V

SS

25 P3.6/AD6

/PBUS.6

46 P6.0/WG1# 67 NC

5 P5.0/ALE/ADV# 26 P3.5/AD5

/PBUS.5

47 P1.3/RXD1 68 P2.2/EPA1

/PROG#

6V

PP

27 P3.4/AD4

/PBUS.4

48 P1.2/TXD1 69 P2. 3/CO M P3

7 P5.3/RD# 28 P3.3/AD3

/PBUS.3

49 NC 70 P2.7/SCLK1#

/BCLK1

8 P5.5/BHE#/WRH# 29 P3.2/AD2

/PBUS.2

50 NC 71 NC

9 NC 30 P3.1/AD1

/PBUS.1

51 P1.1/RXD0 72 NC

10 P5.2/WR#/WRL # 31 P3.0/AD0

/PBUS.0

52 P1.0/TXD0 73 P2. 4/CO M P0

/AINC#

11 P5.7/BUSWIDTH 32 NC 53 P0.7/ACH7

/T1DIR/PMODE. 3

74 P2.5/COMP1

/PACT#

12 P4.7/AD15

/PBUS.15

33 RESET# 54 P0.6/ACH6

/T1CLK/PMOD E.2

75 P2.6/COMP2

/CPVER

13 P4.6/AD14

/PBUS.14

34 NMI 55 ANGND 76 P6.7/PWM1

14 V

CC

35 NC 56 V

REF

77 P6.6/PWM0

15 P4.5/AD13

/PBUS.13

36 EA# 57 P0.5/ACH5

/PMODE.1

78 NC

16 NC 37 V

SS

58 P0.4/ACH4

/PMODE.0

79 NC

17 P4.4/AD12

/PBUS.12

38 NC 59 P0.3/ACH3 80 NC

18 P4.3/AD11

/PBUS.11

39 V

CC

60 P0.2/ACH2 81 XTAL2

19 P4.2/AD10

/PBUS.10

40 P6.5/WG3 61 P 0.1/ ACH1 82 XTAL1

20 P4.1/AD9/PBUS.9 41 P6.4/WG3 # 62 P0.0/ ACH0 83 V

SS

21 P4.0/AD8/PBUS.8 42 P6.3/WG 2 63 NC 84 EXTINT

8XC196MH INDUSTRIAL MOTO R CONTRO L CHMO S MICRO CO NTR OLL ER

®

10

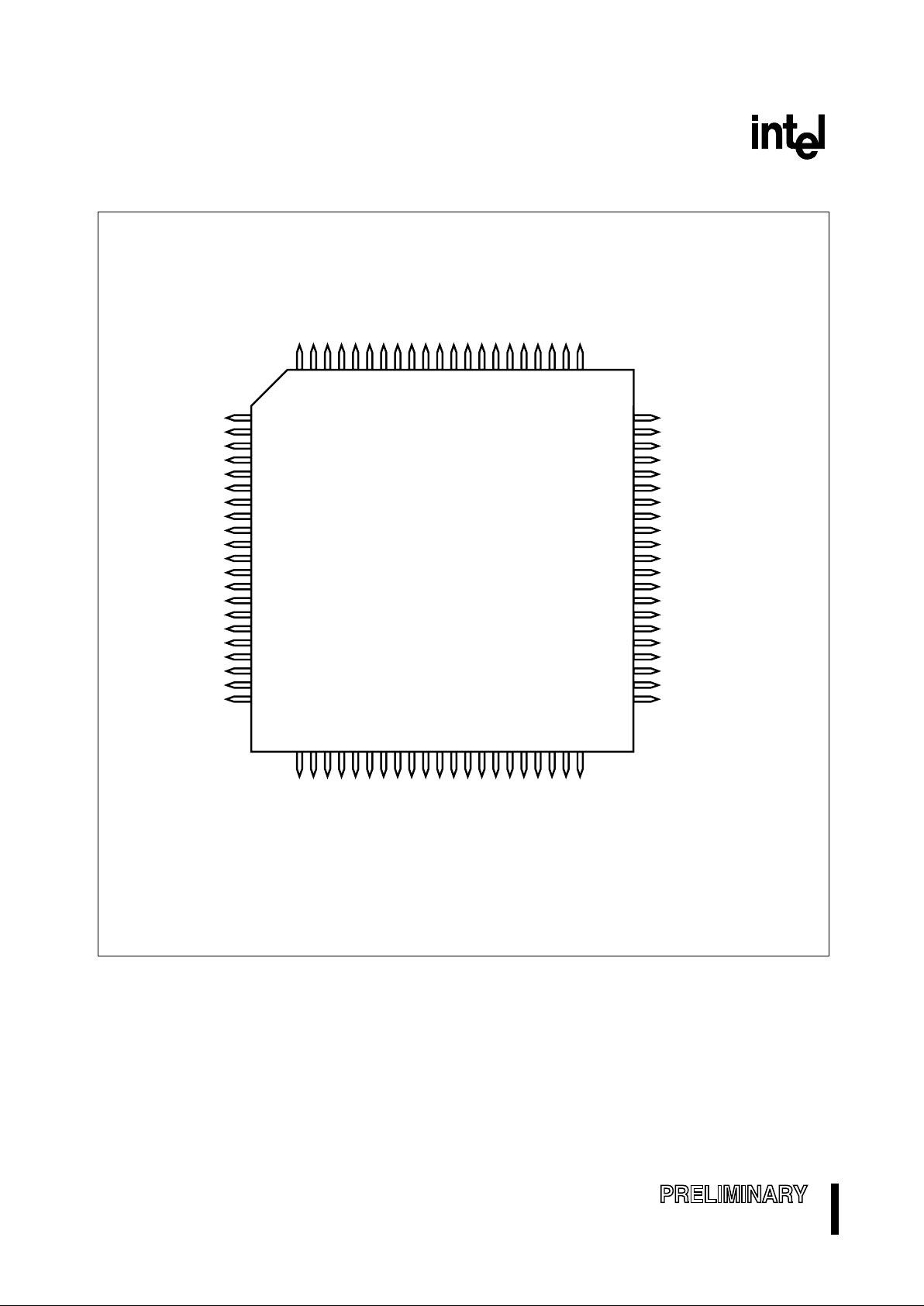

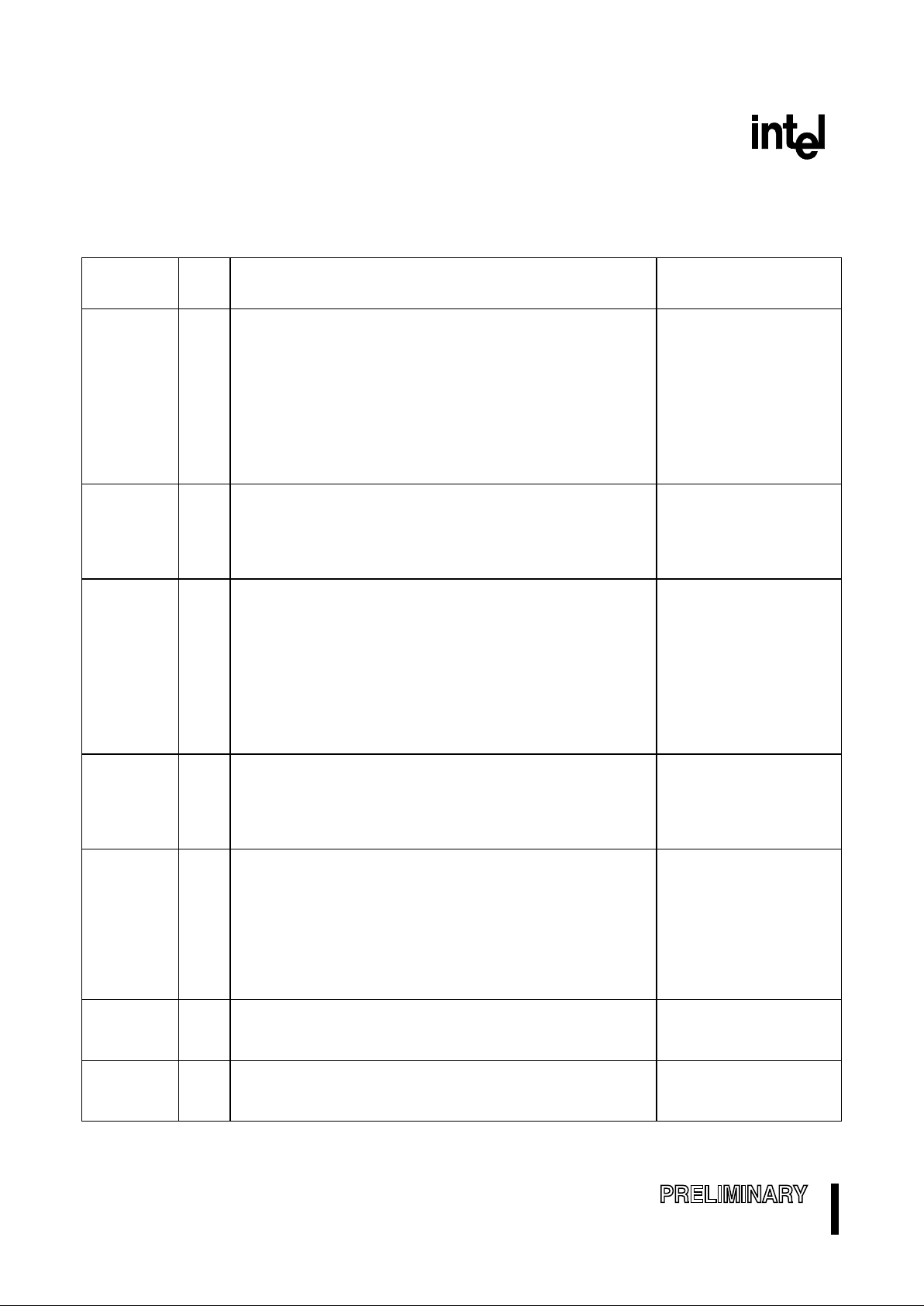

Figure 5. 8XC196MH 80-lead Shrink EIAJ/Q FP Packag e

1

2

3

4

5

6

7

8

9

10

12

17

13

14

16

18

19

11

15

20

21

24

25 26 28 2927

23

22

3938

37343230 31 33 35

36

40

42

41

43

44

45

46

47

48

49

52

53

50

51

55

54

56

57

59

58

60

61

62

63

64

65

6667

68

6973747679 77

75

72 71 70

80

78

P6.7/PWM1

P2.6/COMP2/CPVER

P2.5/COMP1/PACT#

P2.4/COMP0/AINC#

NC

NC

P2.7/SCLK1#/BCLK1

P2.3/COMP3

P2.2/EPA1/PROG#

P2.0/EPA0/PVER

NC

NC

P0.6/ACH6/T1CLK/PMODE.2

NC

P2.1/SCLK0#/BCLK0/PALE#

ANGND

P0.0/ACH0

P0.1/ACH1

P0.2/ACH2

P0.3/ACH3

P0.4/ACH4/PMODE.0

V

REF

P0.5/ACH5/PMODE.1

P0.7/ACH7/T1DIR/PMODE.3

P4.7/AD15/PBUS.15

P5.2/WR#/WRL#

P5.7/BUSWIDTH

P4.6/AD14/PBUS.14

V

CC

P4.5/AD13/PBUS.13

NC

P4.3/AD11/PBUS.11

P4.4/AD12/PBUS.12

P4.2/AD10/PBUS.10

P3.7/AD7/PBUS.7

P4.1/AD9/PBUS.9

P4.0/AD8/PBUS.8

P3.6/AD6/PBUS.6

P3.4/AD4/PBUS.4

P3.3/AD3/PBUS.3

P3.1/AD1/PBUS.1

P3.0/AD0/PBUS.0

NMI

NC

EA#

RESET#

P3.5/AD5/PBUS.5

P3.2/AD2/PBUS.2

V

SS

NC

P6.4/WG3#

P6.1/WG1

V

CC

P6.5/WG3

P6.3/WG2

V

SS

P6.2/WG2#

P1.3/RXD1

P6.0/WG1#

P1.2/TXD1

NC

NC

P1.1/RXD0

P1.0/TXD0

V

PP

P5.3/RD#

P5.1/INST

P5.0/ALE/ADV#

P5.4/ONCE#

P5.6/READY

VSSXTAL1

EXTINT

XTAL2NCNC

P6.6/PWM0

NC

P5.5/BHE#/WRH#

V

SS

S8XC196MH

TOP VIEW

(Looking down

on component side of

PC board)

A2574-01

8XC196MH INDUSTRIAL MOTOR CONT ROL CHM OS MICRO CO NTR OLL ER

®

11

Table 6. 80-lead Shrink EIAJ/QFP Pin Assignment

Pin Name Pin Name Pin Name Pin Name

1 P5.2/WR#/WRL# 21 NC 41 P0.7/ACH7/T1DIR

/PMODE.3

61 P2.4/COMP0

/AINC#

2 P5.7/BUSWIDTH 22 RESET# 42 P0.6/ACH6

/T1CLK/PMODE.2

62 P2.5/COMP1

/PACT#

3 P4.7/AD15

/PBUS.15

23 NMI 43 ANGND 63 P2.6/COMP2

/CPVER

4 P4.6/AD14

/PBUS.14

24 EA# 44 V

REF

64 P6.7/PWM1

5V

CC

25 V

SS

45 P0.5/ACH5

/PMODE.1

65 P6.6/PWM0

6 P4.5/AD13

/PBUS.13

26 NC 46 P0.4/ACH4

/PMODE.0

66 NC

7NC 27V

CC

47 P0.3/ACH3 67 NC

8 P4.4/AD12

/PBUS.12

28 P6.5/WG3 48 P0.2/ACH2 68 NC

9 P4.3/AD11

/PBUS.11

29 P6.4/WG3# 49 P0.1/ACH1 69 XTAL2

10 P4.2/AD10

/PBUS.10

30 P6.3/WG2 50 P0.0/ACH0 70 XTAL1

11 P4.1/AD9/PBUS.9 31 V

SS

51 NC 71 V

SS

12 P4.0/AD8/PBUS.8 32 P6.2/WG2# 52 P2.0/EPA0/PVER 72 EXTINT

13 P3.7/AD7/PBUS.7 33 P6.1/WG1 53 P2.1/SCLK0#

/BCLK0/PALE#

73 P5.4/ONCE#

14 P3.6/AD6/PBUS.6 34 P6.0/WG1# 54 NC 74 P5.6/READY

15 P3.5/AD5/PBUS.5 35 P1.3/RXD1 55 NC 75 P5.1/INST

16 P3.4/AD4/PBUS.4 36 P1.2/TXD1 56 P2.2/EPA1

/PROG#

76 V

SS

17 P3.3/AD3/PBUS.3 37 NC 57 P2.3/COMP3 77 P5.0/ALE/ADV#

18 P3.2/AD2/PBUS.2 38 NC 58 P2.7/SCLK1#

/BCLK1

78 V

PP

19 P3.1/AD1/PBUS.1 39 P1.1/RXD0 59 NC 79 P5.3/RD#

20 P3.0/AD0/PBUS.0 40 P1.0/TXD0 60 NC 80 P5.5/BHE#/WRH#

8XC196MH INDUSTRIAL MOTO R CONTRO L CHMO S MICRO CO NTR OLL ER

®

12

PIN DESCRIPTIONS

Table 7. Signal Descriptions

Signal

Name

Type Description

Multiplexed

With

ACH7

ACH6

ACH5

ACH4

ACH3:0

I Analog Channels. These pins are analog inputs to the A/D

converter.

These pins are multiplexed with the port 0 pins. While it is

possible for the pins to function simultaneously as analog and

digital inputs, this is not recommended because reading the

port while a conversion is in process can produce unreliable

conversion results.

The ANGND and V

REF

pins must be connected for the A/D

converter and the multiplexed port pins to function.

P0.7/T1DIR/PMO DE .3

P0.6/T1CLK/PMODE.2

P0.5/PMODE.1

P0.4/PMODE.0

P0.3:0

AD15:8

AD7:0

I/O Address/Data Lines. The se pins provide a multiplexed

address and data bus. During the address phase of the bus

cycle, address bits 0–15 are presented on the bus and can

be latched using ALE or ADV#. During the data phase, 8- or

16-bit data is transferred.

P4.7:0/PBUS.15:8

P3.7:0/PBUS.7:0

ADV# O Address Valid. This active-low output signal is asserted only

during external memory accesses.

ADV# indicates that valid address information is available on

the system address/data bus. The signal remains low while a

valid bus cycle is in progress and is returned high as soon as

the bus cycle completes.

An external latch can use the ADV# signal to demultiplex the

address from the address/data bus. Used with a decoder,

ADV# can generate chip-selects for external memory.

P5.0/ALE

AINC# I Auto Increment. In slave programming mode, this active-low

input signal enables the autoincrement mode. Auto increment

allows reading from or writing to sequential OTPROM

locations without requiring address transactions across the

programming bus for each read or write.

P2.4/COMP0

ALE O Address Latch En ab le. This act ive-high output signa l is

asserted only during external memory cycles.

ALE signals the start of an external bus cycle and indicates

that valid address information is available on the system

address/data bus. ALE differs from ADV# in that it is not

returned high until a new bus cycle is to begin.

An external latch can use ALE to demultiplex the address

from the address/data bus.

P5.0/ADV#

ANGND GND Analog Ground. Reference ground for the A/D convert er

and the logic used to read port 0. ANGND must be held at

nominally the same potential as V

SS

.

—

BCLK1

BCLK0

I Serial Communications Baud Clock 0 and 1. BCLK0 and 1

are alternate clock sources for the serial ports. The maximum

input frequency is F

OSC

/4.

P2.7/SCLK1#

P2.1/SCLK0#/PALE#

8XC196MH INDUSTRIAL MOTOR CONT ROL CHM OS MICRO CO NTR OLL ER

®

13

BHE# O Byte High Enable. During 16-bit bus cycles, this active-low

output signal is asserted for word reads and writes and for

high-byte reads and writes to external memory. BHE#

indicates that valid data is being transferred over the upper

half of the system address/data bus.

BHE#, in conjunction with A0, selects the memory byte to be

accessed:

BHE# A0 Byte(s) Accessed

0 0 both bytes

0 1 high byte only

1 0 low byte only

P5.5/WRH#

BUSWIDTH I Bus Width. When enabled in the chip configuration register,

this active-high input signal dynamically selects the bus width

of the bus cycle in progress. When BUSWIDTH is high, a 16bit bus cycle occurs; when BUSWIDTH is low, an 8-bit bus

cycle occurs. BUSWIDTH is active during a CCR fetc h.

P5.7

COMP3

COMP2

COMP1

COMP0

O Event Processor Array (EPA) Compare Pins. These

signals are the output of the EPA compare modules. These

pins are multiplexed with other signals and may be

configured as standard I/O.

P2.3

P2.6/CPVER

P2.5/PACT#

P2.4/AINC#

CPVER O Cumulative Program Verification. This active-high output

signal indicates whether any verify errors have occurred

since the device entered programming mode. CPVER

remains high until a verify error occurs, at which time it is

driven low. Once an error occurs, CPVER remains low until

the device exits programming mode. When high, CPVER

indicates that all locations have programmed correctly since

the device entered programming mode.

P2.6/COMP2

EA# I External Access. This active-low input signal directs

memory accesses to on-chip or off-chip memory. If EA# is

low, the memory access is off-chip. If EA# is high and the

memory address is within 2000H–2FFFH, the access is to

on-chip ROM or OTPROM. Otherwise, an access with EA#

high is to off-chip memory.

EA# is sampled only on the rising edge of RESET#.

If EA# = V

EA

on the rising edge of RESET#, the device enters

the programming mode selected by PMODE.3:0.

For devices without ROM, EA# must be tied low.

—

EPA1

EPA0

I/O Event Processor Array (EPA) Input/O utpu t pins. These

are the high-speed input/output pins for the EPA

capture/compare modules. These pins are multiplexed with

other signals and may be configured as standard I/O.

P2.2/PROG#

P2.0/PVER

Table 7. Signal Descriptions (Continued)

Signal

Name

Type Description

Multiplexed

With

Loading...

Loading...