Intel Corporation S80296SA-50 Datasheet

80296SA COMMERCIAL

CHMOS 16-BIT MICROCONTROLLER

■ 50 MHz Operation

■ 6 Mbytes of Linear Address Space

■ 512 Bytes of Register RAM

■ 2 Kbytes of Code/Data RAM

■ Register-regist er Architecture

■ Footprint and Functionally Compatible

Upgrade for the 8XC196NP and

80C196NU

■ Optional Phase-locked Loop (PLL)

Circuitry with 2x or 4x Clock Multiplier

■ 32 I/O Port Pins

■ 19 Interrupt Sources, 14 with

Programmable Priorities

■ 4 External Interrupt Pins and NMI Pin

■ 2 Flexible 16-bit Timer/Counters with

Quadrature Counting Capability

■ 3 Pulse-width Modulator (PWM)

Outputs with High Drive Capability

■ Full-duplex Serial Port with Dedicated

Baud-rate Generator

†

40 MHz standard; 50 MHz is Speed Premium

†

PRELIMINARY

■ Chip-select Unit

—6 Chip-select Pins

—Dynamic Demultiplexed/Multiplexed

Address/Data Bus for Each

Chip Select

—Programmable Wait States

(0–15) for Each Chip Select

—Programmable Bus Width

(8- or 16-bit) for Each Chip Select

—Programmable Address Range for

Each Chip Select

■ Event Processor Array (EPA) with

4 High-speed Capture/Compare

Channels

■ Multiply and Accumulate Executes in

80 ns Using the 40-bit Hardware

Accumulator

■ 880 ns 32/16 Unsigned Division

■ 100-pin QFP Package

■ Complete System Development

Support

■ High-speed CHMOS Technology

The 80296SA is a member of Intel’s 16-bit MCS® 96 microcontroller family. The 80296SA features 6 Mbytes

of linear address space, a demultiplexed bus, and a chip-select unit . The external bus can dynamically switch

between multiplexed and demultiplexed operation. The device has hardware and instructions to support

various dig i tal signal proces sing algorithms.

NOTE

This datasheet contains information on new products in pr oduction. The specifications

are subject to change without notice. Verify with your local Intel sales office that you have

the latest datasheet before fi nalizing a design.

COPYRIGHT © INTEL CORPORATION, 1997 January 1997 Order Number: 272748-003

Information in this document is provided in connection with Inte l p r oducts. No license, express or impl i ed, by

estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in

Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating t o fitness for a particular purp os e, merchantability, or infringement of any patent, copy right or

other intell ect ual pr oper ty r ight . Int el p rodu ct s a re n ot inte nded fo r use i n medi cal , l ife s avi ng, or life sustai nin g

applications.

Intel retai ns the right to make changes to specifi cations and product description s at any time, with out notice.

*Third-party brands and names are the propert y of their respective owners.

Copies of documents which have an orderin g number and are referenced in this document, or other Intel liter-

ature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-548-4 725

CONTENTS

80296SA Commercial

CHMOS 16-bit Microcontroller

1.0 Product Overview................................................................................................................ 1

2.0 Nomenclature Overview...................................................................................................... 2

3.0 Pinout.................................................................................................................................. 3

4.0 Signals ................................................................................................................................ 6

5.0 Address Map..................................................................................................................... 13

6.0 Electrical Characteristics......................................................... ......... ........ ......... ........ ........ 14

6.1 DC Characteristics........................................................................................................ 14

6.2 AC Characteristics........................................................................................................ 18

6.2.1 Relationship of XTAL1 to CLKOUT .......................................................................18

6.2.2 Explanation of AC Symbols ...................................................................................19

6.2.3 AC Characteristics — Multiplexed Bus Mode ........................................................20

6.2.3.1 System Bus Timings, Multiplexed Bus ......................................................22

6.2.3.2 READY Timing, Multiplexed Bus ...............................................................23

6.2.4 AC Characteristics — Demultiplexed Bus Mode ...................................................24

6.2.4.1 System Bus Timings, Demultiplexed Bus ..................................................26

6.2.4.2 READY Timing, Demultiplexed Bus ..........................................................27

6.2.4.3 80296SA Deferred Bus Timing Mode ........................................................28

6.2.5 HOLD#, HLDA# Timings .......................................................................................29

6.2.6 AC Characteristics — Serial Port, Synchronous Mode 0 ......................................30

6.2.7 External Clock Drive ..............................................................................................31

7.0 Thermal Characteristics.................................................................................................... 33

8.0 80296SA Errata................................................................................................................. 33

9.0 Datasheet Revision History............................................................................................... 33

FIGURES

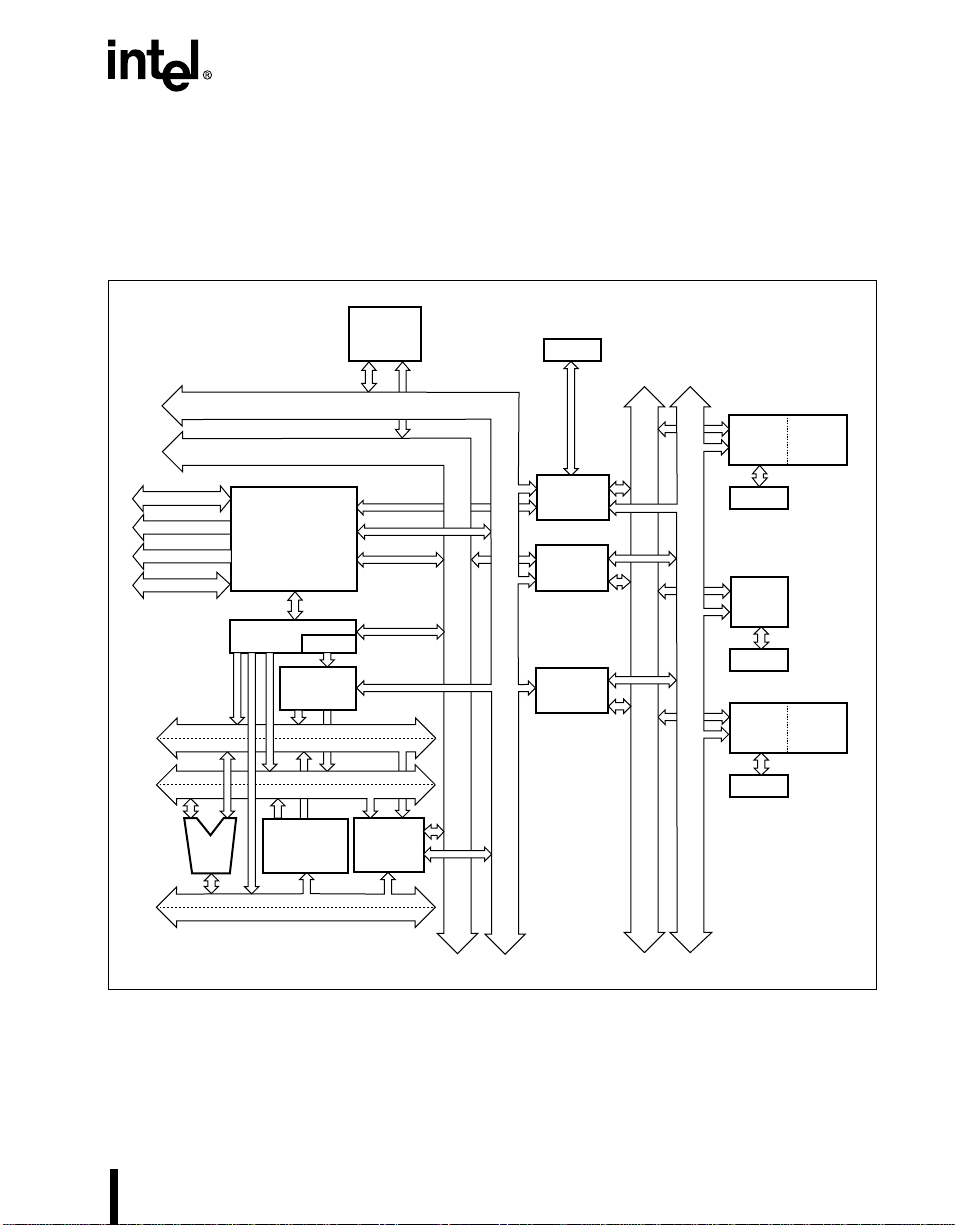

1. 80296SA Block Diagram......................................................................................................1

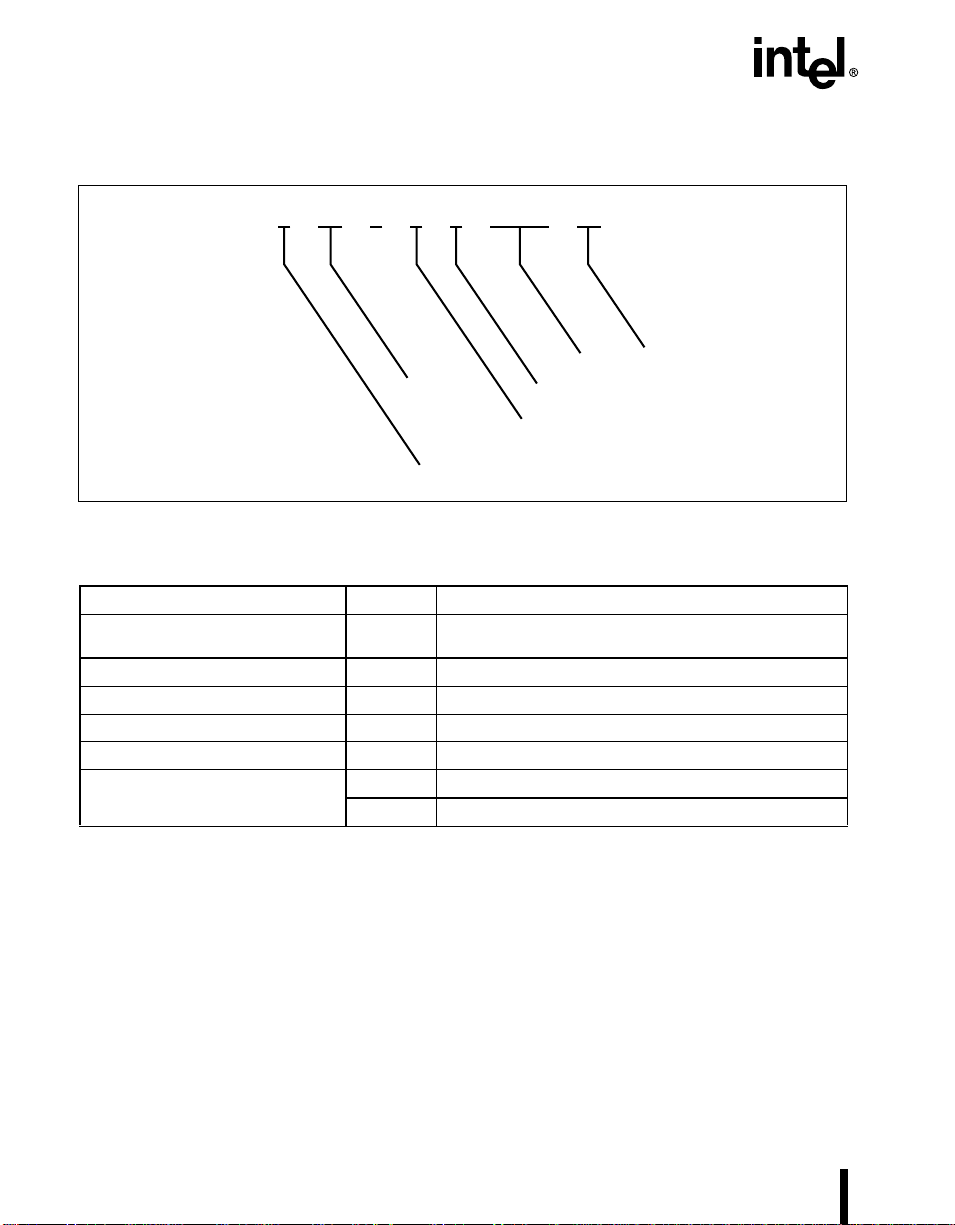

2. The 80296SA Family Nomenclature ....................................................................................2

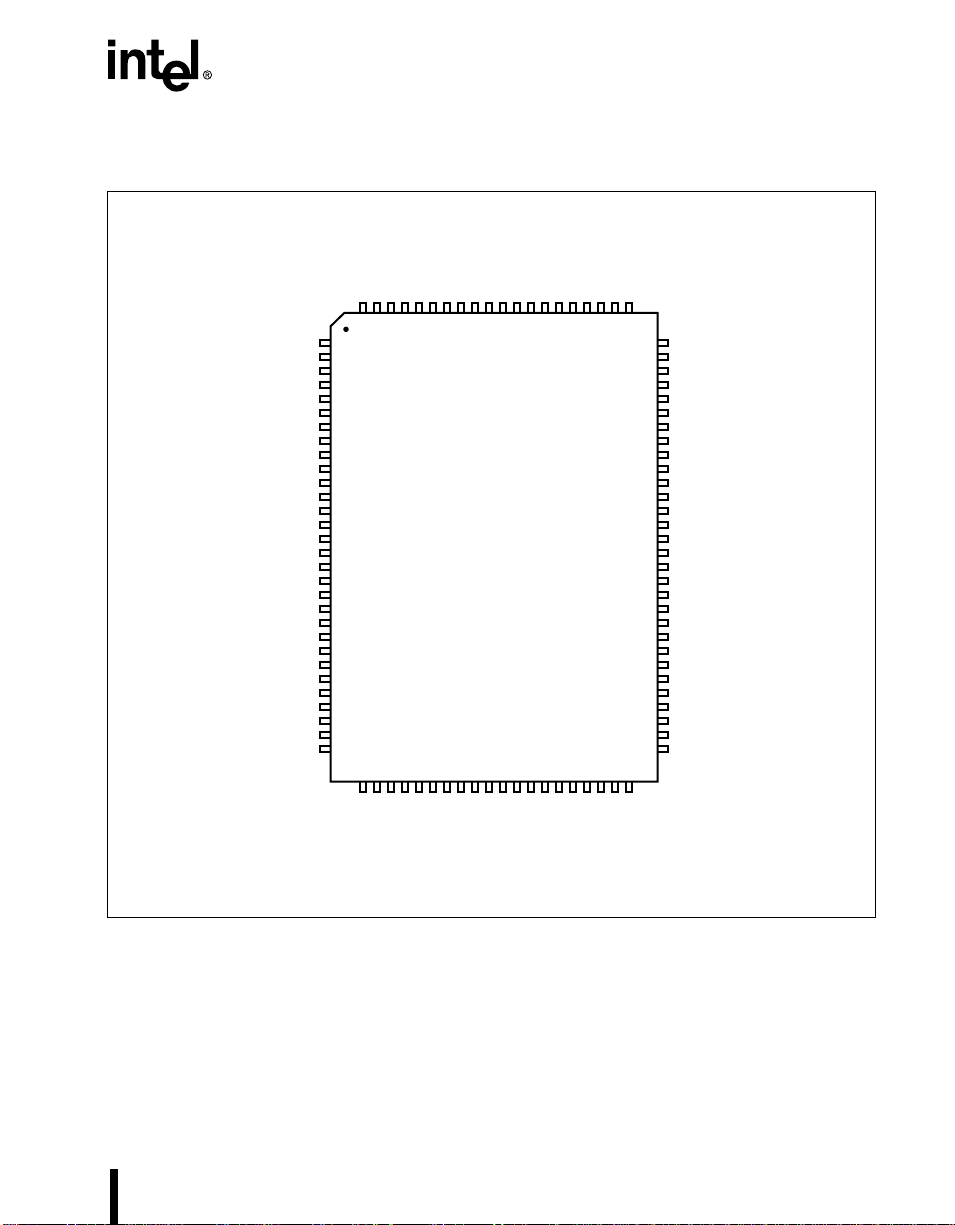

3. 80296SA 100-pin QFP Package..........................................................................................3

4. ICC versus Frequency in Reset...........................................................................................17

5. Effect of Clock Mode on CLKOUT......................................................................................18

6. System Bus Timings, Multiplexed Bus Mode.....................................................................22

7. Example READY Timings at 50 MHz, Multiplexed Bus, BUSCONx = 1 Wait State...........23

8. System Bus Timings, Demultiplexed Bus Mode.................................................................26

9. Example READY Timings at 50 MHz, Demultiplexed Bus, BUSCONx = 1 Wait State......27

10. Deferred Bus Mode Timing Diagram..................................................................................28

11. HOLD#, HLDA# Timing Diagram.......................................................................................29

12. Serial Port Waveform — Synchronous Mode 0..................................................................30

13. External Clock Drive Waveforms........................................................................................31

14. AC Testing Input and Output Waveforms During 5.0 Volt Testing.....................................32

15. Float Waveforms During 5.0 Volt Testing...........................................................................32

PRELIMINARY iii

CONTENTS

TABLES

1. Description of Product Nomenclature ..................................................................................2

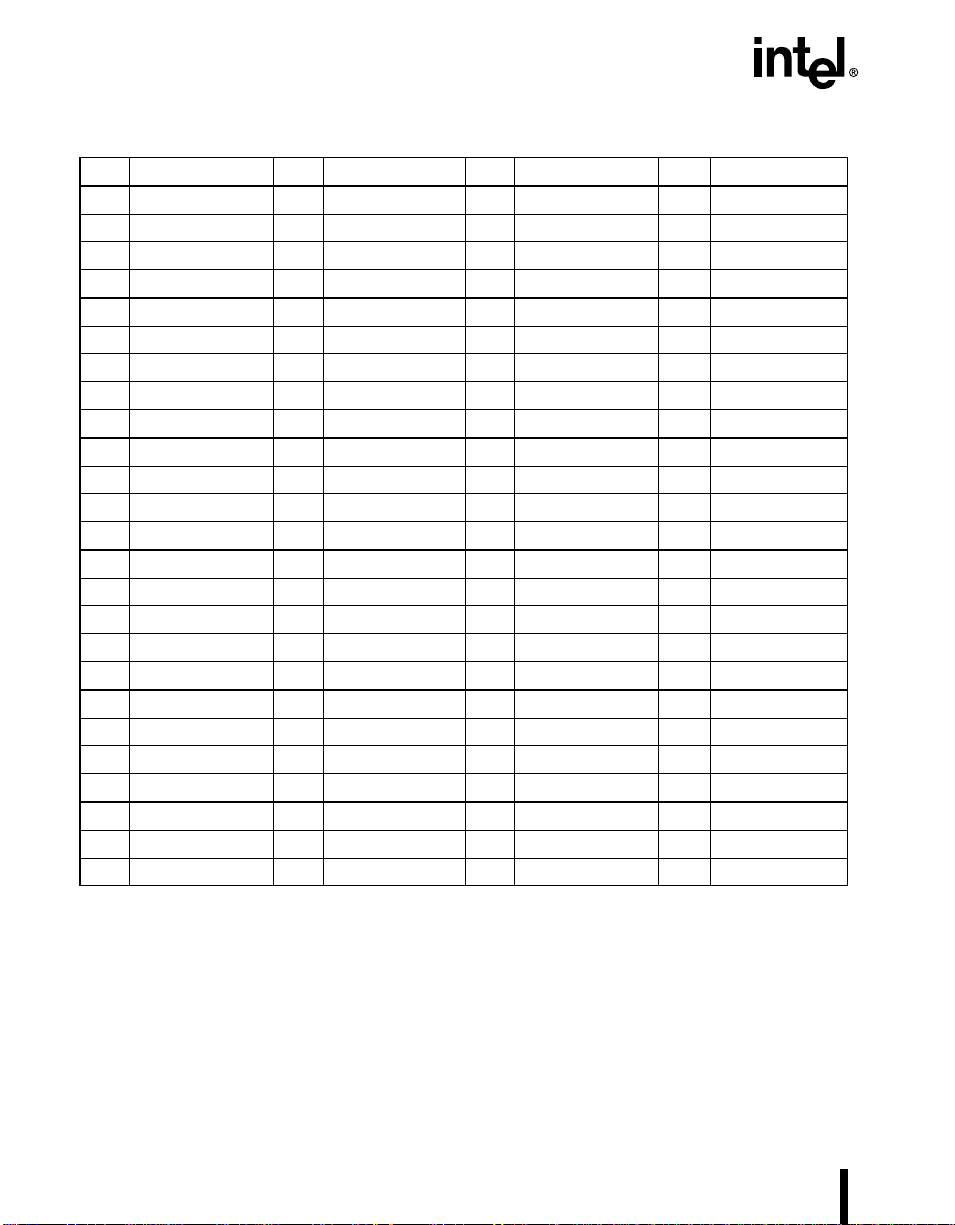

2. 80296SA 100-pin QFP Pin Assignment...............................................................................4

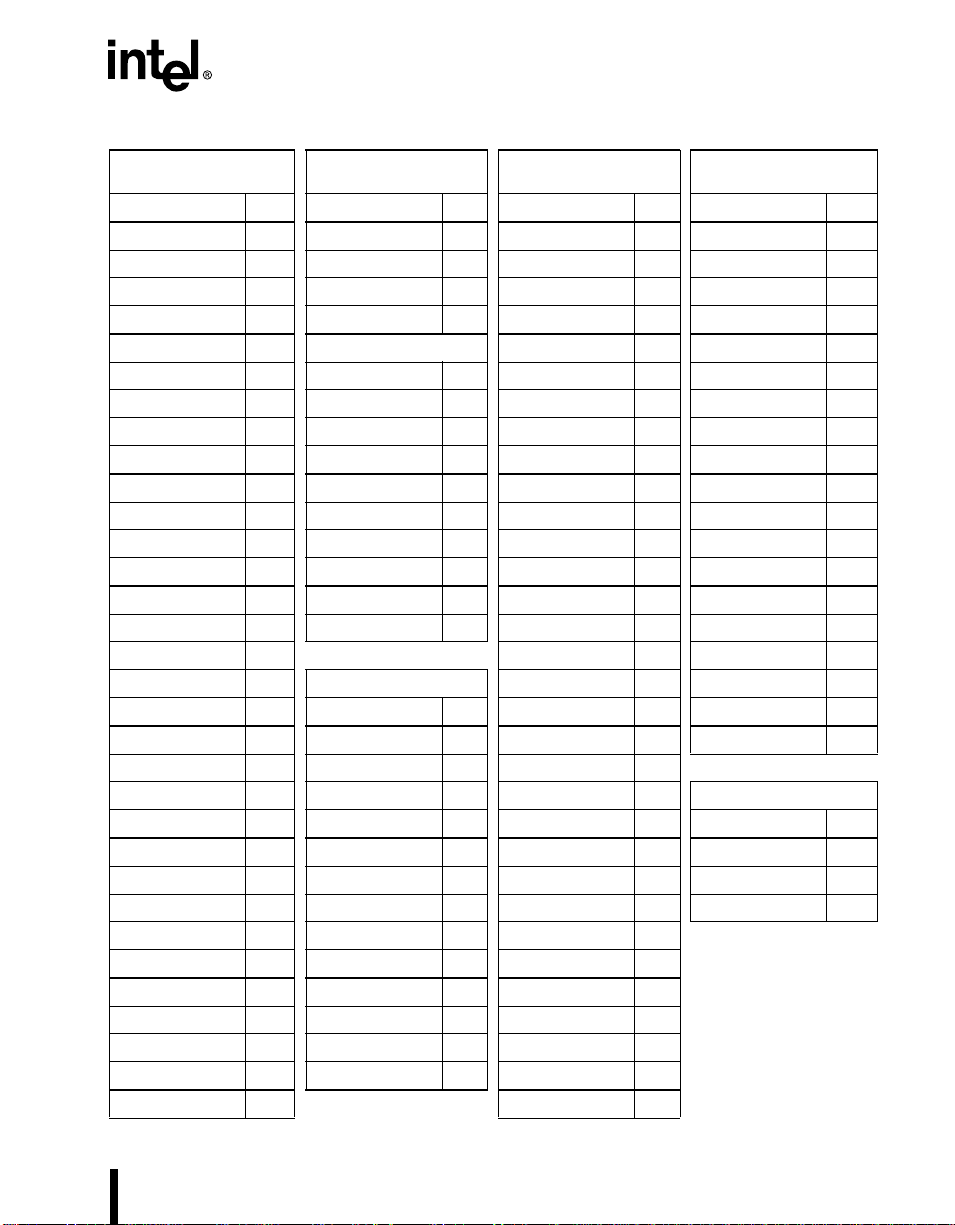

3. 80296SA 100-pin QFP Pin Assignment Arranged by Functional Categories ......................5

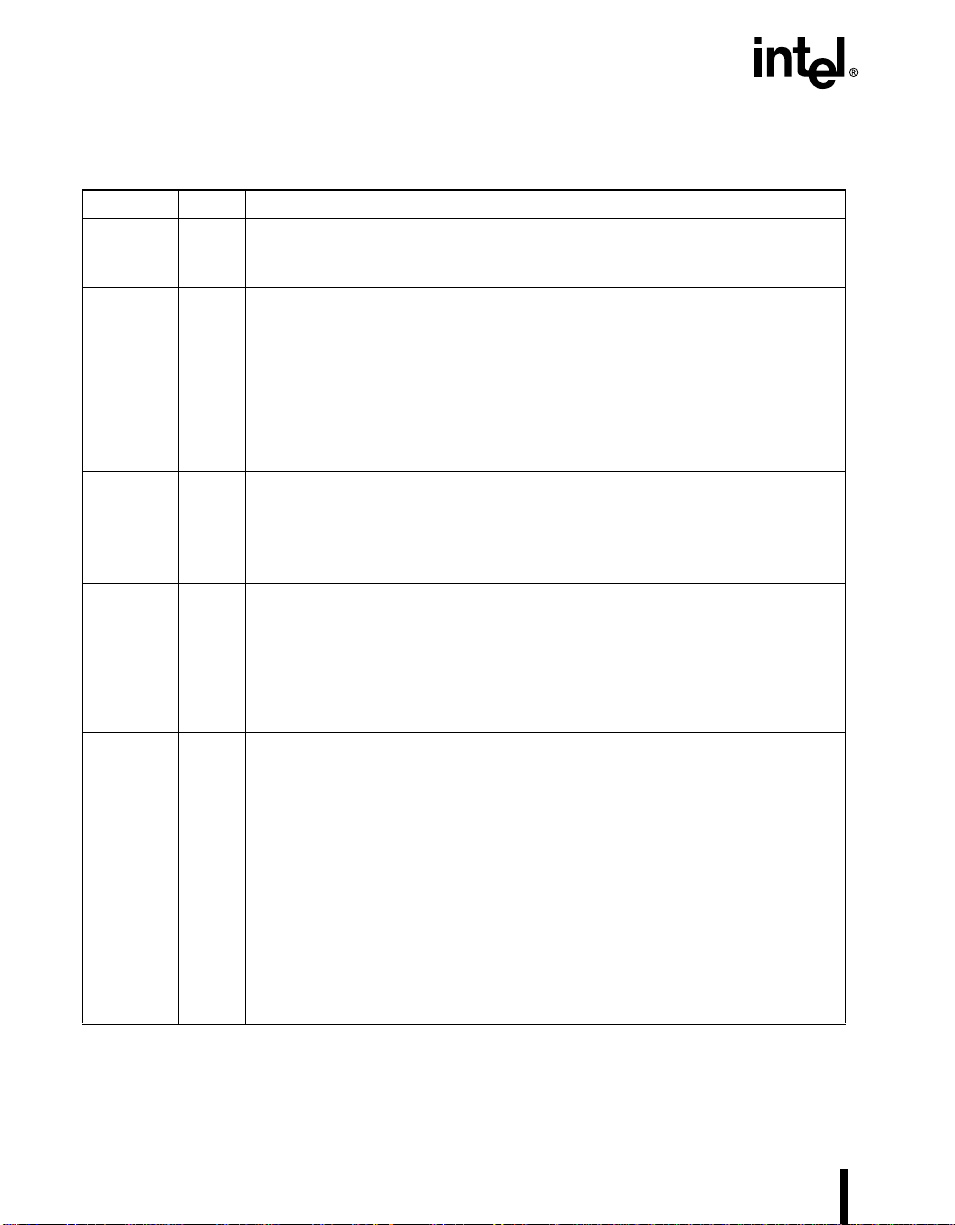

4. Signal Descriptions .............................................. ......... ........ ........ ......... ........ ......... ........ .....6

5. 80296SA Address Map......................................................................................................13

6. DC Characteristics Over Specified Operating Conditions..................................................14

7. AC Timing Symbol Definitions............................................................................................19

8. AC Characteristics the 80C296SA Will Meet, Multiplexed Bus Mode................................20

9. AC Characteristics the External Memory System Must Meet, Multiplexed Bus Mode.......21

10. AC Characteristics the 80C296SA Will Meet, Demultiplexed Bus Mode...........................24

11. AC Characteristics the External Memory System Must Meet, Demultiplexed Bus Mode ..25

12. HOLD#, HLDA# Timings....................................................................................................29

13. Serial Port Timing — Synchronous Mode 0.......................................................................30

14. External Clock Drive...........................................................................................................31

15. Thermal Characteristics.....................................................................................................33

iv PRELIMINARY

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

1.0 PRODUCT OVERVIEW

The 80296SA is a member of Intel’s 16-bit MCS® 96 microcontrol l er family. The 80296SA features 6 Mbytes

of linear address space, a demultiplexed bus, and a chi p-select unit. The external bus can dynamically switch

between multiplexed and demultiplexed operation. The device has hardware and instructions to support

various dig i tal signal proces sing algorithms.

Code/Data

RAM

(2 Kbytes)

Memory Addr Bus (24)

Memory Data Bus (16)

Port 3

SIO

Baud-

rate

Generator

Bus Control Signals

A19:16

A15:0

AD15:0

ALU

Controller

Aligner

Bus

Queue

Instruction

Sequencer

Source 1 Addr (24)

Source 1 Data (16)

Source 2 Addr (24)

Source 2 Data (16)

Register File

(3-port RAM)

Destination Addr (24)

Destination Data (16)

Chip-select

Unit

Peripheral

Bus

Interface

Interrupt

Controller

Memory

Interface

Unit

Memory Addr Bus (24)

Memory Data Bus (16)

Figure 1. 80296 SA Block Diagram

Port 2

PWM

Port 4

EPA

Port 1

Peripheral Addr Bus (8)

Peripheral Data Bus (16)

Timer 1

Timer 2

A3175-02

PRELIMINARY 1

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

2.0 NOMENCLATURE OVERVIEW

XXXXX XXXX8XXX

Program-memory Options

Packaging Options

Temperature and Burn-in Options

Figure 2. The 80296SA Family Nomenclature

Table 1. Description of Product Nomenclature

Parameter Options Description

Temperature and Burn-in Options

Packaging Options S QFP

Program–memory Options 0 Without ROM

Process Information no mark CHMOS

Product Famil y 296SA —

Device Speed

no mark Commercial operating temperature range (0°C to 70°C)

40 40 MHz

50 50 MHz

Process Information

with Intel standard burn-in.

Product Family

Device Speed

A2815-01

2 PRELIMINARY

3.0 PINOUT

AD0

NC

RESET#

NMI

NC

V

V

V

V

PLLEN1

P3.0 / CS0#

P3.1 / CS1#

P3.2 / CS2#

P3.3 / CS3#

V

P3.4 / CS4#

P3.5 / CS5#

P3.6 / EXTINT2

P3.7 / EXTINT3

NC

P1.0 / EPA0

V

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

CC

SS

AD8

AD1

AD2

AD3

AD4

AD5

99

98

97

96

100

1

2

3

4

5

A0

6

A1

7

8

CC

9

SS

A2

10

A3

11

A4

12

A5

13

A6

14

A7

15

16

CC

17

SS

18

19

20

21

22

23

SS

24

25

26

27

28

29

30

CC

View of component as

mounted on PC board

31

32

33

34

35

AD6

AD7

V

95

94

93

S80296SA

36

37

38

SS

CC

V

V

V

AD9

AD10

AD11

AD12

AD13

92

91

90

89

88

87

86

39

40

41

42

43

44

45

SS

CC

V

V

P4.3

AD14

AD15

A16 / EPORT.0

85

84

83

46

47

48

CC

A17 / EPORT.1

V

82

81

V

80

SS

A18 / EPORT.2

79

A19 / EPORT.3

78

WR# / WRL#

77

RD#

76

BHE# / WRH#

75

ALE

74

INST

73

READY

72

RPD

71

ONCE

70

PLLEN2

69

V

68

CC

V

67

SS

A8

66

A9

65

A10

64

A11

63

A12

62

A13

61

A14

60

A15

59

V

58

SS

XTAL1

57

XTAL2

56

V

55

SS

P2.7 / CLKOUT

54

V

53

CC

P2.6 / HLDA#

52

P2.5 / HOLD#

51

49

50

P2.0 / TXD

P1.1 / EPA1

P1.2 / EPA2

P1.3 / EPA3

P1.4 / T1CLK

P1.5 / T1DIR

P1.6 / T2CLK

P1.7 / T2DIR

P4.0 / PWM0

P4.1 / PWM1

P4.2 / PWM2

P2.1 / RXD

P2.3 / BREQ#

P2.2 / EXTINT0

P2.4 / EXTINT1

A3155-02

Figure 3. 80296SA 100-pin QFP Package

PRELIMINARY 3

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

Table 2. 80296SA 100-pin QFP Pin Assignment

Pin Name Pin Name Pin Name Pin Name

1 AD0 26 EXTINT2/P3.6 51 HOLD#/P2.5 76 RD#

2 NC (see Note) 27 NC (see Note) 52 HLDA#/P2.6 77 WR#/WRL#

3 RESET# 28 EXTINT3/P3.7 53 V

CC

4 NMI 29 EPA0/P1.0 54 CLKOUT/P2.7 79 EPORT.2/A18

5 NC (see Note) 30 V

55 V

CC

SS

6 A0 31 EPA1/P1.1 56 XTAL2 81 V

7 A1 32 EPA2/P1.2 57 XTAL1 82 EPORT.1/A17

8V

9V

33 EPA3/P1.3 58 V

CC

34 T1CLK/P1.4 59 A15 84 AD15

SS

SS

10 A2 35 T1DIR/P1.5 60 A14 85 AD14

11 A3 36 V

61 A13 86 AD13

CC

12 A4 37 T2CLK/P1.6 62 A12 87 AD12

13 A5 38 V

63 A11 88 AD11

SS

14 A6 39 T2DIR/P1.7 64 A10 89 AD10

15 A7 40 PWM0/P4.0 65 A9 90 AD9

16 V

17 V

18 PLLEN1 43 P4.3 68 V

19 CS0#/P3.0 44 V

20 CS1#/P3.1 45 V

41 PWM1/P4.1 66 A8 91 VSS

CC

42 PWM2/P4.2 67 VSS 92 AD8

SS

93 VCC

CC

69 PLLEN2 94 AD7

CC

70 ONCE 95 AD6

SS

21 CS2#/P3.2 46 TXD/P2.0 71 RPD 96 AD5

22 CS3#/P3.3 47 RXD/P2.1 72 READY 97 AD4

23 V

SS

48 EXTINT0/P2.2 73 INST 98 AD3

24 CS4#/P3.4 49 BREQ#/P2.3 74 ALE 99 AD2

25 CS5#/P3.5 50 EXTINT1/P2.4 75 BHE#/WRH# 100 AD1

NOTE: For compatibility with future products, tie pin 5 to V

and leave pins 2 and 27 unconnected.

CC

78 EPORT.3/A19

80 VSS

CC

83 EPORT.0/A16

4 PRELIMINARY

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

Table 3. 80296SA 100-pin QFP Pin Assignment Arranged by Functional Categories

Address & Data

Name Pin Name Pin Name Pin Name Pin

A0 6 AD12 87 CS0#/P3.0 19 V

A1 7 AD13 86 CS1#/P3.1 20 V

A2 10 AD14 85 CS2#/P3.2 21 V

A3 11 AD15 84 CS3#/P3.3 22 V

A4 12 Bus Control & Status CS4#/P3.4 24 V

A5 13 Name Pin CS5#/P3.5 25 V

A6 14 ALE 74 EPA0/P1.0 29 V

A7 15 BHE#/WRH# 75 EPA1/P1.1 31 V

A8 66 BREQ# 49 EPA2/P1.2 32 V

A9 65 HOLD# 51 EPA3/P1.3 33 V

A10 64 HLDA# 52 EPORT.0 83 V

A11 63 INST 73 EPORT.1 8 2 V

A12 62 RD# 76 EPORT.2 79 V

A13 61 READY 72 EPORT.3 78 V

A14 60 W R#/WRL# 77 P2.2 48 V

A15 59 P2.3 49 V

A16 83 Processor Control P2.4 50 V

A17 82 Name Pin P2.5 51 V

A18 79 CLKOUT 54 P2.6 52 V

A19 78 EXTINT0 48 P2.7 54

AD0 1 EXTINT1 50 P3.6 26 No Connection

AD1 100 EXTINT2 26 P3.7 28 Name Pin

AD2 99 EXTINT3 28 P4.3 43 NC 2

AD3 98 NMI 4 PWM0/P4.0 40 NC 5

AD4 97 ONCE 70 PWM1/P4.1 41 NC 27

AD5 96 RESET# 3 PWM2/P4.2 42

AD6 95 RPD 71 RXD/P2.1 47

AD7 94 XTAL1 57 T1CLK/P1.4 34

AD8 92 XTAL2 56 T1DIR/P1.5 35

AD9 90 PLLEN1 18 T2CLK/P1.6 37

AD10 89 PLLEN2 69 T2DIR/P1.7 39

AD11 88 TXD/P2.0 46

Address & Data

(continued)

Input/Output Power & Ground

CC

CC

CC

CC

CC

CC

CC

CC

CC

SS

SS

SS

SS

SS

SS

SS

SS

SS

SS

8

16

30

36

44

53

68

81

93

9

17

23

38

45

55

58

67

80

91

PRELIMINARY 5

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

4.0 SIGNALS

Table 4. Signal Descriptions

Name Type Description

A15:0 I/O System Address Bus

These address pins provide address bits 0–15 during the entire external memory

cycle during bot h multiplexed and demultiplexed bus modes.

A19:16 I/O Address Pins 16–19

These address pin s provide address bits 16–19 during the entire ext ernal memory

cycle during bot h multiplexed and demultiplexed bus modes, supporting extended

addressing of the 1-Mbyte address space.

NOTE: Internally, there are 24 address bits; however, only 20 external ad dress

A19:16 share pac kage pins with EPORT. 3:0.

AD15:0 I/O Address/Data Lines

These pins provi de a multiplexed address and data bus. During the address phase

of the bus cycle, address bits 0–15 are presen te d on the bus and can be latched

using ALE or ADV#. Du ring the data phase, 8- or 16-bit data is trans ferred.

AD7:0 share pack age pins with P3.7:0. AD15:8 share package pins with P4.7:0.

ALE O Address Latch Enable

This active-high output signal is asserted only during external memory cycles. ALE

signals the start of an external bus cycle and indi cate s t hat val id a ddre ss inf ormati on

is available on the system address/data bus (A19:16 and AD15:0 for a multiplex ed

bus; A19:0 for a demultiplexed bus).

An external latch can use this signal to demultip lex address bits 0–15 from the

address/data bus i n mul tiplexed mode.

BHE# O Byte High Enable

During 16-bit bus cycles, this active-lo w output signal is asserted for word and high byte reads and writes to external memory. BHE# indicates that valid data is being

transferred ov er the upper half of th e system data bus. Use BHE#, in conjunction

with address bit 0 (A0 for a demultiplexed address bus, AD0 for a multiplexed

address/data bus), to determine which memory byte is being tr ansferred over the

system bus:

BHE# AD0 or A0 Byte(s) Accessed

0 0 both bytes

0 1 high byte only

1 0 low byte only

BHE# shares a package pin with WRH#.

†

pins (A19:0) are implemented. The internal address space is 16 Mbytes

(000000–FFFFFFH) and the external address space is 1 Mbyte (00000–

FFFFFH). The microcontroller resets to FF2080H.

†

Chip configuration register 0 (CCR0) determines whether this pin functions as

BHE# or as WRH#. CCR0.2 = 1 selects BHE#; CCR0.2 = 0 selects WRH#.

6 PRELIMINARY

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

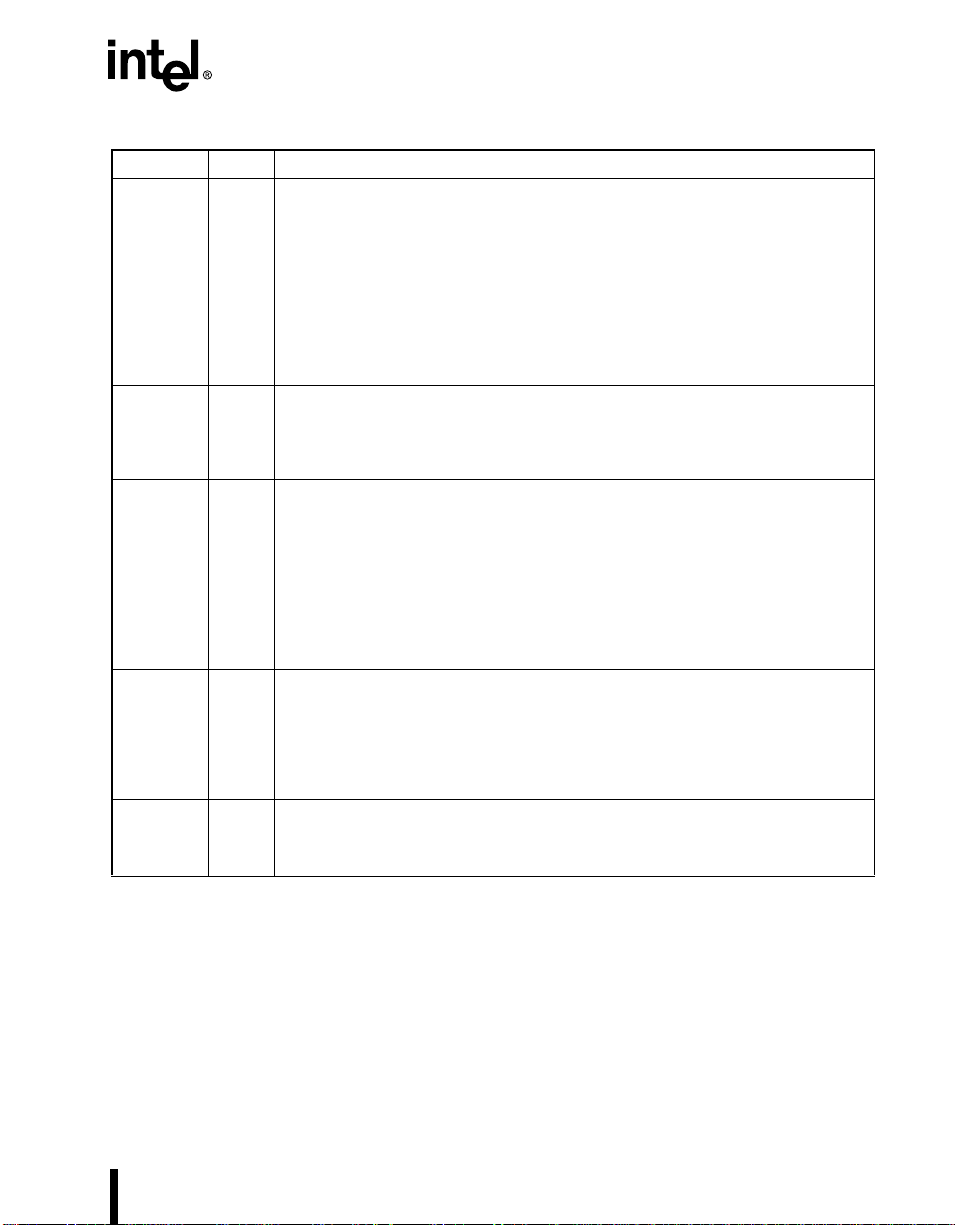

Table 4. Signal D escriptions (Conti nued)

Name Type Description

BREQ# O Bus Request

This active-low output signal is asserted during a hold cycle w hen the bus controller

has a pending external memory cycle. When t he bus-hold protocol i s enabled

(WSR.7 is set), the P2.3/BREQ# pin can function only as BREQ#, regardless of the

configurati on selected through the port configuration registers (P2_MODE, P2_DIR,

and P2_REG). An attempt to change the pin configuration is ignored until the bus hold protocol is disabled (WSR.7 is cleared).

The microcontroller can assert BREQ# at the same time as or after it asserts

HLDA#. Once it is asserted, BREQ# remains asserted until HOLD# is deasserted.

BREQ# shares a package pin with P2.3.

CLKOUT O Clock Output

Output of the internal clock generator. The CLKOUT frequency is ½ the internal

operating freq uency (f). CLKOUT has a 50% duty cycle.

CLKOUT shares a package pin with P2.7.

CS5:0# O Chip-select Lines 0–5

The active-low output CS

address to be accessed is in the range programmed for chip select

x

+1 if remapping is enabled. If the external memory address is outside the range

assigned to the si x chip selects, no chi p-select output is asserted and the bus

configurat i on defaults to th e C S5# values.

Immediately fol lowing reset, CS0# is automatically as signed to the range FF2000–

FF20FFH.

CS5:0# share package pins with P3.5:0.

EPA3:0 I/O Event Processor Array (EPA) Capture/Compare Channels

High-speed input/output signa ls for the EPA capture/c ompare channels. Fo r highspeed PWM applica ti ons, the outputs of two EPA channels (either EPA0 and EPA1

or EPA2 and EPA3) can be remapped to produce a PWM wave form on a shared

output pin.

EPA3:0 share pac kage pins with P1.3:0.

EPORT.3:0 I/O Extended Addressing Port

This is a standard 4-bit, bidirectional port.

EPORT.3:0 share package pins with A19:16.

x

# is asserted during an external memory cycle when the

x

or chip select

PRELIMINARY 7

80296SA COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

Table 4. Signal Descriptions (Continued)

Name Type Description

EXTINT3:0 I External Interrupts

These programmable interrupts are controlled by the EXTINT_CON register. Th i s

register controls whether the interrupt is edge-triggered or level-sensitive and

whether a rising edge/high level or falling edge/low level activates the interrupt.

In standby and powerd own mode s, ass erti ng the E XTINT

to resume normal operation. The interrupt does not need to be ena bl ed, but the pin

must be configured as a special-function input. If the EXTINT

the CPU executes the interrupt service routine. Otherwise, the CPU executes the

instruction that immediately follow s the command that invoked the power-saving

mode.

In idle mode, asserting any enabled interrupt causes the device to resume normal

operation.

EXTINT0 shares a package pin with P2.2, EXTINT1 shares a package pin with

P2.4, EXTI NT 2 sha res a pa c kage pin wi th P 3. 6, an d E XTINT 3 shar es a pac kag e p in

with P3.7.

HLDA# O Bus Hold Acknowledge

This active-l ow output indicat es that the CPU has releas ed the bus as the result of

an external devic e asserting HOLD#. When the bus-hold protocol is enabled

(WSR.7 is set), the P2.6/HLDA # pin can function only as HLDA#, regardless of the

configurati on sele cted thro ugh the port conf igur ati on reg ister s (P2 _MODE, P2 _DIR ,

and P2_REG). An attempt to change the pin configuration is ignored until the bushold protocol is di sabled (WSR.7 is cl eared).

HLDA# shares a package pin with P2.6.

HOLD# I Bus Hold Request

An external device uses this active-low input s i gnal to request c ontrol of the bus.

When the bus-hold protocol is enabled (WSR.7 is set), the P2.5/HOLD# pin can

function only as HOLD#, regardless of the configuration selected through the port

configurati on registers (P2_MODE, P2_DIR, and P2_REG ). An attempt to change

the pin configuration is ignored until the bus-hold protocol is disabled (WSR.7 is

cleared).

HOLD# shares a package pin with P2.5.

INST O Instruction Fetc h

When high, INST indicates that an instruction is b ei n g fetched from ext ernal

memory. The signal remains high during the entire bus cycle of an external

instruction fetch. INST is low for data accesses, including interrupt vector fetches

and chip configuration byte reads . INST is low during internal memory fetches.

x

signal causes the de vice

x

interrupt is enabled,

8 PRELIMINARY

Loading...

Loading...