*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

February 1994COPYRIGHT©INTEL CORPORATION, 1995 Order Number: 270849-004

87C54/87C54-20

CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

WITH 16 KBYTES USER PROGRAMMABLE EPROM

Automotive

Y

Extended Automotive Temperature

Range (

b

40§Ctoa125§C Ambient)

Y

High Performance CHMOS EPROM

Y

Three 16-Bit Timer/Counters

Y

One-to-Three Level Program/Data Lock

System

Y

16K On-Chip EPROM/ROM

Y

256 Bytes of On-Chip Data RAM

Y

Quick Pulse Programming Algorithm

Y

Boolean Processor

Y

32 Programmable I/O Lines

Y

7 Interrupt Sources

Y

Programmable Serial Channel with:

Ð Framing Error Detection

Ð Automatic Address Recognition

Y

TTL and CMOS Compatible Logic

Levels

Y

64K External Program Memory Space

Y

64K External Data Memory Space

Y

MCSÉ-51 Compatible Instruction Set

Y

Power Saving Idle and Power Down

Modes

Y

ONCE (On-Circuit Emulation) Mode

Y

RFI Reduction Mode

Y

Available in 12 MHz, 16 MHz and

20 MHz Versions

Y

Available in PLCC and DIP Packages

(See Packaging Spec., OrderÝ231369)

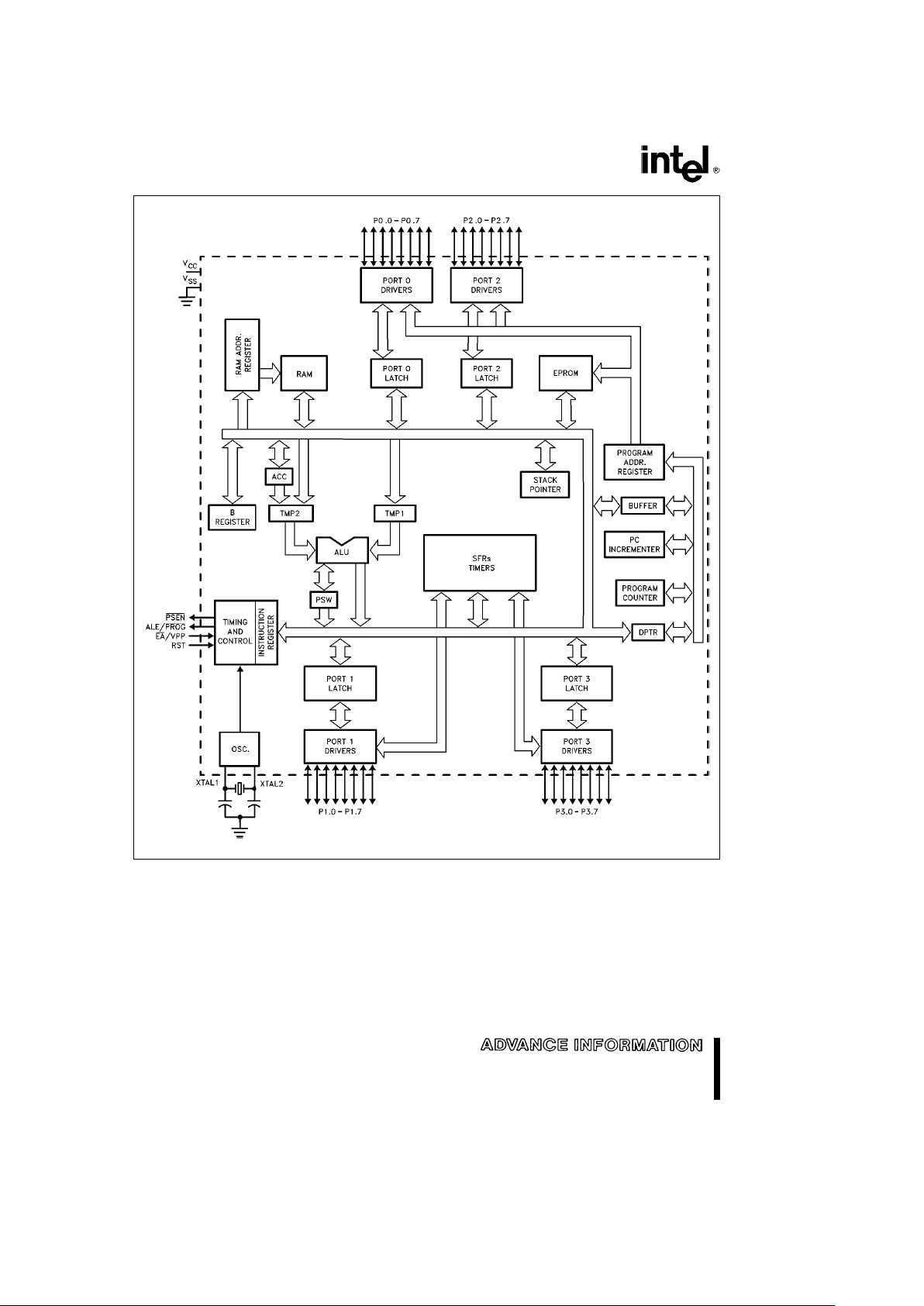

MEMORY ORGANIZATION

PROGRAM MEMORY: Up to 16 Kbytes of the program memory can reside in the on-chip EPROM. The device

can also address up to 64K of program memory external to the chip.

DATA MEMORY: This microcontroller has a 256 x 8 on-chip RAM. In addition it can address up to 64 Kbytes of

external data memory.

The Intel 87C54 is a single-chip control-oriented microcontroller which is fabricated on Intel’s reliable

CHMOS EPROM technology. Being a member of the MCS-51 family, the 87C54 uses the same powerful

instruction set, has the same architecture, and is pin-for-pin compatible with the existing MCS-51 family of

products. The 87C54 is an enhanced version of the 87C51FB. Its added features of 16 Kbytes of program

memory make it an even more powerful microcontroller for applications that require High Speed I/O and

up/down counting capabilities such as brake and traction control.

AUTOMOTIVE 87C54/87C54-20

270849– 1

Figure 1. 87C54 Block Diagram

2

AUTOMOTIVE 87C54/87C54-20

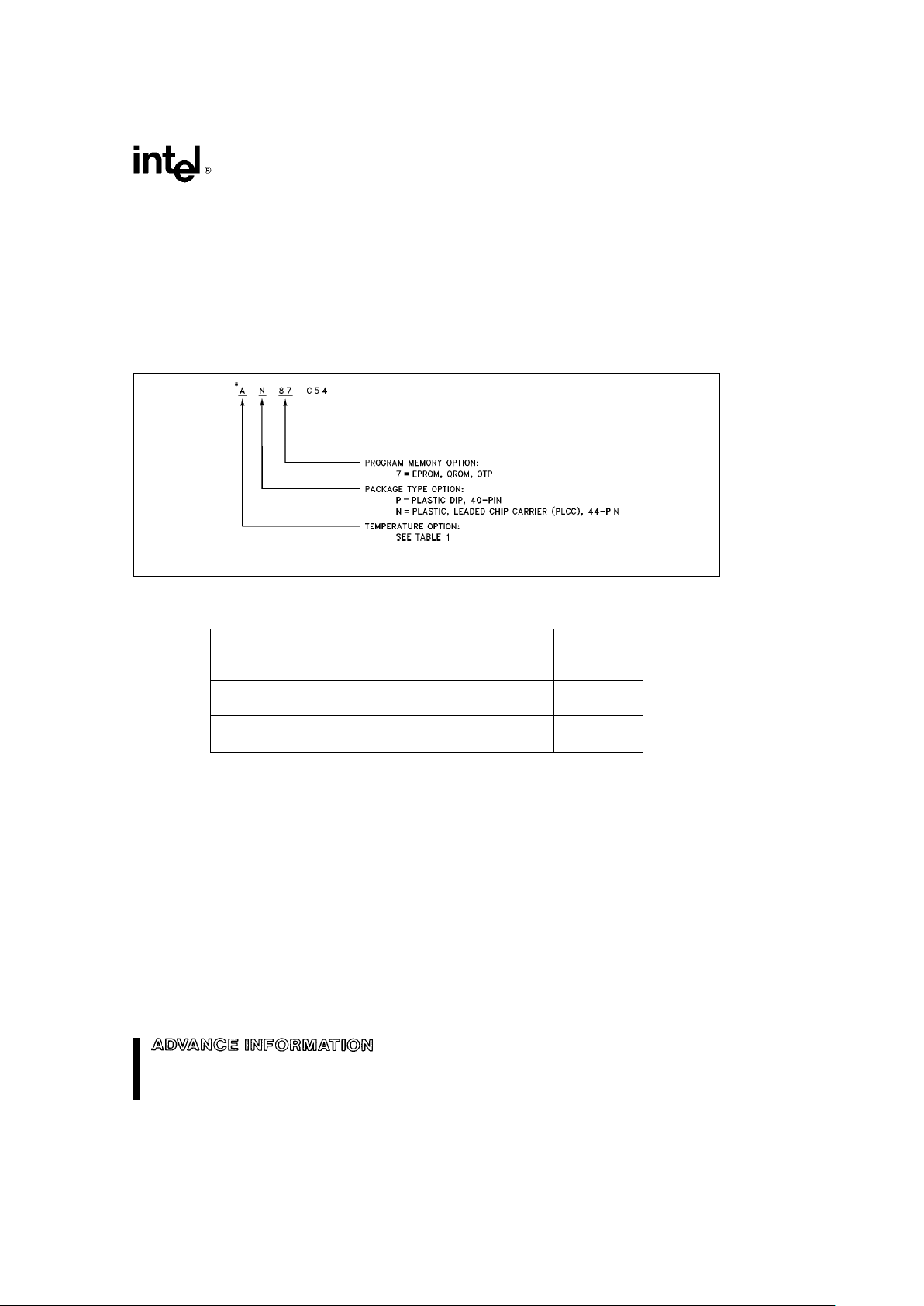

87C54 PRODUCT OPTIONS

Intel’s extended and automotive temperature range

products are designed to meet the needs of those

applications whose operating requirements exceed

commercial standards.

With the commercial standard temperature range,

operational characteristics are guaranteed over the

temperature range of 0

§

Ctoa70§C ambient. With

the extended temperature range option, operational

characteristics are guaranteed over the temperature

range of

b

40§Ctoa85§C ambient. For the automotive temperature range option, operational characteristics are guaranteed over the temperature range

of

b

40§Ctoa125§C ambient. The automotive, extended, and commercial temperature versions of the

MCS-51 product families are available with or without burn-in options.

As shown in Figure 2 temperature, burn-in, and

package options are identified by a one- or two-letter

prefix to the part number.

270849– 4

*Example:

AN87C54 indicates an automotive temperature range version of the 87C54 in a PLCC package with 16 Kbyte E PROM program memory.

Figure 2. Package Options

Table 1. Temperature Options

Temperature Temperature

Operating

Burn-In

Classification Designation

Temperature

Options

§

C Ambient

Extended T

b

40 toa85 Standard

L

b

40 toa85 Extended

Automotive A

b

40 toa125 Standard

B

b

40 toa125 Extended

3

AUTOMOTIVE 87C54/87C54-20

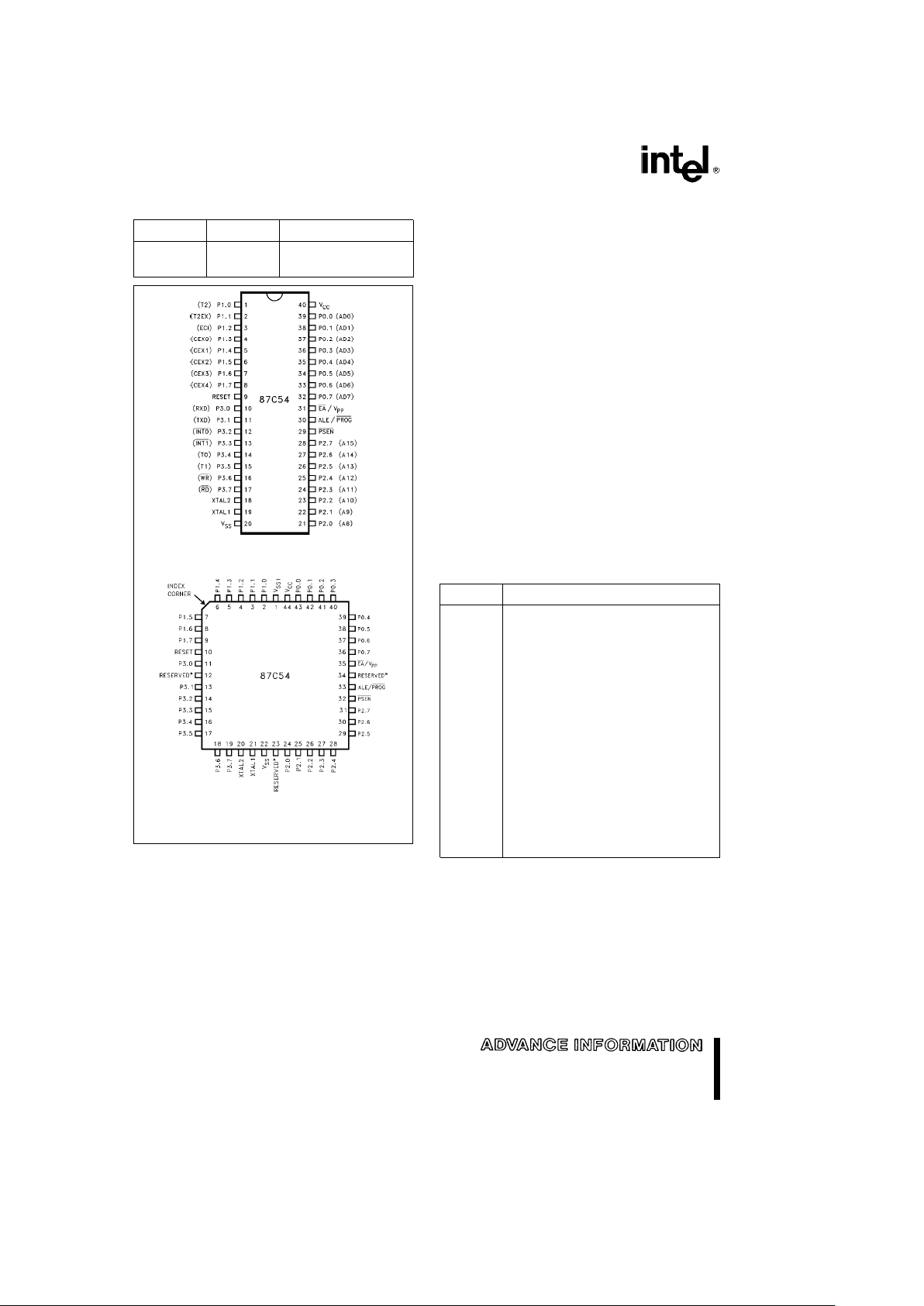

PACKAGES

Part Prefix Package Type

87C54 AP 40-Pin Plastic DIP

87C54 AN 44-Pin PLCC

270849– 2

DIP (PDIP)

270849– 3

*Do not connect reserved pins.

PAD (PLCC)

Figure 3. Pin Connections

PIN DESCRIPTIONS

VCC: Supply voltage.

V

SS

: Circuit ground.

V

SS1

: Secondary ground (in PLCC only). Provided to

reduce ground bounce and improve power supply

by-passing.

NOTE:

This pin is not a substitute for the V

SS

pin (pin 22).

Port 0: Port 0 is an 8-bit, open drain, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. Port 0 pins that have 1’s written to them

float, and in that state can be used as high-impedance inputs.

Port 0 is also the multiplexed low-order address and

data bus during accesses to external Program and

Data Memory. In this application it uses strong internal pullups when emitting1’s, and can source and

sink several LS TTL inputs.

Port 0 also receives the code bytes during EPROM

programming, and outputs the code bytes during

program verification. External pullup resistors are required during program verification.

Port 1: Port 1 is an 8-bit bidirectional I/O port with

internal pullups. The Port 1 output buffers can drive

LS TTL inputs. Port 1 pins that have 1’s written to

them are pulled high by the internal pullups, and in

that state can be used as inputs. As inputs, Port 1

pins that are externally pulled low will source current

(I

IL

, on the data sheet) because of the internal pull-

ups.

In addition, Port 1 serves the functions of the following special features of the 87C54:

Port Pin Alternate Function

P1.0 T2 (External Count Input to Timer/

Counter 2), Clock-Out

P1.1 T2EX (Timer/Counter 2 Capture/

Reload Trigger and Direction Control)

P1.2 ECI (External Count Input to the PCA)

P1.3 CEX0 (External I/O for Compare/

Capture Module 0)

P1.4 CEX1 (External I/O for Compare/

Capture Module 1)

P1.5 CEX2 (External I/O for Compare/

Capture Module 2)

P1.6 CEX3 (External I/O for Compare/

Capture Module 3)

P1.7 CEX4 (External I/O for Compare/

Capture Module 4)

Port 1 receives the low-order address bytes during

EPROM programming and verifying.

Port 2: Port 2 is an 8-bit bidirectional I/O port with

internal pullups. The Port 2 output buffers can drive

LS TTL inputs. Port 2 pins that have 1’s written to

them are pulled high by the internal pullups, and in

that state can be used as inputs. As inputs, Port 2

pins that are externally pulled low will source current

(I

IL

, on the data sheet) because of the internal pull-

ups.

4

AUTOMOTIVE 87C54/87C54-20

Port 2 emits the high-order address byte during

fetches from external Program Memory and during

accesses to external Data Memory that use 16-bit

addresses (MOVX

@

DPTR). In this application it

uses strong internal pullups when emitting 1’s. During accesses to external Data Memory that use 8-bit

addresses (MOVX

@

Ri), Port 2 emits the contents of

the P2 Special Function Register.

Some Port 2 pins receive the high-order address bits

during EPROM programming and program verification.

Port 3: Port 3 is an 8-bit bidirectional I/O port with

internal pullups. The Port 3 output buffers can drive

LS TTL inputs. Port 3 pins that have 1’s written to

them are pulled high by the internal pullups, and in

that state can be used as inputs. As inputs, Port 3

pins that are externally pulled low will source current

(I

IL

, on the data sheet) because of the pullups.

Port 3 also serves the functions of various special

features of the MCS-51 Family, as listed below:

Port Pin Alternate Function

P3.0 RXD (serial input port)

P3.1 TXD (serial output port)

P3.2 INT0

(external interrupt 0)

P3.3 INT1

(external interrupt 1)

P3.4 T0 (Timer 0 external input)

P3.5 T1 (Timer 1 external input)

P3.6 WR

(external data memory write strobe)

P3.7 RD (external data memory read strobe)

In addition, some Port 3 pins receive the high-order

address bits and act as control signals during

EPROM programming and programming verification.

RST: Reset input. A high on this pin for two machine

cycles while the oscillator is running resets the device. The port pins will be driven to their reset condition when a minimum V

IH1

is applied, whether the

oscillator is running or not. An internal pulldown resistor permits a power-on reset with only a capacitor

connected to V

CC

.

ALE: Address Latch Enable output pulse for latching

the low byte of the address during accesses to external memory. This pin (ALE/PROG

) is also the

program pulse input during EPROM programming for

the 87C54.

In normal operation ALE is emitted at a constant

rate of (/6 the oscillator frequency, and may be used

for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

Throughout the remainder of this data sheet, ALE

will refer to the signal coming out of the ALE/PROG

pin, and the pin will be referred to as the ALE/PROG

pin.

PSEN

: Program Store Enable is the read strobe to

external Program Memory.

When the 87C54 is executing code from external

Program Memory, PSEN

is activated twice each

machine cycle, except that two PSEN

activations

are skipped during each access to external Data

Memory.

EA

/VPP: External Access enable. EA must be

strapped to VSS in order to enable the device to

fetch code from external Program Memory locations

0000H to 0FFFFH. Note, however, that if any of the

Lock bits are programmed, EA will be internally

latched on reset.

EA

should be strapped to VCCfor internal program

executions.

This pin also receives the programming supply voltage (V

PP

) during EPROM programming.

XTAL1: Input to the inverting oscillator amplifier.

XTAL2: Output from the inverting oscillator amplifier.

OSCILLATOR CHARACTERISTICS

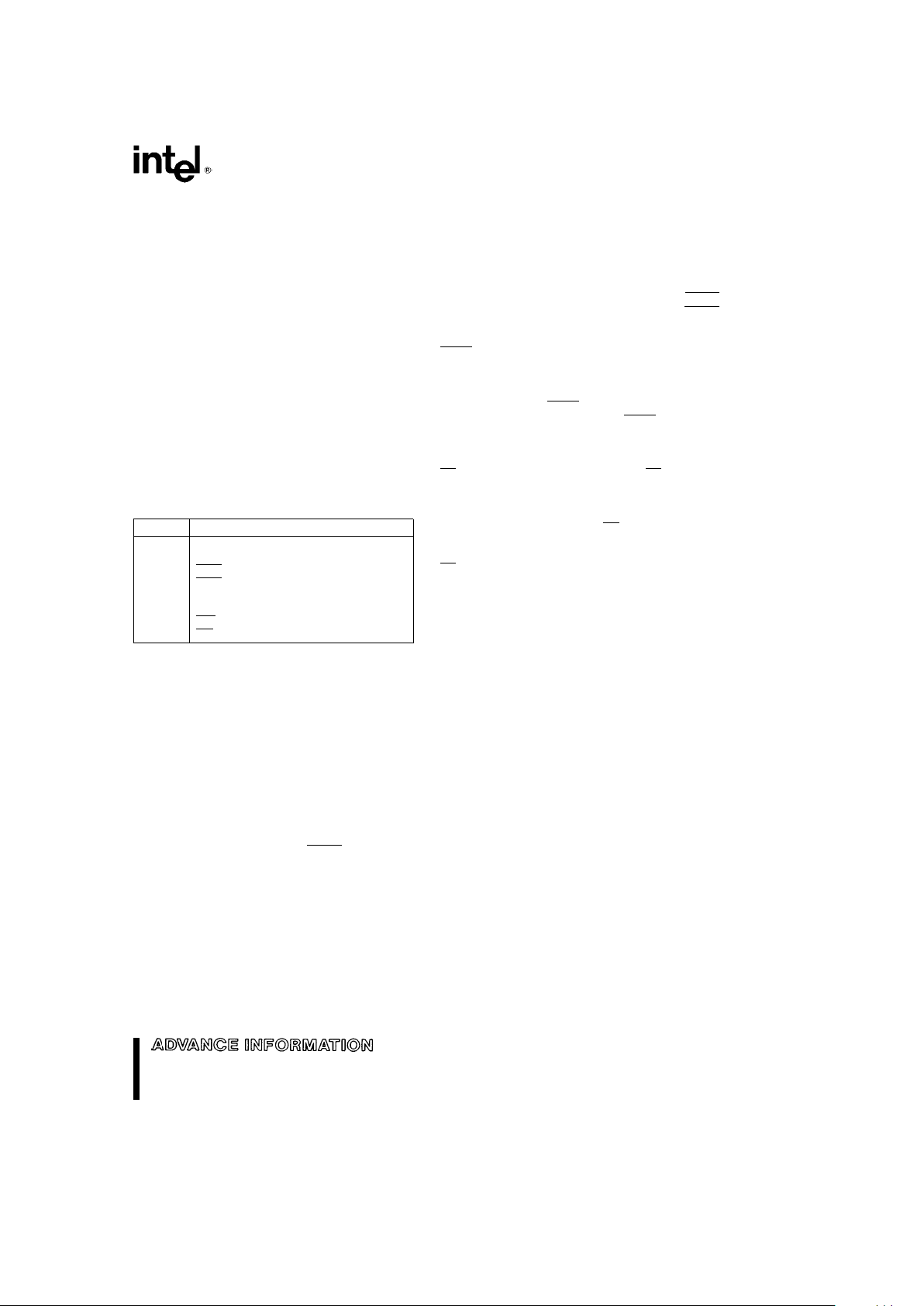

XTAL1 and XTAL2 are the input and output, respectively, of a inverting amplifier which can be configured for use as an on-chip oscillator, as shown in

Figure 4. Either a quartz crystal or ceramic resonator

may be used. More detailed information concerning

the use of the on-chip oscillator is available in Application Note AP-155, ‘‘Oscillators for Microcontrollers.’’

5

AUTOMOTIVE 87C54/87C54-20

270849– 5

C1, C2

e

30 pFg10 pF for Crystals

For Ceramic Resonators, contact resonator manufacturer.

Figure 4. Oscillator Connections

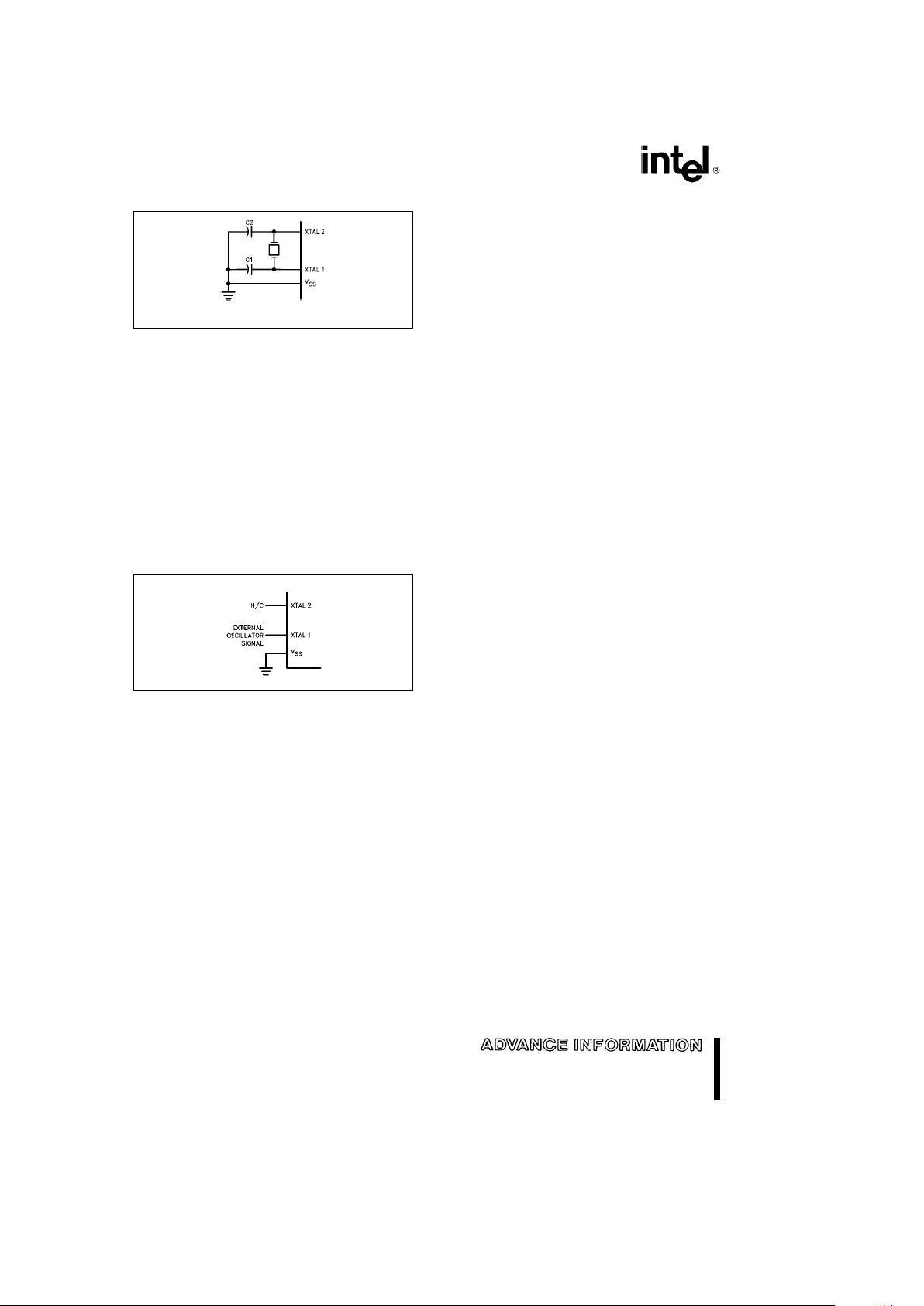

To drive the device from an external clock source,

XTAL1 should be driven, while XTAL2 floats, as

shown in Figure 5. There are no requirements on the

duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum

high and low times specified on the data sheet must

be observed.

An external oscillator may encounter as much as a

100 pF load at XTAL1 when it starts up. This is due

to interaction between the amplifier and its feedback

capacitance. Once the external signal meets the V

IL

and VIHspecifications the capacitance will not exceed 20 pF.

270849– 6

Figure 5. External Clock Drive Configuration

IDLE MODE

The user’s software can invoke the Idle Mode. When

the microcontroller is in this mode, power consumption is reduced. The Special Function Registers and

the onboard RAM retain their values during Idle, but

the processor stops executing instructions. Idle

Mode will be exited if the chip is reset or if an enabled interrupt occurs.

POWER DOWN MODE

To save even more power, a Power Down mode can

be invoked by software. In this mode, the oscillator

is stopped and the instruction that invoked Power

Down is the last instruction executed. The on-chip

RAM and Special Function Registers retain their values until the Power Down mode is terminated.

On the 87C54 either a hardware reset or an external

interrupt can cause an exit from Power Down. Reset

redefines all the SFRs but does not change the onchip RAM. An external interrupt allows both the

SFRs and on-chip RAM to retain their values.

To properly terminate Power down the reset or external interrupt should not be executed before V

CC

is

restored to its normal operating level and must be

held active long enough for the oscillator to restart

and stabilize (normally less than 10 ms).

With an external interrupt, INT0 or INT1 must be enabled and configured as level-sensitive. Holding the

pin low restarts the oscillator but bringing the pin

back high completes the exit. (The oscillator must be

allowed time to stabilize after start up, before this pin

is released high.) Once the interrupt is serviced, the

next instruction to be executed after RETI will be the

one following the instruction that put the device into

Power Down.

DESIGN CONSIDERATION

When the idle mode is terminated by a hardware

reset, the device normally resumes program execution, from where it left off, up to two machine cycles

before the internal reset algorithm takes control. Onchip hardware inhibits access to internal RAM in this

event, but access to the port pins is not inhibited. To

eliminate the possibility of an unexpected write when

Idle is terminated by reset, the instruction following

the one that invokes Idle should not be one that

writes to a port pin or to external memory.

6

Loading...

Loading...