Intel Corporation N87C51GB-1 Datasheet

*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

November 1994COPYRIGHT©INTEL CORPORATION, 1995 Order Number: 272337-002

8XC51GB

CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

Commercial/Express

87C51GBÐ8 Kbytes OTP/8 Kbytes Internal Program Memory

83C51GBÐ8 Kbytes Factory Programmable ROM

80C51GBÐCPU with RAM and I/O

8XC51GBÐ3.5 MHz to 12 MHz

g

20% V

CC

8XC51GB-1Ð3.5 MHz to 16 MHzg20% V

CC

Y

8 Kbytes On-Chip ROM/OTP ROM

Y

256 Bytes of On-Chip Data RAM

Y

Two Programmable Counter Arrays

with:

Ð 2 x 5 High Speed Input/Output

Channels Compare/Capture

Ð Pulse Width Modulators

Ð Watchdog Timer Capabilities

Y

Three 16-Bit Timer/Counters with

Ð Four Programmable Modes:

Ð Capture, Baud Rate Generation

(Timer 2)

Y

Dedicated Watchdog Timer

Y

8-Bit, 8-Channel A/D with:

Ð Eight 8-Bit Result Registers

Ð Four Programmable Modes

Y

Programmable Serial Channel with:

Ð Framing Error Detection

Ð Automatic Address Recognition

Y

Serial Expansion Port

Y

Programmable Clock Out

Y

Extended Temperature Range:

(

b

40§Ctoa85§C)

Y

48 Programmable I/O Lines with

40 Schmitt Trigger Inputs

Y

15 Interrupt Sources with:

Ð 7 External, 8 Internal Sources

Ð 4 Programmable Priority Levels

Y

Pre-Determined Port States on Reset

Y

High Performance CHMOS Process

Y

TTL and CHMOS Compatible Logic

Levels

Y

Power Saving Modes

Y

64K External Data Memory Space

Y

64K External Program Memory Space

Y

Three Level Program Lock System

Y

ONCE (ON-Circuit Emulation) Mode

Y

Quick Pulse Programming Algorithm

Y

MCSÉ51 Microcontroller Fully

Compatible Instruction Set

Y

Boolean Processor

Y

Oscillator Fail Detect

Y

Available in 68-Pin PLCC

MEMORY ORGANIZATION

PROGRAM MEMORY: Up to 8 Kbytes of the program memory can reside in the on-chip ROM. Also, the device

can address up to 64K of program memory external to the chip.

DATA MEMORY: This microcontroller has a 256 x 8 on-chip RAM. In addition it can address up to 64 Kbytes of

external data memory.

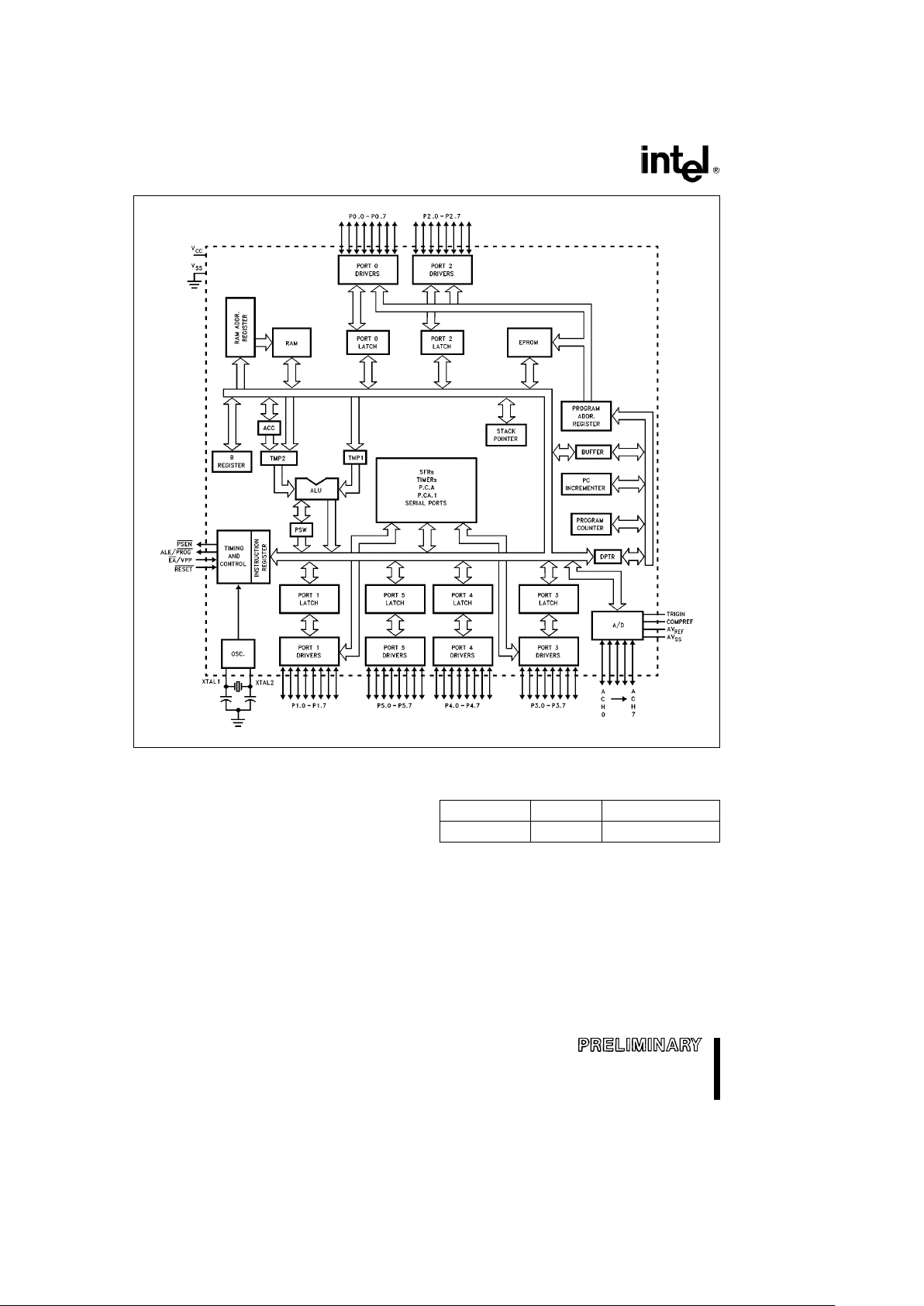

The Intel 8XC51GB is a single-chip control oriented microcontroller which is fabricated on Intel’s CHMOS III-E

technology. The 8XC51GB is an enhanced version of the 8XC51FA and uses the same powerful instruction

set and architecture as existing MCS 51 microcontroller products. Added features make it an even more

powerful microcontroller for applications that require On-Chip A/D, Pulse Width Modulation, High Speed I/O,

up/down counting capabilities and memory protection features. It also has a more versatile serial channel that

facilitates multi-processor communications.

8XC51GB

272337– 1

Figure 1. 8XC51GB Block Diagram

PROCESS INFORMATION

This device is manufactured on P629.0, a CHMOS

III-E process. Additional process and reliability information is available in Intel’s Components Quality

and Reliability Handbook, Order No. 210997.

PACKAGES

Part Prefix Package Type

8XC51GB N 68-Pin PLCC

2

8XC51GB

PARALLEL I/O PORTS

The 8XC51GB contains six 8-bit parallel I/O ports.

All six ports are bidirectional and consist of a latch,

an output driver, and an input buffer. Many of the

port pins have multiplexed I/O and control functions.

Port Pins as Outputs

Port 0 has open drain outputs when it is not serving

as the external data bus. The internal pullup is active

only when the pin is outputting a logic 1 during external memory access. An external pullup resistor is

required on Port 0 when it is serving as an output

port.

Ports 1, 2, 3, 4, and 5 have quasi-bidirectional outputs. A strong pullup provides a fast rise time when

the pin is set to a logic 1. This pullup turns on for two

oscillator periods to drive the pin high and then turns

off. The pin is held high by a weak pullup.

Writing the P0, P1, P2, P3, P4 or P5 Special Function

Register sets the corresponding port pins. All six

port registers are bit addressable.

Port Pins as Inputs

The pins of all six ports are configured as inputs by

writing a logic 1 to them. Since Port 0 is an open

drain port, it provides a very high input impedance.

Since pins of Port 1, 2, 3, 4 and 5 have weak pullups

(which are always on), they source a small current

when driven low externally. All ports except Port 0

have Schmitt trigger inputs.

Port States During Reset

Ports 0 and 3 reset asynchronously to a one and

Ports 1, 2, 4, and 5 reset to a zero asynchronously.

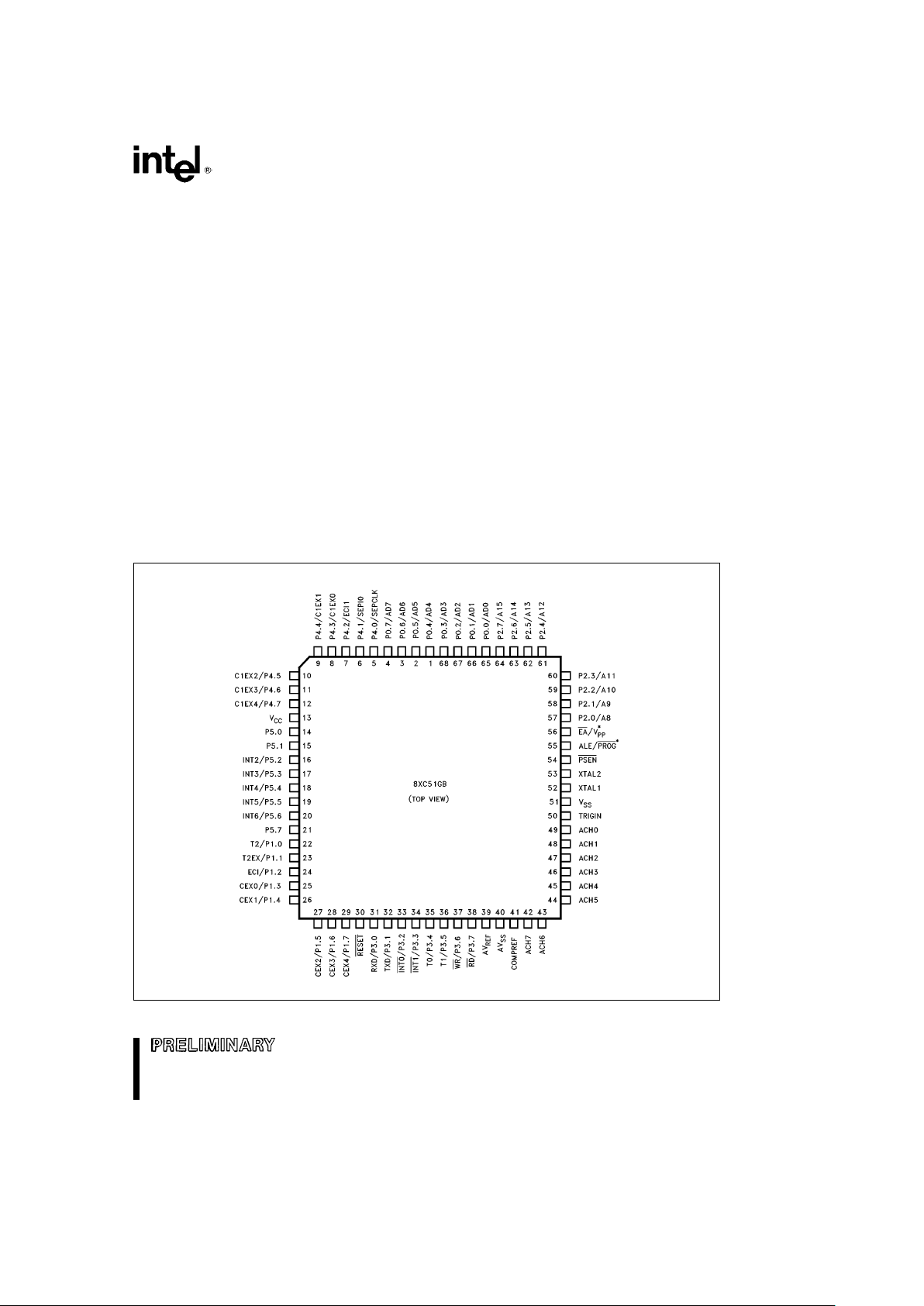

PIN DESCRIPTIONS

The 8XC51GB will be packaged in the 68-lead PLCC

package. Its pin assignment is shown in Figure 2.

V

CC

: Supply Voltage.

V

SS

: Circuit Ground.

Diagram is for Pin Reference Only. Package Size is Not to Scale.

272337– 2

*OTP only

Figure 2. Pin Connections

3

8XC51GB

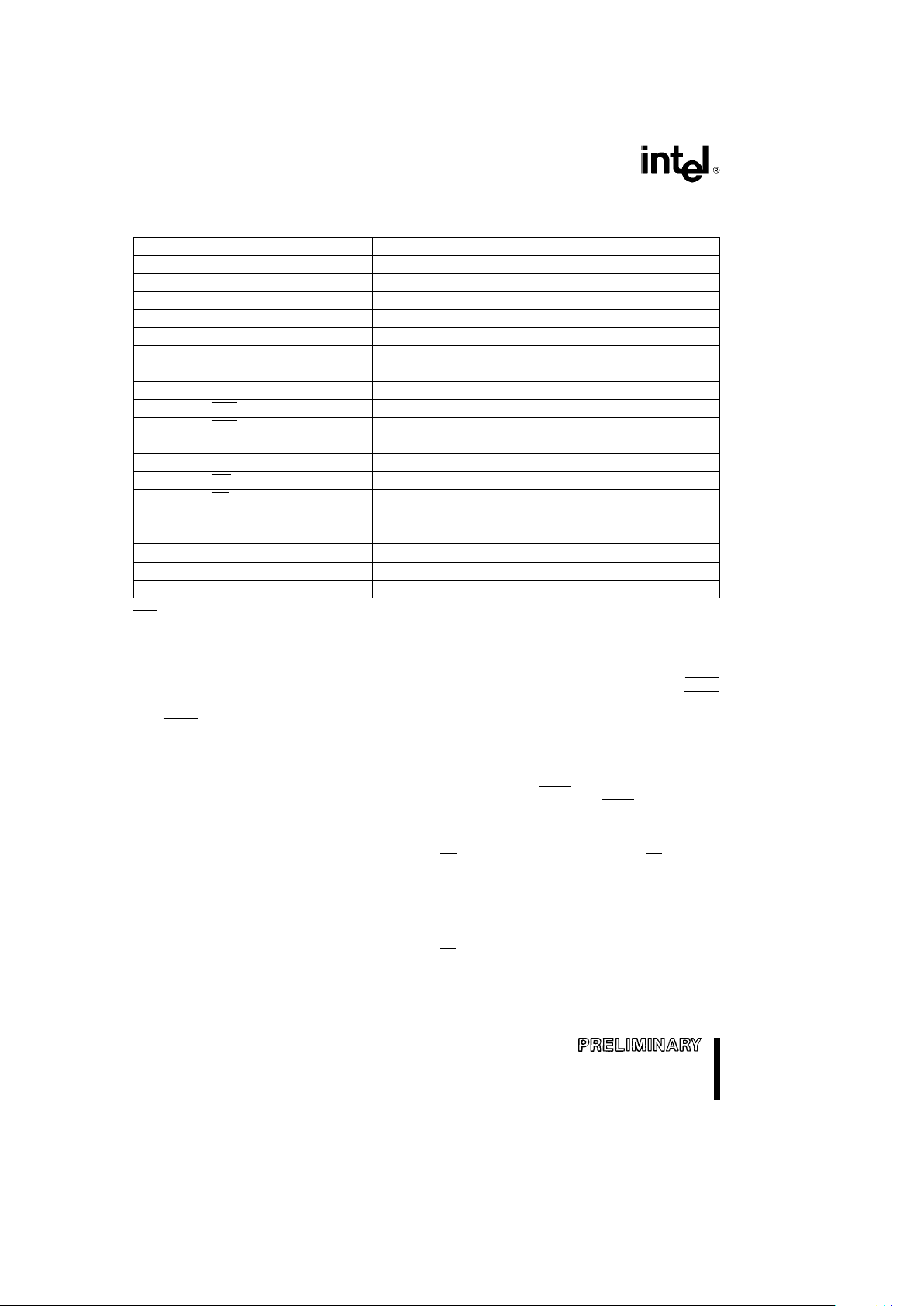

ALTERNATE PORT FUNCTIONS

Ports 0, 1, 2, 3, 4 and 5 have alternate functions as well as their I/O function as described below.

Port Pin Alternate Function

P0.0/ADO–P0.7/AD7 Multiplexed Address/Data for External Memory

P1.0/T2 Timer 2 External Clock Input/Clock-Out

P1.1/T2EX Timer 2 Reload/Capture/Direction Control

P1.2/ECI PCA External Clock Input

P1.3/CEXO–P1.7/CEX4 PCA Capture Input, Compare/PWM Output

P2.0/A8–P2.7/A15 High Byte of Address for External Memory

P3.0/RXD Serial Port Input

P3.1/TXD Serial Port Output

P3.2/INT0 External Interrupt 0

P3.3/INT1 External Interrupt 1

P3.4/T0 Timer 0 External Clock Input

P3.5/T1 Timer 1 External Clock Input

P3.6/WR Write Strobe for External Memory

P3.7/RD Read Strobe for External Memory

P4.0/SEPCLK Clock Source for Serial Expansion Port

P4.1/SEPDAT Data I/O for the Serial Expansion Port

P4.2/ECI1 PCA1 External Clock Input

P4.3/C1EX0–P4.7/C1EX4 PCA1 Capture Input, Compare/PWM Output

P5.2/INT2–P5.6/INT6 External Interrupt INT2 – INT6

RST: Reset input. A low on this pin for two machine

cycles while the oscillator is running resets the device. The port pins will be driven to their reset condition when a voltage below V

IL

max voltage is applied, whether the oscillator is running or not. An

internal pullup resistor permits a power-on reset with

only a capacitor connected to V

SS

.

ALE/PROG

: Address Latch Enable output pulse for

latching the low byte of the address during accesses

to external memory. This pin (ALE/PROG

) is also

the program pulse input during programming of the

87C51GB.

In normal operation ALE is emitted at a constant

rate of (/6 the oscillator frequency, and may be used

for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

If desired, ALE operation can be disabled by setting

bit 0 of SFR location 8EH. With this bit set, the pin is

weakly pulled high. However, the ALE disable feature will be suspended during a MOVX or MOVC instruction, idle mode, power down mode and ICE

mode. The ALE disable feature will be terminated by

reset. When the ALE disable feature is suspended or

terminated, the ALE pin will no longer be pulled up

weakly. Setting the ALE-disable bit has no affect if

the microcontroller is in external execution mode.

Throughout the remainder of this data sheet, ALE

will refer to the signal coming out of the ALE/PROG

pin, and the pin will be referred to as the ALE/PROG

pin.

PSEN

: Program Store Enable is the read strobe to

external Program Memory.

When the 8XC51GB is executing code from external

Program Memory, PSEN is activated twice each machine cycle, except that two PSEN

activations are

skipped during each access to external Data Memory.

EA

/VPP: External Access enable. EA must be

strapped to V

SS

in order to enable the device to

fetch code from external Program Memory locations

0000H to 1FFFH. Note, however, that if either of the

Program Lock bits are programmed, EA

will be inter-

nally latched on reset.

EA

should be strapped to VCCfor internal program

executions.

4

8XC51GB

This pin also receives the 12.75V programming supply voltage (V

PP

) during programming (OTP only).

XTAL1: Input to the inverting oscillator amplifier.

XTAL2: Output from the inverting oscillator amplifi-

er.

A/D CONVERTER

The 8XC51GB A/D converter has a resolution of 8

bits and an accuracy of

g

1 LSB (g2 LSB for channels 0 and 1). The conversion time for a single channel is 20 ms at a clock frequency of 16 MHz with the

sample and hold function included. Independent

supply voltages are provided for the A/D. Also, the

A/D operates both in Normal Mode or in Idle Mode.

The A/D has 8 analog input pins; ACH0 (A/D CHannel 0) . . . ACH7, 1 reference input pin; COMPREF

(COMParison REFerence), 1 control input pin; TRIGIN (TRIGger IN), and 2 power pins; AVREF (Voltage REFerence) and analog ground (ANalog

GrouND). In addition, the A/D has 8 conversion result registers; ADRES0 (A/D result for channel 0) . . .

ADRES7, 1 comparison result register; ACMP (Analog Comparison), and 1 control register; ACON (A/D

Control).

The control bit ACE (A/D Conversion Enable) in

ACON controls whether the A/D is in operation or

not. ACE

e

0 idles the A/D. ACEe1 enables A/D

conversion. The control bit AIM (A/D Input mode) in

ACON controls the mode of channel selection. AIM

e

0 is the Scan Mode, and AIMe1 is the Select

Mode. The result registers ADRES4 . . . ADRES7 always contain the result of a conversion from the corresponding channels ACH4 . . . CH7. However, the

result registers ADRES0 . . . ADRES3 depend on the

mode selected. In the scan mode, ADRES0 . . . ADRES3 contain the values from ACH0 . . . ACH3. In

the Select Mode, one of the four channels ACH0 . . .

ACH3 is converted four times, and the four values

are stored sequentially in locations ADRES0 . . . ADRES3. Its channel is selected by bits ACS1 and

ACS0 (A/D Channel Select 1 and 0) in ACON.

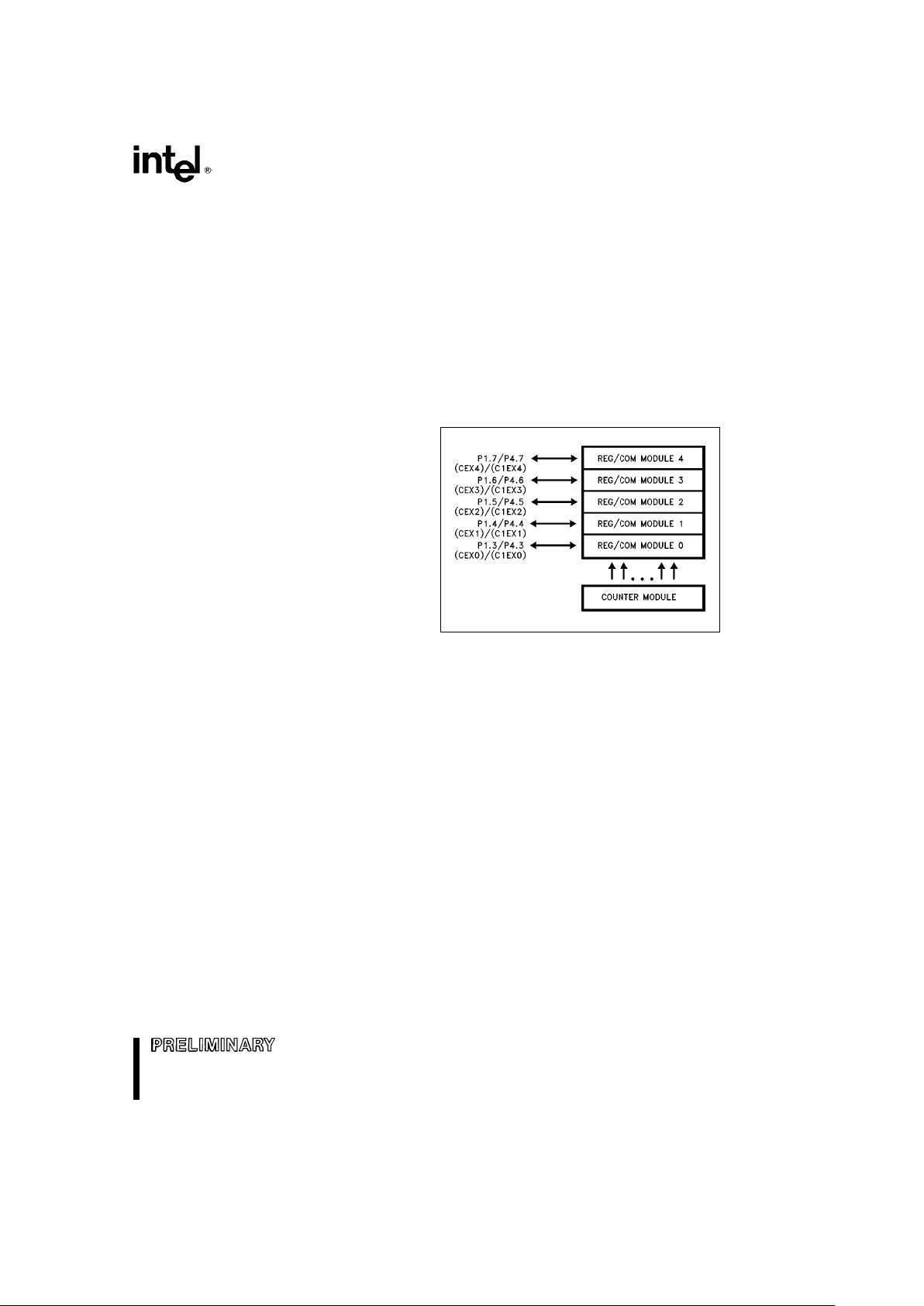

PROGRAMMABLE COUNTER ARRAYS

The Programmable Counter Arrays (PCA–PCA1) are

each made up of a Counter Module and five Register/Comparator Modules as shown below. The

16-bit output of the counter module is available to all

five Register/Comparator Modules, providing one

common timing reference. Each Register/Comparator Module is associated with a pin of Port 1 or Port 4

and is capable of performing input capture, output

compare and pulse width modulation functions. The

PCAs are exactly the same in function except for the

addition of clock input sources on PCA1.

The PCA Counter and five Register/Comparator

Modules each have a status bit in the CCON/

C1CON Special Function Registers. These six

status bits are set according to the selected modes

of operation described below. The CCON/C1CON

Register provides a convenient means to determine

which of the six PCA/PCA1 interrupts has occurred.

The EC Bit in the IE (Interrupt Enable) Special Function Register is a global interrupt enable for the PCA.

272337– 3

Figure 3. Programmable Counter Arrays

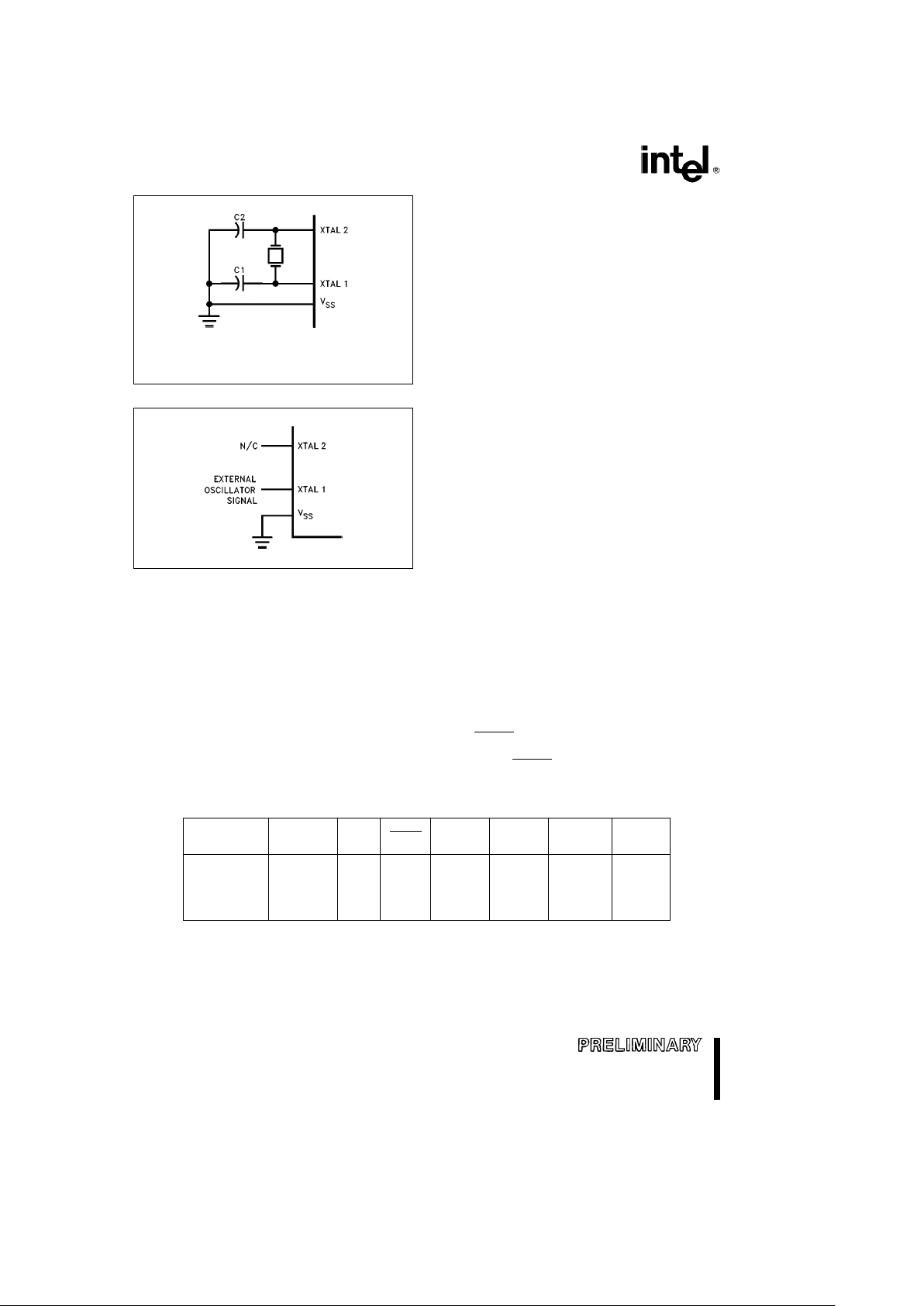

OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in

Figure 4. Either a quartz crystal or ceramic resonator

may be used. More detailed information concerning

the use of the on-chip oscillator is available in Application Note AP-155, ‘‘Oscillators for Microcontrollers,’’ Order No. 230659.

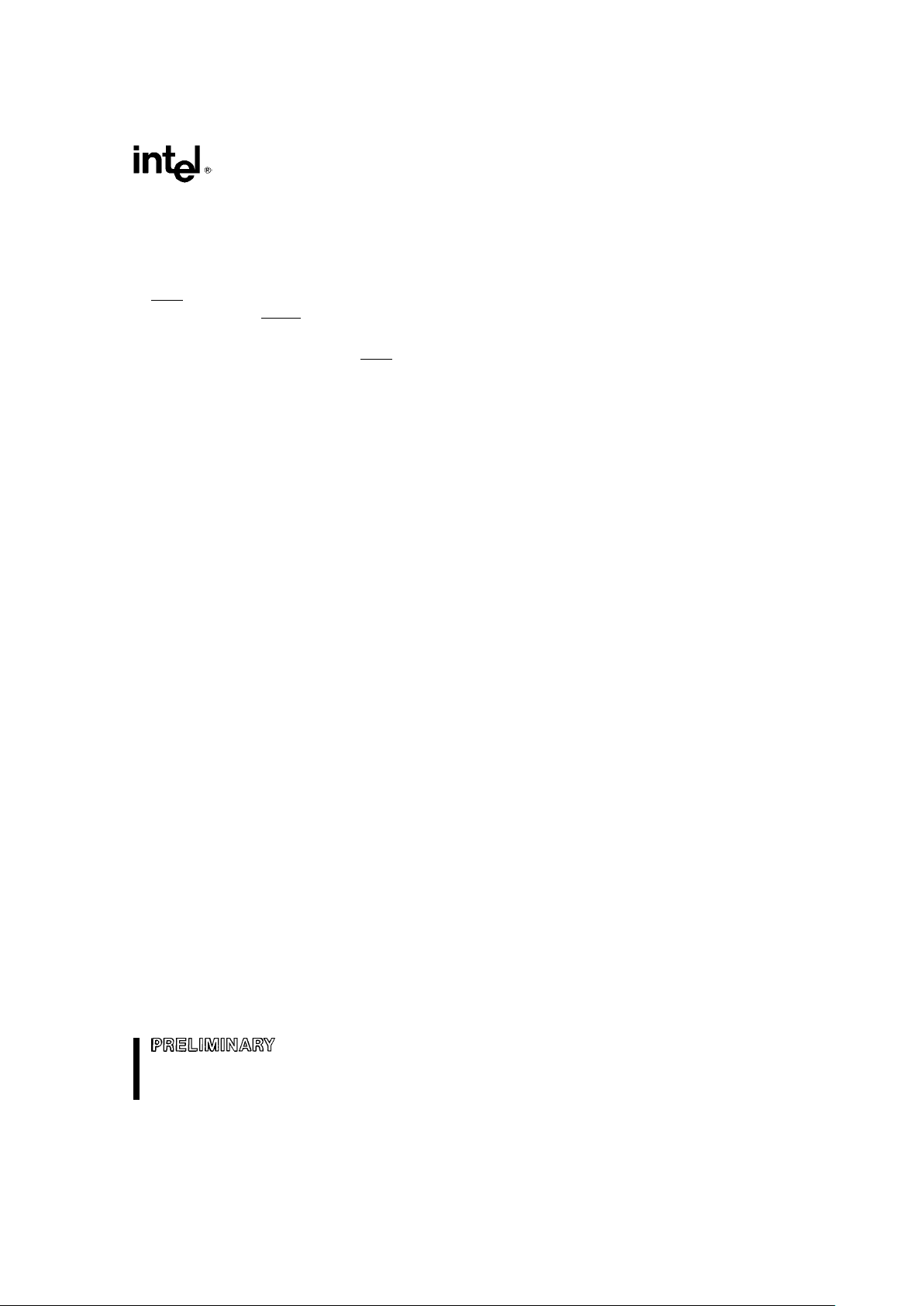

To drive the device from an external clock source,

XTAL should be driven, while XTAL2 floats, as

shown in Figure 5. There are no requirements on the

duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum

high and low times specified on the data sheet must

be observed.

5

8XC51GB

272337– 4

C1, C2e30 pFg10 pF for Crystals

For Ceramic Resonators contact resonator

manufacturer.

Figure 4. Oscillator Connections

272337– 5

Figure 5. External Clock Drive Configuration

IDLE MODE

The user’s software can invoke the Idle Mode. When

the microcontroller is in this mode, power consumption is reduced. The Special Function Registers and

the onboard RAM retain their values during idle, peripherals continue to operate, but the processor

stops executing instructions. Idle Mode will be exited

if the chip is reset or if an enabled interrupt occurs.

The PCA timer/counter can optionally be left running or paused during Idle Mode. The Watchdog

Timer continues to count in Idle Mode and must be

serviced to prevent a device RESET while in Idle.

POWER DOWN MODE

To save even more power, a Power Down mode can

be invoked by software. In this mode, the oscillator

is stopped and the instruction that invoked Power

Down is the last instruction executed. The on-chip

RAM and Special Function Registers retain their values until the Power Down mode is terminated.

On the 8XC51GB either a hardware reset or an external interrupt can cause an exit from Power Down.

Reset redefines all the SFRs but does not change

the on-chip RAM. An external interrupt does not redefine the SFR’s or change the on-chip RAM. An

external interrupt will modify the interrupt associated

SFR’s in the same way an interrupt will in all other

modes. The interrupt must be enabled and configured as level sensitive. To properly terminate Power

Down the reset or external interrupt should not be

executed before V

CC

is restored to its normal operating level. The reset or external interrupt must be

held active long enough for the oscillator to restart

and stabilize. The Oscillator Fail Detect must be disabled prior to entering Power Down.

DESIGN CONSIDERATIONS

#

When the idle mode is terminated by a hardware

reset, the device normally resumes program execution, from where it left off, up to two machine

cycles before the internal reset algorithm takes

control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins

is not inhibited. To eliminate the possibility of an

unexpected write when Idle is terminated by reset, the instruction following the one that invokes

Idle should not be one that writes to a port pin or

to external memory.

#

As RESET rises, the 8XC51GB will remain in reset for up to 5 machine cycles (60 oscillator periods) after RESET

reaches V

IH1

.

Table 1. Status of the External Pins during Idle and Power Down

Mode

Program

ALE PSEN PORT0 PORT1 PORT2 PORT3

Memory

Idle Internal 1 1 Data Data Data Data

Idle External 1 1 Float Data Address Data

Power Down Internal 0 0 Data Data Data Data

Power Down External 0 0 Float Data Data Data

NOTE:

For more detailed information on the reduced power modes refer to current Embedded Microcontrollers

and Processors Handbook Volume I (Order No. 270645), and Application Note AP-252 (Embedded

Applications Handbook, Order No. 270648), ‘‘Designing with the 80C51BH.’’

6

8XC51GB

ONCE MODE

The ONCE (‘‘On-Circuit Emulation’’) Mode facilitates

testing and debugging of systems using the

8XC51GB without removing it from the circuit. The

ONCE Mode is invoked by:

1) Pulling ALE low while the device is in reset and

PSEN

is high;

2) Holding ALE low as RESET is deactivated.

While the device is in ONCE Mode, the Port 0 pins

float, and the other port pins and ALE and PSEN

are

weakly pulled high. The oscillator circuit remains active. While the 8XC51GB is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

Watchdog Timer (WDT)

The 8XC51GB contains a dedicated Watchdog Timer (WDT) to allow recovery from a software or hardware upset. The WDT consists of a 14-bit counter

which is cleared on Reset, and subsequently incremented every machine cycle. While the oscillator is

running, the WDT will be incrementing and cannot

be disabled. The counter may be reset by writing

1EH and E1H in sequence to the WDTRST Special

Function Register. If the counter is not reset before

it reaches 3FFFH (16383D), the chip will be forced

into a reset sequence by the WDT. This works out to

12.28 ms

@

16 MHz. WDTRST is a write only register. The WDT does not force the external reset pin

low.

While in Idle mode the WDT continues to count. If

the user does not wish to exit Idle with a reset, then

the processor must be periodically ‘‘woken up’’ to

service the WDT. In Power Down mode, the WDT

stops counting and holds its current value.

Serial Expansion Port (SEP)

The Serial Expansion Port is a half-duplex synchronous serial interface with the following features:

Four Clock FrequenciesÐ XTAL/12, 24, 48, 96.

Four Interface ModesÐ High/Low/Falling/Rising

Edges.

Interrupt Driven.

Oscillator Fail Detect (OFD)

The Oscillator Fail Detect circuitry triggers a reset if

the oscillator frequency is lower than the OFD trigger frequency. It can be disabled by software by writing E1H followed by 1EH to the OFDCON register.

Before going into Power Down Mode, the OFD must

be disabled or it will force the GB out of Power

Down. The OFD has the following features.

OFD Trigger Frequency: Below 20 KHz, the

8XC51GB will be held in reset. Above 400 KHz,

the 8XC51GB will not be held is reset.

Functions in Normal and Idle Modes.

Reactivated by Reset (or External Interrupt Zero/One Pins) after Software Disable.

8XC51GB EXPRESS

The Intel EXPRESS products are designed to meet

the needs of those applications whose operating requirements exceed commercial standards.

With the commercial standard temperature range,

operational characteristics are guaranteed over the

temperature range of 0

§

Ctoa70§C. With the extended temperature range option, operational characteristics are guaranteed over the range of

b

40§C

to

a

85§C. The 87C51GB EXPRESS is packaged in

the 68-lead PLCC package. In order to designate a

part as an EXPRESS part, a ‘‘T’’ is added as a prefix

to the part number. TN87C51GB denotes an EXPRESS part in a PLCC package.

All AC and DC parameters in this data sheet apply to

the EXPRESS devices.

7

Loading...

Loading...