*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

November 1992COPYRIGHT©INTEL CORPORATION, 1995 Order Number: 270640-004

80C187

80-BIT MATH COPROCESSOR

Y

High Performance 80-Bit Internal

Architecture

Y

Implements ANSI/IEEE Standard 7541985 for Binary Floating-Point

Arithmetic

Y

Upward Object-Code Compatible from

8087

Y

Fully Compatible with 387DX and 387SX

Math Coprocessors. Implements all 387

Architectural Enhancements over 8087

Y

Directly Interfaces with 80C186 CPU

Y

80C186/80C187 Provide a Software/

Binary Compatible Upgrade from

80186/82188/8087 Systems

Y

Expands 80C186’s Data Types to

Include 32-, 64-, 80-Bit Floating-Point,

32-, 64-Bit Integers and 18-Digit BCD

Operands

Y

Directly Extends 80C186’s Instruction

Set to Trigonometric, Logarithmic,

Exponential, and Arithmetic

Instructions for All Data Types

Y

Full-Range Transcendental Operations

for SINE, COSINE, TANGENT,

ARCTANGENT, and LOGARITHM

Y

Built-In Exception Handling

Y

Eight 80-Bit Numeric Registers, Usable

as Individually Addressable General

Registers or as a Register Stack

Y

Available in 40-Pin CERDIP and 44-Pin

PLCC Package

(See Packaging Outlines and Dimensions, OrderÝ231369)

The Intel 80C187 is a high-performance math coprocessor that extends the architecture of the 80C186 with

floating-point, extended integer, and BCD data types. A computing system that includes the 80C187 fully

conforms to the IEEE Floating-Point Standard. The 80C187 adds over seventy mnemonics to the instruction

set of the 80C186, including support for arithmetic, logarithmic, exponential, and trigonometric mathematical

operations. The 80C187 is implemented with 1.5 micron, high-speed CHMOS III technology and packaged in

both a 40-pin CERDIP and a 44-pin PLCC package. The 80C187 is upward object-code compatible from the

8087 math coprocessor and will execute code written for the 80387DX and 80387SX math coprocessors.

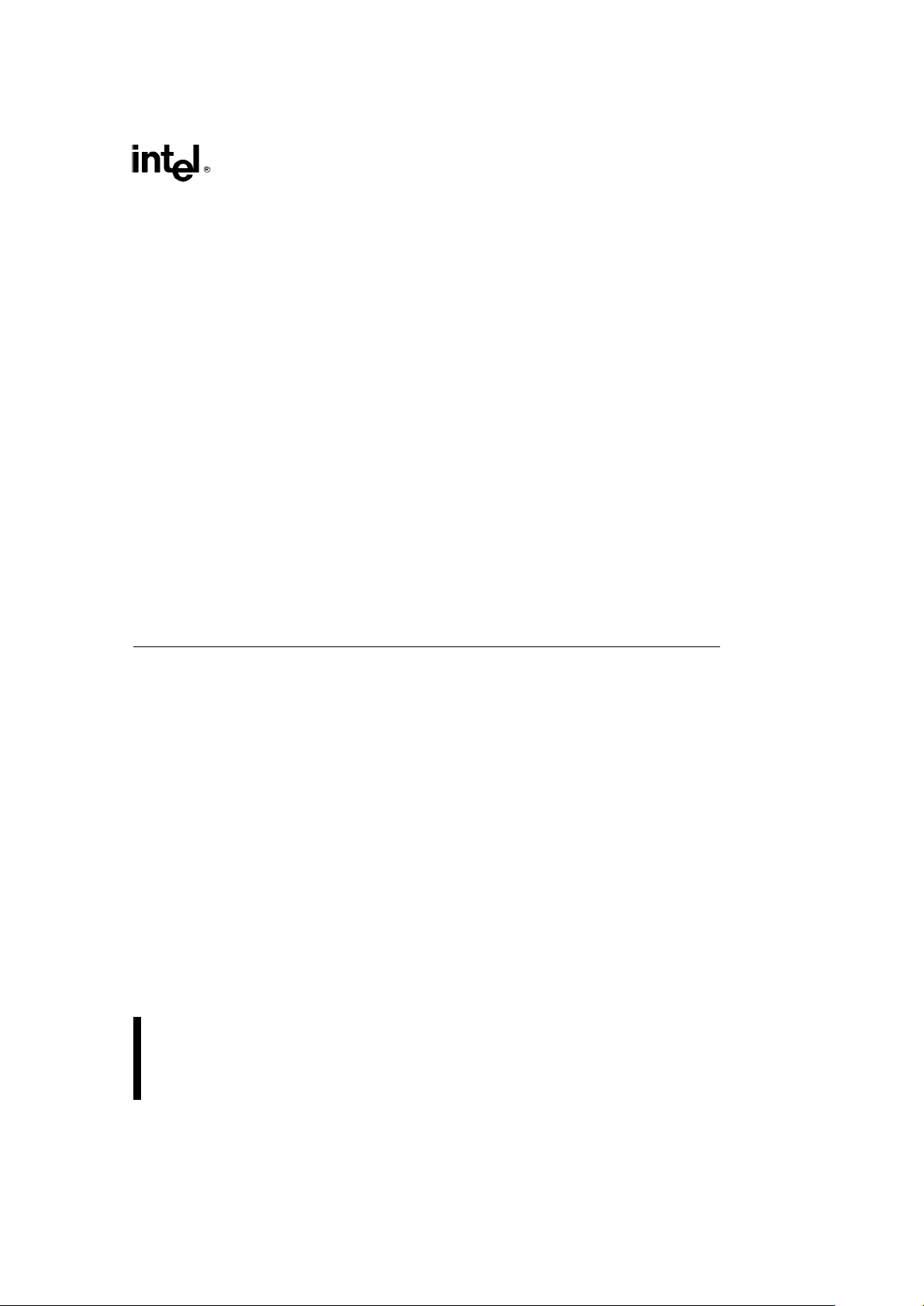

80C187

270640– 1

Figure 1. 80C187 Block Diagram

2

80C187

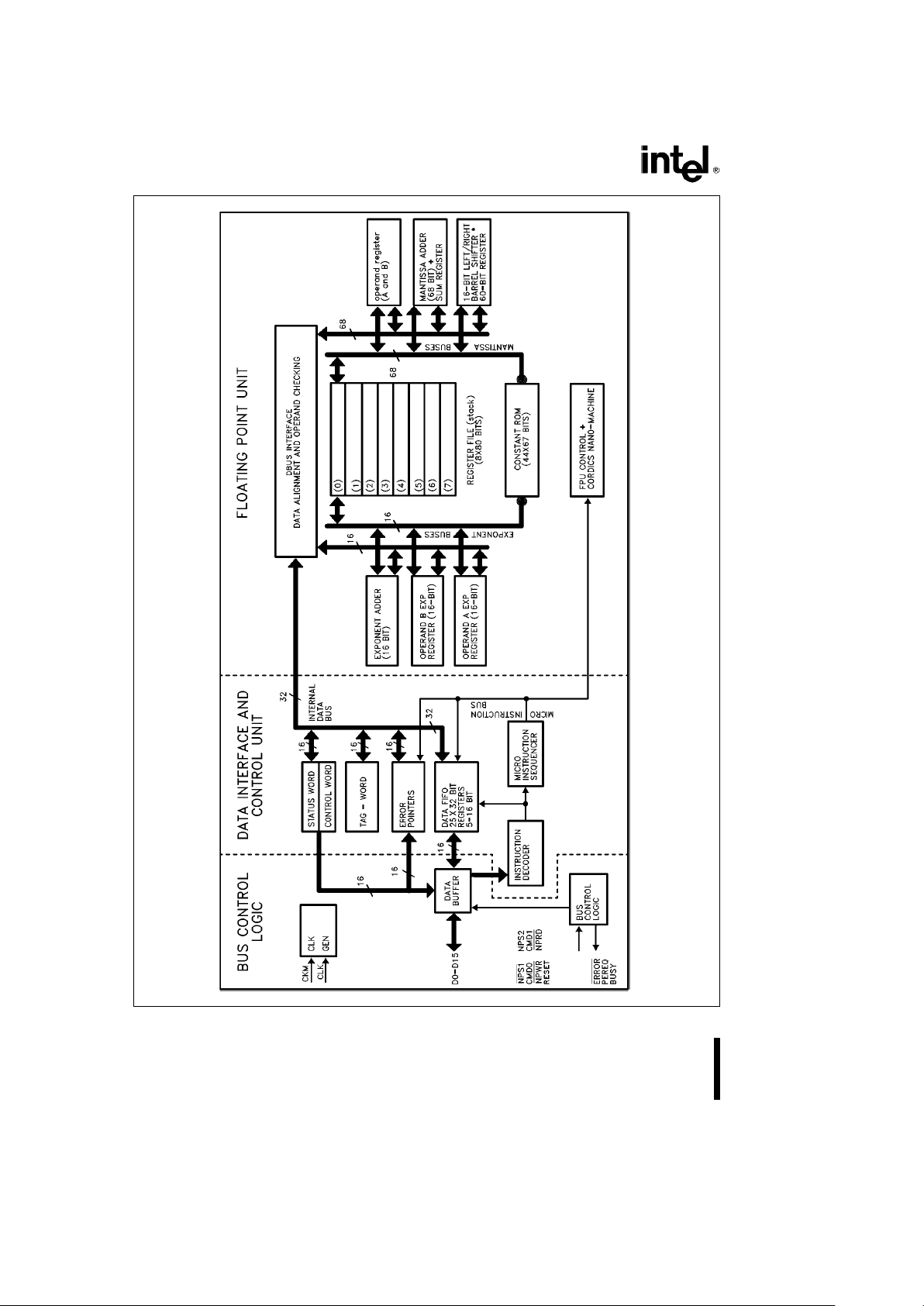

80C187 Data Registers

79 78 64 63 0

R0 SIGN EXPONENT SIGNIFICAND

R1

R2

R3

R4

R5

R6

R7

15 0 15 0

CONTROL REGISTER INSTRUCTION POINTER

STATUS REGISTER DATA POINTER

TAG WORD

Figure 2. Register Set

FUNCTIONAL DESCRIPTION

The 80C187 Math Coprocessor provides arithmetic

instructions for a variety of numeric data types. It

also executes numerous built-in transcendental

functions (e.g. tangent, sine, cosine, and log functions). The 80C187 effectively extends the register

and instruction set of the 80C186 CPU for existing

data types and adds several new data types as well.

Figure 2 shows the additional registers visible to programs in a system that includes the 80C187. Essentially, the 80C187 can be treated as an additional

resource or an extension to the CPU. The 80C186

CPU together with an 80C187 can be used as a single unified system.

A 80C186 system that includes the 80C187 is completely upward compatible with software for the

8086/8087.

The 80C187 interfaces only with the 80C186 CPU.

The interface hardware for the 80C187 is not implemented on the 80C188.

PROGRAMMING INTERFACE

The 80C187 adds to the CPU additional data types,

registers, instructions, and interrupts specifically designed to facilitate high-speed numerics processing.

All new instructions and data types are directly supported by the assembler and compilers for high-level

languages. The 80C187 also supports the full

80387DX instruction set.

All communication between the CPU and the

80C187 is transparent to applications software. The

CPU automatically controls the 80C187 whenever a

numerics instruction is executed. All physical memory and virtual memory of the CPU are available for

storage of the instructions and operands of programs that use the 80C187. All memory addressing

modes are available for addressing numerics operands.

The end of this data sheet lists by class the instructions that the 80C187 adds to the instruction set.

NOTE:

The 80C187 Math Coprocessor is also referred to

as a Numeric Processor Extension (NPX) in this

document.

Data Types

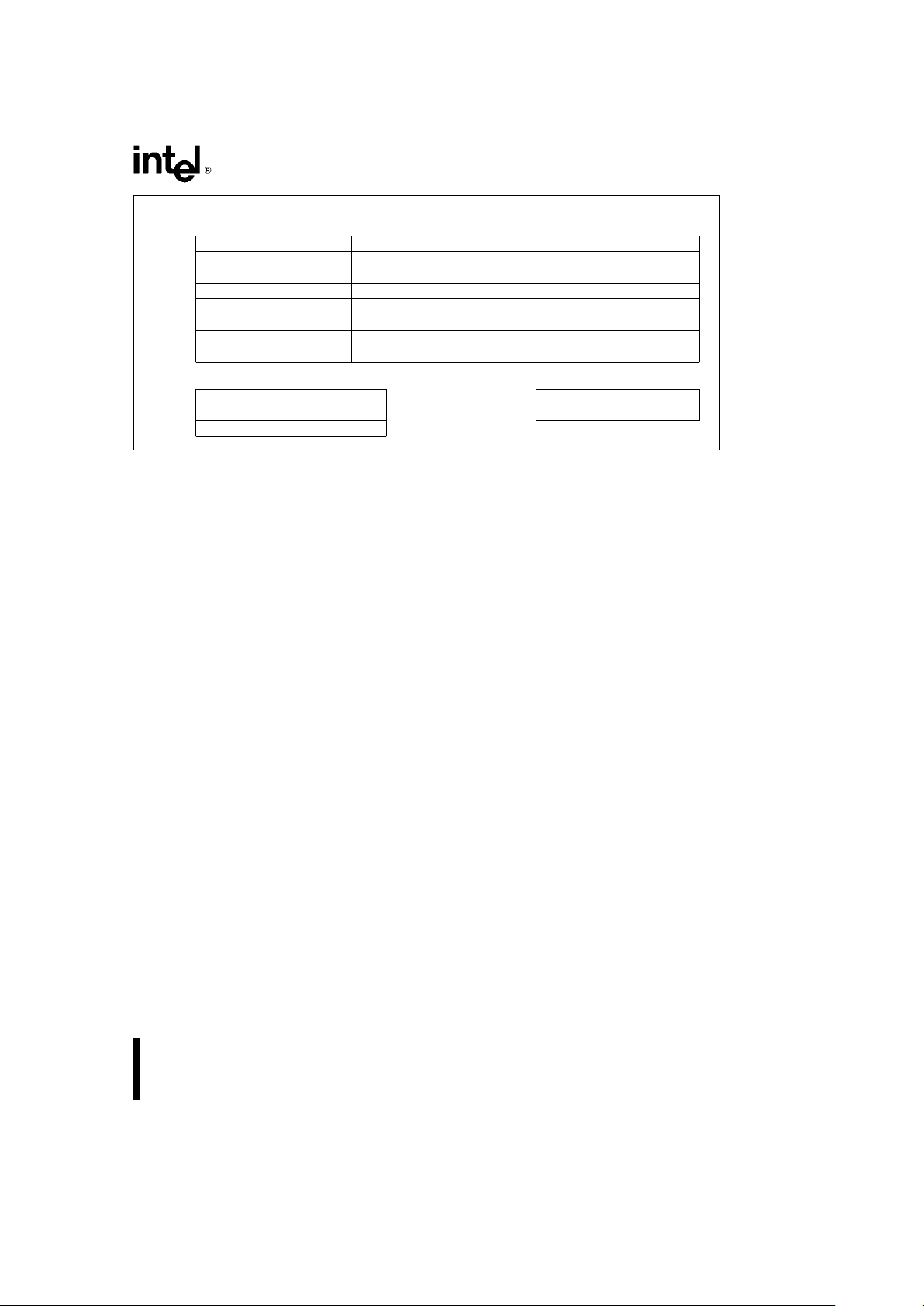

Table 1 lists the seven data types that the 80C187

supports and presents the format for each type. Operands are stored in memory with the least significant digit at the lowest memory address. Programs

retrieve these values by generating the lowest address. For maximum system performance, all operands should start at even physical-memory addresses; operands may begin at odd addresses, but will

require extra memory cycles to access the entire operand.

Internally, the 80C187 holds all numbers in the extended-precision real format. Instructions that load

operands from memory automatically convert operands represented in memory as 16-, 32-, or 64-bit

integers, 32- or 64-bit floating-point numbers, or 18digit packed BCD numbers into extended-precision

real format. Instructions that store operands in memory perform the inverse type conversion.

3

80C187

Numeric Operands

A typical NPX instruction accepts one or two operands and produces one (or sometimes two) results.

In two-operand instructions, one operand is the contents of an NPX register, while the other may be a

memory location. The operands of some instructions

are predefined; for example, FSQRT always takes

the square root of the number in the top stack element (refer to the section on Data Registers).

Register Set

Figure 2 shows the 80C187 register set. When an

80C187 is present in a system, programmers may

use these registers in addition to the registers normally available on the CPU.

DATA REGISTERS

80C187 computations use the extended-precision

real data type.

Table 1. Data Type Representation in Memory

270640– 2

NOTES:

1. S

e

Sign bit (0ePositive, 1eNegative)

2. d

n

e

Decimal digit (two per byte)

3. X

e

Bits have no significance; 80C187 ignores when loading, zeros when storing

4.

U

e

Position of implicit binary point

5. I

e

Integer bit of significand; stored in temporary real, implicit in single and double precision

6. Exponent Bias (normalized values):

Single: 127 (7FH)

Double: 1023 (3FFH)

Extended Real: 16383 (3FFFH)

7. Packed BCD: (

b

1)S(D17...D0)

8. Real: (

b

1)S(2

E-BIAS

)(F0,F1...)

4

80C187

The 80C187 register set can be accessed either as

a stack, with instructions operating on the top one or

two stack elements, or as individually addressable

registers. The TOP field in the status word identifies

the current top-of-stack register. A ‘‘push’’ operation

decrements TOP by one and loads a value into the

new top register. A ‘‘pop’’ operation stores the value

from the current top register and then increments

TOP by one. The 80C187 register stack grows

‘‘down’’ toward lower-addressed registers.

Instructions may address the data registers either

implicitly or explicitly. Many instructions operate on

the register at the TOP of the stack. These instructions implicitly address the register at which TOP

points. Other instructions allow the programmer to

explicitly specify which register to use. This explicit

addressing is also relative to TOP.

TAG WORD

The tag word marks the content of each numeric

data register, as Figure 3 shows. Each two-bit tag

represents one of the eight data registers. The principal function of the tag word is to optimize the

NPX’s performance and stack handling by making it

possible to distinguish between empty and nonempty register locations. It also enables exception handlers to identify special values (e.g. NaNs or denormals) in the contents of a stack location without the

need to perform complex decoding of the actual

data.

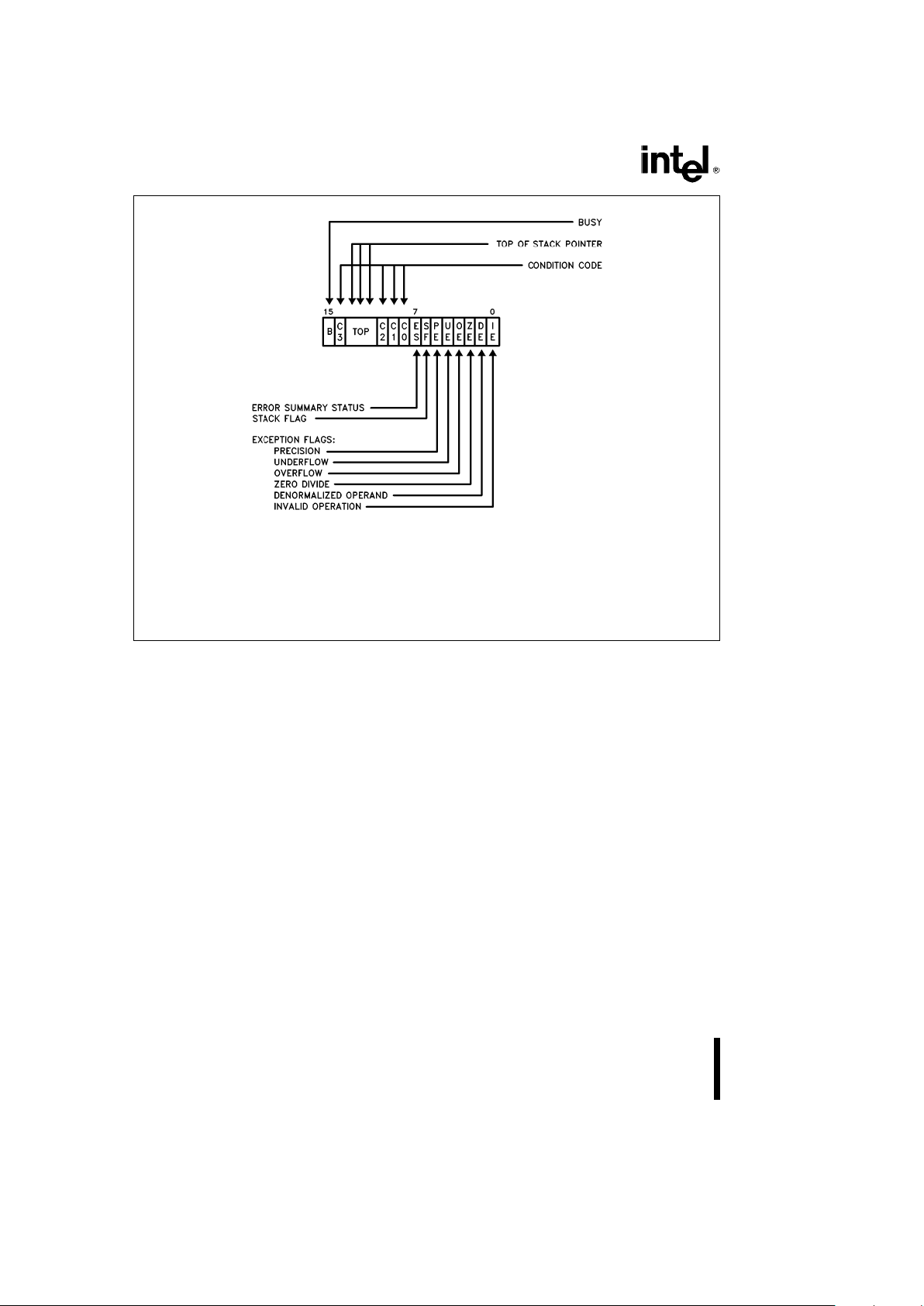

STATUS WORD

The 16-bit status word (in the status register) shown

in Figure 4 reflects the overall state of the 80C187. It

may be read and inspected by programs.

Bit 15, the B-bit (busy bit) is included for 8087 compatibility only. It always has the same value as the

ES bit (bit 7 of the status word); it does not indicate

the status of the BUSY output of 80C187.

Bits 13 –11 (TOP) point to the 80C187 register that

is the current top-of-stack.

The four numeric condition code bits (C

3–C0

) are

similar to the flags in a CPU; instructions that perform arithmetic operations update these bits to reflect the outcome. The effects of these instructions

on the condition code are summarized in Tables 2

through 5.

Bit 7 is the error summary (ES) status bit. This bit is

set if any unmasked exception bit is set; it is clear

otherwise. If this bit is set, the ERROR

signal is as-

serted.

Bit 6 is the stack flag (SF). This bit is used to distinguish invalid operations due to stack overflow or underflow from other kinds of invalid operations. When

SF is set, bit 9 (C

1

) distinguishes between stack

overflow (C

1

e

1) and underflow (C

1

e

0).

Figure 4 shows the six exception flags in bits 5–0 of

the status word. Bits 5 –0 are set to indicate that the

80C187 has detected an exception while executing

an instruction. A later section entitled ‘‘Exception

Handling’’ explains how they are set and used.

Note that when a new value is loaded into the status

word by the FLDENV or FRSTOR instruction, the

value of ES (bit 7) and its reflection in the B-bit (bit

15) are not derived from the values loaded from

memory but rather are dependent upon the values of

the exception flags (bits 5 –0) in the status word and

their corresponding masks in the control word. If ES

is set in such a case, the ERROR

output of the

80C187 is activated immediately.

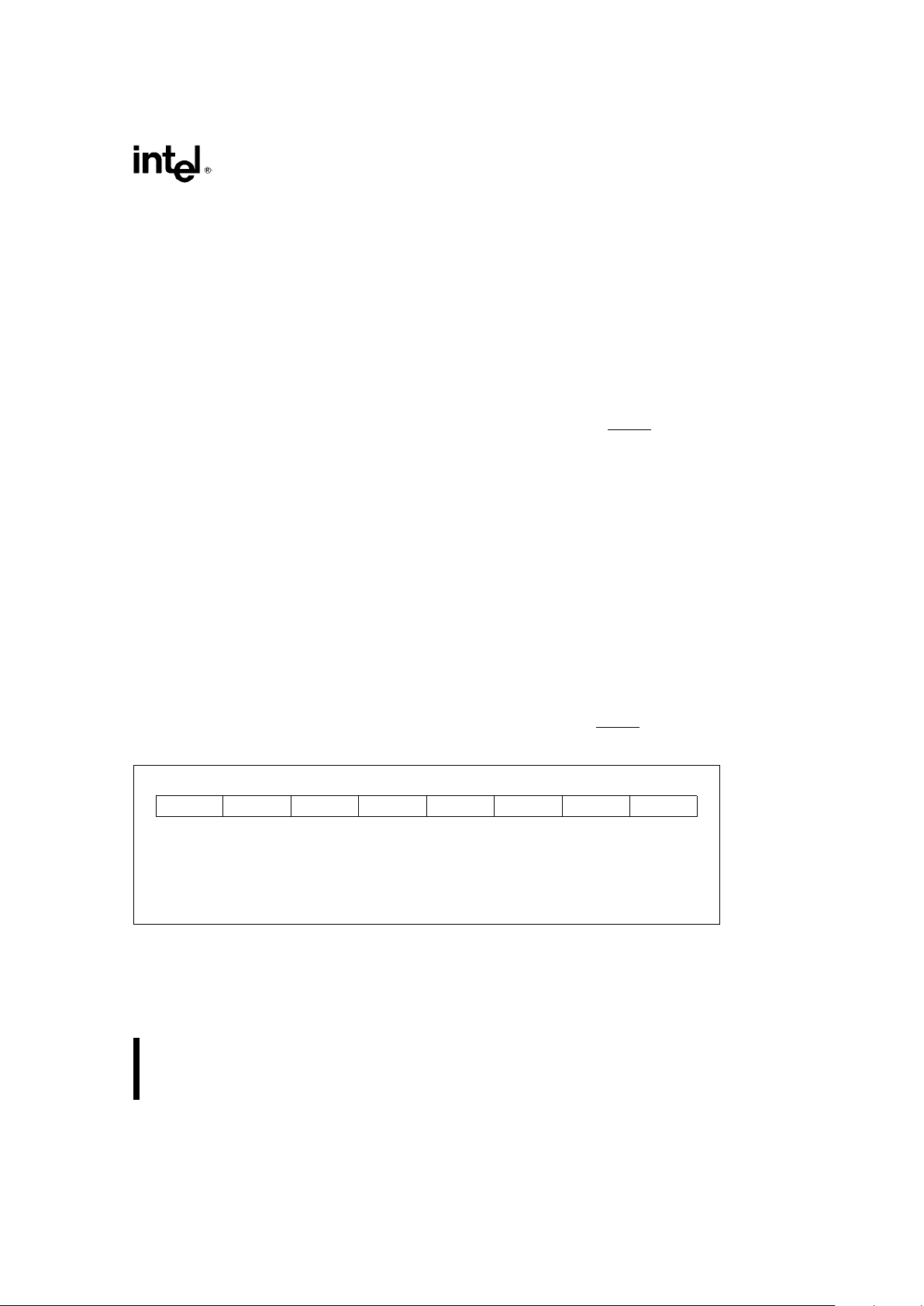

15 0

TAG (7) TAG (6) TAG (5) TAG (4) TAG (3) TAG (2) TAG (1) TAG (0)

NOTE:

The index i of tag(i) is not top-relative. A program typically uses the ‘‘top’’ field of Status Word to determine

which tag(i) field refers to logical top of stack.

TAG VALUES:

00eValid

01

e

Zero

10eQNaN, SNaN, Infinity, Denormal and Unsupported Formats

11eEmpty

Figure 3. Tag Word

5

80C187

270640– 3

ES is set if any unmasked exception bit is set; cleared otherwise.

See Table 2 for interpretation of condition code.

TOP values:

000

e

Register 0 is Top of Stack

001

e

Register 1 is Top of Stack

#

#

#

111eRegister 7 is Top of Stack

For definitions of exceptions, refer to the section entitled,

‘‘Exception Handling’’

Figure 4. Status Word

6

80C187

CONTROL WORD

The NPX provides several processing options that are selected by loading a control word from memory into

the control register. Figure 5 shows the format and encoding of fields in the control word.

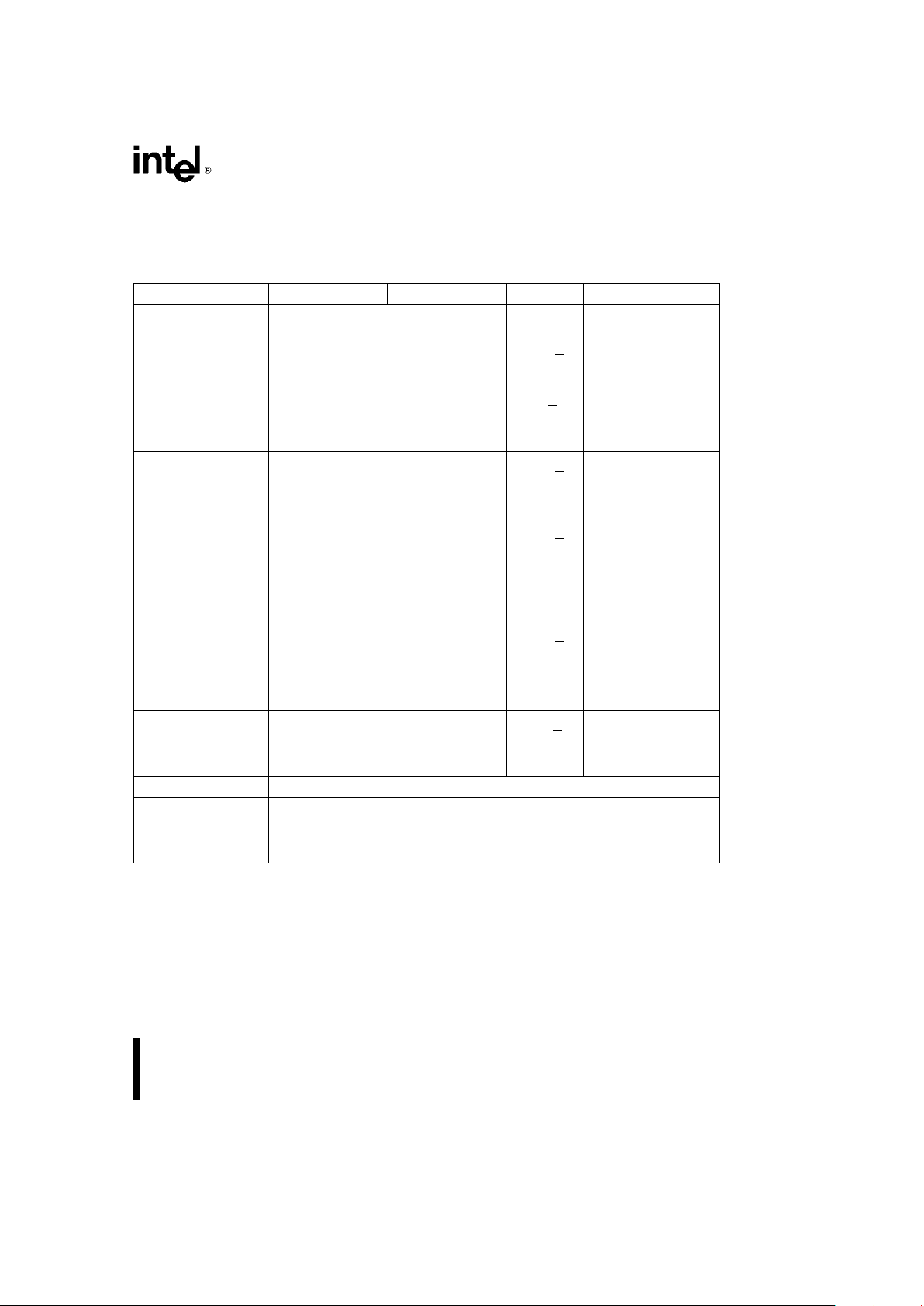

Table 2. Condition Code Interpretation

Instruction C0(S) C3(Z) C1(A) C2(C)

FPREM, FPREM1 Three Least Significant Reduction

(See Table 3) Bits of Quotient 0

e

Complete

Q2 Q0 Q1 1

e

Incomplete

or O/U

FCOM, FCOMP,

FCOMPP, FTST Result of Comparison Zero or Operand is not

FUCOM, FUCOMP, (See Table 4) O/U

Comparable (Table 4)

FUCOMPP, FICOM,

FICOMP

FXAM Operand Class Sign Operand Class

(See Table 5) or O/U

(Table 5)

FCHS, FABS, FXCH,

FINCSTP, FDECSTP,

Constant Loads,

UNDEFINED

Zero

UNDEFINED

FXTRACT, FLD, or O/U

FILD, FBLD,

FSTP (Ext Real)

FIST, FBSTP,

FRNDINT, FST,

FSTP, FADD, FMUL,

UNDEFINED Roundup UNDEFINED

FDIV, FDIVR,

or O/U

FSUB, FSUBR,

FSCALE, FSQRT,

FPATAN, F2XM1,

FYL2X, FYL2XP1

FPTAN, FSIN,

UNDEFINED

Roundup Reduction

FCOS, FSINCOS or O/U

,0

e

Complete

Undefined 1

e

Incomplete

if C2

e

1

FLDENV, FRSTOR Each Bit Loaded from Memory

FLDCW, FSTENV,

FSTCW, FSTSW,

UNDEFINED

FCLEX, FINIT,

FSAVE

O/U When both IE and SF bits of status word are set, indicating a stack exception, this bit distinguishes between

stack overflow (C1

e

1) and underflow (C1e0).

Reduction If FPREM or FPREM1 produces a remainder that is less than the modulus, reduction is complete. When

reduction is incomplete the value at the top of the stack is a partial remainder, which can be used as input to

further reduction. For FPTAN, FSIN, FCOS, and FSINCOS, the reduction bit is set if the operand at the top of

the stack is too large. In this case the original operand remains at the top of the stack.

Roundup When the PE bit of the status word is set, this bit indicates whether one was added to the least significant bit of

the result during the last rounding.

UNDEFINED Do not rely on finding any specific value in these bits.

7

80C187

The low-order byte of this control word configures

exception masking. Bits 5– 0 of the control word

contain individual masks for each of the six exceptions that the 80C187 recognizes.

The high-order byte of the control word configures

the 80C187 operating mode, including precision,

rounding, and infinity control.

#

The ‘‘infinity control bit’’ (bit 12) is not meaningful

to the 80C187, and programs must ignore its value. To maintain compatibility with the 8087, this

bit can be programmed; however, regardless of

its value, the 80C187 always treats infinity in the

affine sense (

b%ka %

). This bit is initialized

to zero both after a hardware reset and after the

FINIT instruction.

#

The rounding control (RC) bits (bits 11–10) provide for directed rounding and true chop, as well

as the unbiased round to nearest even mode

specified in the IEEE standard. Rounding control

affects only those instructions that perform

rounding at the end of the operation (and thus

can generate a precision exception); namely,

FST, FSTP, FIST, all arithmetic instructions (except FPREM, FPREM1, FXTRACT, FABS, and

FCHS), and all transcendental instructions.

#

The precision control (PC) bits (bits 9–8) can be

used to set the 80C187 internal operating precision of the significand at less than the default of

64 bits (extended precision). This can be useful in

providing compatibility with early generation arithmetic processors of smaller precision. PC affects

only the instructions ADD, SUB, DIV, MUL, and

SQRT. For all other instructions, either the precision is determined by the opcode or extended

precision is used.

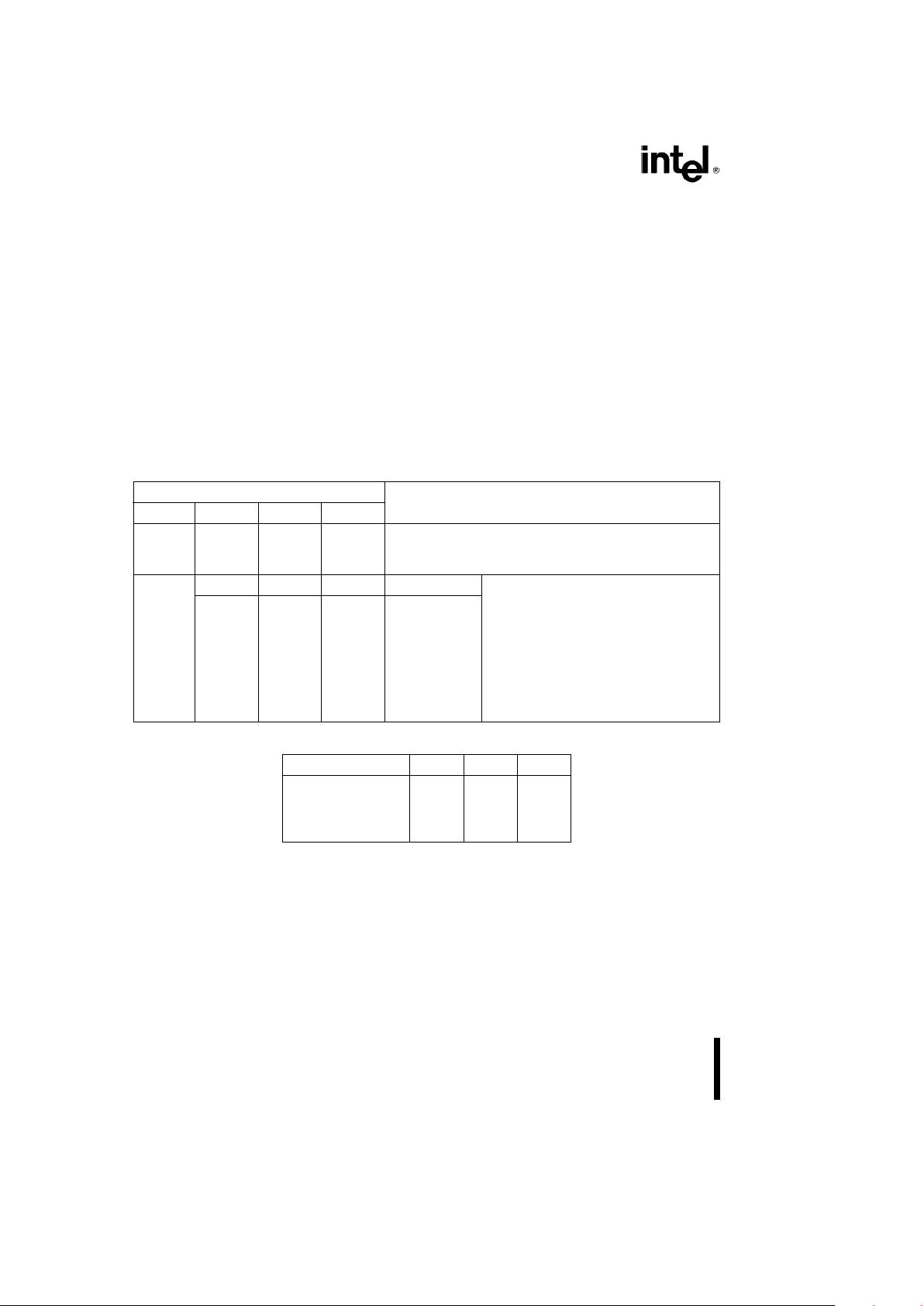

Table 3. Condition Code Interpretation after FPREM and FPREM1 Instructions

Condition Code Interpretation after

C2 C3 C1 C0

FPREM and FPREM1

Incomplete Reduction:

1 X X X Further Iteration Required

for Complete Reduction

Q1 Q0 Q2 Q MOD 8

000 0

0 1 0 1 Complete Reduction:

0

1 0 0 2 C0, C3, C1 Contain Three Least

1 1 0 3 Significant Bits of Quotient

001 4

011 5

101 6

111 7

Table 4. Condition Code Resulting from Comparison

Order C3 C2 C0

TOPlOperand 0 0 0

TOP

k

Operand 0 0 1

TOP

e

Operand 1 0 0

Unordered 1 1 1

8

80C187

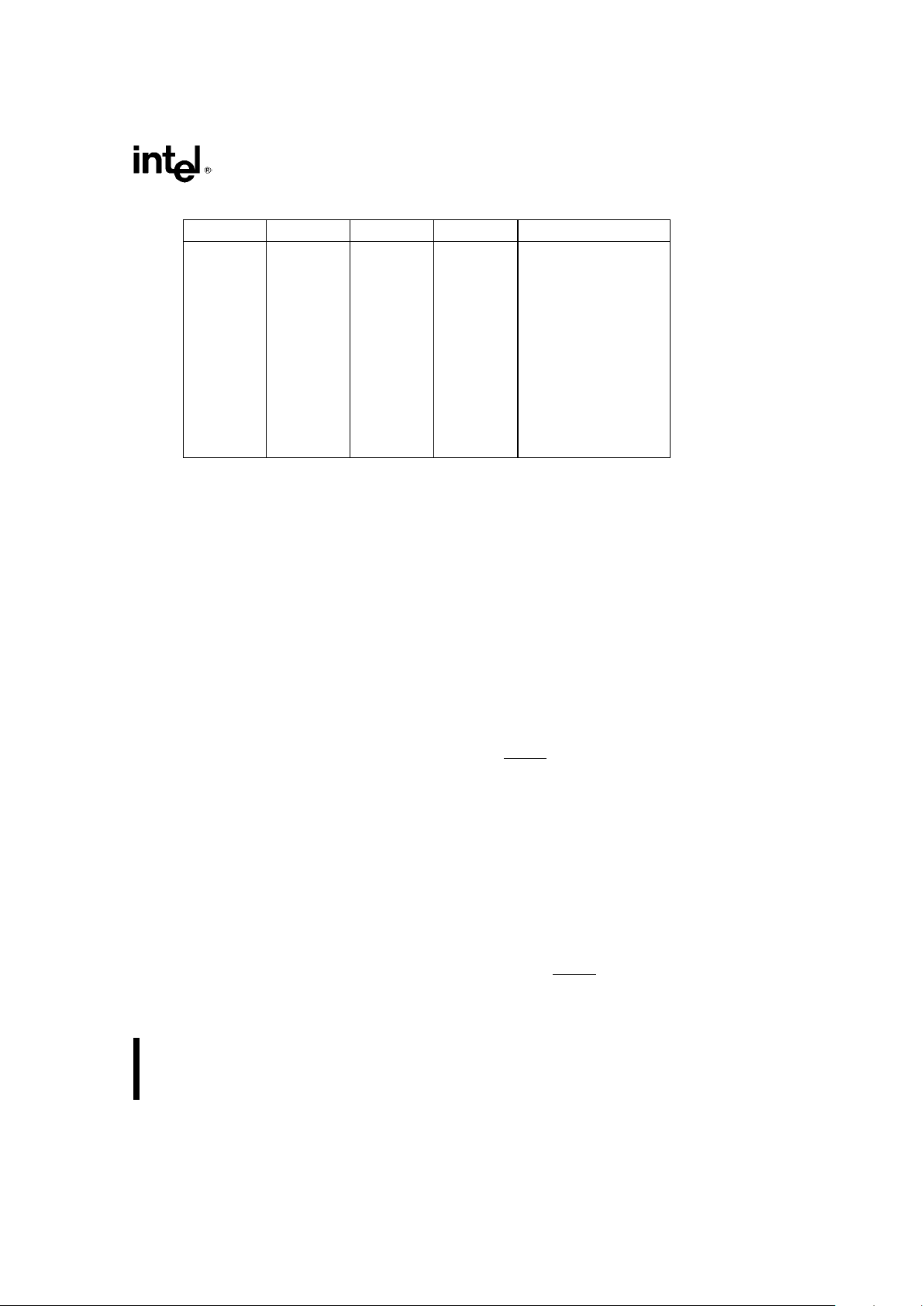

Table 5. Condition Code Defining Operand Class

C3 C2 C1 C0 Value at TOP

0000

a

Unsupported

0001

a

NaN

0010

b

Unsupported

0011

b

NaN

0100

a

Normal

0101

a

Infinity

0110

b

Normal

0111

b

Infinity

1000

a

0

1001

a

Empty

1010

b

0

1011

b

Empty

1100

a

Denormal

1111

b

Denormal

INSTRUCTION AND DATA POINTERS

Because the NPX operates in parallel with the CPU,

any exceptions detected by the NPX may be reported after the CPU has executed the ESC instruction

which caused it. To allow identification of the failing

numerics instruction, the 80C187 contains registers

that aid in diagnosis. These registers supply the opcode of the failing numerics instruction, the address

of the instruction, and the address of its numerics

memory operand (if appropriate).

The instruction and data pointers are provided for

user-written exception handlers. Whenever the

80C187 executes a new ESC instruction, it saves

the address of the instruction (including any prefixes

that may be present), the address of the operand (if

present), and the opcode.

The instruction and data pointers appear in the format shown by Figure 6. The ESC instruction

FLDENV, FSTENV, FSAVE and FRSTOR are used

to transfer these values between the registers and

memory. Note that the value of the data pointer is

undefined

if the prior ESC instruction did not have a

memory operand.

Interrupt Description

CPU interrupt 16 is used to report exceptional conditions while executing numeric programs. Interrupt 16

indicates that the previous numerics instruction

caused an unmasked exception. The address of the

faulty instruction and the address of its operand are

stored in the instruction pointer and data pointer registers. Only ESC instructions can cause this inter-

rupt. The CPU return address pushed onto the stack

of the exception handler points to an ESC instruction

(including prefixes). This instruction can be restarted

after clearing the exception condition in the NPX.

FNINIT, FNCLEX, FNSTSW, FNSTENV, and

FNSAVE cannot cause this interrupt.

Exception Handling

The 80C187 detects six different exception conditions that can occur during instruction execution. Table 6 lists the exception conditions in order of precedence, showing for each the cause and the default

action taken by the 80C187 if the exception is

masked by its corresponding mask bit in the control

word.

Any exception that is not masked by the control

word sets the corresponding exception flag of the

status word, sets the ES bit of the status word, and

asserts the ERROR

signal. When the CPU attempts

to execute another ESC instruction, interrupt 16 occurs. The exception condition must be resolved via

an interrupt service routine. The return address

pushed onto the CPU stack upon entry to the service routine does not necessarily point to the failing

instruction nor to the following instruction. The

80C187 saves the address of the floating-point instruction that caused the exception and the address

of any memory operand required by that instruction.

If error trapping is required at the end of a series of

numerics instructions (specifically, when the last

ESC instruction modifies memory data and that data

is used in subsequent nonnumerics instructions), it is

necessary to insert the FNOP instruction to force the

80C187 to check its ERROR

input.

9

Loading...

Loading...