Intel Corporation MS28F016SV Datasheet

VS28F016SV, MS28F016SV

16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFileTMMEMORY

Y

VS28F016SV

b

Ð

40§Ctoa125§C

Ð SE2 Grade

Y

MS28F016SV

b

Ð

55§Ctoa125§C

Ð QML Certified

Ð SE1 Grade

Y

SmartVoltage Technology

Ð User-Selectable 3.3V or 5V V

Ð User-Selectable 5V or 12V V

Y

Three Voltage/Speed Options

Ð 80 ns Access Time, 5.0V

Ð 85 ns Access Time, 5.0V

Ð 120 ns Access Time, 3.3V

Y

1 Million Erase Cycles per Block

g

g

5%

10%

g

CC

PP

10%

Y

Configurable x8 or x16 Operation

Y

56-Lead SSOP Plastic Package

Y

Backwards-Compatible with VE28F008,

M28F008 and 28F016SA Command Set

Y

Revolutionary Architecture

Ð Multiple Command Execution

Ð Write During Erase

Ð Command Super-Set of the Intel

VE28F008, M28F008

Ð Page Buffer Write

Y

Multiple Power Savings Modes

Y

Two 256-Byte Page Buffers

Y

State-of-the-Art 0.6 mm ETOXTMIV

Flash Technology

Typical

Y

14.3 MB/sec Burst Write Transfer Rate

Intel’s VS/MS28F016SV, 16-Mbit FlashFiIeTMMemory is the latest member of Intel’s high density, high performance memory family for the Industrial, Special Environment, and Military markets. Its user selectable V

and VPP(SmartVoltage Technology), innovative capabilities, 100% compatibility with the VE28F008 and

M28F008, multiple power savings modes, selective block locking, and very fast read/write performance make

it the ideal choice for any applications that need a high density and a wide temperature range memory device.

The VS/MS28F016SV is the ideal choice for designers who need to break free from the dependence on slow

rotating media or battery backed up memory arrays.

With two product grades (SE1:

b

55§Ctoa125§C, and SE2:b40§Ctoa125§C) available, the

VS/MS28F016SV is perfect for the non-PC industries like Telecommunications, Embedded/Industrial, Automotive, Navigation, Wireless Communication, Commercial Aircraft, and all Military programs.

CC

The VS/MS28F016SV’s x8/x16 architecture allows for the optimization of the memory to processor interface.

The flexible block locking options enable bundling of executable application software in a Resident Flash Array

(RFA), PCMCIA Memory or ATA Cards or Memory modules.

The VS/MS28F016SV is offered in a 56-lead SS0P (Shrink Small Outline Package) and is manufactured on

Intel’s 0.6 mm ETOX

*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

TM

IV process technology.

December 1995COPYRIGHT©INTEL CORPORATION, 1995 Order Number: 271312-002

VS28F016SV, MS28F016SV FlashFileTMMEMORY

CONTENTS PAGE

1.0 INTRODUCTION

1.1 Enhanced Features АААААААААААААААААА 3

1.2 Product Overview АААААААААААААААААААА 3

2.0 DEVICE PINOUT ААААААААААААААААААААААА 5

2.1 Lead Descriptions ААААААААААААААААААА 7

3.0 MEMORY MAPS АААААААААААААААААААААА 10

3.1 Extended Status Registers Memory

Map

ААААААААААААААААААААААААААААААААА 11

4.0 BUS OPERATIONS, COMMANDS

AND STATUS REGISTER

DEFINITIONS АААААААААААААААААААААААААА 12

4.1 Bus Operations for Word-Wide

Mode (BYTE

4.2 Bus Operations for Byte-Wide

Mode (BYTE

4.3 VE28F008 or M28F008 Compatible

Mode Command Bus Definitions

4.4 VS/MS28F016SV-Performance

Enhancement Command Bus

Definitions

4.5 Compatible Status Register ААААААААА 16

4.6 Global Status Register АААААААААААААА 17

4.7 Block Status Register ААААААААААААААА 18

4.8 Device Configuration Code ААААААААА 19

ААААААААААААААААААААААА 3

e

Ý

VIH) ААААААААААААААА 12

e

Ý

VIL) ААААААААААААААА 12

ААААА 13

ААААААААААААААААААААААААААА 14

CONTENTS PAGE

5.0 ELECTRICAL SPECIFICATIONS

5.1 Absolute Maximum Ratings ААААААААА 20

5.2 Capacitance АААААААААААААААААААААААА 21

5.3 Timing Nomenclature ААААААААААААААА 22

5.4 DC Characteristics (V

g

0.5V) АААААААААААААААААААААААААААААА 25

5.5 DC Characteristics (V

g

0.5V) АААААААААААААААААААААААААААААА 28

CC

CC

5.6 AC CharacteristicsÐRead Only

Operations

АААААААААААААААААААААААААА 31

5.7 Power-Up and Reset Timings ААААААА 35

5.8 AC Characteristics for

WEÝÐControlled Command Write

Operations

АААААААААААААААААААААААААА 36

5.9 AC Characteristics for

CEÝÐControlled Command Write

Operations

АААААААААААААААААААААААААА 39

5.10 AC Characteristics for

Ý

WE

ÐControlled Page Buffer Write

Operations АААААААААААААААААААААААААА 42

5.11 AC Characteristics for

Ý

CE

ÐControlled Page Buffer Write

Operations АААААААААААААААААААААААААА 44

5.12 Erase and Word/Byte Write

Performance

ААААААААААААААААААААААААА 45

6.0 MECHANICAL SPECIFICATIONS ÀÀÀÀ 47

e

e

ААААА 20

3.3V

5.0V

DEVICE NOMENCLATURE ААААААААААААААА 48

ADDITIONAL INFORMATION АААААААААААА 48

DATA SHEET REVISION HISTORY АААААА 48

2

VS28F016SV, MS28F016SV FlashFileTMMemory

1.0 INTRODUCTION

The documentation of the Intel VS/MS28F016SV

memory device includes this data sheet, a detailed

user’s manual, and a number of application notes,

all of which are referenced at the end of this data

sheet.

The data sheet is intended to give an overview of

the chip feature-set and of the operating AC/DC

specifications. The 28F016SA (compatible with

VS/MS28F016SV) User’s Manual provides complete descriptions of the user modes, system interface examples and detailed descriptions of all principles of operation. It also contains the full list of

software algorithm flowcharts, and a brief section on

compatibility with the Intel VE28F008 and M28F008.

1.1 Enhanced Features

The VS/MS28F016SV is backwards compatible with

the VE28F008 and M28F008 and offers the following enhancements:

SmartVoltage Technology

#

Ð Selectable 5.0V or 12.0V V

VPPLevel Bit in Block Status Register

#

Additional RY/BYÝConfiguration

#

Ð Pulse-On-Write/Erase

Additional Upload Device Information Command

#

Feedback

Ð Device Revision Number

Ð Device Proliferation Code

Ð Device Configuration Code

x8/x16 Architecture

#

Block Locking

#

2 Page Buffers

#

Instruction Queuing

#

PP

1.2 Product Overview

The VS/MS28F016SV is a high-performance,

16-Mbit (16,777,216-bit) block erasable, non-volatile

random access memory, organized as either

1 Mword x 16 or 2 Mbyte x 8. The VS/MS28F016SV

includes thirty-two 64-KB (65,536 byte) blocks or

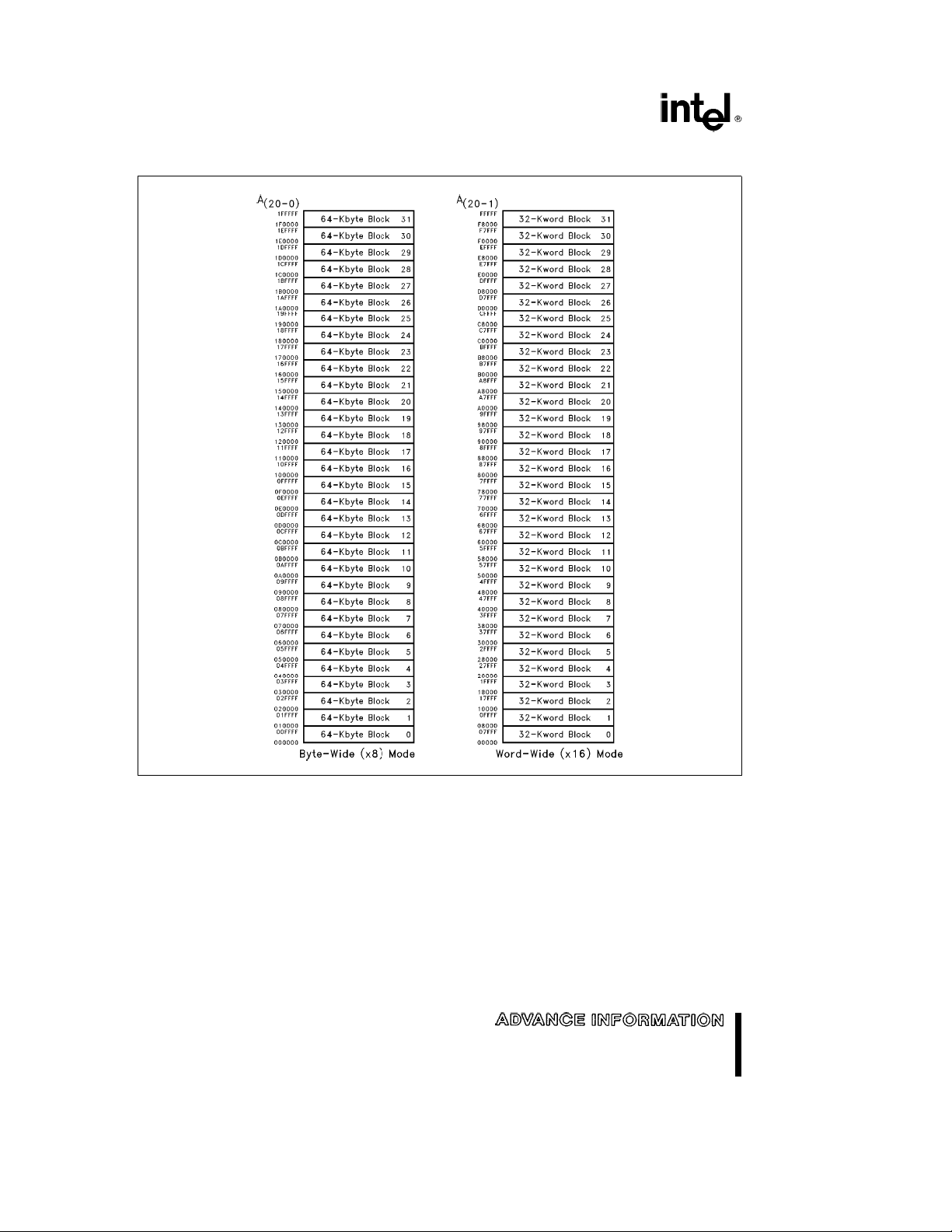

thirty-two 32-KW (32,768 word) blocks. A chip memory map is shown in Figure 3.

The implementation of a new architecture, with

many enhanced features, will improve the device operating characteristics and result in greater product

reliability and ease of use.

The VS/MS28F016SV incorporates SmartVoltage

technology, providing V

and 5.0V and program and erase capability at V

12.0V or 5.0V. Operating at V

VS/MS28F016SV consumes approximately one-half

the power consumption at 5.0V V

provides highest read performance capability. V

e

5.0V operation eliminates the need for a separate

12.0V converter, while V

write/erase performance. In addition to the flexible

program and erase voltages, the dedicated V

gives complete code protection with V

Depending on system design specifications, the

VS/MS28F016SV is capable of supporting

Ð 80 ns access times with a V

loading of 30 pF

Ð 85 ns access times with a V

and loading of 100 pF

Ð 120 ns access times with a V

and loading of 50 pF

Ý

A 3/5

input pin configures the device’s internal cir-

cuitry for optimal 3.3V or 5.0V Read/Write operation.

A Command User Interface (CUI) serves as the system interface between the microprocessor or microcontroller and the internal memory operation.

Internal Algorithm Automation allows Byte/Word

Writes and Block Erase operations to be executed

using a Two-Write command sequence to the CUI in

the same way as the VE28F008 or M28F008 8-Mbit

FlashFile memory.

A super-set of commands has been added to the

basic VE28F008 or M28F008 command-set to

achieve higher write performance and provide additional capabilities. These new commands and features include:

Page Buffer Writes to Flash

#

Command Queuing Capability

#

Automatic Data Writes during Erase

#

Software Locking of Memory Blocks

#

Two-Byte Successive Writes in 8-bit Systems

#

Erase All Unlocked Blocks

#

operation at both 3.3V

CC

e

CC

, while 5.0V V

CC

e

12.0V maximizes

PP

s

PP

of 5.0Vg5% and

CC

of 5.0Vg10%

CC

of 3.3Vg5%

CC

PP

3.3V, the

CC

PP

PP

V

PPLK

e

.

3

VS28F016SV, MS28F016SV FlashFileTMMemory

Writing of memory data is performed in either byte or

word increments typically within 6 msec (12.0V V

b

a 33% improvement over the VE28F008 or

PP

M28F008. A Block Erase operation erases one of

the 32 blocks in about 1.0 sec (12.0V V

dent of the other blocks, which is about a 65% im-

), indepen-

PP

provement over the VE28F008 or M28F008.

Each block can be written and erased a minimum of

100,000 cycles. Systems can achieve one million

Block Erase Cycles by providing wear-leveling algorithms and graceful block retirement. These techniques have already been employed in many flash

file systems and hard disk drive designs.

The VS/MS28F016SV incorporates two Page Buffers of 256 bytes (128 words) each to allow page

data writes. This feature can improve a system write

performance by up to 4.8 times over previous flash

memory devices, which have no Page Buffers.

All operations are started by a sequence of Write

commands to the device. Three Status Registers

(described in detail later in this data sheet) and a

Ý

RY/BY

output pin provide information on the prog-

ress of the requested operation.

While the VE28F008 or M28F008 requires an operation to complete before the next operation can be

requested, the VS/MS28F016SV allows queuing of

the next operation while the memory executes the

current operation. This eliminates system overhead

when writing several bytes in a row to the array or

erasing several blocks at the same time. The

VS/MS28F016SV can also perform Write operations

to one block of memory while performing Erase of

another block.

The VS/MS28F016SV provides selectable block

locking to protect code or data such as Device Drivers, PCMCIA card information, ROM-Executable

O/S or Application Code. Each block has an associated non-volatile lock-bit which determines the

lock status of the block. In addition, the

VS/MS28F016SV has a master Write Protect pin

Ý

(WP

) which prevents any modifications to memory

blocks whose lock-bits are set.

The VS/MS28F016SV contains three types of

Status Registers to accomplish various functions:

A Compatible Status Register (CSR) which is

#

100% compatible with the VE28F008 or

M28F008 FlashFile memory Status Register. The

CSR, when used alone, provides a straightforward upgrade capability to the VS/MS28F016SV

from a VE28F008- or M28F008-based design.

A Global Status Register (GSR) which informs

#

)

the system of command Queue status, Page

Buffer status, and overall Write State Machine

(WSM) status.

32 Block Status Registers (BSRs) which provide

#

block-specific status information such as the

block lock-bit status.

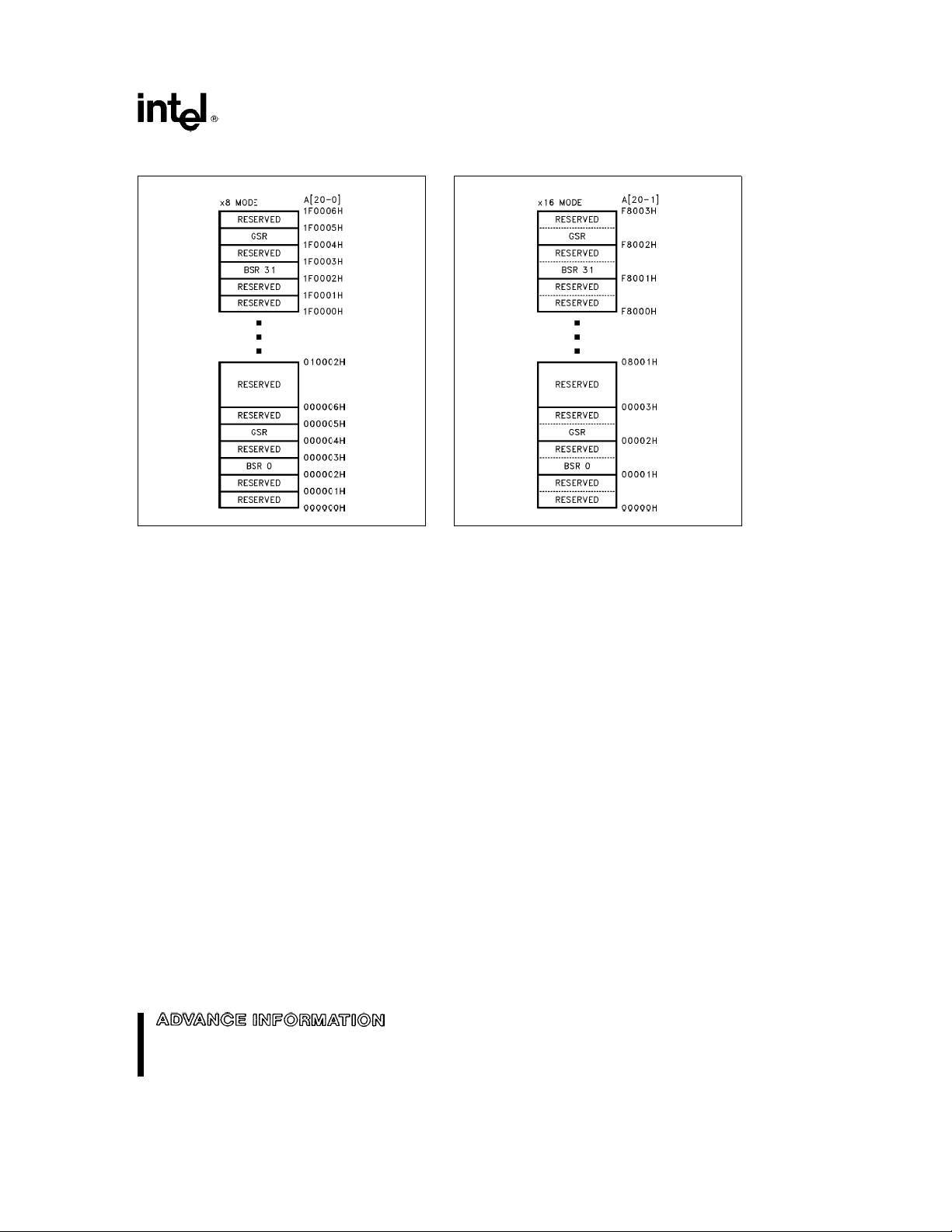

The GSR and BSR memory maps for Byte-Wide and

Word-Wide modes are shown in Figures 4 and 5.

The VS/MS28F016SV incorporates an open drain

Ý

RY/BY

OR-tie many RY/BY

output pin. This feature allows the user to

Ý

pins together in a multiple

memory configuration such as a Resident Flash Array.

Other configurations of the RY/BYÝpin are enabled via special CUI commands and are described

in detail in the 16-Mbit Flash Product Family User’s

Manual.

The VS/MS28F016SV’s Upload Device Information

command is enhanced compared to the VE28F008

or M28F008, providing access to additional device

information. This command uploads the Device Revision Number, Device Proliferation Code and Device Configuration Code. The Device Proliferation

Code for the VS/MS28F016SV is 01H, and the Device Configuration Code identifies the current

Ý

RY/BY

configuration. Section 4.4 documents the

exact page buffer address locations for all uploaded

information. A subsequent Page Buffer Swap and

Page Buffer Read command sequence is necessary

to read the correct device information.

The VS/MS28F016SV also incorporates a dual chipenable function with two input pins, CE

Ý

. These pins have exactly the same functional-

CE

1

ity as the regular chip-enable pin, CE

VE28F008 or M28F008. For minimum chip designs,

Ý

may be tied to ground and system logic may

CE

1

use CE

VS/MS28F016SV uses the logical combination of

Ý

as the chip enable input. The

0

these two signals to enable or disable the entire

chip. Both CE

enable the device. If either one becomes inactive,

Ý

0

and CE

Ý

must be active low to

1

the chip will be disabled. This feature, along with the

open drain RY/BY

Ý

pin, allows the system designer

to reduce the number of control pins used in a large

array of 16-Mbit devices.

The BYTE

to the VS/MS28F016SV. BYTE

lects 8-bit mode with address A

low byte and high byte. On the other hand, BYTE

Ý

pin allows either x8 or x16 read/writes

Ý

at logic low se-

selecting between

0

Ý

0

Ý

,onthe

and

Ý

4

VS28F016SV, MS28F016SV FlashFileTMMemory

at logic high enables 16-bit operation with address

A

becoming the lowest order address and address

1

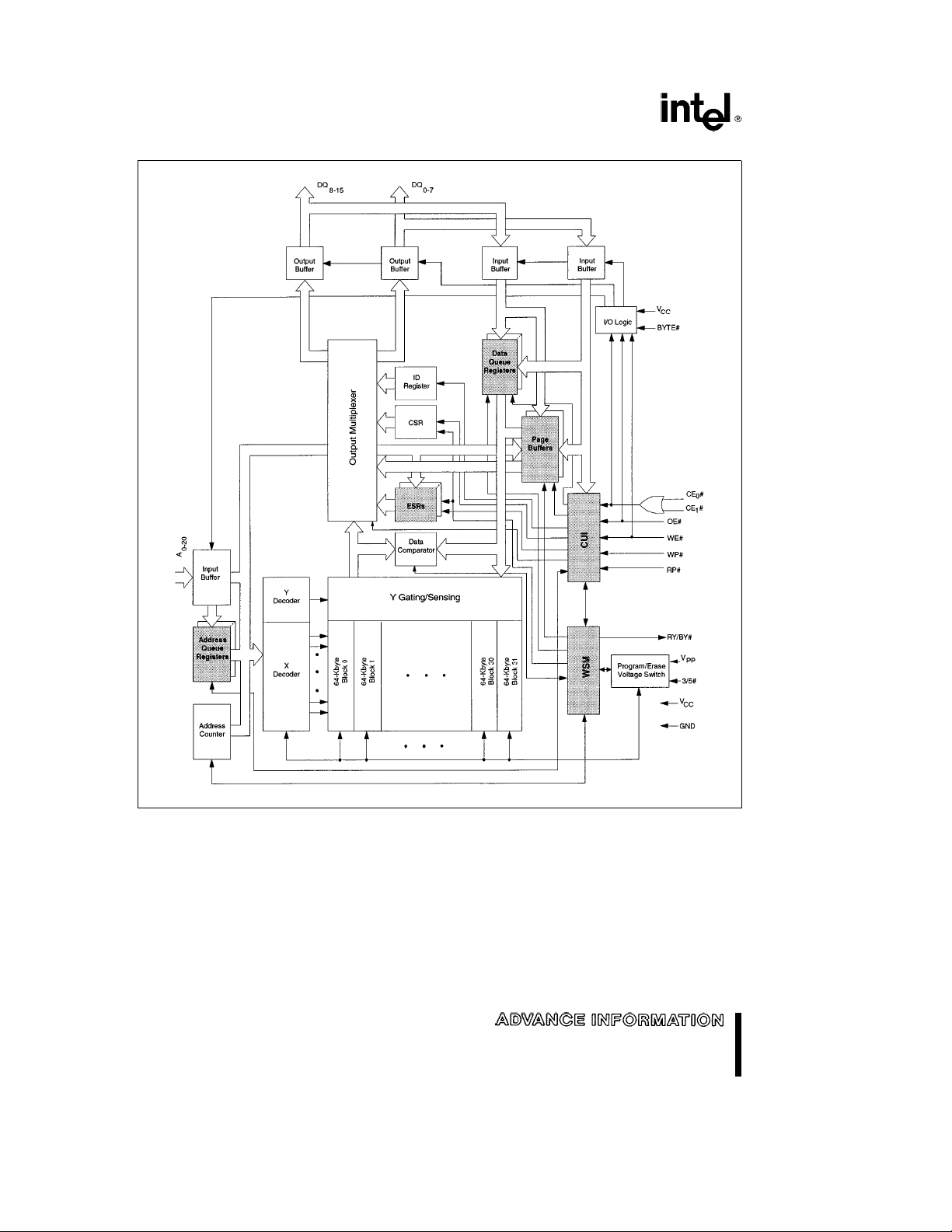

is not used (don’t care). A device block diagram

A

0

is shown in Figure 1.

The VS/MS28F016SV is specified for a maximum

access time of 80 ns (t

to 5.25V) in either the SE1 or SE2 grades. A corre-

) at 5.0V operation (4.75V

ACC

sponding maximum access time of 120 ns at 3.3V

(3.15V to 3.45V) is achieved for reduced power consumption applications.

The VS/MS28F016SV incorporates an Automatic

Power Saving (APS) feature which substantially reduces the active current when the device is in static

mode of operation (addresses not switching). In APS

mode, the typical I

at 3.3V).

current is 1 mA at 5.0V (0.8 mA

CC

A deep power-down mode of operation is invoked

when the RP

Ý

(called PWDÝon the VE28F008 or

M28F008) pin transitions low. This mode brings the

device power consumption to less than 30.0 mA, typically, and provides additional write protection by

acting as a device reset pin during power transitions.

A reset time of 500 ns (5.0V V

quired from RP

Ý

switching high until outputs are

operation) is re-

CC

again valid. In the Deep Power-Down state, the

WSM is reset (any current operation will abort) and

the CSR, GSR and BSR registers are cleared.

A CMOS standby mode of operation is enabled

when either CE

Ý

stays high with all input control pins at CMOS

RP

Ý

0

or CE

Ý

transitions high and

1

levels. In this mode, the device typically draws an

I

standby current of 70 mAat5VVCC.

CC

2.0 DEVICE PINOUT

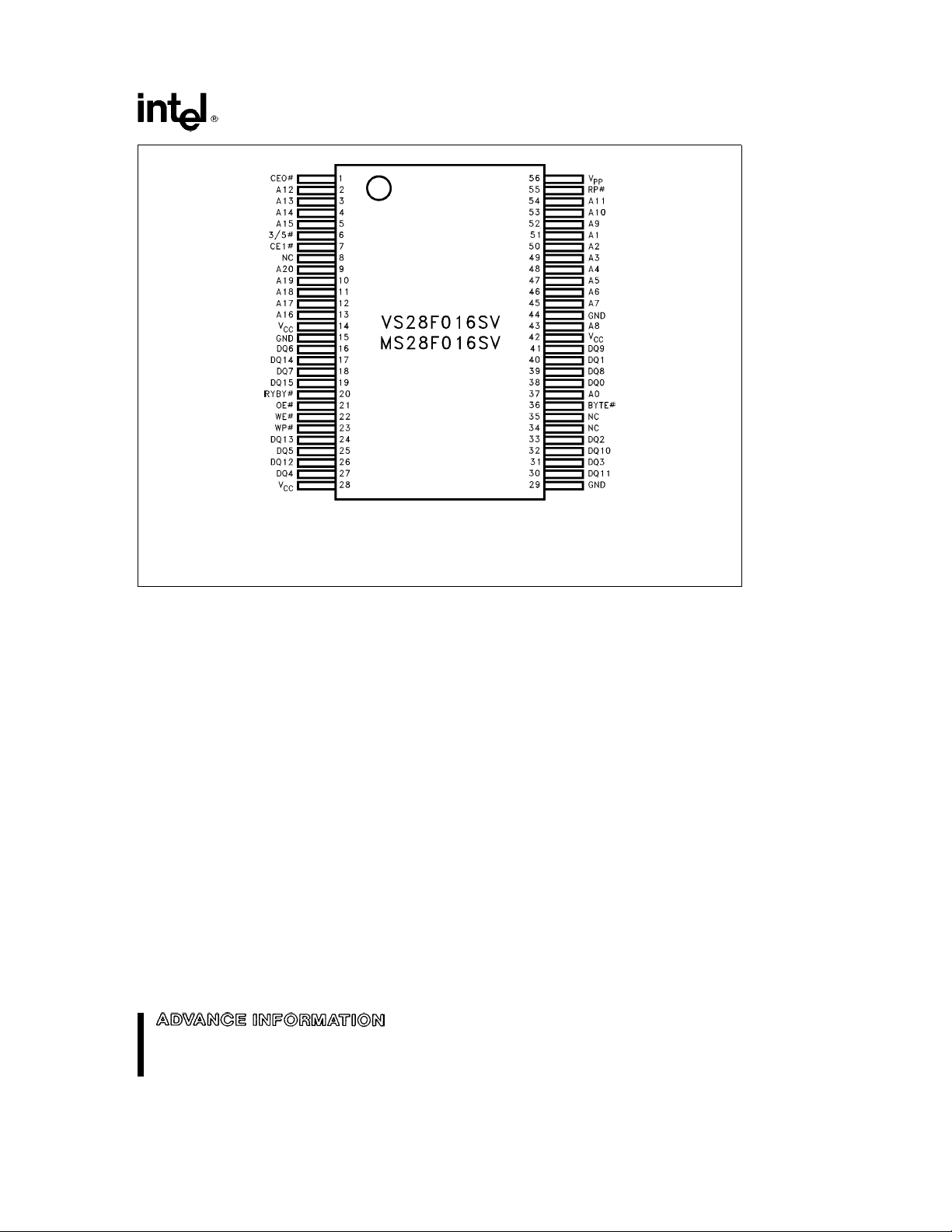

The VS/MS28F016SV 56L-SSOP pinout configuration is shown in Figure 2.

5

VS28F016SV, MS28F016SV FlashFileTMMemory

271312– 21

Figure 1. Block Diagram

6

VS28F016SV, MS28F016SV FlashFileTMMemory

2.1 Lead Descriptions

Symbol Type Name and Function

A

0

A1-A

15

A16-A

20

DQ0-DQ

DQ8-DQ

Ý

CE

,CE

0

Ý

RP

Ý

OE

Ý

WE

INPUT BYTE-SELECT ADDRESS: Selects between high and low byte when

device is in x8 mode. This address is latched in x8 Data Writes. Not

used in x16 mode (i.e., the A

is high).

input buffer is turned off when BYTE

0

INPUT WORD-SELECT ADDRESSES: Select a word within one 64-Kbyte

block. A

columns. These addresses are latched during Data Writes.

selects 1 of 1024 rows, and A

6-15

INPUT BLOCK-SELECT ADDRESSES: Select 1 of 32 Erase blocks. These

addresses are latched during Data Writes, Erase and Lock-Block

operations.

INPUT/OUTPUT LOW-BYTE DATA BUS: Inputs data and commands during CUI write

7

cycles. Outputs array, buffer, identifier or status data in the

appropriate read mode. Floated when the chip is de-selected or the

outputs are disabled.

INPUT/OUTPUT HIGH-BYTE DATA BUS: Inputs data during x16 Data-Write

15

operations. Outputs array, buffer or identifier data in the appropriate

read mode; not used for Status Register reads. Floated when the

chip is de-selected or the outputs are disabled.

Ý

INPUT CHIP ENABLE INPUTS: Activate the device’s control logic, input

1

buffers, decoders and sense amplifiers. With either CE

high, the device is de-selected and power consumption reduces to

standby levels upon completion of any current Data-Write or Erase

Ý

Ý

,CE

operations. Both CE

0

must be low to select the device.

1

All timing specifications are the same for both signals. Device

Selection occurs with the latter falling edge of CE

first rising edge of CE

Ý

0

or CE

Ý

1

INPUT RESET/POWER-DOWN: RPÝlow places the device in a Deep

Power-Down state. All circuits that consume static power, even those

circuits enabled in standby mode, are turned off. When returning from

Deep Power-Down, a recovery time of t

to allow these circuits to power-up.

When RP

Ý

goes low, any current or pending WSM operation(s) are

terminated, and the device is reset. All Status Registers return to

ready (with all status flags cleared).

Exit from Deep Power-Down places the device in read array mode.

INPUT OUTPUT ENABLE: Gates device data through the output buffers

when low. The outputs float to tri-state off when OE

NOTE:

Ý

CE

overrides OEÝ, and OEÝoverrides WEÝ.

x

INPUT WRITE ENABLE: Controls access to the CUI, Page Buffers, Data

Queue Registers and Address Queue Latches. WEÝis active low,

and latches both address and data (command or array) on its rising

edge. Page Buffer addresses are latched on the falling edge of WE

selects 16 of 512

1-5

Ý

disables the device.

PHQV

0

at 5.0V VCCis required

Ý

Ý

0

or CE

is high.

or CE

Ý

. The

1

Ý

Ý

1

Ý

.

7

VS28F016SV, MS28F016SV FlashFileTMMemory

2.1 Lead Descriptions (Continued)

Symbol Type Name and Function

Ý

RY/BY

Ý

WP

BYTE

Ý

3/5

V

PP

V

CC

GND SUPPLY GROUND FOR ALL INTERNAL CIRCUITRY: Do not leave any ground pins

NC NO CONNECT: Lead may be driven or left floating.

OPEN DRAIN READY/BUSY: Indicates status of the internal WSM. When low, it indicates

OUTPUT

that the WSM is busy performing an operation. RY/BY

that the WSM is ready for new operations (or WSM has completed all

Ý

floating indicates

pending operations), or erase is suspended, or the device is in deep powerdown mode. This output is always active (i.e., not floated to tri-state off when

Ý

OEÝor CE

is issued.

Ý

,CE

0

are high), except if a RY/BYÝPin Disable command

1

INPUT WRITE PROTECT: Erase blocks can be locked by writing a nonvolatile lock-

bit for each block. When WP

Ý

is low, those locked blocks as reflected by

the Block-Lock Status bits (BSR.6), are protected from inadvertent data

writes or erases. When WP

regardless of the state ot the lock-bits. The WP

Ý

when RP

Ý

INPUT BYTE ENABLE: BYTEÝlow places device in x8 mode. All data is then input

or output on DQ

and low byte. BYTE

A

0

transitions low (deep power-down mode).

0–7

input buffer. Address A1, then becomes the lowest order address.

Ý

is high, all blocks can be written or erased

, and DQ

Ý

high places the device in x16 mode, and turns off the

float. Address A0selects between the high

8–15

Ý

input buffer is disabled

INPUT 3.3/5.0 VOLT SELECT: 3/5Ýhigh configures internal circuits for 3.3V

Ý

operation. 3/5

low configures internal circuits for 5.0V operation.

NOTE:

Reading the array with 3/5

Ý

high in a 5.0V system could damage the

device. Reference the power-up and reset timings (Section 5.7) for 3/5

switching delay to valid data.

SUPPLY WRITE/ERASE POWER SUPPLY (12.0Vg0.6V, 5.0Vg0.5V): For erasing

memory array blocks or writing words/bytes/pages into the flash array. V

e

5.0Vg0.5V eliminates the need for a 12V converter, while connection to

g

1 2.0V

0.6V maximizes Write/Erase Performance.

NOTE:

Successful completion of write and erase attempts is inhibited with V

below 1.5V. Write and erase attempts with V

between 5.5V and 11.4V, and above 12.6V produce spurious results and

between 1.5V and 4.5V,

PP

should not be attempted.

SUPPLY DEVICE POWER SUPPLY (3.3Vg0.45V, 5.0Vg0.5V, 5.0g0.25V): To

switch 3.3V to 5.0V (or vice versa), first ramp VCCdown to GND, and then

power to the new V

CC

voltage.

Do not leave any power pins floating.

floating.

PP

Ý

PP

at or

8

VS28F016SV, MS28F016SV FlashFileTMMemory

24mm x 13.5mm 0.8mm Lead Pitch

Top View

NOTE:

56-Lead SSOP Mechanical Diagrams and dimensions are shown at the end of this data sheet.

Figure 2. SSOP Pinout Configuration

271312– 2

9

VS28F016SV, MS28F016SV FlashFileTMMemory

3.0 MEMORY MAPS

10

271312– 3

Figure 3. VS/MS28F016SV Memory Maps (Byte-Wide and Word-Wide Modes)

VS28F016SV, MS28F016SV FlashFileTMMemory

3.1 Extended Status Registers Memory Map

271312– 4

Figure 4. Extended Status Register Memory Map

(Byte-Wide Mode)

271312– 5

Figure 5. Extended Status Register Memory Map

(Word-Wide Mode)

11

VS28F016SV, MS28F016SV FlashFileTMMemory

4.0 BUS OPERATIONS, COMMANDS AND STATUS REGISTER DEFINITIONS

e

Ý

4.1 Bus Operations for Word-Wide Mode (BYTE

Mode Notes RP

Read 1,2,7 V

Output Disable 1,6,7 V

Standby 1,6,7 V

Deep Power-Down 1,3 V

Manufacturer ID 4 V

Device ID 4 V

Write 1,5,6 V

Ý

IH

IH

IH

IL

IH

IH

IH

Ý

CE

1

V

IL

V

IL

V

IL

V

IH

V

IH

X X X X X High Z V

V

IL

V

IL

V

IL

CE

Ý

OEÝWE

0

V

IL

V

IL

V

IH

V

IL

V

IH

V

IL

V

IL

V

IL

4.2 Bus Operations for Byte-Wide Mode (BYTE

Mode Notes RP

Read 1,2,7 V

Output Disable 1,6,7 V

Standby 1,6,7 V

Deep Power-Down 1,3 V

Manufacturer ID 4 V

Device ID 4 V

Write 1,5,6 V

NOTES:

1. X can be V

2. RY/BY

RY/BY

operation is in progress.

Ý

3. RP

and A1at VILprovide device manufacturer codes in x8 and x16 modes respectively. A0and A1at VIHprovide device

4. A

0

ID codes in x8 and x16 modes respectively. All other addresses are set to zero.

5. Commands for Erase, Data Write, or Lock-Block operations can only be completed successfully when V

e

V

PP

6. While the WSM is running, RY/BY

to V

OH

7. RY/BY

during a Write operation.

or VILfor address or control pins except for RY/BYÝ, which is either VOLor VOH.

IH

Ý

output is open drain. When the WSM is ready, Erase is suspended or the device is in deep power-down mode.

Ý

will be at VOHif it is tied to VCCthrough a resistor. RY/BYÝat VOHis independent of OEÝwhile a WSM

at GNDg0.2V ensures the lowest deep power-down current.

V

.

PPH2

when the WSM is not busy or in erase suspend mode.

Ý

may be at VOLwhile the WSM is busy performing various operations. For example, a Status Register read

Ý

IH

IH

IH

IL

IH

IH

IH

Ý

in level-mode (default) stays at VOLuntil all operations are complete. RY/BYÝgoes

Ý

CE

1

V

IL

V

IL

V

IL

V

IH

V

IH

X X X X X High Z V

V

IL

V

IL

V

IL

CE

Ý

OEÝWE

0

V

IL

V

IL

V

IH

V

IL

V

IH

V

IL

V

IL

V

IL

VIH)

Ý

A1DQ

V

V

V

IL

V

IH

XD

IH

X High Z X

IH

X X X High Z X

V

V

V

Ý

V

V

V

IL

IL

IH

e

VIL)

IL

IH

VIL0089H V

IH

V

V

IH

IH

V

V

V

XDINX

IL

Ý

A0DQ

XD

IH

X High Z X

IH

66A0H V

X X X High Z X

V

V

V

V

IL

V

IL

IH

V

IH

IH

V

IL

89H V

IL

V

A0H V

IH

XDINX

0-15

OUT

0-7

OUT

RY/BY

RY/BY

PP

e

V

X

OH

OH

OH

X

OH

OH

OH

PPH1

Ý

Ý

or

12

VS28F016SV, MS28F016SV FlashFileTMMemory

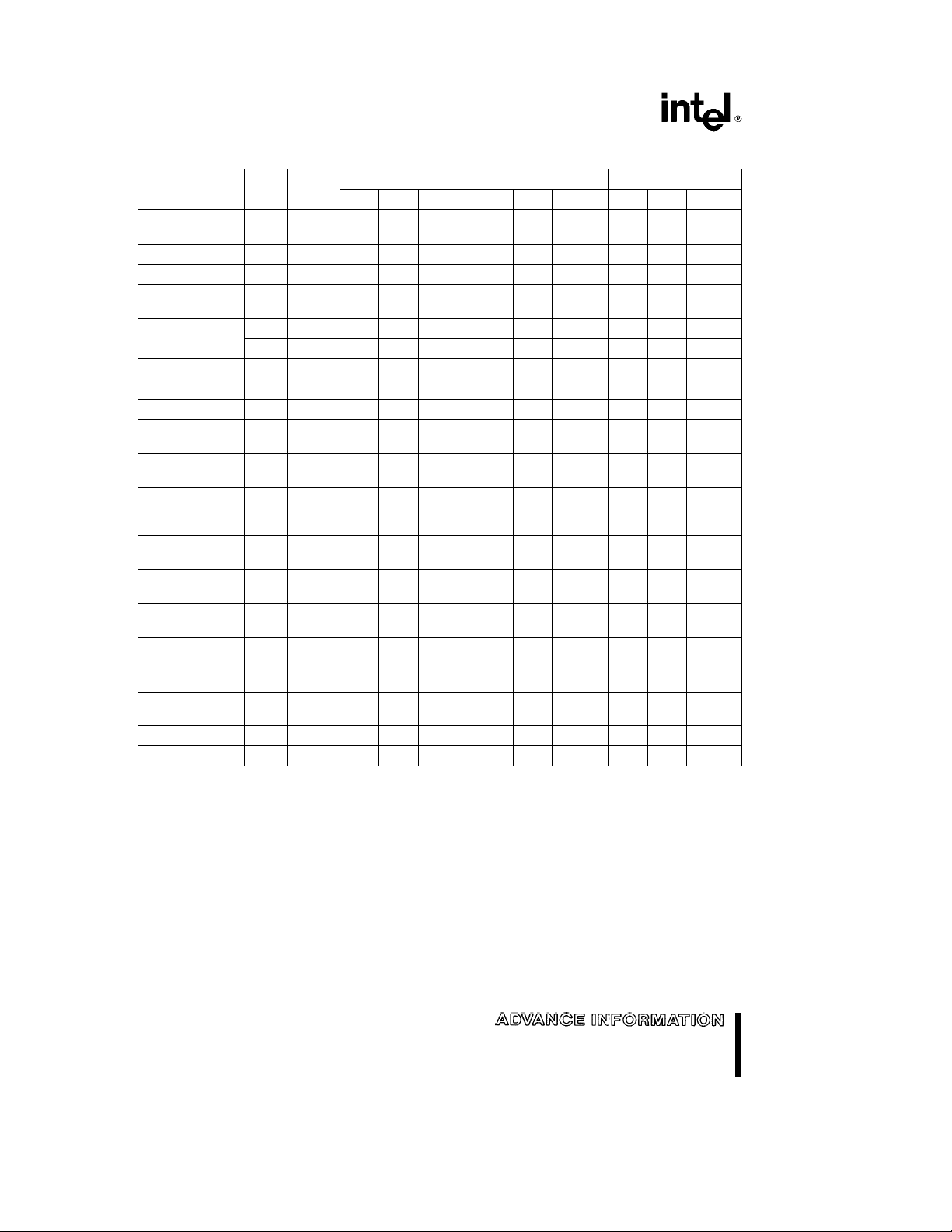

4.3 VE28F008 and M28F008 Compatible Mode Command Bus Definitions

Command Notes

Read Array Write X xxFFH Read AA AD

Intelligent Identiier 1 Write X xx90H Read IA ID

Read Compatible Status Register 2 Write X xx70H Read X CSRD

Clear Status Register 3 Write X xx50H

Word/Byte Write Write X xx40H Write WA WD

Alternate Word/Byte Write Write X xx10H Write WA WD

Block Erase/Confirm Write X xx20H Write BA xxD0H

Erase Suspend/Resume Write X xxB0H Write X xxD0H

ADDRESS DATA

e

Array Address ADeArray Data

AA

e

BA

Block Address CSRDeCSR Data

e

IA

ldentitier Address IDeIdentifier Data

e

Write Address WDeWrite Data

WA

e

X

NOTES:

1. Following the Intelligent Identifier command, two Read operations access the manutacturer and device signature codes.

2. The CSR is automatically available after device enters data write, erase, or suspend operations.

3. Clears CSR.3, CSR.4 and CSR.5. Also clears GSR.5 and all BSR.5, BSR.4 and BSR.2 bits. See Status Register defini-

tions.

4. The upper byte of the data bus (DQ

Don’t Care

) during command writes is a ‘‘Don’t Care’’ in x16 operation of the device.

8–15

First Bus Cycle Second Bus Cycle

Oper Addr Data

(4)

Oper Addr Data

(4)

13

VS28F016SV, MS28F016SV FlashFileTMMemory

4.4 VS/MS28F016SVÐPerformance Enhancement Command Bus Definitions

Command Mode Notes

Read Extended 1 Write X xx71H Read RA GSRD

Status Register

Page Buffer Swap 7 Write X xx72H

Read Page Buffer Write X xx75H Read PA PD

Single Load to Write X xx74H Write PA PD

Page Buffer

Sequential Load to x8 4,6,10 Write X xxE0H Write X BCL Write X BCH

Page Buffer

x16 4,5,6,10 Write X xxE0H Write X WCL Write X WCH

Page Buffer Write x8 3,4,9,10 Write X xx0CH Write A0BC(L,H) Write WA BC(H,L)

to Flash

x16 4,5,10 Write X xx0CH Write X WCL Write WA WCH

Two-Byte Write x8 3 Write X xxFBH Write A0WD(L,H) Write WA WD(H,L)

Lock Block/ Write X xx77H Write BA xxD0H

Confirm

Upload Status 2 Write X xx97H Write X xxD0H

Bits/Confirm

Upload Device 11 Write X xx99H Write X xxD0H

Information/

Confirm

Erase All Unlocked Write X xxA7H Write X xxD0H

Blocks/Confirm

RY/BYÝEnable to 8 Write X xx96H Write X xx01H

Level-Mode

RY/BYÝPulse- 8 Write X xx96H Write X xx02H

On-Write

RY/BYÝPulse- 8 Write X xx96H Write X xx03H

On-Erase

RY/BYÝDisable 8 Write X xx96H Write X xx04H

RY/BYÝPulse- 8 Write X xx96H Write X xx05H

On-Write/Erase

Sleep 12 Write X xxF0H

Abort Write X xx80H

First Bus Cycle Second Bus Cycle Third Bus Cycle

Oper Addr Data

(13)

Oper Addr Data

(13)

Oper Addr Data

BSRD

ADDRESS

e

Block Address

BA

e

Page Butter Address

PA

e

Extended Register Address

RA

e

Write Address

WA

e

Don’t Care

X

14

DATA

e

AD

Array Data

e

Page Buffer Data

PD

e

BSRD

e

GSRD

BSR Data

GSR Data

WC (L,H)

BC (L,H)

WD (L,H)

e

Word Count (Low, High)

e

Byte Count (Low, High)

e

Write Data (Low, High)

VS28F016SV, MS28F016SV FlashFileTMMemory

NOTES:

1. RA can be the GSR address or any BSR address. See Figures 4 and 5 for Extended Status Register memory maps.

2. Upon device power-up, all BSR lock-bits come up locked. The Upload Status Bits command must be written to reflect the

actual lock-bit status.

is automatically complemented to load second byte of data. BYTEÝmust be at VIL.A0value determines which

3. A

0

WD/BC is supplied first: A

4. BCH/WCH must be at 00H for this product because of the 256-byte (128-word) Page Buffer size, and to avoid writing the

Page Buffer contents to more than one 256-byte segment within an array block. They are simply shown for future Page

Buffer expandability.

5. In x16 mode, only the lower byte DQ

6. PA and PD (whose count is given in cycles 2 and 3) are supplied starting in the fourth cycle, which is not shown.

7. This command allows the user to swap between available Page Buffers (0 or 1).

8. These commands reconfigure RY/BY

9. Write address, WA, is the Destination address in the flash array which must match the Source address in the Page Buffer.

Refer to the 16-Mbit Flash Product Family User’s Manual.

e

10. BCL

11. After writing the Upload Device Information command and the Confirm command, the following information is output at

12. To ensure that the 28F0165V’s power consumption during Sleep Mode reaches the deep power-down current level, the

system also needs to de-select the chip by taking either or both CE

13. The upper byte of the data bus (DQ

00H corresponds to a byte count of 1. Similarly, WCLe00H corresponds to a word count of 1.

Page Buffer addresses specified below:

A page buffer swap followed by a page buffer read sequence is necessary to access this information. The contents of

all other Page Buffer locations, after the Upload Device Information command is written, are reserved for future implementation by Intel Corporation. See Section 4.8 for a description of the Device Configuration Code. This code also

corresponds to data written to the 28F016SV after writing the RY/BY

e

0 looks at the WDL/BCL, A

0

is used for WCL and WCH. The upper byte DQ

0-7

Ý

output to one of two pulse-modes or enable and disable the RY/BYÝfunction.

Address Information

06H, 07H (Byte Mode) Device Revision Number

03H (Word Mode) Device Revision Number

1EH (Byte Mode) Device Configuration Code

0FH (DQ

1FH (Byte Mode) Device Proliferation Code (01H)

0FH (DQ

) (Word Mode) Device Configuration Code

0–7

) (Word Mode) Device Proliferation Code (01H)

8–15

) during command wntes is a Don’t Care in x16 operation of the device.

8–15

e

1 looks at the WDH/BCH.

0

Ý

Reconfiguration command.

Ý

or CE

0

1

Ý

high.

is a don’t care.

8-15

15

Loading...

Loading...