Intel Corporation MR80C51FB-16, MD80C51FB-16, MD80C51FB Datasheet

October 1994 Order Number: 271172-002

M80C51FB

CHMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

Military

M80C51FB Ð 3.5 MHz to 12 MHz, V

CC

e

5V

g

20%

M80C51FB-16 Ð 3.5 MHz to 16 MHz, V

CC

e

5Vg20%

Y

Three 16-Bit Timer/Counters

Y

Programmable Clock Out

Y

Programmable Counter Array with:

Ð High Speed Output,

Ð Compare/Capture,

Ð Pulse Width Modulator,

Ð Watchdog Timer capabilities

Y

Up/Down Timer/Counter

Y

256 Bytes of On-Chip Data RAM

Y

Boolean Processor

Y

ONCE (On-Circuit Emulation) Mode

Y

Available in 40-pin CERDIP and

44-pin Leadless Chip Carrier Packages

Y

Gull Wing and J-Lead Packages also

Available

Y

32 Programmable I/O Lines

Y

7 Interrupt Sources

Y

Programmable Serial Channel with:

Ð Framing Error Detection

Ð Automatic Address Recognition

Y

TTL and CMOS Compatible Logic

Levels

Y

64K External Program Memory Space

Y

64K External Data Memory Space

Y

MCSÉ51 Microcontroller Fully

Compatible Instruction Set

Y

Power Saving Idle and Power Down

Modes

Y

Military Temperature Range:

b

55§Ctoa125§C(TC)

MEMORY ORGANIZATION

PROGRAM MEMORY: The M80C51FB can address up to 64K of program memory external to the chip.

DATA MEMORY: This microcontroller has a 256 x 8 on-chip RAM. In addition it can address up to 64K bytes of

external data memory.

The Intel M80C51FB is a single-chip control-oriented microcontroller which is fabricated on Intel’s reliable

CHMOS III-E technology. Being a member of the family of MCS 51 microcontrollers, the M80C51FB uses the

same powerful instruction set, has the same architecture, and is pin for pin compatible with the existing

MCS 51 microcontroller family of products. The M80C51FB is an enhanced version of the M80C51. Its added

features make it an even more powerful microcontroller for applications that require Pulse Width Modulation,

High Speed I/O, and up/down counting capabilities such as motor control or fin actuation. It also has a more

versatile serial channel that facilitates multi-processor communications.

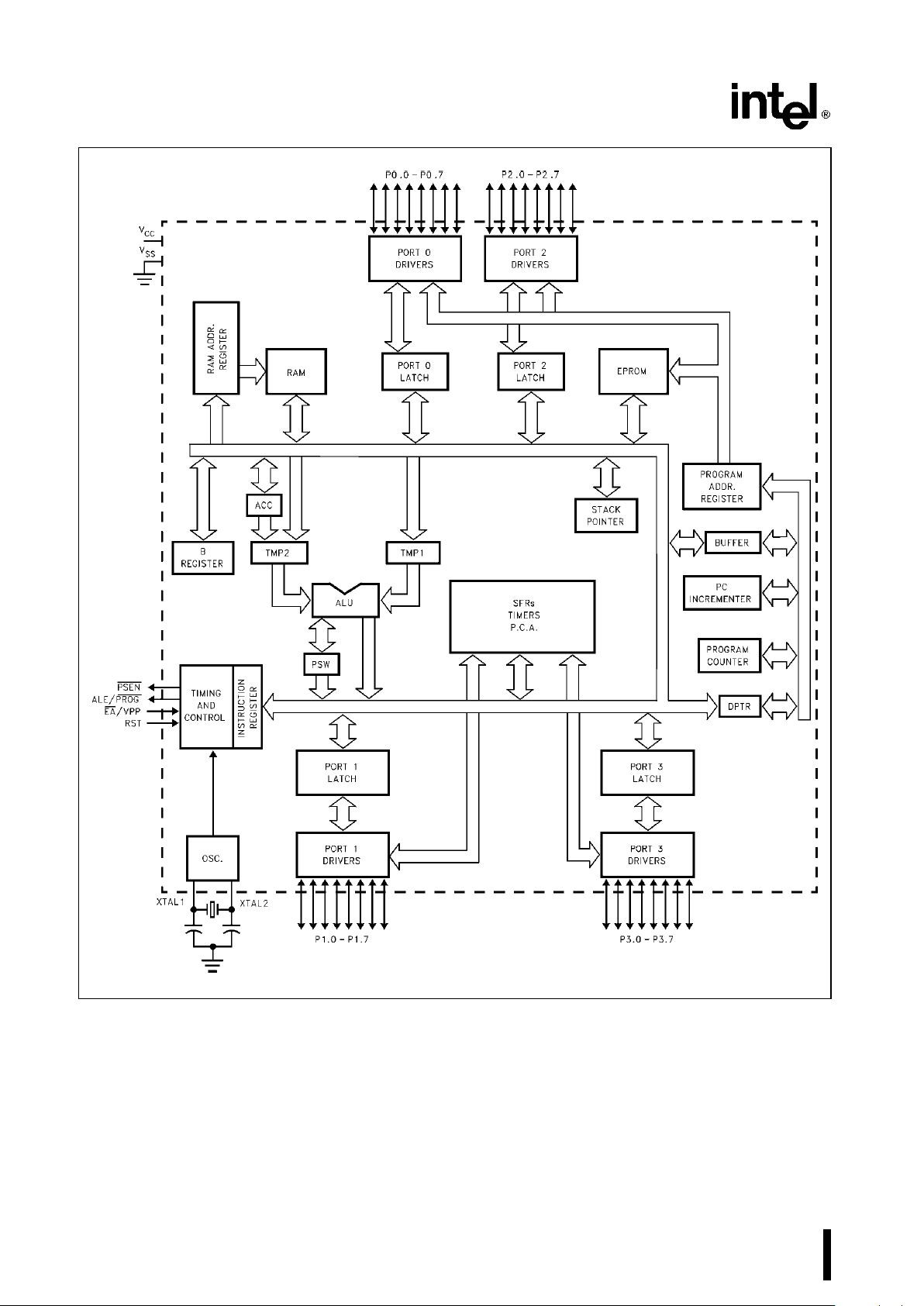

M80C51FB

271172–1

Figure 1. M80C51FB Block Diagram

2

M80C51FB

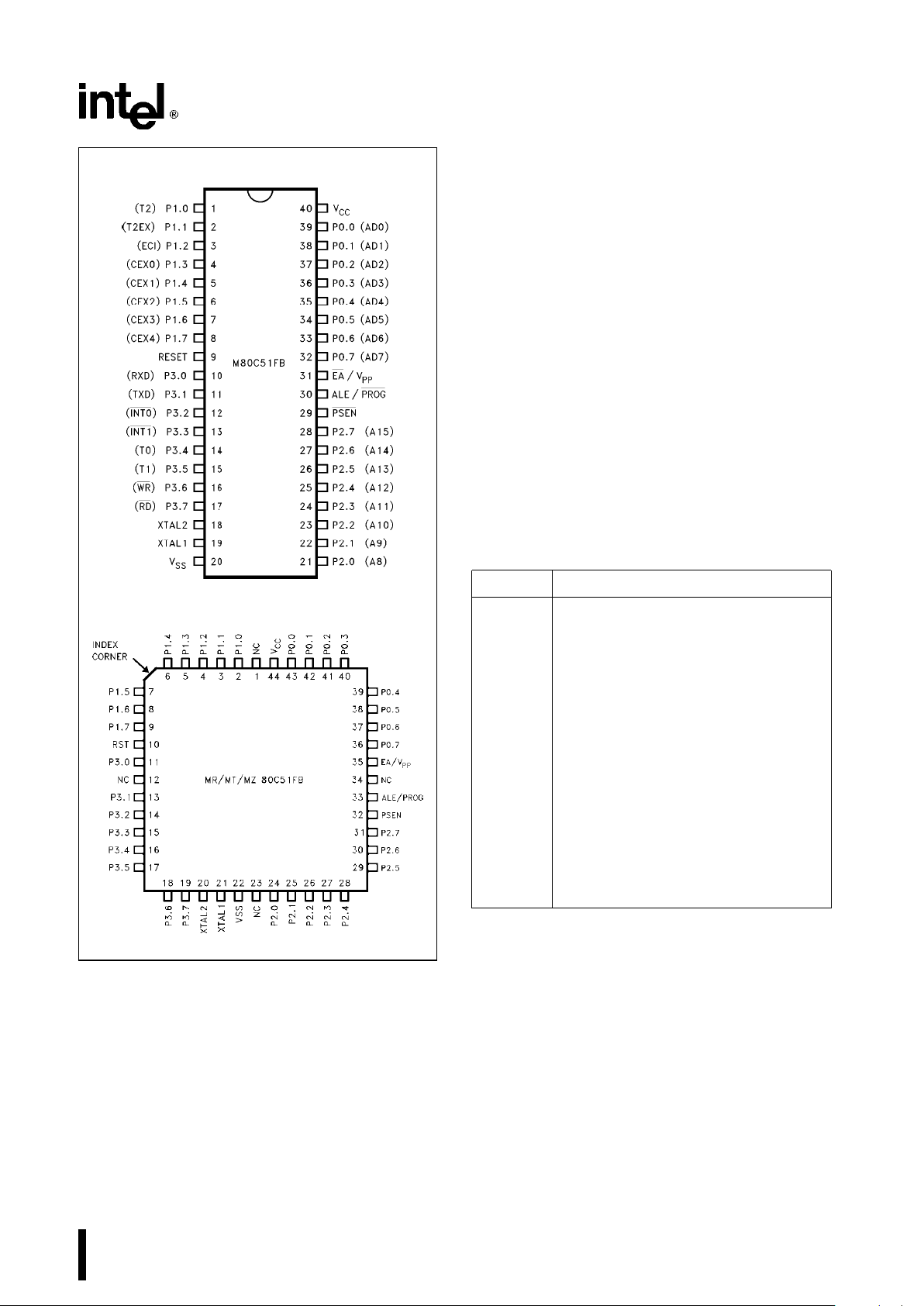

DIP

271172–2

LCC/Gull Wing/J-Lead

271172–3

Figure 2. M80C51FB Pin Connections

PIN DESCRIPTIONS

VCC: Supply voltage.

V

SS

: Circuit ground.

Port 0: Port 0 is an 8-bit, open drain, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. Port 0 pins that have 1’s written to them

float, and in that state can be used as high-impedance inputs.

Port 0 is also the multiplexed low-order address and

data bus during accesses to external Program and

Data Memory. In this application it uses strong internal pullups when emitting1’s, and can source and

sink several LS TTL inputs.

Port 1: Port 1 is an 8-bit bidirectional I/O port with

internal pullups. The Port 1 output buffers can drive

LS TTL inputs. Port 1 pins that have 1’s written to

them are pulled high by the internal pullups, and in

that state can be used as inputs. As inputs, Port 1

pins that are externally being pulled low will source

current (I

IL

, on the data sheet) because of the inter-

nal pullups.

In addition, Port 1 serves the functions of the following special features of the M80C51FB:

Port Pin Alternate Function

P1.0 T2 (External Count Input to Timer/

Counter 2)

P1.1 T2EX (Timer/Counter 2 Capture/

Reload Trigger and Direction Control)

P1.2 ECI (External Count Input to the PCA)

P1.3 CEX0 (External I/O for Compare/

Capture Module 0)

P1.4 CEX1 (External I/O for Compare/

Capture Module 1)

P1.5 CEX2 (External I/O for Compare/

Capture Module 2)

P1.6 CEX3 (External I/O for Compare/

Capture Module 3)

P1.7 CEX4 (External I/O for Compare/

Capture Module 4)

Port 2: Port 2 is an 8-bit bidirectional I/O port with

internal pullups. The Port 2 output buffers can drive

LS TTL inputs. Port 2 pins that have 1’s written to

them are pulled high by the internal pullups, and in

that state can be used as inputs. As inputs, Port 2

pins that are externally being pulled low will source

current (I

IL

, on the data sheet) because of the inter-

nal pullups.

3

M80C51FB

Port 2 emits the high-order address byte during

fetches from external Program Memory and during

accesses to external Data Memory that use 16-bit

addresses (MOVX

@

DPTR). In this application it

uses strong internal pullups when emitting 1’s. During accesses to external Data Memory that use 8-bit

addresses (MOVX

@

Ri), Port 2 emits the contents of

the P2 Special Function Register.

Port 3: Port 3 is an 8-bit bidirectional I/O port with

internal pullups. The Port 3 output buffers can drive

LS TTL inputs. Port 3 pins that have 1’s written to

them are pulled high by the internal pullups, and in

that state can be used as inputs. As inputs, Port 3

pins that are externally being pulled low will source

current (I

IL

, on the data sheet) because of the pull-

ups.

Port 3 also serves the functions of various special

features of the M8051 Family, as listed below:

Port Pin Alternate Function

P3.0 RXD (serial input port)

P3.1 TXD (serial output port)

P3.2 INT0 (external interrupt 0)

P3.3 INT1

(external interrupt 1)

P3.4 T0 (Timer 0 external input)

P3.5 T1 (Timer 1 external input)

P3.6 WR

(external data memory write strobe)

P3.7 RD

(external data memory read strobe)

RST: Reset input. A high on this pin for two machine

cycles while the oscillator is running resets the device. An internal pulldown resistor permits a poweron reset with only a capacitor connected to V

CC

.

ALE: Address Latch Enable output pulse for latching

the low byte of the address during accesses to external memory.

In normal operation ALE is emitted at a constant

rate of (/6 the oscillator frequency, and may be used

for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

PSEN

: Program Store Enable is the read strobe to

external Program Memory.

When the M80C51FB is executing code from external Program Memory, PSEN

is activated twice each

machine cycle, except that two PSEN

activations

are skipped during each access to external Data

Memory.

EA

: External Access enable. EA must be strapped to

VSS in order to enable the device to fetch code from

external Program Memory.

XTAL1: Input to the inverting oscillator amplifier.

XTAL2: Output from the inverting oscillator amplifier.

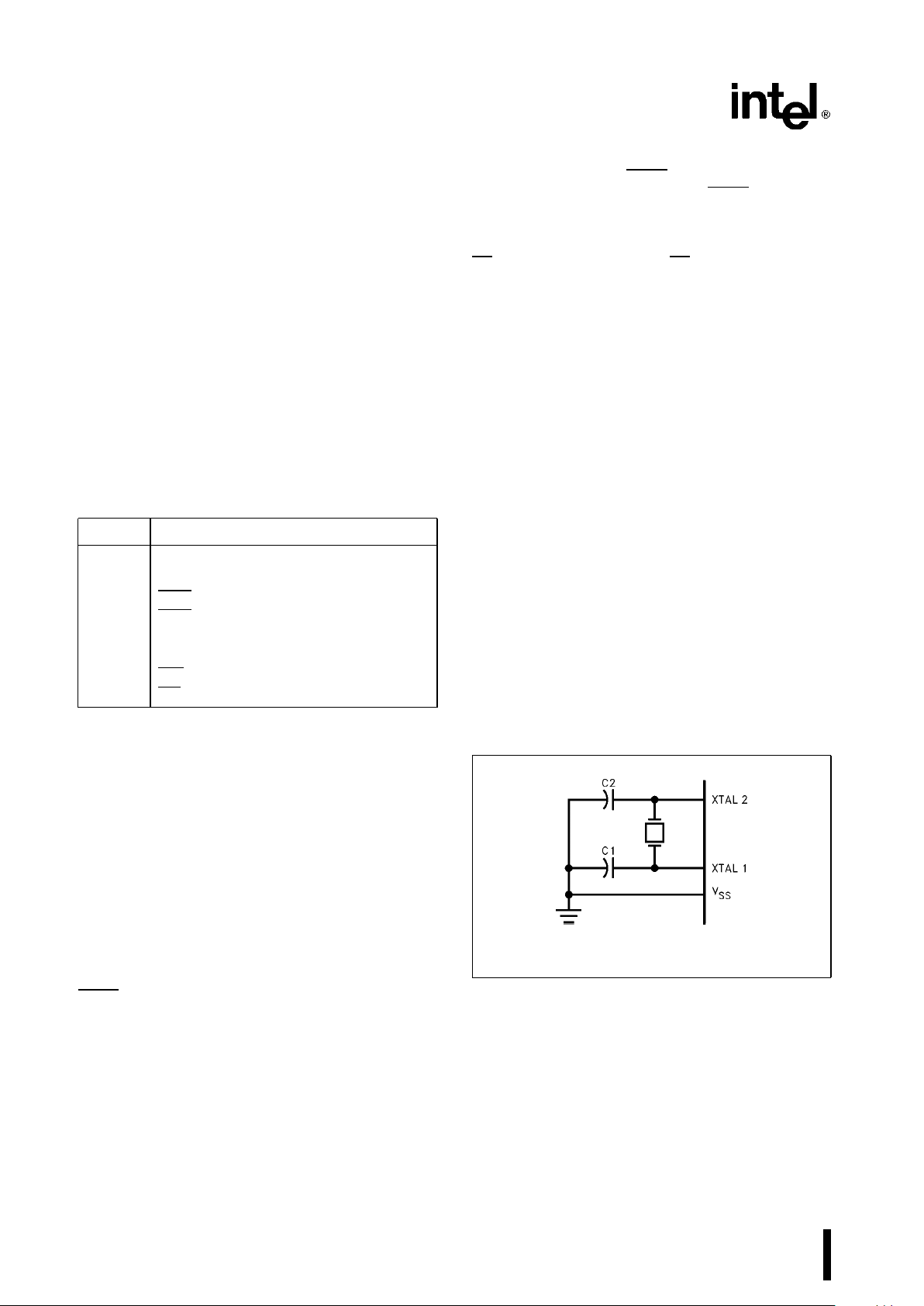

OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in

Figure 3. Either a quartz crystal or ceramic resonator

may be used. More detailed information concerning

the use of the on-chip oscillator is available in Application Note AP-155, ‘‘Oscillators for Microcontrollers.’’

To drive the device from an external clock source,

XTAL1 should be driven, while XTAL2 floats, as

shown in Figure 4. There are no requirements on the

duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum

high and low times specified on the data sheet must

be observed.

271172–4

C1, C2

e

30 pFg10 pF for Crystals

e

10 pF for Ceramic Resonators

Figure 3. Oscillator Connections

4

Loading...

Loading...