Datasheet GT28F032C3T90, GT28F032C3T110, GT28F032C3B90, GT28F032C3B110 Datasheet (Intel Corporation)

E

3 VOLT ADVANCED+ BOOT BLOCK

FLASH MEMORY FAMILY

28F008C3, 28F016C3, 28F032C3

28F800C3, 28F160C3, 28F320C3

n

Flexible SmartVoltage Technology

2.7 V–3.6 V Read/Program/Erase

2.7 V or 1.65 V I/O Option Reduces

Overall System Power

12 V for Fast Production

Programming

n

High Performance

2.7 V–3.6 V: 90 ns Max Access Time

3.0 V–3.6 V: 80 ns Max Access Time

n

Optimized Architecture for Code Plus

Data Storage

Eight 8-Kbyte Blocks,

Top or Bottom Locations

Up to Sixty-Three 64-KB Blocks

Fast Program Suspend Capability

Fast Erase Suspend Capability

n

Flexible Block Locking

Lock/Unlock Any Block

Full Protection on Power-Up

WP# Pin for Hardware Block

Protection

VPP = GND Option

VCC Lockout Voltage

n

Low Power Consumption

9 mA Typical Read Power

10 µA Typical Standby Power with

Automatic Power Savings Feature

n

Extended Temperature Operation

–40 °C to +85 °C

8-, 16-, 32-MBIT

n

Easy-12 V

Faster Production Programming

No Additional System Logic

n

128-bit Protection Register

64-bit Unique Device Identifier

64-bit User Programmable OTP

Cells

n

Extended Cycling Capability

Minimum 100,000 Block Erase

Cycles

n

Flash Data Integrator Software

Flash Memory Manager

System Interrupt Manager

Supports Parameter Storage,

Streaming Data (e.g., voice)

n

Automated Word/Byte Program and

Block Erase

Command User Interface

Status Registers

n

SRAM-Compatible Write Interface

n

Cross-Compatible Command Support

Intel Basic Command Set

Common Flash Interface

n

x 16 for High Performance

48-Ball µBGA* Package

48-Lead TSOP Package

n

x 8 I/O for Space Savings

48-Ball µBGA* Package

40-Lead TSOP Package

n

0.25 µ ETOX™ VI Flash Technology

PRODUCT PREVIEW

The 0.25 µm 3 Volt Advanced+ Boot Block, manufactured on Int el’s latest 0.25 µ technology , represents a

feature-rich solution at overall lower system cost. Smart 3 flash memory devices incorporate low voltage

capability (2.7 V read, program and erase) with high-speed, low-power operation. Flexible block locking

allows any block to be independently locked or unlocked. Add to this the Intel-developed Flash Data

Integrator (FDI) software and you have a cost-effective, flexible, monolit hi c code plus data storage s ol ution on

the market today. 3 Volt Adv anced+ Boot Block product s will be available in 48-lead TSOP , 40-lead TSOP,

and 48-ball µBGA* packages. Additional information on this product family can be obtained by accessing

Intel’s WWW page: http://www.intel.com/design/flcomp.

May 1998 Order Number: 290645-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F008C3, 28F016C3, 28F032C3, 28F800C3, 28F160C3, 28F320C3 may contain design defects or errors known as

errata which may cause the product to deviate from published specifications. Current characterized errata are available on

request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call 1-800-548-4725

or visit Intel’s website at http:\\www.intel.com

COPYRIGHT © INTEL CORPORATION 1998 CG-041493

*Third-party brands and names are the property of their respective owners.

E 3 VOLT ADVANCED+ BOOT BLOCK

CONTENTS

PAGE PAGE

1.0 INTRODUCTION .............................................5

1.1 3 Volt Advanced+ Boot Block Flash Memory

Enhancements............................................5

1.2 Product Overview.........................................6

2.0 PRODUCT DESCRIPTION..............................6

2.1 Package Pinouts..........................................6

2.2 Block Organization.....................................10

2.2.1 Parameter Blocks................................10

2.2.2 Main Blocks.........................................10

3.0 PRINCIPLES OF OPERATION .....................11

3.1 Bus Operation............................................11

3.1.1 Read....................................................11

3.1.2 Output Disable.....................................11

3.1.3 Standby...............................................11

3.1.4 Reset...................................................12

3.1.5 Write....................................................12

3.2 Modes of Operation....................................12

3.2.1 Read Array..........................................12

3.2.2 Read Configuration..............................13

3.2.3 Read Status Register ..........................13

3.2.3.1 Clearing the Status Register.........13

3.2.4 Read Query.........................................13

3.2.5 Program Mode.....................................14

3.2.5.1 Suspending and Resuming

Program .......................................14

3.2.6 Erase Mode.........................................14

3.2.6.1 Suspending and Resuming Erase.15

3.3 Flexible Block Locking................................19

3.3.1 Locking Operation ...............................19

3.3.2 Locked State .......................................19

3.3.3 Unlocked State....................................19

3.3.4 Lock-Down State.................................19

3.3.5 Reading a Block’s Lock Status ............20

3.3.6 Locking Operations during Erase

Suspend.............................................20

3.3.7 Status Register Error Checking ...........20

PRODUCT PREVIEW

3.4 128-Bit Protection Register.........................21

3.4.1 Reading the Protection Register..........21

3.4.2 Programming the Protection Register..21

3.4.3 Locking the Protection Register...........22

3.5 V

Program and Erase Voltages...............22

PP

3.5.1 Easy-12 V Operation for Fast

Manufacturing Programming...............22

3.5.2 V

3.5.3 V

3.6 Power Consumption...................................23

3.6.1 Active Power (Program/Erase/Read)...23

3.6.2 Automatic Power Savings (APS) .........23

3.6.3 Standby Power....................................23

3.6.4 Deep Power-Down Mode.....................24

3.7 Power-Up/Down Operation.........................24

3.7.1 RP# Connected to System Reset ........24

3.7.2 V

3.8 Power Supply Decoupling ..........................24

4.0 ABSOLUTE MAXIMUM RATINGS................25

4.2 Operating Conditions..................................25

4.3 Capacitance...............................................26

4.4 DC Characteristics .....................................26

4.5 AC Characteristics—Read Operations—

4.6 AC Characteristics—Write Operations—

4.7 Erase and Program Timings.......................33

4.8 Reset Operations .......................................35

5.0 ORDERING INFORMATION..........................36

6.0 ADDITIONAL INFORMATION.......................37

APPENDIX A: WSM Current/Next States..........38

APPENDIX B: Program/Erase Flowcharts........40

APPENDIX C: Common Flash Interface Query

Structure......................................................46

≤ V

PP

PP

CC

Extended Temperature..............................30

Extended Temperature..............................32

for Complete Protection...22

PPLK

Usage...........................................22

, VPP and RP# Transitions.............24

3

3 VOLT ADVANCED+ BOOT BLOCK E

APPENDIX D: Architecture Block Diagram......52

APPENDIX E: Word-Wide Memory Map

Diagrams .....................................................53

APPENDIX F: Byte-Wide Memory Map

Diagrams .....................................................55

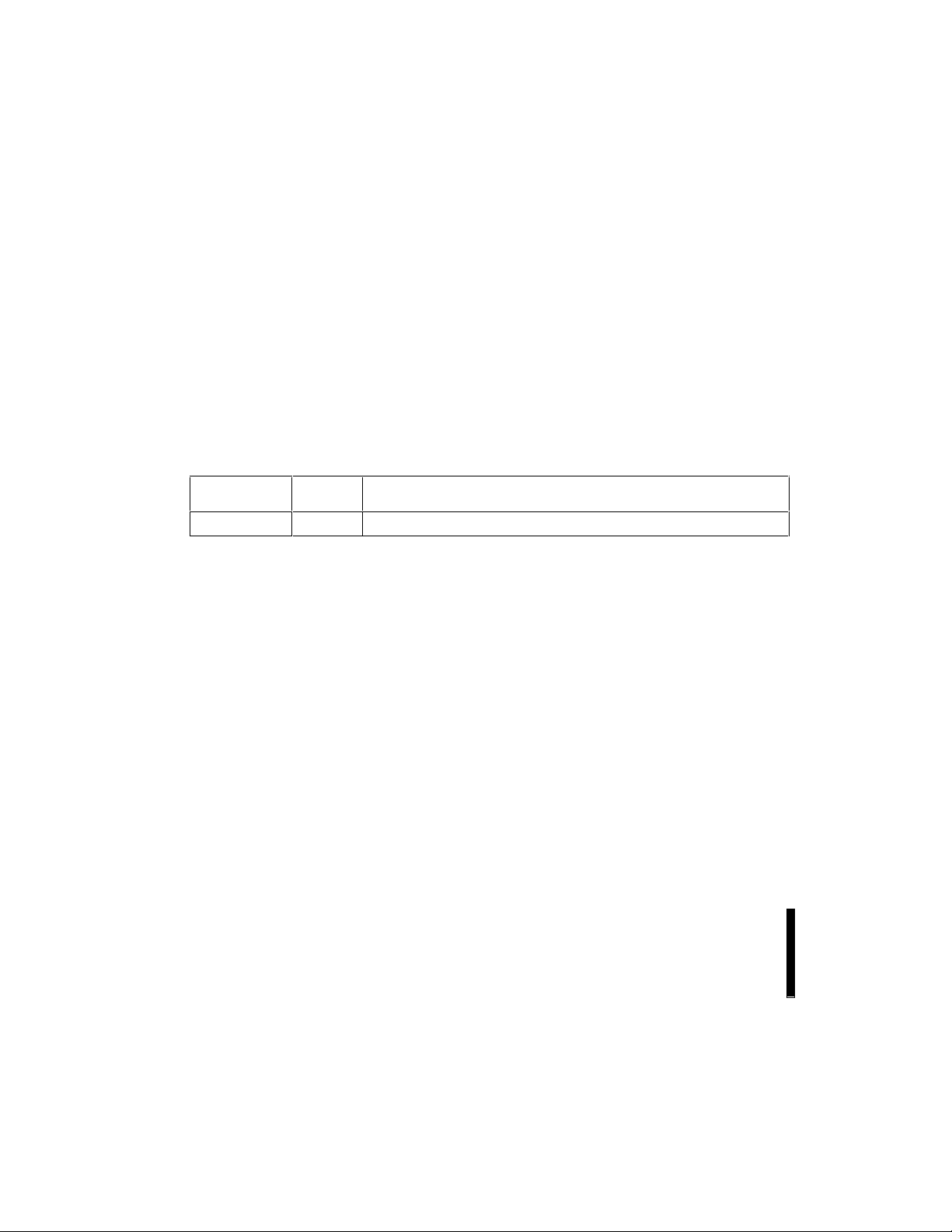

REVISION HISTORY

Date of

Revision

05/12/98 -001 Original version

Version Description

APPENDIX G: Device ID Table ..........................57

APPENDIX H: Protection Register

Addressing..................................................58

4

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

1.0 INTRODUCTION

1.1 3 Volt Advanced+ Boot Block Flash Memory Enhancements

This document contains the specifications for the

3 Volt Advanced+ Boot B lock flash memory family .

These flash memories add features which can be

used to enhance the security of systems: instant

block locking and a protection register.

Throughout this document, t he term “2.7 V” refers

to the full voltage range 2.7 V –3.6 V (except where

noted otherwise) and “V

±5%. Sections 1 and 2 provide an overview of the

flash memory family including appli cations, pinouts,

pin descriptions and memory organization. Section

3 describes the operation of these produc ts . Fi nally ,

Section 4 contains the operating specifications.

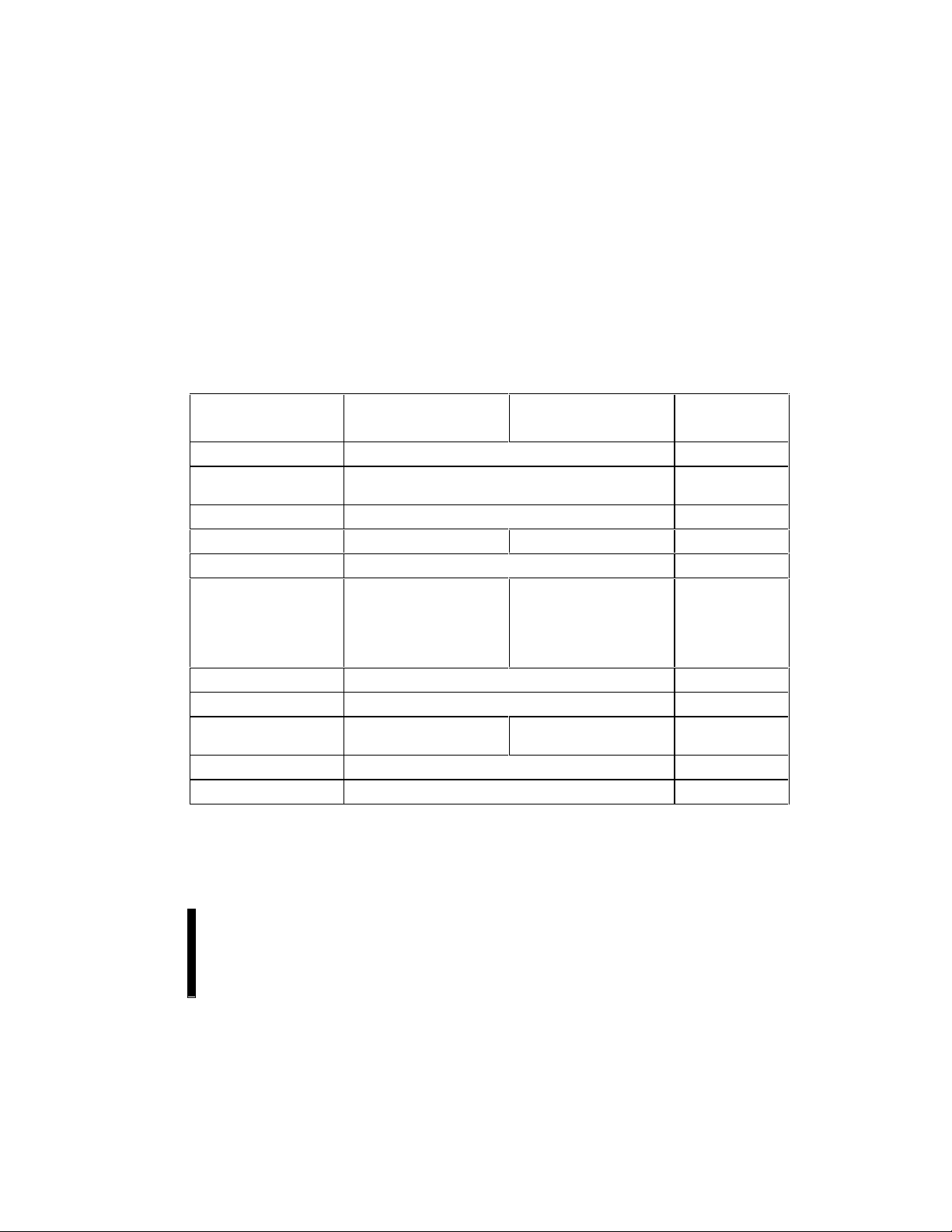

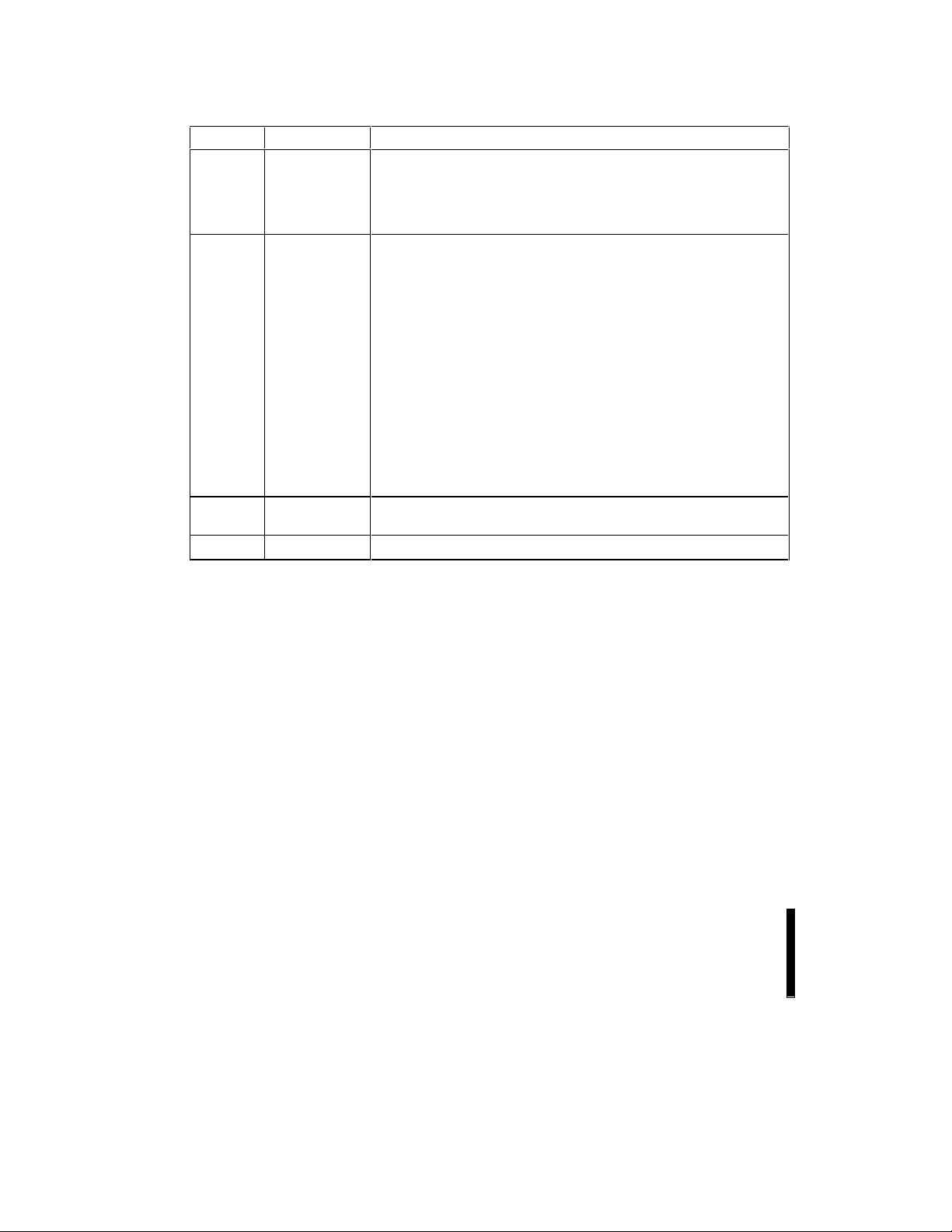

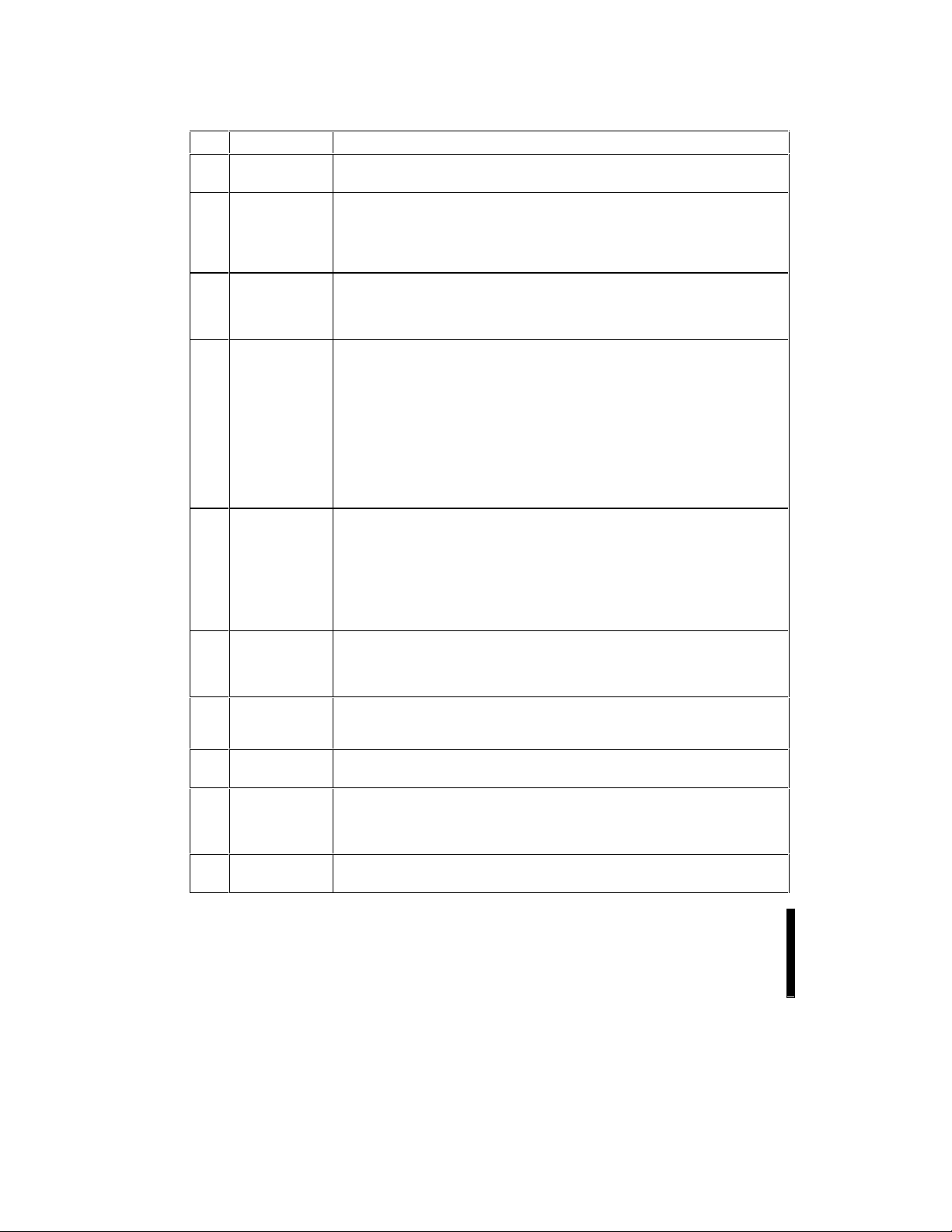

Feature

VCC Operating Voltage 2.7 V – 3.6 V Table 8

VPP Voltage Provides complete write protection with

V

I/O Voltage 2.7 V– 3.6 V Note 3

CCQ

Bus Width 8-bit 16-bit Table 2

Speed (ns) 90, 110 @ 2.7 V and 80, 100 @ 3.0 V Table 11

Blocking (top or bottom) 8 x 8-Kbyte parameter

Operating Temperature Extended: –40 °C to +85 °C Table 8

Program/Erase Cycling 100,000 cycles Table 8

Packages 40-Lead TSOP

Block Locking Flexible locking of any block with zero latency Section 3.3

Protection Register 64-bit unique device number, 64-bit user programmable Section 3.4

NOTES:

1. 32-Mbit density not available in 40-lead TSOP.

2. 8-Mbit density not available in µBGA* CSP.

operation at 1.65 V — 2.5 V available upon request.

3. V

CCQ

= 12 V” refers to 12 V

PP

Table 1. 3 Volt Advanced+ Boot Block Feature Summary

(2)

8 M

16 M

(1)

32 M

optional 12V Fast Programming

4-Mb: 7 x 64-Kbyte main

8-Mb: 15 x 64-Kbyte main

16-Mb: 31 x 64-Kbyte main

32-Mb: 63 x 64-Kbyte main

48-Ball µBGA* CSP

The 3 Volt Advanced+ Boot Block flash memory

features:

• Zero-latency, flexible block locking

• 128-bit Protection Register

• Simple system implementation for 12 V

production programming with 2.7 V in-field

programming

• Ultra-low power operation at 2.7 V

• Minimum 100,000 block erase cycles

• Common Flash Interface for s oftware query of

device specs and features

(2)

8 M

16 M

32 M

Table 8

8 x 4-Kword parameter

4-Mb: 7 x 32-Kword main 8-

Mb: 15 x 32-Kword main

16-Mb: 31 x 32-Kword main

32-Mb: 63 x 32-Kword main

(1)

(2)

48-Lead TSOP

48-Ball µBGA* CSP

Section 2.2

Appendix E and F

Figures 1, 2, 3,

(2)

and 4

Reference

PRODUCT PREVIEW

5

3 VOLT ADVANCED+ BOOT BLOCK E

1.2 Product Overview

Intel provides secure low v oltage memory solutions

with the Advanced Boot B lock fami ly of product s. A

new block locking feature allows instant

locking/unlocking of any block with zero-latency. A

128-bit protection register allows unique flash

device identification.

Discrete supply pins provide single voltage read,

program, and erase capability at 2.7 V while also

allowing 12 V V

programming. Easy-12 V, a new feature designed

to reduce external logic, simplifies board designs

when combining 12 V production programming with

2.7 V in-field programming.

The 3 Volt Advanced+ Boot Block flash memory

products are available in either x8 or x16 pac kages

in the following densities : (see Section 6,

Information

• 8-Mbit (8,388,608 bit) flash memories organized

• 16-Mbit (16,777,216 bit) flash memories

• 32-Mbit (33,554,432 bit) flash memories

Eight 8-KB parameter blocks are located at either

the top (denoted by -T suffix) or the bottom (-B

suffix) of the address map in order t o ac com modate

different microprocessor protocols for kernel code

location. The remaining memory is grouped into 64Kbyte main blocks.

)

as either 512 Kwords of 16 bits each or 1024

Kbytes or 8 bits each.

organized as either 1024 Kwords of 16 bits

each or 2048 Kbytes of 8 bits each.

organized as either 2048 Kwords of 16 bits

each or 4096 Kbytes of 8 bits each.

for faster production

PP

Ordering

The status register indicates the status of the WSM

by signifying block erase or word program

completion and status.

Program and erase automation allows program and

erase operations to be executed using an indust rystandard two-write command sequence t o the CUI.

Program operations are performed in word or byte

increments. Erase operations erase all locations

within a block simultaneously. Both program and

erase operations can be suspended by the system

software in order to read from any other block. In

addition, data can be programmed to anot her block

during an erase suspend.

The 3 Volt Advanced+ Boot Block flash memories

offer two low power savings features: Automatic

Power Savings (APS) and standby mode. The

device automatically enters APS mode following the

completion of a read cycle. Standby mode is

initiated when the system deselects the device by

driving CE# inactive. Combined, these two power

savings features significantly reduce power

consumption.

The device can be reset by lowering RP# to GND.

This provides CPU-memory reset synchronization

and additional protection against bus noise that

may occur during system reset and power-up/down

sequences (see Section 3.5 and 3.6).

Refer to the

complete current and voltage s pecifications. Refer

to the

read and write performance specific ations. Program

and erase times and shown in Section 4.7.

DC Characteristics

AC Characteristic s

Section 4.4 for

Sections 4.5 and 4.6, f or

2.0 PRODUCT DESCRIPTION

All blocks can be locked or unlocked instantly to

provide complete protecti on for code or data. (see

Section 3.3 for details).

The Command User Interface (CUI) s erves as the

interface between the microprocessor or

microcontroller and the internal operation of the

flash memory. The internal Write State Machine

(WSM) automatically executes the algorithms and

timings necessary for program and erase

operations, including verification, thereby

unburdening the microprocessor or microcontroller.

6

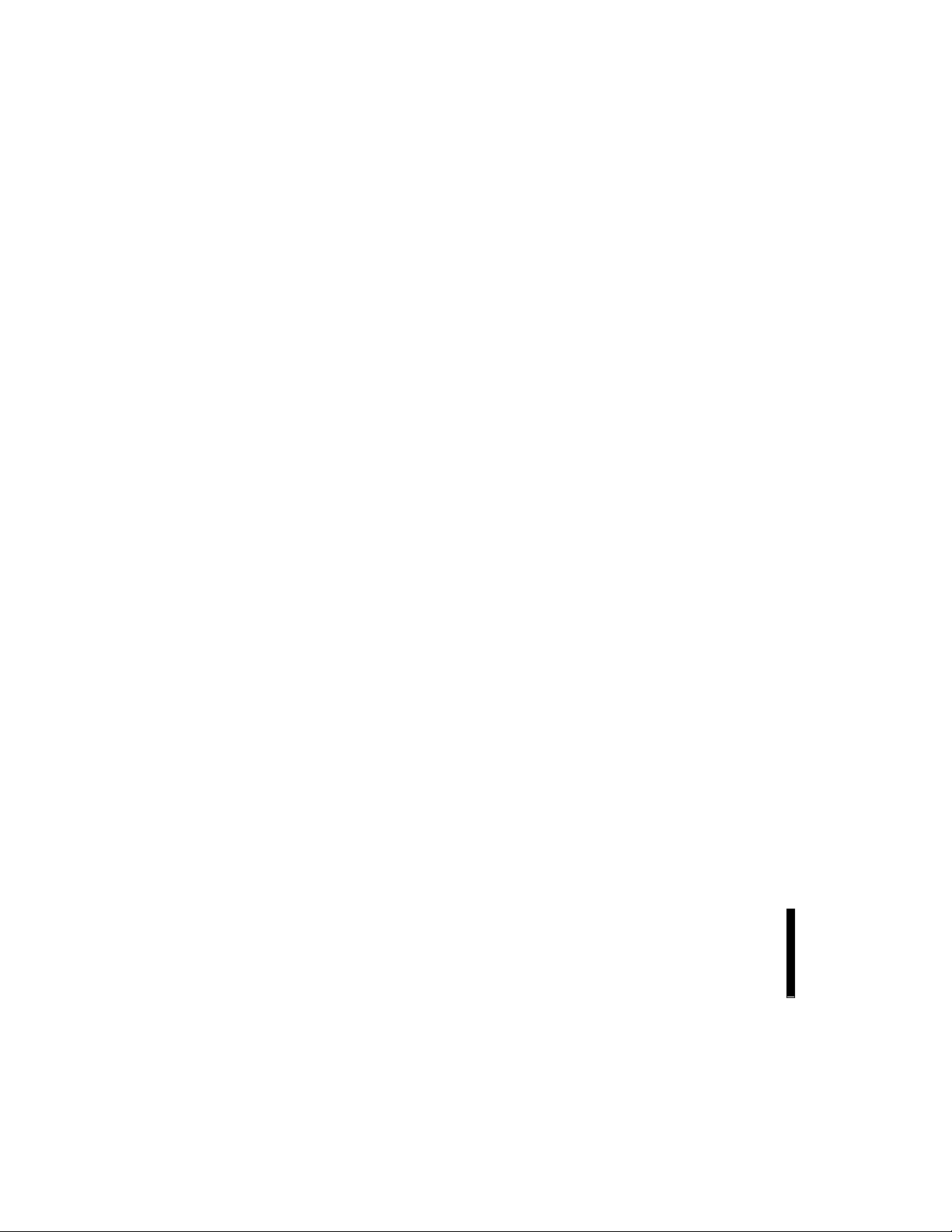

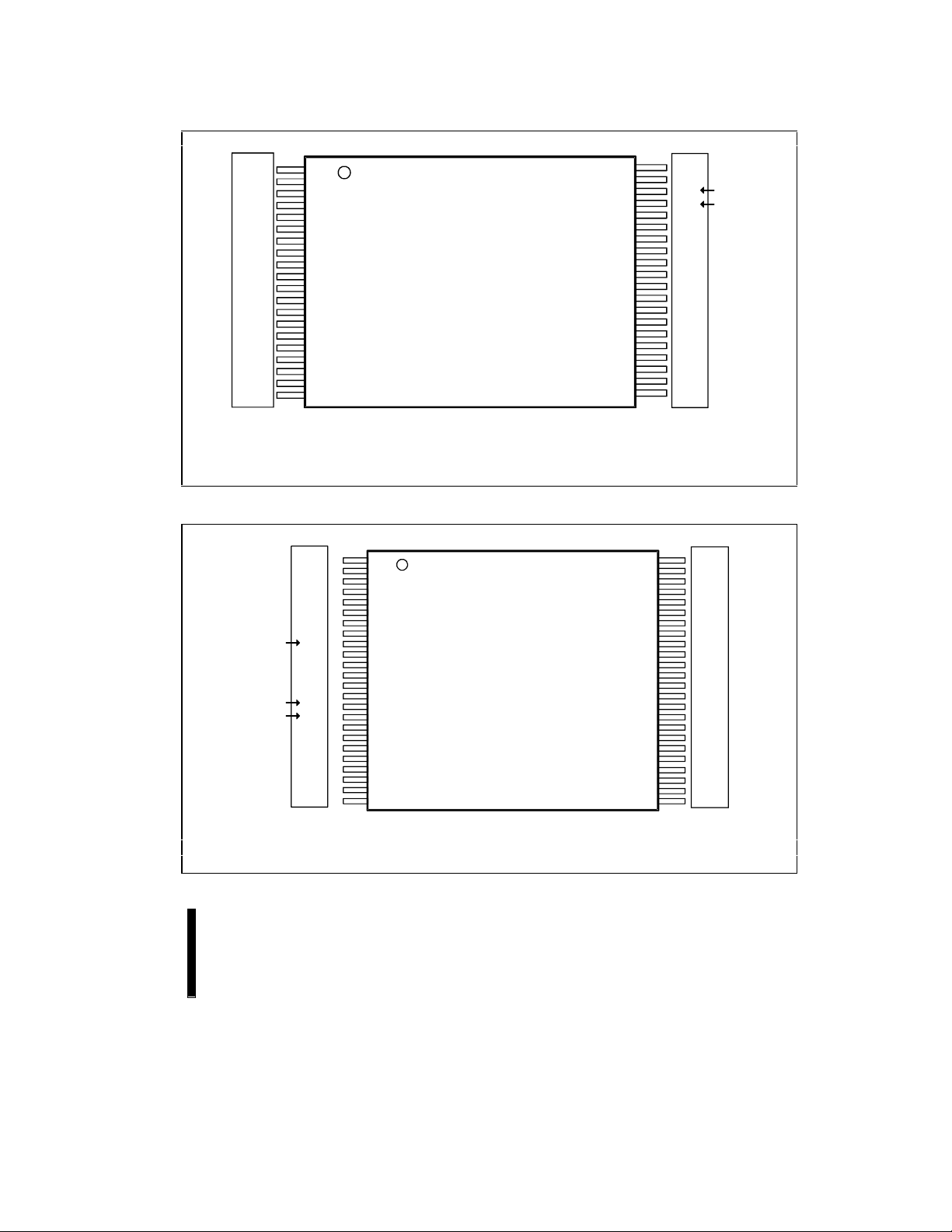

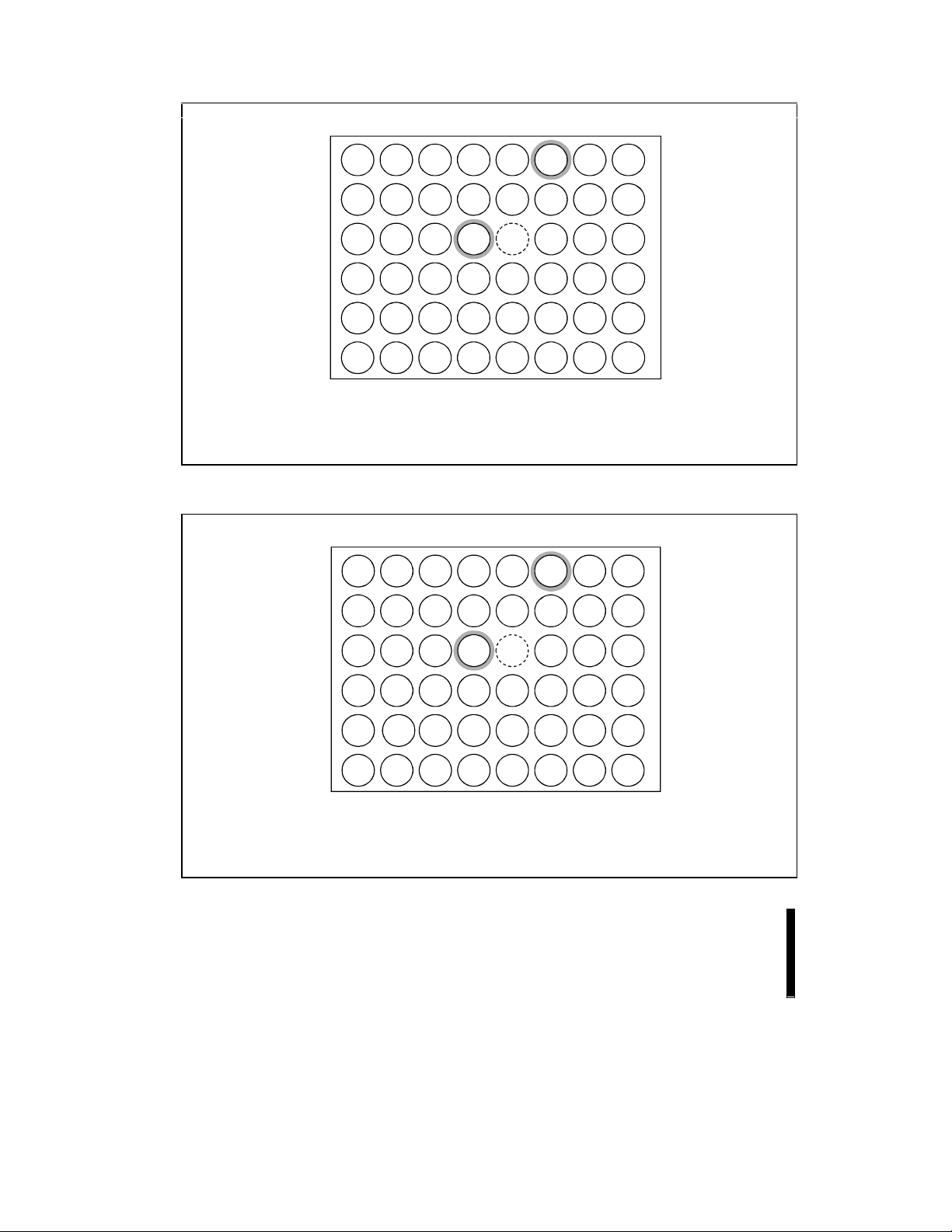

This section provides device pin descriptions and

package pinouts for the 3 Volt Advanced+ Boot

Block flash memory f amily, which is availabl e in 40Lead TSOP (x8, Figure 1), 48-lead TSOP (x16,

Figure 2) and 48-ball µBGA packages (Figures 3

and 4).

2.1 Package Pinouts

In each diagram, upgrade pins from one dens ity to

the next are circled.

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

A

A

A

A

A

A

A

A

WE#

RP#

V

PP

WP#

A

A

A

A

A

A

A

A

16

15

14

13

12

11

9

8

18

7

6

5

4

3

2

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Advanced Boot

40-Lead TSOP

10 mm x 20 mm

TOP VIEW

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

A

17

GND

A

20

A

19

A

10

DQ

DQ

DQ

DQ

V

CCQ

V

CC

NC

DQ

DQ

DQ

DQ

OE#

GND

CE#

A

0

16M

8M

7

6

5

4

3

2

1

0

NOTES:

1. 40-Lead TSOP available for 8- and 16-Mbit densities only.

2. Lower densities will have NC on the upper address pins. For example, an 8-Mbit device will have NC on Pin 38.

Figure 1. 40-Lead TSOP Package for x8 Configurations

A

A

15

A

14

A

13

A

12

A

11

A

10

A

9

A

8

A

32M

20

NC

WE#

RP#

V

PP

WP#

A

16M

19

A

8M

18

A

17

A

7

A

6

A

5

A

4

A

3

A

2

A

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Advanced Boot Block

48-Lead TSOP

12 mm x 20 mm

TOP VIEW

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

NOTE:

Lower densities will have NC on the upper address pins. For example, an 8-Mbit device will have NC on Pins 9 and 15.

16

V

CCQ

GND

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

V

CC

DQ

DQ

DQ

DQ

DQ

DQ

DQ

DQ

OE#

GND

CE#

A

0

15

7

14

6

13

5

12

4

11

3

10

2

9

1

8

0

Figure 2. 48-Lead TSOP Package for x16 Configurations

PRODUCT PREVIEW

7

3 VOLT ADVANCED+ BOOT BLOCK E

12345678

A

13

A

B

14A10

C

A15A

D

A

16D14D5

E

V

CCQ

F

GND D7D

A

11A8

12A9

D

15D6

VPPWP# A

WE# RP# A

32M

A

20

D

11D2

D

12D3

13D4VCCD10D1

16M

A

19

18A17A5

A

6

D8CE# A

D9D0GND

A

7

4A

A

2

A

A

3

1

0

OE#

NOTES:

1. Shaded connections indicate the upgrade address connections. Lower density devices will not have the upper address

solder balls. Routing is not recommended in this area. A19 is the upgrade address for the 16-Mbit device. A20 is the

upgrade address for the 32-Mbit device.

2. 8-Mbit not available on µBGA* CSP.

Figure 3. x16 48-Ball µBGA* Chip Size Package (Top View, Ball Down)

12345678

A

A14A

12A8

V

PP

WP#

16M

A

A

20

A

7

4

A

B

15A10

A16A

C

D

A

17

E

V

CCQA11D6

F

GND

13A9

NC

D

7

WE#

D

NC

32M

5

RP#

A

21

NC

NC

D4V

A19A

D

2

D

3

CC

18A5

A6A

NC CE#

D

NC

D

NC

A

2

A

3

1

A

0

GND

0

OE#

1

NOTES:

1. Shaded connections indicate the upgrade address connections. Lower density devices will not have the upper address

solder balls. Routing is not recommended in this area. A

upgrade address for the 32-Mbit device.

is the upgrade address for the 16-Mbit device. A

20

21

is the

2. 8-Mbit not available on µBGA* CSP.

Figure 4. x8 48-Ball µBGA* Chip Size Package (Top View, Ball Down)

8

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

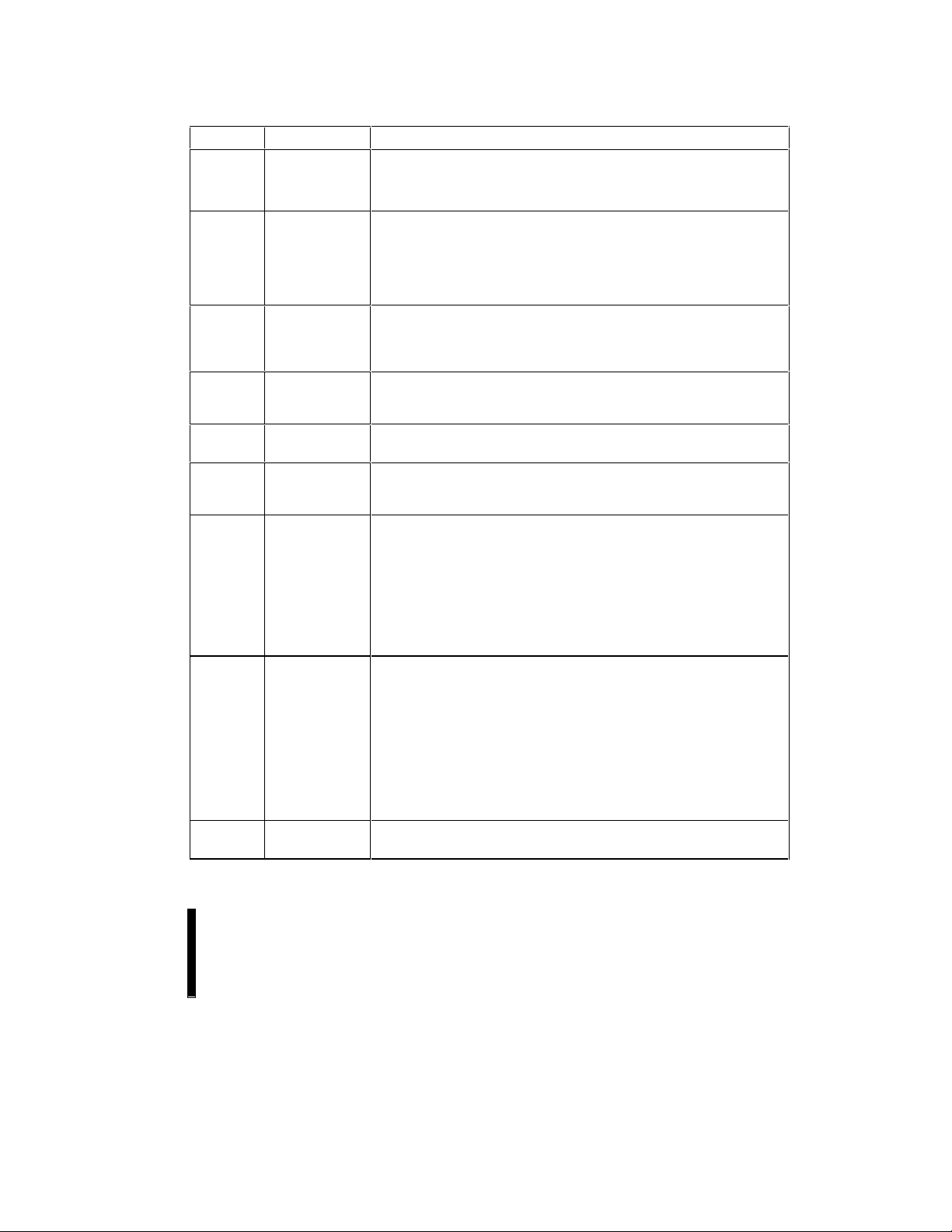

Table 2. 3 Volt Advanced+ Boot Block Pin Descriptions

Symbol Type Name and Function

A0–A

21

DQ0–DQ7INPUT/OUTPUT DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and

DQ8–DQ15INPUT/OUTPUT DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and

CE# INPUT CHIP ENABLE: Activates the internal control logic, input buffers,

OE# INPUT OUTPUT ENABLE: Enables the device’s outputs through the data

WE# INPUT WRITE ENABLE: Controls writes to the Command Register and

RP# INPUT RESET/DEEP POWER-DOWN: Uses two voltage levels (VIL, VIH) to

WP# INPUT WRITE PROTECT: Controls the lock-down function of the flexible

V

CC

INPUT

SUPPLY DEVICE POWER SUPPLY: [2.7 V–3.6 V] Supplies power for device

ADDRESS INPUTS for memory addresses. Addresses are internally

latched during a program or erase cycle.

8-Mbit x 8 A[0-19], 16-Mbit x 8 A[0-20], 32-Mbit x 8 A[0-21]

8-Mbit x 16 A[0-18], 16-Mbit x 16 A[0-19], 32-Mbit x 16 A[0-20]

WE# cycle during a Program command. Inputs commands to the

Command User Interface when CE# and WE# are active. Data is

internally latched. Outputs array, configuration and status register data.

The data pins float to tri-state when the chip is de-selected or the outputs

are disabled.

WE# cycle during a Program command. Data is internally latched.

Outputs array and configuration data. The data pins float to tri-state when

the chip is de-selected. Not included on x8 products.

decoders and sense amplifiers. CE# is active low. CE# high de-selects

the memory device and reduces power consumption to standby levels.

buffers during a read operation. OE# is active low.

memory array. WE# is active low. Addresses and data are latched on

the rising edge of the second WE# pulse.

control reset/deep power-down mode.

When RP# is at logic low, the device is in reset/deep power-down

mode, which drives the outputs to High-Z, resets the Write State

Machine, and minimizes current levels (I

When RP# is at logic high, the device is in standard operation.

When RP# transitions from logic-low to logic-high, the device resets all

blocks to locked and defaults to the read array mode.

Locking feature

When WP# is a logic low, the lock-down mechanism is enabled and

blocks marked lock-down cannot be unlocked through software.

When WP# is logic high, the lock-down mechanism is disabled and

blocks previously locked-down are now locked and can be unlocked and

locked through software. After WP# goes low, any blocks previously

marked lock-down revert to that state.

See Section 3.3 for details on block locking.

operations.

CCD

).

PRODUCT PREVIEW

9

3 VOLT ADVANCED+ BOOT BLOCK E

PP

Table 2. 3 Volt Advanced+ Boot Block Pin Descriptions (Continued)

Symbol Type Name and Function

V

CCQ

V

PP

GND SUPPLY GROUND: For all internal circuitry. All ground inputs must be

NC NO CONNECT: Pin may be driven or left floating.

INPUT I/O POWER SUPPLY: Supplies power for input/output buffers.

[2.7 V–3.6 V] This input should be tied directly to V

CC

.

[1.65 V– 2.5 V] Lower I/O power supply voltage available upon request.

Contact your Intel representative for more information.

INPUT/

SUPPLY

PROGRAM/ERASE POWER SUPPLY: [1.65 V–3.6 V or 11.4 V–12.6 V]

Operates as a input at logic levels to control complete device protection.

Supplies power for accelerated program and erase operations in 12 V ±

5% range. This pin cannot be left floating.

Lower V

PP

≤ V

, to protect all contents against Program and

PPLK

Erase commands.

= VCC for in-system read, program and erase operations. In

Set V

PP

this configuration, V

diode drop from the system supply. Note that if V

signal, V

1.65. That is, V

IH =

can drop as low as 1.65 V to allow for resistor or

is driven by a logic

must remain above 1.65V to perform in-

PP

PP

system flash modifications.

Raise V

environment. Applying 12 V ± 5% to V

to 12 V ± 5% for faster program and erase in a production

PP

can only be done for a

PP

maximum of 1000 cycles on the main blocks and 2500 cycles on the

parameter blocks.

maximum. See Section 3.4 for details on V

VPP may be connected to 12 V for a total of 80 hours

voltage configurations.

PP

connected.

2.2 Block Organization

The 3 Volt Advanced+ Boot Block is an

asymmetrically-blocked architecture that enables

system integration of code and data within a single

flash device. Each block can be erased

independently of the others up to 100,000 times.

For the address locations of each block, see the

memory maps in Appendix E and F.

10

2.2.1 PARAMETER BLOCKS

The 3 Volt Advanced+ Boot Block flash memory

architecture includes parameter blocks to facilitate

storage of frequently updated small parameters

(i.e., data that would normally be stored in an

EEPROM). Each device contains eight parameter

blocks of 8-Kbytes/4-Kwords (8,192 bytes/4,096

words).

2.2.2 MAIN BLOCKS

After the parameter blocks, the remainder of the

array is divided into equal size (64-Kword/32Kword; 65,536 bytes/32,768 words ) main blocks for

data or code storage. Each 8-Mbit, 16-Mbit, or

32-Mbit device contains 15, 31, or 63 main blocks,

respectively.

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

3.0 PRINCIPLES OF OPERATION

The 3 Volt Advanced+ Boot Block flash memory

family utilizes a CUI and automated algorithms to

simplify program and erase operations. The CUI

allows for 100% CMOS

fixed power supplies during erasure and

programming.

-

level control inputs and

the V

command must be issued t o the CUI to enter the

corresponding mode. Upon initial dev ice power

or after exit from reset, the device automatically

defaults to read array mode.

CE# and OE# must be driven active to obtain dat a

at the outputs. CE# is the device s election control;

voltage. The appropriate read mode

PP

when active it enables the flash memory device.

The internal WSM completely automates program

and erase operations while the CUI si gnals the s tart

of an operation and the status register reports

status. The CUI handles t he WE# interface to the

OE# is the data output control and it drives the

selected memory data ont o the I/ O bus . For all read

modes, WE# and RP# must be at V

illustrates a read cycle.

data and address latches, as well as system status

requests during WSM operation.

3.1 Bus Operation

The 3 Volt Advanced+ Boot Block flash memory

devices read, program and erase in

local CPU or microcontroller. All bus cycles to or

from the flash memory conform to standard

microcontroller bus cycles. Four control pins dictate

the data flow in and out of the flash component:

CE#, OE#, WE# and RP#. These bus operations

are summarized in Table 3.

-

system via the

3.1.2 OUTPUT DISABLE

With OE# at a logic

outputs are disabled. Output pins are placed in a

high

-

impedance state.

3.1.3 STANDBY

Deselecting the device by bri nging CE# to a logic

high level (VIH) places the device in standby mode,

which substantially reduces device power

consumption without any latency for subsequent

read accesses. In standby, outputs are placed in a

3.1.1 READ

The flash memory has four read modes available:

read array, read configuration, read s tatus and read

high-impedance state independent of OE#. If

deselected during program or erase operat ion, the

device continues to c onsume active power unt il the

program or erase operation is complete.

query. These modes are accessi ble independent of

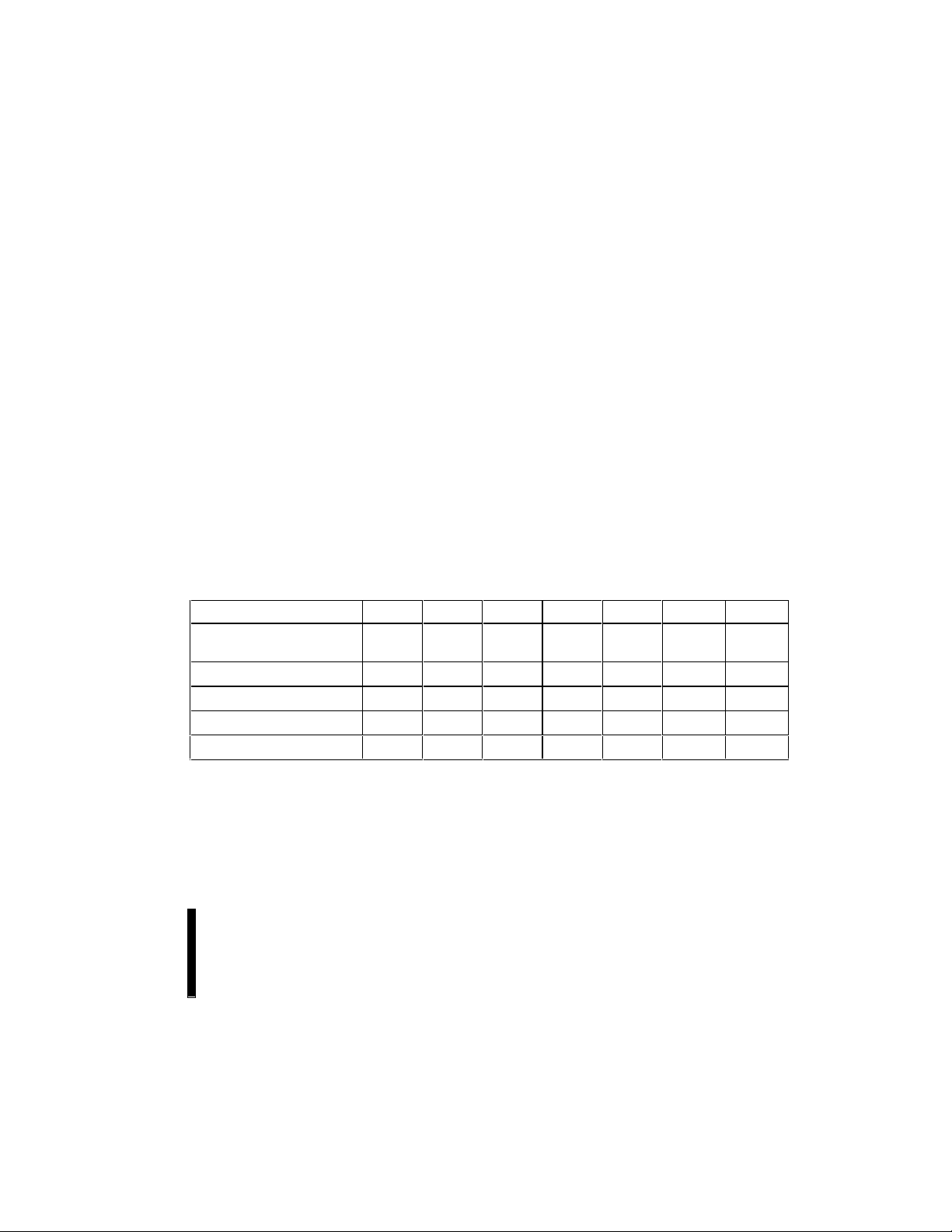

Table 3. Bus Operations

(1)

Mode Note RP# CE# OE# WE# DQ

Read (Array, Status,

Configuration, or Query)

Output Disable 2 V

Standby 2 V

Reset 2,7 V

Write 2,5-7 V

NOTES:

1. 8-bit devices use only DQ[0:7], 16-bit devices use DQ[0:15]

2. X must be V

3. See

4. Manufacturer and device codes may also be accessed in read configuration mode (A

5. Refer to Table 5 for valid D

6. To program or erase the lockable blocks, hold WP# at V

7. RP# must be at GND ± 0.2 V to meet the maximum deep power-down current specified.

, VIH for control pins and addresses.

IL

DC Characteristics

for V

2-4 V

, V

, V

PP1

PP2

, V

PPLK

during a write operation.

IN

IH

IH

IH

IL

IH

, voltages.

PP3

V

IL

V

IL

V

IH

V

IL

V

IH

X X High Z High Z

X X X High Z High Z

V

IL

.

IH

V

IH

1–A20

. Figure 9

IH

-

high level (VIH), the device

DQ

8-15

D

OUT

D

IN

V

IH

V

IH

V

IL

D

High Z High Z

D

= 0). See Table 4.

0–7

OUT

IN

-

up

-

PRODUCT PREVIEW

11

3 VOLT ADVANCED+ BOOT BLOCK E

3.1.4 RESET

From read mode, RP# at V

for time t

IL

PLPH

deselects the memory, places output drivers in a

high

-

impedance state, and turns off all internal

circuits. After return from reset, a time t

PHQV

is

required until the initial read access outputs are

valid. A delay (t

PHWL

or t

) is required after

PHEL

return from reset before a write can be initiated.

After this wake

-

up interval, normal operation is

restored. The CUI resets t o read array mode, and

the status register i s s et t o 80H. This cas e is shown

in Figure 11A.

If RP# is taken low for time t

during a program

PLPH

or erase operation, the operation will be aborted

and the memory contents at the aborted location

(for a program) or block (for an erase) are no longer

valid, since the data may be partially erased or

written. The abort process goes through the

following sequence: When RP# goes low, the

device shuts down the operation in progress, a

process which takes time t

this time t

, the part will either reset to read

PLRH

array mode (if RP# has gone high during t

to complete. After

PLRH

PLRH

Figure 11B) or enter reset mode (if RP# is still logic

low after t

, Figure 11C). In both cases, after

PLRH

returning from an aborted operation, the relevant

time t

PHQV

or t

PHWL/tPHEL

must be waited bef ore a

read or write operation is initiat ed, as discussed in

the previous paragraph. However, in this case,

these delays are referenced to the end of t

PLRH

rather than when RP# goes high.

As with any automated device, it is important to

assert RP# during system reset. When the system

comes out of reset, proc essor expec ts to read from

the flash memory. Automated flash memories

provide status information when read during

program or block erase operations. If a CPU reset

occurs with no flash memory reset, proper CPU

initialization may not occur because the flash

memory may be providing status information

instead of array data. Int el’s flash memories allow

proper CPU initialization following a system reset

through the use of the RP# input. In this application,

RP# is controlled by the same RESET# signal that

resets the system CPU.

addressable memory location. The address and

data buses are latched on the rising edge of the

second WE# or CE# pulse, whichever occ urs first.

Figure 10 illustrates a program and erase operation.

The available commands are shown in Tabl e 6, and

Appendix A provides detailed information on

moving between the different modes of operation

using CUI commands.

There are two commands that modify array data:

Program (40H) and Erase (20H). Writing either of

these commands to the internal Command User

Interface (CUI) initiates a sequence of internally

timed functions that culminate in the c ompletion of

the requested task (unless that operat ion is aborted

by either RP# being driven to V

for t

IL

appropriate suspend command).

3.2 Modes of Operation

The flash memory has four read modes and two

write modes. The read modes are read array, read

configuration, read status, and read query. The

,

write modes are program and block erase. Three

additional modes (erase suspend to program, eras e

suspend to read and program suspend to read) are

available only during suspended operations. These

modes are reached using the commands

summarized in Tables 5 and 6. A comprehensive

chart showing the state transitions is in Appendix A.

3.2.1 READ ARRAY

When RP# transitions from V

device defaults to read array mode and will res pond

to the read control inputs (CE #, address i nputs , and

OE#) without any additional CUI commands.

When the device is in read array mode, four control

signals control data output:

• WE# must be logic high (V

• CE# must be logic low (V

• OE# must be logic low (V

• RP# must be logic high (V

(reset) to VIH, the

IL

)

IH

)

IL

)

IL

)

IH

PLRH

or an

-

3.1.5 WRITE

A write takes place when bot h CE# and WE# are

low and OE# is high. Commands are written to the

Command User Interface (CUI) using standard

microprocessor write timings to control flash

operations. The CUI does not occupy an

12

In addition, the address of the desired l ocat ion mus t

be applied to the address pins. If the dev ice is not

in read array mode, as would be t he case after a

program or erase operation, the Read Array

command (FFH) must be written to the CUI before

array reads can take place.

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

3.2.2 READ CONFIGURATION

The Read Configuration mode outputs the

manufacturer/device identifier. The device is

switched to this mode by writing the Read

Configuration command (90H). Once i n this mode,

read cycles from addresses shown in Table 4

retrieve the specified i nformation. To return to read

array mode, write the Read Array command (FFH).

The Read Configuration mode outputs three types

of information: the manufacturer/device identifier,

the block locking status , and the protec tion regis ter.

The device is switched to this mode by writ ing the

Read Configuration command (90H). Once in this

mode, read cycles from addresses shown in Table

4 retrieve the specified information. To return to

read array mode, write the Read Array command

(FFH).

Table 4. Read Configuration Table

Item Address Data

Manufacturer Code (x16) 00000 0089

Manufacturer Code (x8) 00000 89

Device ID (See Appendix G) 00001 ID

Block Lock Configuration

• Block Is Unlocked DQ0 = 0

• Block Is Locked DQ0 = 1

• Block Is Locked-Down DQ1 = 1

Protection Register Lock

Protection Register (x16) 81-88 PR

Protection Register (x8) (App. H) PR

NOTES:

1. “XX” specifies the block address of lock configuration

being read.

2. See Section 3.3.4 for valid lock status outputs.

3. See Section 3.4 for protection register information.

4. Other locations within the configuration address space

are reserved by Intel for future use.

3.2.3 READ STATUS REGISTER

The status register indicates the status of device

operations, and the success/failure of that

operation. The Read Status Register (70H)

2

3

(1)

XX002

80 PR-LK

LOCK

command causes subsequent reads to output data

from the status register until another command is

issued. To return to reading from t he array, issue a

Read Array (FFH) command.

The status register bits are output on DQ

The upper byte, DQ

Read Status Register command.

The contents of the st atus register are latched on

the falling edge of OE# or CE#, whichever oc curs

last. This prevents possible bus errors which might

occur if status regi ster content s change while being

read. CE# or OE# must be toggled with each

subsequent status read, or the status register will

not indicate completion of a program or erase

operation.

When the WSM is active, SR.7 will indicate the

status of the WSM; t he remaining bits in the st atus

register indicate whether the WSM was successful

in performing the desired operation (see Table 7).

3.2.3.1 Clearing the Status Register

The WSM sets status bits 1 through 7 to “1,” and

clears bits 2, 6 and 7 to “0, ” but cannot clear status

bits 1 or 3 through 5 to “0.” Becaus e bits 1, 3, 4 and

5 indicate various error conditions, these bits can

only be cleared through the use of the Clear Status

Register (50H) command. By allowing the system

software to control the resetting of these bits,

several operations may be performed (such as

cumulatively programming several addresses or

erasing multiple blocks in sequence) before reading

the status register t o determine if an error occurred

during that series. Clear the St atus Register before

beginning another command or sequence. Note

that the Read Array command must be issued

before data can be read from the memory array.

Resetting the device also clears the status register.

3.2.4 READ QUERY

The Read Query mode outputs Common Flash

Interface (CFI) data when the devi ce is read. This

can be accessed by writing the Read Query

Command (98H). The CFI data structure contains

information such as bloc k size, density, c ommand

set and electrical specificat ions. Once i n this mode,

read cycles from addresses shown in Appendi x C

retrieve the specified i nformation. To return to read

array mode, write the Read Array command (FFH).

–DQ15, outputs 00H during a

8

–DQ7.

0

PRODUCT PREVIEW

13

3 VOLT ADVANCED+ BOOT BLOCK E

3.2.5 PROGRAM MODE

-

Programming is executed using a two

write

sequence. The Program Setup command (40H) is

written to the CUI foll owed by a sec ond write which

specifies the address and data to be programmed.

The WSM will execute a sequence of internally

timed events to program desired bits of the

addressed location, then verify the bits are

sufficiently programmed. Programming the memory

results in specific bits within an address location

being changed to a “0.” If the user attempts to

program “1”s, the memory cell contents do not

change and no error occurs.

The status register indicates programming status:

while the program sequence execut es, status bit 7

is “0.” The status regis ter can be poll ed by toggling

either CE# or OE#. While programming, the only

valid commands are Read Status Register,

Program Suspend, and Program Resume.

When programming is complete, the Program

Status bits shoul d be checked. If the programming

operation was unsuccessf ul, bit SR.4 of the status

register is set to indi cate a program f ailure. If S R.3

is set then V

was not within acceptable l i m i ts, and

PP

the WSM did not execute t he program command. If

SR.1 is set, a program operation was att empted on

a locked block and the operation was aborted.

The status register should be cleared before

attempting the next operat ion. Any CUI instruction

can follow after programming is completed;

however, to prevent inadvertent status register

reads, be sure to reset the CUI to read array mode.

3.2.5.1 Suspending and Resuming

Program

The Program Suspend command halts an in

progress program operation so that data can be

read from other locations of memory. Once the

programming process starts, writing the Program

Suspend command to the CUI requests that the

WSM suspend the program sequence (at

predetermined points in the program algorithm).

The device continues to output status register data

after the Program Suspend command is written.

Polling status register bits SR.7 and SR.2 will

determine when the program operation has been

suspended (both will be set to “1”). t

WHRH1/tEHRH1

specify the program suspend latency.

A Read Array command can now be writt en to the

CUI to read data from blocks other than that which

is suspended. The only other valid commands,

while program is suspended, are Read Status

Register, Read Configuration, Read Query, and

Program Resume. After the Program Resume

command is written to t he flash memory, the WSM

will continue with the programming process and

status register bits SR.2 and S R.7 will aut omatic ally

be cleared. The device automatically outputs s tatus

register data when read (see Figure 13 in Appendix

B,

Program Suspend/Resume Flowchart

Program Resume command is written. V

remain at the same V

level used for program

PP

while in program suspend mode. RP# must also

remain at V

.

IH

3.2.6 ERASE MODE

To erase a block, write the Erase Set

Confirm commands to the CUI, along with an

address identifying the block to be erased. This

address is latched internally when the Erase

Confirm command is iss ued. Block erasure results

in all bits within the block being s et to “1.” Only one

block can be erased at a time. The WSM will

execute a sequence of internally timed events to

program all bits within the block to “0, ” erase all bit s

within the block to “1,” t hen verify t hat all bits within

the block are sufficiently erased. While the erase

executes, status bit 7 is a “0.”

When the status register indicates that erasure is

complete, check the erase status bit to verify that

the erase operation was successful. If the Erase

operation was unsuccessful, SR.5 of the status

register will be set to a “1,” indicating an erase

failure. If V

the Erase Confirm command was issued, t he WSM

will not execute the erase sequence; instead, SR.5

-

of the status register is set to indicate an erase

was not within acceptable l imits after

PP

error, and SR.3 is set to a “1” t o identify that V

supply voltage was not within acceptable limits.

After an erase operation, clear the status register

(50H) before attempting the next operation. Any

CUI instruction can follow after erasure is

completed; however, to prevent inadvertent status

register reads, it is adv isable to place the flash in

read array mode after the erase is complete.

) after the

must

PP

-

up and Erase

PP

14

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

3.2.6.1 Suspending and Resuming Erase

Since an erase operation requires on the order of

seconds to complete, an Erase Suspend c ommand

is provided to allow erase

order to read data from or program data to another

block in memory. Once the erase sequence is

started, writing the Erase Suspend com mand to the

CUI suspends the erase sequence at a

predetermined point in the erase algorithm. The

status register will indicate if/when the erase

operation has been suspended. Erase suspend

latency is specified by t

Command Notes Oper Addr Data Oper Addr Data

Read Array 4 Write X FFH

Read Configuration 2, 4 Write X 90H Read IA ID

Read Query 2, 4 Write X 98H Read QA QD

Read Status Register 4 Write X 70H Read X SRD

Clear Status Register 4 Write X 50H

Program 3,4 Write X 40H/10H Write PA PD

Block Erase/Confirm 4 Write X 20H Write BA D0H

Program/Erase Suspend 4 Write X B0H

Program/Erase Resume 4 Write X D0H

Lock Block 4 Write X 60H Write BA 01H

Unlock Block 4 Write X 60H Write BA D0H

Lock-Down Block 4 Write X 60H Write BA 2FH

Protection Program 4 Write X C0H Write PA PD

X = Don’t Care PA = Prog Addr BA = Block Addr IA = Identifier Addr. QA = Query Addr.

SRD = Status Reg. Data PD = Prog Data ID = Identifier Data QD = Query Data

NOTES:

1. Bus operations are defined in Table 3.

2. Following the Read Configuration or Read Query commands, read operations output device configuration or CFI query

information, respectively. See Section 3.2.2 and 3.2.4.

3. Either 40H or 10H command is valid, but the Intel standard is 40H.

4. When writing commands, the upper data bus [DQ

-

sequence interruption in

WHRH2/tEHRH2

.

Table 5. Command Bus Definitions

–DQ15] should be either VIL or VIH, to minimize current draw.

8

A Read Array/Program command can now be

written to the CUI to read/program data from/to

blocks other than that which is suspended. This

nested Program command can subsequently be

suspended to read yet another location. The only

valid commands while erase is suspended are

Read Status Register, Read Configuration, Read

Query, Program Setup, Program Resume, Erase

Resume, Lock Bloc k, Unlock Block and Lock -Down

Block. During erase suspend mode, the c hip c an be

placed in a pseudo

V

. This reduces active current consumption.

IH

Erase Resume continues t he eras e s equenc e when

CE# = V

operation, the status register must be read and

cleared before the next instruction is issued.

First Bus Cycle Second Bus Cycle

. As with the end of a standard erase

IL

-

standby mode by taking CE# to

PRODUCT PREVIEW

15

3 VOLT ADVANCED+ BOOT BLOCK E

Table 6. Command Codes and Descriptions

Code Device Mode Description

FF Read Array Places device in read array mode, such that array data will be output on the

40 Program

Set-Up

20 Erase

Set-Up

D0 Erase Confirm

Program/Erase

Resume

Unlock Block

B0 Program

Suspend

Erase

Suspend

70 Read Status

Register

50 Clear Status

Register

90 Read

Configuration

60 Configuration

Set-Up

01 Lock-Block If the previous command was Configuration Set-Up, the CUI will latch the

data pins.

This is a two-cycle command. The first cycle prepares the CUI for a program

operation. The second cycle latches addresses and data information and

initiates the WSM to execute the Program algorithm. The flash outputs status

register data when CE# or OE# is toggled. A Read Array command is required

after programming to read array data. See Section 3.2.5.

Prepares the CUI for the Erase Confirm command. If the next command is not

an Erase Confirm command, then the CUI will (a) set both SR.4 and SR.5 of the

status register to a “1,” (b) place the device into the read status register mode,

and (c) wait for another command. See Section 3.2.6.

If the previous command was an Erase Set-Up command, then the CUI will

close the address and data latches, and begin erasing the block indicated on the

address pins. During program/erase, the device will respond only to the Read

Status Register, Program Suspend and Erase Suspend commands and will

output status register data when CE# or OE# is toggled.

If a program or erase operation was previously suspended, this command will

resume that operation.

If the previous command was Configuration Set-Up, the CUI will latch the

address and unlock the block indicated on the address pins. If the block had

been previously set to Lock-Down, this operation will have no effect. (Sect. 3.3)

Issuing this command will begin to suspend the currently executing

program/erase operation. The status register will indicate when the operation

has been successfully suspended by setting either the program suspend (SR.2)

or erase suspend (SR.6) and the WSM Status bit (SR.7) to a “1” (ready). The

WSM will continue to idle in the SUSPEND state, regardless of the state of all

input control pins except RP#, which will immediately shut down the WSM and

the remainder of the chip if RP# is driven to V

3.2.6.1.

This command places the device into read status register mode. Reading the

device will output the contents of the status register, regardless of the address

presented to the device. The device automatically enters this mode after a

program or erase operation has been initiated. See Section 3.2.3.

The WSM can set the Block Lock Status (SR.1) , VPP Status (SR.3), Program

Status (SR.4), and Erase Status (SR.5) bits in the status register to “1,” but it

cannot clear them to “0.” Issuing this command clears those bits to “0.”

Puts the device into the Read Configuration mode, so that reading the device

will output the manufacturer/device codes or block lock status. Section 3.2.2.

Prepares the CUI for changes to the device configuration, such as block locking

changes. If the next command is not Block Unlock, Block Lock, or Block LockDown, then the CUI will set both the Program and Erase Status register bits to

indicate a command sequence error. See Section 3.3.

address and lock the block indicated on the address pins. (Section 3.3)

. See Sections 3.2.5.1 and

IL

16

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

Table 6. Command Codes and Descriptions (Continued)

Code Device Mode Description

2F Lock-Down If the previous command was a Configuration Set-Up command, the CUI will

98 Read

Query

C0 Protection

Program

Setup

10 Alt. Prog Set-Up Operates the same as Program Set-up command. (See 40H/Program Set-Up)

00 Invalid/

Reserved

NOTE:

See Appendix A for mode transition information.

latch the address and lock-down the block indicated on the address pins.

(Section 3.3)

Puts the device into the Read Query mode, so that reading the device will

output Common Flash Interface information. See Section 3.2.4 and Appendix C.

This is a two-cycle command. The first cycle prepares the CUI for an program

operation to the Protection Register. The second cycle latches addresses and

data information and initiates the WSM to execute the Protection Program

algorithm to the Protection Register. The flash outputs status register data when

CE# or OE# is toggled. A Read Array command is required after programming

to read array data. See Section 3.4.

Unassigned commands that should not be used. Intel reserves the right to

redefine these codes for future functions.

PRODUCT PREVIEW

17

3 VOLT ADVANCED+ BOOT BLOCK E

PP

level. The WSM interrogates V

is also checked before the

and V

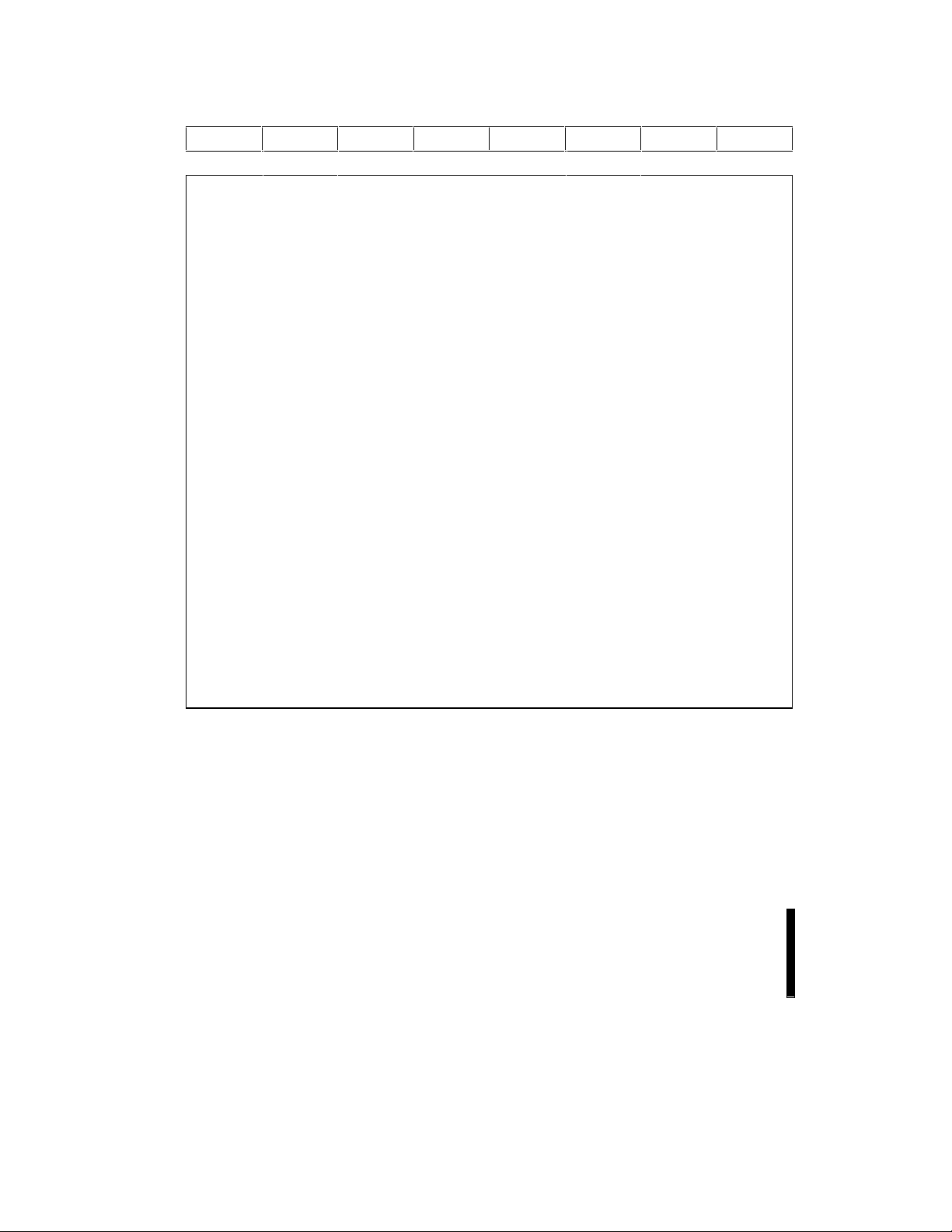

Table 7. Status Register Bit Definition

WSMS ESS ES PS VPPS PSS BLS R

76543210

NOTES:

SR.7 WRITE STATE MACHINE STATUS

1 = Ready (WSMS)

0 = Busy

SR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase In Progress/Completed

SR.5 = ERASE STATUS (ES)

1 = Error In Block Erase

0 = Successful Block Erase

SR.4 = PROGRAM STATUS (PS)

1 = Error in Programming

0 = Successful Programming

SR.3 = VPP STATUS (VPPS)

1 = V

0 = V

Low Detect, Operation Abort

PP

OK

PP

SR.2 = PROGRAM SUSPEND STATUS

(PSS)

1 = Program Suspended

0 = Program in Progress/Completed

SR.1 = BLOCK LOCK STATUS

1 = Prog/Erase attempted on a locked

block; Operation aborted.

0 = No operation to locked blocks

SR.0 = RESERVED FOR FUTURE

ENHANCEMENTS (R)

Check Write State Machine bit first to determine Word

Program or Block Erase completion, before checking

Program or Erase Status bits.

When Erase Suspend is issued, WSM halts execution

and sets both WSMS and ESS bits to “1.” ESS bit

remains set to “1” until an Erase Resume command is

issued.

When this bit is set to “1,” WSM has applied the max.

number of erase pulses to the block and is still unable to

verify successful block erasure.

When this bit is set to “1,” WSM has attempted but failed

to program a word/byte.

The V

of V

status bit does not provide continuous indication

PP

level only after

PP

the Program or Erase command sequences have been

entered, and informs the system if V

switched on. The V

PP

has not been

PP

operation is verified by the WSM. The VPPstatus bit is

not guaranteed to report accurate feedback between

V

PPLK

PP1

Min.

When Program Suspend is issued, WSM halts execution

and sets both WSMS and PSS bits to “1.” PSS bit

remains set to “1” until a Program Resume command is

issued.

If a program or erase operation is attempted to one of the

locked blocks, this bit is set by the WSM. The operation

specified is aborted and the device is returned to read

status mode.

This bit is reserved for future use and should be masked

out when polling the status register.

18

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

3.3 Flexible Block Locking

The Intel® 3 Volt Advanced+ Boot Block products

offer an instant, individual block locking scheme

that allows any block t o be locked or unlocked with

no latency, enabling instant code and data

protection.

This locking scheme offers t wo levels of protec tion.

The first level allows software-only control of bloc k

locking (useful for data blocks that change

frequently), while the second level requires

hardware interaction before locki ng can be changed

(useful for code blocks that change infrequently).

The following sections will discuss the operat ion of

the locking system. The term “state [XYZ]” will be

used to specify locking states; e.g., “state [001],”

where X = value of WP#, Y = bit DQ

Lock status regist er, and Z = bit DQ

Lock status register. Table 9 defines all of these

possible locking states.

3.3.1 LOCKING OPERATION

The following concisely summarizes the locking

functionality.

• All blocks power-up locked, then can be

unlocked or locked with the Unlock and Lock

commands.

• The Lock-Down command locks a block and

prevents it from being unlocked when WP# = 0.

When WP# = 1, Lock-Down is overridden

and commands can unlock/lock lockeddown blocks.

When WP# returns to 0, locked-down

blocks return to Lock-Down.

Lock-Down is cleared only when t he device

is reset or powered-down.

The locking status of each block can s et t o Loc ked,

Unlocked, and Lock-Down, each of which will be

described in the following sections. A

comprehensive state table f or the locking functions

is shown in Table 9, and a flowchart for locking

operations is shown in Figure 16.

of the Block

1

of the Block

0

3.3.2 LOCKED STATE

The default status of all blocks upon power-up or

reset is locked (states [001] or [101]). Locked

blocks are fully protected from alteration. Any

program or erase operations attempted on a l ocked

block will return an error on bit SR.1 of the status

register. The status of a locked block can be

changed to Unlocked or Lock-Down using the

appropriate software commands. An Unlocked

block can be locked by wri ting the Lock command

sequence, 60H followed by 01H.

3.3.3 UNLOCKED STATE

Unlocked blocks (states [000], [100], [110]) can be

programmed or erased. All unlocked blocks return

to the Locked state when the device is reset or

powered down. The status of an unlocked block can

be changed to Locked or Locked-Down using the

appropriate software commands. A Locked block

can be unlocked by writing the Unlock command

sequence, 60H followed by D0H.

3.3.4 LOCK-DOWN STATE

Blocks that are Locked-Down (state [011]) are

protected from program and erase operations (just

like Locked blocks), but their protection status

cannot be changed using software commands

alone. A Locked or Unlocked bloc k can be Lock eddown by writing the Lock-Down command

sequence, 60H followed by 2FH. Locked-Down

blocks revert to the Locked state when the device is

reset or powered down.

The Lock-Down function is dependent on the WP#

input pin. When WP# = 0, blocks in Lock-Down

[011] are protected from program, erase, and loc k

status changes. When WP# = 1, the Lock-Down

function is disabled ([ 111]) and locked-down blocks

can be individually unlock ed by soft ware command

to the [110] state, where they can be erased and

programmed. These blocks can then be relocked

[111] and unlocked [110] as desired while WP#

remains high. When WP# goes low, blocks that

were previously locked-down return to the

Lock-Down state [011] regardless of any changes

made while WP# was high. Device reset or powerdown resets all blocks, including those in LockDown, to Locked state.

PRODUCT PREVIEW

19

3 VOLT ADVANCED+ BOOT BLOCK E

3.3.5 READING A BLOCK’S LOCK STATUS

The lock status of ev ery block can be read in the

Configuration Read mode of the device. To enter

this mode, write 90H to the device. Subsequent

reads at Block Address + 00002 will out put the lock

status of that block . The lock status is represented

by the lowest two output pins , DQ

and DQ1. DQ

0

indicates the Block Lock/Unlock status and is set by

the Lock command and cleared by the Unlock

command. It is also automat ical ly set when entering

Lock-Down. DQ

indicates Lock-Down status and i s

1

set by the Lock-Down command. It cannot be

cleared by software, only by devic e reset or powerdown.

Table 8. Block Lock Status

Item Address Data

Block Lock Configuration XX002 LOCK

• Block Is Unlocked DQ0 = 0

• Block Is Locked DQ0 = 1

• Block Is Locked-Down DQ1 = 1

3.3.6 LOCKING OPERATIONS DURING

ERASE SUSPEND

Changes to block lock status can be performed

during an erase suspend by using the standard

locking command sequences to unlock, lock, or

lock-down a block. This i s useful in the c ase when

another block needs to be updated while an erase

operation is in progress.

the lock status will be changed. After completing

any desired lock, read, or program operations,

resume the erase operation with the Eras e Resume

command (D0H).

If a block is locked or locked-down during a

suspended erase of the same block, the locking

status bits will be changed immediat ely, but when

0

the erase is resumed, the erase operation will

complete.

Locking operations cannot be performed during a

program suspend. Refer to Appendix A for detailed

information on which commands are valid during

erase suspend.

3.3.7 STATUS REGISTER ERROR CHECKING

Using nested locking or program command

sequences during erase suspend can introduce

ambiguity into status register results.

Since locking changes are perf ormed using a two

cycle command sequence, e.g., 60H followed by

01H to lock a block, following the Configuration

Setup command (60H) with an invalid comm and will

produce a lock command error (SR. 4 and SR.5 wi ll

be set to 1) in the status register. If a lock

command error occurs during an erase suspend,

SR.4 and SR.5 will be set to 1, and will remain at 1

after the erase is resumed. When erase is

complete, any possible error during the erase

cannot be detected via the s tatus register becaus e

of the previous locking command error.

To change block locking during an erase operation,

first write the erase s uspend command (B0H), then

check the status register until it indicates that the

erase operation has been suspended. Next write

the desired lock command sequence t o a block and

20

A similar situation happens if an error occ urs during

a program operation error nested within an erase

suspend.

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

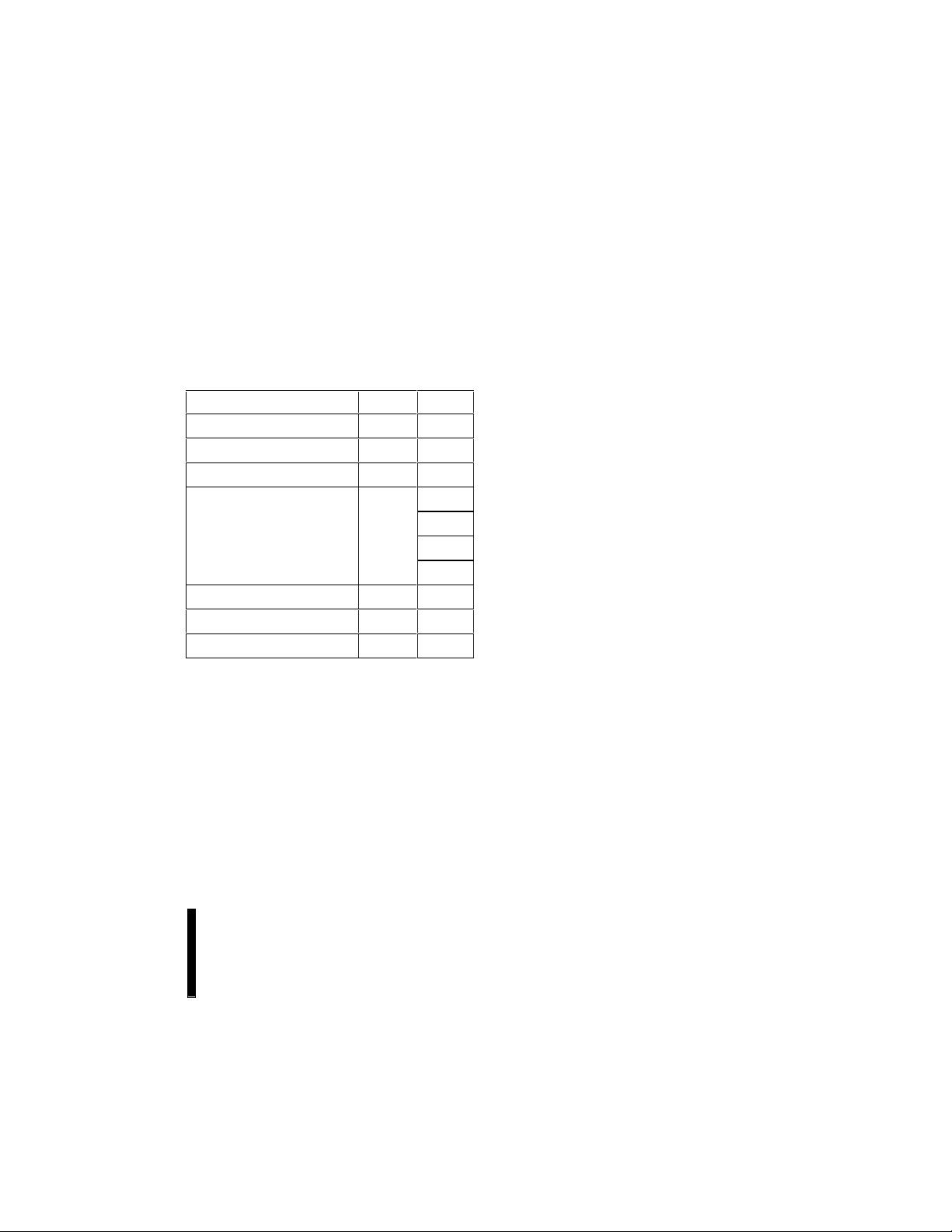

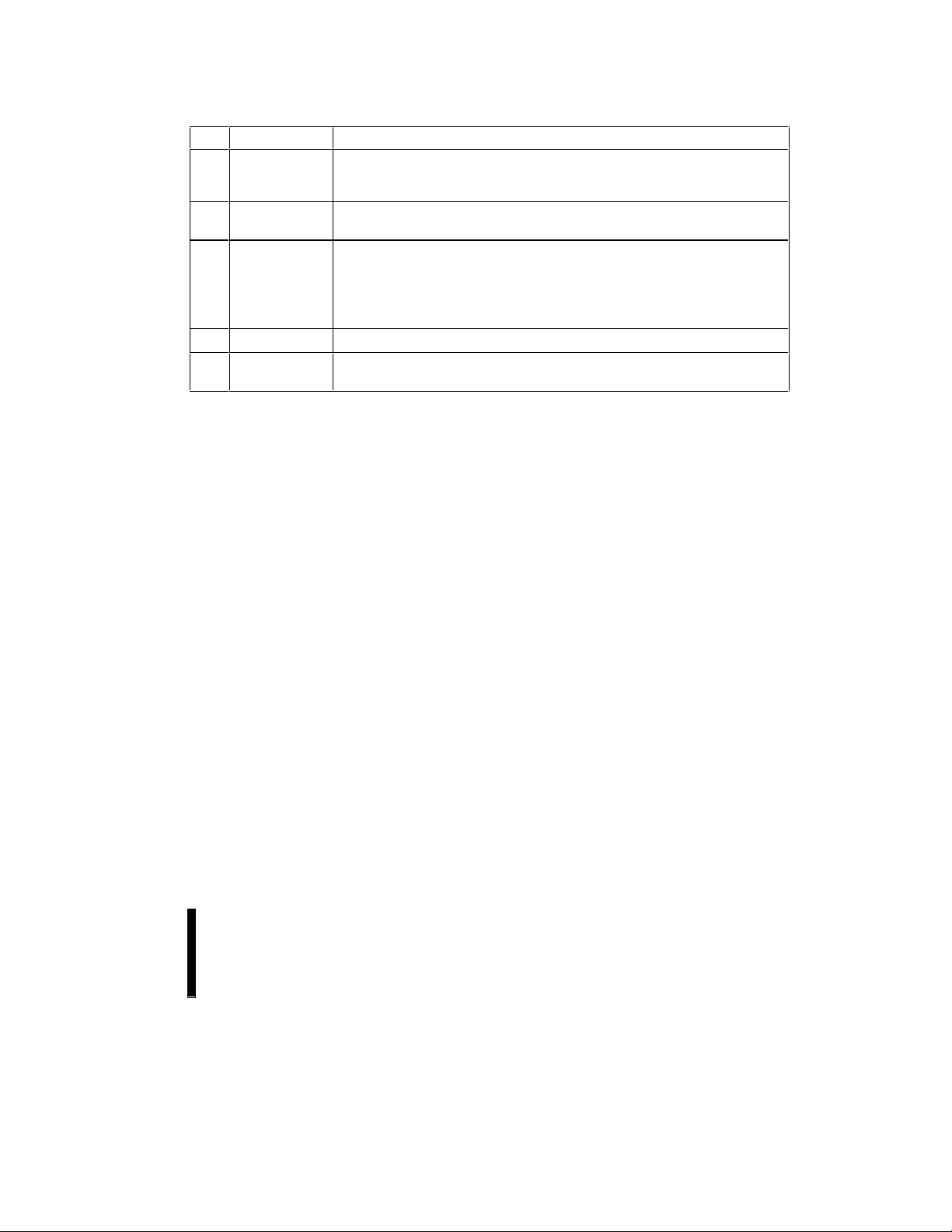

Table 9. Block Locking State Transitions

Current State Erase/Prog Lock Command Input Result [Next State]

WP# DQ1DQ

000 “Unlocked” Yes Goes To [001] No Change Goes To [011]

0 0 1 “Locked” (Default) No No Change Goes To [000] Goes To [011]

0 1 1 “Locked-Down” No No Change No Change No Change

1 0 0 “Unlocked” Yes Goes To [101] No Change Goes To [111]

1 0 1 “Locked” No No Change Goes To [100] Goes To [111]

1 1 0 Lock-Down Disabled Yes Goes To [111] No Change Goes To [111]

1 1 1 Lock-Down Disabled No No Change Goes To [110] No Change

NOTES:

1. In this table, the notation [XYZ] denotes the locking state of a block, where X = WP#, Y = DQ

locking state of a block is defined by the state of WP# and the two bits of the block lock status (DQ

a block is locked (1) or unlocked (0). DQ

2. At power-up or device reset, all blocks default to Locked state [001] (if WP# = 0). Holding WP# = 0 is the recommended

default.

3. The “Erase/Program Allowed?” column shows whether erase and program operations are enabled (Yes) or disabled (No)

in that block’s current locking state.

4. The “Lock Command Input Result [Next State]” column shows the result of writing the three locking commands (Lock,

Unlock, Lock-Down) in the current locking state. For example, “Goes To [001]” would mean that writing the command to a

block in the current locking state would change it to [001].

0

Name Allowed? Lock Unlock Lock-Down

, and Z = DQ0. The current

1

, DQ1). DQ0 indicates if

indicates if a block has been locked-down (1) or not (0).

1

0

3.4 128-Bit Protection Register

The Advanced+ Boot Block arc hitecture includes a

128-bit protection register than can be used to

increase the security of a system design. For

example, the number contained in the protection

register can be used to “mate” the f lash component

with other system com ponents such as the CPU or

ASIC, preventing device substitution. Additional

application information can be found in Intel

application note

Advanced+ Boot Block Flash Memory Architecture

The 128-bits of the protection register are divided

into two 64-bit segments. One of the segments is

programmed at the Intel fact ory wit h a unique 64-bit

number, which is unchangeable. The other segment

is left blank for customer designs to program as

desired. Once the customer segment is

programmed, it can be locked to prevent

reprogramming.

AP-657 Designing with the

PRODUCT PREVIEW

3.4.1 READING THE PROTECTION

The protection register is read in the conf iguration

read mode. The device is switc hed to this mode by

writing the Read Configuration command (90H).

Once in this mode, read cycles from addresses

shown in Appendix H retrieve the specified

information. To return to read array mode, write t he

Read Array command (FFH).

.

3.4.2 PROGRAMMING THE PROTECTION

The protection register bits are programmed us ing

the two-cycle Protection Program command. The

64-bit number is programmed 16 bits at a time for

word-wide parts and eight bits at a time for bytewide parts. First write t he Prot ect ion Program Set up

command, C0H. The next write to the device will

latch in address and data and program the specified

location. The allowable addresses are shown in

Appendix H. See Figure 17 for the

Register Programming Flowchart

REGISTER

REGISTER

.

Protection

21

3 VOLT ADVANCED+ BOOT BLOCK E

Any attempt to address Protection Program

commands outside the defined protection register

address space will result in a Stat us Register error

(Program Error bit SR.4 will be set to 1). Attempting

to program or to a previously locked protection

register segment will result in a status register error

(program error bit SR.4 and lock error bit SR.1 will

be set to 1).

3.4.3 LOCKING THE PROTECTION

REGISTER

The user-programmable segment of the protection

register is lockable by programming Bit 1 of the

PR-LOCK location to 0. Bit 0 of this location is

programmed to 0 at the Intel factory to prot ect the

unique device number. This bit is set using the

Protection Program comm and to program “FFFD” to

the PR-LOCK location. Af ter these bits have been

programmed, no further changes can be made to

the values stored in the protection register.

Protection Program comm ands to a locked section

will result in a status register error (Program Error

bit SR.4 and Lock Error bit SR.1 will be set to 1).

Protection register lockout state is not reversible.

88H

4 Words

User Programmed

85H

84H

4 Words

Factory Programmed

81H

1 Word Lock

80H

0645_05

Figure 5. Protection Register Memory Map

3.5 VPP Program and Erase

Voltages

Intel’s 3 Volt Advanced+ Boot Block products

provide in-system writes plus a V

production programming and complete write

protection.

pin for 12 V

PP

3.5.1 EASY-12 V OPERATION FOR FAST

MANUFACTURING PROGRAMMING

Intel’s 3 Volt Advanced+ Boot Block products

provide in-system programming and erase in the

2.7 V–3.6 V range. For fast production

programming, 3 Volt Advanced+ Boot Block

includes a low-cost, backward-compatible 12 V

programming feature.

When V

and erase current is drawn through the V

Note that if V

V

IH =

is between 1.65 V and 3.6 V, all program

PP

is driven by a logic signal,

1.65 V. That is, V

PP

must remain above 1.65 V

PP

CC

pin.

to perform in-system flash modifications. When V

is connected to a 12 V power supply, the device

draws program and erase current directl y from the

V

pin. This eliminates the need for an external

PP

switching transistor to control the voltage V

PP

Figure 6 shows examples of how the flash power

supplies can be configured for various usage

models.

The 12 V V

mode enhances programming

PP

performance during the short period of time typically

found in manufacturing processes; however, it is

not intended for extended use. 12 V may be applied

to V

during program and erase operations for a

PP

maximum of 1000 cycles on the main blocks and

2500 cycles on the parameter blocks. V

may be

PP

connected to 12 V for a total of 80 hours max imum.

Stressing the devic e beyond these limits may cause

permanent damage.

3.5.2 V

≤ V

PP

PROTECTION

FOR COMPLETE

PPLK

In addition to the flexible block locking, the V

programming voltage can be held low for absolut e

hardware write protection of all blocks in the flash

device. When V

is below V

PP

, any program or

PPLK

erase operation will result in a error, prompt ing the

corresponding status register bit (SR.3) to be set.

3.5.3 V

The V

PP

USAGE

PP

pin is used for two funct i ons : Absolute data

protection and fast production programming.

When V

PP

≤ V

, then all program or erase

PPLK

operations to the device are inhibited, providing

absolute data protection.

PP

.

PP

22

PRODUCT PREVIEW

E 3 VOLT ADVANCED+ BOOT BLOCK

System Supply

12 V Supply

10 K

Ω

12 V Fast Programming

Complete Write Protection When V

System Supply

(Note 1)

12 V Supply

12 V Fast Programming

Full Array Protection Unavailable

NOTE:

1. A resistor can be used if the VCC supply can sink adequate current based on resistor value. See AP-657

the Advanced+ Boot Block Flash Memory Architecture

Figure 6. Example Power Supply Configurations

When V

manufacturing situations , the devi ce direct ly appli es

the high voltage to achieve faster program and

erase.

Designing for in-system writes to the flash memory

requires special consideration of power supply

traces by the printed circuit board designer.

Adequate power supply traces, and decoupling

capacitors placed adjacent to the component, will

decrease spikes and overshoots.

is raised to 12 V, such as in a

PP

V

CC

V

PP

≠ 12 V

PP

V

CC

V

PP

System Supply

Prot#

(Logic Signal)

Low-Voltage Programming Only

Logic Control of Complete Device Protection

System Supply

Low-Voltage Programming Only

Full Array Protection Unavailable

for details.

3.6.1 ACTIVE POWER (Program/Erase/Read)

With CE# at a logic

high level, the device is in the ac ti ve m ode. Refer t o

the DC Characteristic tables for I

Active power is the largest contributor to overall

system power consumption. Minimizing the active

current could have a profound effect on system

power consumption, especi ally for battery

devices.

V

CC

V

PP

V

CC

V

PP

-

low level and RP# at a logic

CC

0645_06

Designing with

current values.

-

operated

-

3.6 Power Consumption

Intel’s flash devices have a tiered approach to

power savings that can significantly reduce ov erall

system power consumption. The Automatic Power

Savings (APS) feature reduces power consumption

when the device is selec ted but idle. If the CE# is

deasserted, the flash enters its standby mode,

where current consumption is even lower. The

combination of these features can minimize

memory power consumption, and therefore, overall

system power consumption.

PRODUCT PREVIEW

3.6.2 AUTOMATIC POWER SAVINGS (APS)

-

Automatic Power Savings provides low

operation during read mode. After data is read from

the memory array and the address lines are

quiescent, APS circuitry places the device in a

mode where typical current is comparable to I

The flash stays in t his st atic s tate wi th outputs val id

until a new location is read.

3.6.3 STANDBY POWER

-

With CE# at a logic

read mode, the flash memory i s in standby mode,

which disables much of the device’s circuitry and

high level (VIH) and device in

power

CCS

23

.

3 VOLT ADVANCED+ BOOT BLOCK E

substantially reduces power consumption. Outputs

are placed in a high

-

impedance state independent

of the status of the OE# signal. I f CE# t ransiti ons to

a logic

-

high level during erase or program

operations, the device will continue to perform the

operation and consume corresponding act iv e power

until the operation is completed.

System engineers should anal yz e the breakdown of

standby time versus active time and quantify the

respective power consumption in each mode for

their specific application. This will provide a more

accurate measure of applic ation

-

specific power and

energy requirements.

3.6.4 DEEP POWER-DOWN MODE

The deep power-down mode is activated when

RP#

(GND ± 0.2 V). During read modes, RP#

= VIL

going low de-selects the memory and places the

outputs in a high impedance s tate. Recovery from

deep power-down requires a minimum time of t

for read operations and t

PHWL/tPHEL

PHQV

for write

operations.

During program or erase modes, RP# transi tioning

low will abort the in-progress operation. The

memory contents of the addres s being program med

or the block being erased are no longer vali d as the

data integrity has been comprom ised by the abort.

During deep power-down, all internal circuits are

switched to a low power savings mode (RP#

transitioning to V

or turning off power to the devic e

IL

clears the status register).

proper CPU/flash initialization following system

reset.

System designers must guard against spurious

writes when V

voltages are above V

CC

LKO

. Since

both WE# and CE# must be low for a command

write, driving either signal to V

will inhibit writ es to

IH

the device. The CUI architecture prov ides additi onal

protection since alterat ion of memory contents c an

only occur after successful completion of the twostep command sequences. The device is also

disabled until RP# is brought to V

, regardless of

IH

the state of its c ontrol inputs. By holding the devic e

in reset (RP# connected to system PowerGood)

during power-up/down, invalid bus conditi ons during

power-up can be masked, providing yet another

level of memory protection.

3.7.2 V

, VPP AND RP# TRANSITIONS

CC

The CUI latches commands as issued by system

software and is not altered by V

or CE#

PP

transitions or WSM actions. Its default state upon

power-up, after exit from reset mode or after V

transitions above V

(Lockout voltage), is read

LKO

CC

array mode.

After any program or block erase operation is

complete (even after V

V

), the CUI must be reset t o read array mode

PPLK

transitions down to

PP

via the Read Array command if access to the fl ash

memory array is desired.

3.8 Power Supply Decoupling

3.7 Power-Up/Down Operation