Intel Corporation GC80960RD, GC80960RP Datasheet

© INT EL CORPORATION, 1997 September, 1997 Order Number: 273001-002

ADVANCE INFORMATION

i960® RP/RD I/O PROCESSOR AT 3.3 VOLTS

• 33 MHz, 3.3 Volt Version (80960RP 33/3.3)

• 66 MHz, 3.3 Volt Version (80960RD 66 /3.3) - Clock Doubl ed 80960JF Core

• Complies with PCI Local Bus Spec if ication Revisio n 2.1

• 5 Volt PCI Signalling Environment

■ High Performance 80960JF Core

— Sustained One Ins truction/Clock

Execution

— 4 Kbyte Two-Way Set-Associati ve

Instruction Cache

— 2 Kbyte Direct-Mapped Data Cache

— Sixteen 32-Bit Global Registers

— Sixteen 32-Bit Local Registers

— Programmable Bus Widths:

8-, 16-, 32-Bit

— 1 Kbyte Internal Data RAM

— Local Regist er Cache

(Eight Available Stack Frames)

— Two 32-Bit On-Chip Timer Units

■ PCI-to-PCI Bridge Unit

— Primary and Secondary PCI Interfaces

— Two 64-Byte Posting Buff ers

— Delayed and Posted Transaction

Support

— Forwards Memory, I/O, Configuration

Commands from PCI Bus to PCI Bus

■ Two Address Translation Units

— Connects Local Bus to PCI Buses

— Inbound/Out bound Address Translation

Support

— Direct Outbound Addressing Support

■ Messaging Unit

— Four Message Registers

— Two Doorbell Register s

— Four Circul ar Q ueues

— 1004 Index Registers

■ Memory Controller

— 256 Mbytes of 32- or 36-Bit DRAM

— Interleaved or Non-Interleaved DRAM

— Fast Page-Mode DRAM Support

— Extended Data Out and Burst

— Extended Data Out DRAM Support

— Two Independent Banks for SRAM / ROM

/ Flash (16 Mbytes/Bank; 8- or 32-Bit)

■ DMA Controller

— Three Independent Channels

— PCI Memory Controller Interface

— 32-Bit Local Bus Addressing

— 64-Bit PCI Bus Addressi ng

— Independent Interface to Primary and

Secondary PCI Buses

— 132 Mbyte/sec Burst Tra nsfers to PCI

and Local Buses

— Direct Addre ssing to and from PCI

Buses

— Unaligned Tr ansfers Supported in

Hardware

— Two Channels Dedicated to Primary

PCI Bus

— One Channel Dedicat ed to Secondary

PCI Bus

■ I/O APIC Bus Interface Unit

— Multipr ocessor Interrupt Management

for Intel Architecture CPUs

(Pentium

®

and Pentium® Pro

Processors)

— Dynamic Interrupt Distribution

— Multiple I/ O Subsystem Support

■ I

2

C Bus Interface Unit

—Serial Bus

— Master/Slave Capabilities

— System Management Functions

■ Secondary PCI Arbitration Unit

— Supports Six Seco ndary PCI Devices

— Multi-priority Arbitration Algorithm

— External Arbitration Support Mode

■ Private PCI Device Support

■ SuperBGA* Package

— 352 Ball-Grid Array (HL-PBG A)

Information in this document is provided in connection with Intel products. No license, express or implied, by

estop pel or other wise, to an y intellec tual prope rty rights is granted by thi s docume nt. Except a s provided in

Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel

disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or

warra nt ies rel atin g to fitn ess fo r a par ticu lar pu rpo se, mer cha ntab ility , or infr ing eme nt of an y pate nt, co pyrig ht

or other intellectual property right. Intel products are not intended for use in medical, life saving, or life

sustainin g ap pl ic ations .

Intel may make changes to specifications and product descriptions at any time, without notice.

*Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel

literature, may be obtained from:

Intel C orporati on

P.O. Box 7 641

Mt. Prospect IL 60056-764

or call 1-800-548-4725

©INTEL CORPORATION, 1997

i960® Rx I/O P rocessor at 3.3 V

iii

1.0 ABOUT THIS DO CU ME NT ............. .... .... .... ........... .... .... .... ........... .... .... .... ........... .... .... .... ............... .... ......1

1.1 Solutions960

®

Program ...................................................................................................................... 1

1.2 Terminology ........................................................................................................................................ 1

1.3 Additional Information Sources ........................................................................................................... 1

2.0 FUNCTIONAL OVERVIE W ...... .... ........... .... .... ... .... .... ............ ... .... .... .... ........... .... .... .... .... ... ................ ... ... 2

2.1 Key Functional Units ...........................................................................................................................3

2.1.1 PCI-to-PCI Bridge Unit ............................................................................................................. 3

2.1.2 Private PCI Device Support .....................................................................................................3

2.1.3 DMA Controller ........................................................................................................................ 3

2.1.4 Address Translation Unit .......................................................................................................... 3

2.1.5 Messaging Unit ........................................................................................................................ 3

2.1.6 Memory Controller ...................................................................................................................3

2.1.7 I2C Bus Interface Unit .............................................................................................................. 3

2.1.8 I/O APIC Bus Interface Unit .....................................................................................................3

2.1.9 Secondary PCI Arbitration Unit ................................................................................................4

2.2 i960 Core Features (80960JF) ........................................................................................................... 4

2.2.1 Burst Bus ................................................................................................................................. 5

2.2.2 Timer Unit ................................................................................................................................ 5

2.2.3 Priority Interrupt Controller ....................................................................................................... 5

2.2.4 Faults and Debugging ..............................................................................................................5

2.2.5 On-Chip Cache and Data RAM ................................................................................................5

2.2.6 Local Register Cache ............................................................................................................... 5

2.2.7 Test Features ........................................................................................................................... 5

2.2.8 Memory-Mapped Control Registers .........................................................................................6

2.2.9 Instructions, Data Types and Memory Addressing Modes ......................................................6

3.0 PACKAGE INFORMATIO N ...... ........... .... .... .... ... ............ .... .... ... .... .... ........... .... .... .... .... ........... ............... ... 8

3.1 Package Int rod uc ti on ......... .... ... .... ............ ... .... .... ............ ... .... .... ........... .... .... .... ........... ............ .......... 8

3.1.1 Functional Signal Definitions .................................................................................................... 8

3.1.2 352-Lead HL-PBGA Package ................................................................................................21

3.2 Package The rm al Specification s ................. .... .... .... ........... .... .... .... ........... .... .... .... ........... .... ............31

3.2.1 Thermal Specifications ........................................................................................................... 31

3.2.1.1 Ambient Temperature ...............................................................................................31

3.2.1. 2 Case Te mpera tu re .... .... .... ... ............ .... .... ... ............ .... ... .... ............ .... ... .... ............ ... .31

3.2.1.3 Thermal Resistance ..................................................................................................31

3.2.2 Thermal Analysis ...................................................................................................................32

3.3 Sources for Heatsinks and Accessories ...........................................................................................33

4.0 ELECTRICAL SPECIFICATIONS ........................................................................................................... 34

4.1 Absolu te Max im um Ratin gs ... ... .... .... .... ........... .... .... .... .... ........... .... .... ... ............ .... .... ... ................... . 34

4.2 V

CC5

Pin Re quirements (V

DIFF

) ............ ....... .... ........ ........ ....... ........ ....... .... ........ ........ ....... ........ ....... . 34

4.3 Targeted DC Specifications ..............................................................................................................35

4.4 Targeted AC Specifications .............................................................................................................. 37

4.4.1 Relative Output Timings ......................................................................................................... 39

4.4.2 Memory Controller Relative Output Timings ..........................................................................39

4.4.3 Boundary Scan Test Signal Timings ......................................................................................42

4.4.4 APIC Bus Interface Signal Timings ........................................................................................42

4.4.5 I2C Interface Signal Timings ..................................................................................................43

4.5 AC Test Conditions ...........................................................................................................................44

4.6 AC Timing Waveforms ...................................................................................................................... 44

4.7 Memory Controller Output Timing Waveforms .................................................................................48

5.0 BUS FUNCTIONAL WAVEFORMS ........................................................................................................ 55

6.0 DEVICE IDENTIFICATION ON RESET ................................................................................................... 64

i960® Rx I/O Processor at 3.3 V

iv

FIGURES

Figure 1. i960

®

Rx I/O Processor at 3.3 V Functional Block Diagram ..........................................................2

Figure 2. 80960JF Core Block Diagram ........................................................................................................4

Figure 3. 352L HL-PBGA Package Diagram (Top and Side View) .............................................................21

Figure 4. 352L HL-PBGA Package Diagram (Bottom View) .......................................................................22

Figure 5. Thermocouple Attachment - No Heat Sink ..................................................................................31

Figure 6. Thermocouple Attachment - With Heat Sink ................................................................................31

Figure 7. VCC5 Current-Limiting Resistor ...................................................................................................34

Figure 8. AC Test Load ...............................................................................................................................44

Figure 9. S_CLK, TCLK Waveform .............................................................................................................44

Figure 10. T

OV

Output Delay Waveform .......................................................................................................45

Figure 11. T

OF

Output Float Waveform .........................................................................................................45

Figure 12. T

IS

and TIH Input Setup and Hold Waveform ...............................................................................46

Figure 13. T

LXL

and T

LXA

Relative Timings Waveform .................................................................................46

Figure 14. DT/R# and DEN# Timings Waveform ..........................................................................................47

Figure 15. I

2

C Interface Sig na l Tim i ng s ...... ... ............ .... ... .... ............ .... ... .... ............ ... .... .... ............ ... .... .......47

Figure 16. Fast Page-Mode Read Access, Non-Interleaved, 2,1,1,1 Wa it State, 32-Bit 80960 Local Bus ...48

Figure 17. Fast Page-Mode Write Access, Non-Interlea ved, 2,1,1,1 Wait States, 32-Bit 80960 Local Bus .49

Figure 18. FPM DRAM System Read Access, Interleaved, 2,0,0,0 Wait States ..........................................50

Figure 19. FPM DRAM System Write Access, Interleaved, 1,0,0,0 Wait States ...........................................51

Figure 20. EDO DRAM, Read Cycle .............................................................................................................52

Figure 21. EDO DRAM, Write Cycle .............................................................................................................52

Figure 22. BEDO DRAM , Rea d Cycle . ........... .... .... .... ........... .... .... .... ........... .... .... .... ........... .... .... .... ... ...........53

Figure 23. BEDO DRAM, Write Cycle ...........................................................................................................53

Figure 24. 32-Bit Bus, SRAM Read Accesses with 0 Wait States ................................................................54

Figure 25. 32-Bit Bus, SRAM Write Accesses with 0 Wait States ................................................................54

Figure 26. Non-Burst Read and Write Transactions without Wait States, 32-Bit 80960 Local Bus ..............55

Figure 27. Burst Read and Write Transactions without Wait States, 32-Bit 80960 Local Bus ......................56

Figure 28. Burst Write Transactions with 2,1,1,1 Wait States, 32-Bit 80960 Local Bus ................................57

Figure 29. Burst Read and Write Transactions without Wait States, 8-Bit 80960 Local Bus ........................58

Figure 30. Burst Read and Write Transactions with 1, 0 Wait States and Extra Tr State on Read,

16-Bit 80 96 0 Lo cal Bus .. .... .... .... ... ............ .... ... .... ............ .... ... .... ............ ... .... .... ............ ... ........ ...59

Figure 31. Bus Transactions Generated by Doubl e Word Re ad Bus Request, Misaligned One Byte From

Quad Word Boundary, 32-Bit 80960 Local Bus ...........................................................................60

Figure 32. HOLD/HOLDA Waveform For Bus Arbitration .............................................................................61

Figure 33. 80960 Core Cold Reset Waveform ..............................................................................................62

Figure 34. 80960 Local Bus Warm Reset Waveform ....................................................................................63

TABLES

Table 1. Relat ed Docu men tation ....... ............ .... ... ............ .... .... ........... .... .... ........... .... .... ........... ............ ... ... 1

Table 2. 80960R x Instru c tio n Set .................. .... ... ............ .... .... ... ............ .... ... ............ .... .... ........... .... .... ......7

Table 3. Signal Type Definition ....................................................................................................................8

Table 4. Signal Descr ip tio ns ........... ... .... ............ ... .... ............ .... ... .... ............ ... .... ............ .... ... .... ............ ... ... 9

Table 5. Power Requi r eme nt, Processor Contr ol an d Tes t Sig na l D escri pt io ns ........ ........... .... .... ........... . 13

Table 6. Interrupt Unit Signal Descriptions ................................................................................................ 14

Table 7. PCI Signal Des c rip tio ns ........... .... ........... .... .... .... ........... .... .... ........... .... .... ............ ... ................ ... . 15

Table 8. Memory Con tro lle r Sign al Desc rip ti ons .............. .... .... ... ............ .... ... ............ .... .... ... ............ ........18

Table 9. DMA, APIC, I

2

C Units Signal Descriptions .................................................................................. 19

Table 10 . Clock Sig nal .. .... .... .... .... ........... .... .... .... ........... .... .... .... ........... .... .... ... ............ .... ....... .... .... .... ........ 20

Table 11 . ICE Signal Des c rip tio ns ............... ........... .... .... .... ........... .... .... .... ........... .... .... .... .......................... . 20

Table 12 . 352-Lead HL-PBGA Package — Signal Name Order

(Sheet 1 of 4) ........................................... 23

Table 13. 352-Lead HL-PBGA Pinout — Ballpad Number Order (Sheet 1 of 4) .........................................27

Table 14. 352-Lead HL-PBGA Package Thermal Characteristics ............................................................... 32

Table 15 . Heatsin k Infor ma tio n . .... .... ... ............ .... ... .... ............ .... ... ............ .... ... ............ .... .... ....... .... .... .... ....33

Table 16 . Operatin g C on ditio ns ........... .... .... ........... .... .... ............ ... .... .... ........... .... .... ............ ... .... .... ........... . 34

Table 17 . V

DIFF

Specification for Dual Power Supply Requirements (3.3 V, 5 V) ....................................... 34

Table 18 . DC Charac te ris tic s .... .... .... ... ............ .... ... .... ............ .... ... .... ............ ... .... .... ............ ................... ... . 35

Table 19 . I

CC

Characteristics .......................................................................................................................36

Table 20. Input Clock Timings .....................................................................................................................37

Table 21 . Synchron ou s Outp ut Timi ng s .. ............ ... .... .... ............ ... .... .... ........... .... .... .... ........... .... .... ........ ... . 37

Table 22 . Synchron ou s Inp u t Timing s ..... .... .... ........... .... .... .... .... ........... .... .... ... ............ .... .... ... ................... . 38

Table 23 . Relat ive Ou tp ut Timi ng s ...... .... .... .... .... ........... .... .... .... ........... .... .... ........... .... .... .... ....................... 39

Table 24. Fast Page Mode Non-interleaved DRAM Output Timings ...........................................................39

Table 25. Fast Page Mode Interleaved DRAM Output Timings ...................................................................40

Table 26. EDO DRAM Output Timings ........................................................................................................40

Table 27 . BEDO DRAM Outpu t Timin gs .. .... .... ........... .... .... .... ........... .... .... .... ........... .... .... .... ........... ........ ....41

Table 28 . SRAM/R OM Ou tp ut Ti ming s .... ............ ... .... .... ............ ... .... .... .... ........... .... .... .... ........... .... ........ ... . 41

Table 29. Boundary Scan Test Signal Timings ............................................................................................ 42

Table 30 . APIC Bus Interf ac e Sig na l Timin gs ......... .... .... .... ........... .... .... .... ........... .... .... .... ........... .... ........ ....42

Table 31. I2C Interface Signal Timings ........................................................................................................43

Table 32. Processor Device ID Register - PDIDR ......................................................................................64

i960® Rx I/O Processor at 3.3 V

vi

i960® Rx I/O Processor at 3.3 V

ADVANCE INFORMATION 1

1.0 ABOUT THIS DOCUMENT

This is the ADVANCE INFORMATION data sheet for

the low-power (3.3 V) versions of Intel’s i960

®

Rx I/O

Proc essor family, including:

• 80960RD 66/3.3

• 80960RP 33/3.3

Throughout this document, these family members

are referred to as

80960R x

when the in formatio n is

common to both. For product-specific information,

such as e lectric al c h ar a ct er i st ic s, the fam ily me m be r

names are used.

This does not contain specifications for the 5 Volt

version (809 60 R P 33/5. 0) . For spec i fic at ions on th at

product, refer to the

i960® RP I/O Processor

Data

Sheet (272737).

This data sheet contains a functional overview,

mechanical data (package signal locations and

simulated thermal characteristics), ta rgeted electrical

specifications (simulated), and bus functional waveforms. Detailed functional descriptions other than

parametric performance is published in the

i960® RP

Microprocessor User’s Guide

(272736).

1.1 Solutions960® Program

Intel’s

Solutions960

®

program features a wide

variety of development tools which support the i960

processor family. Many of these tools are developed

by partner companies; some are developed by Intel,

such as profile-driven optimizing compilers. For

more information on these products, contact your

local Intel repres entati ve .

1.2 Terminology

In this document, the following terms are used:

•

local bus

refers to the 80960Rx’s internal local

bus, not the PCI local bus.

•

Primary and Secondary PCI buses

are the

80960Rx’s internal PCI buses which conform to

PCI SIG specifications.

•

80960 core

refers to the 80960JF processor which

is integrated into the 80960Rx.

1.3 Additional Information Sources

Intel documentation is available from your local Intel

Sales Representative or Intel Literature Sales.

Intel Corporation

Literature Sal es

P.O. Box 7641

Mt. Prospect IL 60056-7641

1-800-879-4683

Table 1. Related Documentation

Document Title Order / Contact

i960® RP Microprocessor User’s Guide

Intel Order # 272736

i960® RP Processor: A Single-Chip Intelligent I/O Subsystem

Technical Brief

Intel Order # 272738

i960® Jx Micro processor User’s Guide

Intel Order # 272483

80960RP Spec ificat ion Update

Intel Order # 272918

PCI Local Bus Specification

Revision 2.1 PCI Special Interest Group 1-800-433-5177

PCI-to-PCI Bridge Architecture Specification

Revision 1.0 PCI Special Interest Group 1-800-433-5177

I2C Peripherals for Microcontrollers

Philips Semiconductor

2 ADVANCE INFORMATION

i960® Rx I/O Processor at 3.3 V

2.0 FUNCTIONAL OVERVIEW

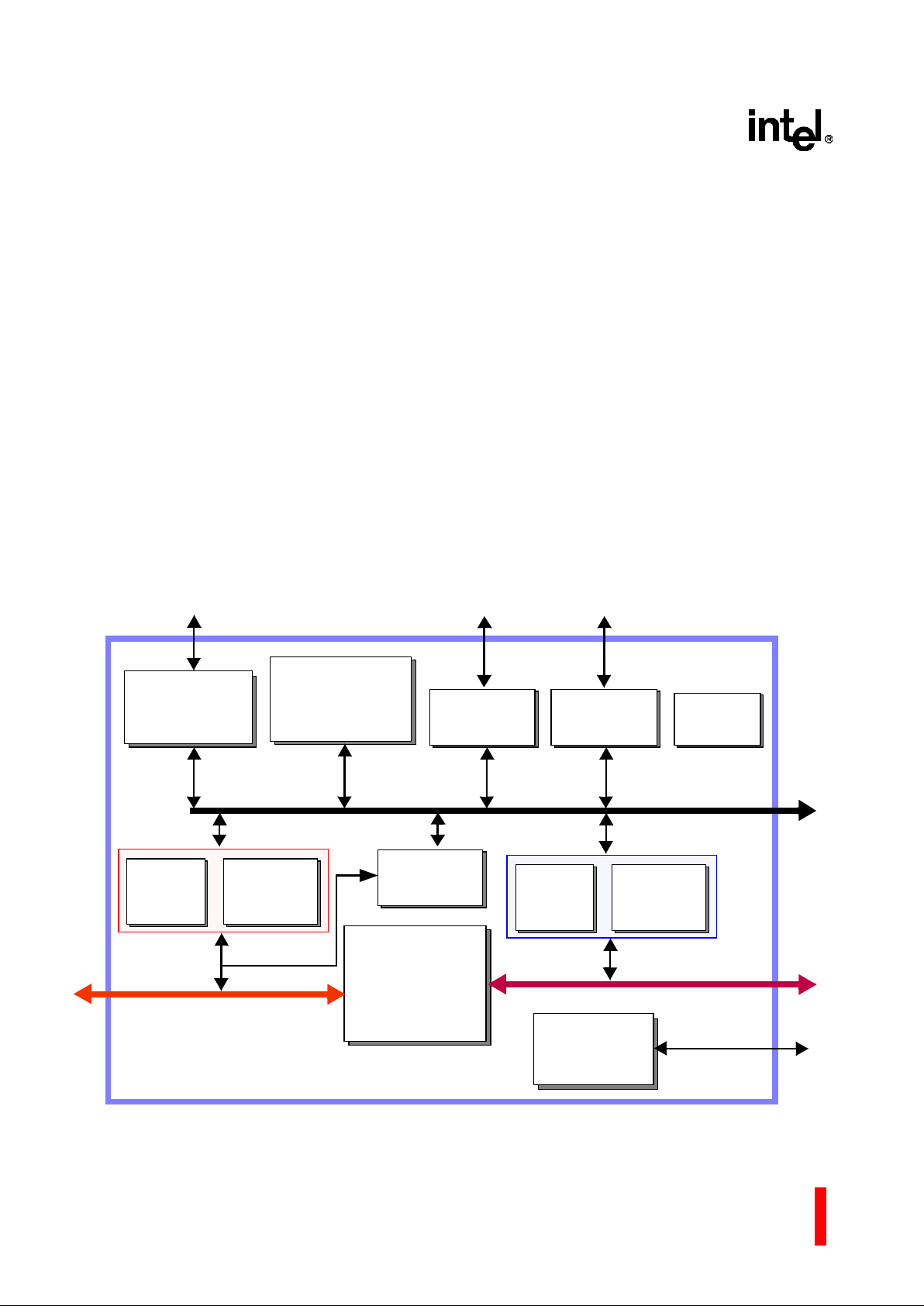

As indicated in Figure 1, the 80960Rx combines

many featur es with the 80960JF to crea te an intel ligent I/O processor. Subsections following the figure

briefl y descri be the ma in feat ures; for d etailed functional descriptions, refer to the

i960® RP Micropro-

cessor User’s Guide

(272736).

The PCI bus is an industry standard, high performanc e, low laten cy system bu s that ope rates up to

132 Mbyte/s. The 80960Rx, a multi-function PCI

device, is fully compliant with the

PCI Local Bus

Specification

Revisio n 2.1. Func tion 0 is the PCI -toPCI bridge unit; Function 1 is the ad dress translation

unit.

The PCI-to-PCI bridge unit is the connection path

between two independent 32-bit PCI buses and

provide s the ability to overcome PCI electri cal load

limits. The addition of the i960 core processor brings

intelligence to the bridge.

The 80960Rx, object code compatible with the i960

core processor, is capable of sustained execution at

the rate of one instruction per clock.

The local bus, a 32-bit multiplexed burst bus, is a

high-speed in terface to sys tem memory and I/O. A

full complement of control signals simplifies the

connection of the 80960Rx to external components.

Physical and logical memory attributes are

programmed via memory-mapped control registers

(MMRs), an extension not found on the i960 Kx, Sx

or Cx p roces sors . P hysi cal and l ogic al co nfig ura tion

registers enable the processor to operate with all

combinations of bus width and data object alignment.

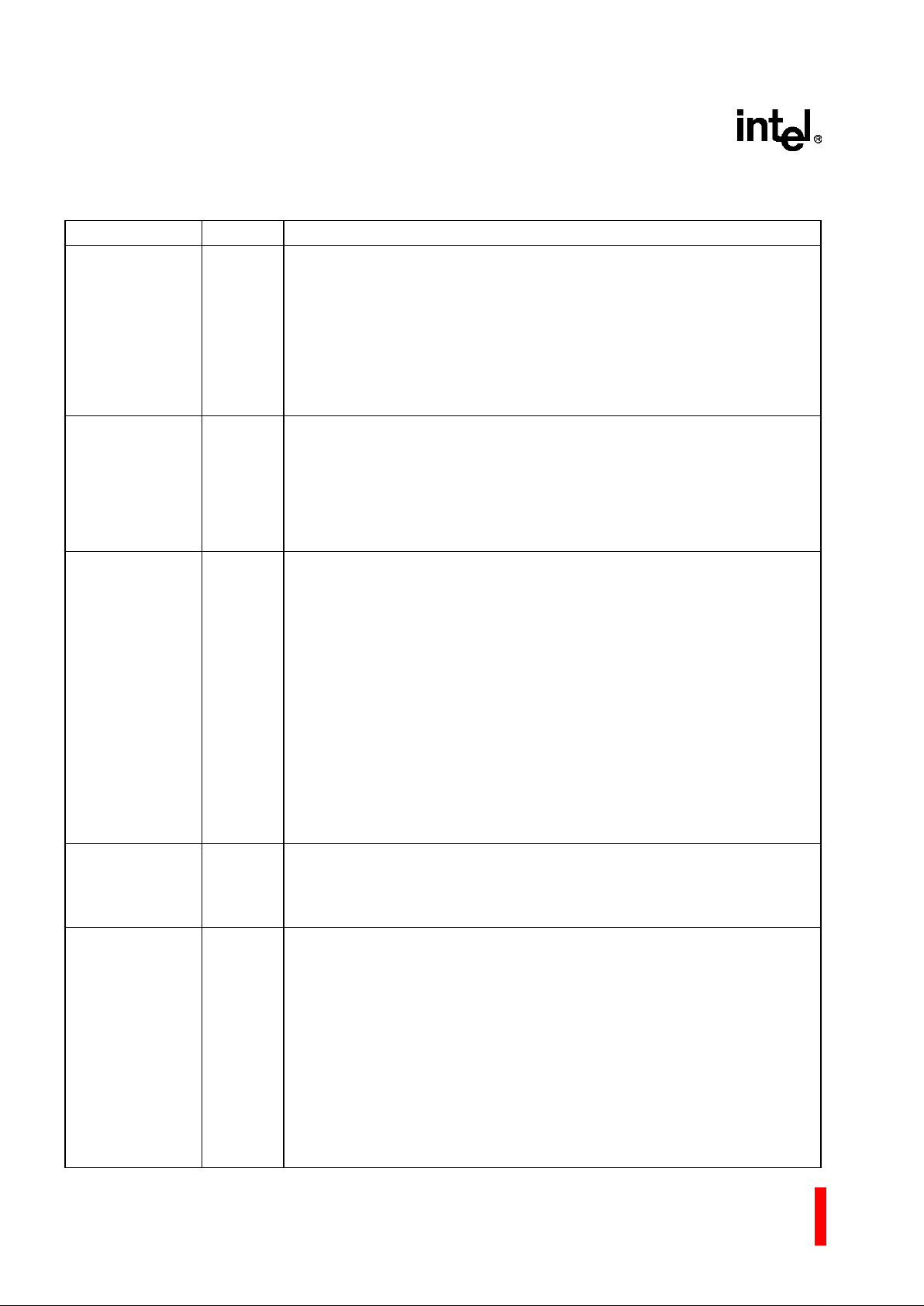

Figure 1. i960

®

Rx I/O Processor at 3.3 V Functional Block Diagram

PCI-to-PCI

Bridge Unit

i960

®

JF

Core

Processor

Secondary

PCI Arbitration

Unit

Secondary PCI Bus

Primary PCI Bus

Local Memory

I2C Bus

Interface Unit

Memory

Controller

Internal

Arbitration

I2C Serial Bus

I/O APIC Bus

Interface Unit

I/O APIC Bus

Address

Translation

Unit

Two DMA

Channels

Address

Translation

Unit

One DMA

Channel

Message

Unit

Local Bus

Primary ATU

Secondary ATU

i960® Rx I/O Processor at 3.3 V

ADVANCE INFORMATION 3

2.1 Key Functional Units

2.1.1 PCI-to-PCI Bridge Unit

The PCI-to-PCI bridge unit (referred to as “bridge”)

connects two independent PCI buses. It is fully

compliant with the

PCI-to-PCI Bridge Architecture

Specification

Revision 1.0 published by the PCI

Special Interest Group. It allows certain bus transactions on one PCI bus t o be forwarde d to the other

PCI bus. Dedicated data queues support high performance bandwidth on the PCI buses. The i960

®

Rx

I/O Processor at 3.3 V supports PCI 64-bit Dual

Address Cycle (DAC) addressing.

The bridge has dedicated PCI configuration space

that is accessible through the primary PCI bus.

2.1.2 Private PCI Device Support

A key design feature is that the 80960Rx explicitly

suppor ts pri vate PCI de vices on the s econd ary PCI

bus without being detected by PCI configuration software. T he bridg e a nd Address T ran slatio n U n it work

togethe r to hide priv ate d evic es fr om P CI co nf igura tion cycles and allow these devices to use a private

PCI address space. The Address Translation Unit

uses normal PCI configuration cycles to configure

these devices.

2.1.3 DMA Controller

The DMA Controller supports low-latency, highthroughput data transfers between PCI bus agents

and 80960 local memory. Three separate DMA

channels accommodate data transfers: two for

primary PCI bus, one for the secondary PCI bus.

The DMA Controller supports chaining and

unaligned data transfers. It is programmable only

through the i960 core processor.

2.1.4 Address Translation Unit

The Address Translation Unit (ATU) allows PCI

transactions direct access to the 80960Rx local

memor y. Th e 80 96 0Rx ha s di rec t acce ss t o bo th P CI

buses. The ATU supports transactions between PCI

address space and 80960Rx addr ess space.

Address translation is controlled through programmable r egister s accessib le from bot h the PCI in terface a nd the 8096 0 core. Dual access to regi sters

allows flexibility in mapping the two address spaces.

2.1.5 Messaging Unit

The Messaging Unit (MU) provides data transfer

between the PCI system and the 80960Rx. It uses

interrupts to notify each system when new data

arrives. The MU has four messaging mechanisms.

Each allows a host processor or external PCI device

and the 80960Rx to communicate through message

passing and interrupt generation. The four mechanisms are Message Registers, Doorbell Registers,

Circular Queues, and Index Registers.

2.1.6 Memory Controller

The Memory Controller allows direct control of

externa l memo ry syst ems, incl uding D RAM, SR AM,

ROM and Fl a sh Mem or y. It pr ov ides a dir ec t co nnect

interface to memory that typically does not require

external logic. It features programmable chip selects,

a wait state generator and byte parity. External

memory can be configured as PCI addressable

memory or priv ate processor memory.

2.1.7 I

2

C Bus Interface Unit

The I

2

C (Inter-Inte grated Circuit) Bus Inter face Unit

allows the 80960 core to serve as a master and

slave device residing on the I

2

C bus. The I2C bus is

a serial bus developed by Philips Semiconductor

consi sting of a tw o pin in terfa ce. Th e bus allow s the

80960Rx to interface to other I

2

C peripherals and

microc ontrollers fo r system m anagemen t functions.

It requires a min imum of hardwa re for an economical

syste m to rel ay status and relia bility in formatio n on

the I/O sub system to an external device. For more

information, see

I2C Perip he rals for Micr ocon tro llers

(Philips Semiconductor)

2.1.8 I/O APIC Bus Interface Unit

The I/O APIC Bus Interface Unit provides an interface to the three-wire Advanced Programmable

Interrupt Con troller (APIC) bus that allows I/O API C

emulation in software. Interrupt messages can be

sent on the bus and EOI messages can be received.

4 ADVANCE INFORMATION

i960® Rx I/O Processor at 3.3 V

2.1.9 Secondary PCI Arbitration Unit

The Secondary PCI Arbitration Unit provides PCI

arbitration for the secondary PCI bus. It includes a

fairness algorithm with programmable priorities and

six PCI Request and Grant signal pairs. This arbitration unit can also be disabled to allow for external

arbitration.

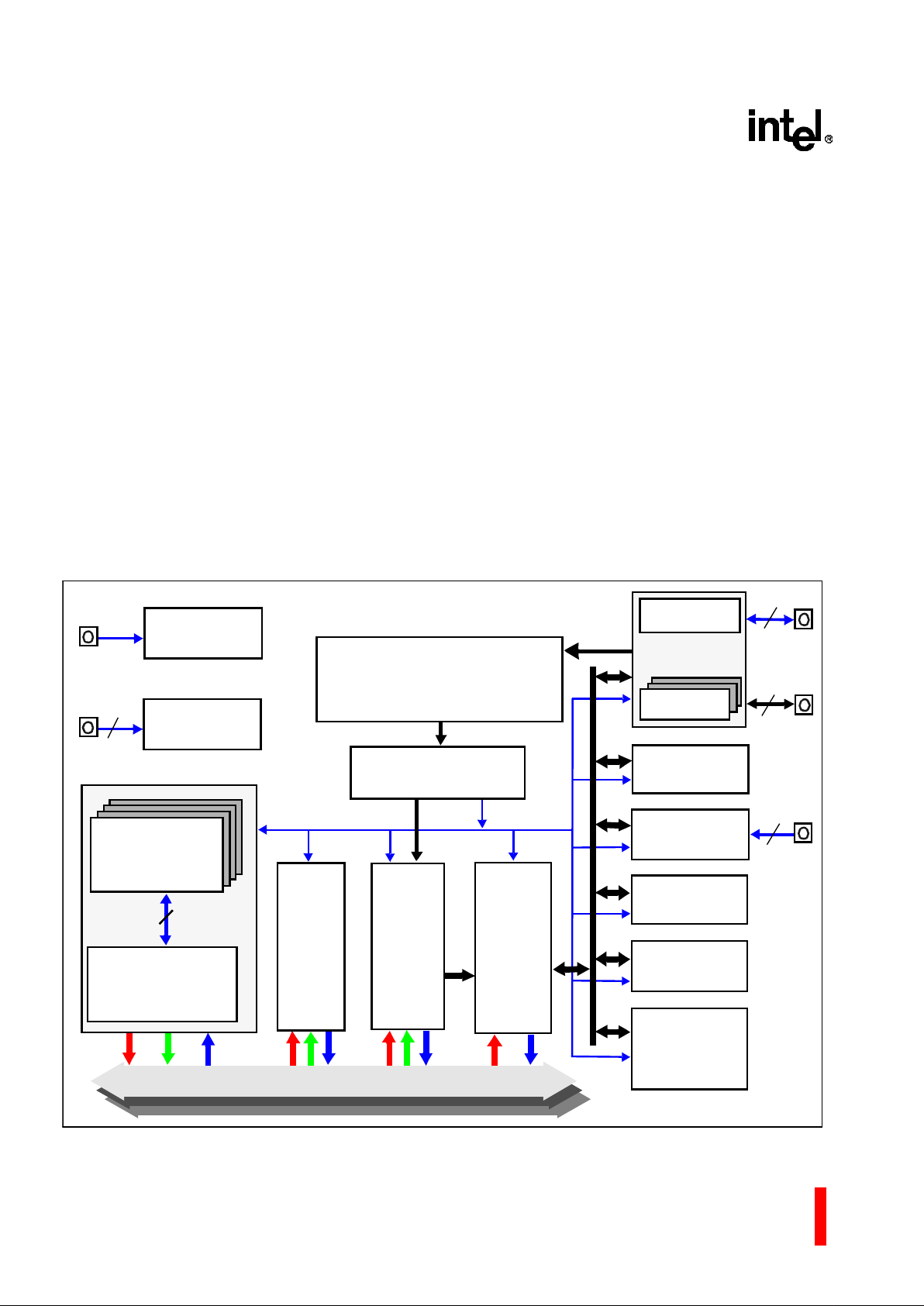

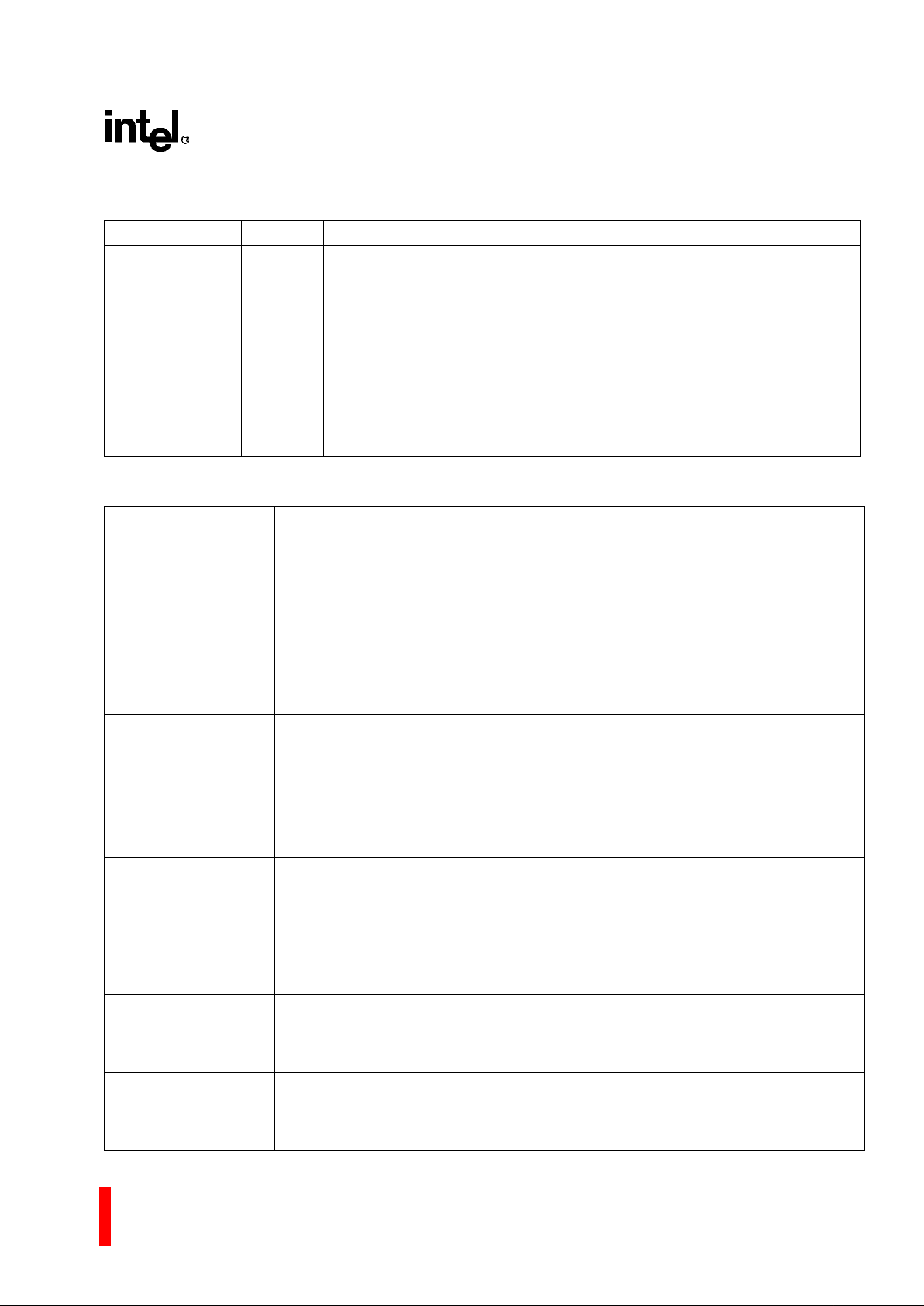

2.2 i960 Core Features (80960JF)

The processing power of the 80960Rx comes from

the 80960J F pro c es sor core. The 80 96 0J F i s a n ew ,

scalar implementation of the 80960 Core Architecture. Figure 2 shows a block diagram of the 80960JF

Core processor.

Factors that contribute to the 80960 family core’s

per form a n c e in cl ud e:

• Single-clock execution of most instructions

• Independent Multiply/Divide Unit

• Efficient instruction pipeline minimizes pipeline

break latenc y

• Register and resource scoreboarding allow

overlapped instruction execution

• 128-bit regi ster bus speeds local regi ster caching

• 4 Kbyte two-wa y set-associati v e, integrated

inst ruc tion cac he

• 2 Kbyte direct-mapped, integrated data cache

• 1 Kbyte integrated data RAM delivers zero w ait

state program data

The 80960 core operates out of its own 32-bit

address space, which is independent of the PCI

address space. The local bus memory can be:

• Made visible to the PCI address space

• Kept private to the 80960 core

• Allocated as a combination of the two

Figure 2. 80960JF Core Block Diag ram

Programmable

Bus

Control Unit

Interrupt Controller

Control

Address/

Instruction Sequencer

Physical Region

Configuration

Interrupt

Port

1K byte

Data RAM

Memory

Interface

Execution

Multiply

Unit

Divide

Unit

Memory-Mapped

Register Interface

Data Bus

Global / Local

Register File

SRC2 DSTSRC1

Address

Control

Effective

Constants

Generation

Unit

Address

32-bit Addr

32-bit Data

Bus Request

Queues

and

Two 32-Bit

Timers

8-Set

Local Register

SRC1

SRC2

DST

PLL, Clocks,

Power Mgmt

Boundary Scan

Controller

TAP

5

128

SRC1

SRC2

DST

SRC1

DST

9

32

32-bit buses

address / data

3 Independent 32-Bit SRC1, SRC2, and DST Buses

Instruction Cache

4 Kbyte Two-Way Set Associative

2Kbyte

Direct Mapped

Data Cache

S_CLK

Cache

i960® Rx I/O Processor at 3.3 V

ADVANCE INFORMATION 5

2.2.1 Burst Bu s

A 32-bit high-performance bus controller interfaces

the 80960Rx to external memory and peripherals.

The Bus Control Unit fetches instructions and transfers data on the l ocal bus at the r ate of up to four 32bit words per six clock cycles. The external

addre s s/d a ta bus is mul tip le xed.

Users may configure the 80960R x’s bus controller to

match an ap plic at ion’s fund ame ntal mem ory orga nization. Physi cal bus width is programmable for up to

eight re gion s. Data c aching is prog rammed through

a group of logica l memor y templa tes and a d efaults

register. The Bus Control Unit’s featur es include:

• Multiplexed external bus minimizes pin count

• 32-, 16- and 8-bit bus widths simplify I/O interfaces

• External ready control for address-to-data, data-todata and data-to-next-address wait state types

• Litt le endi an byte ordering

• Unaligned bus accesses performed transparently

• Three-deep load/store queue decouples the bus

from the 8096 0 core

Upon reset, th e 80960Rx conducts an i nternal self

test. Before executing its first instruction, it performs

an external bus confidence test by performing a

check su m on th e fir s t w or d s o f the In iti al iz at ion B o ot

Record.

2.2.2 Timer Unit

The tim er unit (TU ) con tains t wo in depe nden t 3 2-bit

timers that are capable of counting at several clock

rates and generating interr upts. Each is programme d

by use of the Timer Unit registers. These memorymapped registers are addressable on 32-bit boundaries. The timers have a single-shot mode and autoreload capabilities for continuous operation. Each

timer has an independent interrupt request to the

80960Rx’s interrupt controller. The TU can generate

a fault when unauthorized writes from user mode are

detected.

2.2.3 Priority Interrupt Controller

Low interrupt laten cy is criti cal to many embedded

applications. As part of its highly flexible interrupt

mechanism, the 80960Rx exploits several techniques to minimize latency:

• Inte rrupt vec tor s and int errup t hand ler ro utine s can

be reserved on-chip

• Register frames for high-priority interrupt handlers

can be cached on-chip

• The in terrupt stack can be plac ed in cacheable

memory space

2.2.4 Faults and Debugging

The 80960Rx employs a comprehensive fault model.

The pro cessor respon ds to faul ts by mak ing imp licit

calls to a fa ult h andl ing r outin e. Spec ific info rmati on

collected for each fault allows the fault handler to

diagno se exceptions an d rec ov e r appr op r ia tel y.

The processor also has built-in debug capabilities.

Via software, the 80960Rx may be configured to

detect as many as seven differ ent trace event types.

Alternatively, mark and fmark instructions can

generate trace events explicitly in the instruction

stream. Hardware breakpoint registers are also

available to trap on execution and data addresses.

2.2.5 On-Chip Cache and Data RAM

Memory subsystems often impose substantial wait

state penalties. The 80960Rx integrates considerable storage resources on-chip to decouple CPU

execution from the external b us. It also includes a

4 Kbyte instruction cache, a 2 Kbyte data cache and

1 Kbyte data RAM.

2.2.6 Local Register Cache

The 809 60 R x rap id ly allocates and deal loc a tes l oc al

register sets during context switches. The processor

needs to flush a register set to the stack only when it

saves more than seven sets to its local register

cache.

2.2.7 Test Features

The 80960Rx incorporates numerous features that

enhance the user’s ability to test both the processor

and the system to which it is attached. These

features include ONCE (On-Circuit Emulation) mode

and Boundary Scan (JTAG).

The 80960Rx provides testability features compatible with IEEE Standard Test Access Port and

Boundary Scan Architecture (IEEE Std. 1149.1).

i960® Rx I/O Processor at 3.3 V

6

ADVANCE INFORMATION

One of the boundary scan instructions, HIGHZ,

forces the processor to float all its output pins

(ONCE mode). ONCE mode can also be initiated at

reset without using the boundary scan mechanism.

ONCE mode is useful for board-level testing. This

feature allows a mounted 80960Rx to electrically

“remove” itself from a circuit board. This mode allows

system-level testing where a remote tester can

exercise the processor system.

The test logic does not interfere with component or

system behavior and ensures that components

function correctly, and also the connections between

variou s components are corr ect.

The JTAG Boundary Scan feature is an alternative

to conventional “bed-of-nails” testing. It can examine

conn ection s that mig ht otherw ise be inaccess ible to

a test sys tem.

2.2.8 Memory-Mapped Control Registers

The 80960Rx is compliant with 80960 family architecture and has the added advantage of memorymapp ed, intern al contro l registe rs not fo und on th e

80960K x, Sx or C x pro c es sors . T hi s fe atur e prov id es

software an interface to easily read and modify

internal control registers.

Each memory-mapped, 32-bit register is accessed

via regular memory-format instructions. The

processor ensures that these accesses do not

generate external bu s cycles.

2.2.9 Instructions, Data Types and Memory

Addressing Modes

As with all 80960 family processors, the 80960Rx

instru ction set suppor ts several different d ata types

and formats:

•Bit

• Bit fields

• I nt eg er (8-, 16-, 32-, 64-b it )

• Ordinal (8-, 16-, 32-, 64-bit unsigned integers)

• Tripl e word (96 bits)

• Quad word (128 bits)

The 80960Rx provides a full set of addressing

modes for C and assembly:

• Two Absolute modes

• Five Register Indire ct modes

• Index with displacement mode

• IP with displacement mode

Table 2 shows the available instructions.

i960® Rx I/O P rocessor at 3.3 V

ADVANCE INFORMATION 7

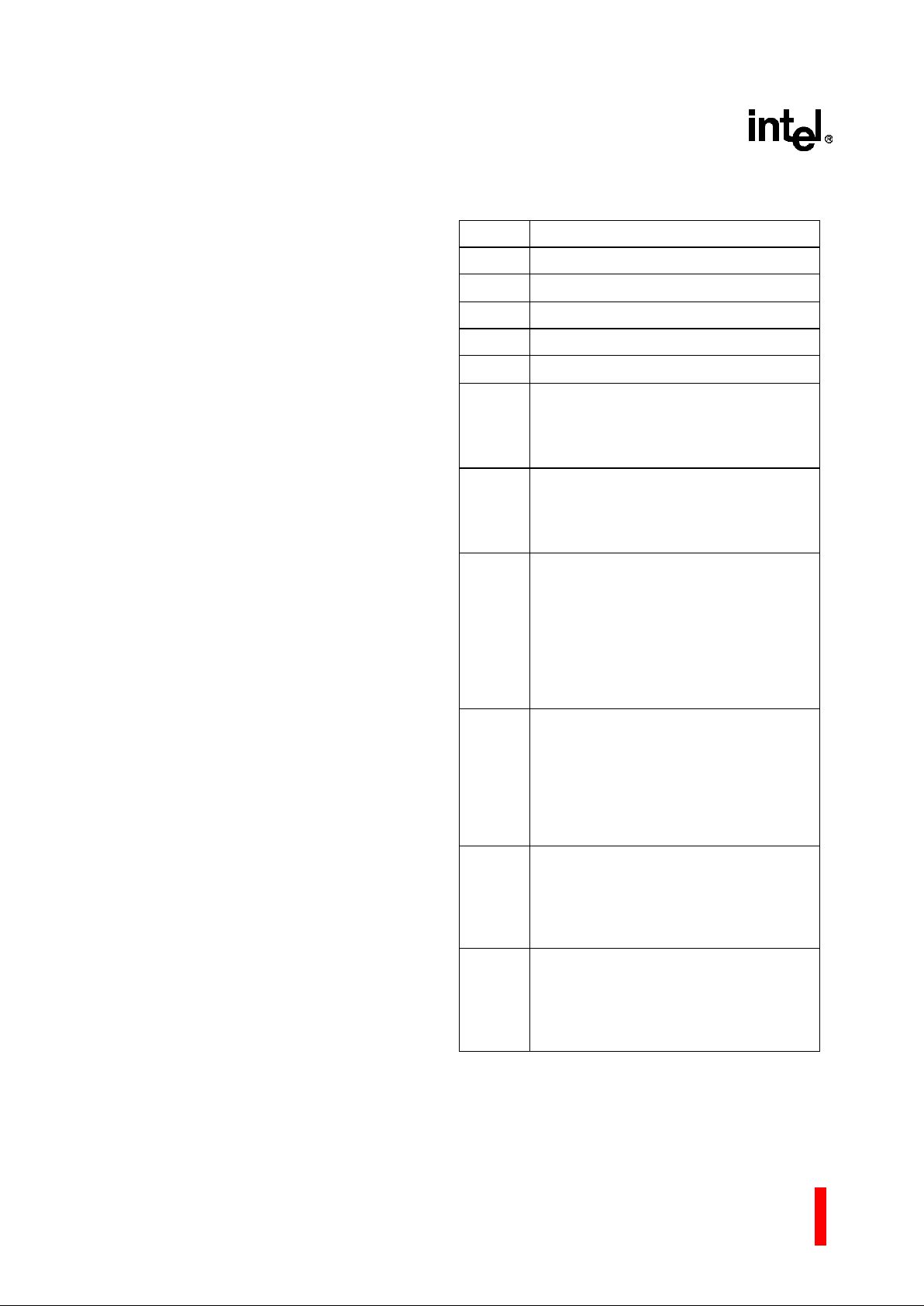

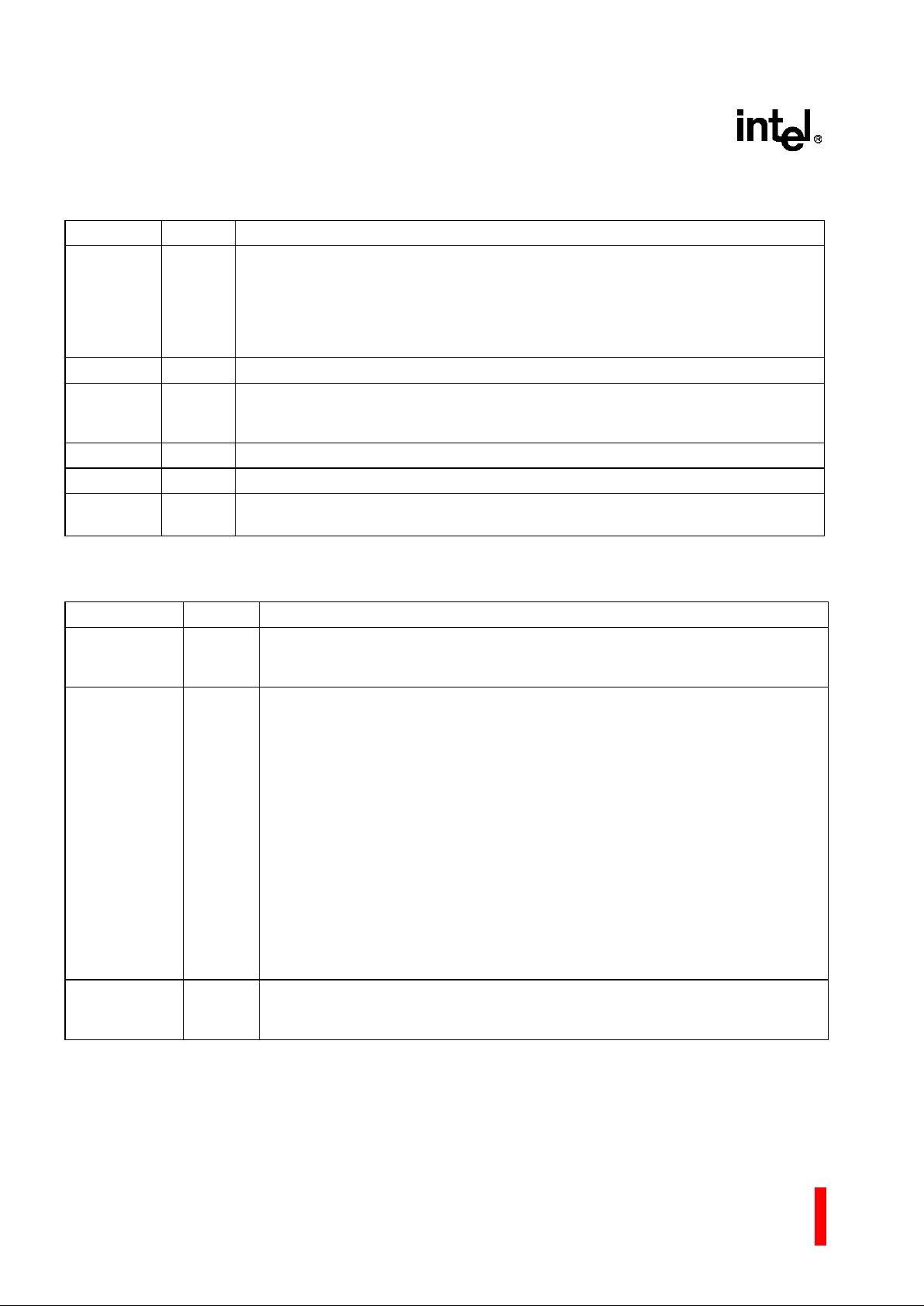

Table 2. 80960Rx Instruction Set

Data Movement Arithmetic Logical Bit, Bit Field and Byte

Load

Store

Move

Conditional Select

Load Address

Add

Subtract

Multiply

Divide

Remai nder

Modulo

Shift

Extended Shift

Exten de d Mu ltiply

Extended Divide

Add with Carry

Subtract with Carry

Condi tio na l A dd

Condi tio nal Subtr a ct

Rotate

And

Not And

And Not

Or

Exclusive Or

Not Or

Or Not

Nor

Exclusive Nor

Not

Nand

Set Bit

Clear Bit

Not Bit

Alter Bit

Scan For Bit

Span Over Bit

Extract

Modify

Scan Byte for Equal

Byte Swap

Comparison Branch Call/Return Fault

Compare

Conditional Compare

Compare and

Increment

Compare and

Decrement

Test Condition Code

Check Bit

Unconditional Branch

Condi tio na l B ran c h

Compa re and Br anch

Call

Call Extended

Call System

Return

Branch and Link

Conditional Fault

Synch ron iz e Fa ults

Debug

Processor

Manage me nt

Atomic

Modify Trace Controls

Mark

Force Mark

Flush Local Registers

Modify Arithmetic

Controls

Modify Process

Controls

Halt

System Control

Cache Control

Interrupt Control

Atomic Add

Atom i c Mo di fy

i960® Rx I/O Processor at 3.3 V

8

ADVANCE INFORMATION

3.0 PACKAGE INFORMATION

3.1 Package Introduction

The 80960Rx is offered in a SuperBGA* Ball Grid

Array (HL-PBG A) pac kag e. This is a peri mete r array

package with four rows of ball connections in the

outer area of the package. See Figure 4, 352L HLPBGA Package Diagram (Bottom View) (pg. 22).

Section 3.1.1, Functional Signal Definitions

describes signal function; Section 3.1.2, 352-Lead

HL-PBGA Pack age defines the signal and ball loca-

tions.

3.1.1 Functional Signal Definitions

Table 3 pres ents t he legend for interpreting the Type

Field in th e foll owi ng ta bles . Table 4 defines signals

associated with the bus interface. Table 5 defines

signals associated with basic control and test functions. Table 6 defines signals associated with the

Interrupt Unit. Table 7 define s PCI signa ls. Table 8

defin es Memo ry Contro ller sign als. Table 9 defines

DMA, APIC and I

2

C sign als. Tabl e 10 defin es cloc k

sign als. Table 11 defines ICE signals.

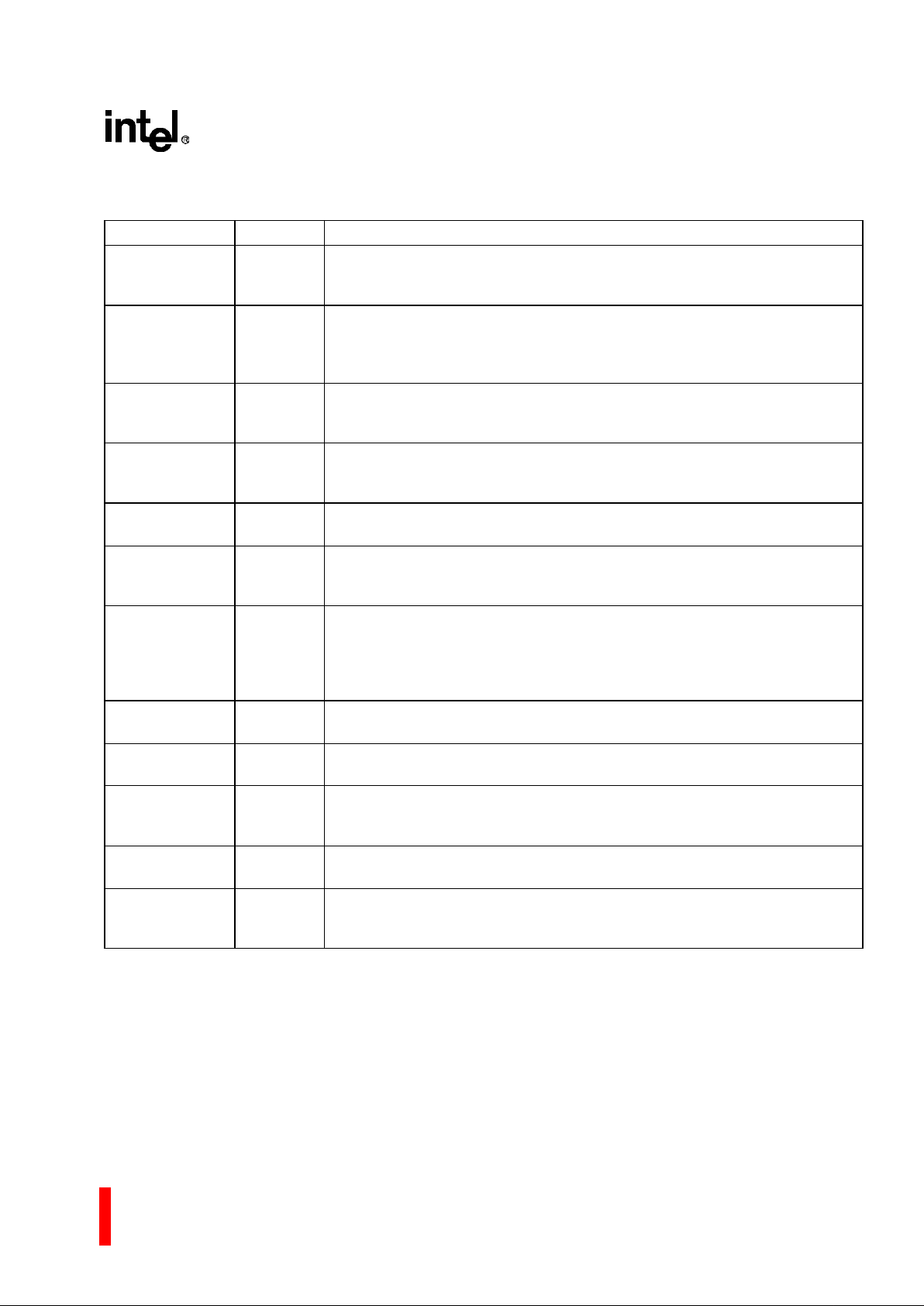

Table 3. Signal Type Definition

Symbol Description

I Input signal only.

O Output signal only.

I/O Signal can be either an input or out put.

OD Open Drain signal.

– Signal must be connected as described.

S (...) Synchronous. Inputs must meet setup

and hold times relative to S_CLK.

S(E) Edge sensitive input

S(L) Level sensitive input

A (...) Asynchronous. Inputs may be

asynchronous relative to S_CLK.

A(E) Edge sensitive input

A(L) Level sensitive input

R (...) While the P_RST# signal is asserted,

the signal:

R(1) is driven to V

CC

R(0) is driven to V

SS

R(Q) is a valid output

R(Z) Floats

R(H) is pulled up to V

CC

R(X) is driven to an unknown state

H (...) While the 80960Rx is in the hold state,

the signal:

H(1) is driven to V

CC

H(0) is driven to V

SS

H(Q) Maintains previous state or

continues to be a valid output

H(Z) Floats

P (...) While the 80960Rx is halted, the signal:

P(1) is driven to V

CC

P(0) is driven to V

SS

P(Q) Maintains previous state or

continues to be a valid output

K (...) While the Secondary PCI Bus is being

parked, the signal:

K(Z) Floats

K(Q) Maintains previous state or

continues to be a valid output

i960® Rx I/O P rocessor at 3.3 V

ADVANCE INFORMATION 9

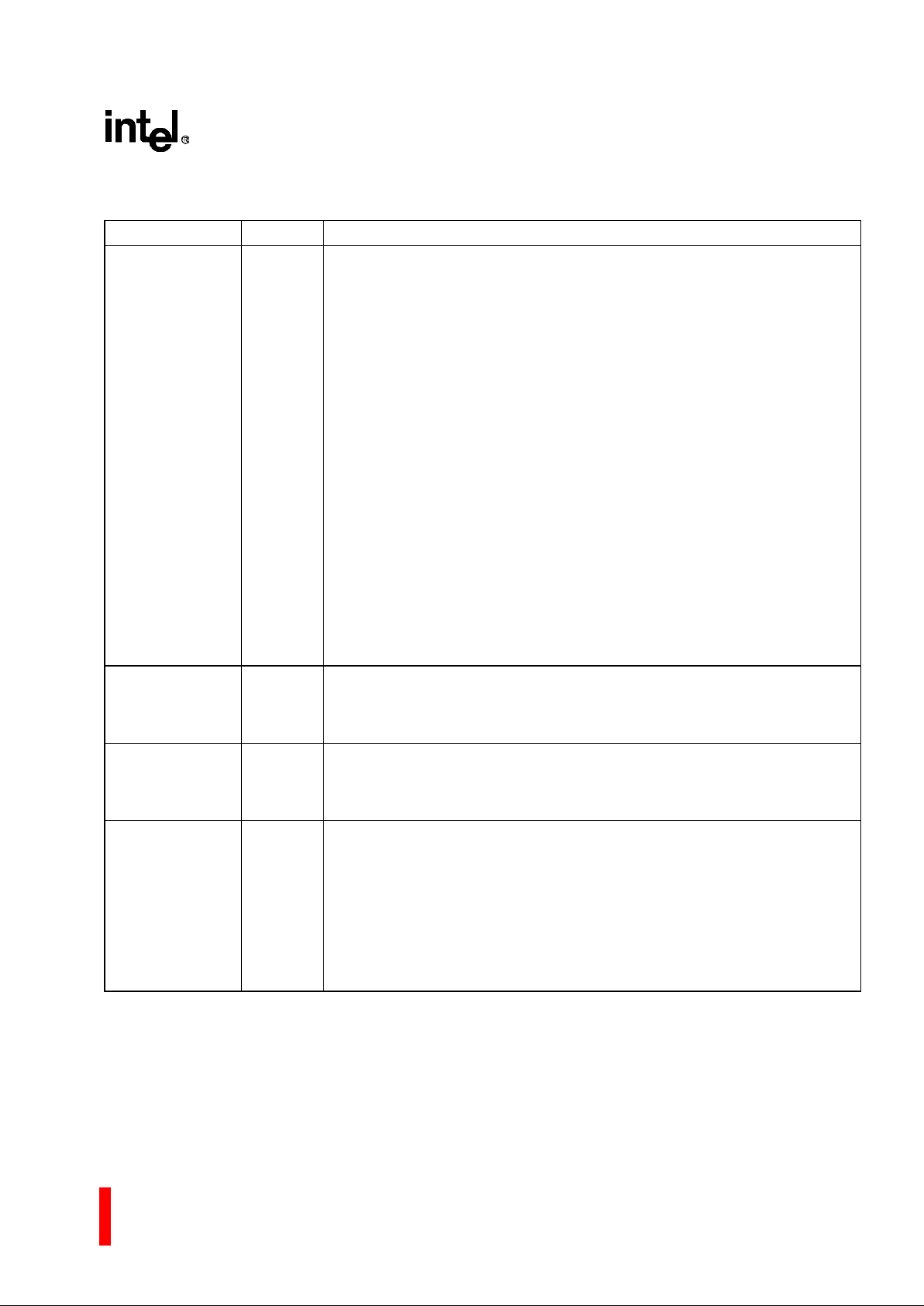

Table 4. Signal Descriptions (Sheet 1 of 5)

NAME TYPE DESCRIPTION

AD31:0 I/O

S(L)

R(Z)

H(Z)

P(Q)

ADDRESS / DATA BUS carries 3 2-bit physic al addresses and 8-, 16- or 32bit data to and from memory. During an address (

T

a

) cycle, bits 2-31 contain

a physical word address (bits 0- 1 indicate SIZE; see below). During a data

(T

d

) cycle, read or write data is present on one or more contiguous bytes,

comprising A D31:24, AD23:1 6, AD15:8 and AD 7:0. Du ring write operation s,

unused signals are driven to determinate values.

SIZE, which comprises bits 0-1 of the AD lines dur ing a

T

a

cycle, specifies

the number of da ta transfers du ring the bus tra nsaction on the local bus.

When the DMA or ATUs initiate data transfers, transfer size shown below is

not valid.

AD1 AD0 Bus Transfers

0 0 1 Tran sfer

0 1 2 Tran sfers

1 0 3 Tran sfers

1 1 4 Transfers

When the 80960Rx enters Halt mode and the previous bus opera tion was:

• write — AD31:2 are driven with the last data value on the AD bus.

• read — AD31:2 are driven with the last address value on the AD bus.

Typically, AD1:0 reflect the SIZE i nformation of t he last bus transaction

(either instruction fetch or load/store) that was executed before entering Halt

mode.

ADS# O

R(1)

H(Z)

P(1)

ADDRESS STROBE indicate s a valid address and the start of a n ew bus

access. The processor asserts ADS# for the entire

T

a

cycle. External bus

contr ol logic typically samples ADS# at the end of the cycle.

ALE O

R(0)

H(Z)

P(0)

ADDRESS LATCH ENABLE indicates the transfer of a physical address.

ALE is asserted during a

T

a

cycle and deasserted before the beginning of the

T

d

state. It is active HIGH and floats to a high impedance state during a hold

cycle (T

h

).

BLAST# O

H(Z)

P(1)

BURST LAST indicates the last transfer in a bus access. B LAST# is

asserted in the last data transfer of burst and non-burst accesses. BLAST#

remains active while wait states are detected via the LRDYRCV# or

RDYRCV# signal on the memory controller. BLAST# becomes inactive after

the final data transfer in a bus cycle. BLAST# has a weak internal pullup

which is act ive dur ing res et to en sure normal ope ration when the signal is

not co nnect ed.

0 = Last Data Transfer

1 = Not the Last Data Transfer

i960® Rx I/O Processor at 3.3 V

10

ADVANCE INFORMATION

BE3:0# O

R(1)

H(Z)

P(1)

BYTE ENABLES select which of up to four data bytes on the bus participate

in the current bus access. Byte enable encoding depe nds on the bus widt h

of the memory region accessed:

32-bit bus:

BE3# en ab le s data on AD3 1: 24

BE2# en ab le s data on AD2 3: 16

BE1# en ab le s data on AD1 5: 8

BE0# en ab le s data on AD7 :0

16-bit bus:

BE3# becomes By te High Enable (enabl es data o n AD15:8)

BE2# is not used (state is high)

BE1# becomes Address Bit 1 (A1)

(increments with the assertion of LRDY# or RDYRCV#)

BE0# becomes By te Low En able (enables data on AD7:0)

8-bit bus:

BE3# is not used (state is high)

BE2# is not used (state is high)

BE1# becomes Address Bit 1 (A1)

(increments with the assertion of LRDY# or RDYRCV#)

BE0# becomes Address Bit 0 (A0)

(increments with the assertion of LRDY# or RDYRCV#)

The processor asserts byte enables, byte high enable and byte low enable

during

T

a

. Since unaligned bus r equests are split into separate bus transac-

tions, these signals do not toggle during a burst (32-bit bus only) from the

i960 core processor; they do toggle for DMA and ATU cycles. They remain

active through the last T

d

cycle.

DEN# O

H(Z)

P(1)

DATA ENABLE indicates data transfer cycles during a bus access. DEN# is

asserted at the start of the first data cycle in a bus access and deasserted at

the en d o f the l a st da ta cycle . DEN # is us ed w ith D T/ R # to pr ov ide c on tr ol f o r

data transceivers connected to the data bus. DEN# has a weak internal

pullup which is active during reset to ensure norm al operation when the

sig nal is not connected.

0 = Data Cycle

1 = Not a Data Cycle

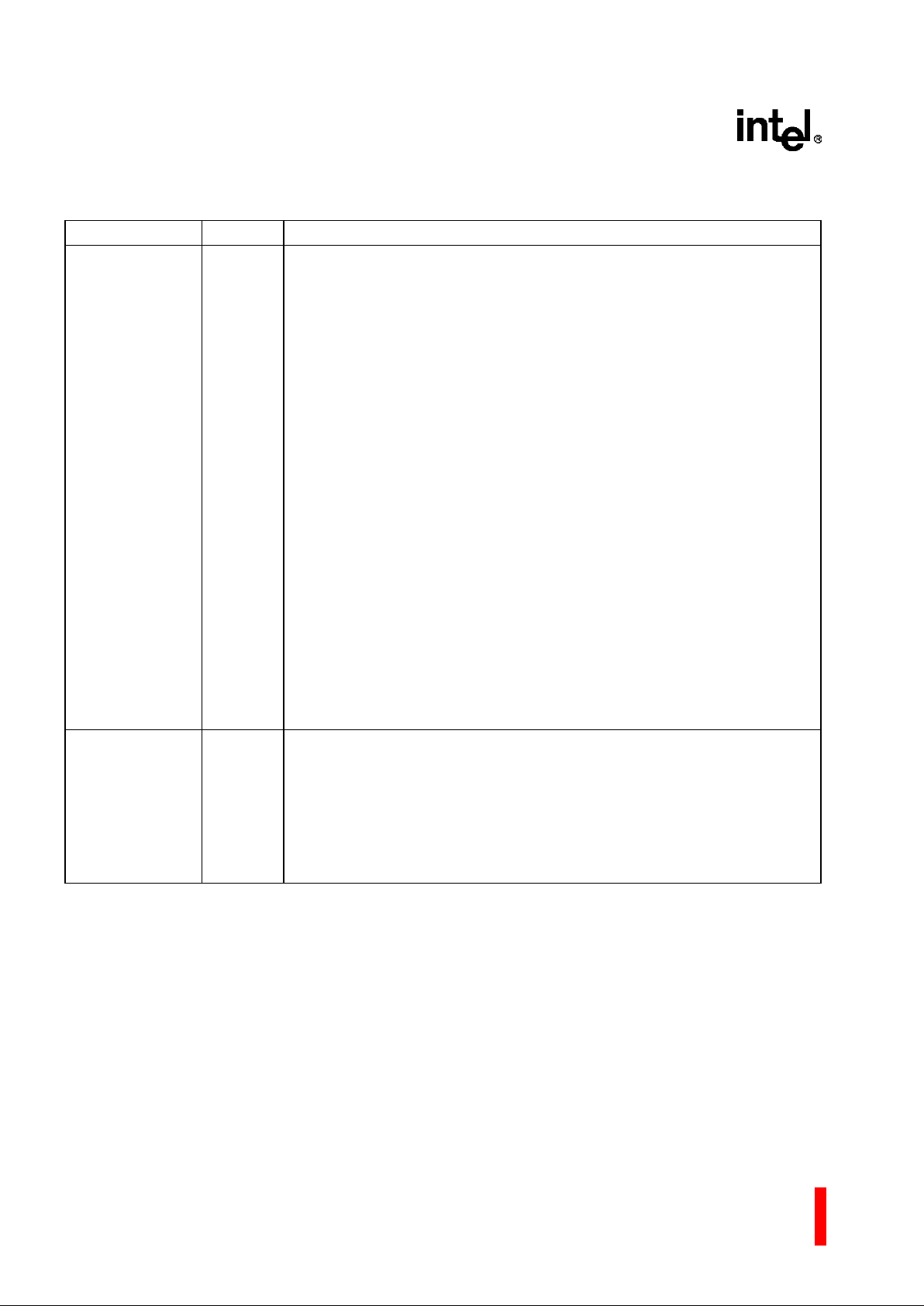

Table 4. Signal Descriptions (Sheet 2 of 5)

NAME TYPE DESCRIPTION

i960® Rx I/O P rocessor at 3.3 V

ADVANCE INFORMATION 11

D/C#/

RST_MODE#

I/O

R(H)

H(Z)

P(Q)

DATA/CODE/RESET_MODE indicates that a bus access is a data access

or an instruction access. D/C# has the same timing as W/R#.

0 = Instruction Access

1 = Data Access

The RST_MODE# signal is sampled at Primary PCI bus reset to determine

whether the 80960 core is to be held in reset. When RST_MODE# is high,

the 80960Rx begins ini tialization immediately following the deassertion of

P_RST. When RST_MOD E is low, the 80960 core remains in re set until the

80960 core reset bit is cleared in the extended bridge contr ol register. This

signal has a weak internal pullup that is active during reset to ensure normal

operation when the signal is left unconnected.

0 = RST_MODE enab led

1 = RST_MODE not enabled

While the 80960 core is in reset, all peripherals may be accessed from th e

primary or sec ondary PCI buses depending on the status of the

WIDTH/HLTD1/RETRY/ signal.

DT/R# O

R(0)

H(Z)

P(Q)

DATA TRANSMIT / RECEIVE indicates the direction of data transfer to and

from the address/data bus. It is low during T

a

and Tw/Td cycles for a read; it

is high du r in g

T

a

and Tw/Td cycles for a write. DT/R # never changes state

when DEN# is asserted.

0 = Receive

1 = Tran smit

LOCK#/ONCE# I/O

S(L)

R(H)

H(Z)

P(Q)

BUS LOCK indica tes that an atomic read-modify-write operation is in

progress. The LOCK# output is asserted in the first clock of an atomic

operation and deasserted in the last data transfe r of the sequence. The

proce ss or does not grant HOLDA while ass e rting LOCK# . T hi s pre ve nt s

external agents from accessing memory involved in semaphore ope rations.

0 = Atomic Read-Modify- Write in Progress

1 = No Atomic Read-Modify-Write in Progress

ONCE MODE: The processor samples the ONCE input during reset. When

ONCE# is asser ted LOW at the end of reset, the processor enters O NCE

mode, stops all clocks and floats all output signals. LOCK#/ONCE# has a

weak internal pullup which is active during reset to ensure normal operation

when the signal is not connected.

0 = ONCE Mode Enabled

1 = ONCE Mode Not Enabled

LRDYRCV# O

R(1)

H(Q)

P(Q)

LOCAL READY/RECOVER, generat ed by th e 809 60 Rx’s memory controller

unit, is an output version of the READY/RECOVER (RDYRCV#) signal.

Refer to the RDYRCV# signal description.

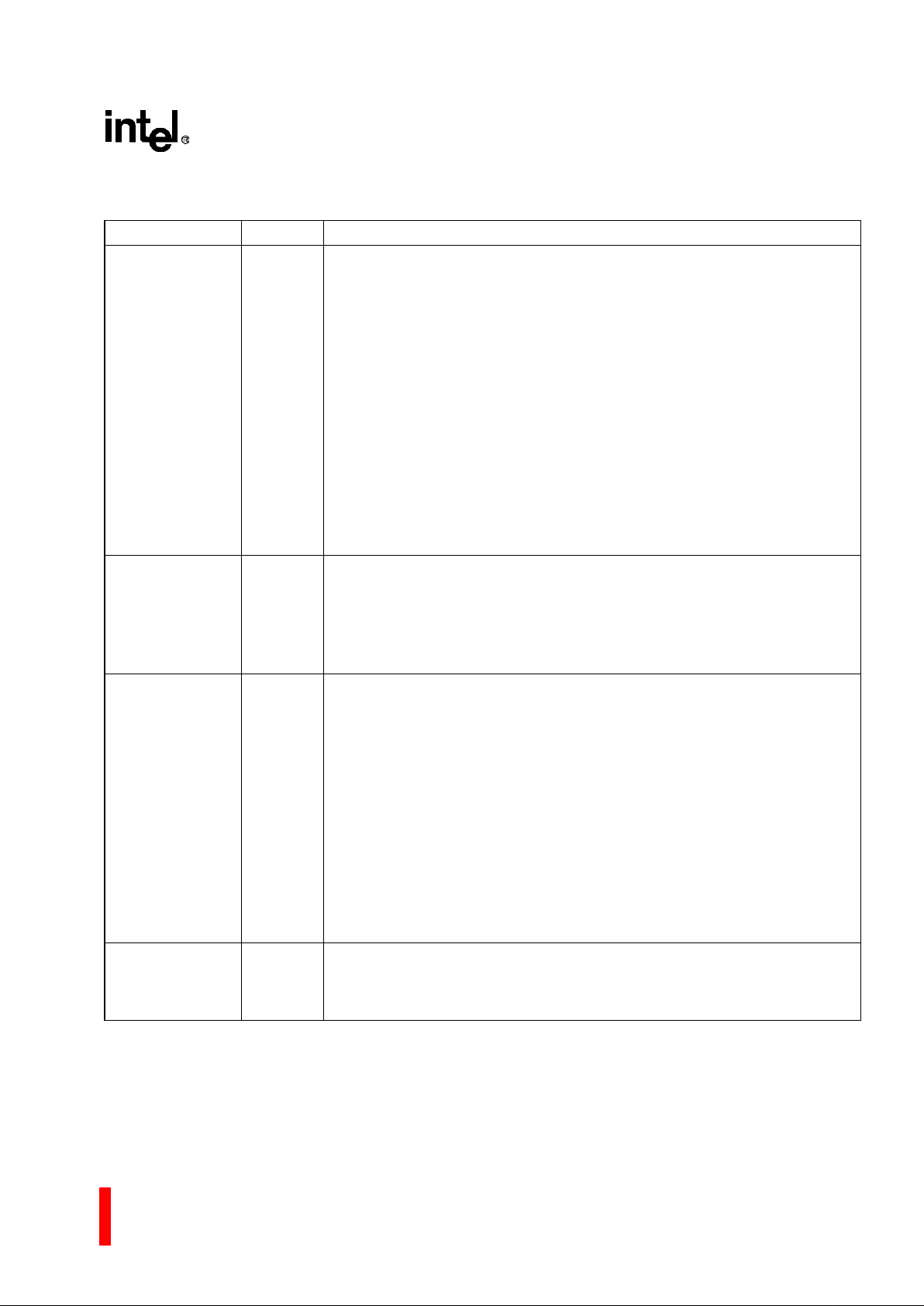

Table 4. Signal Descriptions (Sheet 3 of 5)

NAME TYPE DESCRIPTION

i960® Rx I/O Processor at 3.3 V

12

ADVANCE INFORMATION

HOLD I

S(L)

HOLD is a re qu es t fro m an e xt ern al bu s mast er to ac qu ir e th e b us . When th e

processor receives HOLD and grants bus control to another master, it

asserts HOLDA , floats the address/data and control lines and enters the T

h

state. When HOLD is deasserted, the processor deasserts HOLDA and

enters either the T

i

or Ta state, resuming control of the address/data and

control lines. See Figure 32, HOLD/HOLDA Waveform For Bus Arbitration

(pg. 61).

0 = No Hold Request

1 = Hold Requested

HOLDA O

R(0)

H(1)

P(Q)

HOLD ACKNOWLEDGE indicates to an external bus master that the

processor has relinquished bus control. The processor can grant HOLD

requests and enter the T

h

state and while halted as well as during regular

operation. See Figure 32, HOLD /HOLDA Waveform For Bus Arbitration ( pg.

61).

0 = No Hold Acknowledged

1 = Hold Acknowledged

RDYRCV# I

S(L)

READY/RECOVER is only us ed in systems that use an external memory

con tro ll er ( a nd do no t u se th e 8 09 60 Rx’s memory controller unit). This signal

indicates that data on AD lines can be sampled or removed. When

RDYRC V# i s n ot as sert ed du rin g a T

d

cycle, th e Td cycle extends to the next

cycle by inserting a wait state (T

w

).

0 = Sample Data

1 = Do Not Sample Data

RDYRCV# has an alter nate function durin g the recovery (T

r

) state. The

processor co ntinues to insert recover y states until it samples the signal

HIGH. This gives slow external devices more time to float their buffers

before the processor drives addresses.

0 = Insert Wait States

1 = Recovery Complete

When using the internal memory controller, conn ect thi s signal to V

CC

through a 2.7 KΩ resistor.

W/R# O

R(0)

H(Z)

P(Q)

WRITE/READ specifies during a

T

a

cycle whether the operation is a write or

read. It is latched on-chip and remains valid during T

d

cycles.

0 = Read

1 = Write

WIDTH/

HLTD0

I/O

R(H)

H(Z)

P(Q)

WIDTH denotes the physical memory attributes for a bus transaction in

conjunction with WIDTH/HLTD1/RETRY:

WIDTH/HLTD1/RETRY WIDTH/HLTD0

0 0 8 Bits Wide

0 1 16 Bits Wide

1 0 32 Bits Wide

1 1 Undefined

WIDTH/HLTD0 For proper operation, do not connect this signal to ground.

This signal has a weak internal pullup which is active during reset to ensure

normal operation.

HLTD0 signal name has no function in the 80960Rx; the signal name is

included for 80960JF nami ng convention compatibility.

Table 4. Signal Descriptions (Sheet 4 of 5)

NAME TYPE DESCRIPTION

i960® Rx I/O P rocessor at 3.3 V

ADVANCE INFORMATION 13

WIDTH/

HLTD1/

RETRY

I/O

R(H)

H(Z)

P(Q)

WIDTH denotes the physical memory attributes for a bus tr ansact ion in

conjunction with the WIDTH/HLTD0 signal. Refer to description above.

RETRY is sampled at Primary PCI bus reset to determine when the Primary

PCI interface is disabled. When hi gh, the Primary PCI interface d isables PC I

config ur at io n cy cl es b y s igna li ng a RE TRY u ntil t he Ex tend ed B rid ge Co nt rol

Register’s Configuration Cycle Disable bit is cleared. When low, the Primary

PCI interface allows configurat ion cycles to occur. WIDTH/HLTD1/RETR Y

has a wea k internal pullup whic h is active during reset t o ensure normal

operation when the signal is not connected.

HLTD1 signal name has no function in the 80960Rx; the signal name is

included for 80960JF naming convention compatibility.

Table 5. Power Requirement, Processor Control and Test Signal Descriptions (Sheet 1 of 2)

NAME TYPE DESCRIPTION

FAIL# O

R(0)

H(Q)

FAIL indicates a failure of the processor’s built-in self-test performed during initialization. FAIL# is asserted immediately upon reset and toggles during self-test to

indicate the status of individual tests:

• When self-test passes, the processor deasserts F AIL# and commences operation

from user code.

• When self-test fails, the proces sor asserts FAI L# and th en stop s executi ng. Selftest failing does not caus e the bridge to stop exec ution.

0 = Self Test Failed

1 = Self Test Passed

L_RST# O LOCAL BUS RESET notifies external devices that the local bus has reset.

STEST I

S(L)

SELF TEST enables or disables the processor’s internal self-test feature at initialization. STEST is examined at the end of P_RST#. When STEST is asserted, the

processor performs its internal self-test and the external bus confidence test. When

STEST is deasserted, the processor performs only the external bus confidence test.

0 = Self Test Disabled

1 = Self Test Enabled

TCK I TEST CLOCK is a CPU input that provides the clocking function for IEEE 1149.1

Boundary Scan Testing (JTAG). State information and data ar e clocked into the

processor on the rising edge; data is clocked out of the processor on the falling edge.

TDI I

S(L)

TEST DATA INPUT is the serial input signal for JTAG. TDI is sampled on the rising

edge of TCK, during the SHIFT-IR and SHIFT-DR states of the Test Access Port.

This signal has a weak internal pullup whi c h is active during rese t to ensure normal

operation when the signal is not connected.

TDO O

R(Q)

H(Q)

P(Q)

TEST DATA OUTPUT is the serial output signal for JTAG. TDO is driven on the

falling edge of TCK during the SHIFT-IR and SHIFT-DR states of the Test Access

Port. At other times, TDO floats.

TMS I

S(L)

TEST MODE SELECT is sampled at the rising edge of TCK to select the operation of

the test logic for IEEE 1149.1 Boundary Scan testing. This signal has a weak internal

pullup which is active during reset to ensure norm al operation when the signal is not

connected.

Table 4. Signal Descriptions (Sheet 5 of 5)

NAME TYPE DESCRIPTION

i960® Rx I/O Processor at 3.3 V

14

ADVANCE INFORMATION

TRST# I

A(L)

TEST RESET asynchronously resets the Test Access Port (TAP) controller function

of IEEE1149.1 Boundary Scan testing (JTAG ). When using the Boundary Scan

feature, connect a pulldown resistor (1.5 KΩ) between this signal and V

SS

. Whe n

TAP is not used , this si gnal mu st be connected t o V

SS

; however, no resistor is

required. The signal has a weak internal pullup which must be overcome during reset

to ensure normal operation.

VCC – POWER. Connect to a 3.3 Volt V

CC

board plane.

VCC5 – 5 VOLT REFERENCE VOLTAGE. Input is the referen c e voltage for the 5 V-tolerant

I/O buffers. Connect this signal to +5 V for use with signals which exceed 3.3 V.

When all inputs are from 3.3 V components, connect this signal to 3.3 V.

VSS – GROUND. Connect to a V

SS

board plane.

N.C. – NO CONNECT. Do not make electrical connections to these balls.

VCCPLL3:1 I PLL POWER. For external connection to a 3.3 V V

CC

board plane. Power to PLLs

requires external filtering.

Table 6. Interrupt Unit Signal Descriptions

NAME TYPE DESCRIPTIO N

NMI# I

A(L)

NON-MASKABLE INTERRUPT causes a non-maskable interrupt event to occur.

NMI# is the highest priorit y inte rrupt source an d is level-det ect. When NMI# is

unused, it is recomm ended th at you connect it to V

CC

.

S_INT[A:D]#/

XINT3:0#

I

A(L)

SECONDARY PCI BUS INTERRUPT

1

requests an interrupt. S_INTx# assertion

and deassertion is asynchronous to S_CLK. A device asserts S_INTx# when

requesting attention from its device driver. When S_INTx# is asserted, it remains

asserted until the device driver clears the pending request. S_INTx# Interr upts

are level sensitive.

EXTERNAL INTERRUPT. Ext ern al devi ces us e t h is sign al t o re qu est a n in te rr up t

service. These signals operate in dedicated mode, where each signal is assigned

a dedicated interrupt level.

The S_INT[A:D]#/XINT3:0# signals can be directed as follows:

Sec. PCI Primary PCI 80960 Core Processor

S_INTA#

⇒ P_INTA# or XINT0#

S_INTB#

⇒ P_INTB# or XINT1#

S_INTC#

⇒ P_INTC# or XINT2#

S_INTD#

⇒ P_INTD# or XINT3#

XINT7:4# I

A(L)

EXTERNAL INTERRUPT. Ext ern al devi ces us e t h is sign al t o re qu est a n in te rr up t

service. These signals operate in dedicated mode, where each signal is assigned

a dedicated interrupt level.

NOTE:

1. PCI signal functions are summarized in this data sheet; refer to the

PCI Local Bus Specification

Revision

2.1 for a more complete definition .

Table 5. Power Requirement, Processor Control and Test Signal Descriptions (Sheet 2 of 2)

NAME TYPE DESCRIPTION

i960® Rx I/O P rocessor at 3.3 V

ADVANCE INFORMATION 15

Table 7. PCI Signal Descriptions (Sheet 1 of 3)

NAME TYPE DESCRIPTION

1

P_AD31:0 I/O

K(Q)

R(Z)

PRIMARY PCI ADDRESS/DATA is the primary multiplexed PCI address

and data bus.

P_C/BE3:0# I/O

K(Q)

R(Z)

PRIMARY PCI BUS COMMAND and BYTE ENABLE signals are

multiplexed on the same PCI signals. During an address phase,

P_C/BE3:0# define the bus command. During a data phase, P_C/BE3:0#

are used as byte enabl es.

P_DEVSEL# I/O

R(Z)

PRIMARY PCI BUS DEVICE SELECT is driven by a target agent that has

succe ssfully decoded the add ress. As an input, it indicates whether or not

an agent has been selected.

P_FRAME# I/O

R(Z)

PRIMARY PCI BUS CYCLE FRAME is asserted to indicate the beginning

and duration of an access on th e Primar y PCI bus.

P_GNT# I

R(Z)

PRIMARY PCI BUS GRANT indicates to the agent that access to the bus

has been granted. This is a point-to-point signal.

P_IDSEL I

S(L)

PRIMARY PCI BUS INITIALIZATION DEVICE SELECT selects the

80960Rx durin g a Configurat ion Read or Write command on the primary

PCI b us.

P_INT[A:D]# O

OD

R(Z)

PRIMARY PCI BUS INTERRUPT requests an interrupt. The assertion and

deassertion o f P_INTx# is asynchronous to S_CLK. A device a sserts its

P_INTx# line when requesting attention from its device driver. Once the

P_INTx# signal is asserted, it remains asserted until the device driver

clears the pending request. P_INTx# Interrupts are level sensitive.

P_IRDY# I/O

R(Z)

PRIMARY PCI BUS INITIATOR READY indicates the initiating agent’s

(bus master’s) ability to complete the current data phase of the transaction.

P_LOCK# I

S(L)

PRIMARY PCI BUS LOCK indicates an atomic operation that may require

multiple transactions to complete.

P_PAR I/O

K(Q)

R(Z)

PRIMARY PCI BUS PARITY. This signal ensures even parity across

P_AD31:0 an d P_C /BE3:0. A ll PCI devi c es mus t pr o vi de a par it y si gn al.

P_PERR# I/O

R(Z)

PRIMARY PCI BUS PARITY ERROR is used for reporting data parity

errors during all PCI transa ctions except a special cy cle.

P_REQ# O

K(Q)

R(Z)

PRIMARY PCI BUS REQUEST indicates to the arbiter that this agent

desires use of the bus. This is a point to point signal.

NOTE:

1. PCI signal functions are summarized in this data sheet; refer to the

PCI Local Bus Specification

Revision

2.1 for a more complete definition.

Loading...

Loading...