E

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

© INTEL CORPORATION 1997 April 1997 Order Number: 290562-001

Supported Kits for both Pentium® and

Pentium

®

II Microprocessors

82430TX ISA Kit

82440LX ISA/DP Kit

Multifunction PCI to ISA Bridge

Supports PCI at 30 MHz and 33 MHz

Supports PCI Rev 2.1 Specification

Supports Full ISA or Extended I/O

(EIO) Bus

Supports Full Positive Decode or

Subtractive Decode of PCI

Supports ISA and EIO at 1/4 of PCI

Frequency

Supports both Mobile and Desktop

Deep Green Environments

3.3V Operation with 5V Tolerant

Buffers

Ultra-low Power for Mobile

Environments Support

Power-On Suspend, Suspend to

RAM, Suspend to Disk, and SoftOFF System States

All Registers Readable and

Restorable for Proper Resume

from 0.V Suspend

Power Management Logic

Global and Local Device

Management

Suspend and Resume Logic

Supports Thermal Alarm

Support for External

Microcontroller

Full Support for Advanced

Configuration and Power Interface

(ACPI) Revision 1.0 Specification

and OS Directed Power

Management

Integrated IDE Controller

Independent Timing of up to

4 Drives

PIO Mode 4 and Bus Master IDE

Transfers up to 14 Mbytes/sec

Supports “Ultra DMA/33”

Synchronous DMA Mode Transfers

up to 33 Mbytes/sec

Integrated 16 x 32-bit Buffer for IDE

PCI Burst Transfers

Supports Glue-less “Swap-Bay”

Option with Full Electrical Isolation

Enhanced DMA Controller

Two 82C37 DMA Controllers

Supports PCI DMA with 3 PC/PCI

Channels and Distributed DMA

Protocols (Simultaneously)

Fast Type-F DMA for Reduced PCI

Bus Usage

Interrupt Controller Based on Two

82C59

15 Interrupt Support

Independently Programmable for

Edge/Level Sensitivity

Supports Optional I/O APIC

Serial Interrupt Input

Timers Based on 82C54

System Timer, Refresh Request,

Speaker Tone Output

USB

Two USB 1.0 Ports for Serial

Transfers at 12 or 1.5 Mbit/sec

Supports Legacy Keyboard and

Mouse Software with USB-based

Keyboard and Mouse

Supports UHCI Design Guide

SMBus

Host Interface Allows CPU to

Communicate Via SMBus

Slave Interface Allows External

SMBus Master to Control Resume

Events

Real-Time Clock

256-byte Battery-Back CMOS SRAM

Includes Date Alarm

Two 8-byte Lockout Ranges

Microsoft Win95* Compliant

324 mBGA Package

82371AB PCI-TO-ISA / IDE

XCELERATOR (PIIX4)

82371AB (PIIX4) E

2

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

The 82371AB PCI ISA IDE Xcelerator (PIIX4) is a multi-function PCI device implementing a PCI-to-ISA bridge

function, a PCI IDE function, a Universal Serial Bus host/hub function, and an Enhanced Power Management

function. As a PCI-to-ISA bridge, PIIX4 integrates many common I/O functions found in ISA-based PC

systems—two 82C37 DMA Controllers, two 82C59 Interrupt Controllers, an 82C54 Timer/Counter, and a Real

Time Clock. In addition to compatible transfers, each DMA channel supports Type F transfers. PIIX4 also

contains full support for both PC/PCI and Distributed DMA protocols implementing PCI-based DMA. The

Interrupt Controller has Edge or Level sensitive programmable inputs and fully supports the use of an external

I/O Advanced Programmable Interrupt Controller (APIC) and Serial Interrupts. Chip select decoding is provided

for BIOS, Real Time Clock, Keyboard Controller, second external microcontroller, as well as two Programmable

Chip Selects. PIIX4 provides full Plug and Play compatibility. PIIX4 can be configured as a Subtractive Decode

bridge or as a Positive Decode bridge. This allows the use of a subtractive decode PCI-to-PCI bridge such as

the Intel 380FB PCIset which implements a PCI/ISA docking station environment.

PIIX4 supports two IDE connectors for up to four IDE devices providing an interface for IDE hard disks and CD

ROMs. Up to four IDE devices can be supported in Bus Master mode. PIIX4 contains support for “Ultra DMA/33”

synchronous DMA compatible devices.

PIIX4 contains a Universal Serial Bus (USB) Host Controller that is Universal Host Controller Interface (UHCI)

compatible. The Host Controller’s root hub has two programmable USB ports.

PIIX4 supports Enhanced Power Management, including full Clock Control, Device Management for up to

14 devices, and Suspend and Resume logic with Power On Suspend, Suspend to RAM or Suspend to Disk. It

fully supports Operating System Directed Power Management via the Advanced Configuration and Power

Interface (ACPI) specification. PIIX4 integrates both a System Management Bus (SMBus) Host and Slave

interface for serial communication with other devices.

Information in this document is provided in conjunction with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Except as provided in

Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express

or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

The 82371AB PIIX4 may contain design defects or errors known as errata. Current characterized errata are available

on request.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this

specification. Intel does not warrant or represent that such use will not infringe such rights.

I2C is a two-wire communication bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was

developed by Intel. Implementation of the I2C bus/protocol or the SMBus bus/protocol may require licenses from various

entities, including Philips Electronics N.V. and North American Philips Corporation.

Third-party brands and names are the property of their respective owners.

E 82371AB (PIIX4)

3

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

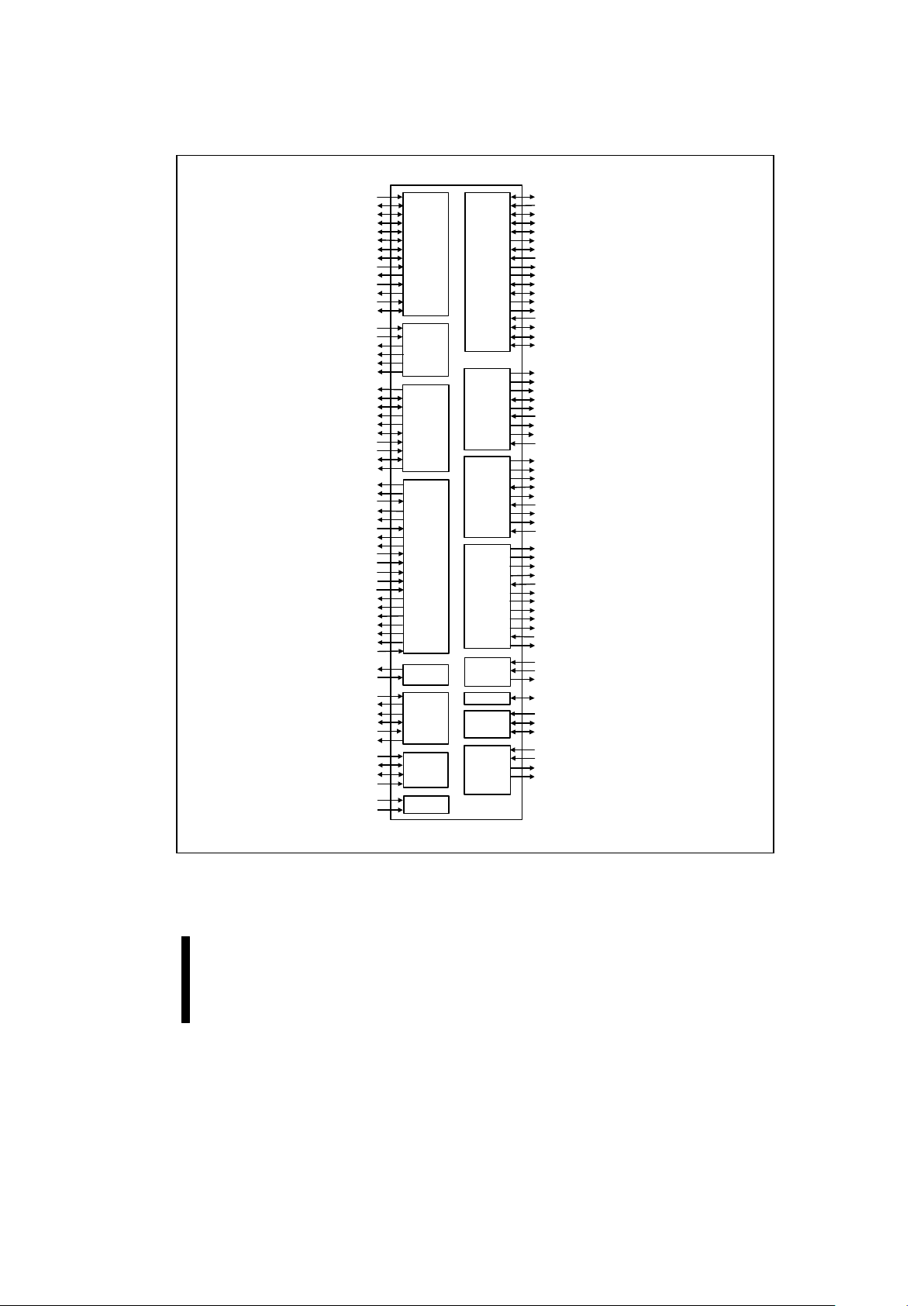

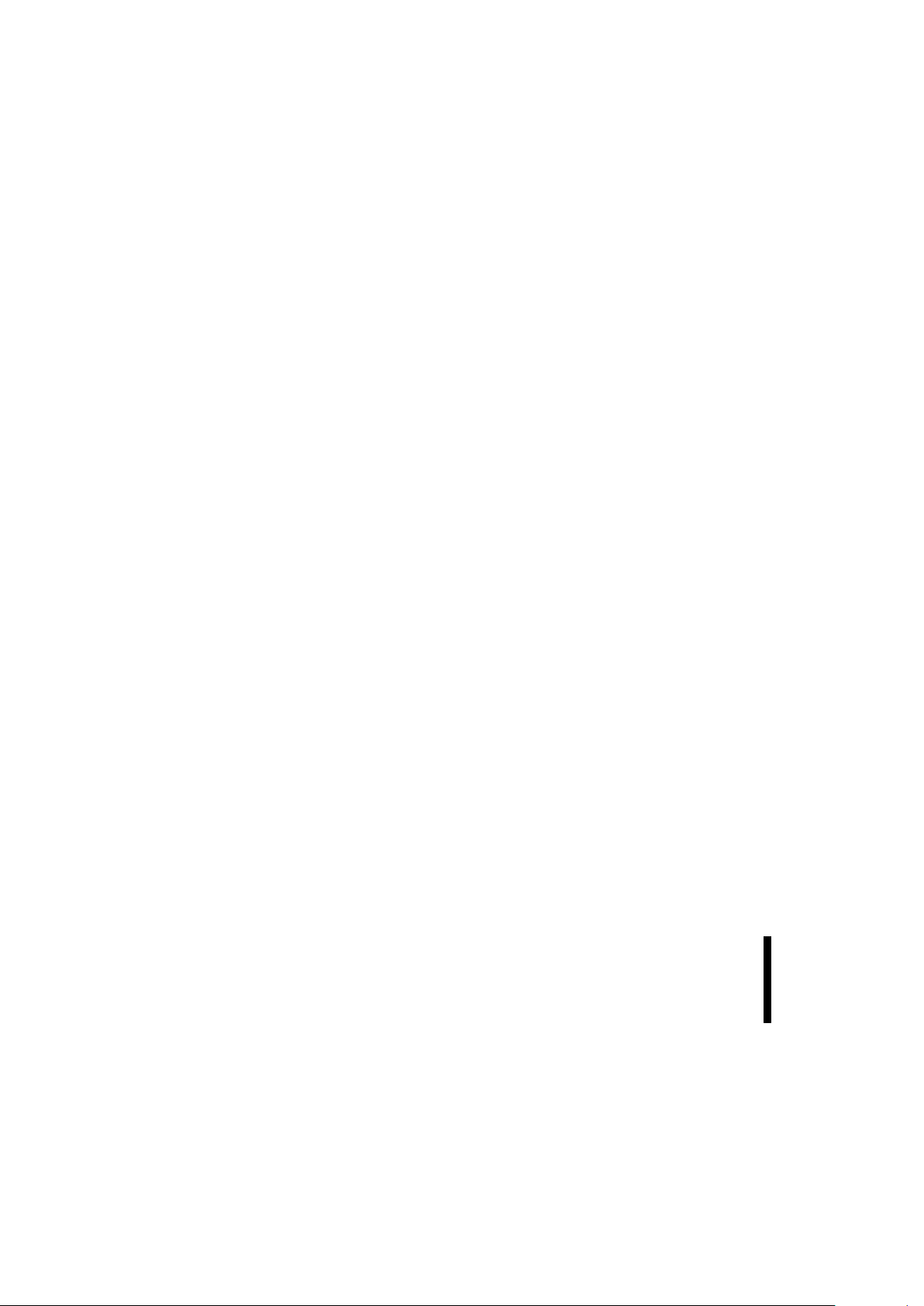

PCICL

K

AD[31:0]

C/BE[3:0]#

FRAME#

TRDY#

IRDY#

STOP#

DEVSEL#

SERR#

PAR

IDSEL

PHOLD#

PHLKA#

CLKR

UN#

RCIN#

PWROK

CPURST

RSTDRV

INIT

PCIRST#

IRQ0//GPO14

IRQ8#/GPI6

IRQ12/M

INTR

NMI

IRQ[15,14,11:9,7:3,1]

SERIRQ/GPI7

PRIQ[A:C]

PIRQD

IRQ9OUT#/GPO29

SMI#

STPCLK#

EXTSMI#

SLP#

SUSCLK

BATLOW#/GPI9

THRM#/GPI8

LID//GPI10

RI#/GPI12

RSMRST#

PWRBTN#

SUSA#

SUSB#/GPO15

SUSC#/GPO16

ZZ/GPO19

PCIREQ[D:A]#

SPKR

OSC

DREQ[7:5,3:0]

DACK[7:5,3:0]#

TC

REFRESH#

REQ[A:C]#/GPI[2:4]

GNT[A:C]#/GPO[9:11]

CLK48

USBPO±

USBP1±

OC[1:0]#

CONFIG[2:1]

TEST#

PCI Bus

Interface

ISA Bus

Interface

System

Reset

Interrupt

Primary

IDE

Interface

Secondary

IDE

Interface

System

Power

Mgmt.

X-Bus

Support

Logic

Timers/

Counters

DMA

I/O APIC

Support

Logic

Universal

Serial

Bus

RTC

SMBUS

General

Purpose

Inputs

and

Outputs

Test

SD[15:0]

IOCS16#

MEMCS16#

MEMR#

MEMW#

AEN

IOCHRDY

IOCHK#/GPI0

SYSCLK

BALE

IOR#

IOW#

SMEMR#

SMEMW#

ZEROWS#

SA[19:0]

LA[23:17]/GPO[7:1]

SBHE#

PDCS1#

PDCS3#

PDA[2:0]

PDD[15:0]

PDDACK#

PDDREQ

PDIOIR#

PDIOW#

PIORDY

SDCS1#

SDCS3#

SDA[2:0]

SDD[15:0]

SDDACK#

SDDREQ

SDIOR#

SDIOW#

SIORDY

PCS[1:0]#

XDIR#/GPO22

XOE#/GPO23

RTCALE/GPO25

FERR#

IGNNE#

BIOSCS#

RTCCS#/GPO24

KBCCS#/GPO26

A20M#

A20GATE

MCCS#

APICCS#/GPO13

APICACK#/GPO12

APCIREQ#/GPI5

RTCX[2:1]

SMBALERT#

SMBCLK

SMBDATA

GPI[21:13,1]

GPI[12:2,0] (Multiplexed)

GPO[30,28:27,8,0]

GPO[29,26:9,7:1] (Multiplexed)

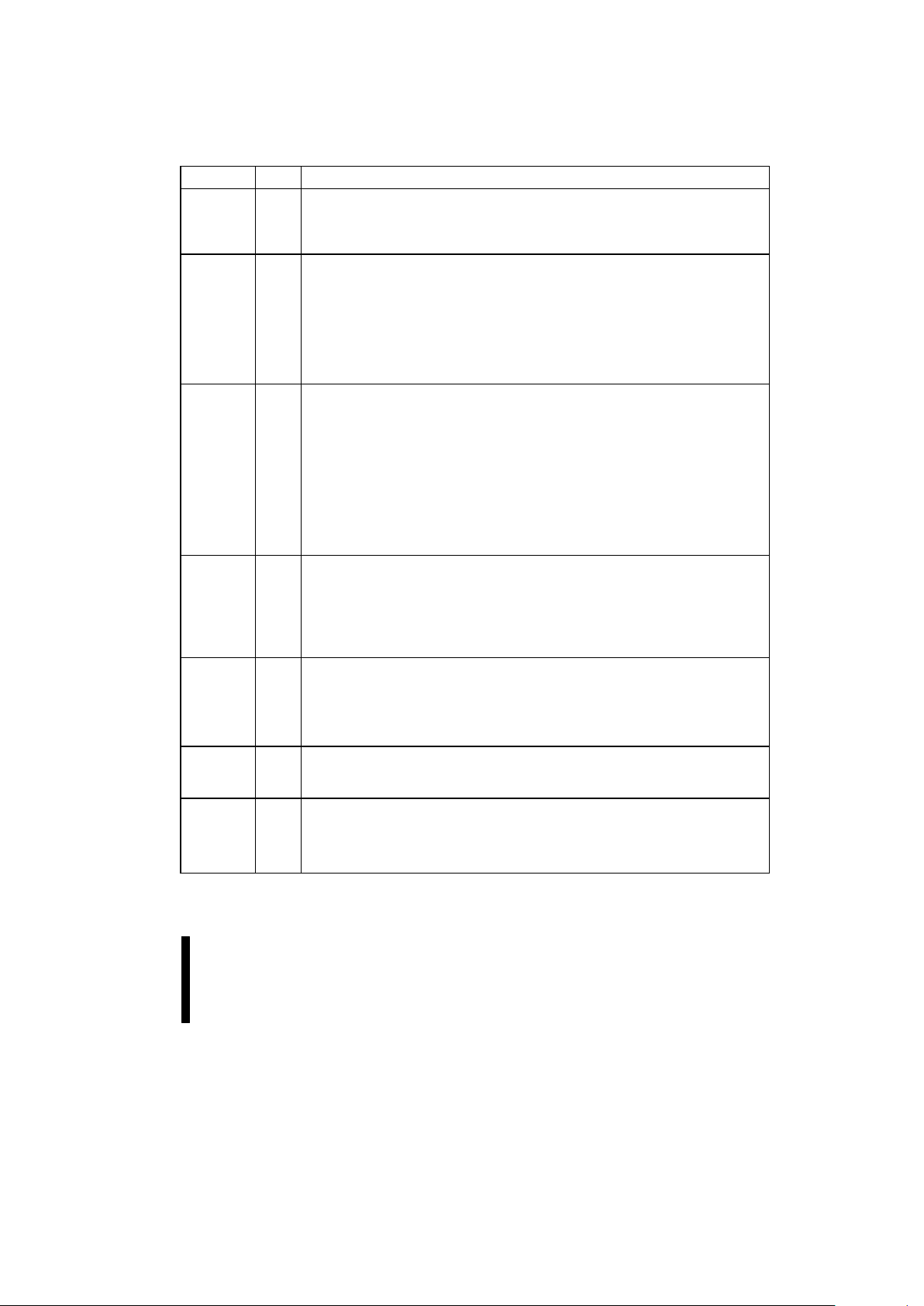

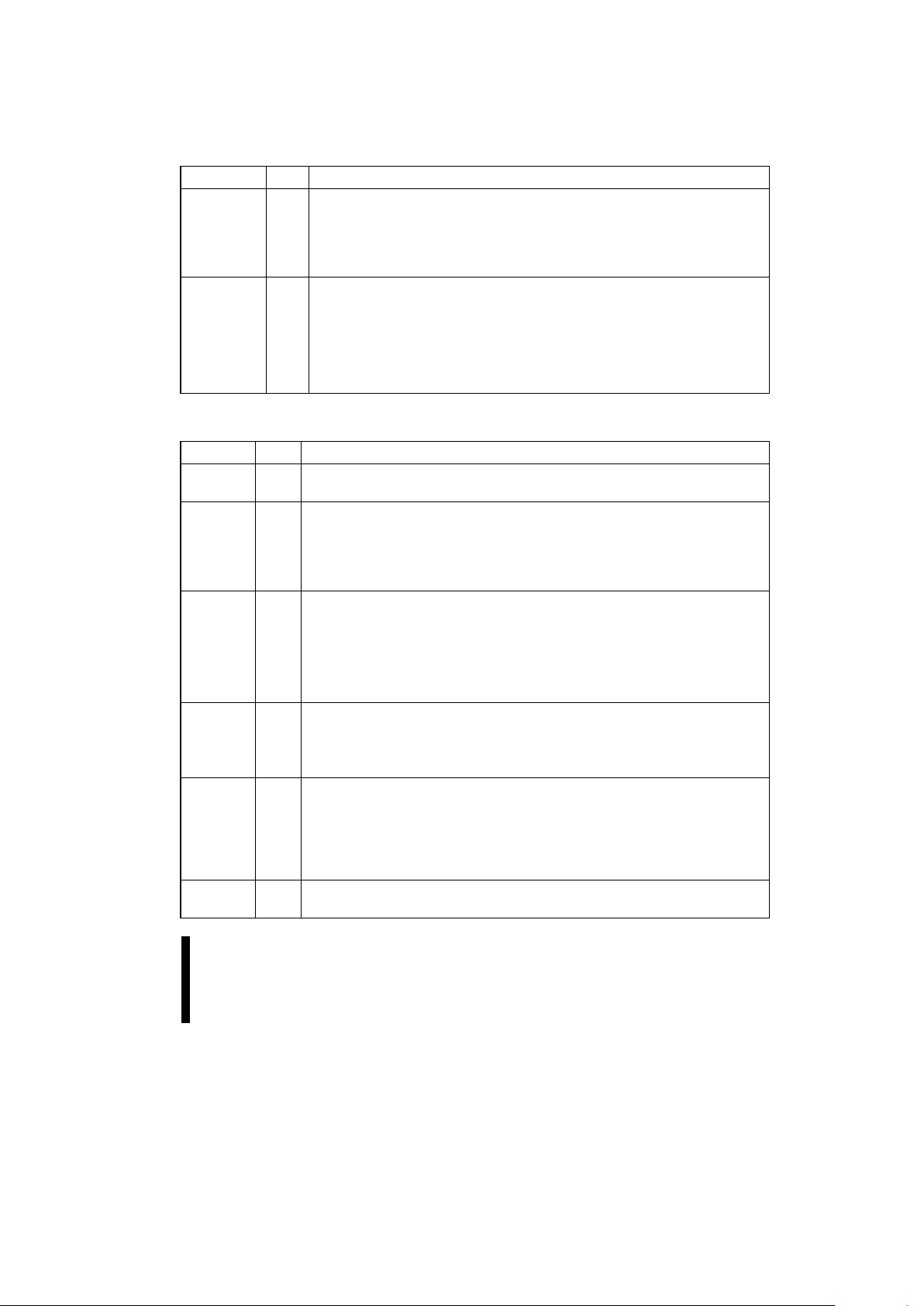

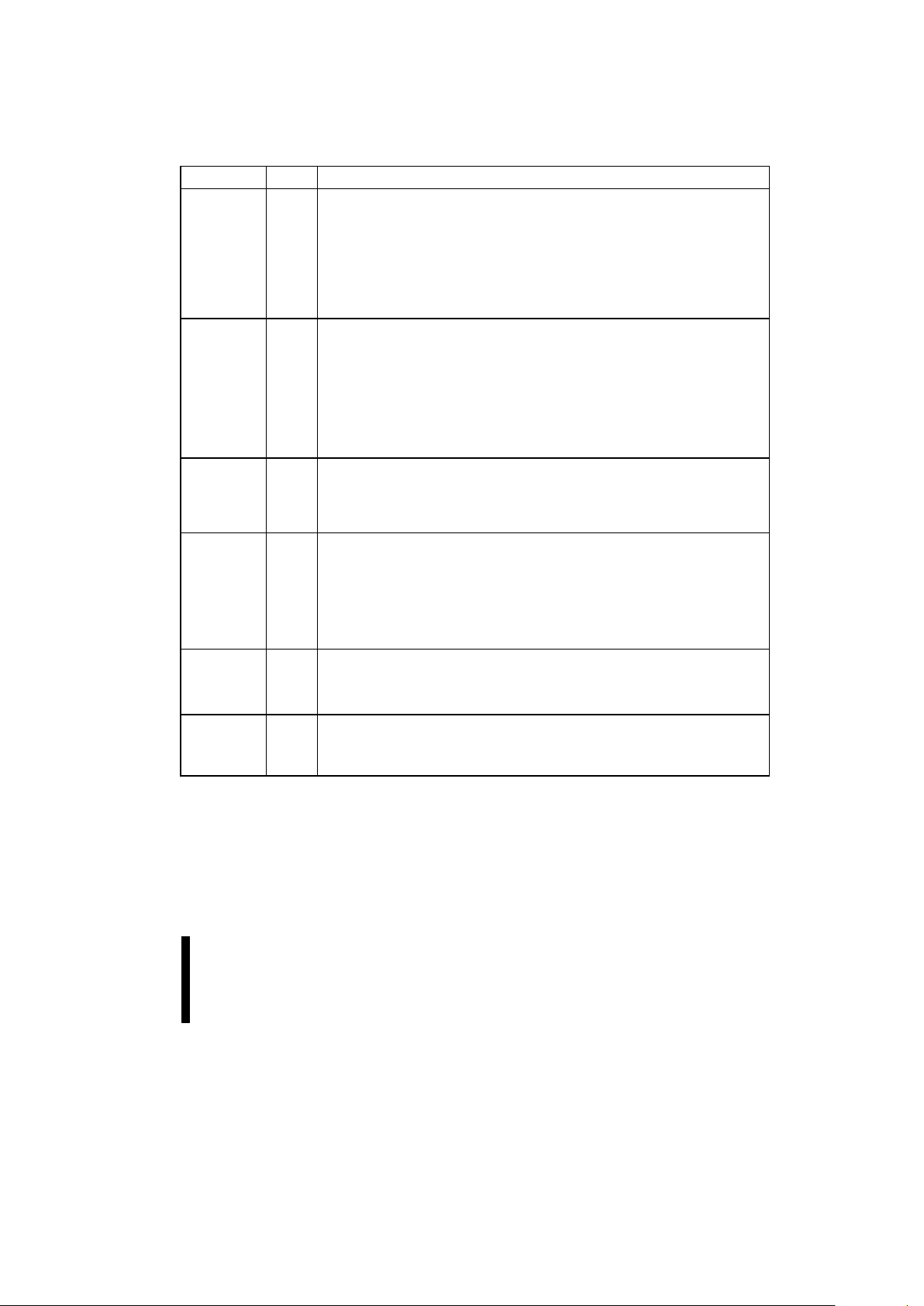

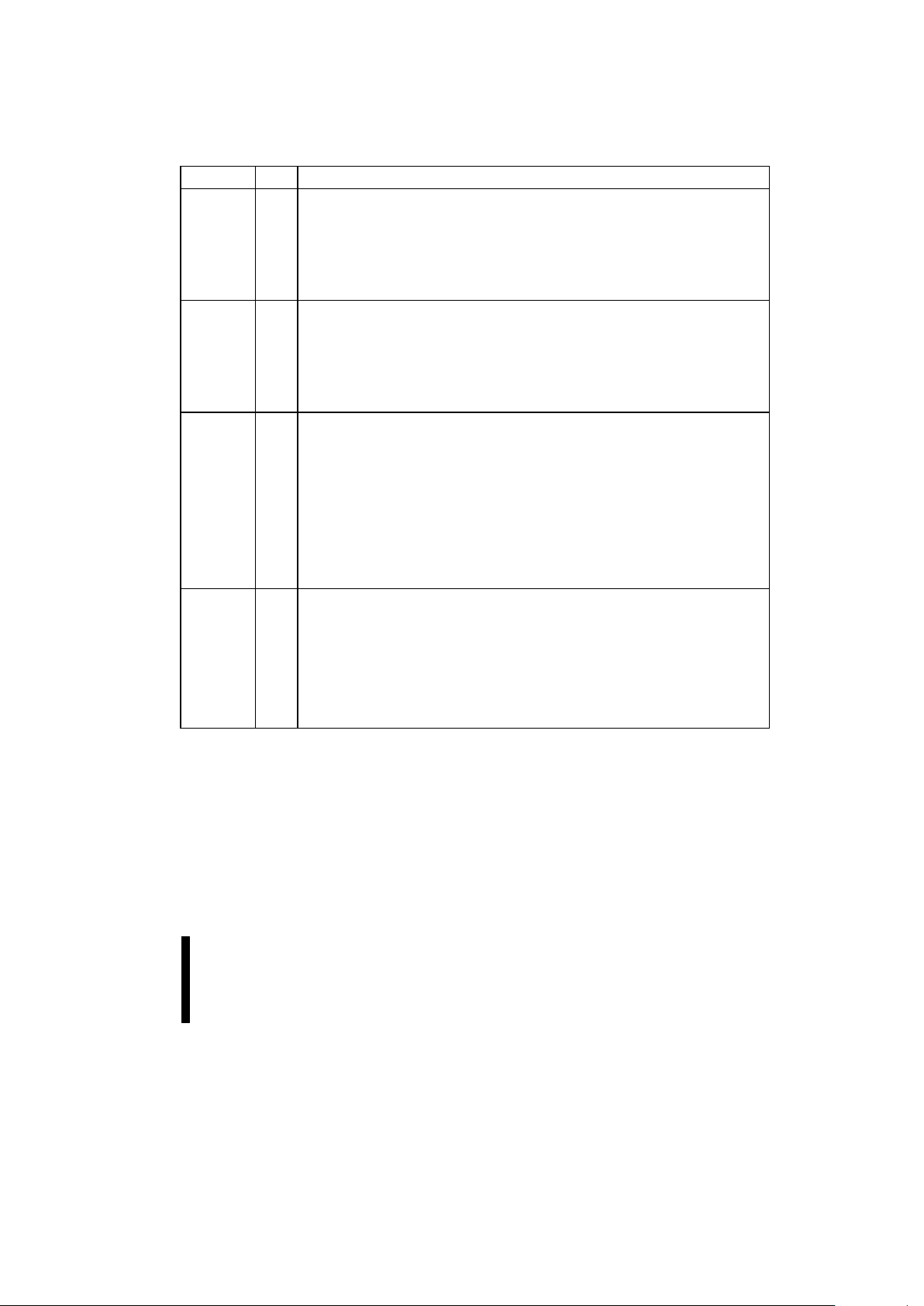

Pix4_blk

Simplified Block Diagram

82371AB (PIIX4) E

4

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

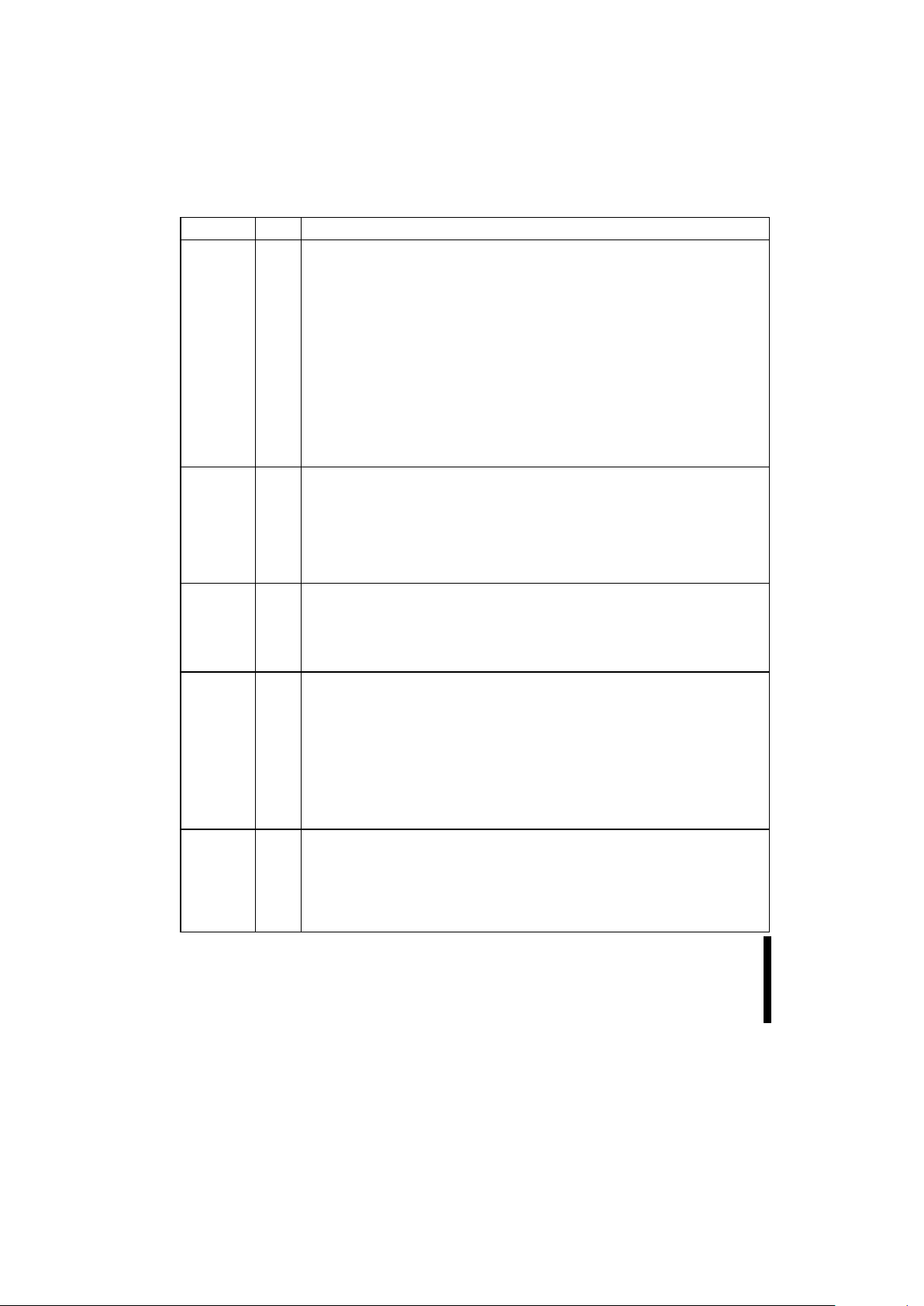

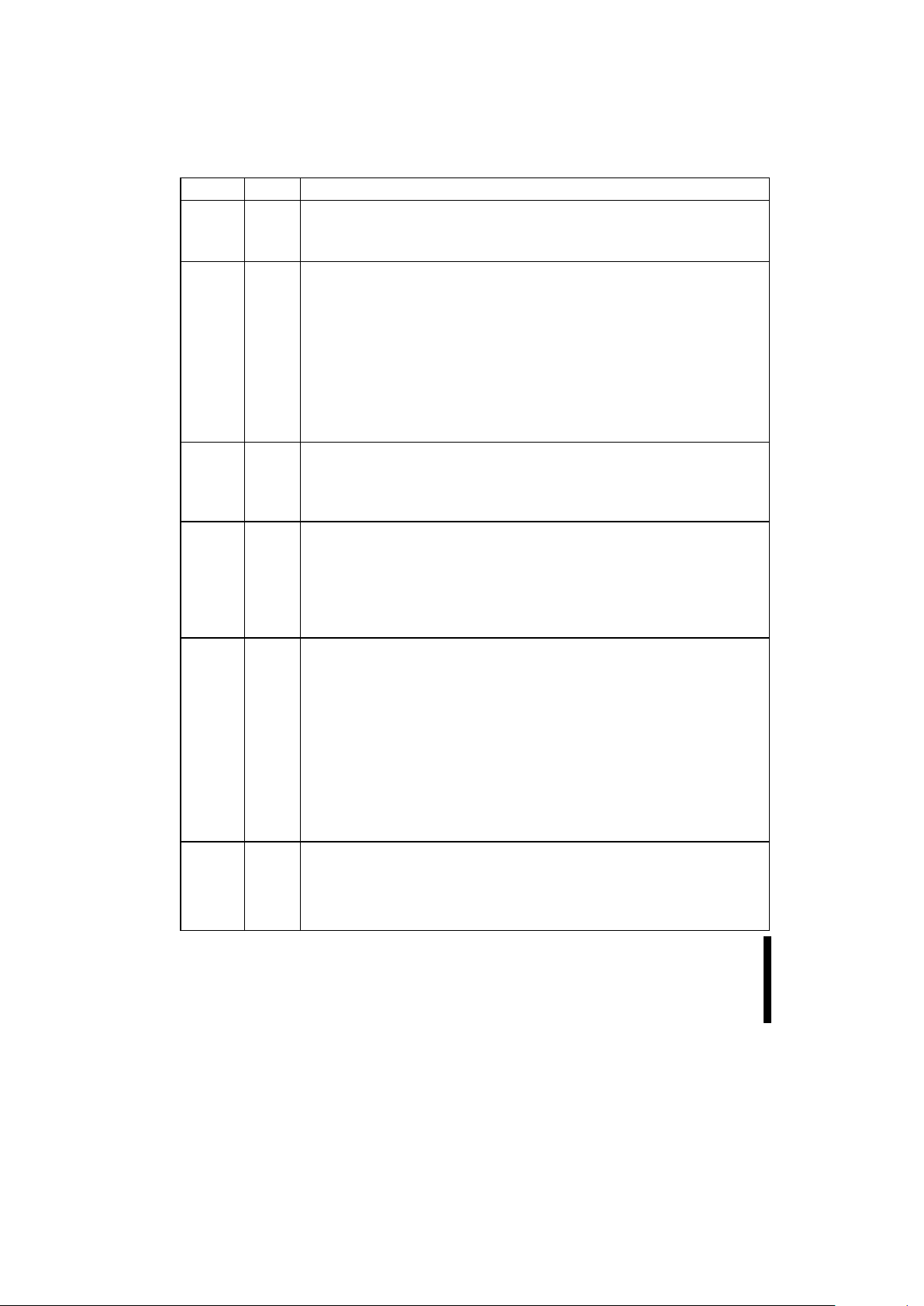

CONTENTS

PAGE

1.0. ARCHITECTURAL OVERVIEW....................................................................................................................12

2.0. SIGNAL DESCRIPTION................................................................................................................................15

2.1. PIIX4 Signals ..............................................................................................................................................16

2.1.1. PCI Bus Interface.................................................................................................................................16

2.1.2. ISA Bus Interface.................................................................................................................................18

2.1.3. X-Bus Interface....................................................................................................................................21

2.1.4. DMA Signals........................................................................................................................................23

2.1.5. Interrupt Controller/APIC Signals.........................................................................................................24

2.1.6. CPU Interface Signals .........................................................................................................................26

2.1.7. Clocking Signals..................................................................................................................................28

2.1.8. IDE Signals..........................................................................................................................................28

2.1.9. Universal Serial Bus Signals ...............................................................................................................33

2.1.10. Power Management Signals..............................................................................................................33

2.1.11. General Purpose Input and Output Signals.......................................................................................35

2.1.12. Other System and Test Signals.........................................................................................................39

2.1.13. Power and Ground Pins.....................................................................................................................39

2.2. Power Planes..............................................................................................................................................40

2.3. Power Sequencing Requirements..............................................................................................................41

3.0. REGISTER ADDRESS SPACE.....................................................................................................................42

3.1. PCI/ISA Bridge Configuration.....................................................................................................................42

3.1.1. PCI Configuration Registers (Function 0)............................................................................................43

3.1.2. IO Space Registers .............................................................................................................................44

3.2. IDE Configuration........................................................................................................................................47

3.2.1. PCI Configuration Registers (Function 1)............................................................................................47

3.2.2. IO Space Registers .............................................................................................................................48

3.3. Universal Serial Bus (USB) Configuration..................................................................................................48

3.3.1. PCI Configuration Registers (Function 2)............................................................................................48

3.3.2. IO Space Registers .............................................................................................................................49

3.4. Power Management Configuration .............................................................................................................50

3.4.1. IO Space Registers .............................................................................................................................51

4.0. PCI TO ISA/EIO BRIDGE REGISTER DESCRIPTIONS..............................................................................53

4.1. PCI to ISA/EIO Bridge PCI Configuration Space Registers (PCI Function 0)............................................53

4.1.1. VID—Vendor Identification Register (Function 0)................................................................................53

4.1.2. DID—Device Identification Register (Function 0)................................................................................53

4.1.3. PCICMD—PCI Command Register (Function 0) ................................................................................54

4.1.4. PCISTS—PCI Device Status Register (Function 0)............................................................................55

4.1.5. RID—Revision Identification Register (Function 0).............................................................................55

E 82371AB (PIIX4)

5

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

4.1.6. CLASSC—Class Code Register (Function 0).....................................................................................56

4.1.7. HEDT—Header Type Register (Function 0)........................................................................................56

4.1.8. IORT—ISA I/O Recovery Timer Register (Function 0).......................................................................56

4.1.9. XBCS—X-Bus Chip Select Register (Function 0)...............................................................................57

4.1.10. PIRQRC[A:D]—PIRQX Route Control Registers (Function 0) .........................................................59

4.1.11. SERIRQC—Serial IRQ Control Register (Function 0) ......................................................................59

4.1.12. TOM—Top of Memory Register (Function 0)....................................................................................60

4.1.13. MSTAT—Miscellaneous Status Register (Function 0)......................................................................61

4.1.14. MBDMA[1:0]—Motherboard Device DMA Control Registers (Function 0)........................................61

4.1.15. APICBASE—APIC Base Address Relocation Register (Function 0)................................................62

4.1.16. DLC—Deterministic Latency Control Register (Function 0)..............................................................62

4.1.17. PDMACFG—PCI DMA Configuration Register (Function 0).............................................................63

4.1.18. DDMABP—Distributed DMA Slave Base Pointer Registers (Function 0).........................................64

4.1.19. GENCFG—General Configuration Register (Function 0) .................................................................65

4.1.20. RTCCFG—Real Time Clock Configuration Register (Function 0)....................................................67

4.2. PCI to ISA/EIO Bridge IO Space Registers (IO) ........................................................................................68

4.2.1. DMA Registers.....................................................................................................................................68

4.2.1.1. DCOM—DMA Command Register (IO)........................................................................................68

4.2.1.2. DCM—DMA Channel Mode Register (IO)....................................................................................69

4.2.1.3. DR—DMA Request Register (IO).................................................................................................70

4.2.1.4. WSMB—Write Single Mask Bit (IO) .............................................................................................70

4.2.1.5. RWAMB—Read/Write All Mask Bits (IO).....................................................................................71

4.2.1.6. DS—DMA Status Register (IO)....................................................................................................71

4.2.1.7. DBADDR—DMA Base and Current Address Registers (IO).......................................................72

4.2.1.8. DBCNT—DMA Base and Current Count Registers (IO)..............................................................72

4.2.1.9. DLPAGE—DMA Low Page Registers (IO)...................................................................................73

4.2.1.10. DCBP—DMA Clear Byte Pointer Register (IO)..........................................................................73

4.2.1.11. DMC—DMA Master Clear Register (IO) ....................................................................................73

4.2.1.12. DCLM—DMA Clear Mask Register (IO).....................................................................................74

4.2.2. Interrupt Controller Registers...............................................................................................................74

4.2.2.1. ICW1—Initialization Command Word 1 Register (IO) ..................................................................74

4.2.2.2. ICW2—Initialization Command Word 2 Register (IO) ..................................................................75

4.2.2.3. ICW3—Initialization Command Word 3 Register (IO) ..................................................................75

4.2.2.4. ICW3—Initialization Command Word 3 Register (IO) ..................................................................76

4.2.2.5. ICW4—Initialization Command Word 4 Register (IO) ..................................................................76

4.2.2.6. OCW1—Operational Control Word 1 Register (IO)......................................................................77

4.2.2.7. OCW2—Operational Control Word 2 Register (IO)......................................................................77

4.2.2.8. OCW3— Operational Control Word 3 Register (IO).....................................................................78

4.2.2.9. ELCR1—Edge/Level Control Register (IO)..................................................................................79

4.2.2.10. ELCR2—Edge/Level Control Register (IO)................................................................................79

4.2.3. Counter/Timer Registers......................................................................................................................80

4.2.3.1. TCW—Timer Control Word Register (IO).....................................................................................80

4.2.3.2. TMRSTS—Timer Status Registers (IO).......................................................................................82

82371AB (PIIX4) E

6

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

4.2.3.3. TMRCNT—Timer Count Registers (IO) .......................................................................................82

4.2.4. NMI Registers......................................................................................................................................83

4.2.4.1. NMISC—NMI Status and Control Register (IO)...........................................................................83

4.2.4.2. NMIEN—NMI Enable Register (Shared with Real-Time Clock Index Register) (IO)...................84

4.2.5. Real Time Clock Registers..................................................................................................................84

4.2.5.1. RTCI—Real-Time Clock Index Register (Shared with NMI Enable Register) (IO) ......................84

4.2.5.2. RTCD—Real-Time Clock Data Register (IO)...............................................................................85

4.2.5.3. RTCEI—Real-Time Clock Extended Index Register (IO).............................................................85

4.2.5.4. RTCED—Real-Time Clock Extended Data Register (IO)............................................................85

4.2.6. Advanced Power Management (APM) Registers................................................................................86

4.2.6.1. APMC—Advanced Power Management Control Port (IO)...........................................................86

4.2.6.2. APMS—Advanced Power Management Status Port (IO) ............................................................86

4.2.7. X-Bus, Coprocessor, and Reset Registers .........................................................................................86

4.2.7.1. RIRQ—Reset X-Bus IRQ12/M and IRQ1 Register (IO)...............................................................86

4.2.7.2. P92—Port 92 Register (IO)...........................................................................................................87

4.2.7.3. CERR—Coprocessor Error Register (IO) ....................................................................................87

4.2.7.4. RC—Reset Control Register (IO).................................................................................................88

5.0. IDE CONTROLLER REGISTER DESCRIPTIONS (PCI FUNCTION 1) ......................................................89

5.1. IDE Controller PCI Configuration Registers (PCI Function 1)....................................................................89

5.1.1. VID—Vendor Identification Register (Function 1)................................................................................89

5.1.2. DID—Device Identification Register (Function 1)................................................................................89

5.1.3. PCICMD—PCI Command Register (Function 1) ................................................................................89

5.1.4. PCISTS—PCI Device Status Register (Function 1)............................................................................90

5.1.5. RID—Revision Identification Register (Function 1).............................................................................91

5.1.6. CLASSC—Class Code Register (Function 1).....................................................................................91

5.1.7. MLT—Master Latency Timer Register (Function 1)............................................................................91

5.1.8. HEDT—Header Type Register (Function 1)........................................................................................92

5.1.9. BMIBA—Bus Master Interface Base Address Register (Function 1)..................................................92

5.1.10. IDETIM—IDE Timing Register (Function 1) ......................................................................................93

5.1.11. SIDETIM—Slave IDE Timing Register (Function 1)..........................................................................95

5.1.12. UDMACTL—Ultra DMA/33 Control Register (Function 1) ................................................................96

5.1.13. UDMATIM—Ultra DMA/33 Timing Register (Function 1)..................................................................96

5.2. IDE Controller IO Space Registers.............................................................................................................99

5.2.1. BMICX—Bus Master IDE Command Register (IO).............................................................................99

5.2.2. BMISX—Bus Master IDE Status Register (IO) .................................................................................100

5.2.3. BMIDTPX—Bus Master IDE Descriptor Table Pointer Register (IO)................................................101

6.0. USB HOST CONTROLLER REGISTER DESCRIPTIONS (PCI FUNCTION 2)........................................102

6.1. USB Host Controller PCI Configuration Registers (PCI Function 2)........................................................102

6.1.1. VID—Vendor Identification Register (Function 2)..............................................................................102

6.1.2. DID—Device Identification Register (Function 2)..............................................................................102

6.1.3. PCICMD—PCI Command Register (Function 2) ..............................................................................103

6.1.4. PCISTS—PCI Device Status Register (Function 2)..........................................................................103

E 82371AB (PIIX4)

7

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

6.1.5. RID—Revision Identification Register (Function 2)...........................................................................104

6.1.6. CLASSC—Class Code Register (Function 2)...................................................................................104

6.1.7. MLT—Master Latency Timer Register (Function 2)..........................................................................105

6.1.8. HEDT—Header Type Register (Function 2)......................................................................................105

6.1.9. INTLN—Interrupt Line Register (Function 2).....................................................................................105

6.1.10. INTPN—Interrupt Pin (Function 2) ..................................................................................................106

6.1.11. SBRNUM—Serial Bus Release Number (Function 2) ....................................................................106

6.1.12. LEGSUP—Legacy Support Register (Function 2)..........................................................................107

6.1.13. USBBA—USB I/O Space Base Address Register (Function 2)......................................................108

6.1.14. MISCSUP—Miscellaneous Support Register (Function 2).............................................................109

6.2. USB Host Controller IO Space Registers.................................................................................................109

6.2.1. USBCMD—USB Command Register (IO) ........................................................................................109

6.2.2. USBSTS—USB Status Register (IO)................................................................................................111

6.2.3. USBINTR—USB Interrupt Enable Register (IO)...............................................................................112

6.2.4. FRNUM—Frame Number Register (IO)............................................................................................113

6.2.5. FLBASEADD—Frame List Base Address Register (IO)...................................................................113

6.2.6. SOFMOD—Start Of Frame (SOF) Modify Register (IO)...................................................................114

6.2.7. PORTSC—Port Status and Control Register (IO).............................................................................115

7.0. POWER MANAGEMENT REGISTER DESCRIPTIONS............................................................................117

7.1. Power Management PCI Configuration Registers (PCI Function 3) ........................................................117

7.1.1. VID—Vendor Identification Register (Function 3)..............................................................................117

7.1.2. DID—Device Identification Register (Function 3)..............................................................................117

7.1.3. PCICMD—PCI Command Register (Function 3) ..............................................................................117

7.1.4. PCISTS—PCI Device Status Register (Function 3)..........................................................................118

7.1.5. RID—Revision Identification Register (Function 3)...........................................................................119

7.1.6. CLASSC—Class Code Register (Function 3)...................................................................................119

7.1.7. HEDT—Header Type Register (Function 3)......................................................................................119

7.1.8. INTLN—Interrupt Line Register (Function 3).....................................................................................120

7.1.9. INTPN—Interrupt Pin (Function 3) ....................................................................................................120

7.1.10. PMBA—Power Management Base Address (Function 3)...............................................................120

7.1.11. CNTA—Count A (Function 3)..........................................................................................................121

7.1.12. CNTB—Count B (Function 3)..........................................................................................................121

7.1.13. GPICTL—General Purpose Input Control (Function 3)...................................................................123

7.1.14. DEVRESD—Device Resource D (Function 3)................................................................................123

7.1.15. DEVACTA—Device Activity A (Function 3) ....................................................................................125

7.1.16. DEVACTB—Device Activity B (Function 3) ....................................................................................126

7.1.17. DEVRESA—Device Resource A (Function 3)................................................................................127

7.1.18. DEVRESB—Device Resource B (Function 3)................................................................................129

7.1.19. DEVRESC—Device Resource C (Function 3)................................................................................130

7.1.20. DEVRESE—Device Resource E (Function 3)................................................................................131

7.1.21. DEVRESF—Device Resource F (Function 3).................................................................................131

7.1.22. DEVRESG—Device Resource G (Function 3) ...............................................................................132

82371AB (PIIX4) E

8

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

7.1.23. DEVRESH—Device Resource H (Function 3)................................................................................133

7.1.24. DEVRESI—Device Resource I (Function 3)...................................................................................133

7.1.25. DEVRESJ

Device Resource J (Function 3) .................................................................................134

7.1.26. PMREGMISC

Miscellaneous Power Management (Function 3)..................................................134

7.1.27. SMBBA—SMBUS Base Address (Function 3)................................................................................135

7.1.28. SMBHSTCFG

SMBUS Host Configuration (Function 3)..............................................................135

7.1.29. SMBSLVC

SMBUS Slave Command (Function 3).......................................................................135

7.1.30. SMBSHDW1

SMBUS Slave Shadow Port 1 (Function 3)............................................................136

7.1.31. SMBSHDW2

SMBUS Slave Shadow Port 2 (Function 3)............................................................136

7.1.32. SMBREV

SMBUS Revision Identification (Function 3) ................................................................136

7.2. Power Management IO Space Registers.................................................................................................137

7.2.1. PMSTS

Power Management Status Register (IO) .........................................................................137

7.2.2. PMEN

Power Management Resume Enable Register (IO)............................................................138

7.2.3. PMCNTRL

Power Management Control Register (IO)...................................................................138

7.2.4. PMTMR

Power Management Timer Register (IO)..........................................................................139

7.2.5. GPSTS

General Purpose Status Register (IO) ..............................................................................139

7.2.6. GPEN

General Purpose Enable Register (IO) ...............................................................................140

7.2.7. PCNTRL

Processor Control Register (IO)......................................................................................141

7.2.8. PLVL2

Processor Level 2 Register (IO) .........................................................................................142

7.2.9. PLVL3

Processor Level 3 Register (IO) ........................................................................................142

7.2.10. GLBSTS

Global Status Register (IO) ...........................................................................................143

7.2.11. DEVSTS

Device Status Register (IO) ..........................................................................................144

7.2.12. GLBEN

Global Enable Register (IO) ............................................................................................144

7.2.13. GLBCTL

Global Control Register (IO)..........................................................................................145

7.2.14. DEVCTL

Device Control Register (IO).........................................................................................146

7.2.15. GPIREG

General Purpose Input Register (IO).............................................................................147

7.2.16. GPOREG

General Purpose Output Register (IO)........................................................................148

7.3. SMBus IO Space Registers......................................................................................................................148

7.3.1. SMBHSTSTS

SMBus Host Status Register (IO)............................................................................148

7.3.2. SMBSLVSTS

SMBus Slave Status Register (IO) ..........................................................................149

7.3.3. SMBHSTCNT

SMBus Host Control Register (IO)..........................................................................150

7.3.4. SMBHSTCMD

SMBus Host Command Register (IO)....................................................................150

7.3.5. SMBHSTADD

SMBus Host Address Register (IO)........................................................................151

7.3.6. SMBHSTDAT0

SMBus Host Data 0 Register (IO).........................................................................151

7.3.7. SMBHSTDAT1

SMBus Host Data 1 Register (IO).........................................................................151

7.3.8. SMBBLKDAT

SMBus Block Data Register (IO).............................................................................152

7.3.9. SMBSLVCNT

SMBus Slave Control Register (IO).........................................................................152

7.3.10. SMBSHDWCMD

SMBus Shadow Command Register (IO).........................................................153

7.3.11. SMBSLVEVT

SMBus Slave Event Register (IO) .........................................................................153

7.3.12. SMBSLVDAT

SMBus Slave Data Register (IO)...........................................................................153

8.0. PCI/ISA BRIDGE FUNCTIONAL DESCRIPTION ......................................................................................154

8.1. Memory and IO Address Map...................................................................................................................154

E 82371AB (PIIX4)

9

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

8.1.1. I/O Accesses .....................................................................................................................................154

8.1.2. Memory Address Map........................................................................................................................154

8.1.3. BIOS Memory....................................................................................................................................155

8.2. PCI Interface.............................................................................................................................................157

8.2.1. Transaction Termination....................................................................................................................157

8.2.2. Parity Support....................................................................................................................................157

8.2.3. PCI Arbitration....................................................................................................................................157

8.3. ISA/EIO Interface......................................................................................................................................158

8.4. DMA Controller .........................................................................................................................................158

8.4.1. DMA Transfer Modes.........................................................................................................................159

8.4.2. DMA Transfer Types .........................................................................................................................160

8.4.3. DMA Timings .....................................................................................................................................161

8.4.4. DMA Buffer for Type F Transfers ......................................................................................................161

8.4.5. DREQ and DACK# Latency Control..................................................................................................161

8.4.6. Channel Priority .................................................................................................................................162

8.4.7. Register Functionality........................................................................................................................162

8.4.8. Address Compatibility Mode..............................................................................................................162

8.4.9. Summary of DMA Transfer Sizes......................................................................................................163

8.4.9.1. Address Shifting When Programmed for 16-Bit I/O Count by Words.........................................163

8.4.10. Autoinitialize.....................................................................................................................................163

8.4.11. Software Commands.......................................................................................................................164

8.4.12. ISA Refresh Cycles .........................................................................................................................164

8.5. PCI DMA...................................................................................................................................................165

8.5.1. PC/PCI DMA......................................................................................................................................165

8.5.2. Distributed DMA.................................................................................................................................168

8.6. Interrupt Controller....................................................................................................................................171

8.6.1. Programming the Interrupt Controller ................................................................................................172

8.6.2. End-of-Interrupt Operation.................................................................................................................173

8.6.3. Modes of Operation ...........................................................................................................................173

8.6.4. Cascade Mode...................................................................................................................................175

8.6.5. Edge and Level Triggered Mode........................................................................................................175

8.6.6. Interrupt Masks..................................................................................................................................176

8.6.7. Reading the Interrupt Controller Status.............................................................................................176

8.6.8. Interrupt Steering...............................................................................................................................177

8.7. Serial Interrupts.........................................................................................................................................178

8.7.1. Protocol..............................................................................................................................................178

8.8. Timer/Counters.........................................................................................................................................180

8.8.1. Programming the Interval Timer ........................................................................................................180

8.9. Real Time Clock .......................................................................................................................................183

8.9.1. RTC Registers and RAM...................................................................................................................183

8.9.1.1. Control Register A.......................................................................................................................185

8.9.1.2. Control Register B.......................................................................................................................186

8.9.1.3. Control Register C ......................................................................................................................187

82371AB (PIIX4) E

10

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

8.9.1.4. Control Register D ......................................................................................................................187

8.9.2. RTC Update Cycle.............................................................................................................................188

8.9.3. RTC Interrupts...................................................................................................................................188

8.9.4. Lockable RAM Ranges......................................................................................................................188

8.9.5. RTC External Connections................................................................................................................188

8.10. X-Bus Support ........................................................................................................................................188

8.11. Reset Support.........................................................................................................................................189

8.12. Stand-Alone I/O APIC Support...............................................................................................................190

9.0. IDE CONTROLLER FUNCTIONAL DESCRIPTION ..................................................................................191

9.1. IDE Signal Configuration...........................................................................................................................191

9.2. ATA Register Block Decode.....................................................................................................................192

9.3. PIO IDE Transactions...............................................................................................................................193

9.4. Bus Master Function.................................................................................................................................195

9.5. “Ultra DMA/33” Synchronous DMA Operation..........................................................................................197

10.0. USB HOST CONTROLLER FUNCTIONAL DESCRIPTION ...................................................................199

11.0. POWER MANAGEMENT FUNCTIONAL DESCRIPTION .......................................................................201

11.1. Power Management Overview ...............................................................................................................201

11.2. Clock Control..........................................................................................................................................202

11.2.1. Host Clock Control Mechanisms.....................................................................................................202

11.2.2. Stop Clock and Deep Sleep State Example Sequence...................................................................208

11.2.3. PCI Clock Control............................................................................................................................210

11.3. Peripheral Device Management .............................................................................................................210

11.3.1. Device Idle Timer.............................................................................................................................211

11.3.2. Device Trap .....................................................................................................................................212

11.3.3. Peripheral Device Management Sequence.....................................................................................212

11.3.4. Device Location on PCI Bus or ISA Bus .........................................................................................212

11.3.5. Device Specific Details....................................................................................................................215

11.3.5.1. Device 0: IDE Primary Drive 0..................................................................................................215

11.3.5.2. Device 1: IDE Primary Drive 1..................................................................................................216

11.3.5.3. Device 2: IDE Secondary Drive 0.............................................................................................216

11.3.5.4. Device 3: IDE Secondary Drive 1.............................................................................................217

11.3.5.5. Device 4: Audio.........................................................................................................................218

11.3.5.6. Device 5: Floppy Disk Drive .....................................................................................................219

11.3.5.7. Device 6: Serial Port A..............................................................................................................220

11.3.5.8. Device 7: Serial Port B..............................................................................................................221

11.3.5.9. Device 8: LPT (Parallel Port)....................................................................................................222

11.3.5.10. Device 9: Generic I/O Device 0..............................................................................................223

11.3.5.11. Device 10: Generic I/O Device 1............................................................................................224

11.3.5.12. Device 11: User Interface (Keyboard, Mouse, Video)............................................................225

11.3.5.13. Device 12: Cardbus Slot (or Generic I/O and MEM Device)..................................................226

11.3.5.14. Device 13: Cardbus Slot (or Generic I/O and MEM Device)..................................................227

E 82371AB (PIIX4)

11

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

11.4. Suspend/Resume and Power Plane Control..........................................................................................228

11.4.1. System Suspend..............................................................................................................................228

11.4.2. System Resume ..............................................................................................................................230

11.4.3. System Suspend and Resume Control Signaling............................................................................232

11.4.3.1. Power Supply Timings..............................................................................................................232

11.4.3.2. Power Level Active Status Signal Timings...............................................................................233

11.4.3.3. Power Management Signal Timings (Powered From Suspend Power Well) ...........................234

11.4.3.4. PCI Clock Stop and Start Timing Relationships.......................................................................235

11.4.3.5. Power Management Signal Timings (Powered From PIIX4 Main Core Well) ..........................236

11.4.3.6. Power Management Signal Timings (Powered From PIIX4 Main Core Well) ..........................238

11.4.3.7. Mechanical Off to On Condition Timings..................................................................................240

11.4.3.8. On State to Power On Suspend State Timing..........................................................................242

11.4.3.9. Power On Suspend to On Timing (With a Full System Reset).................................................244

11.4.3.10. System Transition From Power On Suspend to On (With Only Processor Reset)................246

11.4.3.11. Power On Suspend to On Timing (With No Resets)..............................................................248

11.4.3.12. On State to Suspend to RAM State Timing............................................................................250

11.4.3.13. Suspend-To-RAM to On Timing (With Full System Reset)....................................................252

11.4.3.14. On State to Suspend to Disk/Soft Off State Timings..............................................................254

11.4.3.15. Suspend-To-Disk to On (With Full System Reset).................................................................256

11.4.4. Shadow Registers............................................................................................................................258

11.5. System Management..............................................................................................................................262

11.5.1. SMI Operation..................................................................................................................................262

11.5.2. SMI# Generation Events..................................................................................................................263

11.5.3. Global Standby Timer Operation.....................................................................................................265

11.5.4. SMBus Functional Description ........................................................................................................266

11.5.4.1. SMBus Host Interface...............................................................................................................266

11.5.4.2. SMBus Slave Interface.............................................................................................................267

11.6. ACPI Support..........................................................................................................................................268

11.6.1. SCI Generation................................................................................................................................268

11.6.2. Power Management Timer...............................................................................................................268

11.6.3. Global Lock......................................................................................................................................269

12.0. PINOUT INFORMATION...........................................................................................................................270

13.0. PIIX4 PACKAGE INFORMATION.............................................................................................................274

14.0. TESTABILITY ............................................................................................................................................277

14.1. Test Mode Description............................................................................................................................277

14.2. Tri-state Mode.........................................................................................................................................278

14.3. NAND Tree Mode...................................................................................................................................278

82371AB (PIIX4) E

12

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

1.0. ARCHITECTURAL OVERVIEW

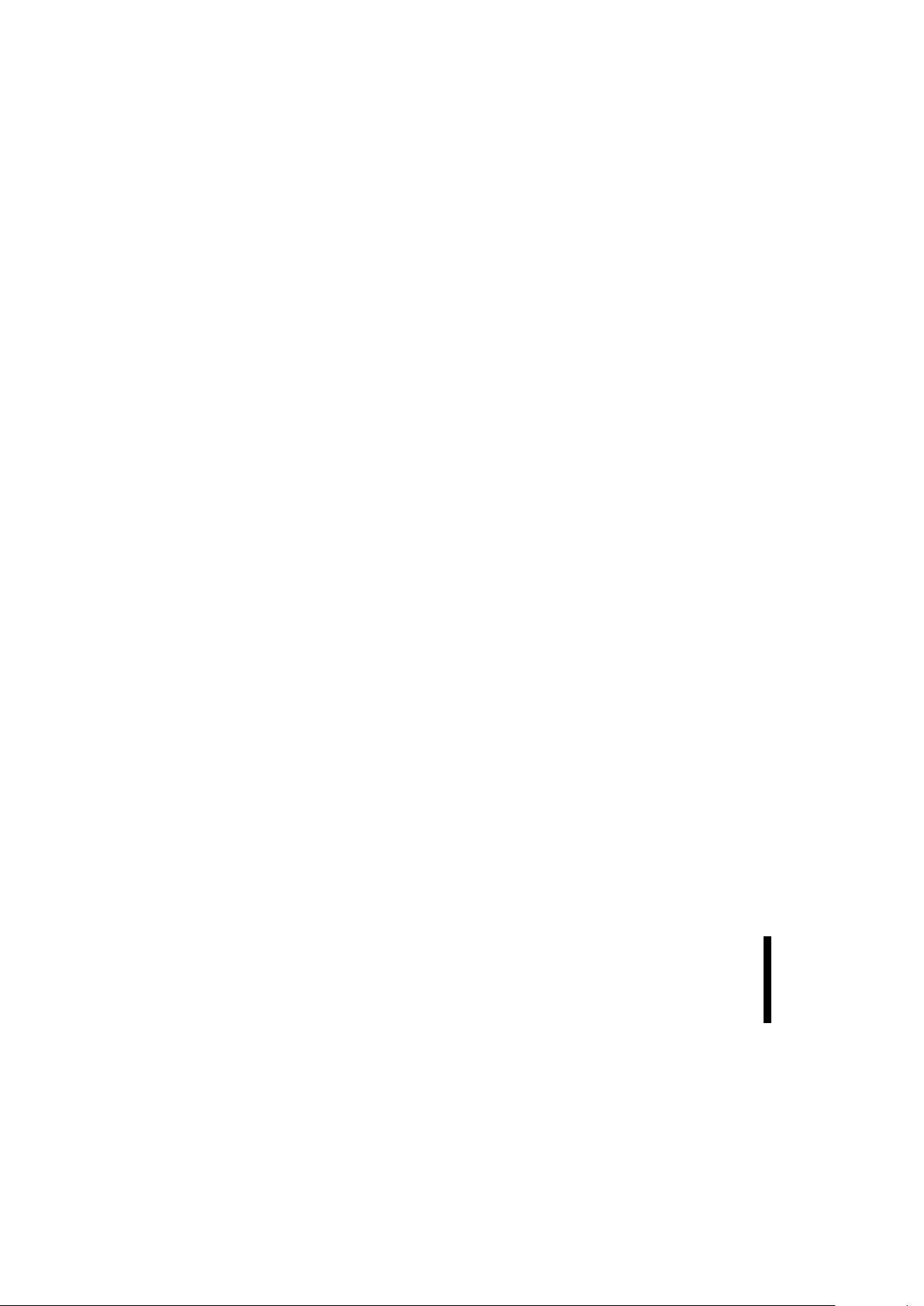

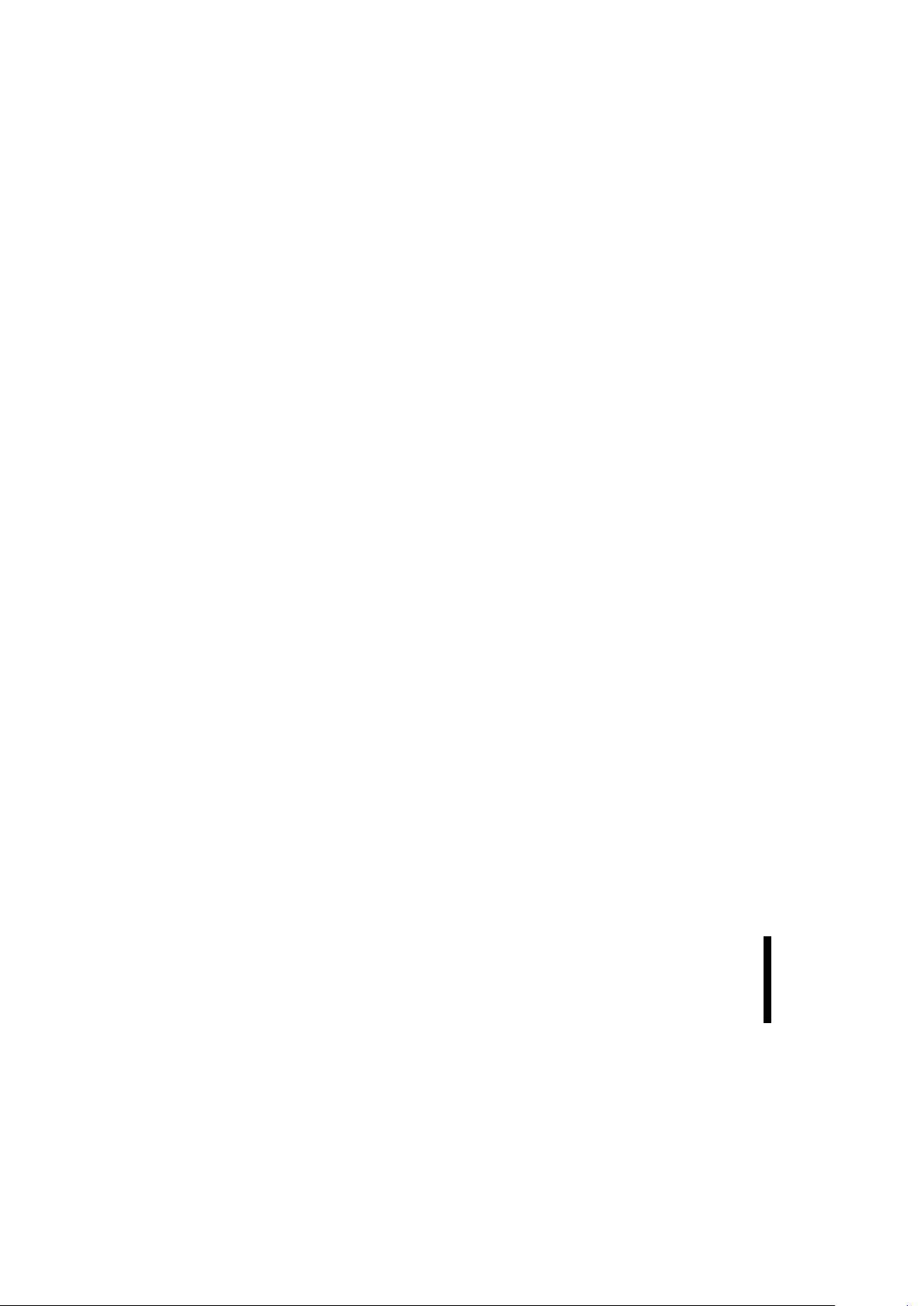

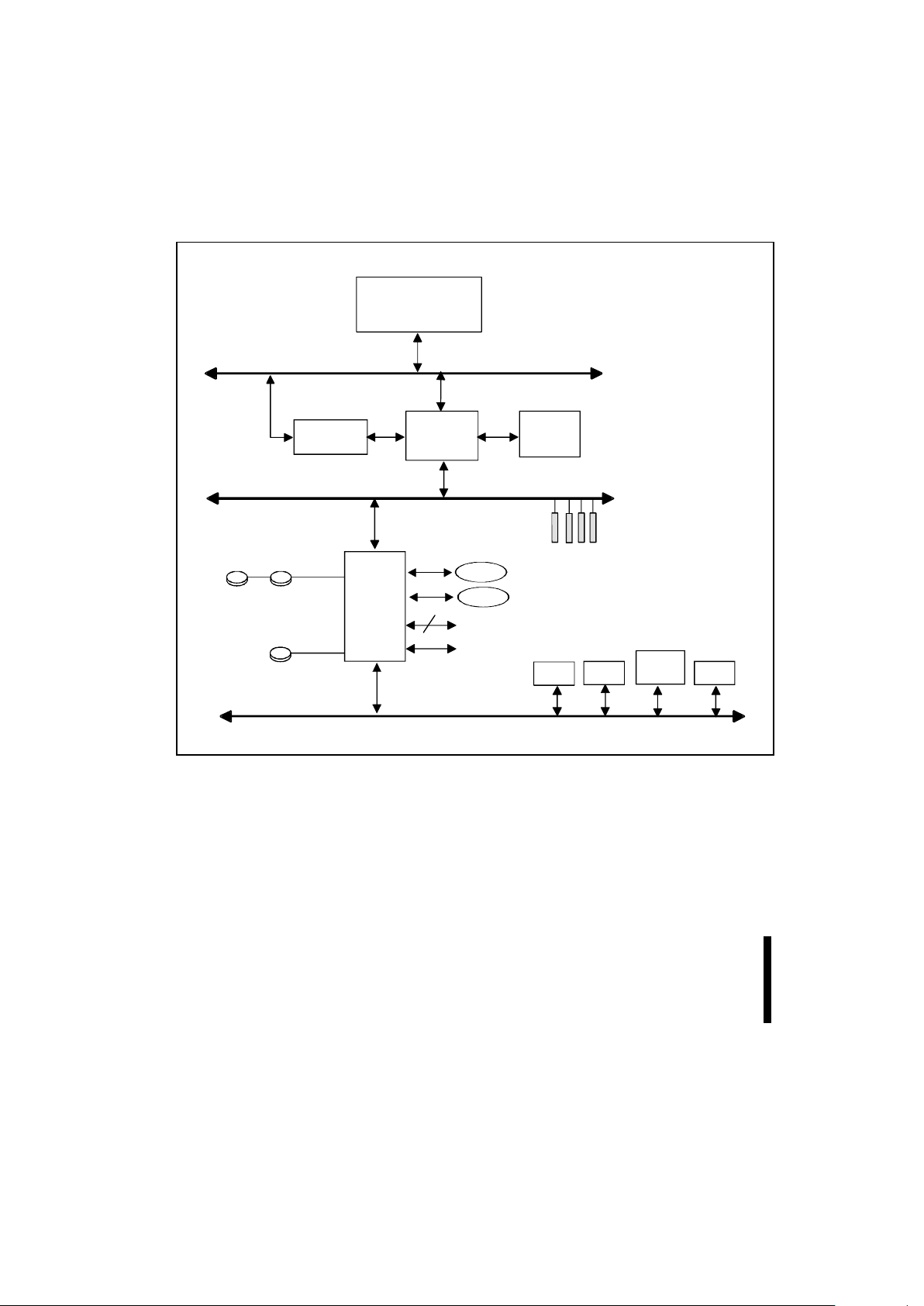

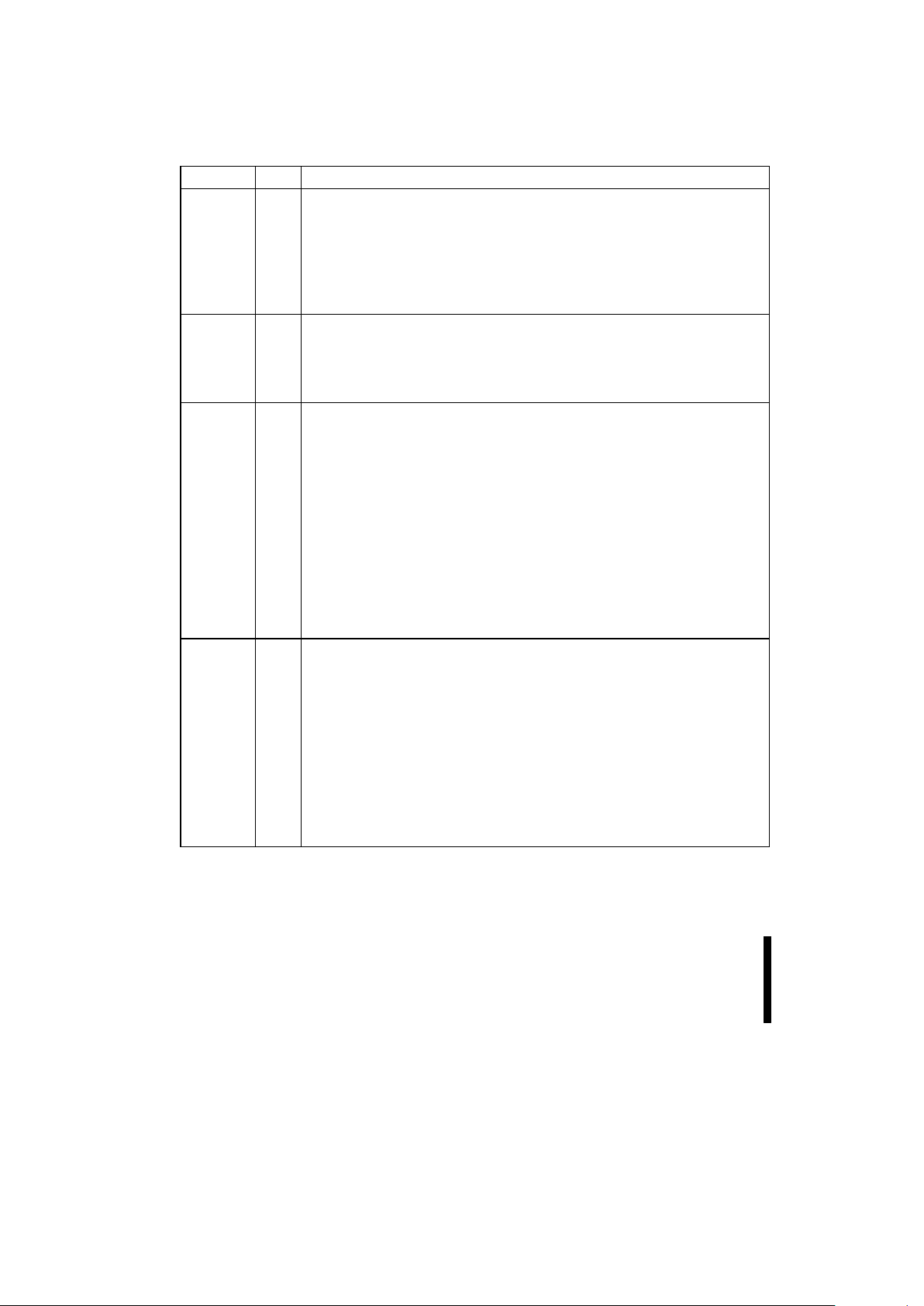

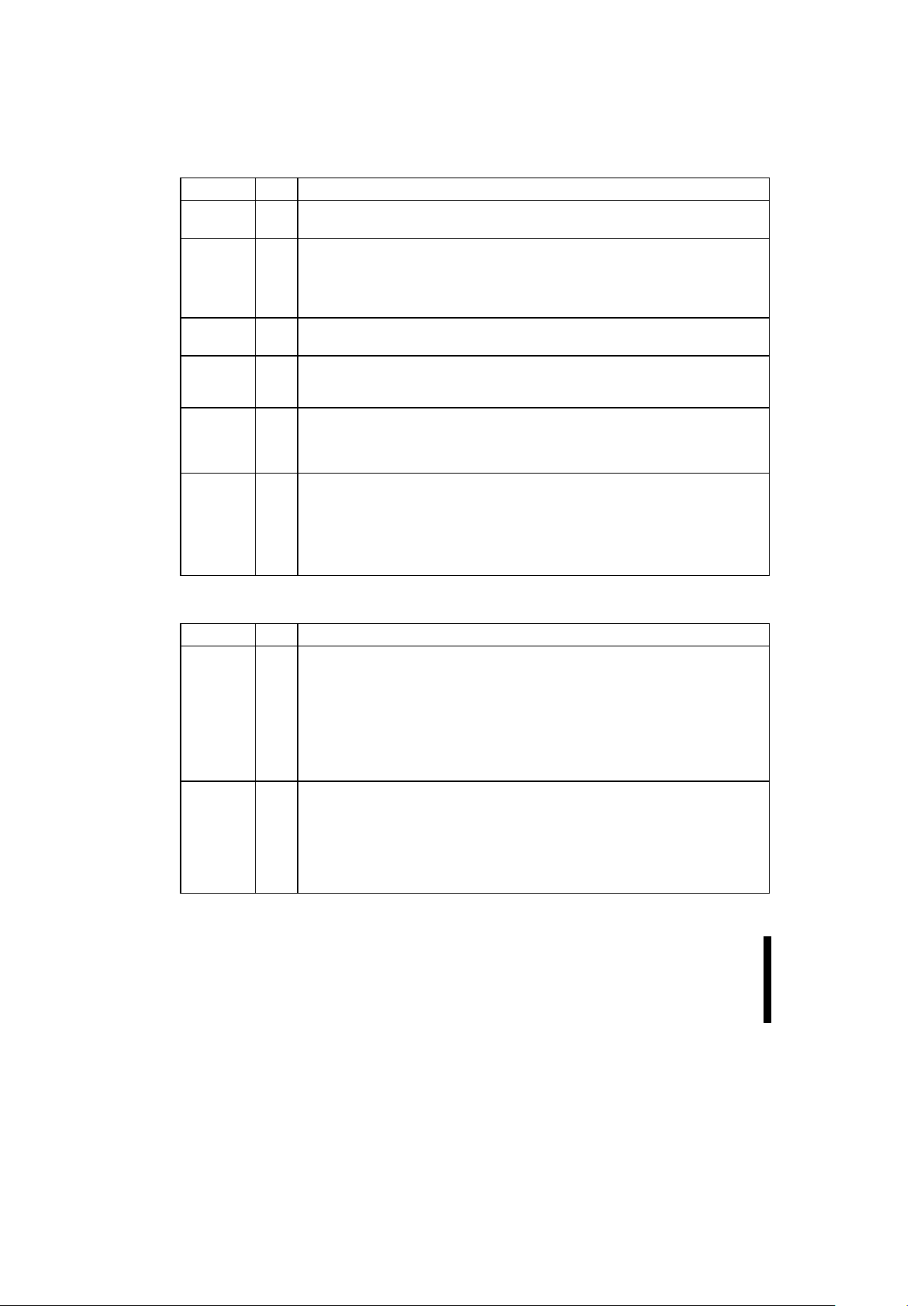

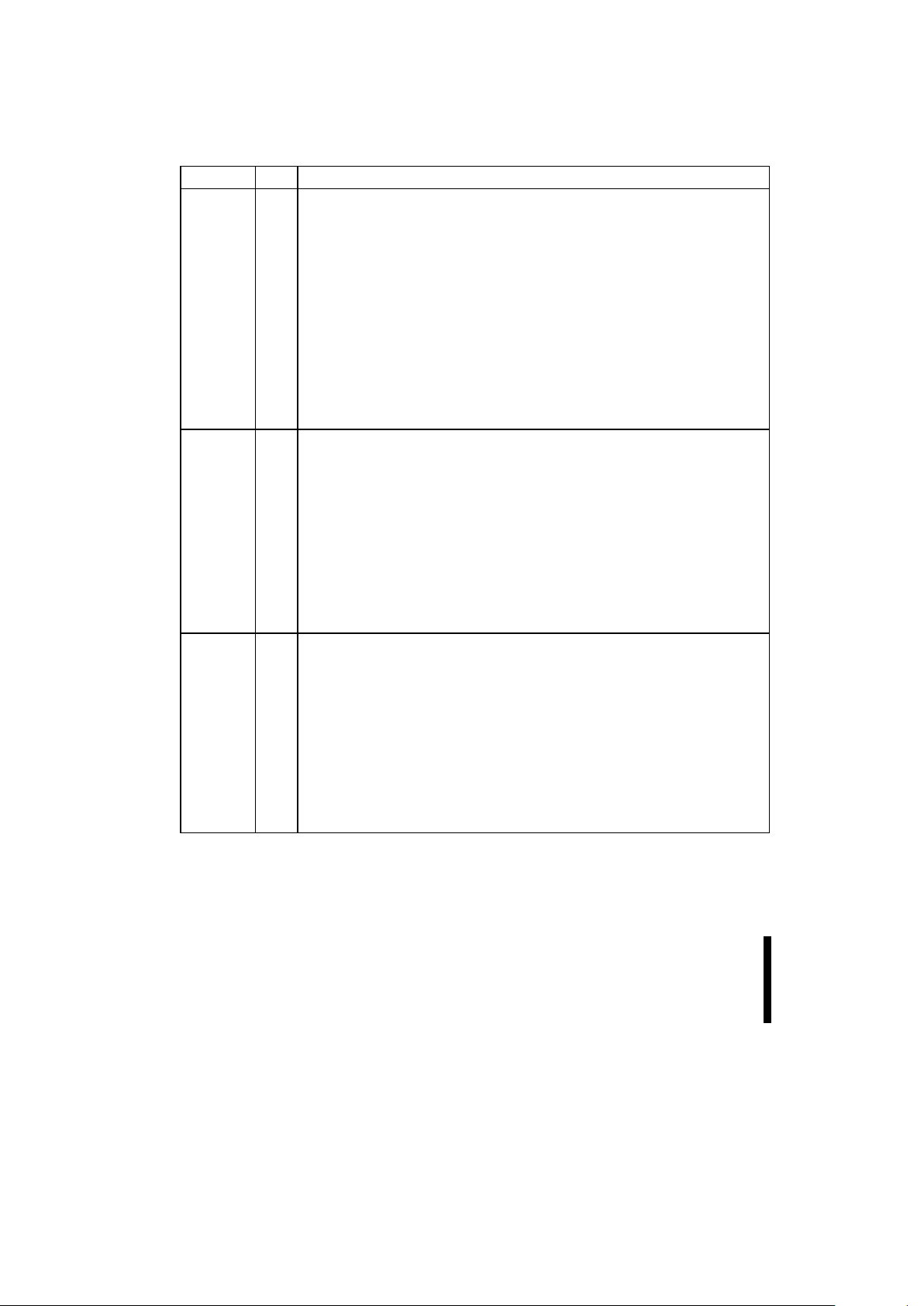

PIIX4 is a multi-function PCI device that integrates many system-level functions. Figure 1 shows an example

system block diagram using PIIX4.

PCI Bus (3.3V or 5V, 30/33 MHz)

Main

Memory

(DRAM)

Processor

Host Bus

Second Level

Cache

Host-to-PCI

Bridge

BMI IDE

Ultra DMA/33

CD ROM

Hard

Disk

ISA/EIO Bus

(3.3V; 5V Tolerant)

USB 2

USB 1

82371AB

(PIIX4)

GP[I,O] (30+)

SMBus

Audio

KBD

SP, PP,

FDC, IR

BIOS

PCI Slots

Hard

Disk

pix4_sys

Figure 1. PIIX4 System Block Diagram

PCI to ISA/EIO Bridge

PIIX4 is compatible with the PCI Rev 2.1 specification, as well as the IEEE 996 specification for the ISA (AT)

bus. On PCI, PIIX4 operates as a master for various internal modules, such as the USB controller, DMA

controller, IDE bus master controller, distributed DMA masters, and on behalf of ISA masters. PIIX4 operates as

a slave for its internal registers or for cycles that are passed to the ISA or EIO buses. All internal registers are

positively decoded.

E 82371AB (PIIX4)

13

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

PIIX4 can be configured for a full ISA bus or a subset of the ISA bus called the Extended IO (EIO) bus. The use

of the EIO bus allows unused signals to be configured as general purpose inputs and outputs. PIIX4 can directly

drive up to five ISA slots without external data or address buffering. It also provides byte-swap logic, I/O

recovery support, wait-state generation, and SYSCLK generation. X-Bus chip selects are provided for Keyboard

Controller, BIOS, Real Time Clock, a second microcontroller, as well as two programmable chip selects.

PIIX4 can be configured as either a subtractive decode PCI to ISA bridge or as a positive decode bridge. This

gives a system designer the option of placing another subtractive decode bridge in the system (e.g., an Intel

380FB Dock Set).

IDE Interface (Bus Master capability and synchronous DMA Mode)

The fast IDE interface supports up to four IDE devices providing an interface for IDE hard disks and CD ROMs.

Each IDE device can have independent timings. The IDE interface supports PIO IDE transfers up to 14

Mbytes/sec and Bus Master IDE transfers up to 33 Mbytes/sec. It does not consume any ISA DMA resources.

The IDE interface integrates 16x32-bit buffers for optimal transfers.

PIIX4’s IDE system contains two independent IDE signal channels. They can be electrically isolated

independently, allowing for the implementation of a “glueless” Swap Bay. They can be configured to the standard

primary and secondary channels (four devices) or primary drive 0 and primary drive 1 channels (two devices).

This allows flexibility in system design and device power management.

Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller)

The DMA controller incorporates the logic of two 82C37 DMA controllers, with seven independently

programmable channels. Channels [0:3] are hardwired to 8-bit, count-by-byte transfers, and channels [5:7] are

hardwired to 16-bit, count-by-word transfers. Any two of the seven DMA channels can be programmed to

support fast Type-F transfers. The DMA controller also generates the ISA refresh cycles.

The DMA controller supports two separate methods for handling legacy DMA via the PCI bus. The PC/PCI

protocol allows PCI-based peripherals to initiate DMA cycles by encoding requests and grants via three PC/PCI

REQ#/GNT# pairs. The second method, Distributed DMA, allows reads and writes to 82C37 registers to be

distributed to other PCI devices. The two methods can be enabled concurrently. The serial interrupt scheme

typically associated with Distributed DMA is also supported.

The timer/counter block contains three counters that are equivalent in function to those found in one 82C54

programmable interval timer. These three counters are combined to provide the system timer function, refresh

request, and speaker tone. The 14.31818-MHz oscillator input provides the clock source for these three

counters.

PIIX4 provides an ISA-Compatible interrupt controller that incorporates the functionality of two 82C59 interrupt

controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are

possible. In addition, PIIX4 supports a serial interrupt scheme. PIIX4 provides full support for the use of an

external IO APIC.

All of the registers in these modules can be read and restored. This is required to save and restore system state

after power has been removed and restored to the circuit.

Enhanced Universal Serial Bus (USB) Controller

The PIIX4 USB controller provides enhanced support for the Universal Host Controller Interface (UHCI). This

includes support that allows legacy software to use a USB-based keyboard and mouse.

82371AB (PIIX4) E

14

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

RTC

PIIX4 contains a Motorola* MC146818A-compatible real-time clock with 256 bytes of battery-backed RAM. The

real-time clock performs two key functions: keeping track of the time of day and storing system data, even when

the system is powered down. The RTC operates on a 32.768-kHz crystal and a separate 3V lithium battery that

provides up to 7 years of protection.

The RTC also supports two lockable memory ranges. By setting bits in the configuration space, two 8-byte

ranges can be locked to read and write accesses. This prevents unauthorized reading of passwords or other

system security information.

The RTC also supports a date alarm, that allows for scheduling a wake up event up to 30 days in advance,

rather than just 24 hours in advance.

GPIO and Chip Selects

Various general purpose inputs and outputs are provided for custom system design. The number of inputs and

outputs varies depending on PIIX4 configuration. Two programmable chip selects are provided which allows the

designer to place devices on the X-Bus without the need for external decode logic.

Pentium

®

and Pentium® II Processor Interface

The PIIX4 CPU interface allows connection to all Pentium and Pentium II processors. The Sleep mode for the

Pentium II processors is also supported.

Enhanced Power Management

PIIX4’s power management functions include enhanced clock control, local and global monitoring support for 14

individual devices, and various low-power (suspend) states, such as Power-On Suspend, Suspend-to-DRAM,

and Suspend-to-Disk. A hardware-based thermal management circuit permits software-independent entrance to

low-power states. PIIX4 has dedicated pins to monitor various external events (e.g., interfaces to a notebook lid,

suspend/resume button, battery low indicators, etc.). PIIX4 contains full support for the Advanced Configuration

and Power Interface (ACPI) Specification.

System Management Bus (SMBus)

PIIX4 contains an SMBus Host interface that allows the CPU to communicate with SMBus slaves and an SMBus

Slave interface that allows external masters to activate power management events.

Configurability

PIIX4 provides a wide range of system configuration options. This includes full 16-bit I/O decode on internal

modules, dynamic disable on all the internal modules, various peripheral decode options, and many options on

system configuration.

E 82371AB (PIIX4)

15

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

2.0. SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups

according to their associated interface.

The “#” symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is

at a low voltage level. When “#” is not present after the signal name, the signal is asserted when at the high

voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a

mixture of “active low” and “active high” signal. The term assert, or assertion indicates that a signal is active,

independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates

that a signal is inactive.

Certain signals have different functions, depending on the configuration programmed in the PCI configuration

space. The signal whose function is being described is in bold font. Some of the signals are multiplexed with

General Purpose Inputs and Outputs. The default configuration and control bits for each are described in Table 1

and Table 2.

Each output signal description includes the value of the signal During Reset, After Reset, and During POS.

During Reset refers to when the PCIRST# signal is asserted. After Reset is immediately after negation of

PCIRST# and the signal may change value anytime thereafter. The term High-Z means tri-stated. The term

Undefined means the signal could be high, low, tri-stated, or in some in-between level. Some of the power

management signals are reset with the RSMRST# input signal. The functionality of these signals during

RSMRST# assertion is described in the Suspend/Resume and Power Plane Control section.

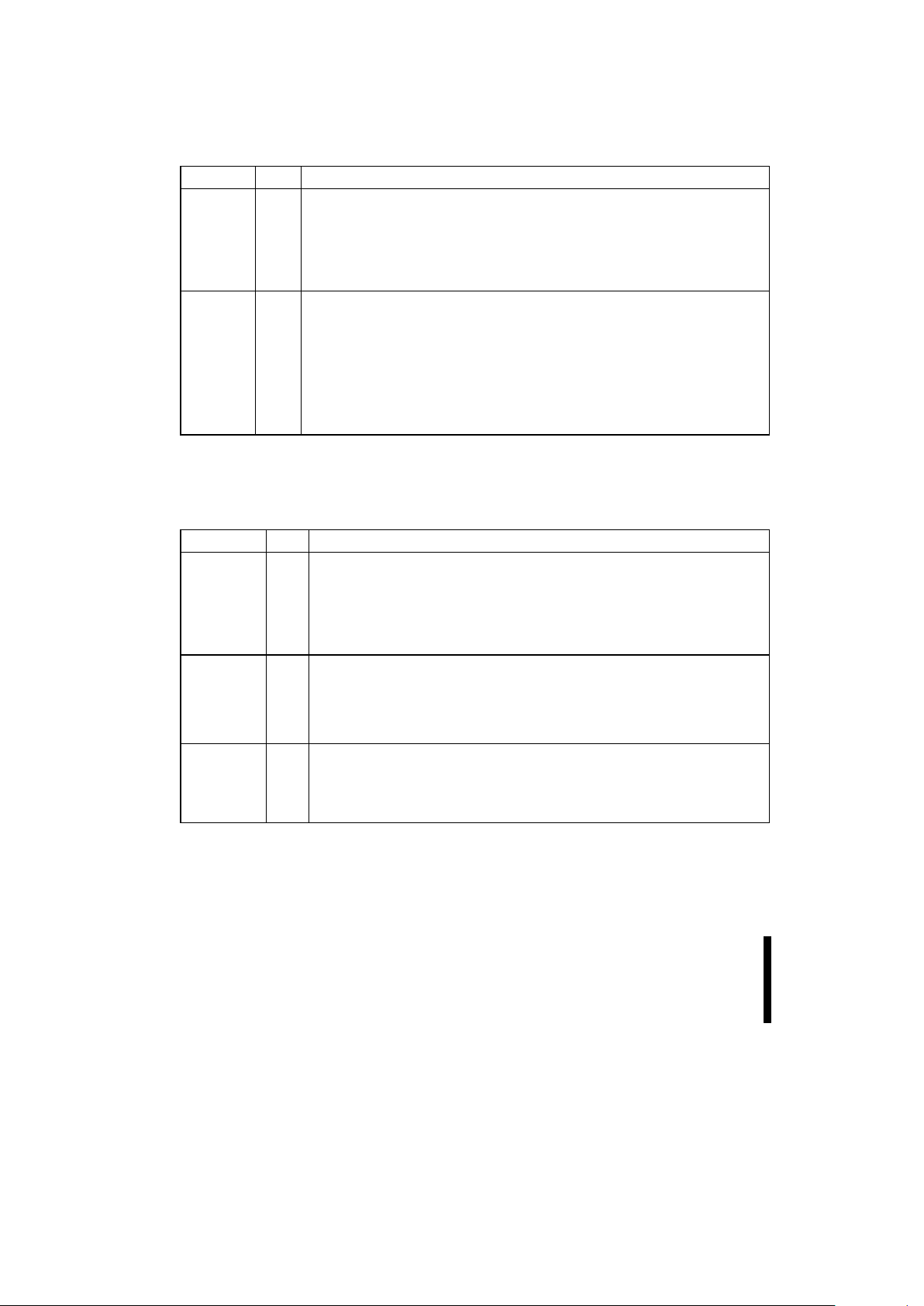

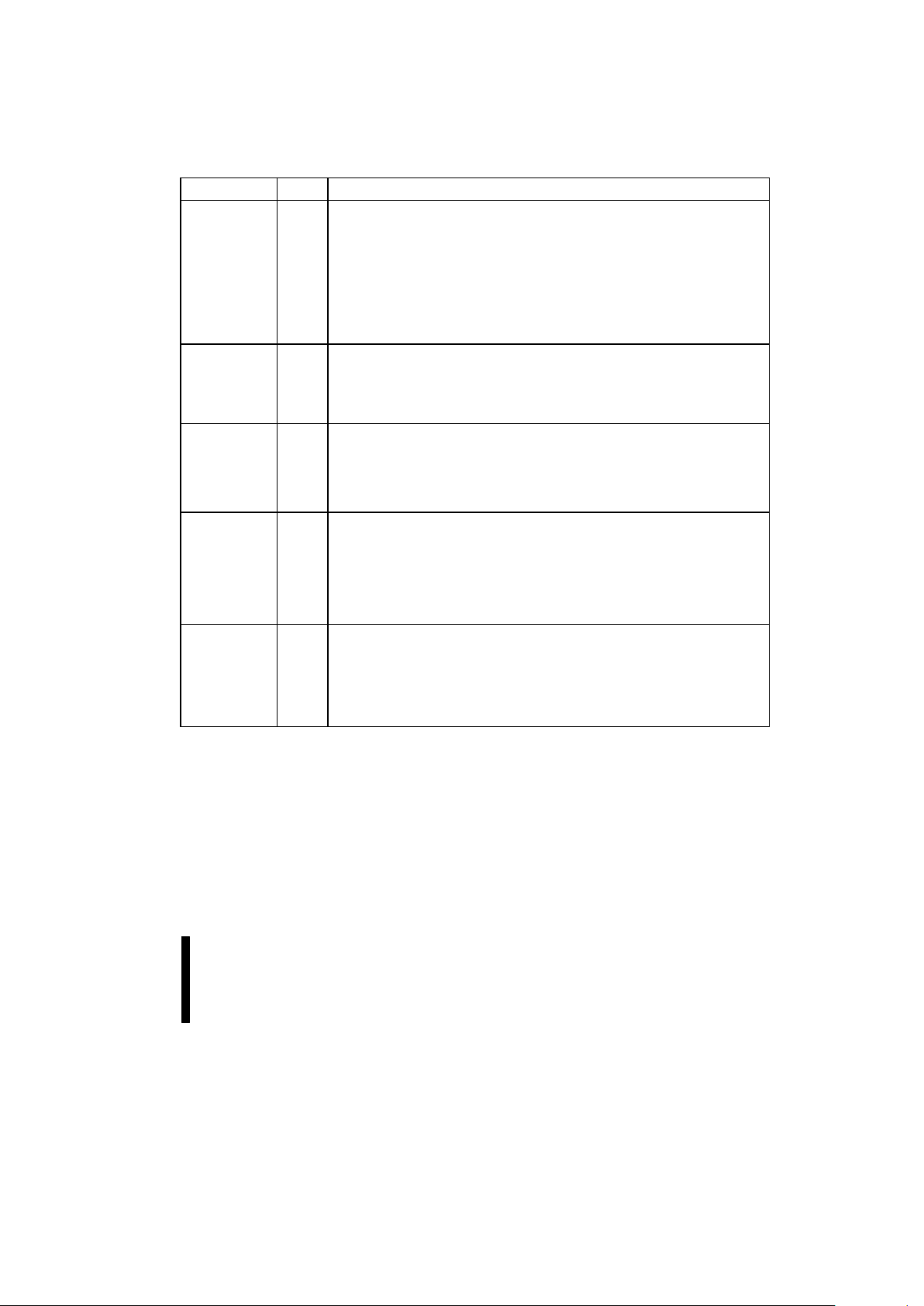

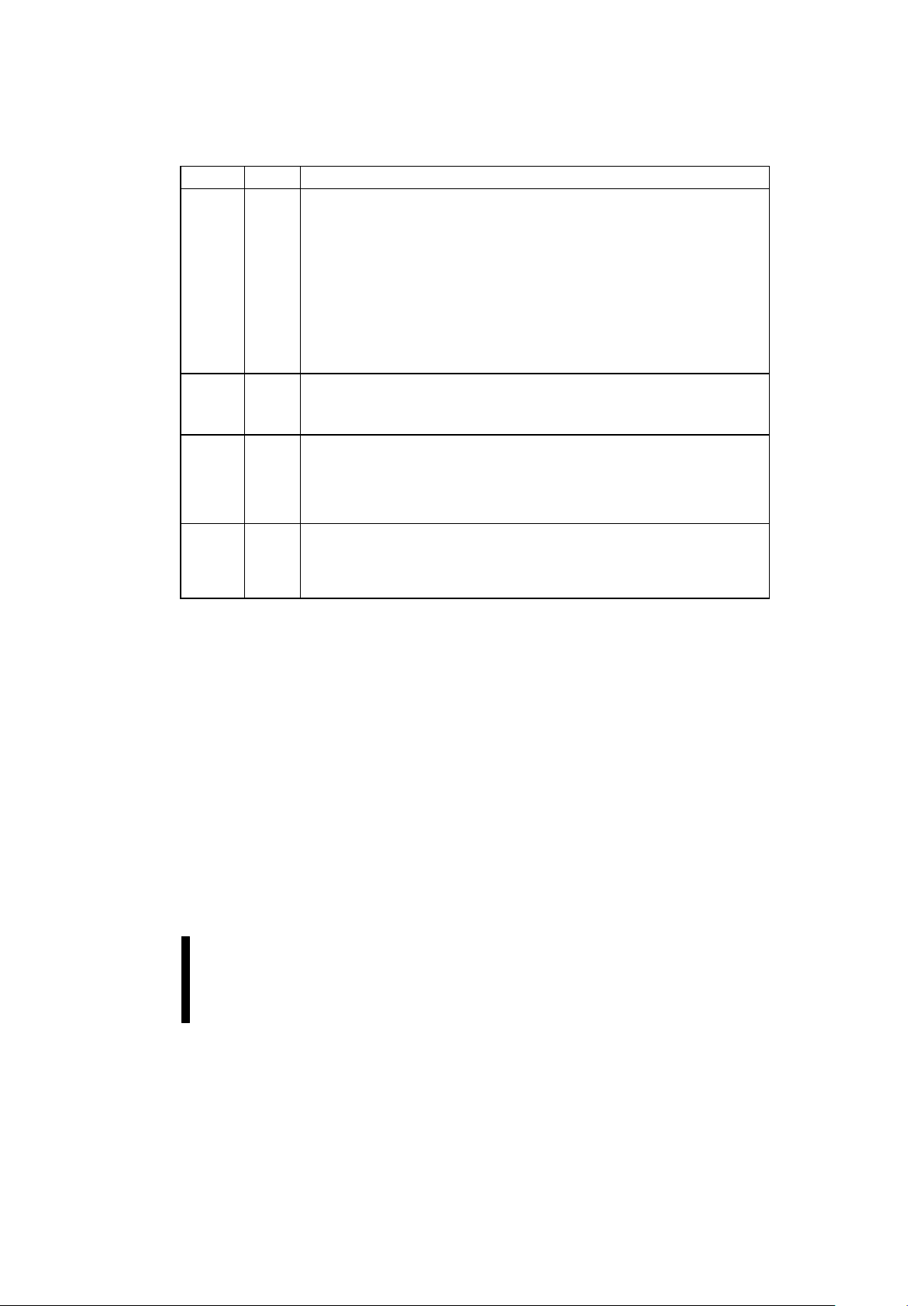

The I/O buffer types are shown below:

Buffer Type Description

I input only signal

O totem pole output

I/O bi-direction, tri-state input/output pin

s/t/s sustained tri-state

OD open drain

I/OD input/open drain output is a standard input buffer with an open drain output

V This is not a standard signal. It is a power supply pin.

3.3V/2.5V Indicates the buffer is 3.3V or 2.5V only, depending on the voltage (3.3V or 2.5V) connected to

V

CCX pins.

3.3V/5V Indicates that the output is 3.3V and input is 3.3V receiver with 5V tolerance.

5V Indicates 3.3V receiver with 5V tolerance.

All 3V output signals can drive 5V TTL inputs. Most of the 3V input signals are 5V tolerant. The 3V input signals

which are powered via the RTC or Suspend power planes should not exceed their power supply voltage (see

Power Planes chapter for additional information). The open drain (OD) CPU interface signals should be pulled up

to the CPU interface signal voltage.

82371AB (PIIX4) E

16

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

2.1. PIIX4 Signals

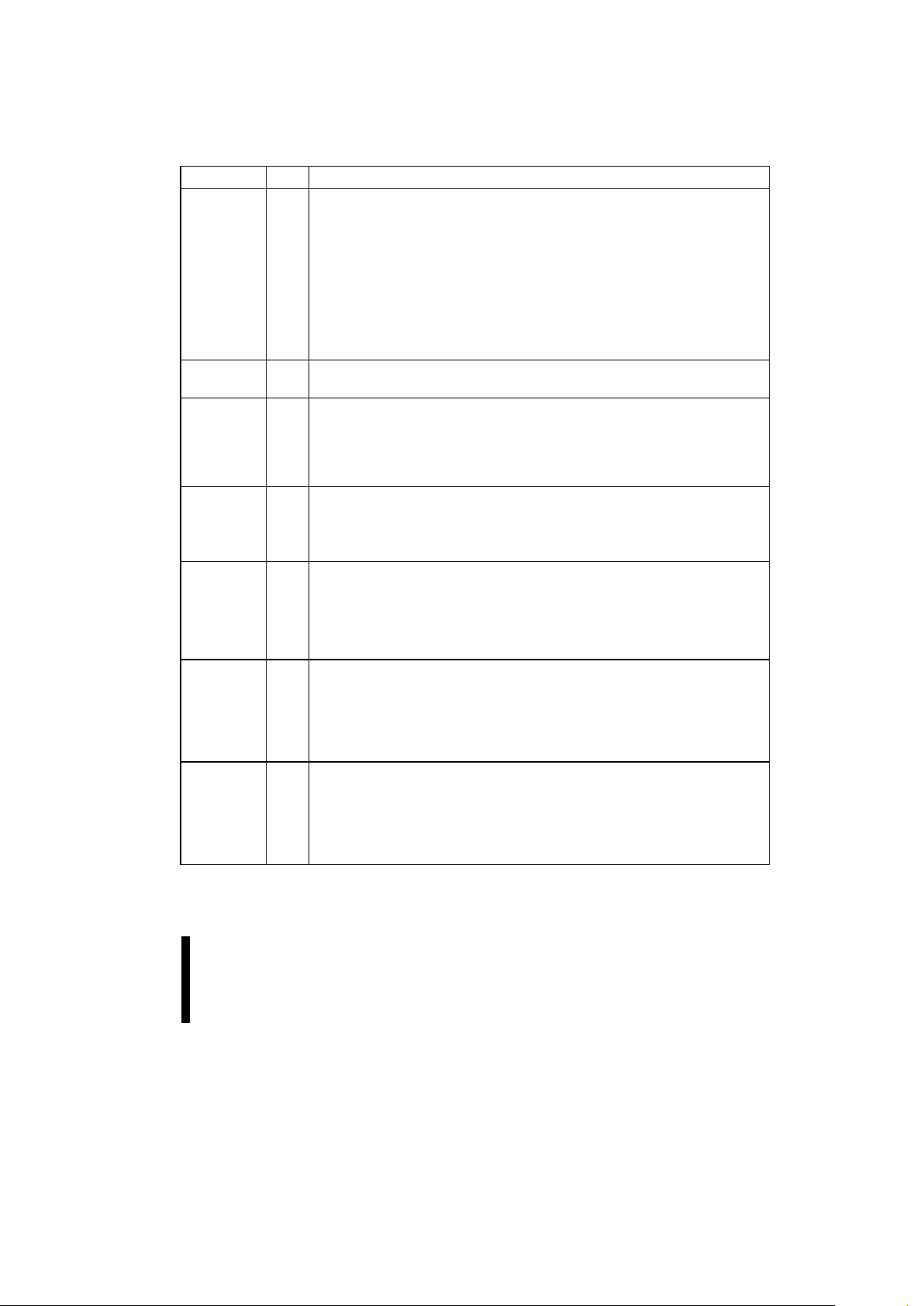

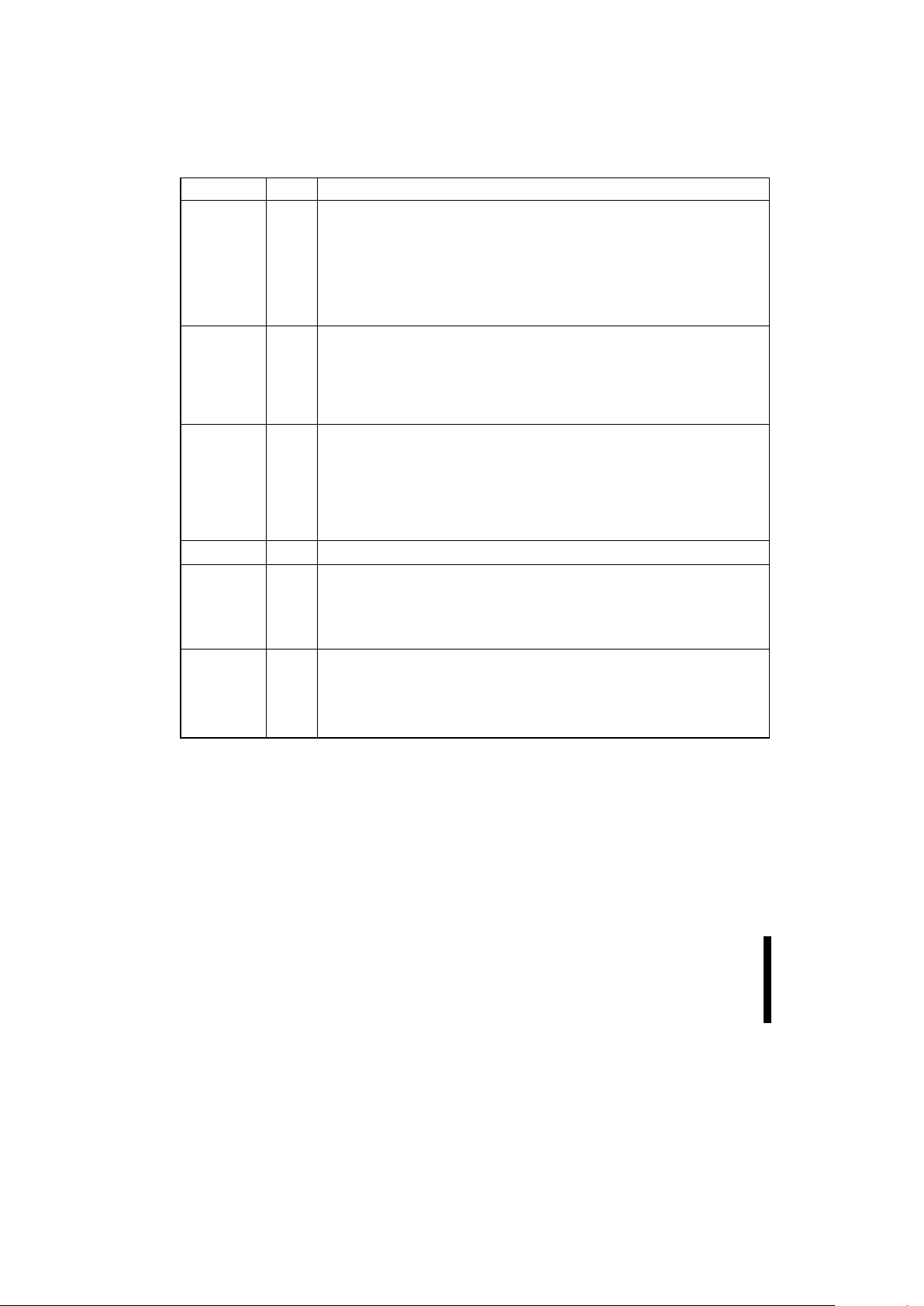

2.1.1. PCI BUS INTERFACE

Name Type Description

AD[31:0] I/O PCI ADDRESS/DATA. AD[31:0] is a multiplexed address and data bus. During the first

clock of a transaction, AD[31:0] contain a physical byte address (32 bits). During

subsequent clocks, AD[31:0] contain data.

A PIIX4 Bus transaction consists of an address phase followed by one or more data

phases. Little-endian byte ordering is used. AD[7:0] define the least significant byte

(LSB) and AD[31:24] the most significant byte (MSB).

When PIIX4 is a Target, AD[31:0] are inputs during the address phase of a transaction.

During the following data phase(s), PIIX4 may be asked to supply data on AD[31:0] for

a PCI read, or accept data for a PCI write.

As an Initiator, PIIX4 drives a valid address on AD[31:2] and 0 on AD[1:0] during the

address phase, and drives write or latches read data on AD[31:0] during the data

phase.

During Reset: High-Z After Reset: High-Z During POS: High-Z

C/BE#[3:0] I/O BUS COMMAND AND BYTE ENABLES. The command and byte enable signals are

multiplexed on the same PCI pins. During the address phase of a transaction,

C/BE[3:0]# define the bus command. During the data phase C/BE[3:0]# are used as

Byte Enables. The Byte Enables determine which byte lanes carry meaningful data.

C/BE0# applies to byte 0, C/BE1# to byte 1, etc. PIIX4 drives C/BE[3:0]# as an Initiator

and monitors C/BE[3:0]# as a Target.

During Reset: High-Z After Reset: High-Z During POS: High-Z

CLKRUN# I/O CLOCK RUN#. This signal is used to communicate to PCI peripherals that the PCI

clock will be stopped. Peripherals can assert CLKRUN# to request that the PCI clock

be restarted or to keep it from stopping. This function follows the protocol described in

the PCI Mobile Design Guide, Revision 1.0.

During Reset: Low After Reset: Low During POS: High

DEVSEL# I/O DEVICE SELECT. PIIX4 asserts DEVSEL# to claim a PCI transaction through positive

decoding or subtractive decoding (if enabled). As an output, PIIX4 asserts DEVSEL#

when it samples IDSEL active in configuration cycles to PIIX4 configuration registers.

PIIX4 also asserts DEVSEL# when an internal PIIX4 address is decoded or when PIIX4

subtractively or positively decodes a cycle for the ISA/EIO bus or IDE device. As an

input, DEVSEL# indicates the response to a PIIX4 initiated transaction and is also

sampled when deciding whether to subtractively decode the cycle. DEVSEL# is tristated from the leading edge of PCIRST#. DEVSEL# remains tri-stated until driven by

PIIX4 as a target.

During Reset: High-Z After Reset: High-Z During POS: High-Z

FRAME# I/O CYCLE FRAME. FRAME# is driven by the current Initiator to indicate the beginning and

duration of an access. While FRAME# is asserted data transfers continue. When

FRAME# is negated the transaction is in the final data phase. FRAME# is an input to

PIIX4 when it is the Target. FRAME# is an output when PIIX4 is the initiator. FRAME#

remains tri-stated until driven by PIIX4 as an Initiator.

During Reset: High-Z After Reset: High-Z During POS: High-Z

E 82371AB (PIIX4)

17

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

Name Type Description

IDSEL I INITIALIZATION DEVICE SELECT. IDSEL is used as a chip select during PCI

configuration read and write cycles. PIIX4 samples IDSEL during the address phase of

a transaction. If IDSEL is sampled active, and the bus command is a configuration read

or write, PIIX4 responds by asserting DEVSEL# on the next cycle.

IRDY# I/O INITIATOR READY. IRDY# indicates PIIX4’s ability, as an Initiator, to complete the

current data phase of the transaction. It is used in conjunction with TRDY#. A data

phase is completed on any clock both IRDY# and TRDY# are sampled asserted. During

a write, IRDY# indicates PIIX4 has valid data present on AD[31:0]. During a read, it

indicates PIIX4 is prepared to latch data. IRDY# is an input to PIIX4 when PIIX4 is the

Target and an output when PIIX4 is an Initiator. IRDY# remains tri-stated until driven by

PIIX4 as a master.

During Reset: High-Z After Reset: High-Z During POS: High-Z

PAR O CALCULATED PARITY SIGNAL. PAR is “even” parity and is calculated on 36 bits;

AD[31:0] plus C/BE[3:0]#. “Even” parity means that the number of “1”s within the

36 bits plus PAR are counted and the sum is always even. PAR is always calculated on

36 bits regardless of the valid byte enables. PAR is generated for address and data

phases and is only guaranteed to be valid one PCI clock after the corresponding

address or data phase. PAR is driven and tri-stated identically to the AD[31:0] lines

except that PAR is delayed by exactly one PCI clock. PAR is an output during the

address phase (delayed one clock) for all PIIX4 initiated transactions. It is also an

output during the data phase (delayed one clock) when PIIX4 is the Initiator of a PCI

write transaction, and when it is the Target of a read transaction.

During Reset: High-Z After Reset: High-Z During POS: High-Z

PCIRST# O PCI RESET. PIIX4 asserts PCIRST# to reset devices that reside on the PCI bus. PIIX4

asserts PCIRST# during power-up and when a hard reset sequence is initiated through

the RC register. PCIRST# is driven inactive a minimum of 1 ms after PWROK is driven

active. PCIRST# is driven for a minimum of 1 ms when initiated through the RC register.

PCIRST# is driven asynchronously relative to PCICLK.

During Reset: Low After Reset: High During POS: High

PHOLD# O PCI HOLD. An active low assertion indicates that PIIX4 desires use of the PCI Bus.

Once the PCI arbiter has asserted PHLDA# to PIIX4, it may not negate it until PHOLD#

is negated by PIIX4. PIIX4 implements the passive release mechanism by toggling

PHOLD# inactive for one PCICLK.

During Reset: High-Z After Reset: High During POS: High

PHLDA# I PCI HOLD ACKNOWLEDGE. An active low assertion indicates that PIIX4 has been

granted use of the PCI Bus. Once PHLDA# is asserted, it cannot be negated unless

PHOLD# is negated first.

SERR# I/O SYSTEM ERROR. SERR# can be pulsed active by any PCI device that detects a

system error condition. Upon sampling SERR# active, PIIX4 can be programmed to

generate a non-maskable interrupt (NMI) to the CPU.

During Reset: High-Z After Reset: High-Z During POS: High-Z

82371AB (PIIX4) E

18

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

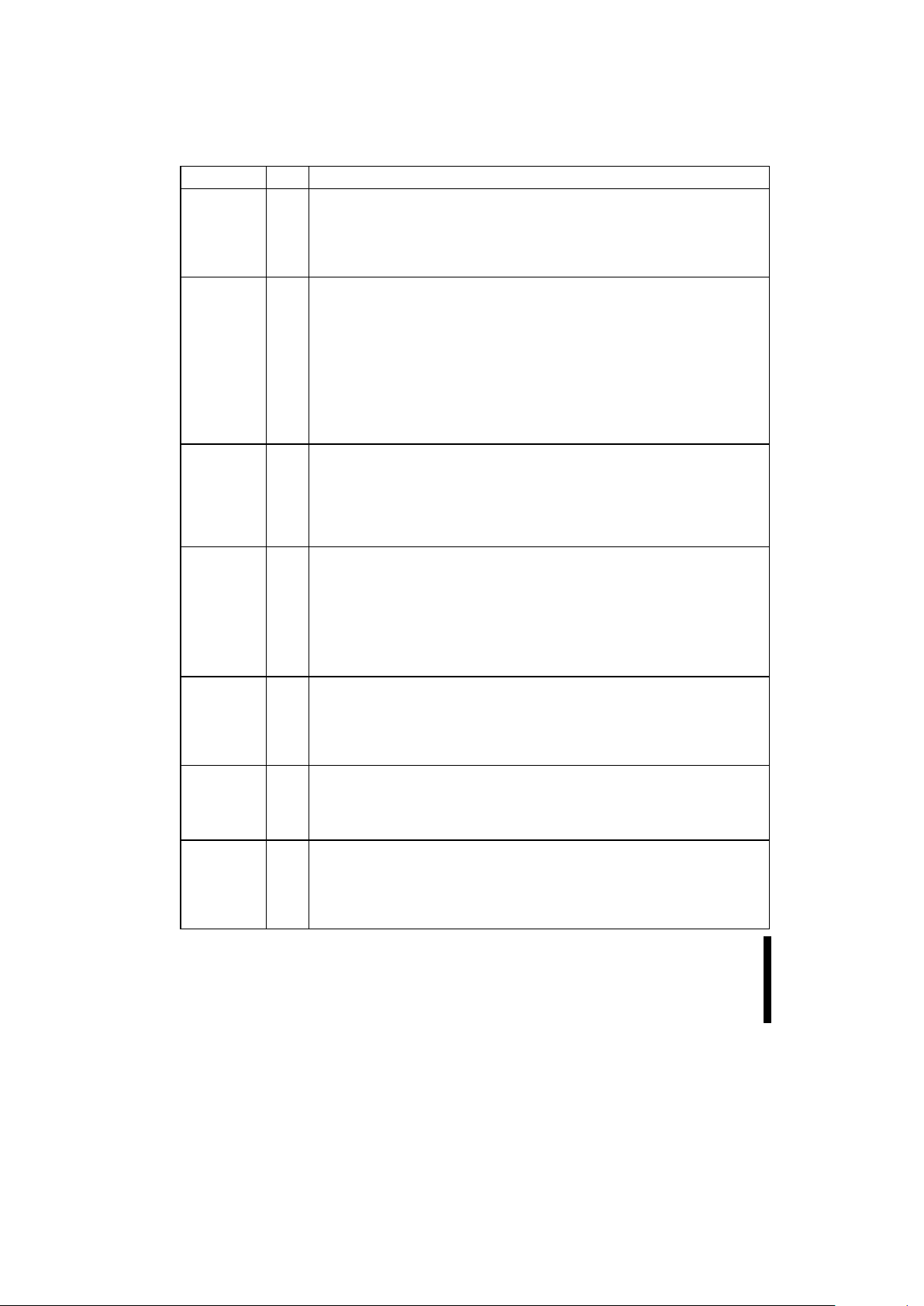

Name Type Description

STOP# I/O STOP. STOP# indicates that PIIX4, as a Target, is requesting an initiator to stop the

current transaction. As an Initiator, STOP# causes PIIX4 to stop the current transaction.

STOP# is an output when PIIX4 is a Target and an input when PIIX4 is an Initiator.

STOP# is tri-stated from the leading edge of PCIRST#. STOP# remains tri-stated until

driven by PIIX4 as a slave.

During Reset: High-Z After Reset: High-Z During POS: High-Z

TRDY# I/O TARGET READY. TRDY# indicates PIIX4’s ability to complete the current data phase

of the transaction. TRDY# is used in conjunction with IRDY#. A data phase is

completed when both TRDY# and IRDY# are sampled asserted. During a read, TRDY#

indicates that PIIX4, as a Target, has place valid data on AD[31:0]. During a write, it

indicates PIIX4, as a Target is prepared to latch data. TRDY# is an input to PIIX4 when

PIIX4 is the Initiator and an output when PIIX4 is a Target. TRDY# is

tri-stated from the leading edge of PCIRST#. TRDY# remains tri-stated until driven

by PIIX4 as a slave.

During Reset: High-Z After Reset: High-Z During POS: High-Z

NOTES:

All of the signals in the host interface are described in the Pentium Processor data sheet. The preceding table

highlights PIIX4 specific uses of these signals.

2.1.2. ISA BUS INTERFACE

Name Type Description

AEN O ADDRESS ENABLE. AEN is asserted during DMA cycles to prevent I/O slaves from

misinterpreting DMA cycles as valid I/O cycles. When negated, AEN indicates that an

I/O slave may respond to address and I/O commands. When asserted, AEN informs

I/O resources on the ISA bus that a DMA transfer is occurring. This signal is also

driven high during PIIX4 initiated refresh cycles.

During Reset: High-Z After Reset: Low During POS: Low

BALE O BUS ADDRESS LATCH ENABLE. BALE is asserted by PIIX4 to indicate that the

address (SA[19:0], LA[23:17]) and SBHE# signal lines are valid. The LA[23:17]

address lines are latched on the trailing edge of BALE. BALE remains asserted

throughout DMA and ISA master cycles.

During Reset: High-Z After Reset: Low During POS: Low

IOCHK#/

GPI0

I I/O CHANNEL CHECK. IOCHK# can be driven by any resource on the ISA bus.

When asserted, it indicates that a parity or an uncorrectable error has occurred for

a device or memory on the ISA bus. A NMI will be generated to the CPU if the NMI

generation is enabled. If the EIO bus is used, this signal becomes a general purpose

input.

E 82371AB (PIIX4)

19

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

Name Type Description

IOCHRDY I/O I/O CHANNEL READY. Resources on the ISA Bus negate IOCHRDY to indicate that

wait states are required to complete the cycle. This signal is normally high. IOCHRDY

is an input when PIIX4 owns the ISA Bus and the CPU or a PCI agent is accessing an

ISA slave, or during DMA transfers. IOCHRDY is output when an external ISA Bus

Master owns the ISA Bus and is accessing DRAM or a PIIX4 register. As a PIIX4

output, IOCHRDY is driven inactive (low) from the falling edge of the ISA commands.

After data is available for an ISA master read or PIIX4 latches the data for a write

cycle, IOCHRDY is asserted for 70 ns. After 70 ns, PIIX4 floats IOCHRDY. The 70 ns

includes both the drive time and the time it takes PIIX4 to float IOCHRDY. PIIX4 does

not drive this signal when an ISA Bus master is accessing an ISA Bus slave.

During Reset: High-Z After Reset: High-Z During POS: High-Z

IOCS16# I 16-BIT I/O CHIP SELECT. This signal is driven by I/O devices on the ISA Bus to

indicate support for 16-bit I/O bus cycles.

IOR# I/O I/O READ. IOR# is the command to an ISA I/O slave device that the slave may drive