Intel Corporation DA82562ET Datasheet

82562ET 10/100 Mbps Platform LAN

Connect (PLC)

Networking Silicon

Datashe et

Product Features

■ IEEE 802.3 10BASE-T/100BASE-TX

compliant physical la yer interfa ce

■ IEEE 802.3u Auto-Negotiation support

■ Digital Adaptive Equalization control

■ Link status interrupt capability

■ XOR tree mode support

■ 3-port LED support (speed, link and

activity)

■ 10BASE-T auto-polarity correction

■ LAN Connect Inter face

■ Diagnostic loopback mode

■ 1:1 transmit trans f orm er ratio support

■ Low power (less than 300 mW in active

transmit mode)

■ Reduced po wer in “ unplugged mode” (less

than 50 mW )

■ Automatic detection of “unplugged mode”

■ 3.3 V device

■ 48-pin S h r in k Small Ou tl in e Packag e

Revision 1.3

March 2003

Datasheet

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating

to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82562ET PLC may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-

548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © 2003, Intel Corporation

* Other brands and names are the property of their respective owners.

Datasheet iii

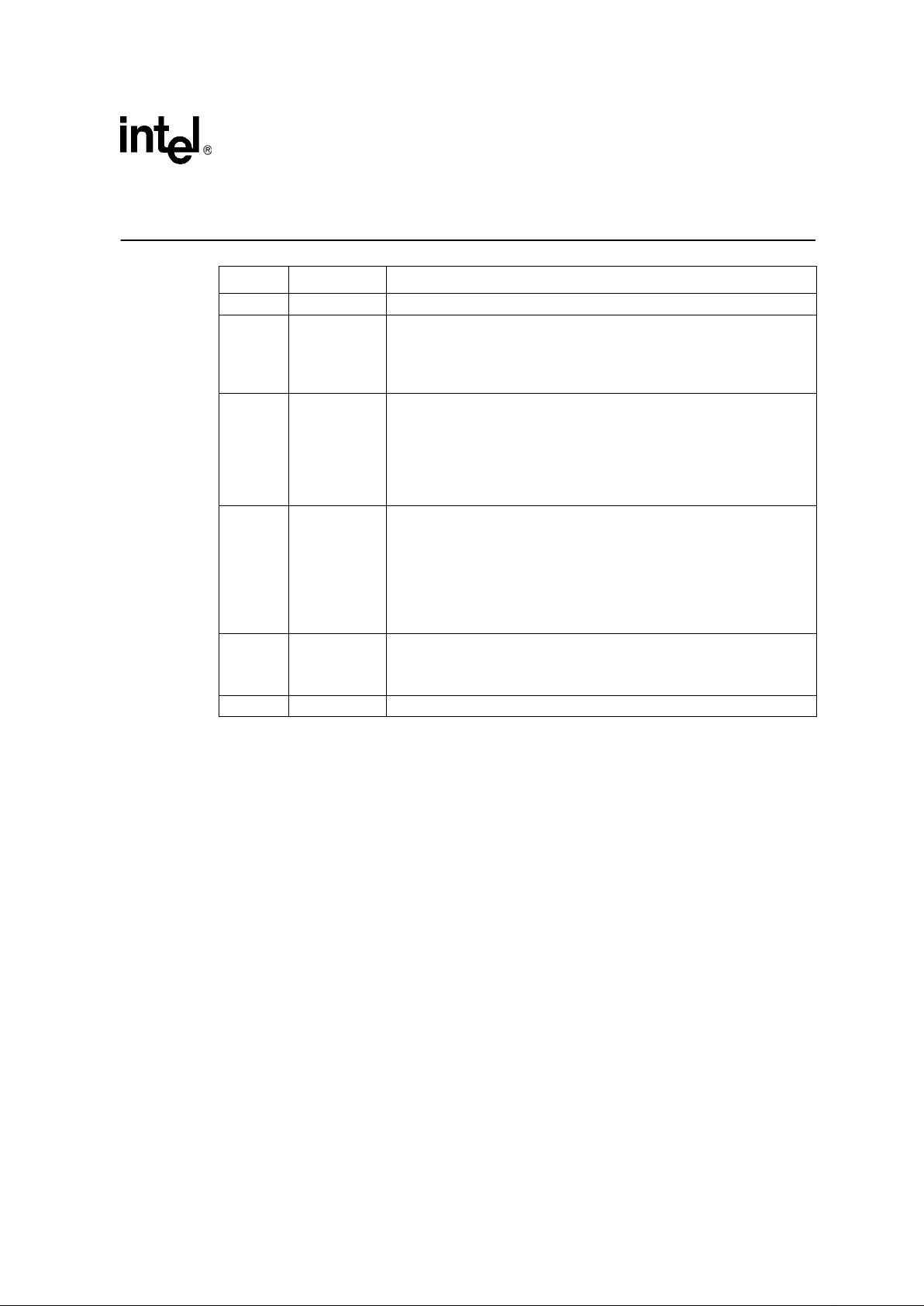

Networking Silicon — 82562ET

Revision History

Revision Revision Date Description

1.3 March 2003 Added product ordering code in Section 1.0.

1.2 October 2001 Removed confidential status.

• Removed sections: “Physical Layer Interface Functionality” and “Platform

LAN Connect”.

• Changed “Electrical and Timing Specifications” section to “Voltage and Temperature Specifications” and remove d timing specifications.

1.1 June 2000 Advance Information Datasheet release (Intel Confidential).

• On cover page, replac ed Boundary Scan Supp ort with XOR tr ee mode support. Adde d bullet for LA N Connect I/F.

• Pg. 3, added a Solution Block Diag ram as included in OR-2338 Pg. 4 but

replaced EM with ET in diagram.

• Pg. 11, removed Figure 4, “NRZ to MLT-3 Encoding Diagram”.

• Pg. 35, changed the Rev. number on the 82562 Pinout symbo l to 1.0.

1.0 May 2000 Advance Information Datasheet release (Intel Secret).

• Modif ied Tab le 1 “8256 2E T H ard w a re C onf ig ur at io n” to ad d o ne ro w for XOR

Tree and include column for comments.

• Updated the desc rition of the Activity LED signal in Section 3.6, “LED Pins”.

• Revised Sect ion 3.7, “Miscellaneous Control Pins” to reflect references to

Table 1 “82562ET H ardware Configuration”.

• Updated Section 4.0, “Voltage and Temperature Specifications”.

• Replaced diagrams in Sec tion 5.1 , “Package Information”.

0.6 Nov. 1999 • Corrected Figure 4 “NRZ to MLT-3 Encoding Diagram on Pg. 11 to reflect

correct signal transitions.

• Removed “10BASE-T Error Detection and Reporting” section since the

82562 does not do 10BASE-T error reporting.

0.55 Sept. 1999 Initial rele ase.

82562ET — Networking Silicon

iv Datasheet

Datasheet v

Networking Silicon — 82562ET

Contents

1.0 Introduction.........................................................................................................................1

1.1 Overview...............................................................................................................1

1.2 Features................................................................................................................1

1.3 References............................................................................................................1

2.0 82562ET Architect ural Overview........................................................................................3

3.0 82562ET Signal Descript ions.............................................................................................5

3.1 Signal Type Definitions ................................................................................ ....... ..5

3.2 Twisted Pair Ethernet (TPE) Pins .........................................................................5

3.3 External Bia s Pins ............ ................ ................. ....................... .......... ..................5

3.4 Clock Pins ............................................................................................................6

3.5 Platform LAN Con nect Interface Pins....................................................................6

3.6 LED Pins ..............................................................................................................7

3.7 Miscellan eous Control Pins ......... ................. ................. ................ ................. ......7

3.8 Power and Ground Connections .......................................................................... 8

4.0 Voltage and Temperature S pecifications ...........................................................................9

4.1 Absolute Maximum Ratings...................................................................................9

4.2 DC Characteristics ............................................................................................... 9

4.2.1 X1 Clock DC Specifications .................. ................ .......... ................ .........9

4.2.2 LAN Connect Interface DC Specifications . ............................................10

4.2.3 LED DC Specifications .......................................................................... 10

4.2.4 10BASE-T Voltage and Current DC Specifications ...............................10

4.2.5 100BASE-TX Voltage and Current DC Specifications ..........................11

5.0 Package and Pinout Information ......................................................................................13

5.1 Package Information ...........................................................................................13

5.2 Pinout Information ...............................................................................................14

5.2.1 8256 2ET Pin Assignm ents ....................................................................14

5.2.2 82562E T Shrink Small Outlying Package Diagram ...............................15

82562ET — Networking Silicon

vi Datasheet

Networking Silicon — 82562ET

Datasheet 1

1.0 Introduction

1.1 Overview

The Intel® 82562ET is a highly-integrated Platform LAN Connect device designed for 10 or 100

Mbps Ethernet systems. It i s ba sed on the IEEE 10 B ASE -T and 100B ASE-TX s tanda rds. The IEEE

802.3u standard for 100BASE-TX defines networking over two pairs of Category 5 unshielded

twisted pair cable or Type 1 shielded twist ed pair cable.

The 82562ET complie s with th e IEEE 802.3u Auto- Ne goti ation standa rd and the IEEE 802.3 x Full

Duplex Flow Control standard. The 8256 3ET als o includes a PHY interface compliant to the

current platform LAN connect interface.

1.2 Features

• IEEE 802.3 10BASE-T/ 100BASE-TX compliant physical layer int erface

• IEEE 802.3u Auto-Negotiation support

• Digital Adaptive Equalization control

• Link status interru pt capability

• XOR Tree mode support for board testing

• 3-port LED support (speed, link and activity)

• 10BASE-T auto-pol arity correction

• Diagnostic loopback mode

• 1:1 transmit transformer ratio support

• Low power (less than 300 mW in active transmit mode)

• Reduced power in “un plugged mode” (less than 50 mW)

• Automatic detecti on of “unplugged mode”

• 3.3 V device

• 48-pin Shrink Small Outline Package

• Platform LAN connect interface support

1.3 References

• IEEE 802.3 Standard for Local and Metropolitan Area Networks, Institute of Electrical and

Electronics Engineers

• 82555 10/100 Mbps LAN Physical Layer Interface Datasheet, Intel Corporation

• LAN Connect Interface Specification, Intel Corporation

Loading...

Loading...