Intel Corporation DT28F320S5-120, DA28F320S5-120 Datasheet

E ADVANCED INFORMATION

January 1998 Order Number: 290609-003

n

Two 32-Byte Write Buffers

2 µs per Byte Effective

Programming Time

n

Operating Voltage

5 V V

CC

5 V V

PP

n

70 ns Read Access Time (16 Mbit)

90 ns Read Access Time (32 Mbit)

n

High-Density Symmetrically-Blocked

Architecture

32 64-Kbyte Erase Blocks (16 Mbit)

64 64-Kbyte Erase Blocks (32 Mbit)

n

System Performance Enhancements

STS Status Output

n

Industry-Standard Packaging

SSOP and TSOP (16 Mbit)

SSOP (32 Mbit)

n

Cross-Compatible Command Support

Intel Standard Command Set

Common Flash Interface (CFI)

Scaleable Command Set (SCS)

n

Block Erase Cycles

100,000 at 0 °C to +70 °C

(Commercial)

10,000 at –40 °C to +85 °C

(Extended)

n

Enhanced Data Protection Features

Absolute Protection with V

PP

= GND

Flexible Block Locking

Block Erase/Program Lockout

during Power Transitions

n

Configurable x8 or x16 I/O

n

Automation Suspend Options

Program Suspend to Read

Block Erase Suspend to Program

Block Erase Suspend to Read

n

ETOX™ V Nonvolatile Flash

Technology

Intel’s Word-Wide FlashFile™ mem ory family prov ides high-density, low-cost, nonv olatile, read/ write storage

solutions for a wide range of applications. The word-wi de memories are available at v arious densities in t he

same package type. Their sym metrically-blocked archit ecture, voltage, and extended c ycling provide highly

flexible components suitable for resident flash arrays, SIMMs, and memory cards. Enhanced suspend

capabilities provide an ideal solution for code or data storage applications. For secure code storage

applications, such as networking, where code is ei ther direc tl y ex ecut ed out of flas h or downloaded t o DRAM ,

the word-wide memories offer three lev els of protecti on: absolut e protect ion with V

PP

at GND, selective bloc k

locking, and program/erase lockout during power transitions. These alternatives give designers ultimate

control of their code security needs.

This family of product s is manufactured on Intel’s 0.4 µm ETOX™ V process technology. It c omes in the

industry-standard 56-lead SSOP. In addition, the 16-Mb device is available in the industry-s tandard 56-lead

TSOP package.

WORD-WIDE

FlashFile™ MEMORY FAMILY

28F160S5, 28F320S5

Includes Extended Temperature Specifications

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provi ded in Intel ’s Terms and Condi tions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F160S3 and 28F320S3 may contain design defects or errors known as errata. Current characterized errata are available

on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-4725

or call 1-800-548-4725

or visit Intel’s website at http:\\www.intel.com

COPYRIGHT © INTEL CORPORATION 1997, 1998 CG-041493

*Third-party brands and names are the property of their respective owners.

E 28F160S5, 28F320S5

3

ADVANCED INFORMATION

CONTENTS

PAGE PAGE

1.0 INTRODUCTION ........................................... 5

1.1 New Features............................................. 5

1.2 Product Overview....................................... 5

1.3 Pinout and Pin Description......................... 6

2.0 PRINCIPLES OF OPERATION ..................... 9

2.1 Data Protection ........................................ 10

3.0 BUS OPERATION....................................... 10

3.1 Read........................................................10

3.2 Output Disable......................................... 11

3.3 Standby.................................................... 11

3.4 Deep Power-Down................................... 11

3.5 Read Query Operation............................. 11

3.6 Read Identifier Codes Operation.............. 11

3.7 Write ........................................................ 12

4.0 COMMAND DEFINITIONS.......................... 12

4.1 Read Array Command.............................. 16

4.2 Read Query Mode Command................... 16

4.2.1 Query Structure Output ..................... 16

4.2.2 Query Structure Overview ................. 18

4.2.3 Block Status Register........................19

4.2.4 CFI Query Identification String........... 20

4.2.5 System Interface Information............. 21

4.2.6 Device Geometry Definition............... 22

4.2.7 Intel-Specific Extended Query Table . 23

4.3 Read Identifier Codes Command............. 24

4.4 Read Status Register Command.............. 24

4.5 Clear Status Register Command.............. 25

4.6 Block Erase Command ............................ 25

4.7 Full Chip Erase Command....................... 25

4.8 Write to Buffer Command......................... 26

4.9 Byte/Word Program Command.................26

4.10 STS Configuration Command................. 27

4.11 Block Erase Suspend Command............27

4.12 Program Suspend Command.................27

4.13 Set Block Lock-Bit Command.................28

4.14 Clear Block Lock-Bits Command............ 28

5.0 DESIGN CONSIDERATIONS...................... 38

5.1 Three-Line Output Control........................38

5.2 STS and WSM Polling..............................38

5.3 Power Supply Decoupling ........................38

5.4 V

PP

Trace on Printed Circuit Boards........ 38

5.5 V

CC

, VPP, RP# Transitions........................ 38

5.6 Power-Up/Down Protection......................38

6.0 ELECTRICAL SPECIFICATIONS................ 39

6.1 Absolute Maximum Ratings......................39

6.2 Operating Conditions................................39

6.3 Capacitance.............................................40

6.4 DC Characteristics ...................................40

6.5 AC Characteristics—Read-Only

Operations...............................................44

6.6 AC Characteristics—Write Operations......46

6.7 Erase, Write, and Lock-Bit Configuration

Performance............................................49

7.0 ADDITIONAL INFORMATION.....................50

7.1 Device Nomenclature and Ordering

Information..............................................50

7.2 Intel Documentation .................................51

28F160S5, 28F320S5 E

4

ADVANCED INFORMATION

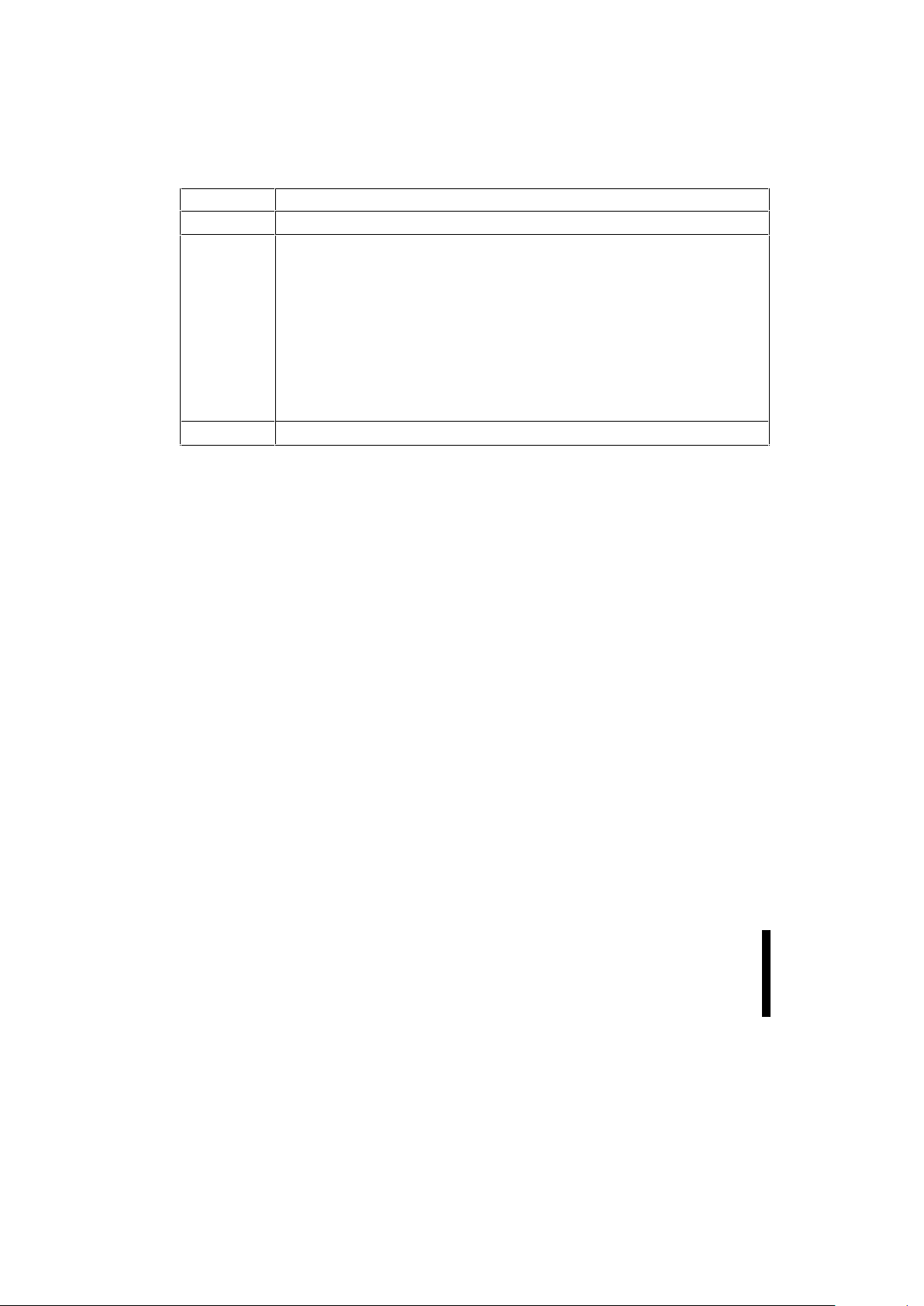

REVISION HISTORY

Number Description

-001 Original version

-002 Added commercial temperature information throughout the document.

Updated address in Figure 5.

Added descriptive information for CFI query to Section 4.2.5,

System Interface Information

Updated addresses and added descriptive information in Table 9 and Table 10.

Corrected documentation errors in Table 15 and Table 16.

Updated Figure 6. Modified decision diamond for checking counter.

Corrected documentation errors in Figure 11 and Figure 12.

Updated Table 19 to include commercial and extended temperature range specifications.

Updated note 4 in Table 19 for clarification.

Updated Table 20 to show 16 Mb/32 Mb specifications more clear and corrected

documentation error.

Corrected documentation error in Figure 17 and Table 23.

Updated package designators and order codes in Appendix A.

-003 Corrected error in datasheet designator

E 28F160S5, 28F320S5

5

ADVANCED INFORMATION

1.0 INTRODUCTION

This datasheet contains Word-Wide FlashFile™

memory (28F160S5, 28F320S5) specifications.

Section 1.0 provides a flash memory overview.

Sections 2.0 through 5.0 describe the memory

organization and functionality. Section 6.0 covers

electrical specifications for extended temperature

product offerings. Finally, Section 7.0 provides

ordering and reference information.

1.1 New Features

The Word-Wide FlashFile memory family m aintains

basic compatibility with Intel’s 28F016SA and

28F016SV. Key enhancements include:

• Common Flash Interface (CFI) Support

• Scaleable Command Set (SCS) Support

• S5 Technology

• Enhanced Suspend Capabilities

They share a compatible status register, basic

software commands, and pinout. These s imilarities

enable a clean migration from the 28F016SA or

28F016SV. When upgrading, it is im portant to note

the following differences:

• Because of new feature and density options,

the devices have different device identifier

codes. This allows for software optimization.

• New software commands.

• To take advantage of the 5 V t echnol ogy on the

28F160S5 and 28F320S5, allow V

PP

connection to VCC. The 28F160S5 and

28F320S5 FlashFile memories do not support a

12 V V

PP

option.

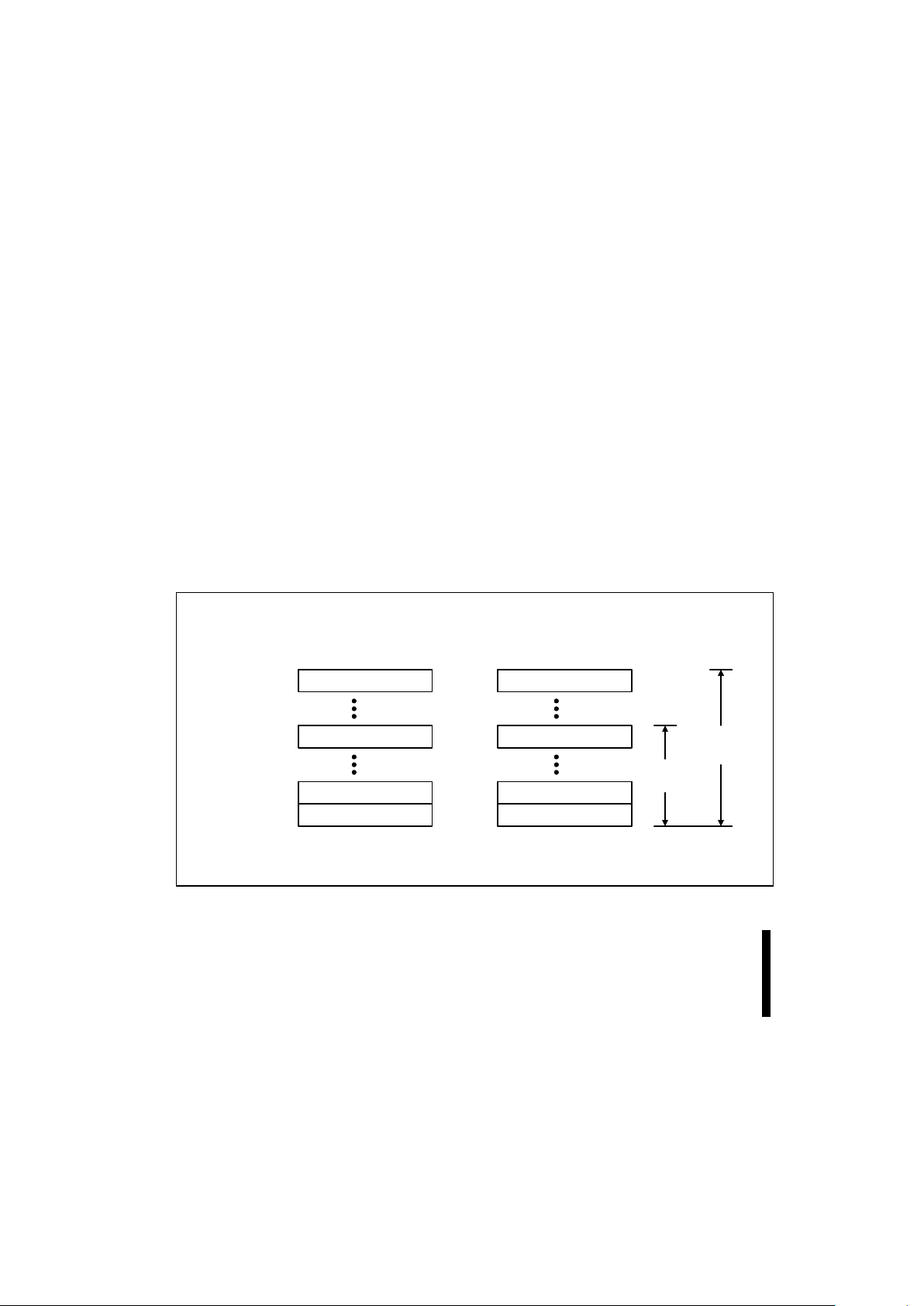

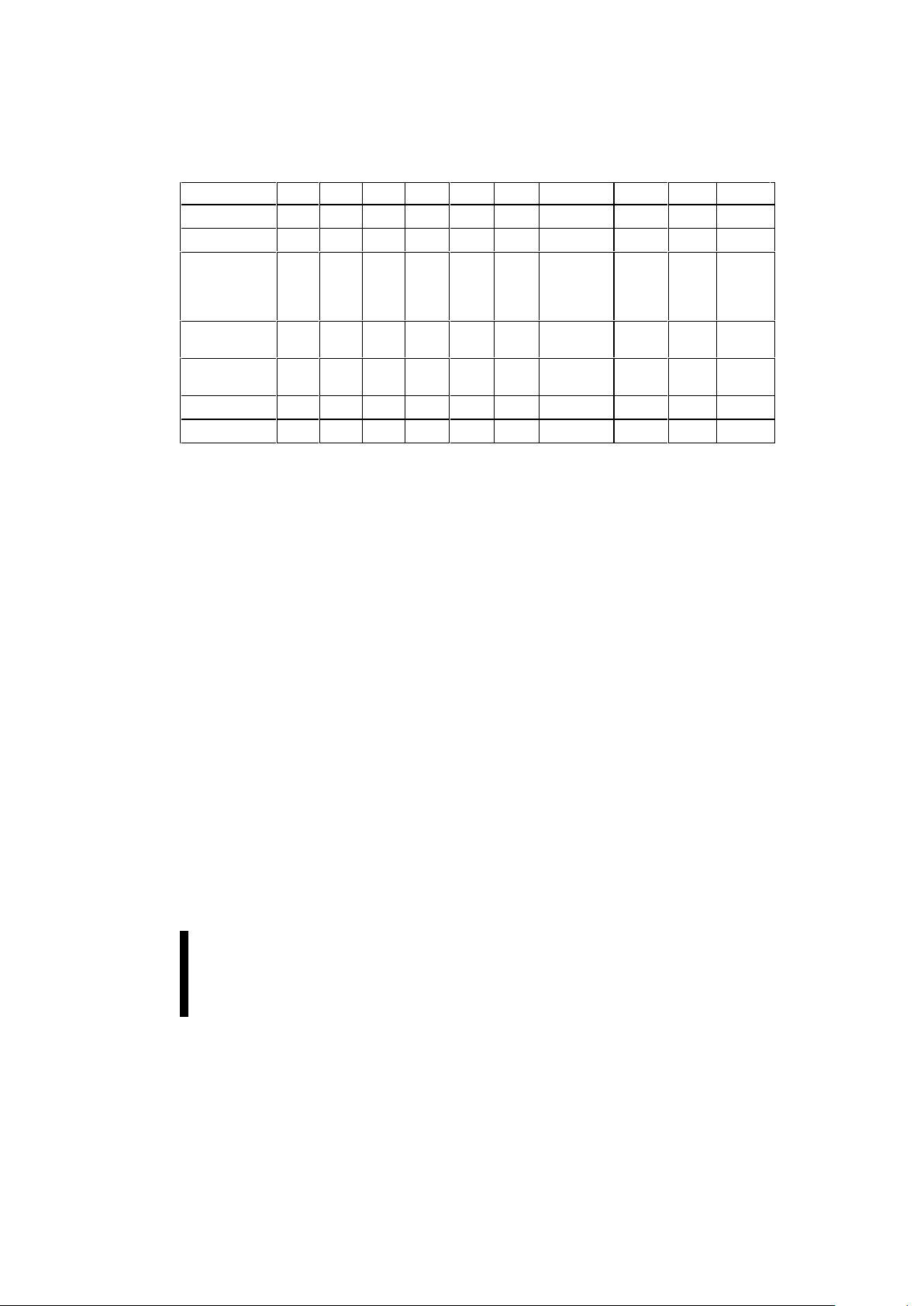

1.2 Product Overview

The Word-Wide FlashFile memory family provides

density upgrades with pinout compatibility for the

16- and 32-Mbit densities. They are highperformance memories arranged as 1 Mword and

2 Mwords of 16 bits or 2 Mbyte and 4 Mbyte of

8 bits. This data is grouped i n thirty-two and sixt yfour 64-Kbyte blocks that can be erased, locked,

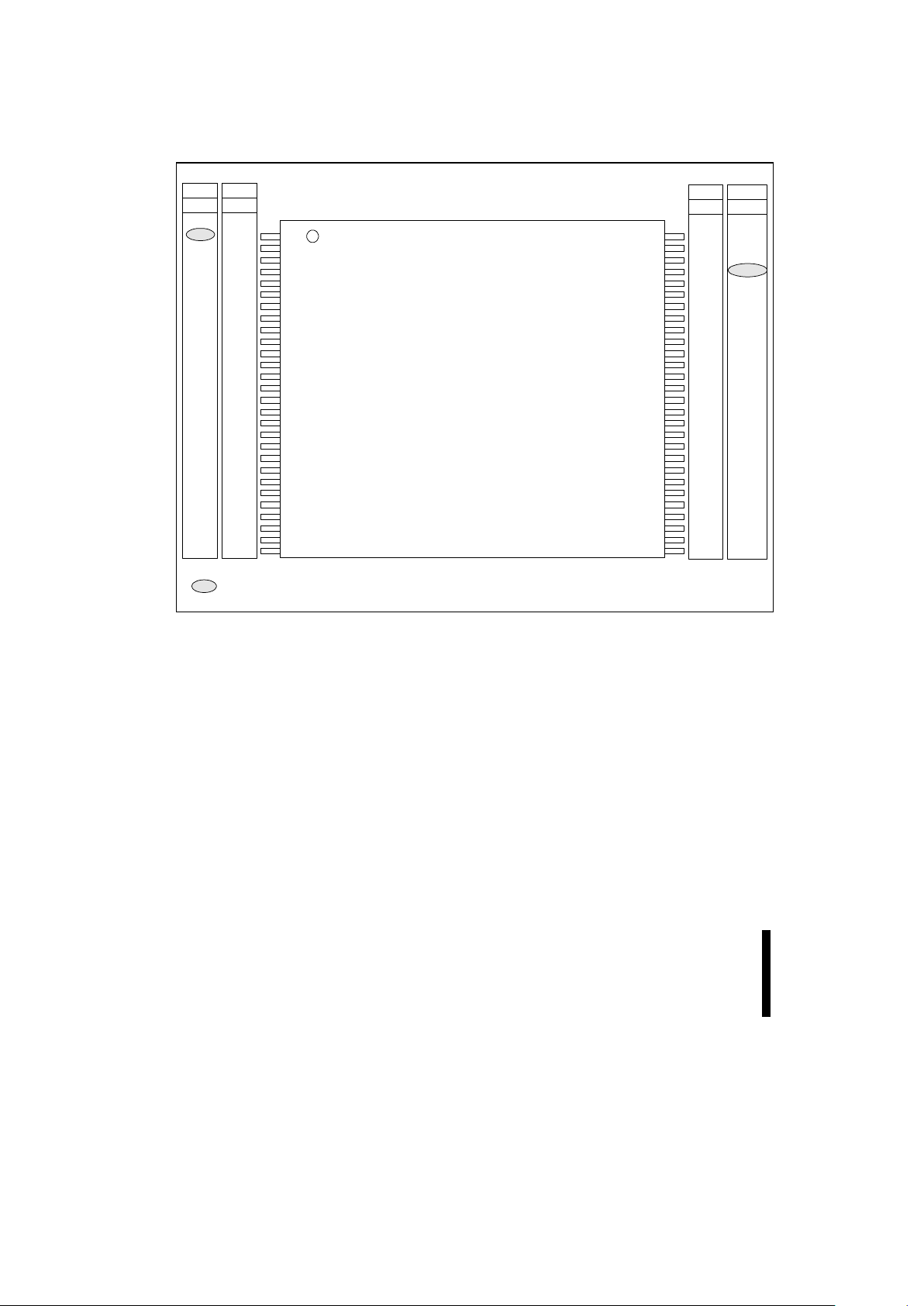

and unlocked in-system. Figure 1 shows the block

diagram, and Figure 4 illustrates the memory

organization.

Specifically designed for 5 V systems, the

28F160S5 and 28F320S5 support read and write

operation with V

CC

equal to VPP. Coupled with this

capability, high programming performance is

achieved through small, highly-optimized write

buffer operations. Additionally, the dedicated V

PP

pin gives complete data protection when VPP ≤

V

PPLK

.

A Common Flash Interface (CFI) permits OEMspecified software algorithms to be us ed for entire

families of devices. This allows deviceindependent, JEDEC ID-independent, and forwardand backward-compatible soft ware support for the

specified flash device families. Flash vendors can

standardize their existing interfaces for long-term

compatibility.

Scaleable Command Set (SCS) allows a single,

simple software driver in all host systems to work

with all SCS-compliant flash memory devices,

independent of system-level packaging (e.g.,

memory card, SIMM, or direct-to-board placement).

Additionally, SCS provides the highest

system/device data transfer rates and minimizes

device and system-level implementation costs.

A Command User Interface (CUI) serves as the

interface between the system processor and

internal device operation. A valid command

sequence written to the CUI initiates device

automation. An internal Writ e State Machine (WSM)

automatically executes the algorithms and timings

necessary for block erase, program, and lock-bit

configuration operations.

A block erase operation erases one of the devic e’s

64-Kbyte blocks typically within t

WHQV2/EHQV2

independent of other blocks. Each block can be

independently erased 100,000 times in the

commercial temperature range (0 °C to +70 °C) and

10,000 times in the extended temperature range

(–40 °C to +85 °C). Block erase suspend allows

system software to suspend block erase to read or

write data from any other block.

Data is programmed in byte, word or page

increments. Program suspend mode enables the

system to read data or execute code from any other

flash memory array location.

The device incorporates two Write Buffers of 32

bytes (16 words) to allow optimum-performance

data programming. This feature can improve

system program performance by up to eight times

over non-buffer programming.

28F160S5, 28F320S5 E

6

ADVANCED INFORMATION

Individual block locking uses a com binati on of bl ock

lock-bits to lock and unlock blocks. Block lock-bits

gate block erase, full c hip eras e, program and wri te

to buffer operations. Lock-bit configuration

operations (Set Block Lock-Bit and Clear Block

Lock-Bits commands) set and clear lock-bits.

The status register and the STS pin in RY/BY#

mode indicate whether or not the device is busy

executing an operation or ready for a new

command. Polling the status register, system

software retrieves WSM f eedback. STS i n RY/BY#

mode gives an additional indic ator of WSM activi ty

by providing a hardware status signal. Like the

status register, RY /B Y#-low i ndicat es that the WSM

is performing a block erase, program, or lock-bit

operation. RY/BY#-high indicat es that the WSM is

ready for a new command, block erase is

suspended (and program is inactive), program is

suspended, or the device is in deep power-down

mode.

The Automatic Power Savings (APS) feature

substantially reduces active current when the

device is in static mode (addresses not switching).

The BYTE# pin allows either x8 or x16 read/writes

to the device. BYTE# at logic low selects 8-bit

mode with address A

0

selecting between the low

byte and high byte. BYTE# at logic high enables

16-bit operation with address A

1

becoming the

lowest order address. Address A

0

is not used in

16-bit mode.

When one of the CE

X

# pins (CE0#, CE1#) and RP#

pins are at V

CC

, the component enters a CMOS

standby mode. Driving RP# to GND enables a deep

power-down mode which significantly reduces

power consumption, provides write protection,

resets the device, and c lears the status regist er. A

reset time (t

PHQV

) is required from RP# switching

high until outputs are valid. Likewise, the device

has a wake time (t

PHEL

) from RP#-high until writ es

to the CUI are recognized.

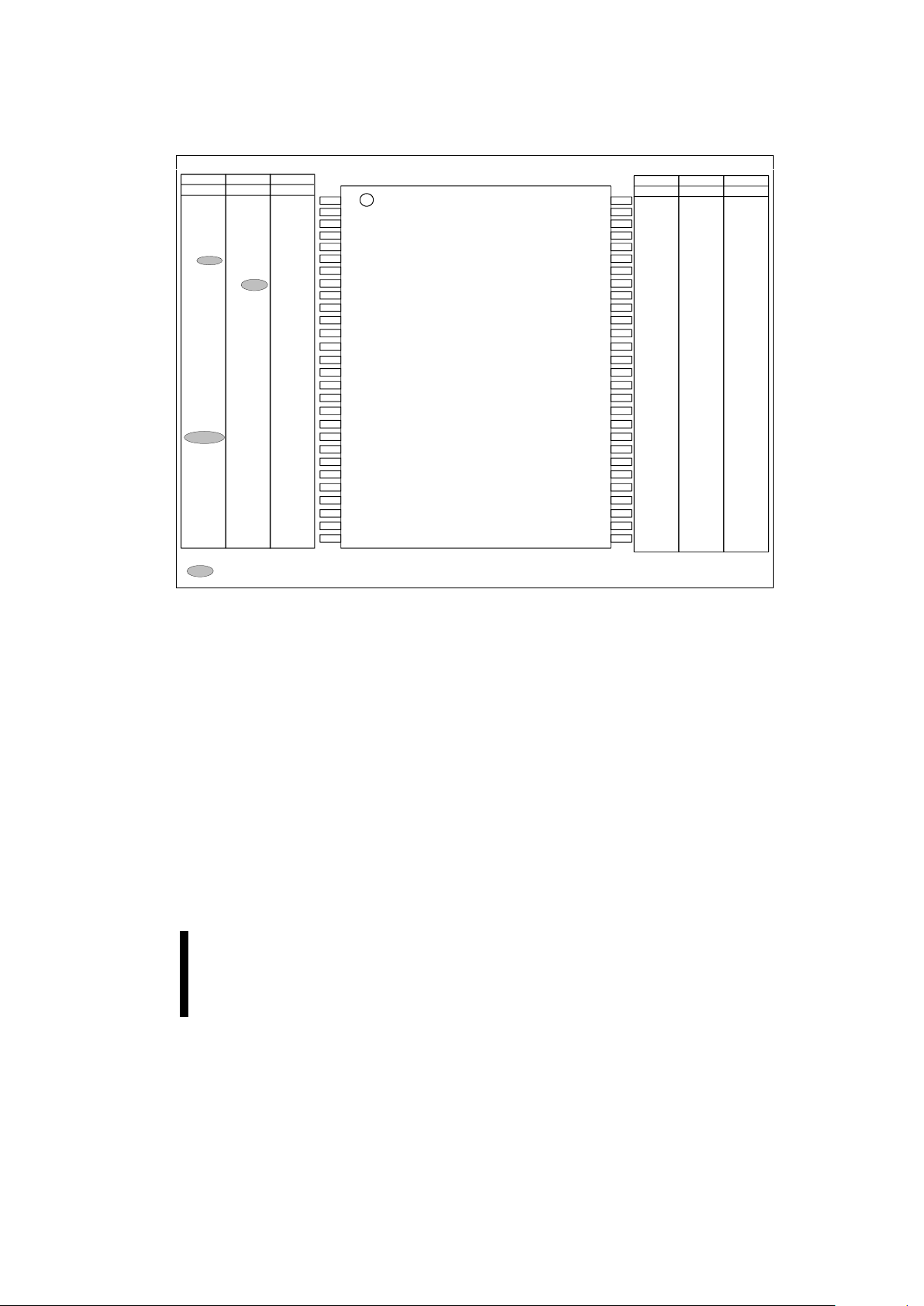

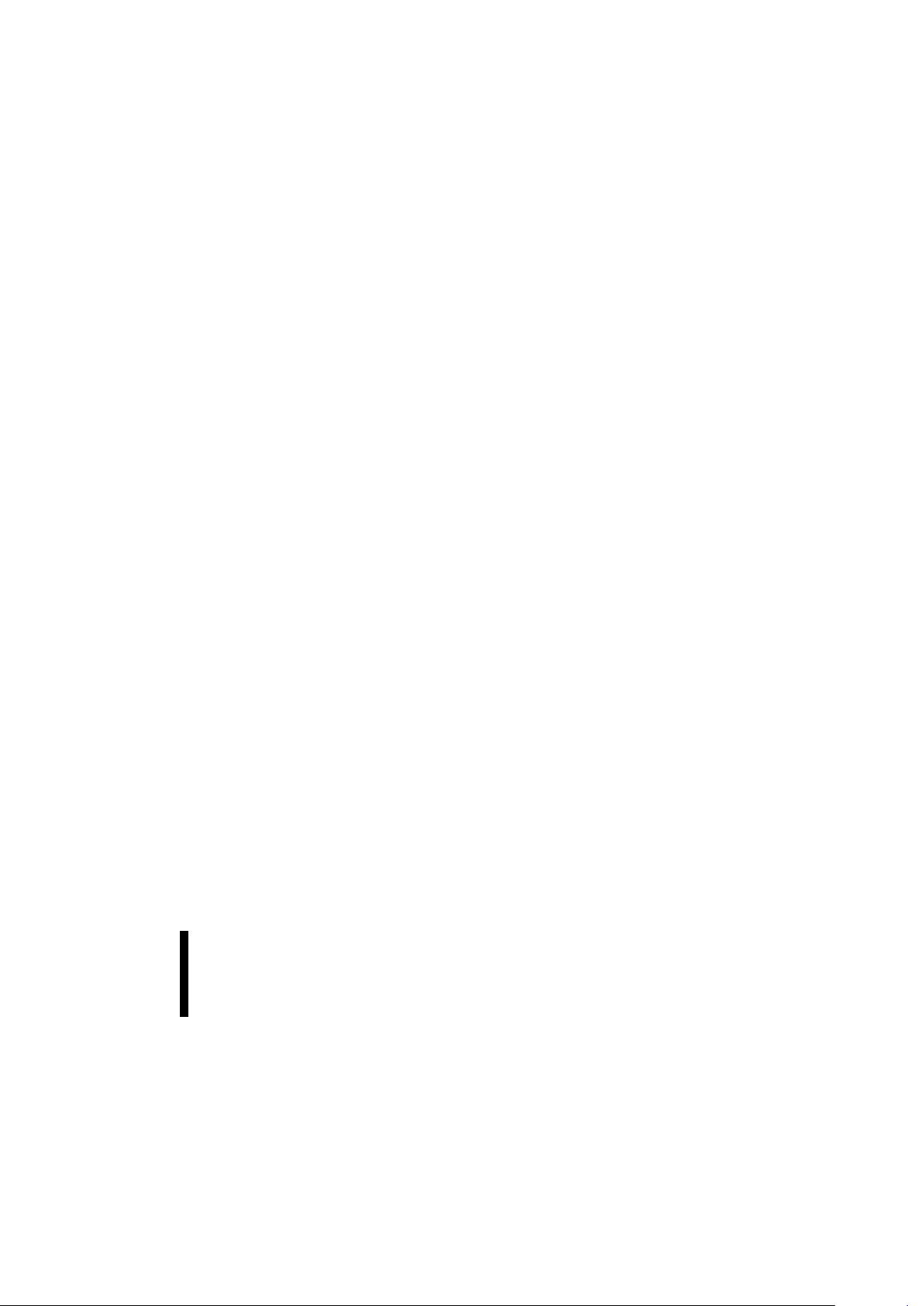

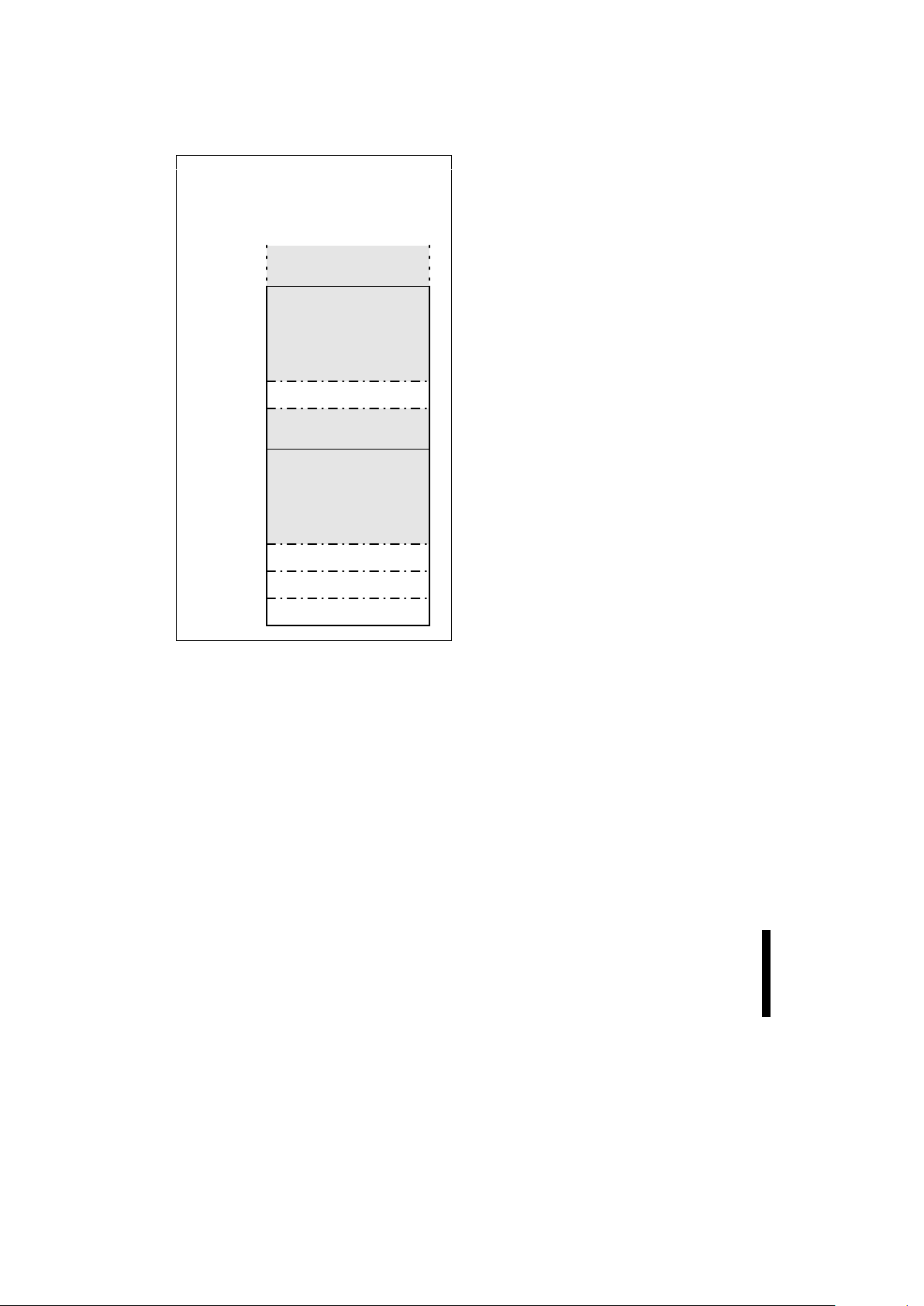

1.3 Pinout and Pin Description

The 16-Mbit device is available in the 56-lead

TSOP and 56-lead SSOP. The 32-Mb device is

available in the 56-lead SSOP. The pinouts are

shown in Figures 2 and 3.

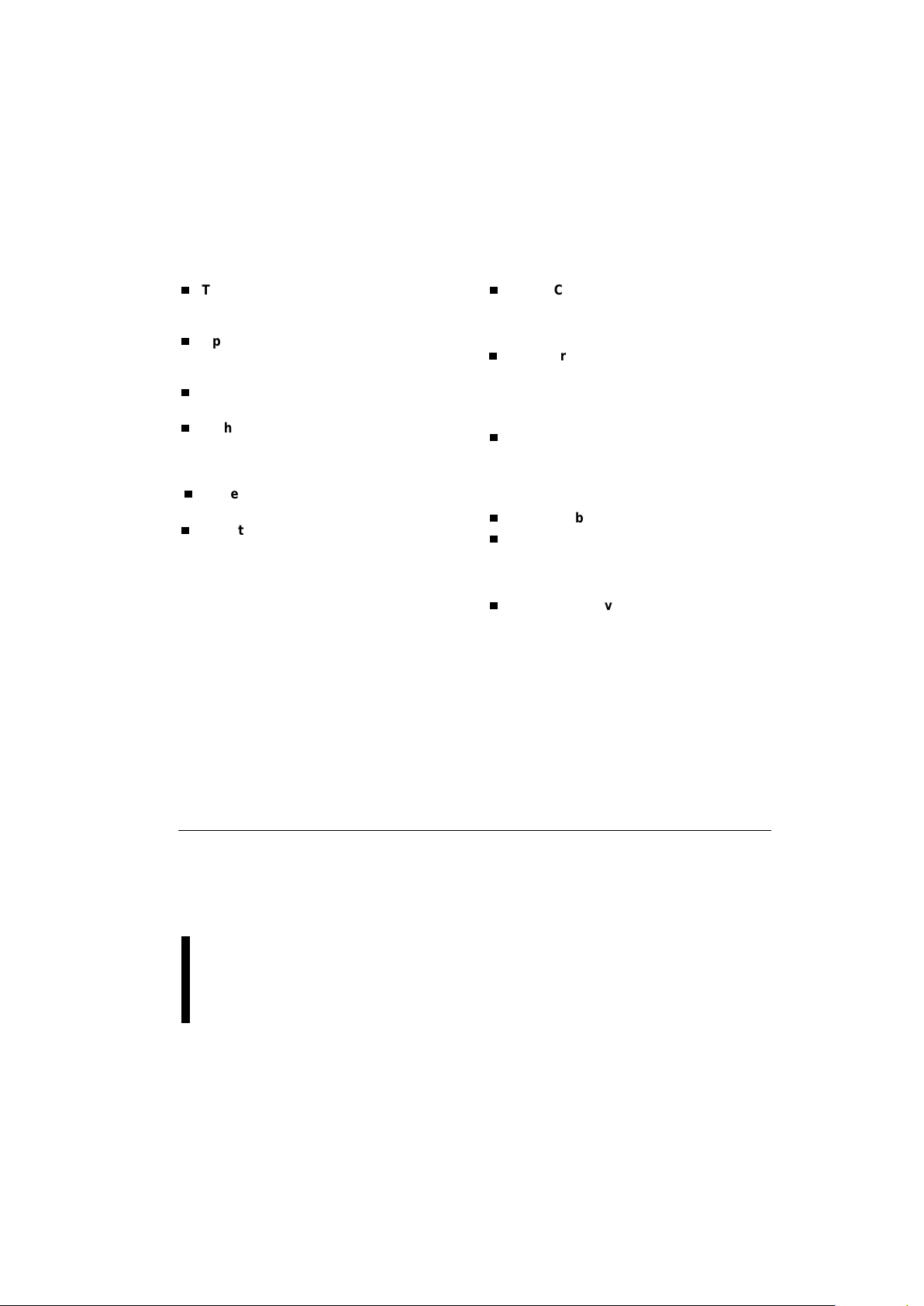

16-Mbit: Thirty-two

32-Mbit: Sixty-four

64-Kbyte Blocks

Input Buffer

Output

Multiplexer

Y-Gating

Program/Erase

Voltage Switch

Data

Comparator

Status

Register

Identifier

Register

Data

Register

I/O Logic

Address

Latch

Address

Counter

X-Decoder

Y-Decoder

Input Buffer

Output Buffer

GND

V

CC

V

PP

CE#

WE#

OE#

RP#

WP#

BYTE#

Command

User

Interface

16-Mbit: A0- A

20

32-Mbit: A

0 - A21

DQ0 - DQ

15

V

CC

Write Buffer

Write State

Machine

Multiplexer

Query

STS

0609_01

Figure 1. 28F320S5 and 28F160S5 Block Diagram

E 28F160S5, 28F320S5

7

ADVANCED INFORMATION

Table 1. Pin Descriptions

Sym Type Name and Function

A0–A

21

INPUT ADDRESS INPUTS: Address inputs for read and write operations are internally

latched during a write cycle. A

0

selects high or low byte when operating in x8 mode.

In x16 mode, A

0

is not used; input buffer is off.

16-Mbit → A

0–A20

32-Mbit → A0–A

21

DQ0–

DQ

15

INPUT/

OUTPUT

DATA INPUT/OUTPUTS: Inputs data and commands during CUI write cycles;

outputs data during memory array, status register, query and identifier code read

cycles. Data pins float to high-impedance when the chip is deselected or outputs

are disabled. Data is internally latched during a write cycle.

CE0#,

CE

1

#

INPUT CHIP ENABLE: Activates the device’s control logic, input buffers, decoders, and

sense amplifiers. With CE0# or CE1# high, the device is deselected and power

consumption reduces to standby levels. Both CE

0

# and CE1# must be low to select

the device. Device selection occurs with the latter falling edge of CE

0

# or CE1#. The

first rising edge of CE

0

# or CE1# disables the device.

RP# INPUT RESET/DEEP POWER-DOWN: When driven low, RP# inhibits write operations

which provides data protection during system power transitions, puts the device in

deep power-down mode, and resets internal automation. RP#-high enables normal

operation. Exit from deep power-down sets the device to read array mode.

OE# INPUT OUTPUT ENABLE: Gates the device’s outputs during a read cycle.

WE# INPUT WRITE ENABLE: Controls writes to the CUI and array blocks. Addresses and data

are latched on the rising edge of the WE# pulse.

STS OPEN

DRAIN

OUTPUT

STATUS: Indicates the status of the internal state machine. When configured in

level mode (default), it acts as a RY/BY# pin. For this and alternate configurations

of the STATUS pin, see the Configuration command. Tie STS to V

CC

with a pull-up

resistor.

WP# INPUT WRITE PROTECT: Master control for block locking. When VIL, locked blocks

cannot be erased or programmed, and block lock-bits cannot be set or cleared.

BYTE# INPUT BYTE ENABLE: Configures x8 mode (low) or x16 mode (high).

V

PP

SUPPLY BLOCK ERASE, PROGRAM, LOCK-BIT CONFIGURATION POWER SUPPLY:

Necessary voltage to perform block erase, program, and lock-bit configuration

operations. Do not float any power pins.

V

CC

SUPPLY DEVICE POWER SUPPLY: Do not float any power pins.

GND SUPPLY GROUND: Do not float any ground pins.

NC NO CONNECT: Lead is not internally connected; it may be driven or floated.

28F160S5, 28F320S5 E

8

ADVANCED INFORMATION

1 56

2 55

3 54

4 53

5 52

6 51

7 50

8 49

9 48

10 47

11 46

12 45

13 44

14 43

15 42

16 41

17 40

18 39

19 38

20 37

21 36

22 35

23 34

24 33

25 32

26 31

27 30

28 29

56-LEAD TSOP

STANDARD PINOUT

14 mm x 20 mm

TOP VIEW

Highlights pinout changes.

WP#

WE#

OE#

RY/BY#

DQ

15

DQ

7

DQ

14

DQ

6

GND

DQ

13

DQ

5

DQ

12

DQ

4

V

CC

GND

DQ

11

DQ

3

DQ

10

DQ

2

V

CC

DQ

9

DQ

1

DQ

8

DQ

0

A

0

BYTE#

NC

NC

28F016SA

28F016SV

RY/BY#

3/5#

CE

1

#

NC

A

20

A

19

A

18

A

17

A

16

V

CC

A

15

A

14

A

13

A

12

CE0#

V

PP

RP#

A

11

A

10

A

9

A

8

GND

A

7

A

6

A

5

A

4

A

3

A

2

A

1

28F016SA

28F016SV

3/5#

NC

CE

1

#

NC

A

20

A

19

A

18

A

17

A

16

V

CC

A

15

A

14

A

13

A

12

CE0#

V

PP

RP#

A

11

A

10

A

9

A

8

GND

A

7

A

6

A

5

A

4

A

3

A

2

A

1

28F160S3

28F160S5

WP#

WE#

OE#

STS

DQ

15

DQ

7

DQ

14

DQ

6

GND

DQ

13

DQ

5

DQ

12

DQ

4

V

CC

GND

DQ

11

DQ

3

DQ

10

DQ

2

V

CC

DQ

9

DQ

1

DQ

8

DQ

0

A

0

BYTE#

NC

NC

28F160S3

28F160S5

0609_02

Figure 2. 28F160S5 TSOP 56-Lead Pinout

E 28F160S5, 28F320S5

9

ADVANCED INFORMATION

56-LEAD SSOP

STANDARD PINOUT

16 mm x 23.7 mm

TOP VIEW

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

28F016SA

NC

WE#

WP#

OE#

GND

A

12

CE #

0

A

13

A

14

A

15

CE #

1

A

20

A

19

A

18

A

17

A

16

V

CC

V

CC

DQ

13

DQ

5

DQ

12

DQ

4

DQ

6

DQ

14

DQ

7

DQ

15

STS

GND

BYTE#

NC

NC

GND

DQ

2

DQ

10

DQ

3

DQ

11

DQ

0

A

0

DQ

8

DQ

1

DQ

9

V

CC

A

8

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

9

A

10

A

11

V

PP

28F016SV

NC

WE#

WP#

OE#

GND

A

12

CE #

0

A

13

A

14

A

15

CE #

1

A

20

A

19

A

18

A

17

A

16

V

CC

V

CC

DQ

13

DQ

5

DQ

12

DQ

4

DQ

6

DQ

14

DQ

7

DQ

15

NC

NC

WE#

WP#

OE#

GND

A

12

CE #

0

A

13

A

14

A

15

CE #

1

A

20

A

19

A

18

A

17

A

16

V

CC

V

CC

DQ

13

DQ

5

DQ

12

DQ

4

DQ

6

DQ

14

DQ

7

DQ

15

28F016SA

GND

BYTE#

NC

NC

GND

DQ

2

DQ

10

DQ

3

DQ

11

DQ

0

A

0

DQ

8

DQ

1

DQ

9

V

CC

A

8

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

9

A

10

A

11

V

PP

28F016SV

GND

BYTE#

NC

NC

GND

DQ

2

DQ

10

DQ

3

DQ

11

DQ

0

A

0

DQ

8

DQ

1

DQ

9

V

CC

A

8

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

9

A

10

A

11

V

PP

STS

R/P#

R/P#

R/P#

RY/BY#

3/5#

A

21

Highlights pinout changes.

28F320S5

28F320S3

28F160S5

28F160S3

28F320S5

28F320S3

28F160S5

28F160S3

0609_03

Figure 3. 28F320S5 and 28F160S5 SSOP 56-Lead Pinout

2.0 PRINCIPLES OF OPERATION

The Word-Wide FlashFile memories include an

on-chip Write State Machine (WSM) to manage

block erase, program, and lock-bit configuration

functions. It allows for: 100% TTL-level control

inputs, fixed power suppli es during bl ock eras ure,

programming, lock-bit conf iguration, and minimal

processor overhead with RAM-like interface

timings.

After initial device power-up or return from deep

power-down mode (see

Bus Operations

), the

device defaults to read array mode. Manipul ation

of external memory control pins all ow array read,

standby, and output disable operations.

Read Array, status regis ter, query, and identifi er

codes can be accessed through the CUI

independent of the V

PP

voltage. Proper

programming voltage on V

PP

enables successful

block erasure, program, and lock-bit

configuration. All functions associated with

altering memory contents—bloc k erase, program,

lock-bit configuration, status, and identifier

codes—are accessed via the CUI and verified

through the status register.

Commands are written using standard microprocessor write timings. The CUI c ontents serve

as input to the WSM that controls the block

erase, programming, and lock-bit configuration.

The internal algorithms are regulated by the

WSM, including pulse repetition, internal

verification, and margining of data. Addresses

and data are internally latched during write

cycles. Writing the appropriate command outputs

array data, identifier codes, or status register

data.

Interface software that initiates and polls

progress of block erase, program ming, and lock-

28F160S5, 28F320S5 E

10

ADVANCED INFORMATION

bit configuration can be stored in any bloc k. This

code is copied to and executed from system

RAM during flash memory updates. After

successful com pletion, reads are again possible

via the Read Array command. Block erase

suspend allows system software to suspend a

block erase to read or write dat a from any other

block. Program suspend all ows system software

to suspend a program to read data from any

other flash memory array location.

2.1 Data Protection

Depending on the application, the system

designer may choose to make the V

PP

power

supply switchable or hardwired to V

PPH

. The

device supports either design practice, and

encourages optimization of the processormemory interface.

When V

PP

≤ V

PPLK

, memory contents cannot be

altered. When high voltage is appli ed to V

PP

, the

two-step block erase, program, or lock-bit

configuration command sequences provide

protection from unwanted operations. All write

functions are disabled when V

CC

voltage is below

the write lockout v oltage V

LKO

or when RP# is at

V

IL

. The device’s block locking capability

provides additional protection from inadvertent

code or data alteration.

3.0 BUS OPERATION

The local CPU reads and writes fl ash mem ory i nsystem. All bus cycles to or from the flash

memory conform to standard mic roprocessor bus

cycles.

3.1 Read

Block information, query information, identifier

codes and status registers can be read

independent of the V

PP

voltage.

The first task is to place the device into the

desired read mode by writing the appropriate

read-mode command (Read Array, Query, Read

Identifier Codes, or Read Stat us Register) to the

CUI. Upon initial device power-up or after exit

from deep power-down mode, the device

automatically reset s to read array mode. Control

pins dictate the data flow in and out of the

component. CE

0

#, CE1# and OE# must be driven

active to obtain data at the outputs. CE

0

# and

CE

1

# are the device selection controls, and,

when both are active, enable the selected

memory device. OE# is the data output (DQ

0

–

DQ

15

) control: When active it drives the selected

memory data onto the I/O bus. WE # must be at

V

IH

and RP# must be at VIH. Figure 16 illustrates

a read cycle.

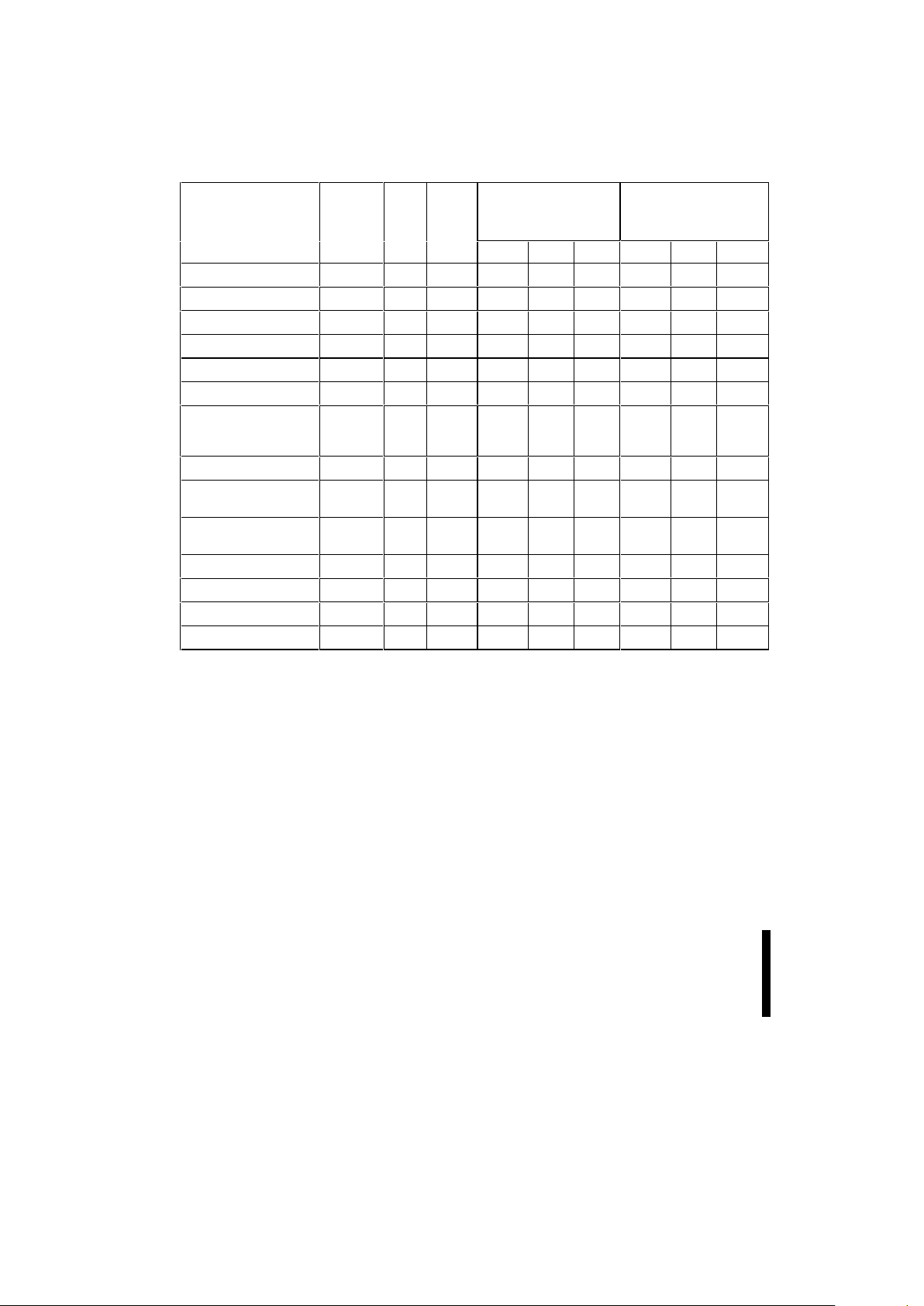

64-Kbyte Block

3FFFFF

3F0000

63

64-Kbyte Block

1FFFFF

1F0000

31

64-Kbyte Block

01FFFF

010000

1

64-Kbyte Block

00FFFF

000000

0

32-Kword Block

1FFFFF

1F0000

63

32-Kword Block

0FFFFF

0F8000

31

32-Kword Block

00FFFF

008000

1

32-Kword Block

007FFF

000000

0

32-Mbit: A[

21-1

]

16-Mbit: A[

20-1

]

32-Mbit: A[

21-0

]

16-Mbit: A[

20-0

]

Byte-Wide (x8) Mode

Word-Wide (x16) Mode

16 Mbit

32 Mbit

0609_04

Figure 4. Memory Map

E 28F160S5, 28F320S5

11

ADVANCED INFORMATION

3.2 Output Disable

With OE# at a logic-high level (VIH), the device

outputs are disabled. Output pi ns DQ

0

–DQ15 are

placed in a high-impedance state.

3.3 Standby

CE0# or CE1# at a logic-high level (VIH) places

the device in standby mode, substantially

reducing device power consumption. DQ

0

–DQ

15

(or DQ0– DQ7 in x8 mode) outputs are placed in

a high-impedance state independent of OE#. If

deselected during block erase, programming, or

lock-bit configuration, the device continues

functioning and consuming acti ve power until the

operation completes.

3.4 Deep Power-Down

RP# at VIL initiates the deep power-down mode.

In read mode, RP#-low deselects the memory,

places output drivers in a high-impedance state,

and turns off all internal circuits. RP# must be

held low for time t

PLPH

. Time t

PHQV

is required

after return from power-down until initial memory

access outputs are valid. After this wake-up

interval, normal operation is restored. The CUI

resets to read array mode, and the status regis ter

is set to 80H.

During block erase, programming, or lock-bit

configuration modes, RP#-low will abort the

operation. STS in RY/BY# mode remains low

until the reset operation is complete. Memory

contents being altered are no longer valid; the

data may be partially corrupted after

programming or partially altered aft er an erase or

lock-bit configuration. Ti me t

PHWL

is required after

RP# goes to logic-high (V

IH

) before another

command can be written.

It is important in any automated system to assert

RP# during system reset. When the system

comes out of reset, it expects to read from the

flash memory. Automated flash memories

provide status informat ion when access ed during

block erase, programming, or lock-bit

configuration modes. I f a CPU reset occurs with

no flash memory reset, proper CPU initialization

may not occur because the f las h memory may be

providing status inform ation i nst ead of array data.

Intel’s Flash memories allow proper CPU

initialization following a system reset through the

use of the RP# input. In t his application, RP# is

controlled by the same RESET# signal that

resets the system CPU.

3.5 Read Query Operation

The read query operation outputs block status,

Common Flash Interface (CFI) ID string, system

interface, device geometry, and Intel-specific

extended query information.

3.6 Read Identifier Codes

Operation

The read-identifier codes operation outputs the

manufacturer code, devic e code, and block lock

configuration codes for eac h block configuration

(see Figure 5). Using the manufacturer and

device codes, the system software can

automatically match the device with its proper

algorithms. The block-lock configuration codes

identify each block’s lock-bit setting.

28F160S5, 28F320S5 E

12

ADVANCED INFORMATION

Reserved for Future

Implementation

(Subsequent Blocks)

Reserved for Future

Implementation

Block 1 Lock Configuration

Reserved for Future

Implementation

Device Code

Manufacturer Code

Block 0

Block 1

Word

Address

0FFFF

08004

08003

08002

08000

07FFF

00004

00003

00002

00001

00000

A[

20-1

]: 16-Mbit

A[

21-1

]: 32-Mbit

Block 0 Lock Configuration

0609_05

Figure 5. Device Identifier Code Memory Map

3.7 Write

Writing commands to the CUI enables reading of

device data, query, identifier codes, inspection

and clearing of the status register. Additionally,

when V

PP

= V

PPH

, block erasure, programming,

and lock-bit configuration can also be performed.

The Block Erase command requires appropriate

command data and an address within the block

to be erased. The Byte/Word Write command

requires the command and address of the

location to be written. Set Block Lock-Bit

commands require the command and address

within the block to be locked. The Clear Block

Lock-Bits command requires the command and

an address within the device.

The CUI does not occupy an addressable

memory location. I t is written when WE#, CE

0

#,

and CE

1

# are active and OE# = VIH. The address

and data needed to execute a command are

latched on the rising edge of WE# or CE

X

#

(CE

0

#, CE1#), whichever goes high first.

Standard microprocessor writ e timings are used.

Figure 17 illustrates a write operation.

4.0 COMMAND DEFINITIONS

VPP voltage ≤ V

PPLK

enables read operations

from the status register, identifier codes, or

memory blocks. Placing V

PPH

on VPP enables

successful bloc k erase, programming, and lockbit configuration operations.

Device operations are select ed by writi ng s peci fi c

commands into the CUI. Table 2 and Table 3

define these commands.

E 28F160S5, 28F320S5

13

ADVANCED INFORMATION

Table 2. Bus Operations

Mode Notes RP# CE0#CE1# OE#

(11)

WE#

(11)

Address V

PP

DQ

(8)

STS

(3)

Read 1,2 V

IH

V

IL

V

IL

V

IL

V

IH

XXD

OUT

X

Output Disable V

IH

V

IL

V

IL

V

IH

V

IH

X X High Z X

Standby V

IH

V

IL

V

IH

V

IH

V

IH

V

IL

V

IH

X X X X High Z X

Reset/PowerDown Mode

10 V

IL

X X X X X X High Z High Z

(9)

Read Identifier

Codes

4VIHV

IL

V

IL

V

IL

V

IH

See

Figure 5

XD

OUT

High Z

(9)

Read Query 5 V

IH

V

IL

V

IL

V

IL

VIHSee Table 6 X D

OUT

High Z

(9)

Write 3,6,7 V

IH

V

IL

V

IL

V

IH

V

IL

XV

PPH

D

IN

X

NOTES:

1. Refer to

DC Characteristics

. When VPP ≤ V

PPLK

, memory contents can be read, but not altered.

2. X can be V

IL

or VIH for control and address input pins and V

PPLK

or V

PPH

for VPP. See

DC Characteristics

, for V

PPLK

and

V

PPH

voltages.

3. STS in RY/BY# mode (default) is V

OL

when the WSM is executing internal block erase, programming, or lock-bit

configuration algorithms. It is V

OH

when the WSM is not busy, in block erase suspend mode (with programming inactive),

program suspend mode, or deep power-down mode.

4. See Section 4.3 for read identifier code data.

5. See Section 4.2 for read query data.

6. Command writes involving block erase, write, or lock-bit configuration are reliably executed when V

PP

= V

PPH

and

V

CC

= V

CC1/2

(see Section 6.2).

7. Refer to Table 3 for valid D

IN

during a write operation.

8. DQ refers to DQ

0–7

if BYTE# is low and DQ

0–15

if BYTE# is high.

9. High Z will be V

OH

with an external pull-up resistor.

10. RP# at GND ± 0.2 V ensures the lowest deep power-down current.

11. OE# = V

IL

and WE# = VIL concurrently is an undefined state and should not be attempted.

28F160S5, 28F320S5 E

14

ADVANCED INFORMATION

Table 3. Word-Wide FlashFile™ Memory Command Set Definitions

(13)

Command Scaleable

or Basic

Command

Set

(14)

Bus

Cycles

Req'd

Notes First Bus Cycle Second Bus Cycle

Oper

(1)

Addr

(2)

Data

(3,4)

Oper

(1)

Addr

(2)

Data

(3,4)

Read Array SCS/BCS 1 Write X FFH

Read Identifier Codes SCS/BCS ≥2 5 Write X 90H Read IA ID

Read Query SCS ≥ 2 Write X 98H Read QA QD

Read Status Register SCS/BCS 2 Write X 70H Read X SRD

Clear Status Register SCS/BCS 1 Write X 50H

Write to Buffer SCS > 2 8, 9, 10 Write BA E8H Write BA N

Word/Byte Program SCS/BCS 2 6,7 Write X 40H

or

10H

Write PA PD

Block Erase SCS/BCS 2 6,10 Write X 20H Write BA D0H

Block Erase, Word/Byte

Program Suspend

SCS/BCS 1 6 Write X B0H

Block Erase, Word/Byte

Program Resume

SCS/BCS 1 6 Write X D0H

STS pin Configuration SCS 2 Write X B8H Write X CC

Set Block Lock-Bit SCS 2 11 Write X 60H Write BA 01H

Clear Block Lock-Bits SCS 2 12 Write X 60H Write X D0H

Full Chip Erase SCS 2 10 Write X 30H Write X D0H

E 28F160S5, 28F320S5

15

ADVANCED INFORMATION

NOTES:

1. Bus operations are defined in Table 2.

2. X = Any valid address within the device.

BA = Address within the block being erased or locked.

IA = Identifier Code Address: see Table 12.

QA = Query database Address.

PA = Address of memory location to be programmed.

3. ID = Data read from Identifier Codes.

QD = Data read from Query database.

SRD = Data read from status register. See Table 15 for a description of the status register bits.

PD = Data to be programmed at location PA. Data is latched on the rising edge of WE#.

CC = Configuration Code. (See Table 14.)

4. The upper byte of the data bus (DQ

8–15

) during command writes is a “Don’t Care” in x16 operation.

5. Following the Read Identifier Codes command, read operations access manufacturer, device, and block-lock codes. See

Section 4.3 for read identifier code data.

6. If a block is locked (i.e., the block’s lock-bit is set to 0), WP# must be at V

IH

in order to perform block erase, program and

suspend operations. Attempts to issue a block erase, program and suspend operation to a locked block while WP# is V

IL

will fail.

7. Either 40H or 10H are recognized by the WSM as the byte/word program setup.

8. After the Write to Buffer command is issued, check the XSR to make sure a Write Buffer is available.

9. N = byte/word count argument such that the number of bytes/words to be written to the input buffer = N + 1. N = 0 is 1

byte/word length, and so on. Write to Buffer is a multi-cycle operation, where a byte/word count of N + 1 is written to the

correct memory address (WA) with the proper data (WD). The Confirm command (D0h) is expected after exactly N + 1 write

cycles; any other command at that point in the sequence aborts the buffered write. Writing a byte/word count outside the

buffer boundary causes unexpected results and should be avoided.

10. The write to buffer, block erase, or full chip erase operation does not begin until a Confirm command (D0h) is issued.

Confirm also reactivates suspended operations.

11. A block lock-bit can be set only while WP# is V

IH

.

12. WP# must be at V

IH

to clear block lock-bits. The clear block lock-bits operation simultaneously clears all block lock-bits.

13. Commands other than those shown above are reserved for future use and should not be used.

14. The Basic Command Set (BCS) is the same as the 28F008SA Command Set or Intel Standard Command Set. The

Scaleable Command Set (SCS) is also referred to as the Intel Extended Command Set.

28F160S5, 28F320S5 E

16

ADVANCED INFORMATION

4.1 Read Array Command

Upon initial device power-up and after exit from

deep power-down mode, the device defaul t s to read

array mode. This operation is also initiated by

writing the Read Array command. The device

remains enabled for reads until another c ommand

is written. Once the int ernal WSM has start ed bloc k

erase, program, or lock-bit confi guration, the dev ice

will not recognize the Read Array command until

the WSM completes it s operation—unless the WSM

is suspended via an Erase-Suspend or ProgramSuspend command. The Read Array command

functions independently of the V

PP

voltage.

4.2 Read Query Mode Command

This section defines the data structure or

“database” returned by the Common Fl ash Interface

(CFI) Query command. System software should

parse this structure t o gain critic al information such

as block size, density, x8/x16, and electrical

specifications. Once this information has been

obtained, the software will know which command

sets to use to enable flash writes, block erases, and

otherwise control the flas h component. The Query

is part of an overall specification for multiple

command set and control interface descriptions

called Common Flash Interface, or CFI.

4.2.1 QUERY STRUCTURE OUTPUT

The Query “database” allows system software to

gain critical information for controlling the flash

component. This section describes the device’s

CFI-compliant interface that allows the host system

to access Query data.

Query data are always presented on the lowestorder data outputs (DQ

0-7

) only. The numerical

offset value is the address relat ive to the maxi mum

bus width supported by the device. On t his device,

the Query table device starting address is a 10h

word address, since the maximum bus width is x16.

For this word-wide (x16) device, t he first two bytes

of the Query structure, “Q” and ”R” in ASCII, appear

on the low byte at word addresses 10h and 11h.

This CFI-compliant device outputs 00H data on

upper bytes. Thus, the devi ce outputs ASCII “Q” in

the low byte (DQ

0-7

) and 00h in the high byte

(DQ

8-15

).

Since the device is x 8/x16 capable, the x8 data is

still presented in word-relative (16-bit) addresses.

However, the “fill data” (00h) is not the same as

driven by the upper bytes in the x16 mode. As in

x16 mode, the byte address (A

0

) is ignored for

Query output so that the “odd byte address” (A

0

high) repeats the “even byte address” data (A0 low).

Therefore, in x8 mode using byte addressing, the

device will output the sequence “Q”, “Q”, “R”, “R”,

“Y”, “Y”, and so on, beginning at byte-relative

address 20h (which is equivalent to word offs et 10h

in x16 mode).

At Query addresses containing two or more byt es

of information, the least significant data byte is

presented at the lower address, and the most

significant data byte is presented at the higher

address.

Loading...

Loading...