Intel Corporation AN87C196CA Datasheet

87C196KR, 87C196JV, 87C196JT,

87C196JR, and 87C196CA Advanced

16-Bit CHMOS Microcontrollers

Automotive

Datasheet

Product Features

■ –40 °C to +125°C Ambient

■ High Performance CHMOS 16-Bit CPU

■ Up to 48 Kbytes of On-Chip EPROM

■ Up to 1.5 Kbytes of On-Chip Register

RAM

■ Up to 512 Bytes of Addi ti onal RAM (Co de

RAM)

■ Register-Register Architecture

■ Up to Eight Channel/10-Bit A/D with

Sample/Hold

■ Up to 37 Prioritize d Interrupt Source s

■ Up to Seven 8-Bit (56) I/O Ports

■ Full Duplex Serial I/O Port

■ Dedicated Baud Rate Generator

■ Interprocessor Communication Slave Port

■ High Speed Peripheral Transaction Server

(PTS)

■ Two 16-Bit Softw are Timers

■ Up to 10 High Sp eed Capture/Co mpare

(EPA)

■ Full Duplex Synchronous Serial I/O Port

(SSIO)

■ Two Flexible 16-Bit Timer/Counters

■ Quadrature Count in g Input s

■ Flexible 8-/16-Bit External Bus

■ Programmable Bus (HLD/HLDA)

■ 1.75 µs 16 x 16 Multiply

■ 3 µs 32/16 Divide

■ 68-Pin and 52-Pin PLCC Packages

■ Supports CAN (Controller Area Network)

Specification 2.0 (CA only)

Order Number: 270827-0 07

April 1998

Datasheet

Informa ti on in this doc um ent is provi ded i n connectio n wi t h Intel prod uc t s. No license, ex pr ess or impli ed, by estoppe l or ot h e rwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and In t el disclaims any exp r ess or implied warranty, rel at ing to sale and/or use of Inte l products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 87C196KR, JV, JT, JR and CA microcontrollers may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-

548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © I ntel Corpor at i on, 1998

*Third-party brands and names are the property of their respective owners.

Datasheet 3

Automotive —

87C196KR, JV, JT, JR, and CA Microcontrollers

Contents

1.0 Introduction..................................................................................................................5

2.0 Architecture..................................................................................................................6

2.1 CPU Featu re s...... .. ............ ........... ............ ........... .. ............ ........... ............ ........... ..6

2.2 Peripheral Features...............................................................................................6

2.3 New Instr u ct io n s.................... ............ .. ............ ........... ........... ............ ........... ... ......7

2.3.1 XCH/XC HB........ ............ ........... ............ .. ............ ........... ........... ............ ....7

2.3.2 BMOVi.... ........... ............ .. ............ ........... ............ ........... ........... ... ........... ..7

2.3.3 TIJMP.............. .. ............ ........... ............ ........... ............ .. ........... ............ ....7

2.3.4 EPTS/D P T S ......... .. .. ............ ........... ............ ........... ............ .. ........... .........7

2.4 SFR Opera tion ............... ... ........... .. ............ ........... ............ ........... ............ .. ...........7

3.0 Packaging Information.............................................................................................9

4.0 Electrical Characteristics......................................................................................14

4.1 Absolute M a x im u m R a ti ng s...... .. .. ............ ........... ............ .. ........... ............ ...........14

4.2 Operatin g C ond itions........... ........... ............ ........... ... ........... ............ ........... .........14

4.3 DC Charac te ristics ............ .. ........... ............ ........... ... ........... ............ ........... .........15

4.4 AC Characteristics...... .. .. ............ ........... ............ ........... ............ .. ........... ............ ..18

4.4.1 Explanation of AC Symbols ....................................................................23

4.4.2 EPROM Specifications...........................................................................23

4.4.3 A to D Converter Specifications .............................................................25

4.4.4 AC Charac te r is tics—Slav e P o rt ......... ........... ........... ............ ........... .......28

4.4.5 AC Characteristics—Serial Port— Shift Register Mode.........................30

4.4.6 Waveform—Serial Port—Shift Register Mode 0 ........ ......................... ...30

5.0 52-Lead Devices .......................................................................................................31

6.0 Design Considerations..........................................................................................32

6.1 87C196KR, JV, JT, JR, and CA Design Considerations.....................................32

6.2 87C196JR C-step to JR D-step – or – JV/JT A-step Design

Considerations ....................................................................................................33

6.2.1 87C196CA Design Considerations...................................... .. .................36

7.0 Revision History.......................................................................................................37

87C196KR, JV, JT, JR, and CA Microcontroller s

— Automotive

4 Datasheet

Figures

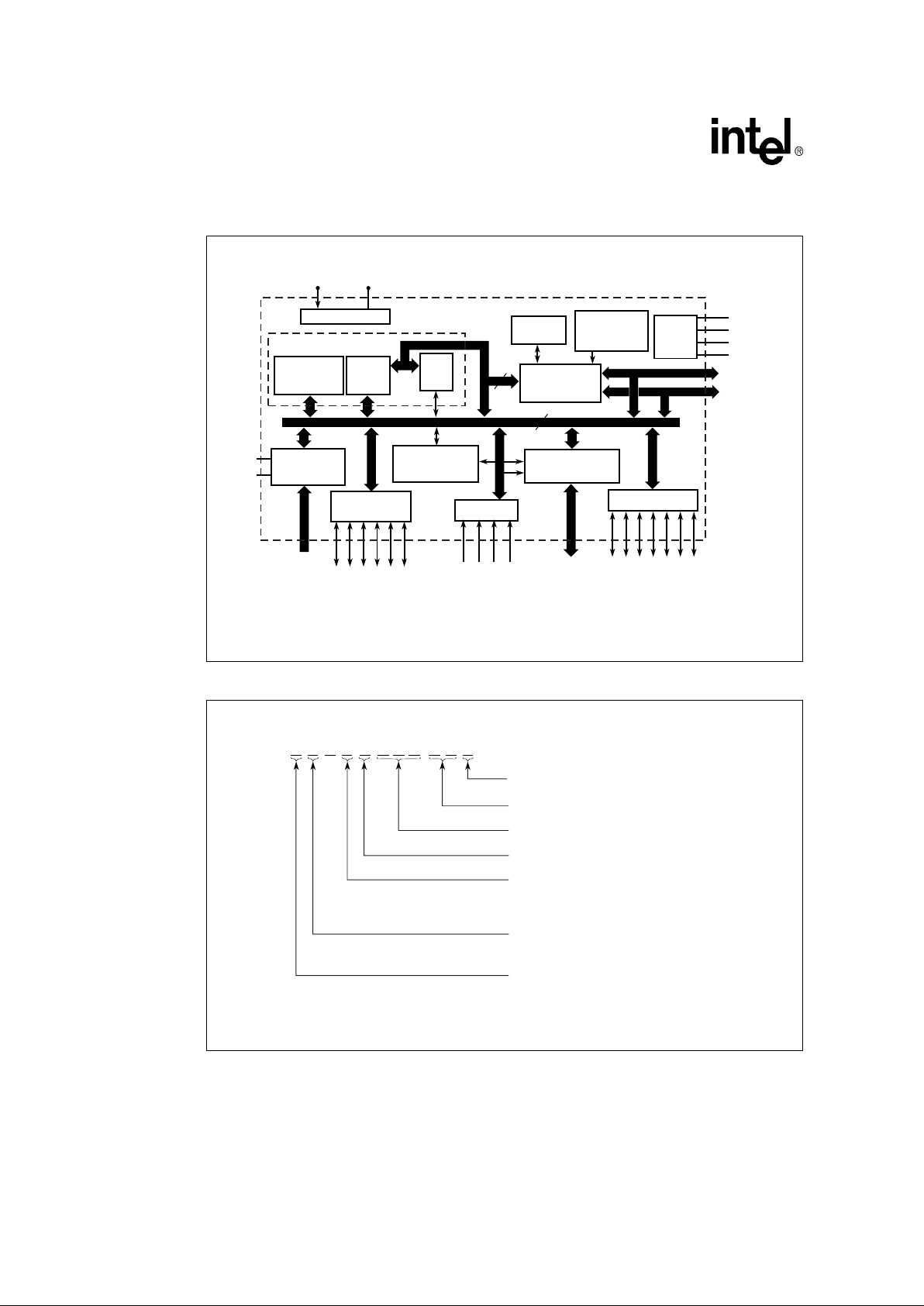

1 Block Diagram.......................................................................................................8

2 8XC196Kx, Jx, and CA Family Nomenclature ......................................................8

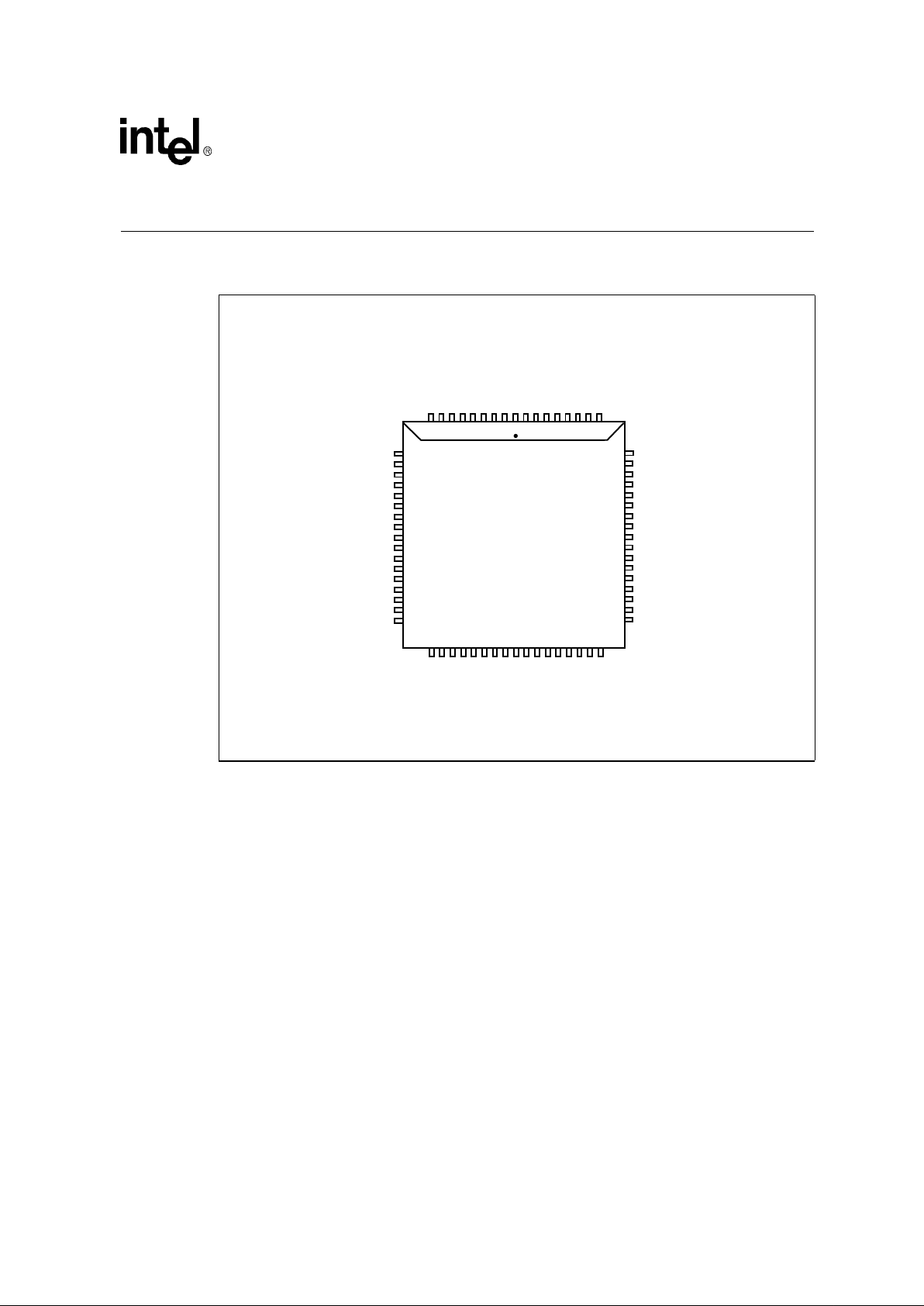

3 87C196KR 68-Pin PLCC Package Diagram.........................................................9

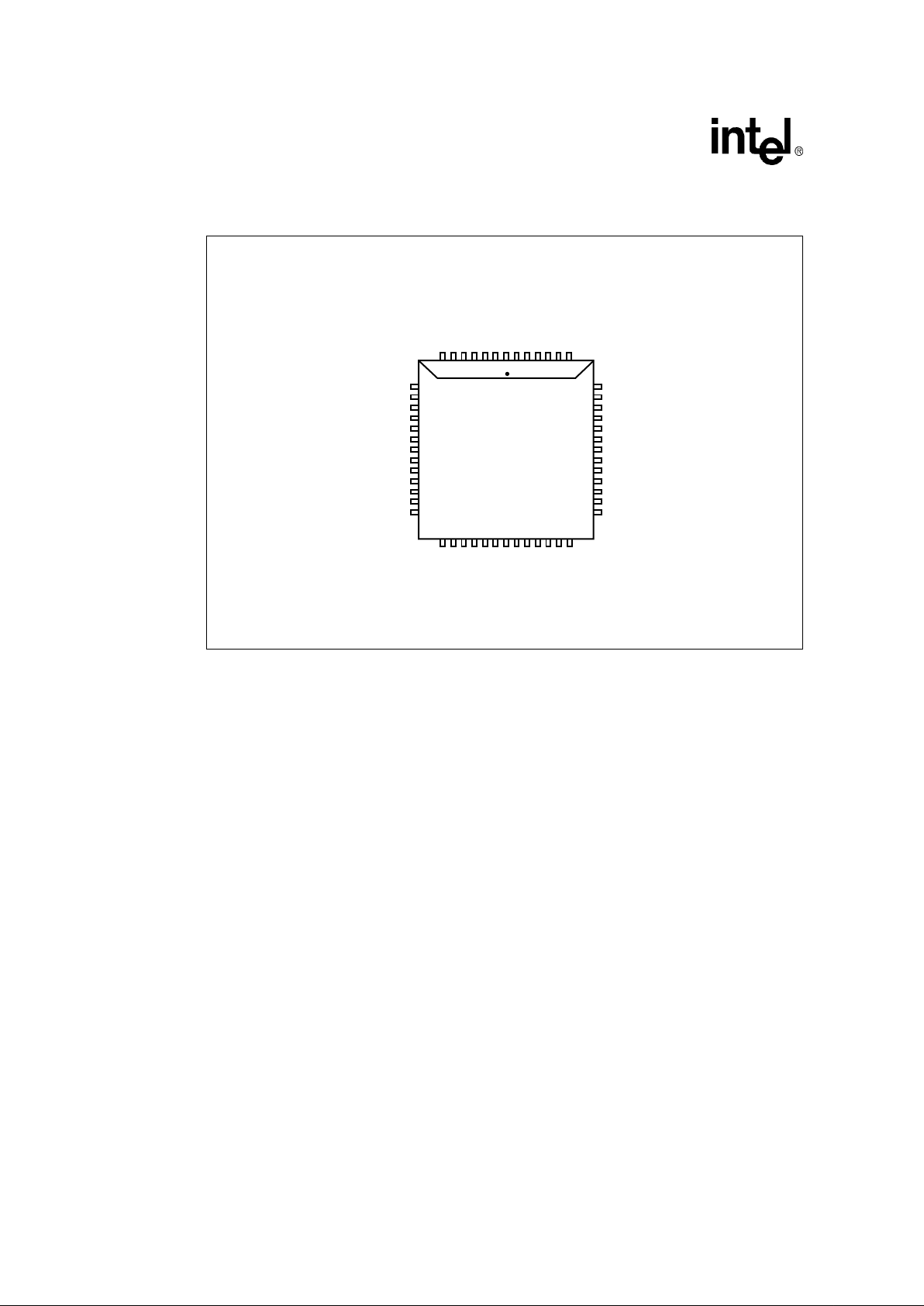

4 87C196JV, JT, JR 52-Pin PLCC Package Diagram ...........................................10

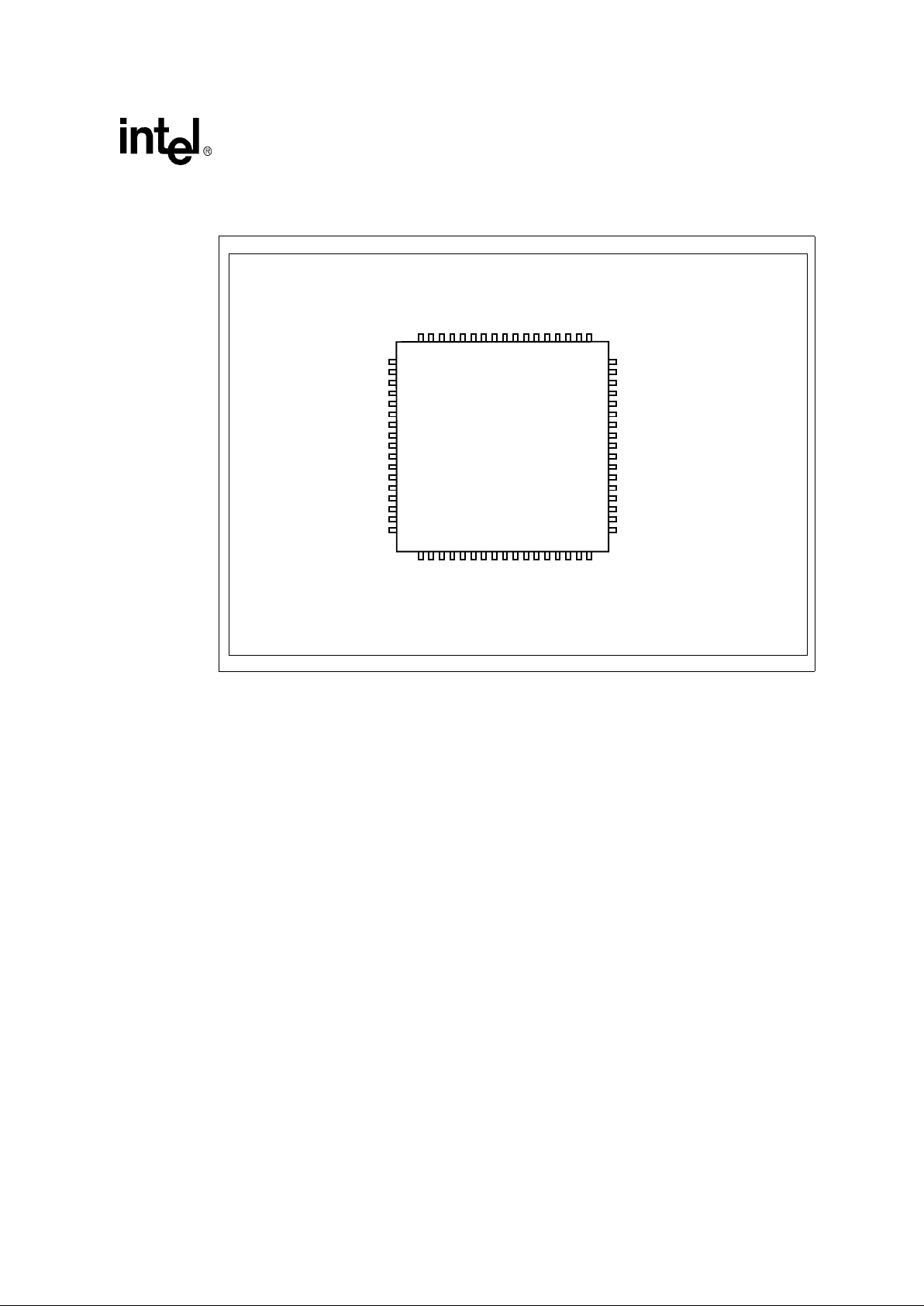

5 87C196CA 68-Pin PLCC Package Diagram.......................................................11

6 87C196KR and JR I

CC

vs. Frequency.............. .......... ........... ..................... .........16

7JT I

CC

vs. Frequency ..........................................................................................17

8 87C196CA I

CC

vs. Frequency.............................................................................17

9 System Bus Timing .............................................................................................20

10 READY/Buswidth Timing ....................................................................................21

11 External Clock Drive Waveforms ........................................................................21

12 AC Testing Input, Output Waveforms ................... ............ ..................................22

13 Float Wav e fo rms......... ........... ........... ... ........... ............ ........... ............ ........... .. ....22

14 Slave Programmin g Mode Data Program Mode with Single

Program Pulse .................................................................................................... 24

15 Slave Programmin g Mode in Word Dump or Data Verif y Mode wit h

Auto Increment.................................................................................................... 24

16 Slave Programming Mode Timing in Data Program Mode with

Repeated PROG Pulse and Auto Increment............. .............. .. ..........................25

17 HOLD Timin g s... ... .. ........... ............ ........... ............ ........... ... ........... ........... ...........27

18 Slave Port Waveform (SLPL = 0)........................................................................28

19 Slave Port Waveform (SLPL = 1)........................................................................29

20 Serial Port Waveform—Shift Register Mode.......................................................30

Tables

1 87C196Kx and Jx Features Summary ..................................................................6

1 Pin Descri p tio n s .............. ............ .. ........... ............ ........... ............ ........... .. ...........12

2 Absolute Maximum Ratings ................................................................................14

3 Operating Conditi ons................ ............ ............ ............. ............ .........................14

4 DC Characteristics ..............................................................................................15

5 AC Characteristics ..............................................................................................18

6 External Clock Drive............................................................................................21

7 Thermal Ch a ra c te ristics ....... ........... .. ............ ........... ............ ........... ............ .. ......22

8 AC EPROM Programming Characteristics..........................................................23

9 DC EPROM Programming Characteristics .........................................................24

10 A/D Operating Conditions ...................................................................................25

11 A/D Operating Parameter Values........................................................................26

12 HOLD#/HL D A # T imings................ ........... ............ ........... ... ........... ........... ...........27

13 DC Specifications in HOLD .................................................................................27

14 Slave Port Timing–( SLPL = 0)................. .............. .. ............................ .. ..............28

15 Slave Port Timing–( SLPL = 1)................. .............. .. ............................ .. ..............29

16 Serial Port Timing—Shift Register Mode ............................................................30

Automotive —

87C196KR, JV, JT, JR, CA Microcontrollers

Datasheet 5

1.0 Introduction

The MCS 96 microcontroller family members are all high performance microcontrollers with a 16bit CPU.

The 87C196Kx and Jx family members are composed of the high-speed (16 MHz) core as well as

the following peripherals:

• Up to 48 Kbytes of Programmable EPROM

• Up to 1.5 Kbytes of reg ister RAM and 512 bytes of cod e RAM (16-bit addres sing mode s) with

the ability to execute from this RAM space

• Up to eight channels–10-Bit/ ± 3 LSB analog to digital converter with programmable S/H

times with conversion times < 5 µs at 16 MHz

• An asynchronous/synchronous serial I/O port (8096 compatible) with a dedicated 16-bit baud

rate generator

• Interprocessor communication slave port

• Synchronous serial I/O port with full duplex master/slave transceivers

• A flexible timer/counter structure with prescaler, cascading, and quadrature capabilities

• Up to ten modularized multiplexed high speed I/O for capture and compare (called Event

Processor Array) with 250 ns resolution and double buffered inputs

• A sophisticated prioritized interrupt structure with programmable Peripheral Transaction

Server (PTS). The PTS has several channel modes, including sing le/burst bloc k t ran sf ers from

any memory location to any memory location, a PWM and PWM toggle mode to be used in

conjunction with the EPA, and an A/D scan mode.

• Serial communications protocol CAN 2.0 with 15 message objects of 8 bytes data length (CA

only)

The 87C196KR, JV, JT, JR, and CA devices represent the fourth generation of MCS

®

96

microcontroller products implemented on Intel’s advanced 1 micron process technology. These

products are based on the 80C196KB device with improvements for automotive applications. The

instruction set is a true super set of 80C196KB. The 87C196JR, JT, and JV are 52-pin versions of

the 87C196KR device.

The 87C196JV and JT devices are memory scalars of the 87C196JR and are designed for strict

functional and electrical compatibility. The JT has 32 Kbytes of on-chip EPROM, 1.0 Kbytes of

Register RAM and 512 byt es of Co de RAM. The J V has 48 Kby tes of on-chi p EPROM, 1.5 Kb ytes

of Register RAM and 512 bytes of Code RAM.

The 87C196CA device is a mem ory s calar of the 87C196KR i n a 6 8-pin p ackage with 32 Kbyt es of

on-chip EPROM, 1.0 Kbytes of register RAM, and 256 bytes of code RAM. In addition, the CA

contains an extra peripheral for serial communications protocol CAN 2.0.

Table 1 summarizes the features of the 87C196Kx, Jx, and CA devices.

87C196KR, JV, JT, JR, CA Microcontrollers

— Automotive

6 Datasheet

Refer to the following datasheets for higher frequency versions of devices contained within this

datasheet:

• 87C196JT 20 MHz Advanced 16-Bit CHMOS Microcontroller datasheet, order #272529

• 87C196JV 20 MHz Advanced 16-Bit CHMOS Microcontroller datasheet, order #272580.

2.0 Architecture

The 87C196KR, JV, JT, JR, and CA are members of the MCS 96 microcontroller family, have the

same architecture and use the same instruction set as the 80C196KB/KC. Many new features have

been added including:

2.1 CPU Features

• Powerdown and Idle Modes

• 16 MHz Operating Frequency

• A High Performance Peripheral Transaction Server (PTS)

• Up to 37 Interrupt Vectors

• Up to 512 Bytes of Code RAM

• Up to 1.5 Kbytes of Register RAM

• “Windowing” Allows 8-Bit Addressing to Some 16-Bit Addresses

• 1.75

µ

s 16 x 16 Multiply

• 3 µs 32/16 Divide

• Oscillator Fail Detect

2.2 Peripheral Features

• Programmable A/D Conversion and S/H Times

• Up to 10 Capture/Compare I/O with 2 Flexible Timers

• Synchronous Serial I/O Port for Full Duplex Serial I/O

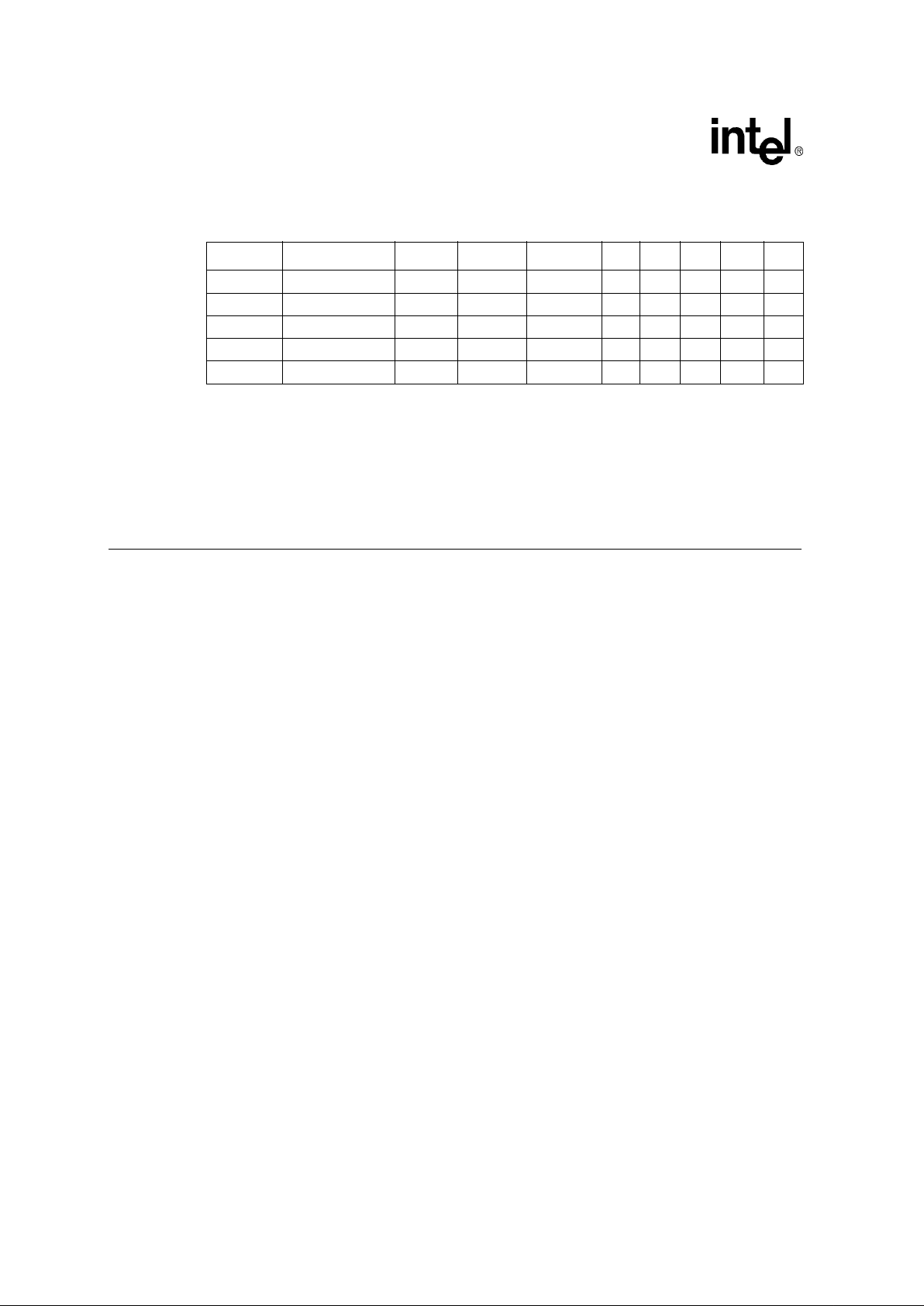

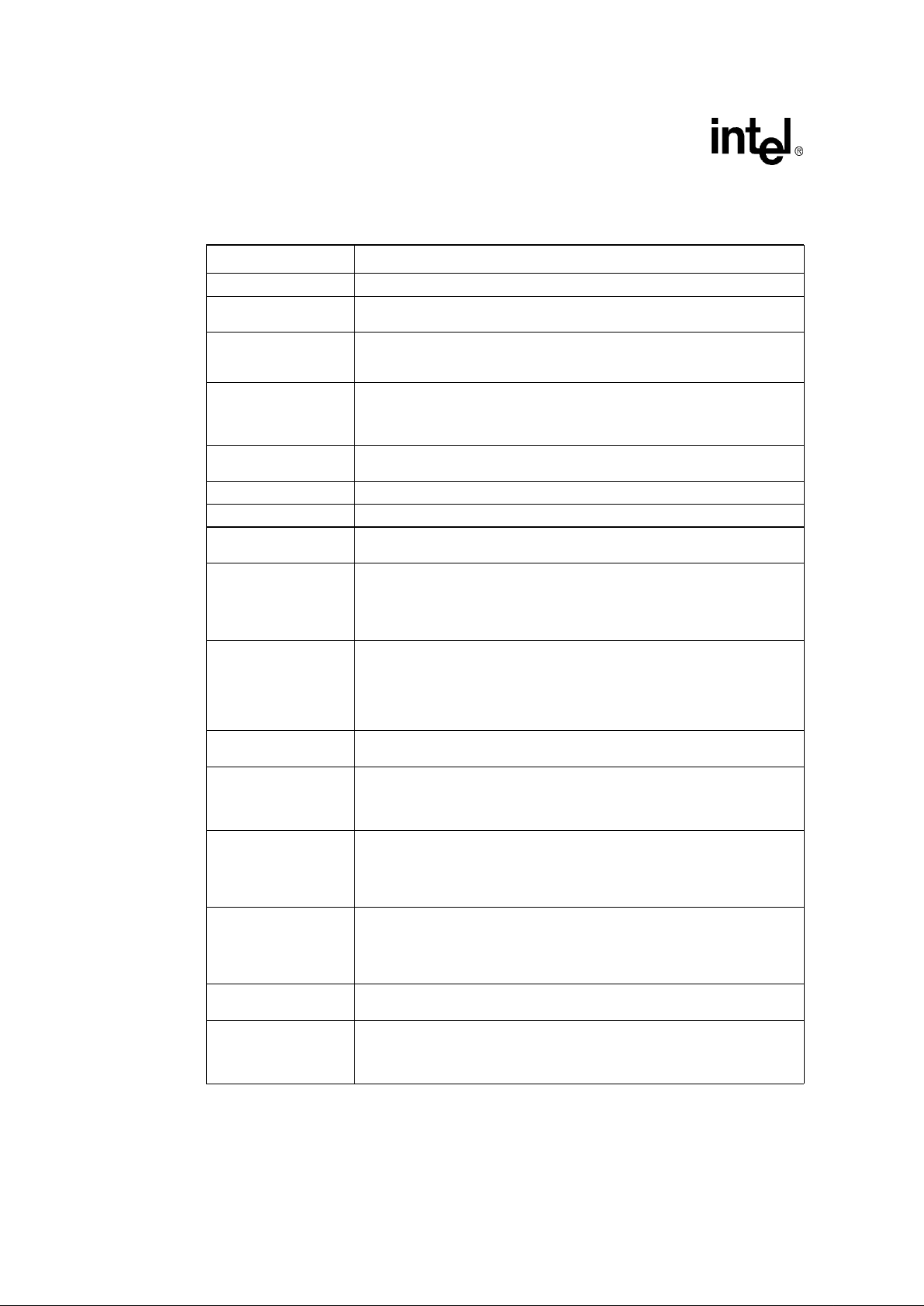

Table 1. 87C196Kx and Jx Features Summary

Device Pins/Package EPROM Reg RAM Code RAM I/O EPA SIO SSIO A/D

87C196KR 68-Pin PLCC 16 K 512 256 56 10 Y Y 8

87C196JV 52-Pin PLCC 48 K 1.5 K 512 41 6 Y Y 6

87C196JT 52-Pin PLCC 32 K 1.0K 512 41 6 Y Y 6

87C196JR 52-Pin PLCC 16 K 512 256 41 6 Y Y 6

87C196CA 68-Pin PLCC 32 K 1.0 K 256 38 6 Y Y 6

Automotive —

87C196KR, JV, JT, JR, CA Microcontrollers

Datasheet 7

• Total Ut ilization of ALL Available Pi ns (I/O Mu x’d with Control)

• Two 16-Bit Timers with Prescale, Cascading and Quadrature Counting Capabilities

• Up to 12 Externally Triggered Interrupts

2.3 New Instructions

2.3.1 XCH/XCHB

Exchange the contents of two locations, either Word or Byte is supported.

2.3.2 BMOVi

Interruptable Block Move Instruction, allows the user to be interrupted during long executing

Block Moves.

2.3.3 TIJMP

Table Indirect JUMP. This instruction incorporates a way to do complex CASE level branches

through one instruction. An example of such code savings: several interrupt sources and only one

interrupt ve ct or. The TIJMP instruction wil l s ort thr ough the s our ces and branch to the appr opr iate

sub-code level in one instruction. This instruction was added especially for the EPA structure, but

has other code saving advantages.

2.3.4 EPTS/DPTS

Enable and Disable PTS Interrupts (Works like EI and DI).

2.4 SFR Operation

An additional 2 56 bytes of SFR r egi st er s wer e adde d t o t he 8XC196Kx, Jx, and CA devi ces. These

locations were a dded to support the wide rang e of on-chip peripherals t hat t hese devices have. This

memory space (1F00–1FFFH) has the ability to be addressed as direct 8-bit addresses through the

“windowing” technique. Any 32-, 64- or 128-byte section can be relocated in the upper 32, 64 or

128 bytes of the internal register RAM (080–FFH) address space. The CA contains an additional

256 bytes of SFR registers for CAN functions located in memory space IE00-1EFFh.

87C196KR, JV, JT, JR, CA Microcontrollers

— Automotive

8 Datasheet

Figure 1. Block Diagram

Figure 2. 8XC196Kx, Jx, and CA Family Nomenclature

A4643-01

Clock Generator

PORT0

EPA0 - 9

ACH0 - 7

PORT1

T2CLK

T2DIR

T1CLK

T1DIR

PORT2

PORT3

PORT4

PORT5

SC0

SC1

SD0

SD1

TXD

RXD

PORT6

I/O Ports

Timer 1 & 2

Register

RAM

A/D Converter

(10-Bit)

[8 Channels]

Peripheral

Transaction

Server (PTS)

Power

and

GND

ALU

XTAL2

Control Signals

ADDR/

Data Bus

XTAL1

16

Code

RAM

On-chip

EPROM

(optional)

Event Processor

Array (EPA)

Programmable

Interrupt

Controller

Serial I/O

(UART & SSIO)

V

CC

V

SS

V

SS

V

SS

V

REF

ANGND

16

Memory

Controller with

Prefetch Queue

A4644-02

AN87C RK196

0 = ROMless

3 = Masked ROM

7 = EPROM, OTP, QROM

Product Designation: KR, JV, JT, JR, CA

Frequency Designation (no mark = 16 MHz)

Product Family

CHMOS Technology

Program Memory Options:

N = PLCC (plastic leaded chip carrier)

Package Type Options:

A = -40

˚

C to +125˚C

ambient with

Intel Standard Burn-in

Temperature and Burn-in Options:

Automotive —

87C196KR, JV, JT, JR, CA Microcontrollers

Datasheet 9

3.0 Packaging Information

Figure 3. 87C196KR 68-Pin PLCC Package Diagram

A4645-02

P6.2 / T1CLK

P6.1 / EPA9

P6.0 / EPA8

P1.0 / EPA0 / T2CLK

P1.1 / EPA1

P1.2 / EPA2 / T2DIR

P1.3 / EPA3

P1.4 / EPA4

P1.5 / EPA5

P1.6 / EPA6

P1.7 / EPA7

V

REF

ANGND

P0.7 / ACH7

P0.6 / ACH6

P0.5 / ACH5

P0.4 / ACH4

WR# / WRL# / P5.2

BHE# / WRH# / P5.5

RD# / P5.3

VPPVSSALE / ADV# / P5.0

INST / P5.1

READY / P5.6

P5.4 / SLPINT

VSSXTAL1

XTAL2

P6.7 / SD1

P6.6 / SC1

P6.5 / SD0

P6.4 / SC0

P6.3 / T1DIR

BUSWIDTH / P5.7

AD15 / P4.7

AD14 / P4.6

AD13 / P4.5

AD12 / P4.4

AD11 / P4.3

AD10 / P4.2

AD9 / P4.1

AD8 / P4.0

AD7 / P3.7

AD6 / P3.6

AD5 / P3.5

AD4 / P3.4

AD3 / P3.3

AD2 / P3.2

AD1 / P3.1

AD0 / P3.0

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

87C196KR

68-Pin

PLCC

View of component as

mounted on PC board

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

RESET#

NMI

EA#

V

SS

V

CC

P2.0 /

TXD

P2.1 / RXD

P2.2 / EXTINT

P2.3 / BREQ#

P2.4 / INTOUT#

P2.5 / HLD#

P2.6 / HLDA#

P2.7 / CLKOUT

P0.0 / ACH0

P0.1 / ACH1

P0.2 / ACH2

P0.3 / ACH3

2728293031323334353637383940414243

987654321

68676665646362

61

87C196KR, JV, JT, JR, CA Microcontrollers

— Automotive

10 Datasheet

Figure 4. 87C196JV, JT, JR 52-Pin PLCC Package Diagram

A4646-02

P6.1 / EPA9

P6.0 / EPA8

P1.0 / EPA0

P1.1 / EPA1

P1.2 / EPA2

P1.3 / EPA3

V

REF

ANGND

P0.7 / ACH7

P0.6 / ACH6

P0.5 / ACH5

P0.4 / ACH4

P0.3 / ACH3

AD15 / P4.7

WR# / WRL# / P5.2

RD# / P5.3

VPPVSSALE / ADV# / P5.0

VSSXTAL1

XTAL2

P6.7 / SD1

P6.6 / SC1

P6.5 / SD0

P6.4 / SC0

AD14 / P4.6

AD13 / P4.5

AD12 / P4.4

AD11 / P4.3

AD10 / P4.2

AD9 / P4.1

AD8 / P4.0

AD7 / P3.7

AD6 / P3.6

AD5 / P3.5

AD4 / P3.4

AD3 / P3.3

AD2 / P3.2

46

45

44

43

42

41

40

39

38

37

36

35

34

87C196JV

87C196JT

87C196JR

52-Pin

PLCC

View of component as

mounted on PC board

8

9

10

11

12

13

14

15

16

17

18

19

20

AD1 / P3.1

AD0 / P3.0

RESET#

EA#

V

SS

V

CC

P2.0 /

TXD

P2.1 / RXD

P2.2 / EXTINT

P2.4

P2.6

P2.7 / CLKOUT

P0.2 / ACH2

21222324252627282930313233

7654321

5251504948

47

Automotive —

87C196KR, JV, JT, JR, CA Microcontrollers

Datasheet 11

Figure 5. 87C196CA 68-Pin PLCC Package Diagram

A4676-01

NC

NC

V

CC

EPA9 / P6.1

EPA8 / P6.0

EPA0 / P1.0 / T2CLK

EPA1 / P1.1

EPA2 / P1.2 / T2DIR

EPA3 / P1.3

NC

V

REF

ANGND

ACH7 / P0.7

ACH6 / P0.6

ACH5 / P0.5

ACH4 / P0.4

NC

WR# / P5.2

WRH# / P5.5

RD# / P5.3

VPPVSSALE / P5.0

READY / P5.6

P5.4

V

SS1

XTAL1

XTAL2

RXCAN

TXCAN

SD1 / P6.7

SC1 / P6.6

SD0 / P6.5

SC0 / P6.4

NC

AD15 / P4.7

AD14 / P4.6

AD13 / P4.5

AD12 / P4.4

AD11 / P4.3

AD10 / P4.2

AD9 / P4.1

AD8 / P4.0

AD7 / P3.7

AD6 / P3.6

AD5 / P3.5

AD4 / P3.4

AD3 / P3.3

AD2 / P3.2

NC

NC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

87C196CA

68 – ld PLCC

View of component as

mounted on PC board

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

P3.1 / AD1

P3.0 / AD0

RESET#

NMI

EA#

V

SS1

V

CC

V

SS

TXD / P2.0

RXD / P2.1

EXTINT / P2.2

P2.4

P2.6

CLKOUT / P2.7

ACH2 / P0.2

ACH3 / P0.3

NC

2728293031323334353637383940414243

987654321

68676665646362

61

87C196KR, JV, JT, JR, CA Microcontrollers

— Automotive

12 Datasheet

Table 2. Pin Descriptions (Sheet 1 of 2)

Symbol Name and Function

V

CC

Main supply voltage (+5 V).

V

SS

Digital circuit ground (0 V). There are three VSS pins, all of which MUST be

connected to a single ground plane.

V

REF

Reference for t he A/D converter (+5 V). V

REF

is also the sup ply voltage to the

analog portion of the A/D convert er and the logic used to read Port 0. Must be

connected for A/D and Port 0 to funct ion.

V

PP

Programming vol tage for the EPROM p arts . It sho uld be +12 .5V for programmin g.

It is also the timing pin for the return f r om powerdown circuit. Con nect this pi n w ith

a 1 µF capa cito r t o V

SS

and a 1 MΩ resistor to VCC. If thi s fu ncti o n is not used , VPP

may be tied to V

CC

.

ANGND

Reference gr ound for the A/D converter. Must be held at nominally the same

potential as V

SS

.

XTAL1 Input of the oscillator inverter and the internal clock generator.

XTAL2 Output of the oscillator inverter.

P2.7/CLK OUT

Output of the in te rna l cl ock gene rat or. The f re que ncy i s ½ the os cil lator f req uen cy.

It has a 50% duty cycle. Also LSIO pin when not used as CLKOUT.

RESET#

Reset input to the chip. In put low for at least 16 state times will rese t the chip. The

subsequent low to high transition res ynchronizes CLKOUT and commence s a 10state time sequence in which the PSW is cleared, bytes are read from 2018H and

201AH loading t he CCBs , and a jump t o lo cati on 20 80H i s ex ecu ted. In put hi gh fo r

normal operation. RESET# has an internal pullup.

P5.7/BUSWIDTH

Input for bus width selection. If CCR bit 1 is a one and CCR1 bit 2 is a one, this pin

dynamically controls the Bus width of the bus cycle in progress. If BUSWIDTH is

low, an 8-bit cycle occurs. If BUSWIDTH is high, a 16-bit cycle occurs. If CCR bit 1

is “0” and CCR1 bit 2 is “1”, all b us cycles are 8-b it; if CCR bit 1 is “1 ” and CCR1 bit

2 is “0”, all bus cycles are 16-bit. CCR bit 1 =”0'' and CCR1 bit 2 = “0” is illega l.

Also an LSIO pi n when not used as BUSWIDTH.

NMI

A positive tra nsition causes a non-maskable interrupt vector through memory

location 20 3EH .

P5.1/INST

Output high duri ng an external memory read indicates t he read is an instruc tion

fetch. INST is valid throughout the bus cycle. INST is active only during external

memory fetches. During internal [EP]ROM fetches INST is held low. Also LSIO

when not INST .

EA#

Input for memory select (External Access). EA# equal to a high causes memory

accesses wit hi n the [EP]ROM address space to be directed to on-chip EPROM/

ROM. EA# equal to a l ow caus es acc ess es to these locat ions to be dir ec ted to off chip memo r y . EA # = +1 2. 5 V causes execution to be g i n i n th e Pr o grammin g

Mode. EA# latched at reset.

P5.0/ALE/ADV#

Address Latch Enable or Address Valid output , as selected by CCR. Both pin

options provide a latch to demul tiplex the address from the address/data bus .

When the pin is ADV#, it goes inactive (high) at the end of the bus cycl e. ADV#

can be used as a chip select for external memory. ALE /ADV# is active only during

external memory accesses. Also LSIO when not used as ALE .

P5.3/RD#

Read signal output to extern al memory. RD# is ac tive only during external memory

reads. LSIO when not used as RD#.

P5.2/WR#/WRL#

Write and Write Low output to external memory, as selected by the CCR, WR# will

go low for every external write, while WRL# will go low only for external writes

where an even byte is being written. WR#/WRL# i s active during external memory

writes. Also an LSIO pin when not used as WR#/WRL#.

Loading...

Loading...