A28F400BX-T/B

4-MBIT (256K x16, 512K x8) BOOT BLOCK FLASH

MEMORY FAMILY

Automotive

Y

x8/x16 Input/Output Architecture

Ð A28F400BX-T, A28F400BX-B

Ð For High Performance and High

Integration 16-bit and 32-bit CPUs

Y

Optimized High Density Blocked

Architecture

Ð One 16 KB Protected Boot Block

Ð Two 8 KB Parameter Blocks

Ð One 96 KB Main Block

Ð Three 128 KB Main Blocks

Ð Top or Bottom Boot Locations

Y

Extended Cycling Capability

Ð 1,000 Block Erase Cycles

Y

Automated Word/Byte Write and Block

Erase

Ð Command User Interface

Ð Status Register

Ð Erase Suspend Capability

Y

SRAM-Compatible Write Interface

Y

Automatic Power Savings Feature

Ð 1 mA Typical I

Active Current in

CC

Static Operation

Y

Very High-Performance Read

Ð 90 ns Maximum Access Time

Ð 45 ns Maximum Output Enable Time

Y

Low Power Consumption

Ð 25 mA Typical Active Read Current

Y

Deep Power-Down/Reset Input

Ð Acts as Reset for Boot Operations

Y

Automotive Temperature Operation

b

Ð

40§Ctoa125§C

Y

Write Protection for Boot Block

Y

Hardware Data Protection Feature

Ð Erase/Write Lockout During Power

Transitions

Y

Industry Standard Surface Mount

Packaging

Ð JEDEC ROM Compatible

44-Lead PSOP

Y

12V Word/Byte Write and Block Erase

e

ÐV

Y

ETOXTMIII Flash Technology

12Vg5% Standard

PP

Ð 5V Read

*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or

copyright, for sale and use of Intel products except as provided in Intel’s Terms and Conditions of Sale for such products. Intel retains the right to make

changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

November 1995COPYRIGHT©INTEL CORPORATION, 1995 Order Number: 290501-003

A28F400BX-T/B

Intel’s 4-Mbit Flash Memory Family is an extension of the Boot Block Architecture which includes blockselective erasure, automated write and erase operations and standard microprocessor interface. The 4-Mbit

Flash Memory Family enhances the Boot Block Architecture by adding more density and blocks, x8/x16 input/

output control, very high speed, low power, an industry standard ROM compatible pinout and surface mount

packaging. The 4-Mbit flash family is an easy upgrade from Intel’s 2-Mbit Boot Block Flash Memory Family.

The Intel A28F400BX-T/B are 16-bit wide flash memory offerings optimized to meet the rigorous environmental requirements of Automotive Applications. These high density flash memories provide user selectable bus

operation for either 8-bit or 16-bit applications. The A28F400BX-T and A28F400BX-B are 4,194,304-bit nonvolatile memories organized as either 524,288 bytes or 262,144 words of information. They are offered in 44Lead plastic SOP packages. The x8/x16 pinout conforms to the industry standard ROM/EPROM pinout. Read

and Write characteristics are guaranteed over the ambient temperature range of

These devices use an integrated Command User Interface (CUI) and Write State Machine (WSM) for simplified

word/byte write and block erasure. The A28F400BX-T provide block locations compatible with Intel’s

MCS-186 family, 80286, i386

TM

, i486TM, i860TMand 80960CA microprocessors. The A28F400BX-B provides

compatibility with Intel’s 80960KX and 80960SX families as well as other embedded microprocessors.

The boot block includes a data protection feature to protect the boot code in critical applications. With a

maximum access time of 90 ns, these 4-Mbit flash devices are very high performance memories which

interface at zero-wait-state to a wide range of microprocessors and microcontrollers.

Manufactured on Intel’s 0.8 micron ETOX

TM

III process, the 4-Mbit flash memory family provides world class

quality, reliability and cost-effectiveness at the 4-Mbit density level.

b

40§Ctoa125§C.

2

A28F400BX-T/B

1.0 PRODUCT FAMILY OVERVIEW

Throughout this datasheet the A28F400BX refers to

both the A28F400BX-T and A28F400BX-B devices.

Section 1 provides an overview of the 4-Mbit flash

memory family including applications, pinouts and

pin descriptions. Section 2 describes in detail the

specific memory organization for the A28F400BX.

Section 3 provides a description of the family’s principles of operations. Finally the family’s operating

specifications are described.

1.1 Main Features

The A28F400BX boot block flash memory family is a

very high performance 4-Mbit (4,194,304 bit) memory family organized as either 256-KWords (262,144

words) of 16 bits each or 512-Kbytes (524,288

bytes) of 8 bits each.

Seven Separately Erasable Blocks including a

Hardware-Lockable boot block (16,384 Bytes),

Two parameter blocks (8,192 Bytes each) and

Four main blocks (1 block of 98,304 Bytes and 3

blocks of 131,072 Bytes) are included on the 4-Mbit

family. An erase operation erases one of the main

blocks in typically 3 seconds and the boot or parameter blocks in typically 1.5 seconds independent of

the remaining blocks. Each block can be independently erased and programmed 1,000 times.

The Boot Block is located at either the top

(A28F400BX-T) or the bottom (A28F400BX-B) of the

address map in order to accommodate different microprocessor protocols for boot code location. The

hardware lockable boot block provides the most

secure code storage. The boot block is intended to

store the kernel code required for booting-up a system. When the RP

the boot block is unlocked and program and erase

operations can be performed. When the RP

at or below 6.5V the boot block is locked and program and erase operations to the boot block are

ignored.

The A28F400BX products are available in the ROM/

EPROM compatible pinout and housed in the

44-Lead PSOP (Plastic Small Outline) package as

shown in Figure 3.

The Command User Interface (CUI) serves as the

interface between the microprocessor or microcontroller and the internal operation of the A28F400BX

flash memory.

Program and Erase Automation allows program

and erase operations to be executed using a twowrite command sequence to the CUI. The internal

Write State Machine (WSM) automatically executes

Ý

pin is between 11.4V and 12.6V

Ý

pin is

the algorithms and timings necessary for program

and erase operations, including verifications, thereby unburdening the microprocessor or microcontroller. Writing of memory data is performed in word or

byte increments typically within 9 ms which is a

100% improvement over previous flash memory

products.

The Status Register (SR) indicates the status of the

WSM and whether the WSM successfully completed

the desired program or erase operation.

Maximum Access Time of 90 ns (TACC) is achieved

over the automotive temperature range, 10% V

supply range (4.5V to 5.5V) and 100 pF output load.

maximum Program current is 40 mA for x16

I

PP

operation and 30 mA for x8 operation. I

current is 30 mA maximum. V

gramming voltage is 11.4V to 12.6V (V

g

5%) under all operating conditions. Typical

Active Current of 25 mA is achieved.

I

CC

erase and pro-

PP

PP

PP

Erase

e

CC

12V

The 4-Mbit boot block flash memory family is also

designed with an Automatic Power Savings (APS)

feature to minimize system battery current drain and

allows for very low power designs. Once the device

is accessed to read array data, APS mode will immediately put the memory in static mode of operation

where I

next read is initiated.

When the CE

BYTE

Standby mode is enabled where I

80 mA.

active current is typically 1 mA until the

CC

Ý

Ý

and RPÝpins are at VCCand the

pin is at either VCCor GND the CMOS

is typically

CC

A Deep Power-Down Mode is enabled when the

Ý

RP

pin is at ground minimizing power consumption

and providing write protection during power-up conditions. I

is 50 mA typical. An initial maximum access time or

Reset Time of 300 ns is required from RP

current during deep power-down mode

CC

Ý

switching until outputs are valid. Equivalently, the device

has a maximum wake-up time of 210 ns until writes

to the Command User Interface are recognized.

When RP

Ý

is at ground the WSM is reset, the

Status Register is cleared and the entire device is

protected from being written to. This feature prevents data corruption and protects the code stored

in the device during system reset. The system Reset

Ý

pin can be tied to RP

to reset the memory to normal read mode upon activation of the Reset pin.

With on-chip program/erase automation in the

4-Mbit family and the RP

Ý

functionality for data protection, when the CPU is reset and even if a program

or erase command is issued, the device will not recognize any operation until RP

Ý

returns to its normal

state.

3

A28F400BX-T/B

For the A28F400BX, Byte-wide or Word-wide Input/Output Control is possible by controlling the

Ý

BYTE

the device is in the byte-wide mode (x8) and data is

read and written through DQ[0:7]. During the bytewide mode, DQ[8:14]are tri-stated and DQ15/A-1

becomes the lowest order address pin. When the

BYTE

word-wide mode (x16) and data is read and written

through DQ[0:15].

pin. When the BYTEÝpin is at a logic low

Ý

pin is at a logic high the device is in the

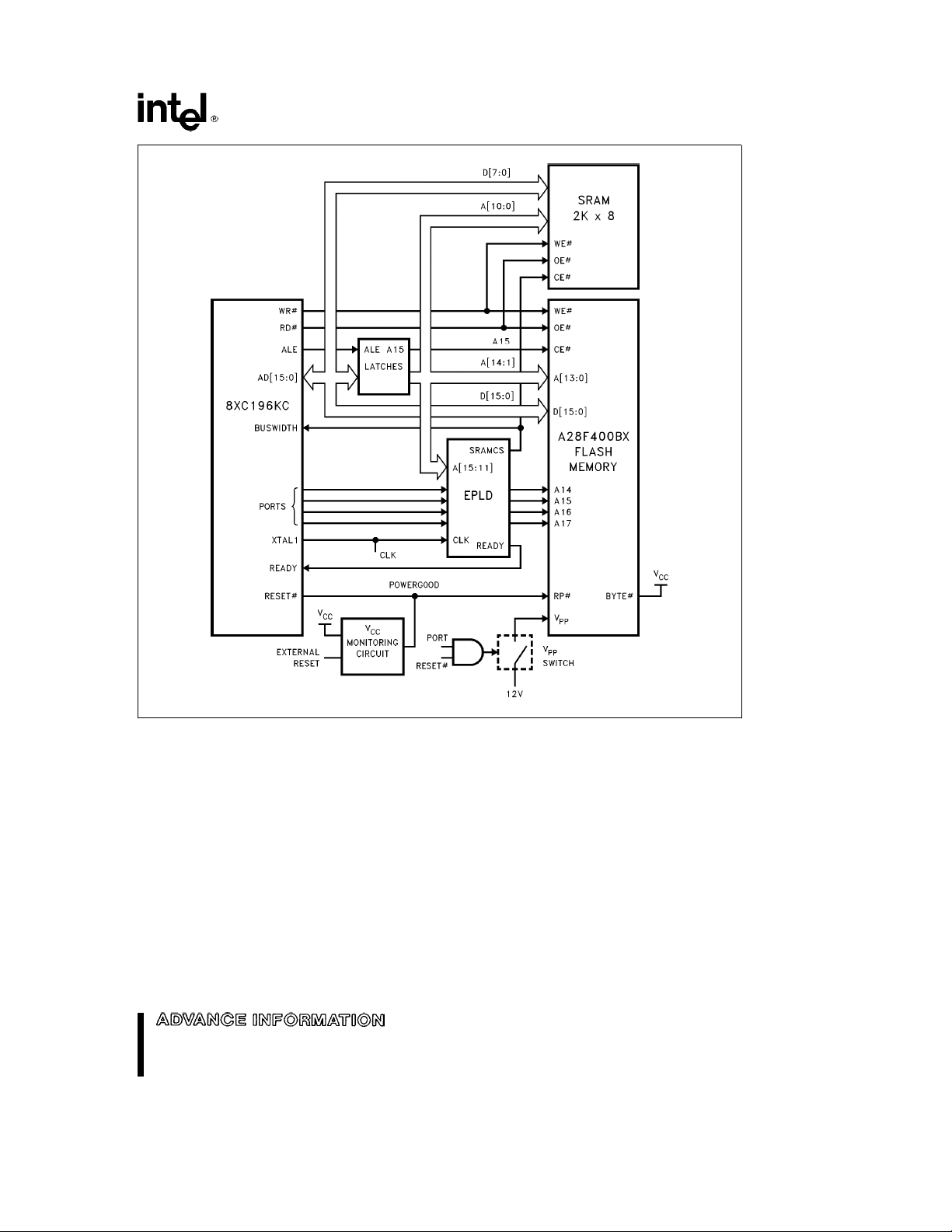

1.2 Applications

The 4-Mbit boot block flash memory family combines high density, high performance, cost-effective

flash memories with blocking and hardware protec-

tion capabilities. Its flexibility and versatility will reduce costs throughout the product life cycle. Flash

memory is ideal for Just-In-Time production flow, reducing system inventory and costs, and eliminating

component handling during the production phase.

During the product life cycle, when code updates or

feature enhancements become necessary, flash

memory will reduce the update costs by allowing either a user-performed code change via floppy disk

or a remote code change via a serial link. The 4-Mbit

boot block flash memory family provides full function, blocked flash memories suitable for a wide

range of automotive applications.

4

A28F400BX-T/B

Figure 1. A28F400BX Interface to 8XC196KC

290501– 1

5

A28F400BX-T/B

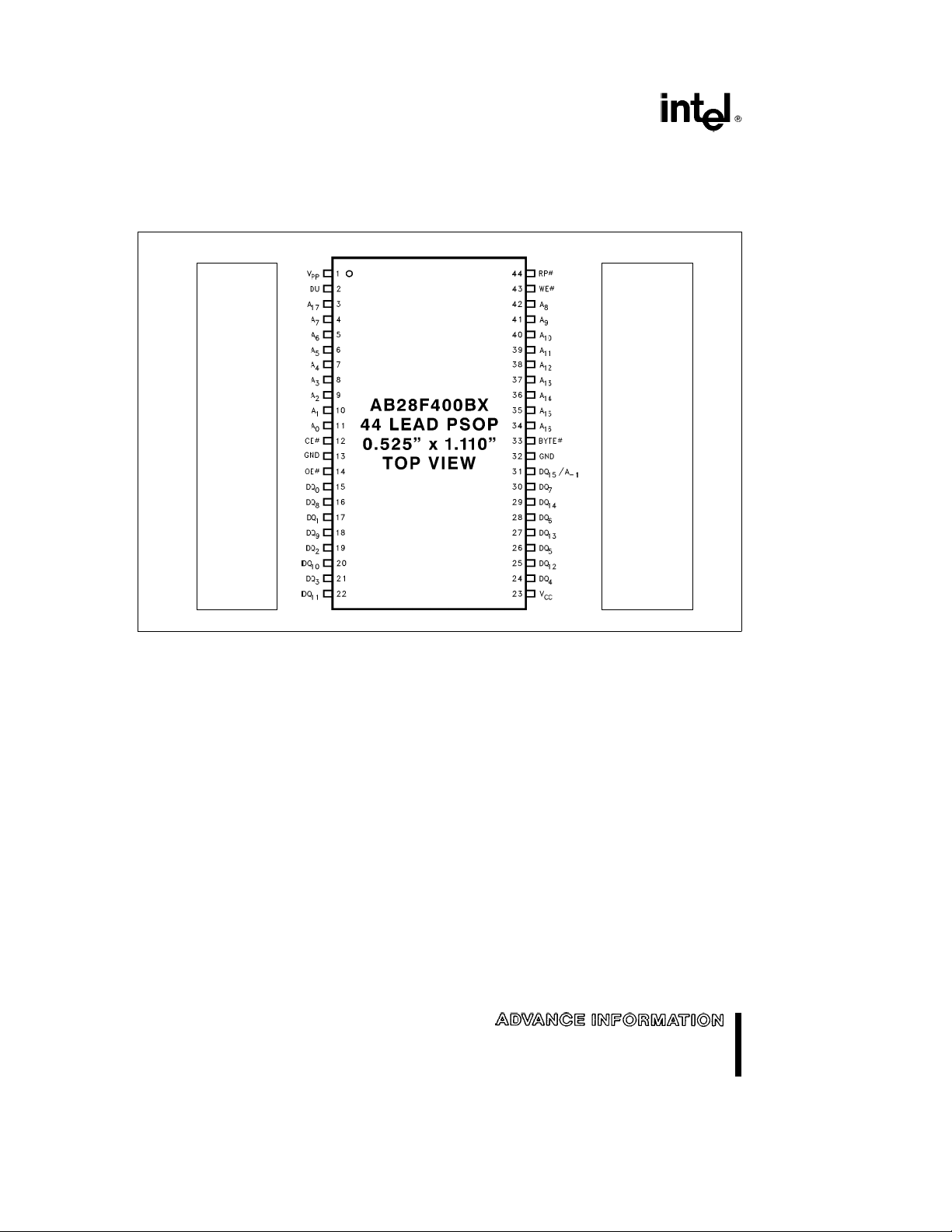

1.3 Pinouts

The A28F400BX 44-Lead PSOP pinout follows the

industry standard ROM/EPROM pinout as shown in

Figure 2.

27C400

NC

NC

A

17

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

Ý

CE

GND

Ý

OE

DQ

0

DQ

8

DQ

1

DQ

9

DQ

2

DQ

10

DQ

3

DQ

11

290501– 3

Figure 2. PSOP Lead Configuration

27C400

NC

NC

A

8

A

9

A

10

A

11

A

12

A

13

A

14

A

15

A

16

BYTEÝ/V

GND

DQ

/A

15

DQ

7

DQ

14

DQ

6

DQ

13

DQ

5

DQ

12

DQ

4

V

CC

PP

b

1

6

A28F400BX-T/B

1.4 A28F400BX Pin Descriptions

Symbol Type Name and Function

A0–A

17

A

9

DQ0–DQ7I/O DATA INPUTS/OUTPUTS: Inputs array data on the second CEÝand WEÝcycle during a

DQ8–DQ15I/O DATA INPUTS/OUTPUTS: Inputs array data on the second CEÝand WEÝcycle during a

Ý

CE

Ý

RP

Ý

OE

Ý

WE

Ý

BYTE

V

PP

V

CC

GND GROUND: For all internal circuitry.

NC NO CONNECT: Pin may be driven or left floating.

DU DON’T USE PIN: Pin should not be connected to anything.

I ADDRESS INPUTS for memory addresses. Addresses are internally latched during a write

cycle.

I ADDRESS INPUT: When A9is at 12V the signature mode is accessed. During this mode A

decodes between the manufacturer and device ID’s. When BYTEÝis at a logic low only the

lower byte of the signatures are read. DQ

Ý

is low.

BYTE

program command. Inputs commands to the command user interface when CE

/A

is a don’t care in the signature mode when

b

15

1

Ý

and WE

are active. Data is internally latched during the write and program cycles. Outputs array,

intelligent identifier and Status Register data. The data pins float to tri-state when the chip is

deselected or the outputs are disabled.

program command. Data is internally latched during the write and program cycles. Outputs

array data. The data pins float to tri-state when the chip is deselected or the outputs are

disabled as in the byte-wide mode (BYTE

becomes the lowest order address for data output on DQ0-DQ7.

e

Ý

‘‘0’’). In the byte-wide mode DQ15/A

b

1

I CHIP ENABLE: Activates the device’s control logic, input buffers, decoders and sense

amplifiers. CE

consumption to standby levels. If CE

standby current will increase due to current flow through the CE

Ý

is active low; CEÝhigh deselects the memory device and reduces power

Ý

and RPÝare high, but not at a CMOS high level, the

Ý

and RPÝinput stages.

I RESET/POWER-DOWN: Provides three-state control. Puts the device in deep power-down

mode. Locks the boot block from program/erase.

Ý

When RP

is at logic high level and equals 6.5V maximum the boot block is locked and

cannot be programmed or erased.

e

Ý

When RP

11.4V minimum the boot block is unlocked and can be programmed or

erased.

Ý

When RP

is at a logic low level the boot block is locked, the deep power-down mode is

enabled and the WSM is reset preventing any blocks from being programmed or erased,

Ý

therefore providing data protection during power transitions. When RP

transitions from

logic low to logic high the flash memory enters the read array mode.

I OUTPUT ENABLE: Gates the device’s outputs through the data buffers during a read cycle.

Ý

OE

is active low.

I WRITE ENABLE: Controls writes to the Command Register and array blocks. WEÝis active

Ý

low. Addresses and data are latched on the rising edge of the WE

pulse.

I BYTEÝENABLE: Controls whether the device operates in the byte-wide mode (x8) or the

Ý

word-wide mode (x16). BYTE

CMOS current in the standby mode. BYTE

is read and programmed on DQ

that decodes between the upper and lower byte. DQ

wide mode. BYTE

programmed on DQ

Ý

0

e

–DQ15.

pin must be controlled at CMOS levels to meet 130 mA

–DQ7and DQ15/A

0

‘‘1’’ enables the word-wide mode where data is read and

e

Ý

‘‘0’’ enables the byte-wide mode, where data

becomes the lowest order address

b

1

–DQ14are tri-stated during the byte-

8

PROGRAM/ERASE POWER SUPPLY: For erasing memory array blocks or programming

data in each block.

Note: V

k

V

PP

memory contents cannot be altered.

PPLMAX

DEVICE POWER SUPPLY (5Vg10%)

0

Ý

7

A28F400BX-T/B

2.0 A28F400BX WORD/BYTE-WIDE PRODUCTS DESCRIPTION

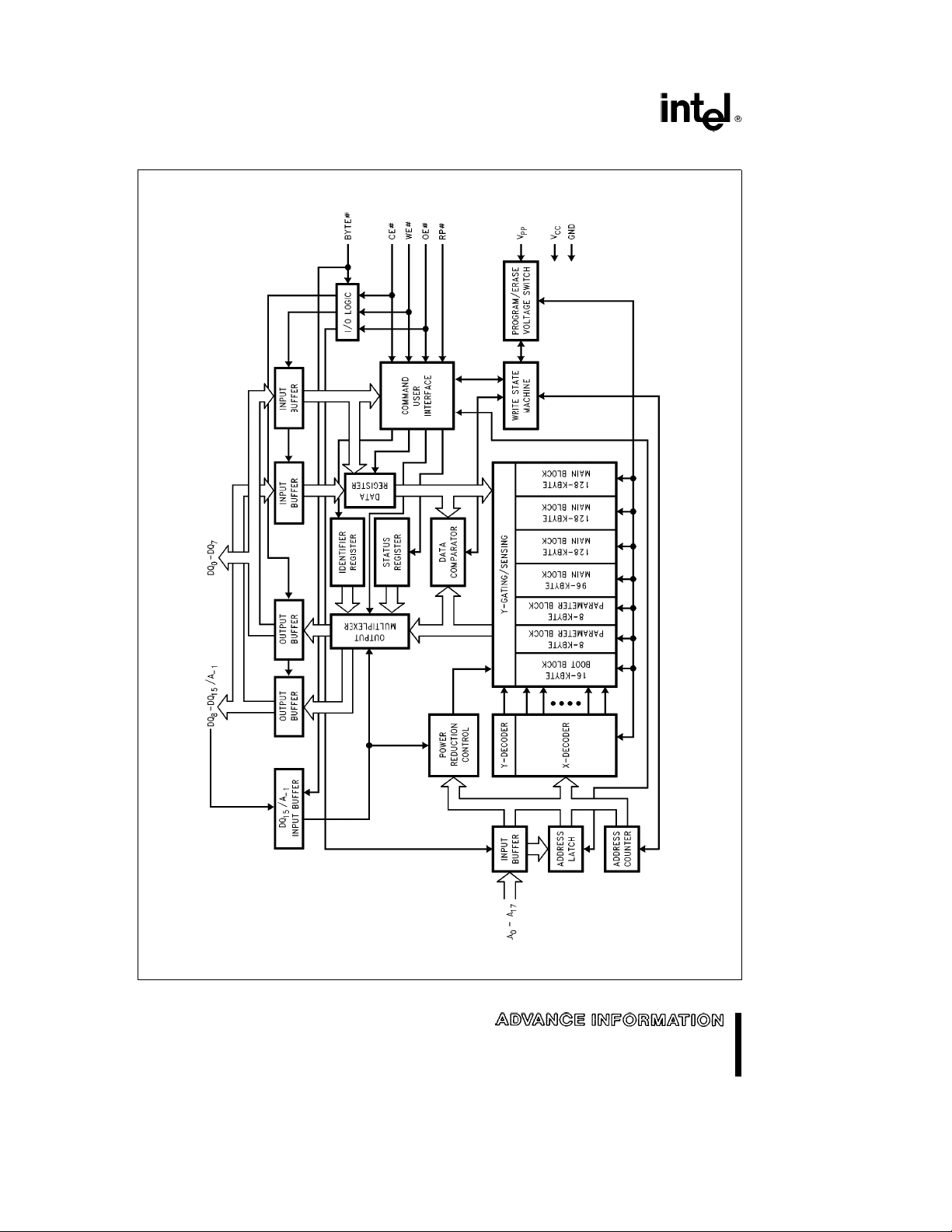

290501– 4

Figure 3. A28F400BX Word/Byte Block Diagram

8

A28F400BX-T/B

2.1 A28F400BX Memory Organization

2.1.1 BLOCKING

The A28F400BX uses a blocked array architecture

to provide independent erasure of memory blocks. A

block is erased independently of other blocks in the

array when an address is given within the block address range and the Erase Setup and Erase Confirm

commands are written to the CUI. The A28F400BX

is a random read/write memory, only erasure is performed by block.

2.1.1.1 Boot Block Operation and Data

Protection

The 16-Kbyte boot block provides a lock feature for

secure code storage. The intent of the boot block is

to provide a secure storage area for the kernel code

that is required to boot a system in the event of power failure or other disruption during code update.

This lock feature ensures absolute data integrity by

preventing the boot block from being written or

erased when RP

be erased and written when RP

the duration of the erase or program operation. This

allows customers to change the boot code when

necessary while providing security when needed.

See the Block Memory Map section for address locations of the boot block for the A28F400BX-T and

A28F400BX-B.

2.1.1.2 Parameter Block Operation

The A28F400BX has 2 parameter blocks (8 Kbytes

each). The parameter blocks are intended to provide

storage for frequently updated system parameters

and configuration or diagnostic information. The parameter blocks can also be used to store additional

boot or main code. The parameter blocks however,

do not have the hardware write protection feature

that the boot block has. The parameter blocks provide for more efficient memory utilization when dealing with parameter changes versus regularly blocked

devices. See the Block Memory Map section for address locations of the parameter blocks for the

A28F400BX-T and A28F400BX-B.

2.1.1.3 Main Block Operation

Four main blocks of memory exist on the

A28F400BX (3 x 128 Kbyte blocks and 1 x 96-Kbyte

blocks). See the following section on Block Memory

Map for the address location of these blocks for the

A28F400BX-T and A28F400BX-B products.

Ý

is not at 12V. The boot block can

Ý

is held at 12V for

2.1.2 BLOCK MEMORY MAP

Two versions of the A28F400BX product exist to

support two different memory maps of the array

blocks in order to accommodate different microprocessor protocols for boot code location. The

A28F400BX-T memory map is inverted from the

A28F400BX-B memory map.

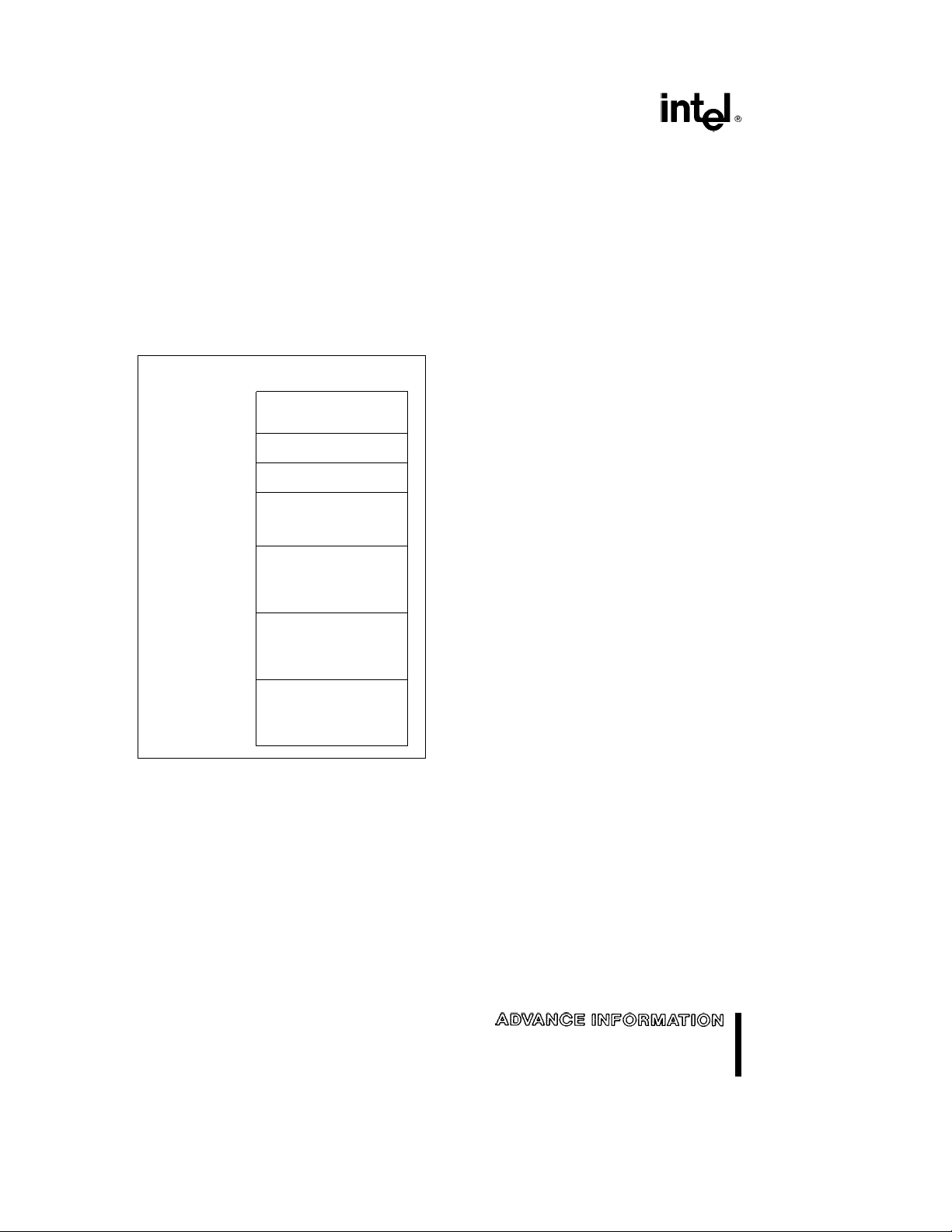

2.1.2.1. A28F400BX-B Memory Map

The A28F400BX-B device has the 16-Kbyte boot

block located from 00000H to 01FFFH to accommodate those microprocessors that boot from the bottom of the address map at 00000H. In the

A28F400BX-B the first 8-Kbyte parameter block resides in memory space from 02000H to 02FFFH.

The second 8-Kbyte parameter block resides in

memory space from 03000H to 03FFFH. The 96Kbyte main block resides in memory space from

04000H to 0FFFFH. The three 128-Kbyte main

block resides in memory space from 10000H to

1FFFFH, 20000H to 2FFFFH and 30000H to

3FFFFH (word locations). See Figure 4.

(Word Addresses)

3FFFFH

128-Kbyte MAIN BLOCK

30000H

2FFFFH

128-Kbyte MAIN BLOCK

20000H

1FFFFH

128-Kbyte MAIN BLOCK

10000H

0FFFFH

96-Kbyte MAIN BLOCK

04000H

03FFFH

03000H

02FFFH

02000H

01FFFH

00000H

8-Kbyte PARAMETER BLOCK

8-Kbyte PARAMETER BLOCK

16-Kbyte BOOT BLOCK

Figure 4. A28F400BX-B Memory Map

9

A28F400BX-T/B

2.1.2.2 A28F400BX-T Memory Map

The A28F400BX-T device has the 16-Kbyte boot

block located from 3E000H to 3FFFFH to accommodate those microprocessors that boot from the top

of the address map. In the A28F400BX-T the first

8-Kbyte parameter block resides in memory space

from 3D000H to 3DFFFH. The second 8-Kbyte parameter block resides in memory space from

3C000H to 3CFFFH. The 96-Kbyte main block resides in memory space from 30000H to 3BFFFH.

The three 128-Kbyte main blocks reside in memory

space from 20000H to 2FFFFH, 10000H to 1FFFFH

and 00000H to 0FFFFH as shown below in Figure 5.

(Word Addresses)

3FFFFH

3E000H

3DFFFH

3D000H

3CFFFH

3C000H

3BFFFH

30000H

2FFFFH

20000H

1FFFFH

10000H

0FFFFH

16-Kbyte BOOT BLOCK

8-Kbyte PARAMETER BLOCK

8-Kbyte PARAMETER BLOCK

96-Kbyte MAIN BLOCK

128-Kbyte MAIN BLOCK

128-Kbyte MAIN BLOCK

128-Kbyte MAIN BLOCK

3.0 PRODUCT FAMILY PRINCIPLES

OF OPERATION

Flash memory augments EPROM functionality with

in-circuit electrical write and erase. The 4-Mbit flash

family utilizes a Command User Interface (CUI) and

internally generated and timed algorithms to simplify

write and erase operations.

The CUI allows for 100% TTL-level control inputs,

fixed power supplies during erasure and programming, and maximum EPROM compatibility.

In the absence of high voltage on the V

4-Mbit boot block flash family will only successfully

execute the following commands: Read Array, Read

Status Register, Clear Status Register and Intelligent Identifier mode. The device provides standard

EPROM read, standby and output disable operations. Manufacturer Identification and Device Identification data can be accessed through the CUI or

through the standard EPROM A

cess (V

) for PROM programming equipment.

ID

high voltage ac-

9

The same EPROM read, standby and output disable

functions are available when high voltage is applied

to the V

lows write and erase of the device. All functions as-

pin. In addition, high voltage on VPPal-

PP

sociated with altering memory contents: write and

erase, Intelligent Identifier read and Read Status are

accessed via the CUI.

The purpose of the Write State Machine (WSM) is to

completely automate the write and erasure of the

device. The WSM will begin operation upon receipt

of a signal from the CUI and will report status back

through a Status Register. The CUI will handle the

Ý

WE

interface to the data and address latches, as

well as system software requests for status while the

WSM is in operation.

PP

pin, the

00000H

Figure 5. A28F400BX-T Memory Map

10

3.1 Bus Operations

Flash memory reads, erases and writes in-system

via the local CPU. All bus cycles to or from the flash

memory conform to standard microprocessor bus

cycles.

A28F400BX-T/B

e

Table 1. Bus Operations for WORD-WIDE Mode (BYTE

Mode Notes RPÝCEÝOEÝWE

Read 1, 2, 3 V

Output Disable V

Standby V

Deep Power-Down 9 V

Intelligent Identifier (Mfr) 4 V

Intelligent Identifier (Device) 4, 5 V

Write 6, 7, 8 V

V

IH

V

IH

V

IH

IL

V

IH

V

IH

V

IH

V

IL

IL

IH

IL

V

IH

X X X X X High Z

X X X X X X High Z

V

IL

IL

IL

IL

V

IL

V

IH

Table 2. Bus Operations for BYTE-WIDE Mode (BYTEeVIL)

Mode Notes RPÝCEÝOEÝWEÝA9A0A

Read 1, 2, 3 V

Output Disable V

Standby V

Deep Power-Down 9 V

Intelligent 4 V

V

V

V

IH

IL

IL

V

IH

IH

IL

IH

V

IL

IH

V

X X X X X X High Z High Z

IH

X X X X X X X High Z High Z

V

V

IL

IL

XX X XD

IH

V

X X X X High Z High Z

IH

V

IHVIDVIL

Identifier (Mfr)

Intelligent 4, 5 V

V

V

IH

IL

IL

V

IHVIDVIH

Identifier (Device) 71H

Write 6, 7, 8 V

NOTES:

1. Refer to DC Characteristics.

2. X can be V

3. See DC Characteristics for V

4. Manufacturer and Device codes may also be accessed via a CUI write sequence. A

5. Device ID

6. Refer to Table 3 for valid D

7. Command writes for Block Erase or Word/Byte Write are only executed when V

8. To write or erase the boot block, hold RP

Ý

must be at GNDg0.2V to meet the 80 mA maximum deep power-down current.

9. RP

for control pins and addresses, V

IL,VIH

e

4470H for A28F400BX-T and 4471H for A28F400BX-B.

PPL,VPPH,VHH,VID

during a write operation.

IN

V

V

V

IH

IL

IH

or V

PPL

PPH

Ý

voltages.

at VHH.

XX X X DINHigh Z

IL

for VPP.

Ý

VIH)

Ý

A9A0V

V

V

V

V

V

XX X D

IH

X X X High Z

IH

VIDV

IH

IH

IL

b

IL

VIDV

IH

XX X D

1VPP

X X 89H High Z

X X 70H High Z

e

X.

V

.

PPH

PP

1–A17

e

DQ

DQ

PP

0–15

OUT

X 0089H

X 4470H

4471H

IN

DQ

0–7

OUT

8–14

High Z

3.2 Read Operations

The 4-Mbit boot block flash family has three user

read modes; Array, Intelligent Identifier, and Status

Register. Status Register read mode will be discussed in detail in the ‘‘Write Operations’’ section.

During power-up conditions (V

takes a maximum of 300 ns from when V

4.5V minimum to valid data on the outputs.

supply ramping), it

CC

CC

is at

3.2.1 READ ARRAY

If the memory is not in the Read Array mode, it is

necessary to write the appropriate read mode command to the CUI. The 4-Mbit boot block flash family

has three control functions, all of which must be logically active, to obtain data at the outputs. Chip-En-

Ý

able CE

Power-Down, RP

put-Enable OE

is the device selection control. Reset/

Ý

is the device power control. Out-

Ý

is the DATA INPUT/OUTPUT

(DQ[0:15]or DQ[0:7]) direction control and when

active is used to drive data from the selected memory on to the I/O bus.

11

Loading...

Loading...