Intel Corporation A83C196EA Datasheet

ADVANCE INFORMATION

COPYRIGHT © INTEL CORPORATION, 1997 March 1997 Order Number: 272788-002

83C196EA

CHMOS 16-BIT MICROCONTROLLER

Automotive

The 83C196EA is the first member of a new family of microcontrollers with features that are useful in

automotiv e applications, such as powertrain control. Tw o Mbytes of linear address space provide more space

for high-level language compilation. A demultiplexed address/data bus and three chip-select signals make it

easier to design low-cost memory solutions. The external bus can dynamically switch between multiplexed

and demult i pl exed operati on.

NOTE

This datas heet con tai ns in fo rmati on on prod uc ts bein g sampl ed o r in t he i nit ial prod ucti on

phase of development. The specifications are subject to change without notice. Verify

with your loc al Intel sales office that you have the la test datashe et before finalizing a

design.

■ 40 MHz operation

■ Opt ional clock doubler

■ 2 Mbytes of linear address space

■ 1 Kbyte of register RAM

■ 3 Kbytes of code RAM

■ 8 Kbytes of ROM

■ Register-to-register architecture

■ Stack overflow/underflow monitor with

user-defined upper and lower stack

pointer boundary limits

■ 2 peripheral interrupt handlers (PIH)

provide direct ha rdware handling of up

to 16 peripheral interrupts

■ Peripheral transaction server (PTS) with

high-speed, microcoded interrupt

service routines

■ Up to 83 I/O port pins

■ 2 full-duplex serial ports with dedicated

baud-rate generators

■ Enhanced synchronous serial unit

■ 8 pulse-width modulator (PWM) outputs

with 8-bit resolution

■ 16-bit watchdog timer

■ Sixteen 10-bit A/D channels with auto-

scan mode and dedicated results

registers

■ Serial debug unit provides read and

write access to code RAM with no CPU

overhead

■ Chip-select unit (CSU)

■ 3 chip-select pins

■ Dynamic demultip lexed /m ult iple xed

address/data bus for each

chip-select

■ Programmable wait states

(0, 1, 2, or 3) for each chip-select

■ Programmable bus width

(8- or 16-bit) for each chip-select

■ Programmable address range for each

chip-select

■ Event processor array (EPA)

■ 4 flexible 16-bit timer/counters

■ 17 high-speed capture/compare

channels

■ 8 output-only channels capture value of

any other timer upon compare, providing

easy conversio n bet ween an gle and t ime

domains

■ Programmable clock output signal

■ 160-pin QFP package

■ Complete system development support

■ High-speed CHMOS technology

Information in this document is provi ded i n connection w ith Intel p r oducts. No license, expres s or implied, by

estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in

Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relati ng to fitness for a partic ular purpose, merchan tability, or infringement of any patent, copy right or

other int elle ctua l pr oper ty r ight . I nt el p rodu cts ar e not int en ded fo r use in medic al , l ife sav ing , or li fe sus ta inin g

applicati ons.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

*Third-party brands and names are the pr operty of their respective owners.

Copies of documents whi ch have an ordering number and are referenced in this doc ument, or other Intel liter-

ature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospec t, IL 60056-7641

or call 1-800-548-4725

ADVANCE INFORMATION iii

CONTENTS

83C196EA

CHMOS 16-bit Microcontroller

1.0 Product Overview................................................................................................................ 1

2.0 Nomenclature Overview...................................................................................................... 2

3.0 Pinout.................................................................................................................................. 3

4.0 Signals ................................................................................................................................ 6

5.0 Address Map..................................................................................................................... 15

6.0 Electrical Characteristics........................ ................................. ......... ........ ......... ........ ........ 17

6.1 DC Characteristics........................................................................................................ 17

6.2 AC Characteristics — Multiplexed Bus Mode............................................................... 19

6.3 AC Characteristics — Demultiplexed Bus Mode.......................................................... 23

6.4 Deferred Bus Timing Mode........................................................................................... 27

6.5 AC Characteristics — Serial Port, Shift Register Mode................................................ 28

6.6 AC Characteristics — Synchronous Serial Port ........................................................... 29

6.7 A/D Sample and Conversion Times ............................................................................. 30

6.7.1 AC Characteristics — A/D Converter, 10-bit Mode ...............................................31

6.7.2 AC Characteristics — A/D Converter, 8-bit Mode .................................................32

6.8 External Clock Drive..................................................................................................... 34

6.9 Test Output Waveforms ............................................................................................... 35

7.0 Thermal Characteristics.................................................................................................... 36

8.0 83C196EA Errata.................. ........ ......... ........ ......... ................................. ......... ........ ........ 36

9.0 DataSheet Revision History.............................................................................................. 36

Figures

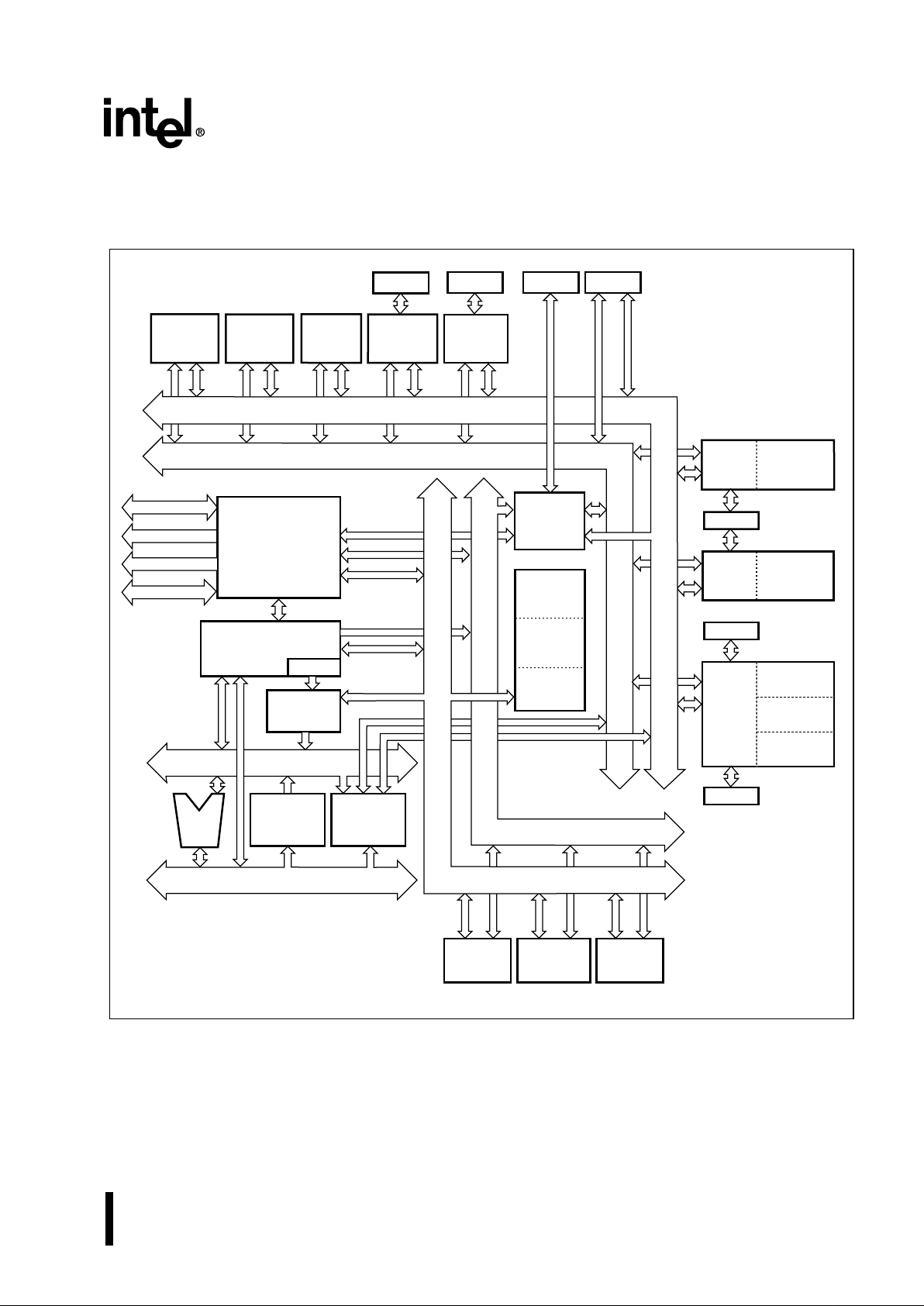

1. 83C196EA Block Diagram............. ......... ........ ......... ........ .................................. ........ ........ ...1

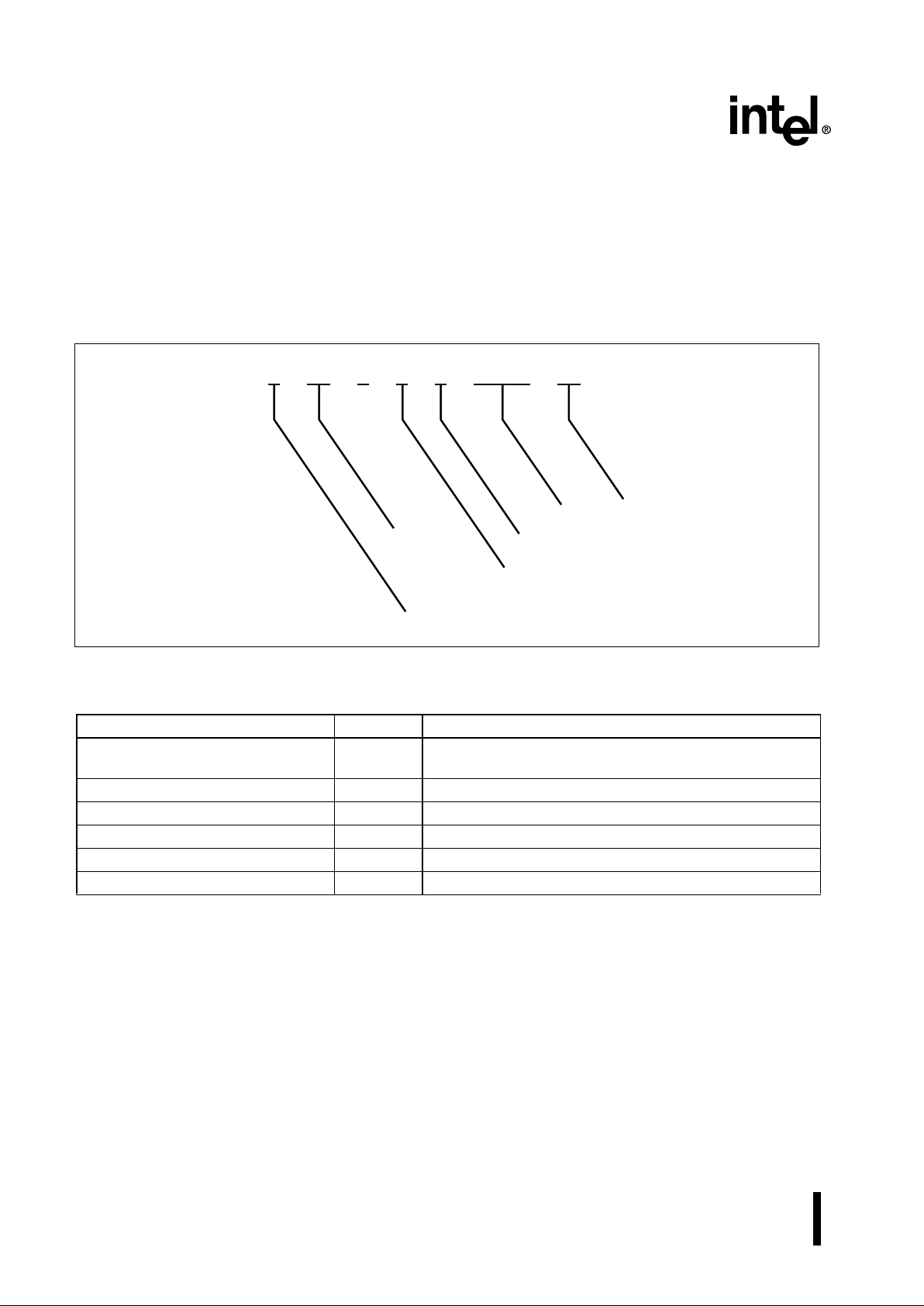

2. Product Nomenclature .........................................................................................................2

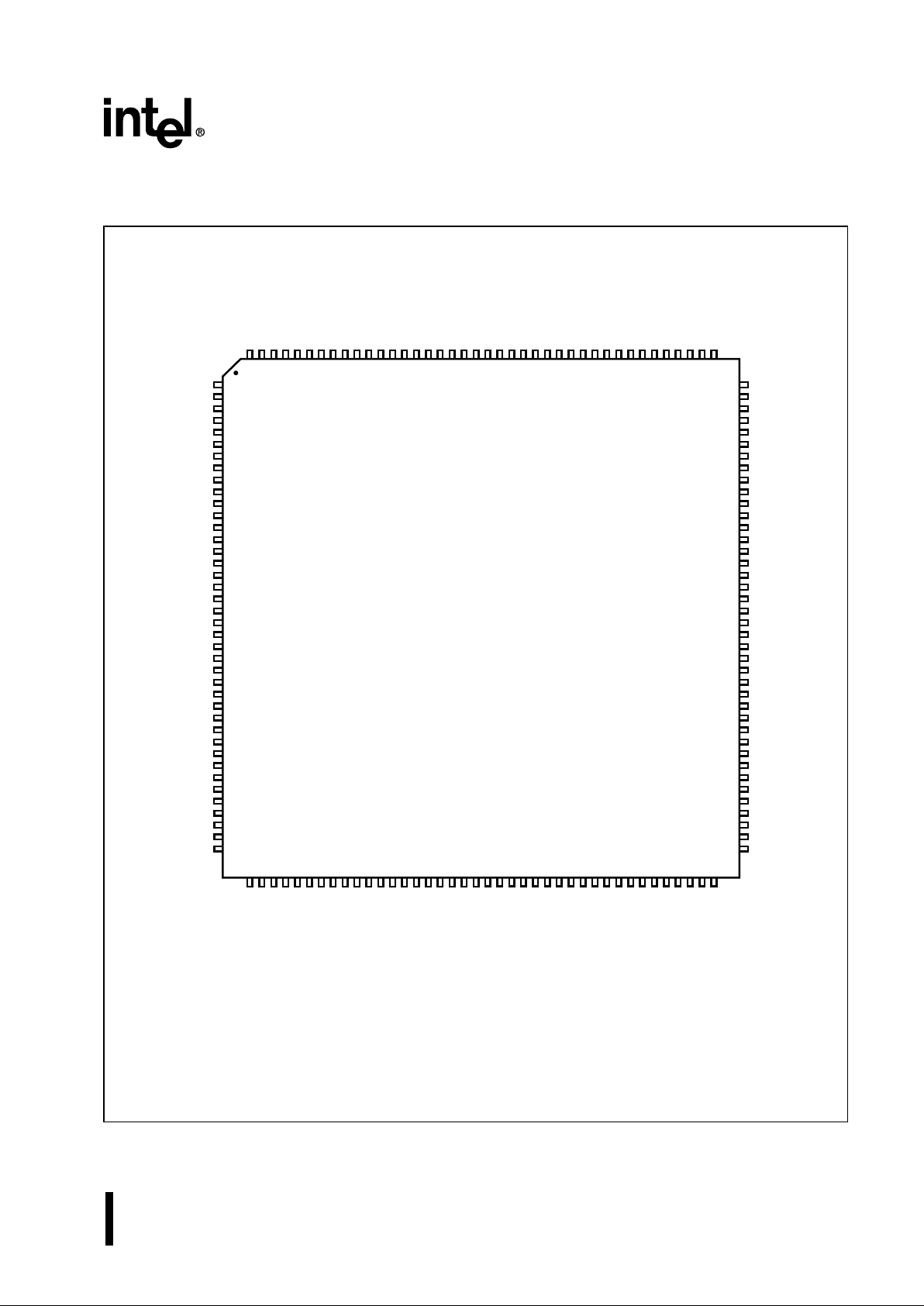

3. 83C196EA 160-pin QFP Package .......................................................................................3

4. System Bus Timing Diagram (Multiplexed Bus Mode).......................................................21

5. READY Timing Diagram (Multiplexed Bus Mode)..............................................................22

6. System Bus Timing Diagram (Demultiplexed Bus Mode) ..................................................25

7. READY Timing Diagram (Demultiplexed Bus Mode).........................................................26

8. Deferred Bus Mode Timing Diagram..................................................................................27

9. Serial Port Waveform — Shift Register Mode....................................................................28

10. Synchronous Serial Port....................................................................................................29

11. External Clock Drive Waveforms........................................................................................34

12. AC Testing Output Waveforms...........................................................................................35

13. Float Waveforms During 5.0 Volt Testing...........................................................................35

iv ADVANCE INFORMATION

CONTENTS

Tables

1. Description of Product Nomenclature ..................................................................................2

2. 83C196EA 160-pin QFP Package Pin Assignments............................................................4

3. Pin Assignment Arranged by Functional Categories............................................................5

4. Signal Descriptions ..................... ........ ......... ........ ......... ................................. ......... ........ .....6

5. 83C196EA Address Map....................................................................................................15

6. DC Characteristics at VCC = 4.5 V – 5.5 V..........................................................................17

7. AC Characteristics, Multiplexed Bus Mode........................................................................19

8. AC Timing Symbol Definitions............................................................................................20

9. AC Characteristics, Demultiplexed Bus Mode ...................................................................23

10. Serial Port Timing — Shift Register Mode .........................................................................28

11. Synchronous Serial Port Timing......................................................................................... 29

12. 10-bit A/D Operating Conditions (1)...................................................................................31

13. 10-bit Mode A/D Characteristics Over Specified Operating Conditions (7)........................31

14. 8-bit A/D Operating Conditions (1).....................................................................................32

15. 8-bit Mode A/D Characteristics Over Specified Operating Conditions (7)..........................33

16. External Clock Drive...........................................................................................................34

ADVANCE INFORMATION 1

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

1.0 PRODUCT OVERVIEW

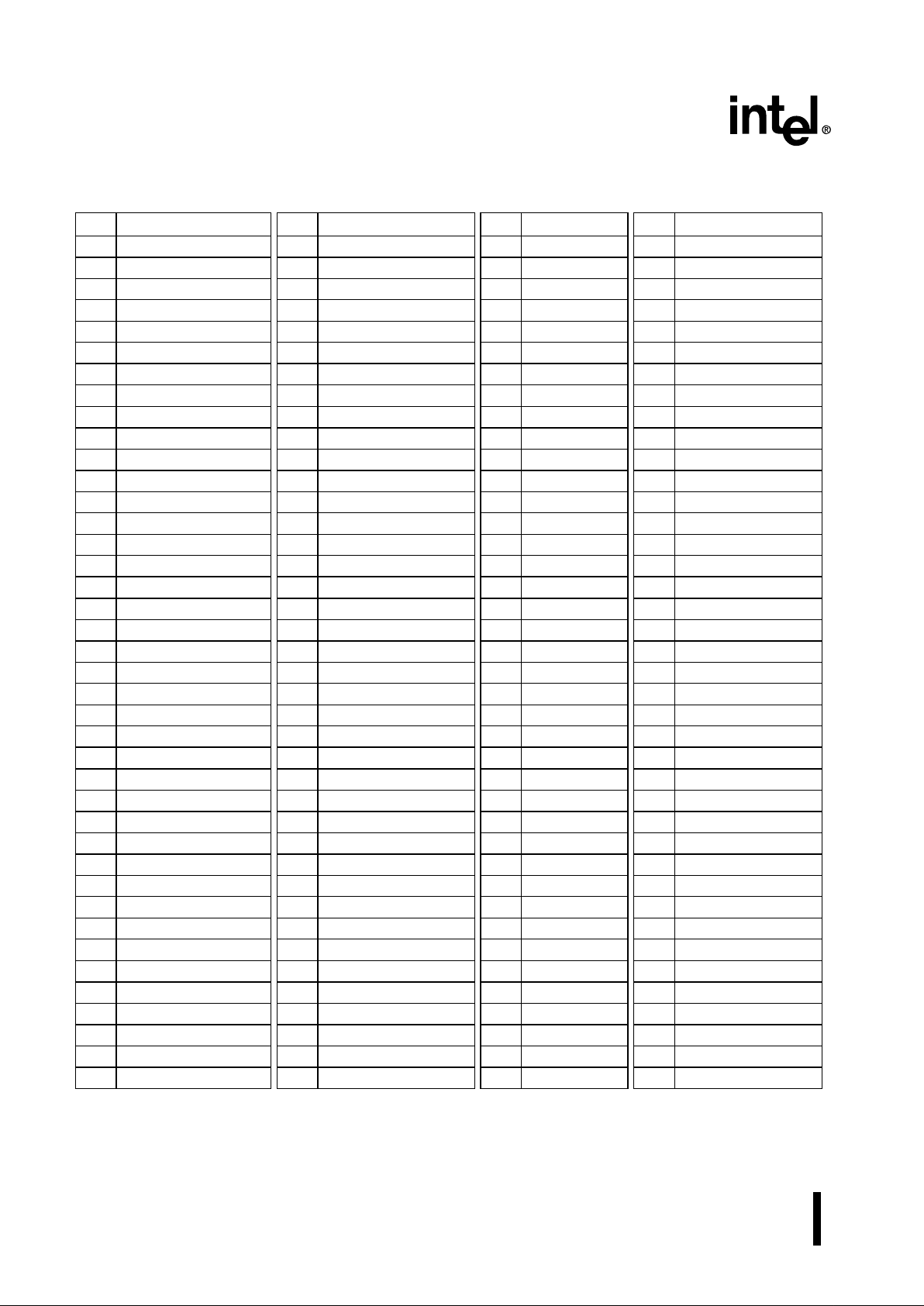

Figure 1. 83C 196EA Block Diagram

The 83C196EA is highly integrated with an enhanced peripheral set. The serial debug unit (SDU) provides

system debug and development capabi lities. The SDU can set a single hardware breakpoint and provides

read and write access to code RAM through a high-speed, dedicated serial link. A stack overflow/underflow

monitor assists in code development by causing an unmaskable interrupt if the stack pointer crosses a userdefined boundary. The 16-channel A/D converter supports an auto-scan mode that operates with no CPU

Code/Data

RAM

3 Kbytes

EPORT

Queue

A20:16

Source (16)

Destination (16)

AD15:0

SIO0

Baud-rate

Generator

EPA 4 Timers

Ports 7,8

Port 11

17 Capture/

Compares

A/D

Converter

Bus

Controller

A15:0

Serial Debug

Unit

Watchdog

Timer

Stack

Overflow

Module

Pulse-width

Modulators

SSIO0

SSIO1

ROM

8 Kbytes

A3178-03

SIO1

Baud-rate

Generator

Port 10

Bus-Control

Interface Unit

Microcode

Engine

Chip-select

Unit

Peripheral

Transaction

Server

Memory

Interface

Unit

Register

RAM

1 Kbyte

ALU

Interrupt

Controller

Peripheral

Interrupt

Handler

Bus Control

Peripheral Addr Bus (10)

Peripheral Data Bus (16)

Memory Addr Bus (24)

Port 12

8 Output/

Simulcaptures

Port 9

Port 2

Memory Data Bus (16)

2 ADVANCE INFORMATION

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

overhead. Each A/D channel has a dedicated result register. The EPA supports high-speed input captures

and output compares with 17 programmable, high-speed capture/compare channels. Eight output-only

channels provide support for time-base conversions by capturing the value of one of four timers when a

comp a r e oc curs.

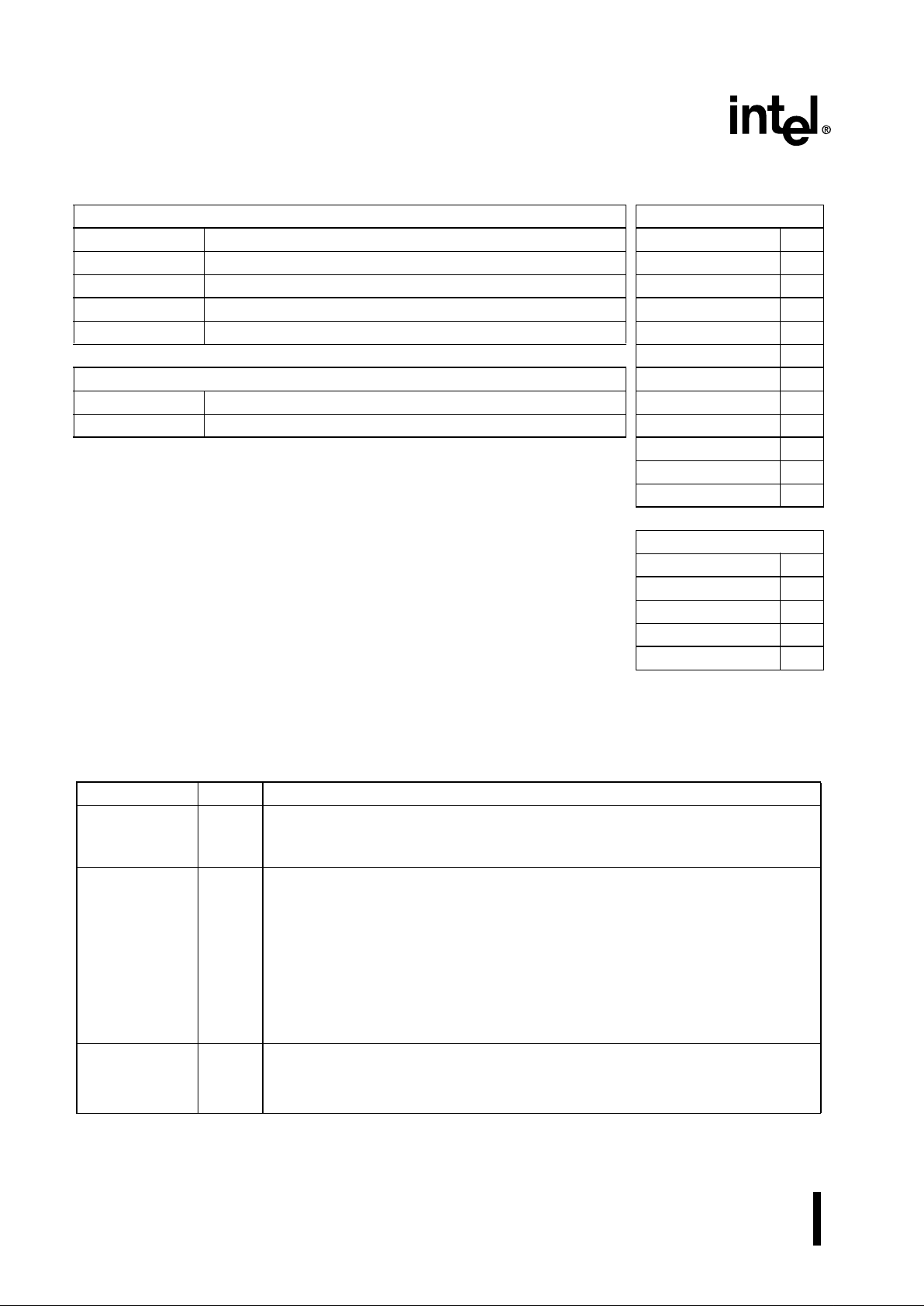

2.0 NOMENCLATURE OVERVIEW

Figure 2. Product Nomenclature

Table 1. Description of Product Nomenclature

Parameter Options Description

Temperature and Burn-in Opti ons A Automotive operating temperature range (–40° C to

125° C case) with Intel standa rd burn-in.

Packaging Options S QFP

Program Memory Options 3 Internal ROM

Process Information C CHMOS

Product Family 196EA

Device Speed no mark 40 MHz

Program Memory Options

XXXXX XXXX8XXX

Packaging Options

Temperature and Burn-in Options

A2815-01

Process Information

Product Family

Device Speed

ADVANCE INFORMATION 3

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

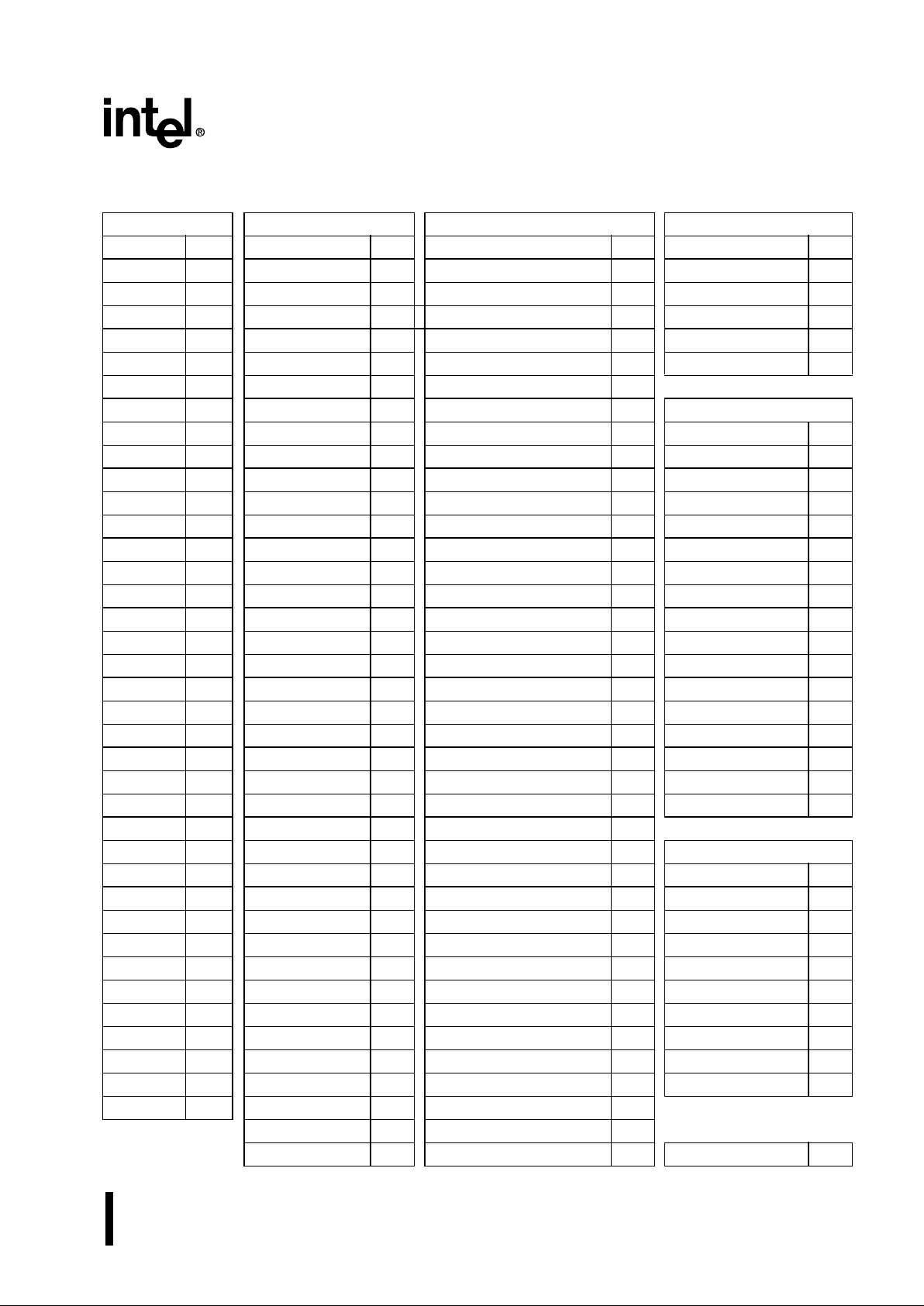

3.0 PINOUT

Figure 3. 83C196EA 160-pin QFP Package

A3151-02

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

AS83C196EA

View of component as

mounted on PC board

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

AD0 / P3.0

AD1 / P3.1

AD2 / P3.2

AD3 / P3.3

AD4 / P3.4

AD5 / P3.5

AD6 / P3.6

AD7 / P3.7

V

CC

V

CC

V

SS

V

SS

AD8 / P4.0

AD9 / P4.1

AD10 / P4.2

AD11 / P4.3

AD12 / P4.4

AD13 / P4.5

AD14 / P4.6

AD15 / P4.7

P5.7 / RPD

P5.4/BREQ#/TMODE#

P5.6 / READY

P5.1 / INST

P5.0 / ALE

P5.5 / BHE# / WRH#

P5.3 / RD#

P5.2 / WR# / WRL#

V

SS

V

CC

A20 / EPORT.4

A16 / EPORT.0

A17 / EPORT.1

A18 / EPORT.2

A19 / EPORT.3

EPORT.5 / CS0#

EPORT.6 / CS1#

EPORT.7 / CS2#

NC

NC

NC

NC

NC

NC

EA#

V

CC

PLLEN

XTAL2

XTAL1

V

SS

V

CC

P2.7 / CLKOUT

P2.6 / ONCE#

P2.5

P2.4 /RXD1

P2.3 / TXD1

P2.2 / EXTINT

P2.1 / RXD0

P2.0 / TXD0

V

CC

V

SS

CRBUSY#

CROUT

CRIN

CRDCLK

V

CC

NC

V

SS

V

SS

ACH15

ACH14

ACH13

ACH12

ACH11

ACH10

ACH9

ACH8

ACH7

ACH6

NC

A15

A14

A13

A12

A11

A10

A9

A8

V

CC

V

SS

A7

A6

A5

A4

A3

A2

A1

A0

P9.7 / OS7

P9.6 / OS6

P9.5 / OS5

P9.4 / OS4

P9.3 / OS3

P9.2 / OS2

P9.1 / OS1

P9.0 / OS0

P7.0 / EPA0 / T1CLK

P7.1 / EPA1 / T1RST

P7.2 / EPA2 / T2CLK

P7.3 / EPA3 / T2RST

P7.4 / EPA4 / T3CLK

P7.5 / EPA5 / T3RST

V

SS

V

CC

P7.6 / EPA6 / T4CLK

P7.7 / EPA7 / T4RST

P8.7 / EPA15

P8.6 / EPA14

P8.5 / EPA13

NC

P8.4 / EPA12

P8.3 / EPA11

P8.2 / EPA10

P8.1 / EPA9

P8.0 / EPA8

P10.5

P10.4 / EPA16

P10.3 / SD1

P10.2 / SC1 / CHS#

P10.1 / SD0

P10.0 / SC0

P11.4 / PWM4

P11.5 / PWM5

P11.6 / PWM6

P11.7 / PWM7

P11.3 / PWM3

P11.2 / PWM2

P11.1 / PWM1

P11.0 / PWM0

V

SS

V

CC

P12.4

P12.0

P12.1

P12.2

P12.3

V

SS

NC

V

CC

NC

RESET#

NMI

V

REF

ANGND

ACH0

ACH1

ACH2

ACH3

ACH4

ACH5

†

††

This pin supplies voltage to the phase-locked loop circuitry, so use extra care to keep it stable.

This pin supplies voltage to the code RAM. Maintain at 5 volts to retain data in code RAM.

NC pins must be unconnected to prevent accidental entry into a test mode.

†††

4 ADVANCE INFORMATION

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

Table 2. 83C196EA 160-pin QF P Package Pin Assi gnments

Pin Name Pin Name Pin Name Pin Name

1 AD0 / P3.0 41 NC 81 ACH5 121 NC

2 AD1 / P3.1 42 NC 82 ACH4 122 P8.5 / EPA13

3 AD2 / P3.2 43 NC 83 ACH3 123 P8.6 / EPA14

4 AD3 / P3.3 44 NC 84 ACH2 124 P8.7 / EPA15

5 AD4 / P3.4 45 EA# 85 ACH1 125 P7.7 / EPA7 / T4RST

6 AD5 / P3.5 46 V

CC

86 ACH0 126 P7.6 / EPA6 / T4CLK

7 AD6 / P3.6 47 PLLEN 87 ANGND 127 V

CC

8 AD7 / P3.7 48 XTAL2 88 V

REF

128 V

SS

9V

CC

49 XTAL1 89 NMI 129 P7.5 / EPA5 / T3RST

10 V

CC

50 V

SS

90 RESET# 130 P7.4 / EPA4 / T3CLK

11 V

SS

51 V

CC

91 NC 131 P7.3 / EPA3 / T2RST

12 V

SS

52 P2.7 / CLKOUT 92 V

CC

132 P7.2 / EPA2 / T2CLK

13 AD8 / P4.0 53 P2.6 / ONCE# 93 NC 133 P7.1 / EPA1 / T1RST

14 AD9 / P4. 1 54 P2.5 94 V

SS

134 P7.0 / EPA0 / T1CLK

15 AD10 / P4.2 55 P2.4 / RXD1 95 P12.3 135 P9.0 / OS0

16 AD11 / P4.3 56 P2.3 / TXD1 96 P12.2 136 P9.1 / OS1

17 AD12 / P4.4 57 P2.2 / EXTINT 97 P12.1 137 P9.2 / OS2

18 AD13 / P4.5 58 P2.1 / RXD0 98 P12.0 138 P9.3 / OS3

19 AD14 / P4.6 59 P2.0 / TXD0 99 P12.4 139 P9.4 / OS4

20 AD15 / P4.7 60 V

CC

100 V

CC

140 P9. 5 / OS5

21 P5.7 / RPD 61 V

SS

101 V

SS

141 P9. 6 / OS6

22 P5.4/BREQ#/TMODE# 62 CRBUSY# 102 P11.0 / PWM0 142 P9.7 / OS7

23 P5.6 / READY 63 CROUT 103 P11.1 / PWM1 143 A0

24 P5.1 / INST 64 CRIN 104 P11.2 / PWM2 144 A1

25 P5.0 / ALE 65 CRDCL K 105 P11.3 / PWM3 145 A2

26 P5.5 / BHE# / WRH# 66 V

CC

106 P11.7 / PWM7 146 A3

27 P5.3 / RD # 67 NC 107 P11.6 / PWM6 147 A4

28 P5.2 / WR# / WRL# 68 V

SS

108 P11.5 / PWM5 148 A5

29 V

SS

69 V

SS

109 P11.4 / PWM4 149 A6

30 V

CC

70 ACH15 110 P10.0 / SC0 150 A7

31 A20 / EPORT.4 71 ACH14 111 P10.1 / SD0 151 V

SS

32 A16 / EPORT.0 72 ACH13 112 P10.2 / SC1 152 V

CC

33 A17 / EPORT.1 73 ACH12 113 P10.3 / SD1 153 A8

34 A18 / EPORT.2 74 ACH11 114 P10.4 / EPA16 154 A9

35 A19 / EPORT.3 75 ACH10 115 P10.5 155 A10

36 EPORT.5 / CS0# 76 ACH9 116 P8.0 / EPA8 156 A11

37 EPORT.6 / CS1# 77 ACH8 117 P8.1 / EPA9 157 A12

38 EPORT.7 / CS2# 78 ACH7 118 P8.2 / EPA10 158 A13

39 NC 79 ACH6 119 P8.3 / EPA11 159 A14

40 NC 80 NC 120 P8.4 /EPA12 160 A15

ADVANCE INFORMATION 5

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

Table 3. Pin Assignment Arranged by Functional Categories

Addr & Data Input/Output Input/Output (Cont’d) Input/Output (Cont’d)

Name Pin Name Pin Name Pin Name Pin

A0 143 P2.0 / TXD0 59

EPORT.7 38 P12.0 98

A1 144 P2.1 / RXD0 58

P7.0 / EPA0 / T1CLK 134 P12.1 97

A2 145 P2.2 57

P7.1 / EPA1 / T1RST 133 P12.2 96

A3 146 P2.3 / TXD1 56

P7.2 / EPA2 / T2CLK 132 P12.3 95

A4 147 P2.4 / RXD1 55

P7.3 / EPA3 / T2RST 131 P12.4 99

A5 148 P2.5 54

P7.4 / EPA4 / T3CLK 130

A6 149 P2.6 53 P7.5 / EPA5 / T3RST 129 Analog Inputs

A7 150 P2.7 52

P7.6 / EPA6 / T4CLK 126 Name Pin

A8 153 P3.0 1

P7.7 / EPA7 / T4RST 125 ACH0 86

A9 154

P3.1 2 P8.0 / EPA8 116 ACH1 85

A10 155 R3.2 3

P8.1 / EPA9 117 ACH2 84

A11 156 P3.3 4

P8.2 / EPA10 118 ACH3 83

A12 157

P3.4 5 P8.3 / EPA11 119 ACH4 82

A13 158 P3.5 6

P8.4 / EPA12 120 ACH5 81

A14 159 P3.6 7

P8.5 / EPA13 122 ACH6 79

A15 160 P3.7 8

P8.6 / EPA14 123 ACH7 78

A16 32 P4.0 13

P8.7 / EPA15 124 ACH8 77

A17 33 P4.1 14

P9.0 / OS0 135 ACH9 76

A18 34 P4.2 15

P9.1 / OS1 136 ACH10 75

A19 35 P4.3 16

P9.2 / OS2 137 ACH11 74

A20 31 P4.4 17

P9.3 / OS3 138 ACH12 73

AD0 1

P4.5 18 P9.4 / OS4 139 ACH13 72

AD1 2 P4.6 19

P9.5 / OS5 140 ACH14 71

AD2 3 P4.7 20

P9.6 / OS6 141 ACH15 70

AD3 4

P5.0 25 P9.7 / OS7 142

AD4 5 P5.1 24

P10.0 / SC0 110 Bus Control & Status

AD5 6 P5.2 28

P10.1 / SD0 111 Name Pin

AD6 7 P5.3 27

P10.2 / SC1 112 ALE 25

AD7 8 P5.4 22

P10.3 / SD1 113 BHE#/WRH# 26

AD8 13 P5.5 26

P10.4 / EPA16 114 BREQ# 22

AD9 14 P5.6 23

P10.5 115 CS0# 36

AD10 15

P5.7 21 P11.0 / PWM0 102 CS1# 37

AD11 16

EPORT.0 32 P11.1 / PWM1 103 CS2# 38

AD12 17

EPORT.1 33 P11.2 / PWM2 104 INST 24

AD13 18

EPORT.2 34 P11.3 / PWM3 105 RD# 27

AD14 19

EPORT.3 35 P11.4 / PWM4 109 READY 23

AD15 20

EPORT.4 31 P11.5 / PWM5 108

EPORT.5 36 P11.6 / PWM6 107

EPORT.6 37 P11.7 / PWM7 106 WR#/WRL# 28

6 ADVANCE INFORMATION

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

4.0 SIGNALS

Power & Ground Processor Control

Name

Pins Name Pin

ANGND

87 CLKOUT 52

V

CC

9, 10, 30, 46†, 51, 60, 66††, 92, 100, 127, 152 EA# 45

V

SS

11, 12, 29, 50, 61, 68, 69, 94, 101, 128, 151 EXTINT 57

V

REF

88 NMI 89

ONCE# 53

No Connection PLLEN 47

Name

Pins RESET# 90

NC

†††

39–44, 67, 69, 80, 91, 93, 121 RPD 21

TMODE# 22

XTAL1 49

XTAL2 48

†

This pin sup pl ies voltage to the phase-locked loop circuitry, so use extra

care to keep it stable.

††

This pin supplies voltage to code RAM. To retain data, maintain 5 volts.

†††

Always leave NC (no connect) pins unconnected to prevent accidental

entry into test modes.

Code Debug

Name Pin

CRBUSY# 62

CRDCLK 6 5

CRIN 64

CROUT 63

Table 4. Signal Descriptions

Name Type Description

A15:0 I/O System Address Bus

These address lines provide address bits 0–15 during the entire external

memory cycle during both multiplexe d and demultiplex ed bus modes.

A20:16 I/O Address Li nes 16–20

These address lines provide address bits 16–20 during the entire external

memory cycle, supporting extended addressing of the 2 Mbyte address space.

NOTE: Internally, there are 24 address bits; however, only 21 external

address pins (A20:0) are implemented. The internal address space is

16 Mbytes (000000–FFFFFFH) and the external addr ess space is 2

Mbytes (00000–1FFFFFH). The device resets to FF2080H in internal

memory or 1F2080H in external memory.

A20:16 are multiplexed with EPORT.4:0.

ACH15:0 I Analog Channels

These pins are analog inputs to the A/D converter.

The ANGND and V

REF

pins must be con nected for the A/D converter to functi on.

Table 3. Pin Assignment Arranged by Functional Categories (Continued)

ADVANCE INFORMATION 7

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

AD15:0 I/O Address/Data Lines

The function of these pins depend on the bus size and mode. When a bus

access is not occurring, these pins revert to their I/O port function.

16-bit Multiplexed Bus Mode:

AD15:0 dr ive ad dres s bit s 0– 15 d uring th e firs t half of t he bus cycl e and driv e or

receive dat a during the second half of the bus cycle.

8-bit Multiplexed Bus Mode:

AD15:8 drive address bits 8–15 during the ent i re bus cycle. AD7:0 drive

address bit s 0–7 during the first half of the bus cycle and drive or r eceive data

during the second half of the bus cycle .

16-bit D em u lt ip lexed Mode :

AD15:0 drive or receive data during the entire bus cycle.

8-bit Demultiplexed Mode:

AD7:0 drive or receive data dur ing the en tire bus cycle. AD1 5 :8 driv e the data

that is cur r ently on the high byte of the internal bus.

ALE O Address Latch Enable

This active-high output signal is asserted only during external memory cycles.

ALE signals the start of an external bus cycle and indicates that valid address

information is available on the system address/da ta bus (A20:16 and AD1 5:0

for a multipl exed bus; A20:0 for a de mul tiplexed bus).

An external latch can use thi s signal to demul tiplex address bits 0–15 from the

address/data bus in multiplexed mode.

ALE shares a package pin with P5.0.

ANGND GND Analog Ground

ANGND must be connected for A/D converter operat i on. ANGND and V

SS

should be nomi nally at the same potential.

BHE# O Byte High Enable

†

During 16-bi t bus cycles, this active-low output signal is asserted for w ord and

high-byte reads and wri tes to external memory. BHE# indicates that valid data

is being transferred over the upper half of the system data bus. Use BHE#, in

conjunct i on with AD0, to determine which memory byte is being transferred

over the system bus:

BHE# AD0 Byte(s) Accessed

0 0 both bytes

0 1 high byte only

1 0 low byte only

BHE# shares a package pin with P5.5 and WRH#.

†

The chip configuration register 0 (CCR0) determines whether this pin functions as BHE# or WRH#. CCR0.2 = 1 selects BHE#; CCR0.2 = 0 selects

WRH#.

BREQ# O Bus Request

This active-low output signal is assert ed during a hold cycl e w hen the bus

controller has a pending external memory cycle.

You must enable the bus-ho l d protocol before using this signal.

BREQ# shares a package pin with P5.4.

Table 4. Signal Descriptions (Continued)

Name Type Description

8 ADVANCE INFORMATION

83C196EA CHMOS 16-BIT MICROCONTROLLER — AUTOMOTIVE

CLKOUT O Clock Output

Output of the internal clo ck generator. The CLKOUT frequency can be

programmed to one of five frequencies: the internal operating frequency (f)

divided by a factor of two, four, eight, or sixteen, or the s ame frequency as the

oscillator input (F

XTAL1

). CLKOUT has a 50% d uty cycle.

CLKOUT shares a package pin with P2.7

CRBUSY# O Code RAM Busy

This signal indicates that the serial debug unit (SDU) is not ready to conduct a

transaction.

CRDCLK I Code RAM Clock

Provides the clock signal for the serial debug unit (SDU). The maxi mum clock

frequency equals the operati ng frequency (f) divided by two.

CRIN I Code RAM Data Input

Serial input for test instructions and dat a i nto the serial debug unit (SDU). Da ta

is transfer red in 8-bit byte s wit h the mos t-s ignif ican t bit (MSB ) fir st. Each by te i s

sampled on the rising edge of CRDCLK.

CROUT O Code RAM Data Output

Serial output for data from the serial debug unit (SDU). Data is transferred in 8bit bytes with the most-signif i cant bit (MSB) first. Each byt e is valid on the ri sing

edge of CRDCLK.

CS2:0# O Chip-select Lines 0–2

The active-low output CS

x

# is asserted during an external memory cycle when

the address to be accessed is in the range programme d for chip select

x

. If the

external memory address is outs ide the range assigned to the three chip

selects, no chip-select output is ass e rted and the bus configuration defaults to

the CS2# values.

Immediately following res et, CS0# is automatically assi gned to the range

FF2000–FF20FFH (1F2000–1F20FFH if external).

CS2:0# share package pins with EPORT.7:5.

EA# I External Ac ce s s

This input determines whether memory accesses to special -purpose and

program memory partitions (FF2000–FF3FFFH) are directed to internal or

external memory. These accesses are directed to internal memory if EA# is

held high and to extern al memo ry if EA# is he ld low . For an ac ces s to any ot her

memory location, the value of EA# is irrelevant.

EA# is sampled and latched only on the rising edge of RESET#. Changing the

level of EA# aft er reset has no effect.

On devices with no internal nonvolatile memory, always c onnect EA# to V

SS

.

EPA16:0 I/O Event Proc essor Array (EPA) Capture/Compare Channels

High-speed input/output signals for the EPA capture/compare channels.

EPA16:0 share package pins with the followi ng signals : EPA0/P7.0/T 1CLK,

EPA1/P7.1/T1RST, EPA2/P7.2/T2CLK, EPA3/P7.3 /T 2RST,

EPA4/P7.4/T3CLK, EPA5/P7.5/T3RST, EPA6/P7.6/T4CLK,

EPA7/P7.7/T4RST, EPA 8 /P8.0, EPA9/P8.1, EPA10/P8.2, EPA11/P8.3,

EPA12/P8.4, EPA13/P8.5, EPA14/P8.6, EPA 15/P8.7, and EPA16/P10.4.

Table 4. Signal Descriptions (Continued)

Name Type Description

Loading...

Loading...