Intel Corporation A610, 610 Datasheet

E

June 1997

Order Number 242323-004

n

Compatible with Large Software Base

− MS-DOS*, Windows*, OS/2*, UNIX*

n

32-Bit CPU with 64-Bit Data Bus

n

Superscalar Architecture

− Two Pipelined Integer Units Are

Capable of 2 Instructions/Clock

− Pipelined Floating Point Unit

n

Separate Code and Data Caches

− 8K Code, 8K Writeback Data

− MESI Cache Protocol

n

Advanced Design Features

− Branch Prediction

− Virtual Mode Extensions

n

3.3V BiCMOS Silicon Technology

n

4M Pages for Increased TLB Hit Rate

n

IEEE 1149.1 Boundary Scan

n

Internal Error Detection Features

n

SL Enhanced Power Management

Features

−

System Management Mode

−

Clock Control

n

Fractional Bus Operation

−

75-MHz Core / 50-MHz Bus

The Pentium® processor is fully compatible with the entire installed base of applic ations for DOS*, Windows *,

OS/2*, and UNIX*, and all other software that runs on any earlier Intel 8086 family product. The Pentium

processor’s superscalar architecture can execute two instructions per clock cycle. Branch prediction and

separate caches also increase performance. The pipelined floating-point unit delivers workstation level

performance. Separate c ode and data c ac hes reduc e c ac he c onflic ts while r emaining s oftwar e trans parent. The

Pentium processor (610\75) has 3.3 million transistors, is built on Intel’s advanced 3.3V BiCMOS silicon

technology, and has full SL Enhanced power management features, including System Management Mode

(SMM) and clock control. The additional SL Enhanc ed features, 3.3V operation, and the TCP pac kage, which

are not available in the Pentium processor (510\60, 567\66), make the Pentium processor (610\75) TCP ideal for

enabling mobile Pentium processor designs. The Pentium processor may contain design defects or errors

known as er rata which may c ause the product to deviate from published s pecifications. Current characteriz ed

errata are available upon request.

PENTIUM® PROCESSOR at iCOMP® INDEX 610\75 MHz

PENTIUM

®

PROCESSOR (610\75) E

CONTENTS

PAGE

1.0. INTRODUCTION................................................2

1.1. Pentium

®

Processor (610\75) SPGA

Specifications and Differences from the TCP

Package.............................................................2

2.0. MICROPROCESSOR ARCHITECTURE

OVERVIEW...........................................................3

2.1. Pentium

®

Processor Family Architecture........4

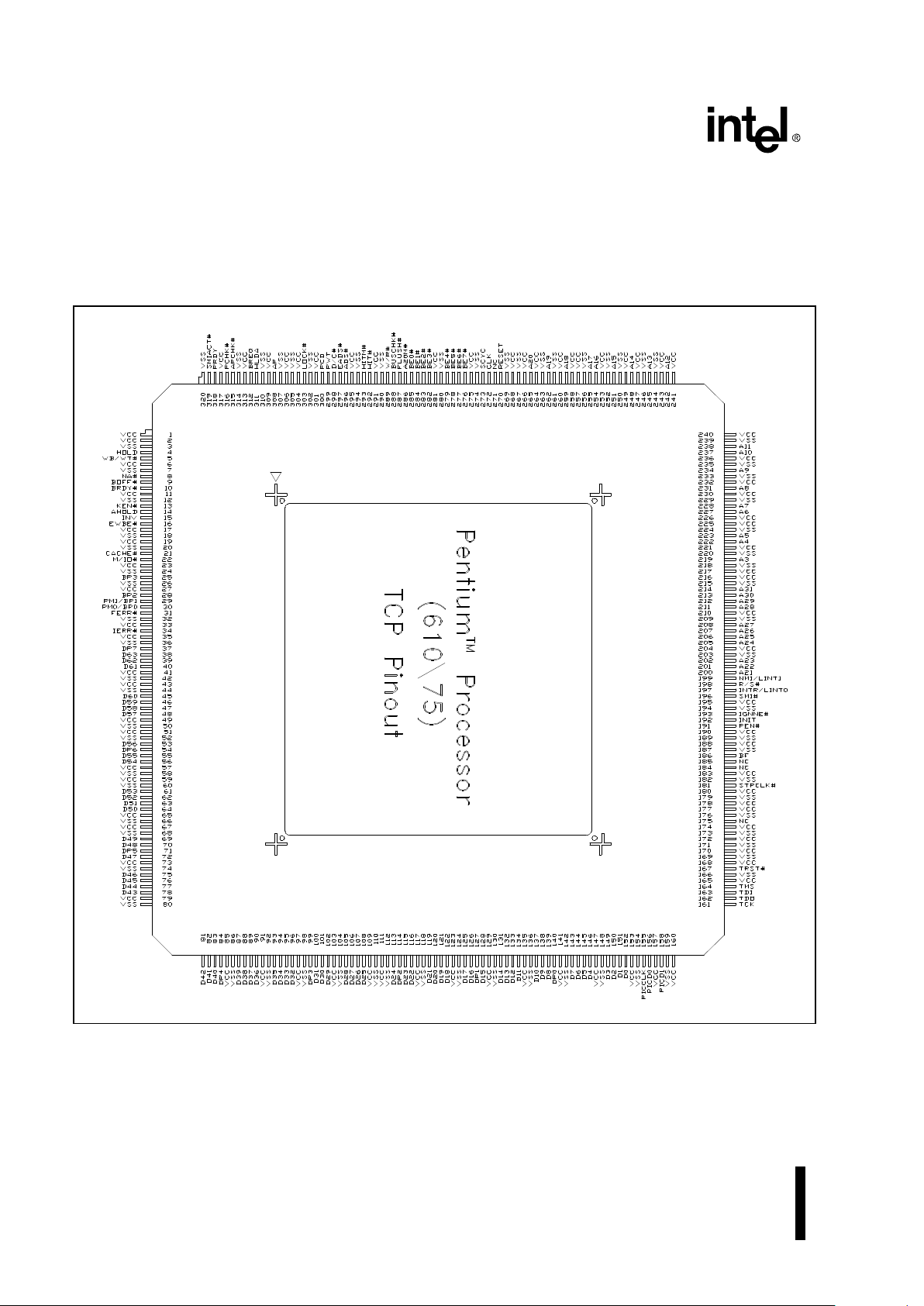

3.0. TCP PINOUT......................................................7

3.1. TCP Pinout and Pin Descriptions...................7

3.1.1. Pentium

®

Processor (610\75) TCP

PINOUT.........................................................7

3.1.2. PIN CROSS REFERENCE TABLE FOR

Pentium

®

Processor (610\75) TCP................8

3.2. Design Notes................................................10

3.3. Quick Pin Reference.....................................10

3.4. Pin Reference Tables...................................19

3.5. Pin Grouping According to Function.............22

4.0. Pentium

®

Processor (610\75) TCP

ELECTRICAL SPECIFICATIONS......................23

4.1. Maximum Ratings.........................................23

4.2. DC Specifications.........................................23

PAGE

4.3. AC Specifications..........................................25

4.3.1. POWER AND GROUND.......................25

4.3.2. DECOUPLING RECOMMENDATIONS25

4.3.3. CONNECTION SPECIFICATIONS ......26

4.3.4. AC TIMINGS FOR A 50-MHZ BUS.......26

4.4. I/O Buffer Models..........................................35

4.4.1. BUFFER MODEL PARAMETERS........38

4.4.2. SIGNAL QUALITY SPECIFICATIONS.39

4.4.2.1. Ringback.........................................40

4.4.2.2. Settling Time...................................40

5.0. Pentium

®

Processor (610\75) TCP

MECHANICAL SPECIFICATIONS.....................42

5.1. TCP Package Mechanical Diagrams............42

6.0. Pentium® Processor (610\75) TCP THERMAL

SPECIFICATIONS...............................................47

6.1. Measuring Thermal Values...........................47

6.2. Thermal Equations........................................47

6.3. TCP Thermal Characteristics........................47

6.4. PC Board Enhancements..............................47

6.4.1. STANDARD TEST BOARD

CONFIGURATION ......................................48

Information in this document is provided in connec tion with Intel products. No licens e, express or implied, by estoppel or otherwis e, to any

intellectual property rights is gr anted by this document. Ex cept as prov ided in Intel’s Terms and Conditions of Sale for suc h products , Intel

assu mes n o liab ility w ha ts oe v er , and Intel disc laims any expr ess or implied warranty , relating to sale and/or use of Intel produc ts including

liability o r w ar r an ties r e latin g to fit nes s f or a p ar tic ula r pur p os e, mer c hantability , or infringement of any patent, copyr ight or other intellectual

property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not r ely on the absence or charac teristics of any features or instructions mark ed "res erved" or "undefined." Intel reser ves

these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium

®

process or may contain design defects or errors known as errata which may cause the pr oduct to deviate from published

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect IL 60056-7641

or call 1-800-879-4683

or visit Intel’s website at http:\\www.intel.com

Copyright © Intel Corporation 1996, 1997.

* Third-party brands and names are the property of their respective owners.

PENTIUM® PROCESSOR (610\75)

1

1.

0. INTRODUCTION

Intel is now manufacturing its latest version of the

Pentium® processor family that is designed

specifically for mobile systems, with a core

frequency of 75 MHz and a bus frequency of 50

MHz. The Pentium processor (610\75) is provided

in the TCP (Tape Carrier Package) and SPGA

packages, and has all of the advanced features of

the Pentium processor (735\90, 815\100) .

The new Pentium processor (610\75) TCP

package has several features which allow highperformance notebooks to be designed with the

Pentium processor, including the following:

• TCP package dimensions are ideal for small

form-factor designs.

• The TCP package has superior thermal

resistance characteristics.

• 3.3V VCC reduces power consumption by half

(in both the TCP and SPGA packages).

• The SL Enhanced feature set, which was

initially implemented in the Intel486™ CPU.

The architecture and internal features of the

Pentium processor (610\75) TCP and SPGA

packages are identical to those of the Pentium

processor (735\90, 815\100), although several

features have been eliminated for the Pentium

processor (610\75) TCP, as described in section

1.1.

This document should be used in conjunction with

the Pentium processor documents listed below.

List of related documents:

• Pentium® Processor Family Developer’s

Manual, Vol. 1 (Order Number: 241428)

• Pentium® Processor Family Developer’s

Manual, Vol. 3: Architecture and Programming

Manual (Order Number: 241430)

1.1.

Pentium® Processor (610\75)

SPGA Specifications and

Differences from the TCP

Package

This section provides references to the Pentium

processor (610\75) SPGA specifications and

describes the major differences between the

Pentium processor (610\75) SPGA and TCP

packages.

All Pentium processor (610\75) SPGA

specifications, with the exception of power

consumption, are identical to the Pentium

processor (735\90, 815\100) specifications

provided in the Pentium® Processor Family

Developer’s Manual, Volume 1. See Tables 8 and

11 in section 4.2 for the Pentium processor

(610\75) SPGA and TCP power specifications.

The following features have been eliminated for

the Pentium processor (610\75) TCP: the Upgrade

feature, the Dual Processing (DP) feature, and the

Master/Checker functional redundancy feature.

Table 1 lists the corresponding pins which exist on

the Pentium processor (610\75) SPGA but have

been removed on the Pentium processor (610\75)

TCP.

PENTIUM® PROCESSOR (610\75)

2

Table 1. SPGA Signals Removed in TCP

Signal Function

ADSC# Additional Address Status. This signal is mainly used for large or standalone L2

cache memory subsystem support required for high-performance desktop or

server models.

BRDYC# Additional Burst Ready. This signal is mainly used for large or standalone L2

cache memory subsystem support required for high-performance desktop or

server models.

CPUTYP CPU Type. This signal is used for dual processing systems.

D/P# Dual/Primary processor identification. This signal is only used for an Upgrade

processor.

FRCMC# Functional Redundancy Checking. This signal is only used for error detection

via processor redundancy, and requires two Pentium processors

(master/checker).

PBGNT# Private Bus Grant. This signal is only used for dual processing systems.

PBREQ# Private Bus Request. This signal is used only for dual processing systems.

PHIT# Private Hit. This signal is only used for dual processing systems.

PHITM# Private Modified Hit. This signal is only used for dual processing systems.

The I/O buffer models provided in section 4.4 of this

document apply to both the Pentium processor

(610\75) TCP and SPGA packages, although the

capacitance (Cp) and inductance (Lp) parameter

values differ between the two packages. Also, the

thermal parameters, T

CASE

max and θCA, differ

between the TCP and SPGA packages. For

Pentium processor (610\75) SPGA values, refer to

Chapters 24 and 26 of the Pentium® Processor

Family Developer’s Manual, Volume 1 .

2.

0. MICROPROCESSOR

ARCHITECTURE OVERVIEW

The Pentium processor at iCOMP® rating 610\75

MHz extends the Intel Pentium family of

microprocessors. It is compatible with the 8086/88,

80286, Intel386™ DX CPU, Intel386 SX CPU,

Intel486™ DX CPU, Intel486 SX CPU, Intel486

DX2 CPUs, the Pentium processor at iCOMP Index

510\60 MHz and iCOMP Index 567\66 MHz, and

the Pentium processor at iCOMP Index 735\90

MHz and iCOMP Index 815\100 MHz.

The Pentium processor family consists of the new

Pentium processor at iCOMP rating 610\75 MHz,

described in this document, the original Pentium

processor (510\60, 567\66), and the Pentium

processor (735\90, 815\100). The name "Pentium

processor (610\75)" will be used in this document to

refer to the Pentium processor at iCOMP rating

610\75 MHz. "Pentium Processor" will be used in

this document to refer to the entire Pentium

processor family in general.

The Pentium processor family architecture contains

all of the features of the Intel486 CPU family, and

provides significant enhancements and additions

including the following:

• Superscalar Architecture

• Dynamic Branch Prediction

• Pipelined Floating-Point Unit

• Improved Instruction Execution Time

• Separate 8K Code and 8K Data Caches

• Writeback MESI Protocol in the Data Cache

• 64-Bit Data Bus

• Bus Cycle Pipelining

• Address Parity

• Internal Parity Checking

• Execution Tracing

• Performance Monitoring

• IEEE 1149.1 Boundary Scan

• System Management Mode

PENTIUM® PROCESSOR (610\75)

3

• Virtual Mode Extensions

2.1.

Pentium® Processor Family

Architecture

The application instruction set of the Pentium

processor family includes the complete Intel486

CPU family instruction set with extensions to

accommodate some of the additional functionality

of the Pentium processors. All application software

written for the Intel386 and Intel486 family

microprocessors will run on the Pentium processors

without modification. The on-chip memory

management unit (MMU) is completely compatible

with the Intel386 family and Intel486 family of

CPUs.

The Pentium processors implement several

enhancements to increase performance. The two

instruction pipelines and floating-point unit on

Pentium processors are capable of independent

operation. Each pipeline issues frequently used

instructions in a single clock. Together, the dual

pipes can issue two integer instructions in one

clock, or one floating point instruction (under certain

circumstances, two floating-point instructions) in

one clock.

Branch prediction is implemented in the Pentium

processors. To support this, Pentium processors

implement two prefetch buffers, one to prefetch

code in a linear fashion, and one that prefetches

code according to the BTB so the needed code is

almost always prefetched before it is needed for

execution.

The floating-point unit has been completely

redesigned over the Intel486 CPU. Faster

algorithms provide up to 10X speed-up for common

operations including add, multiply, and load.

Pentium processors include separate code and

data caches integrated on-chip to meet performance goals. Each cache is 8 Kbytes in size, with a

32-byte line size and is 2-way set associative. Each

cache has a dedicated Translation Lookaside Buffer

(TLB) to translate linear addresses to physical

addresses. The data cache is configurable to be

writeback or writethrough on a line-by-line basis

and follows the MESI protocol. The data cache tags

are triple ported to support two data transfers and

an inquire cycle in the same clock. The code cache

is an inherently write-protected cache. The code

cache tags are also triple ported to support

snooping and split line accesses. Individual pages

can be configured as cacheable or non-cacheable

by software or hardware. The caches can be

enabled or disabled by software or hardware.

The Pentium processors have increased the data

bus to 64 bits to improve the data transfer rate.

Burst read and burst writeback cycles are

supported by the Pentium processors. In addition,

bus cycle pipelining has been added to allow two

bus cycles to be in progress simultaneously. The

Pentium processors' Memory Management Unit

contains optional extensions to the architecture

which allow 2-Mbyte and 4-Mbyte page sizes.

The Pentium processors have added significant

data integrity and error detection capability. Data

parity checking is still supported on a byte-by-byte

basis. Address parity checking, and internal parity

checking features have been added along with a

new exception, the machine check exception.

As more and more functions are integrated on chip,

the complexity of board level testing is increased.

To address this, the Pentium processors have

increased test and debug capability. The Pentium

processors implement IEEE Boundary Scan

(Standard 1149.1). In addition, the Pentium

processors have specified 4 breakpoint pins that

correspond to each of the debug registers and

externally indicate a breakpoint match. Execution

tracing provides external indications when an

instruction has completed execution in either of the

two internal pipelines, or when a branch has been

taken.

System Management Mode (SMM) has been

implemented along with some extensions to the

SMM architecture. Enhancements to the virtual

8086 mode have been made to increase

performance by reducing the number of times it is

necessary to trap to a virtual 8086 monitor.

PENTIUM® PROCESSOR (610\75)

4

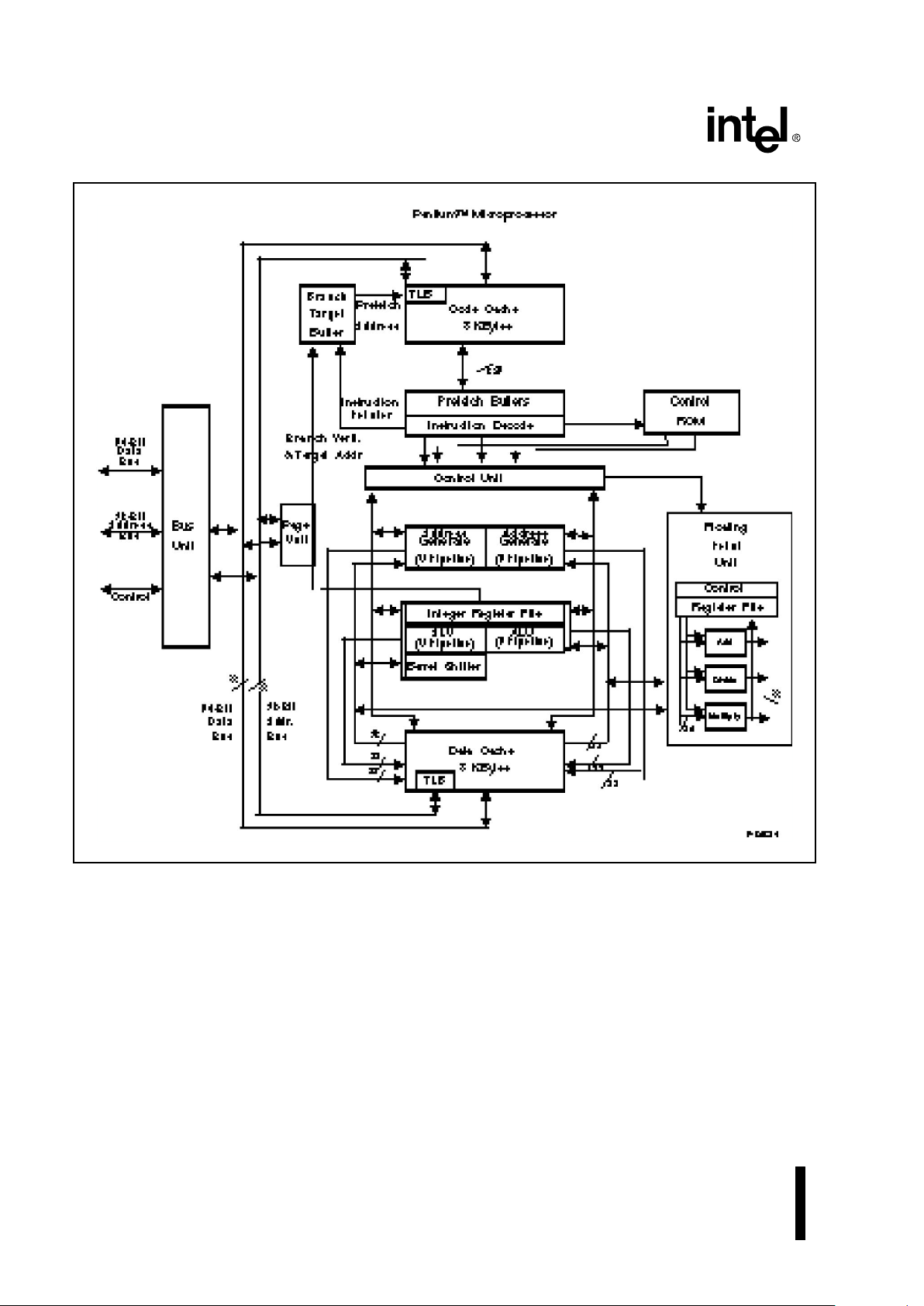

Figure 1. Pentium® Processor Block Diagram

PENTIUM® PROCESSOR (610\75)

5

The block diagram shows the two instruction

pipelines, the "u" pipe and the "v" pipe. The u-pipe

can execute all integer and floating point

instructions. The v-pipe can execute simple integer

instructions and the FXCH floating-point

instructions.

The separate caches are shown, the code cache

and data cache. The data cache has two ports, one

for each of the two pipes (the tags are triple ported

to allow simultaneous inquire cycles). The data

cache has a dedicated Translation Lookaside Buffer

(TLB) to translate linear addresses to the physical

addresses used by the data cache.

The code cache, branch target buffer and prefetch

buffers are responsible for getting raw instructions

into the execution units of the Pentium processor.

Instructions are fetched from the code cache or

from the external bus. Branch addresses are

remembered by the branch target buffer. The code

cache TLB translates linear addresses to physical

addresses used by the code cache.

The decode unit decodes the prefetched

instructions so the Pentium processor can execute

the instruction. The control ROM contains the

microcode which controls the sequence of

operations that must be performed to implement the

Pentium processor architecture. The control ROM

unit has direct control over both pipelines.

The Pentium processors contain a pipelined

floating-point unit that provides a significant

floating-point performance advantage over previous

generations of processors.

The architectural features introduced in this section

are more fully described in the Pentium® Processor

Family Developer’s Manual.

PENTIUM® PROCESSOR (610\75)

6

3.

0. TCP PINOUT

3.1.

TCP Pinout and Pin Descriptions

3.1.1. Pentium® Processor (610\75) TCP PINOUT

Figure 2. Pentium® Processor (610\75) TCP Pinout

PENTIUM® PROCESSOR (610\75)

7

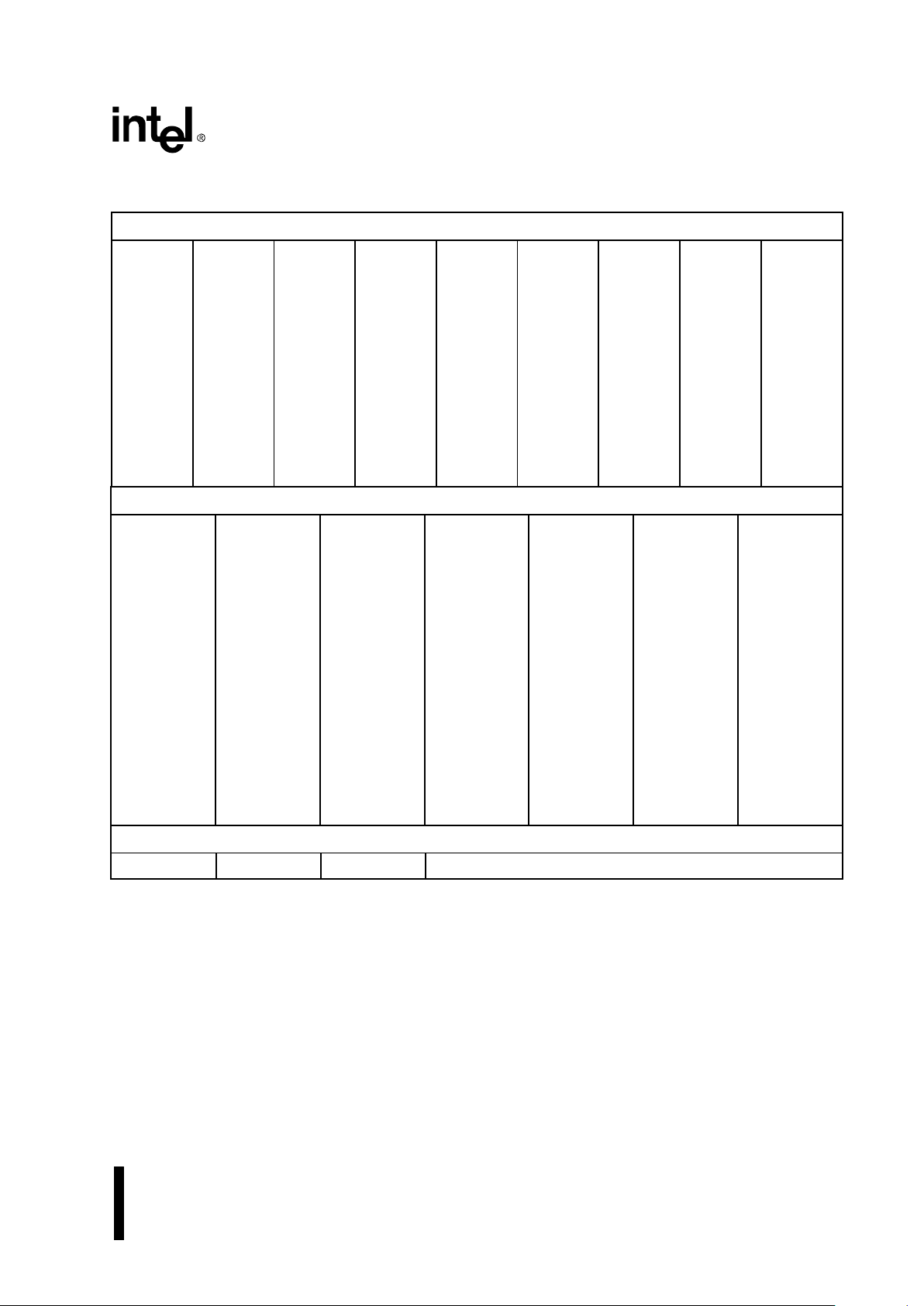

3.1.2. PIN CROSS REFERENCE TABLE FOR Pentium® Processor (610\75) TCP

Table 2. TCP Pin Cross Reference by Pin Name

Address

A3 219 A9 234 A15 251 A21 200 A27 208

A4 222 A10 237 A16 254 A22 201 A28 211

A5 223 A11 238 A17 255 A23 202 A29 212

A6 227 A12 242 A18 259 A24 205 A30 213

A7 228 A13 245 A19 262 A25 206 A31 214

A8 231 A14 248 A20 265 A26 207

Data

D0 152 D13 132 D26 107 D39 87 D52 62

D1 151 D14 131 D27 106 D40 83 D53 61

D2 150 D15 128 D28 105 D41 82 D54 56

D3 149 D16 126 D29 102 D42 81 D55 55

D4 146 D17 125 D30 101 D43 78 D56 53

D5 145 D18 122 D31 100 D44 77 D57 48

D6 144 D19 121 D32 96 D45 76 D58 47

D7 143 D20 120 D33 95 D46 75 D59 46

D8 139 D21 119 D34 94 D47 72 D60 45

D9 138 D22 116 D35 93 D48 70 D61 40

D10 137 D23 115 D36 90 D49 69 D62 39

D11 134 D24 113 D37 89 D50 64 D63 38

D12 133 D25 108 D38 88 D51 63

PENTIUM® PROCESSOR (610\75)

8

Table 2. TCP Pin Cross Reference by Pin Name (Contd.)

Control

A20M# 286 BREQ 312 HITM# 293 PM1/BP1 29

ADS# 296 BUSCHK# 288 HLDA 311 PRDY 318

AHOLD 14 CACHE# 21 HOLD 4 PWT 299

AP 308 D/C# 298 IERR# 34 R/S# 198

APCHK# 315 DP0 140 IGNNE# 193 RESET 270

BE0# 285 DP1 127 INIT 192 SCYC 273

BE1# 284 DP2 114 INTR/LINT0 197 SMI# 196

BE2# 283 DP3 99 INV 15 SMIACT# 319

BE3# 282 DP4 84 KEN# 13 TCK 161

BE4# 279 DP5 71 LOCK# 303 TDI 163

BE5# 278 DP6 54 M/IO# 22 TDO 162

BE6# 277 DP7 37 NA# 8 TMS 164

BE7# 276 EADS# 297 NMI/LINT1 199 TRST# 167

BOFF# 9 EWBE# 16 PCD 300 W/R# 289

BP2 28 FERR# 31 PCHK# 316 WB/WT# 5

BP3 25 FLUSH# 287 PEN# 191

BRDY# 10 HIT# 292 PM0/BP0 30

APIC Clock Control

PICCLK 155 PICD1 158 BF 186 STPCLK# 181

PICD0 156

[APICEN]

CLK 272

[DPEN#]

PENTIUM® PROCESSOR (610\75)

9

Table 2. TCP Pin Cross Reference by Pin Name (Contd.)

V

cc

1*

2

6*

11*

17*

19

23

27*

33*

35

41*

43

49*

51

57*

59

65*

67

73

79

85

91

97

103

109

111*

117

123

129

135

141

147

153*

157*

160

165*

168*

170*

172*

174*

177*

178

180*

183*

188*

190*

195*

204

210

216

217*

221

225*

226

230

232*

236

240*

241

243*

247

249*

253

257*

258

260*

264

266*

268*

275

281

291

295

301

304*

306

309*

313

317*

V

ss

3

7

12

18

20

24

26

32

36

42

44

50

52

58

60

66

68

74

80

86

92

98

104

110

112

118

124

130

136

142

148

154

159

166

169

171

173

176

179

182

187

189

194

203

209

215

218

220

224

229

233

235

239

244

246

250

252

256

261

263

267

269

274

280

290

294

302

305

307

310

314

320

NC

175 184 185 271

NOTE:

*These V

cc

pins are 3.3V supplies for the Pentium processor (610\75) TCP but will be lower voltage pins on future offerings of

this microprocessor family. All other V

cc

pins will remain at 3.3V.

3.2.

Design Notes

For reliable operation, always connect unused

inputs to an appropriate signal level. Unused active

low inputs should be connected to Vcc. Unused

active HIGH inputs should be connected to GND

(Vss).

No Connect (NC) pins must remain unconnected.

Connection of NC pins may result in component

failure or incompatibility with processor steppings.

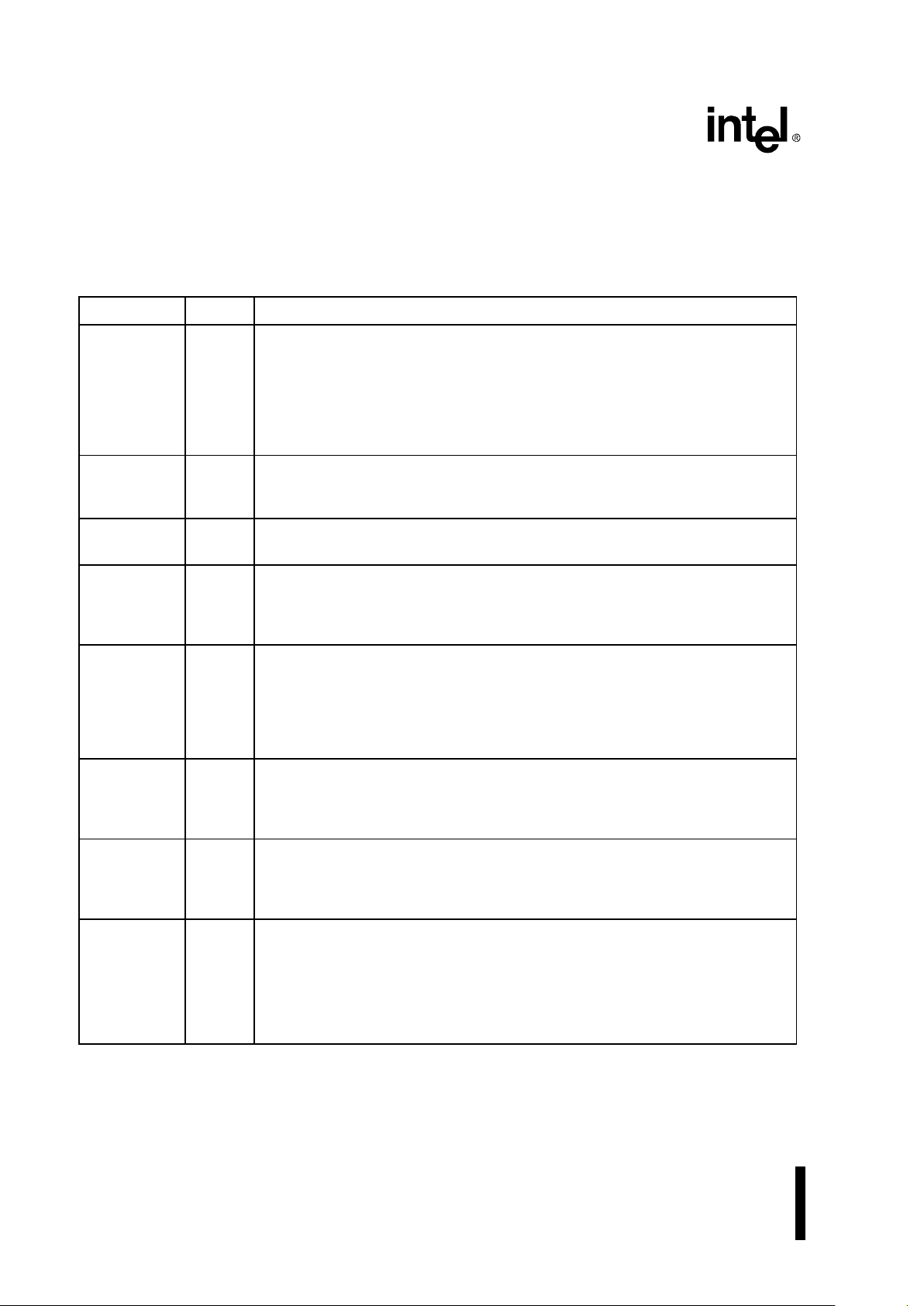

3.3.

Quick Pin Reference

This section gives a brief functional description of

each of the pins. For a detailed description, see the

"Hardware Interface" chapter in the Pentium

®

Processor Family Developer’s Manual, Volume 1.

PENTIUM® PROCESSOR (610\75)

10

Note that all input pins must meet their AC/DC

specifications to guarantee proper functional

behavior.

The # symbol at the end of a signal name indicates

that the active, or asserted state occurs when the

signal is at a low voltage. When a # symbol is not

present after the signal name, the signal is active,

or asserted at the high voltage level.

Table 3. Quick Pin Reference

Symbol Type Name and Function

A20M# I When the address bit 20 mask pin is asserted, the Pentium processor

(610\75) emulates the address wraparound at 1 Mbyte which occurs on the

8086. When A20M# is asserted, the Pentium processor (610\75) masks

physical address bit 20 (A20) before performing a lookup to the internal caches

or driving a memory cycle on the bus. The effect of A20M# is undefined in

protected mode. A20M# must be asserted only when the processor is in real

mode.

A31-A3 I/O As outputs, the address lines of the processor along with the byte enables

define the physical area of memory or I/O accessed. The external system

drives the inquire address to the processor on A31-A5.

ADS# O The address status indicates that a new valid bus cycle is currently being

driven by the Pentium processor (610\75) .

AHOLD I In response to the assertion of address hold, the Pentium processor (610\75)

will stop driving the address lines (A31-A3), and AP in the next clock. The rest

of the bus will remain active so data can be returned or driven for previously

issued bus cycles.

AP I/O Address parity is driven by the Pentium processor (610\75) with even parity

information on all Pentium processor (610\75) generated cycles in the same

clock that the address is driven. Even parity must be driven back to the

Pentium processor (610\75) during inquire cycles on this pin in the same clock

as EADS# to ensure that correct parity check status is indicated by the Pentium

processor (610\75).

APCHK# O The address parity check status pin is asserted two clocks after EADS# is

sampled active if the Pentium processor (610\75) has detected a parity error on

the address bus during inquire cycles. APCHK# will remain active for one clock

each time a parity error is detected.

[APICEN]

PICD1

I The Advanced Programmable Interrupt Controller Enable pin enables or

disables the on-chip APIC interrupt controller. If sampled high at the falling

edge of RESET, the APIC is enabled. APICEN shares a pin with the

Programmable Interrupt Controller Data 1 signal.

BE7#-BE5#

BE4#-BE0#

O

I/O

The byte enable pins are used to determine which bytes must be written to

external memory, or which bytes were requested by the CPU for the current

cycle. The byte enables are driven in the same clock as the address lines

(A31-3).

The lower four byte enables (BE3#-BE0#) are used on the Pentium processor

(610\75) as APIC ID inputs and are sampled at RESET.

PENTIUM® PROCESSOR (610\75)

11

Table 3. Quick Pin Reference (Contd.)

Symbol Type Name and Function

[BF] I Bus Frequency determines the bus-to-core frequency ratio. BF is sampled at

RESET, and cannot be changed until another non-warm ( 1 ms) assertion of

RESET. Additionally, BF must not change values while RESET is active. For

proper operation of the Pentium processor (610\75) this pin should be strapped

high or low. When BF is strapped to V

, the processor will operate at a 2/3

bus/core frequency ratio. When BF is strapped to V

, the processor will

operate at a 1/2 bus/core frequency ratio. If BF is left floating, the Pentium

processor (610\75) defaults to a 2/3 bus ratio. Note the Pentium processor

(610\75) will not operate at a 1/2 bus/core frequency ratio.

BOFF# I The backoff input is used to abort all outstanding bus cycles that have not yet

completed. In response to BOFF#, the Pentium processor (610\75) will float all

pins normally floated during bus hold in the next clock. The processor remains

in bus hold until BOFF# is negated, at which time the Pentium processor

(610\75) restarts the aborted bus cycle(s) in their entirety.

BP[3:2]

PM/BP[1:0]

O The breakpoint pins (BP3-0) correspond to the debug registers, DR3-DR0.

These pins externally indicate a breakpoint match when the debug registers are

programmed to test for breakpoint matches.

BP1 and BP0 are multiplexed with the performance monitoring pins (PM1

and PM0). The PB1 and PB0 bits in the Debug Mode Control Register

determine if the pins are configured as breakpoint or performance monitoring

pins. The pins come out of RESET configured for performance monitoring.

BRDY# I The burst ready input indicates that the external system has presented valid

data on the data pins in response to a read or that the external system has

accepted the Pentium processor (610\75) data in response to a write request.

This signal is sampled in the T2, T12 and T2P bus states.

BREQ O The bus request output indicates to the external system that the Pentium

processor (610\75) has internally generated a bus request. This signal is

always driven whether or not the Pentium processor (610\75) is driving its bus.

BUSCHK# I The bus check input allows the system to signal an unsuccessful completion

of a bus cycle. If this pin is sampled active, the Pentium processor (610\75) will

latch the address and control signals in the machine check registers. If, in

addition, the MCE bit in CR4 is set, the Pentium processor (610\75) will vector

to the machine check exception.

CACHE# O For Pentium processor (610\75)-initiated cycles the cache pin indicates internal

cacheability of the cycle (if a read), and indicates a burst writeback cycle (if a

write). If this pin is driven inactive during a read cycle, the Pentium processor

(610\75) will not cache the returned data, regardless of the state of the KEN#

pin. This pin is also used to determine the cycle length (number of transfers in

the cycle).

PENTIUM® PROCESSOR (610\75)

12

Table 3. Quick Pin Reference (Contd.)

Symbol Type Name and Function

CLK I The clock input provides the fundamental timing for the Pentium processor

(610\75). Its frequency is the operating frequency of the Pentium processor

(610\75) external bus and requires TTL levels. All external timing parameters

except TDI, TDO, TMS, TRST#, and PICD0-1 are specified with respect to the

rising edge of CLK.

D/C# O The data/code output is one of the primary bus cycle definition pins. It is driven

valid in the same clock as the ADS# signal is asserted. D/C# distinguishes

between data and code or special cycles.

D63-D0 I/O These are the 64 data lines for the processor. Lines D7-D0 define the least

significant byte of the data bus; lines D63-D56 define the most significant byte

of the data bus. When the CPU is driving the data lines, they are driven during

the T2, T12, or T2P clocks for that cycle. During reads, the CPU samples the

data bus when BRDY# is returned.

DP7-DP0 I/O These are the data parity pins for the processor. There is one for each byte of

the data bus. They are driven by the Pentium processor (610\75) with even

parity information on writes in the same clock as write data. Even parity

information must be driven back to the Pentium processor (610\75) on these

pins in the same clock as the data to ensure that the correct parity check status

is indicated by the Pentium processor (610\75). DP7 applies to D63-D56; DP0

applies to D7-D0.

[DPEN#]

PICD0

I/O Dual processing enable is an output of the Dual processor and an input of the

Primary processor. The Dual processor drives DPEN# low to the Primary

processor at RESET to indicate that the Primary processor should enable dual

processor mode. Since the dual processing feature is not supported on the

Pentium processor (610\75) TCP package, DPEN# should never be asserted

(low) at RESET. DPEN# shares a pin with PICD0.

EADS# I This signal indicates that a valid external address has been driven onto the

Pentium processor (610\75) address pins to be used for an inquire cycle.

EWBE# I The external write buffer empty input, when inactive (high), indicates that a

write cycle is pending in the external system. When the Pentium processor

(610\75) generates a write, and EWBE# is sampled inactive, the Pentium

processor (610\75) will hold off all subsequent writes to all E- or M-state lines in

the data cache until all write cycles have completed, as indicated by EWBE#

being active.

FERR# O The floating point error pin is driven active when an unmasked floating point

error occurs. FERR# is similar to the ERROR# pin on the Intel387™ math

coprocessor. FERR# is included for compatibility with systems using DOS-type

floating point error reporting.

PENTIUM® PROCESSOR (610\75)

13

Table 3. Quick Pin Reference (Contd.)

Symbol Type Name and Function

FLUSH# I When asserted, the cache flush input forces the Pentium processor (610\75)

to write back all modified lines in the data cache and invalidate its internal

caches. A Flush Acknowledge special cycle will be generated by the Pentium

processor (610\75) indicating completion of the writeback and invalidation.

If FLUSH# is sampled low when RESET transitions from high to low, tristate

test mode is entered.

HIT# O The hit indication is driven to reflect the outcome of an inquire cycle. If an

inquire cycle hits a valid line in either the Pentium processor (610\75) data or

instruction cache, this pin is asserted two clocks after EADS# is sampled

asserted. If the inquire cycle misses the Pentium processor (610\75) cache,

this pin is negated two clocks after EADS#. This pin changes its value only as a

result of an inquire cycle and retains its value between the cycles.

HITM# O The hit to a modified line output is driven to reflect the outcome of an inquire

cycle. It is asserted after inquire cycles which resulted in a hit to a modified line

in the data cache. It is used to inhibit another bus master from accessing the

data until the line is completely written back.

HLDA O The bus hold acknowledge pin goes active in response to a hold request

driven to the processor on the HOLD pin. It indicates that the Pentium

processor (610\75) has floated most of the output pins and relinquished the bus

to another local bus master. When leaving bus hold, HLDA will be driven

inactive and the Pentium processor (610\75) will resume driving the bus. If the

Pentium processor (610\75) has a bus cycle pending, it will be driven in the

same clock that HLDA is de-asserted.

HOLD I In response to the bus hold request , the Pentium processor (610\75) will float

most of its output and input/output pins and assert HLDA after completing all

outstanding bus cycles. The Pentium processor (610\75) will maintain its bus

in this state until HOLD is de-asserted. HOLD is not recognized during LOCK

cycles. The Pentium processor (610\75) will recognize HOLD during reset.

IERR# O The internal error pin is used to indicate internal parity errors. If a parity error

occurs on a read from an internal array, the Pentium processor (610\75) will

assert the IERR# pin for one clock and then shutdown.

IGNNE# I This is the ignore numeric error input. This pin has no effect when the NE bit

in CR0 is set to 1. When the CR0.NE bit is 0, and the IGNNE# pin is asserted,

the Pentium processor (610\75) will ignore any pending unmasked numeric

exception and continue executing floating-point instructions for the entire

duration that this pin is asserted. When the CR0.NE bit is 0, IGNNE# is not

asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the

floating-point instruction is one of FINIT, FCLEX, FSTENV, FSAVE, FSTSW,

FSTCW, FENI, FDISI, or FSETPM, the Pentium processor (610\75) will

execute the instruction in spite of the pending exception. When the CR0.NE bit

is 0, IGNNE# is not asserted, a pending unmasked numeric exception exists

(SW.ES = 1), and the floating-point instruction is one other than FINIT, FCLEX,

FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium

processor (610\75) will stop execution and wait for an external interrupt.

Loading...

Loading...