Page 1

Intel® Xeon™ Processor with

512 KB L2 Cache and Intel®

E7500 Chipset Platform

Design Guide

March 2002

Document Number: 298649-002

Page 2

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any

intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no

liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties

relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are

not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to the m.

The Intel® E7500 chipset and processors in the Intel® Xeon processor family may contain design defects or errors known as errata which may cause the product

to deviate from published specifi catio ns. C urr en t chara cter ized err ata are avail a ble on req ues t.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

2

I

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips

Corporation.

Alert on LAN and Alert on LAN2 are a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

Intel, Pentium, Intel Xeon, Intel Netburst and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United

States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2002, Intel Corporation

Design Guide 2

Page 3

Contents

1 Introduction................................................................................................................15

1.1 Reference Documentation .. ...... ....... ...... ...... ....... ....................................... ...... ....15

1.2 Conventions and Terminology.............................................................................17

1.3 System Overview ................................................................................................19

1.3.1 Intel® Xeon™ Processor with 512 KB L2 Cache ...............................20

1.3.2 Intel® E7500 Chipset .........................................................................21

1.3.2.1 Intel® E7500 Memory Controller Hub (MCH).......................21

1.3.2.2 I/O Controller Hub 3 (Intel

1.3.2.3 PCI/PCI-X 64-bit Hub 2 (Intel

1.3.3 Bandwidth Summary ..........................................................................23

1.3.4 System Configurations .......................................................................23

2 Component Quadrant Layout..............................................................................25

2.1 Intel® Xeon™ Processor with 512 KB L2 Cache Quadrant Layout ....................26

2.2 Intel® E7500 MCH Quadrant Layout...................................................................27

2.3 Intel

2.4 Intel

®

ICH3-S Quadrant Layout...........................................................................28

®

82870P2 P64H2 Quadrant Layout ............................................................29

3 Platform Stack-Up and Component Placement Overview.......................31

3.1 Platform Component Placement .........................................................................31

3.2 Platform Stack-Up ...............................................................................................32

®

ICH3-S).....................................22

®

82870P2 P64H2).................22

4 Platform Clock Routing Guidelines..................................................................35

4.1 Clock Groups............... ....... ...... ....... ...... ....................................... ...... ....... ...... ....38

4.1.1 HOST_CLK Clock Group ...................................................................38

4.1.1.1 HOST_CLK Clock Topology.................................................38

4.1.1.2 HOST_CLK General Routing Guidelines..............................41

4.1.1.3 CK408 vs. CK408B Requirement.........................................41

4.1.2 CLK66 Clock Group ................................ ....... ....................................42

4.1.2.1 CLK66 Skew Requirements..................................................43

4.1.3 CLK33_ICH3-S Clock.........................................................................45

4.1.4 CLK33 Clock Group ................................ ....... ....................................46

4.1.5 CLK14 Clock Group ................................ ....... ....................................48

4.1.6 USBCLK Clock Group........................................................................49

4.2 Clock Driver Decoupling.................................................. ...... ....... ...... ....... ...... ....50

4.3 Clock Driver Power Delivery................................................................................51

4.4 EMI Constraints...................................................................................................51

5 System Bus Routing Guidelines........................................................................53

5.1 Routing Guidelines for the AGTL+ Source Synchronous 2X and 4X Groups .....56

5.1.1 Trace Length Matching.......................................................................56

5.2 Routing Guidelines for Common Clock Signals ..................................................58

5.2.1 Wired-OR Signals...............................................................................58

5.2.2 RESET# Topology..............................................................................59

5.3 Routing Guidelines for Asynchronous GTL+ and Miscellaneous Signals ...........59

5.3.1 Asynchronous GTL+ Signals Driven by the Processor ......................60

5.3.1.1 Proper THERMTRIP# Usage..... ....... ...... ....... ...... ....... ...... ....61

Design Guide 3

Page 4

5.3.2 Asynchronous GTL+ Signals Driven by the Chipset ..........................61

5.3.2.1 Proper Power Good Usage ..................................................62

5.3.2.2 Voltage Translation for INIT#................................................62

5.3.3 VID[4:0] ..............................................................................................63

5.3.4 SMBus Signals...................................................................................63

5.3.5 System Bus COMP Routing Guidelines.............................................64

5.3.6 BR[3:0]# Routing Guidelines..............................................................64

5.3.7 ODTEN Signal Routing Guidelines ....................................................64

5.3.8 TESTHI[6:0] Routing Guidelines ................ ....... ...... ...........................65

5.3.9 SKTOCC# Signal Routing Guidelines................................................65

6 Memory Interface Routing Guidelines.............................................................67

6.1 DDR Overview ....................................................................................................68

6.2 Source Synchronous Signal Group.....................................................................70

6.3 Command Clock Routing ....................................................................................73

6.4 Source Clocked Signal Group Routing ...............................................................75

6.5 Chip Select Routing ............................................................................................76

6.6 Clock Enable Routing..........................................................................................77

6.7 Enable Signal (RCVEN#)....................................................................................78

6.8 Miscellaneous Signals.........................................................................................79

6.9 DDR Reference Voltage......................................................................................80

6.10 DDR Signal Termination .....................................................................................81

6.11 Decoupling Requirements...................................................................................82

7 Hub Interface..............................................................................................................83

7.1 Signal Naming Convention..................................................................................83

7.2 Hub Interface 2.0 Implementation......................... ...... ....... ...... ....... ...... ....... ...... .84

7.2.1 Hub Interface 2.0 High-Speed Routing Guidelines ............................84

7.2.2 Hub Interface 2.0 Generation/Distribution of Reference Voltages .....87

7.2.3 Hub Interface 2.0 Resistive Compensation........................................88

7.2.4 Hub Interface 2.0 Decoupling Guidelines...........................................89

7.2.5 Unused Hub Interface 2.0 Interfaces..................................................89

7.3 Hub Interface 1.5 Implementation......................... ...... ....... ...... ....... ...... ....... ...... .89

7.3.1 Hub Interface 1.5 High-Speed Routing Guidelines ............................89

7.3.2 Hub Interface 1.5 Generation/Distribution of Reference Voltages .....90

7.3.3 Hub Interface 1.5 Resistive Compensation........................................91

7.3.4 Hub Interface 1.5 Decoupling Guidelines...........................................92

8Intel

®

82870P2 (P64H2)..........................................................................................93

8.1 PCI/PCI-X Design Guidelines .............................................................................93

8.1.1 PCI/PCI-X Routing Requirements (No Hot Plug)...............................94

8.1.2 PCI/PCI-X Hot Plug Routing Requirements.......................................95

8.1.3 Clock Configuration........................................................ ...... ....... ...... .96

8.1.4 Loop Clock Configuration..................................................... ....... ...... .97

8.1.5 IDSEL Implementation .......................................................................98

8.1.6 SMBus Address..................................................................................98

8.2 Hot Plug Implementation.....................................................................................99

8.2.1 Standard Usage Model.......................................................................99

8.2.1.1 Hot-Removals.......................................................................99

8.2.1.2 Hot-Insertions .....................................................................100

8.2.2 Hot Plug Switch Implementation ......................................................100

4 Design Guide

Page 5

8.2.2.1 Manually-Operated Retention Latch Sensor.......................101

8.2.2.2 Optional Attention Button....................................................102

8.2.3 LED Indicator Outputs......................................................................102

8.2.4 Disabling/Enabling an Intel

®

P64H2 Hot Plug Controller..................103

8.2.4.1 Hot Plug Strapping Options................................................103

8.2.4.2 Hot Plug Registers’ Visibility...............................................103

8.2.5 Single Slot Parallel Mode .................................................................103

8.2.5.1 Required Additional Logic.... ...... ....... ...... ....... ...... ....... ...... ..103

8.2.5.2 PCI Clock............................. ...... ....... ...... ....... ...... ....... ........103

8.2.5.3 Debounced Hot Plug Switch Input......................................104

8.2.5.4 Comparator Circuit for PCIXCAP1/PCIXCAP2 Pins...........104

8.2.5.5 Tri-State Buffer or 2:1 MUX for HPxSLOT [2:0]..................104

8.2.5.6 Hot Plug Muxed Signals in Single Slot Parallel Mode ........105

8.2.5.7 SMBus Address Considerations.........................................106

8.2.5.8 Pull-Ups/Pull-Downs in Single Slot Parallel Mode..............106

8.2.5.9 Reference Schematic for Single-Slot Parallel Mode...........107

8.2.6 Dual Slot Parallel Mode....................................................................108

8.2.6.1 Required Additional Logic.... ...... ....... ...... ....... ...... ....... ...... ..108

8.2.6.2 Debounced Hot Plug Switch Input......................................108

8.2.6.3 Comparator Circuit for PCIXCAP1/PCIXCAP2 Pins...........108

8.2.6.4 Tri-State Buffer or 2:1 Mux for HPxSLOT [2:0]...................108

8.2.6.5 HPx_SID Output Signal ......................................................108

8.2.6.6 Pull-Ups/Pull-Downs in Dual Slot Parallel Mode.................108

8.2.6.7 Hot Plug Muxed Signals in Dual Slot Parallel Mode...........109

8.2.6.8 SMBus Address Considerations.........................................110

8.2.6.9 Reference Schematic for Dual-Slot Parallel Mode .............111

8.2.7 Three or More Slot Serial Mode .......................................................112

8.2.7.1 Hot Plug and Non-Hot Plug Combinations .........................112

8.2.7.2 Required Additional Logic.... ...... ....... ...... ....... ...... ....... ...... ..112

8.2.7.3 Debounced Hot Plug Switch Input......................................112

8.2.7.4 Comparator Circuit for PCIXCAP1/PCIXCAP2 Pins...........112

8.2.7.5 HPxSLOT [2:0]........ ...... ....... ...... ....... ...... ....... ...... ....... ...... ..112

8.2.7.6 Stutter Logic for Implementing Fewer Than Six Slots.........112

8.2.7.7 Pull-Ups/Pull-Downs in Three or More Slot Serial Mode....113

8.2.7.8 Reference Schematic for Serial Mode................................114

8.2.8 Intel

®

P64H2 PCI Interface PCIXCAP and M66EN Pins..................115

8.2.8.1 PCIXCAP Pin Requirements ..............................................115

8.2.8.2 M66EN Pin Requirements ..................................................115

9 I/O Controller Hub..................................................................................................119

9.1 IDE Interface .....................................................................................................119

9.1.1 Cabling .............................................................................................119

9.1.2 Cable Detection for Ultra ATA/66 and Ultra ATA/100 ......................120

9.1.2.1 Combination Host-Side/Device-Side Cable Detection........120

9.1.3 Primary IDE Connector Requirements .............................................121

9.1.4 Secondary IDE Connector Requirements ........................................122

9.2 SPKR Pin Consideration ...................................................................................123

9.3 PCI ....................................................................................................................123

9.4 USB...................................................................................................................124

9.4.1 General Routing and Placement ......................................................124

9.4.2 USB Trace Separation .....................................................................125

9.4.3 USB Trace Length Matching ............................................................125

Design Guide 5

Page 6

9.4.4 Plane Splits, Voids, and Cut-Outs (Anti-Etch)..................................125

9.4.4.1 VCC Plane Splits, Voids, and Cut-Outs (Anti-Etch)............125

9.4.4.2 GND Plane Splits, Voids, and Cut-Outs (Anti-Etch) ...........125

9.4.5 EMI Considerations..........................................................................125

9.4.6 USB Power Line Layout Topologies.................................................126

9.5 Intel

®

ICH3-S SMBus/SMLink Interface............................................................126

9.5.1 SMBus Design Considerations.........................................................127

9.5.2 General Design Note .. ....... ...................................... ....... ...... ....... .....127

9.5.3 The Unified VCC_CORE Architecture..............................................127

9.6 Real Time Clock (RTC).....................................................................................128

9.6.1 RTC External Circuit.........................................................................129

9.6.2 External Capacitors..........................................................................130

9.6.3 RTC Layout Considerations .............................................................131

9.6.4 RTC External Battery Connection ....................................................131

9.6.5 RTC External RTCRST# Circuit.......................................................132

9.6.6 VBIAS DC Voltage and Noise Measurements .................................132

9.6.7 SUSCLK...........................................................................................133

9.6.8 RTC-Well Input Strap Requirements................................................133

9.7 Internal LAN Layout Guidelines ........................................................................133

9.7.1 LCI (LAN Connect Interface) Guidelines..........................................135

9.7.1.1 Bus Topology............................................. ....... ...... ....... .....135

9.7.1.2 Signal Routing and Layout .................................................136

9.7.1.3 Crosstalk Consideration .....................................................136

9.7.1.4 Impedances........................................................................136

9.7.1.5 Line Termination.................................................................136

9.7.2 General LAN Routing Guidelines and Consi der ations .....................137

9.7.2.1 General Trace Routing Considerations ..............................137

9.7.2.2 Trace Geometry and Length...............................................138

9.7.2.3 Signal Isolation ...................................................................138

9.7.2.4 Power and Ground Connections ........................................138

9.7.2.5 General Power and Ground Plane Consideration ..............139

9.7.2.6 Board Design......................................................................140

9.7.2.7 Common Physical Layout Issues .......................................140

9.7.3 Intel

9.7.3.1 Guidelines for Intel

9.7.3.2 Crystals and Oscillators......................................................142

9.7.3.3 Intel

®

82562ET/EM Guidelines ........................................................142

®

82562ET/EM Termination Resistors............. ....... .....143

®

82562ET/EM Component Placement 142

9.7.4 Critical Dimensions...........................................................................143

9.7.5 Terminating Unused Connections....................................................145

10 Debug Port................................................................................................................147

10.1 Logic Analyzer Interface (LAI)...........................................................................147

10.2 Mechanical Considerations...............................................................................147

10.3 Electrical Considerations...................................................................................147

11 EMI and Mechanical Design Considerations..............................................149

11.1 Introduction .......................................................................................................149

11.1.1 Brief EMI Theory ........................... ....... ...... ....... ...... ....... ...... ....... .....149

11.1.2 EMI Regulations and Certifications..................................................150

11.2 EMI Design Considerations...............................................................................150

11.2.1 Spread Spectrum Clocking (SSC)....................................................150

6 Design Guide

Page 7

11.2.2 Differential Clocking .........................................................................151

11.2.3 PCI Bus Clock Control......................................................................152

11.2.4 Heatsink Effects ...............................................................................153

11.2.5 EMI Ground Frames and Faraday Cages ........................................153

11.2.6 EMI Test Capabilities .......................................................................154

11.3 Retention Mechanism Placement and Keep-Outs ............................................155

11.3.1 Grounding Techniques.....................................................................157

12 Platform Power Delivery Guidelines..............................................................159

12.1 Customer Reference Board Power Delivery .....................................................159

12.1.1 Processor Core Voltage ...................................................................161

12.1.2 2.5 V.................................................................................................161

12.1.3 1.25 V...............................................................................................161

12.1.4 1.8 V.................................................................................................161

12.1.5 1.2 V.................................................................................................161

12.1.6 5 VSB ...............................................................................................161

12.1.7 3.3 VSB ............................................................................................162

12.1.8 1.8 VSB ............................................................................................162

12.1.9 Power Summary...............................................................................162

12.2 Processor Power Distribution Guidelines..........................................................162

12.2.1 Processor Power Requirements.......................................................162

12.2.1.1 Multiple Voltages ................................................................162

12.2.1.2 Voltage Tolerance...............................................................163

12.2.2 Processor Current Requirements.....................................................163

12.2.3 Power Delivery Layout Requirements..............................................163

12.2.4 Voltage Regulator Requirements .....................................................164

12.2.4.1 Input Voltages and Currents...............................................165

12.2.4.2 Power Good Output (PWRGD)...........................................165

12.2.4.3 Fault Protection...................................................................166

12.2.5 VR Module 9.1 Recommendations...................................................166

12.2.6 VR Down Recommendations ...........................................................167

12.2.7 Voltage Sequencing .........................................................................169

12.2.8 VCCA, VCCIOPLL, and VSSA Filter Specifications.........................171

12.2.9 Processor Decoupling ......................................................................173

12.2.9.1 High-Frequency Decoupling ...............................................173

12.2.9.2 Bulk Decoupling..................................................................175

12.2.10 GTLREF[3:0] ....................................................................................175

12.2.11 Component Models .............................................. ....... ...... ....... ........177

12.2.12 Measuring Transients.......................................................................177

12.3 MCH Power Delivery Guidelines.......................................................................177

12.3.1 DDR_VTT (1.25 V) Decoupling ........................................................177

12.3.2 VCC_CPU (1.45 V Power Plane).....................................................177

12.3.3 DDR (2.5 V Power Plane) ................................................................178

12.3.4 Hub Interface (1.2 V Power Plane)...................................................178

12.3.5 Filter Specifications (1.2V Power Plane)..........................................179

12.3.6 MCH Power Sequencing Requirement ............................................180

12.4 Intel

®

ICH3-S Power Delivery Guidelines .........................................................181

12.4.1 1.8 V/3.3 V Power Sequencing ........................................................181

12.4.2 3.3V/V5REF Sequencing .................................................................182

12.4.3 Intel

12.4.4 Intel

®

ICH3-S Power Rails................................................................183

®

ICH3-S Decoupling Recommendations..................................183

Design Guide 7

Page 8

12.5 Intel® P64H2 Power Requirements..................................................................185

12.5.1 Intel® P64H2 Current Requirements ...............................................185

12.5.2 Intel® P64H2 Decoupling Requirements .........................................185

12.5.3 PCIRST# Implementation.................................................................186

12.5.4 P64H2 Power Sequencing Requirement..........................................186

13 Schematic Checklist.............................................................................................187

13.1 Processor Schematic Checklist...................... ....... ...... ....... ...... .........................187

13.2 MCH Schematic Checklist.................................................................................193

13.3 Intel

13.4 Intel

13.5 CK408 Schematic Checklist..............................................................................209

®

ICH3-S Schematic Checklist...................................................................196

®

82870P2 P64H2 Schematic Checklist.....................................................204

14 Layout Checklist.....................................................................................................211

14.1 Processor Checklist ........................................................... ...... ....... ...... ....... .....211

14.2 Intel® E7500 MCH Layout Checklist.................................................................213

14.3 Intel® ICH3-S Layout Checklist.........................................................................216

15 Schematics ...............................................................................................................221

8 Design Guide

Page 9

Figures

1-1 Example Intel® Xeon™ Processor with 512 KB L2 Cache / Intel® E7500 Chipset

Based System Configuration23

2-1 Intel® Xeon™ Processor with 512 KB L2 Cache Quadrant Layout (Top View)..26

2-2 Intel

2-3 Intel

2-4 Intel

®

E7500 MCH Quadrant Layout (Top View).................................................27

®

ICH3-S Quadrant Layout (Top View) ........................................................28

®

P64H2 Quadrant Layout (Top View) .........................................................29

3-1 Intel® E7500 Chipset Customer Reference Board System Placement Example32

3-2 8 Layer, 50 Ω Board with 5 mil Traces................................................................33

4-1 Intel® E7500 Chipset-Based System Clocking Diagram.....................................37

4-2 Source Shunt Termination...................................................................................38

4-3 Clock Skew As Measured from Agent to Agent ..................................................40

4-4 Trace Spacing for HOST_CLK Clocks................................................................40

4-5 Stuffing Options for CK408 and CK408B ............................................................41

4-6 Topology for CLK66 ............................................................................................42

4-7 Clock Skew Requirements....................................... ....... ...... ....... ...... ....... ...... ....43

4-8 Example of Adding a Single Connector...............................................................44

4-9 Example of Adding Two Connectors and/or a Riser ...........................................44

4-10 Topology for CLK33_ICH3-S...............................................................................45

4-11 Topology for CLK33 to PCI Device Down ...........................................................46

4-12 Topology for CLK33 to PCI Slot ..........................................................................47

4-13 Topology for CLK14 ............................................................................................48

4-14 Topology for USB_CLK.......................................................................................49

4-15 Decoupling Capacitors Placement and Connectivity ..........................................50

5-1 Dual Processor System Bus Topology .. ...... ....... ...... ....... ...... ....... .......................5 4

5-2 Trace Length Matching for the Dual Processor System Bus...............................57

5-3 RESET# Topology...............................................................................................59

5-4 Topology for Asynchronous GTL+ Signals Driven by the Processor ..................60

5-5 Recommended THERMTRIP# Circuit.................................................................61

5-6 Topology for Asynchronous GTL+ Signals Driven by the Chipset ......................61

5-7 Topology for PWRGOOD (CPUPWRGOOD)......................................................62

5-8 INIT# Routing Topology ......................................................................................62

5-9 Voltage Translator Circuit....................................................................................63

5-10 BR[3:0]# Connection for DP Configuration..........................................................64

6-1 4 DIMM per Channel Implementation..................................................................68

6-2 3 DIMM per Channel Implementation..................................................................68

6-3 Trace Width and Spacing for All DDR Signals Except CMDCLK/CMDCLK#......69

6-4 Source Synchronous Topology...........................................................................71

6-5 Trace Length Matching Requirements for Source Synchronous Routing...........72

6-6 DQS To CMDCLK Pair Length Matching ............................................................72

6-7 Command Clock Topology..................................................................................73

6-8 Trace Width/Spacing for CMDCLK/CMDCLK# Routing......................................74

6-9 Length Matching Requirements for Source Clocked Signal, CKE, and CS[7:0]#74

6-10 Source Clocked Signal Topology........................................................................75

6-11 Chip Select Topology............................................... ....... ...... ....... ...... .................76

6-12 CKE Topology.................................................... ...... ....... ...... ....... ...... ....... ..........77

6-13 Receive Enable Signal Routing Guidelines.........................................................78

6-14 DDRCOMP Resistive Compensation.............................................................. ....79

6-15 DDRCVOL and DDRCVOH Resistive Compensation........................ ....... ...... ....79

Design Guide 9

Page 10

6-16 DDR VREF Voltage Regulator............................................................................80

6-17 DDR VREF Voltage Divider ................................................................................80

6-18 DDR VTerm Plane ..............................................................................................81

6-19 DIMM Decoupling................................................................................................82

7-1 Signal Naming Convention on Both Sides of the Hub Interfaces........................83

7-2 Hub Interface 2.0 Length matching.... ...... ....................................... ...... ....... ...... .86

7-3 Hub Interface 2.0 Routing Guidelines for Device Down Solutions......................86

7-4 Hub Interface 2.0 Routing Guidelines for Hub Interface Connector Solutions....87

7-5 Hub Interface 2.0 with Locally Generated Voltage Divider Circuit ......................88

7-6 Hub Interface 2.0 RCOMP Circuits.......................................... ...........................88

7-7 8-Bit Hub Interface 1.5 Routing...........................................................................89

7-8 Hub Interface 1.5 Locally Generated Reference Divider Circuits........................91

7-9 Hub Interface 1.5 RCOMP Circuits.......................................... ...........................91

8-1 Typical PCI/PCI-X Routing..................................................................................94

8-2 Typical Hot Plug Routing.....................................................................................95

8-3 Hot Plug Clock Configuration..............................................................................96

8-4 No Hot Plug Clock Configuration ........................................................................96

8-5 Loop Clock Configuration....................................................................................97

8-6 IDSEL Sample Implementation Circuit................................................................98

8-7 Manually-Operated Retention Latch Sensor.....................................................101

8-8 Attention Button Implementation.......................................................................102

8-9 Tri-State Buffer Circuit Example........................................................................104

8-10 MUX Circuit Example........................................................................................105

8-11 Single Slot Parallel SMBus Circuit ....................................................................106

8-12 Reference Schematic for Single-Slot Parallel Mode .........................................107

8-13 Dual Slot Parallel SMBus Circuit.......................................................................110

8-14 Reference Schematic for Dual-Slot Parallel Mode............................................111

8-15 Four Slot Stutter Logic Implementation Example..............................................113

8-16 Reference Schematic for Serial Mode ..............................................................114

8-17 M66EN Isolation Switch Solution ......................................................................116

8-18 M66EN Diode Solution......................................................................................117

9-1 Combination Host-Side/Device-Side IDE Cable Detection ...............................120

9-2 Connection Requirements for Primary IDE Connector .....................................121

9-3 Connection Requirements for Secondary IDE Connector.................................122

9-4 Example Speaker Circuit.......................... ...... ....... ...... ....... ...... ....... ...... ....... .....123

9-5 PCI Bus Layout Example..................................................................................124

9-6 Suggested USB Downstream Power Connection.............................................126

9-7 Intel® ICH3-S SMBus / SMLink Interface .........................................................127

9-8 Unified VCC_3.3 Architecture ...........................................................................128

9-9 RTCX1 and SUSCLK Relationship ...................................................................128

9-10 RTC External Circuitry ......................................................................................129

9-11 RTC Connection When Not Using Internal RTC...............................................129

9-12 A Diode Circuit to Connect RTC External Battery.............................................131

9-13 RTCRST# External Circuit................................................................................132

9-14 Platform LAN Connect .....................................................................................134

9-15 Point-to-Point Interconnect Guideline ...............................................................135

9-16 LAN_CLK Routing Example..............................................................................136

9-17 Routing a 90 Degree Bend................................................................................137

9-18 Ground Plane Separation..................................................................................139

9-19 Intel

®

82562ET/EM Termination .......................................................................143

10 Design Guide

Page 11

9-20 Critical Dimensions for Component Placement.................................................143

9-21 Termination Plane.............................................................................................145

11-1 Spread Spectrum Modulation Profile.................................................................151

11-2 Impact of Spread Spectrum Clocking on Radiated Emissions..........................151

11-3 Cancellation of H-fields Through Inverse Currents ...........................................152

11-4 Conceptu al Proc esso r Ground Fram e............................. ..................................154

11-5 Retention Mechanism Outline and Ground Pad Detail......................................155

11-6 Retention Mechanism Placement and Keep-Out Overview ..............................156

11-7 EMI Ground Size and Location .........................................................................157

11-8 Retention Mechanism Ground Ring..................................................................158

12-1 Power Delivery Example ...................................................................................160

12-2 Power Distribution Block Diagrams for Two-Way System Motherboard ...........165

12-3 VRM VID Routing..............................................................................................167

12-4 Simplified VRD Circuit Example........................................................................167

12-5 Example Load Line Selection Circuit.................................................................168

12-6 VID Routing.......................................................................................................169

12-7 Power-Up and Power-Down Timing................................................... ...............170

12-8 Processor Filter Topology .................................................................................171

12-9 Filter Implementation 1: Using Discrete Resistor ..............................................172

12-10 Filter Implementation 2: No Discrete Resistor...................................................172

12-11 Decoupling Example for a Microstrip Baseboard Design..................................174

12-12 1206 Capacitor Pad and Via Layouts................................................................174

12-13 GTLREF Divider................................................................................................175

12-14 Suggested GTLREF Generation ..... ...... ...... ....... ...... ....... ...... ....... ...... ....... ...... ..176

12-15 MCH Decoupling (Backside View) ....................................................................178

12-16 Filter Topology for VCCA_1.2 (DDR Interface).................................................179

12-17 Filter Topology for VCCAHI_1.2 (HUB Interface)..............................................179

12-18 Filter Topology for VCCAHI_1.2 (System Bus).................................................180

12-19 Power Sequencing Requirement for MCH ........................................................180

12-20 Sample 2.5 V Output Enable Control Logic.......................................................181

12-21 Example 1.8 V/3.3 V Power Sequencing Circuit ...............................................182

12-22 Example 3.3 V/V5REF Sequencing Circuitry ....................................................183

12-23 3.3V PCI/PCI-X (VCC_3.3) Capacitor Placement.............................................186

Design Guide 11

Page 12

Tables

1-1 Reference Documents ........................................................................................15

1-2 Intel® Xeon™ Processor with 512 KB L2 Cache Feature Set Overview............20

1-3 Platform Maximum Bandwidth Summary............................................................23

3-1 Assumptions for System Placement Example ....................................................31

3-2 E7500 Chipset Customer Reference Board Requirements ................................33

4-1 CK408B Clock Groups........................................................................................35

4-2 Platform System Clock-Reference......................................................................36

4-3 HOST_CLK[1:0]# Routing Guidelines.................................................................39

4-4 CLK66 Routing Guidelines..................................................................................42

4-5 CLK33_ICH3-S Routing Guidelines................................................ ...... ..............45

4-6 CLK33 Routing Guidelines for PCI Device Down ...............................................46

4-7 CLK33 Routing Guidelines for PCI Slot ..............................................................47

4-8 CLK14 Routing Guidelines..................................................................................48

4-9 USBCLK Routing Guidelines ..............................................................................49

5-1 System Bus Signal Groups .................................................................................53

5-2 System Bus Routing Summary ...........................................................................55

5-3 2X and 4X Signal Groups............................... ....................................... ....... ...... .56

5-4 Source Synchronous Signals with the Associated Strobes.................................56

5-5 AGTL+ Common Clock I/O Signals.....................................................................58

5-6 Asynchronous GTL+ and Miscellaneous Signals................................................59

5-7 BR[3:0]# Connection...........................................................................................64

6-1 DDR Channel Signal Groups ..............................................................................67

6-2 DQ/CB to DQS Mapping .....................................................................................70

6-3 Source Synchronous Signal Group Routing Guidelines .....................................71

6-4 Command Clock Pair Routing Guidelines...........................................................73

6-5 Source Clocked Signal Group Routing Guidelines .............................................75

6-6 Chip Select Routing Guidelines ..........................................................................76

6-7 Clock Enable Routing Guidelines........................................................................77

7-1 Hub Interface 2.0 Signal/Strobe Association......... ...... ....... ...... ....... ...... ..............84

7-2 Hub Interface 2.0 Signal Groups........................... ...... ....... ...... ...........................84

7-3 Hub Interface 2.0 Routing Parameters........................ ....... ...... ....... ...... ....... ...... .84

7-4 Hub Interface 2.0 Reference Circuit Specifications.............................................87

7-5 Hub Interface 2.0 RCOMP Resistor Values........................................................88

7-6 Hub Interface 1.5 Signal Groups........................... ...... ....... ...... ...........................90

7-7 Hub Interface 1.5 Routing Parameters........................ ....... ...... ....... ...... ....... ...... .90

7-8 Hub Interface 1.5 Reference Circuit Specifications.............................................90

7-9 Hub Interface 1.5 RCOMP Resistor Values........................................................91

8-1 PCI/PCI-X Frequencies.......................................................................................93

8-2 Intel® P64H2 PCI/PCI-X Configuration Length Requirements ...........................94

8-3 Intel® P64H2 Hot Plug Configuration Length Requirements ..............................95

8-4 Hot Plug Clock Routing Length Parameters .......................................................96

8-5 No Hot Plug Clock Routing Length Parameters..................................................96

8-6 Loop Clock Configuration Routing Length Parameters.......................................97

8-7 SMBus Address Configuration............................................................................98

8-8 Hot Plug Mode ..................................................................................................103

8-9 Frequency Matrix ..............................................................................................104

8-10 Single Slot Parallel Mode Hot Plug Signal Table ..............................................105

8-11 Hot Plug Controller Output Signal Reset Values...............................................106

12 Design Guide

Page 13

8-12 Dual Slot Parallel Mode Hot Plug Signals Table ...............................................109

8-13 Shift Register Input Data ...................................................................................113

9-1 LAN Design Guide Section Reference..............................................................134

12-1 Power Summary................................................................................................162

12-2 Processor Current Step Parameters .................................................................163

12-3 Component Recommendation—Inductor..........................................................171

12-4 Component Recommendation—Capacitor........................................................171

12-5 Processor High-Frequency Capacitance Recommendations............................173

12-6 Processor Bulk Capacitance Recommendations ..............................................175

12-7 Various Component Models Used at Intel (Not Vendor Specifications)............177

12-8 ICH3-S Power Rail Terminology .......................................................................183

12-9 Intel

®

ICH3-S Decoupling Recommendations...................................................184

12-10 Intel® P64H2 Max Sustained Currents .............................................................185

12-11 Decoupling Capacitor Recommendations.........................................................185

13-1 Processor Schematic Checklist.........................................................................187

13-2 MCH Schematic Checklist.................................................................................193

13-3 Intel

13-4 Intel

®

ICH3-S Schematic Checklist ...................................................................196

®

P64H2 Schematic Checklist........................... ....... ...... ....... ...... ....... ...... ..204

13-5 CK408 Schematic Checklist..............................................................................209

14-1 Processor Layout Checklist...............................................................................211

14-2 MCH Layout Checklist.......................................................................................213

14-3 Intel® ICH3-S Layout Checklist.........................................................................216

Design Guide 13

Page 14

Revision History

Revision Description Date

-001 Initial Release. February 2002

Changed: Section 6.3; DDR Command Clock Figure Notes

-002

Added: Section 12.5.4; New P64H2 Power Sequencing

Requirement

Updated Schematics to reflect changes identified above.

March 2002

14 Design Guide

Page 15

Introduction

Introduction 1

The Intel® Xeon™ Processor with 512 KB L2 Cache and Intel® E7500 Chipset Platform Design

Guide documents In tel’s design recommendations fo r systems based on the Intel

Processor with 512 KB L2 Cache and the E7500 chipset. In addition to providing motherboard

design recommendations such as layout and routing guidelines, this document addresses system

design issues such as power delivery.

Carefully follow the design information, board schematics, debug recommendations, and system

checklists provided in this document. These design guidelines have been developed to ensure

maximum flexibility for board designers while reducing the risk of board related issues.

Note that the guidelines recommended in this document are based on experience and simulation

work done at Intel while developing Intel Xeon processor with 512 KB L2 cache / E7500 chipsetbased systems. This work is ongoing, and the recommendations are subject to change.

Board designers may use the associated I ntel schematics as a referen ce. While the schematics cover

a specific design implementation, the core schematics remain the same for most E7500 chipsetbased platforms. The schematic set provides a reference schematic for each E7500 chipset

component as well as common motherboard options. Additional flexibility is possible through

other permutations of these options and components.

1.1 Reference Documentation

Note: For the latest revision and documentation number, contact your appropriate field representative.

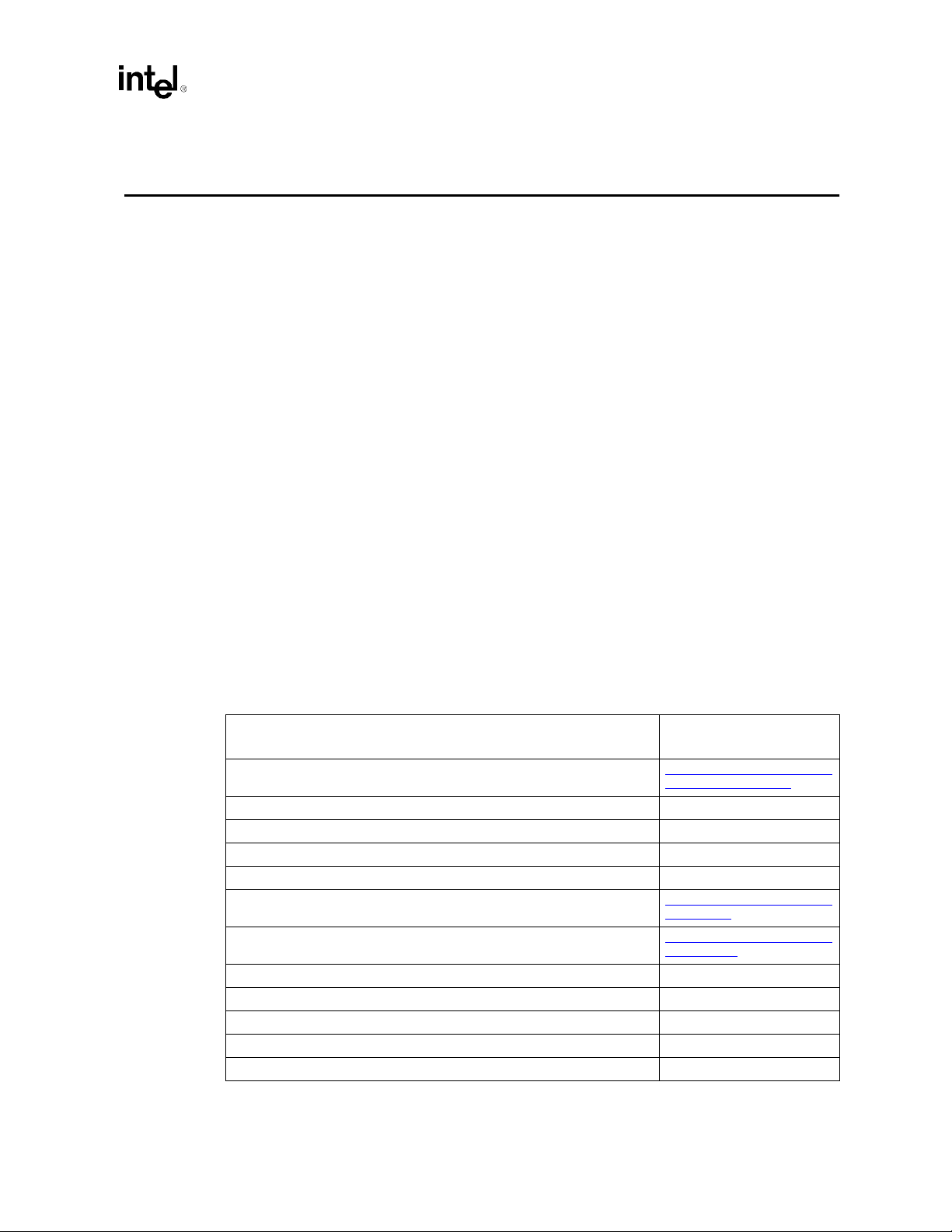

T able 1-1. Reference Documents

®

Xeon™

Document

603-Pin Socket Design Guidelines

82562ET 10/100 Mbps Platform LAN Connect (PLC) Product Datasheet

APIC External Design Specification

AT Attachment - 6 with packet Interface (ATA/ATAPI - 6)

CK-408B Clock Synthesizer/Driver Specification Revision 1.1

ITP700 Debug Port Design Guide

Intel® Xeon™ Processor with 512 KB L2 Cache Signal Integrity Models

Intel® 82801CA I/O Controller Hub 3 (ICH3-S) Datasheet 290733

®

Intel

PCI-64 Hub 2 (P64H2) Thermal and Mechanical Design Guidelines 298648

®

Intel

E7500 Chipset Thermal and Mechanical Design Guidelines 298647

®

Intel

PCI-64 Hub 2 (P64H2) Datasheet 290732

®

Intel

E7500 Chipset Memory Controller Hub (MCH) Datasheet 290730

Design Guide 15

http://developer.intel.com/design/

Xeon/guides/249672.htm

http://developer.intel.com/design/

Xeon/guides/

http://developer.intel.com/design/

Xeon/devtools

Document

Number/Source

Page 16

Introduction

Table 1-1. Reference Documents

Document

http://www.pcisig.com/

PCI Bus Power Management Interface Specification, Revision 1.1

PCI Hot Plug Specification, Revision 1.1

PCI Local Bus Specification, Revision 2.2

PCI-PCI Bridge Architecture Specification, Revision 1.1

PCI Standard Hot-Plug Controller and Subsystem Specification, Revision 1.0

PCI-X Specification, Revision 1.0a

System Management Bus Specification (SMBus), Revision 1.1 http://www.smbus.org/specs/

Universal Serial Bus Specification, Revision 1.1

VRM 9.1 DC-DC Converter Design Guidelines

Intel® Xeon™ Processor Voltage Regulator Down (VRD) Design Guidelines

Intel® Xeon™ Processor with 512 KB L2 Cache System Compatibility

Guidelines

Intel® Xeon™ Processor Thermal Design Guidelines

Intel® Xeon™ Processor Thermal Solution Functional Specifications

Intel® Xeon™ Processor with 512 KB L2 Cache Thermal Models

Intel® Xeon™ Processor with 512 KB L2 Cache Mechanical Model in IGES

Format

Intel® Xeon™ Processor with 512 KB L2 Cache Mechanical Model in ProE*

Format

Intel® Xeon™ Processor with 512 KB L2 Cache at 1.80 GHz, 2 GHz, and

2.20 GHz Datasheet

AP-728 Intel® ICH Family Real Time Clock (RTC) Accuracy and

Considerations Under Test Conditions

specifications/

pci_bus_power_management_int

erface

http://www.pcisig.com/

specifications/pci_hot_plug

http://www.pcisig.com/

specifications/conventional_pci

http://www.pcisig.com/

specifications/

pci_to_pci_bridge_architecture

http://www.pcisig.com/

specifications/pci_hot_plug

http://www.pcisig.com/

specifications/pci_x

http://www.usb.org/developers/

docs.html

http://developer.intel.com/design/

Xeon/guides/

http://developer.intel.com/design/

Xeon/guides/

http://developer.intel.com/design/

Xeon/guides/

http://developer.intel.com/design/

Xeon/guides/298348.ht m

http://developer.intel.com/design/

Xeon/applnots/249673.htm

http://developer.intel.com/design/

Xeon/devtools/

http://developer.intel.com/design/

Xeon/devtools/

http://developer.intel.com/design/

Xeon/devtools/

http://developer.intel.com/design/

Xeon/datashts/298642.htm

http://developer.intel.com/design/

chipsets/applnots/292276.htm

Document

Number/Source

16 Design Guide

Page 17

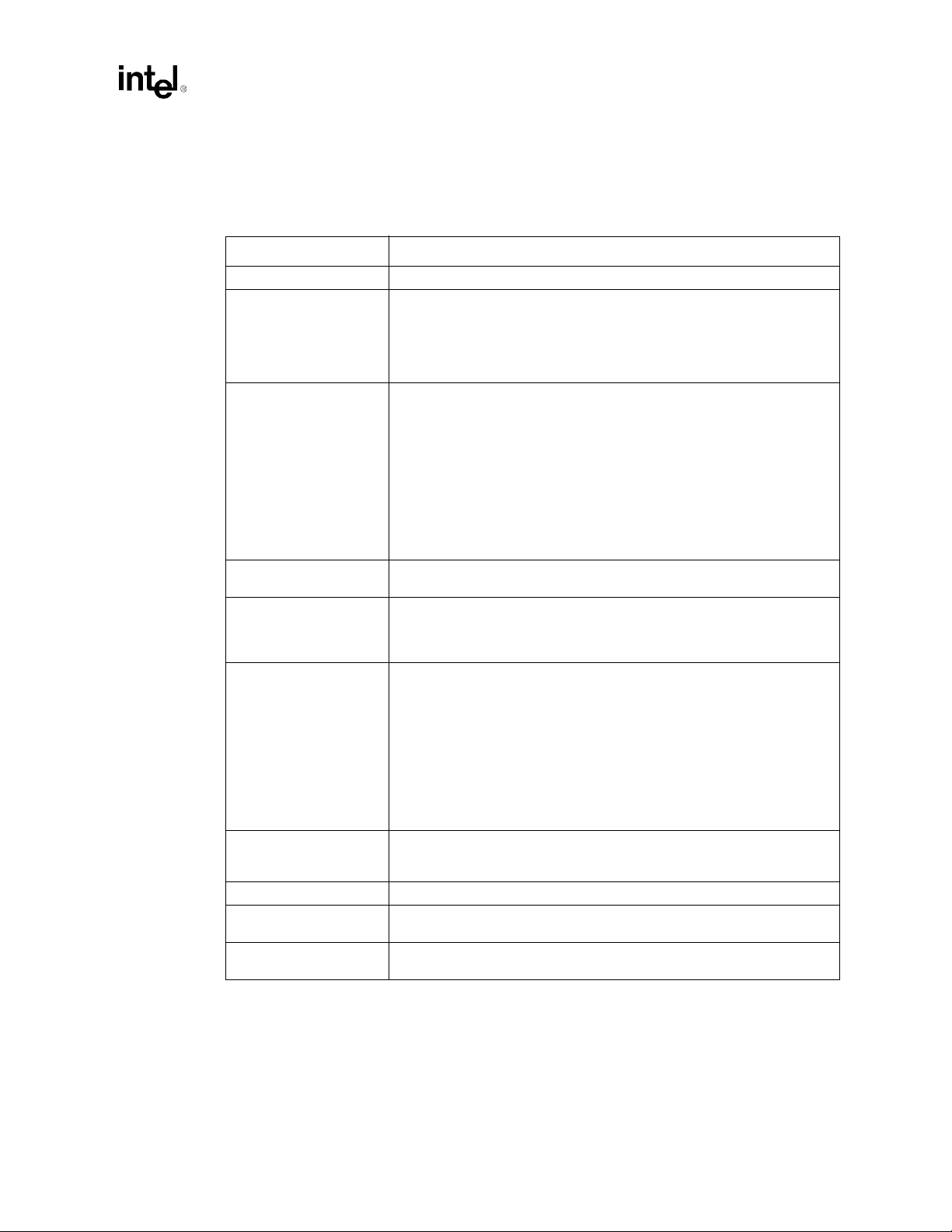

1.2 Conventions and Terminology

This section defines conventions and terminology used throughout the design guide.

Convention/Terminology Description

Aggressor A network that transmits a coupled signal to another network.

AGTL+ The Xeon™ processor family system bus uses a bus technology called AGTL+,

Asynchronous GTL+ Xeon processors do not utilize CMOS voltage levels on any signals that connect

Bus Agent A component or group of components that, when combined, represent a single

Core Power Core power refers to a power rail that is on only during full-power operation.

Crosstalk The reception on a victim network of a signal imposed by aggressor network(s)

Derived power A derived power rail is any power rail that is generated from another power rail

Dual Processor (DP) Used to specify a system configuration using two processors.

Electromagnetic

Compatibility (EMC)

Electromagnetic

Interference (EMI)

or Assisted Gunning Transceiver Logic. AGTL+ buffers are open-drain, and

require pull-up resistors to provide the high logic level and termination. AGTL+

output buffers differ from GTL+ buffers with the addition of an active pMOS pullup transistor to assist the pull-up resistors during the first clock of a low-to-high

voltage transition.

to the processor. As a result, legacy input signals such as A20M#, IGNNE#,

INIT#, LINT0/INTR, LINT1/NMI, PWRGOOD, SMI#, SLP#, and STPCLK# utilize

GTL+ input buffers. Legacy output signals (FERR# and IERR#) and non-AGTL+

signals (THERMTRIP# and PROCHOT#) also utilize GTL+ output buffers. All of

these signals follow the same DC requirements as AGTL+ signals, however the

outputs are not actively driven high (during a logical 0 to 1 transition) by the

processor (the major difference between GTL+ and AGTL+). These signals do

not have setup or hold time specifications in relation to BCLK[1:0], and are

therefore referred to as “Asynchronous GTL+ Signals”. However, all of the

Asynchronous GTL+ signals are required to be asserted for at least two BCLKs

in order for the processor to recognize them.

load on the AGTL+ bus.

These power rails are on when the active-low PSON signal is asserted to the

power supply. The core power rails that are distributed directly from the power

supply are: +12 V, +5 V, and +3.3 V.

through inductive and capacitive coupling between the networks.

• Backward Crosstalk – Coupling that creates a signal in a victim network that

travels in the opposite direction as the aggressor’s signal.

• Forward Crosstalk – Coupling that creates a signal in a victim network that

travels in the same direction as the aggressor’s signal.

• Even Mode Crosstalk – Coupling from a signal or multiple aggressors when

all the aggressors switch in the same direction that the victim is switching.

• Odd Mode Crosstalk – Coupling from a signal or multiple aggressors when

all the aggressors switch in the opposite direction that the victim is switching.

using an on-board voltage regulator. For example, +2.5 V is derived from a +5 V

power rail using a voltage regulator.

The successful operation of electronic equipment in its intended electromagnetic

environment.

Electromagnetic radiation from an electrical source that interrupts the normal

function of an electronic device.

Introduction

Design Guide 17

Page 18

Introduction

Convention/Terminology Description

Flight Time Flight time is a term in the timing equation that includes the signal propagation

Full-power During full-power operation, all components on the motherboard remain

GTLREF Reference voltage for AGTL+ input pins.

Inter-Symbol

Interference (ISI)

Network The network is the trace of a Printed Circuit Board (PCB) that completes an

Overshoot The maximum voltage observed for a signal at the device pad, measured with

Pad The electrical contact point of a semiconductor die to the package substrate. A

Pin The contact point of a component package to the traces on a substrate, such as

Power-Good “Power-Good,” “PWRGOOD,” or “CPUPWRGOOD” (an active high signal)

Power Rails A power supply has five power rails: +12 V, –12 V, +5 V, +3.3 V, and +5 VSB. In

Ringback The voltage to which a signal changes after reaching its maximum absolute

System Bus The System Bus is the bus which connects the processor to the platform.

Setup Window The time between the beginning of Setup to Clock (TSU_MIN) and the arrival of

delay, any effects the system has on the Tco of the driver, plus any adjustments

to the signal at the receiver needed to guarantee the setup time of the receiver.

More precisely, flight time is defined as:

• The time difference between a signal at the input pin of a receiving agent

crossing the switching voltage (adjusted to meet the receiver manufacturer’s

conditions required for AC timing specifications; i.e., ringback, etc.) and the

output pin of the driving agent crossing the switching voltage when the driver

is driving a test load used to specify the driver’s AC timings.

• Maximum and Minimum Flight Time – Flight time variations are caused by

many different parameters. The more obvious causes include variation of

the board dielectric constant, changes in load condition, crosstalk, power

noise, variation in termination resistance, and differences in I/O buffer

performance as a function of temperature, voltage, and manufacturing

process. Some less obvious causes include effects of Simultaneous

Switching Output (SSO) and packaging effects.

• Maximum flight time is the largest acceptable flight time that a network

experiences under all conditions.

• Minimum flight time is the smallest acceptable flight time that a network

experiences under all conditions.

powered. Note that full-power operation includes both the full-on operating state,

and the S1 (processor stop-grant) state.

The effect of a previous signal (or transition) on the interconnect delay. For

example, when a signal is transmitted down a line, and the reflections due to the

transition have not completely dissipated, the following data transition launched

onto the bus is affected. ISI is dependent upon frequency, time delay of the line,

and the reflection coefficient at the driver and receiver. ISI can impact both timing

and signal integrity.

electrical connection between two or more components.

respect to VCC.

pad is only observable in simulations.

the motherboard. Signal quality and timings can be measured at the pin.

indicates that all of the system power supplies and clocks are stable.

PWRGOOD should go active a predetermined time after system voltages are

stable and should go inactive as soon as any of these voltages fail their

specifications.

addition to these power rails from the power supply, several other power rails are

created by voltage regulators on the Reference Board.

value. Ringback may be caused by reflections, driver oscillations, or other

transmission line phenomena.

a valid clock edge. This window may be different for each type of bus agent in

the system.

18 Design Guide

Page 19

Convention/Terminology Description

Introduction

Simultaneous Switching

Output (SSO)

Standby Power Rail Standby power is supplied by the power supply during times when the system is

Stub The branch from the bus trunk terminating at the pad of an agent.

Trunk The main connection, excluding interconnect branches, from one end agent pad

Undershoot The minimum voltage extending below VSS observed for a signal at the device

VCC_CPU VCC_CPU is the core power for the processor. The system bus is terminated to

Victim A network that receives a coupled crosstalk signal from another network is called

VRM 9.1 “VRM 9.1” refers to the Voltage Regulator Module specification for the Xeon

Effects which are differences in electrical timing parameters and degradation in

signal quality caused by multiple signal outputs simultaneously switching voltage

levels in the opposite direction from a single signal or in the same direction.

These are called odd mode and even mode switching, respectively. This

simultaneous switching of multiple outputs creates higher current swings that

may cause additional propagation delay (“push-out”) or a decrease in

propagation delay (“pull-in”). These SSO effects may impact the setup and/or

hold times and are not always taken into account by simulations. System timing

budgets should include margin for SSO effects.

powered down. The purpose is to maintain functions that always need to be

enabled, such as the date and time-of-day within the BIOS. The power supply

provides a +5 VSB power rail.

to the other end agent pad.

pad.

VCC_CPU.

the victim network.

processor. It is a DC-DC converter module that supplies the required voltage and

current to a single processor.

1.3 System Overview

The E7500 chipset is Intel’s first generation server chipset designed for use with the Xeon

processor. The architecture of the chipset provides the performance and feature-set required for

dual-processor based severs in the entry- level and mid-range, front -end and g eneral-purp ose server

market segments. A new chipset component interconnect, the Hub Interface 2.0 (HI2.0), is

designed into the E7500 chipset to provide more efficient communication between chipset

components for high-speed I/O . Each HI2.0 prov ides 1.066 GB/s I/O bandwidt h. The E7500 MC H

has three HI2.0 connectio ns , d eliv eri ng 3.2 G B /s b andw id th fo r h i gh- sp eed I /O, which can be used

for PCI/PCI-X bridges. The system bus, used to connect the processor with the E7500 chipset,

utilizes a 400 MHz transfer rate for data transfers, delivering 3.2 GB/s. The E7500 chipset

architecture supports a 144-bit wide, 200 MHz DDR memory interface also capable of transferring

data at 3.2 GB/s.

In addition to these performance features, E7500 chipset-based platforms also provide the RASUM

(Reliability, Availability, Serviceability, Usability, and Manageability) features required for entrylevel and mid-range servers. These features include: Chipkill* technology ECC for memory, ECC

for all high-performance I/O, out-of-band manageability through SMBus target interfaces on all

major components, memory scrubbing and auto-initialization, processor thermal monito ring, and

hot-plug PCI. For a complete list of the features on this platform, refer to the component datasheets

listed in Section 1.1.

Design Guide 19

Page 20

Introduction

1.3.1 Intel® Xeon™ Processor with 512 KB L2 Cache

The Intel Xeon processor with 512 KB L2 cache is the second generation of microprocessors

targeted for severs and workstations using the Intel

processor delivers performance levels that are sign ificantly hig her th an previou s g eneratio ns of IA32 processors. The E7500 chipset supports all speeds of the Intel Xeon processor with 512 KB L2

cache.

Table 1-2. Intel

L2 Cache 512 KB

Data Bus Transfer Rate 3.2 GB/s

Multi-Processor Support 1–2 CPUs

Manageability Features

Package 603-pin micro-PGA

Operating Voltage 1.50 V

Unless otherwise noted, the term “processor” refers to the Xeon processor.

The Xeon processor includes the following advanced microarchitecture features:

• Hyper Pipelined Technology.

• Advanced Dynamic Execution.

• Execution Trace Cache.

®

NetBurst™ microarchitecture. The Xeon

®

Xeon™ Processor with 512 KB L2 Cache Feature Set Overview

Feature Xeon™

Intel and OEM EEPROMs and

thermal sensor on package

• Streaming SIMD (single instruction, multiple data) Extensions 2.

• Advanced Transfer Cache.

• Enhanced Floating Point and Multimedia Engine.

The Intel Xeon processor system bus utilizes a split-transaction, deferred reply protocol similar to

that of the Intel

with the Pentium III Xeon processor bus. The system bus uses source-synchronous transfer of

address and data to improve performance and enables addressing at 2X the system bus frequency

of 100 MHz and data transfers at 4X the system bus frequency of 100 MHz. This allows the

processors to transfer data at 3.2 GB/s.

The Xeon processor provides manageability features consistent with Intel

processors. These features include the Processor Information ROM, the OEM EEPROM, and the

processor thermal sensor; all of which are accessed through the System Management Bus

(SMBus). The Processor Information ROM is a 128-byte read-only device that incorporates Intel

processor specific data. The OEM EEPROM, also known as the “scratchpad EEPROM,” is a

128-byte read/write EEPROM in which an OEM may program system specific data. The thermal

sensor monitors the temperature of the processor die.

®

Pentium III Xeon™ processor bus, however the system bus is not compatible

®

Pentium® III Xeon™

20 Design Guide

Page 21

1.3.2 Intel® E7500 Chipset

Introduction

The E7500 chipset consists of three major components: the Intel® E7500 Memory Controller Hub

(referred to throughout this document as the MCH), the Intel

(hereafter referred to as ICH3-S), and th e Intel

P64H2). The chipset components communicate via hub interfaces (HIs). The MCH provides four

hub interface connections: one for the ICH3-S and three for high-speed I/O using 82870P2 P64H2

components. The hub interfaces are point-to-po int and therefore on ly support two agents (the MCH

plus one I/O device). Therefore, the system supports a total of three P64H2s.

®

82870P2 PCI/ PCI-X 64-bit Hub 2 (abbreviated to

1.3.2.1 Intel® E7500 Memory Controller Hub (MCH)

The MCH is a 1005-ball FC-BGA package and contains the following functionality:

• System Bus Features:

— Supports dual processors at 100 MHz (x4 transfers).

— System bus bandwidth of 3.2 GB/s (400 MHz).

— Supports 36-bit system bus addressing model.

— 12 deep in-order queue, 2 deep defer queue.

• Memory Bus Features:

— 144-bit wide, DDR-200 memory interface with memory bandwidth of 3.2 GB/s.

— Supports x72, ECC, registered DDR-200 DIMMs using 64-Mb, 128-Mb, 256-Mb and

512-Mb DRAMs.

— Supports a maximum of 16 GB of memory.

— Supports Single 4-bit Error Correct, Double 4-bit Error Detect (S4EC/D4ED) Chipkill

technology ECC (x4 Chipkill technology).

— Supports up to 32 simultaneous open pages.

®

82801CA I/O Controller Hub 3-S

• I/O Features:

— Provides HI1.5 connection for ICH3-S (Hub Interface A):

- 266 MB/s point-to-point connection for ICH3-S with parity protection.

- 8-bit wide, 66 MHz base clock, 4X data transfer.

- Parallel termination mode for longer trace lengths.

- 64-bit inbound addressing, 32-bit outbound addressing.

— Provides 3 HI2.0 Connections for P64H2s (Hub Interfaces B, C and D):

- 1.066 GB/s point-to-point connection for I/O bridges with ECC protection.

- 16-bit wide, 66 MHz base clock, 8X data transfer.

- Parallel termination mode for longer trace lengths.

- 64-bit inbound addressing, 32-bit outbound addressing.

• Power Management Features:

— Supports C0, C1, C2, S0, S1, S4, and S5 power states. (Does not support C3, C4, S2,

and S3).

Design Guide 21

Page 22

Introduction

1.3.2.2 I/O Controller Hub 3 (Intel® ICH3-S)

The I/O Controller Hub (ICH3-S) provides the legacy I/O subsystem for E7500 chipset-based

platforms. Additionally, it integrates many advanced I/O functions. The ICH3-S includes the

following features:

• Provides HI1.5 Connection to MC H:

— 266 MB/s point-to-point connection for ICH3-S with parity protection.

— 8-bit wide, 66 MHz base clock, 4X data transfer.

— Parallel termination mode for longer trace lengths.

— 64-bit inbound addressing, 32-bit outbound addressing.

• 2 channel Ultra ATA/100 bus master IDE controller.

• 3 Universal Host Controller Interface (UHCI) USB 1.1 compliant host controllers

(Capabilities for six ports).

• I/O APIC.

• System Management Bus (SMBus) Specificatio n, Version 1.1 compliant controller.

• LPC interface.

• AC '97 Component Specification, Revision 2.2 compliant interface.

• PCI Local Bus Specification, Revision 2.2 compliant interface.

• Integrated LAN Controller.

1.3.2.3 PCI/PCI-X 64-bit Hub 2 (Intel® 82870P2 P64H2)

The P64H2 provides PCI/PCI-X, high-performance I/O capability on E7500 chipset based

platforms. Each P64H2 component includes:

• 16-bit, HI2.0 Connection to MCH:

— 1 GB/s point-to-point connection for I/O bridges with ECC protection.

— 16-bit wide, 66 MHz base clock, 8X data transfer.

— Parallel termination mode for longer trace lengths.

— 64-bit inbound addressing, 32-bit outbound addressing.

• Two Independent, 64-bit PCI/PCI-X Interfaces:

— PCI-X Specification, Revision 1.0a compliant.

— PCI Local Bus Specification, Revision 2.2 compliant.

— PCI-PCI Bridge Architecture Specification, Revision 1.1 compliant.

— PCI Hot Plug Specification, Revision 1.1 compliant.

— One PCI Hot Plug Controller (PHPC) per PCI/PCI-X interface.

— One IOxAPIC per PCI/PCI-X Interface (16 external, 8 internal interrupts).

— SMBus target for access to all internal PCI registers.

22 Design Guide

Page 23

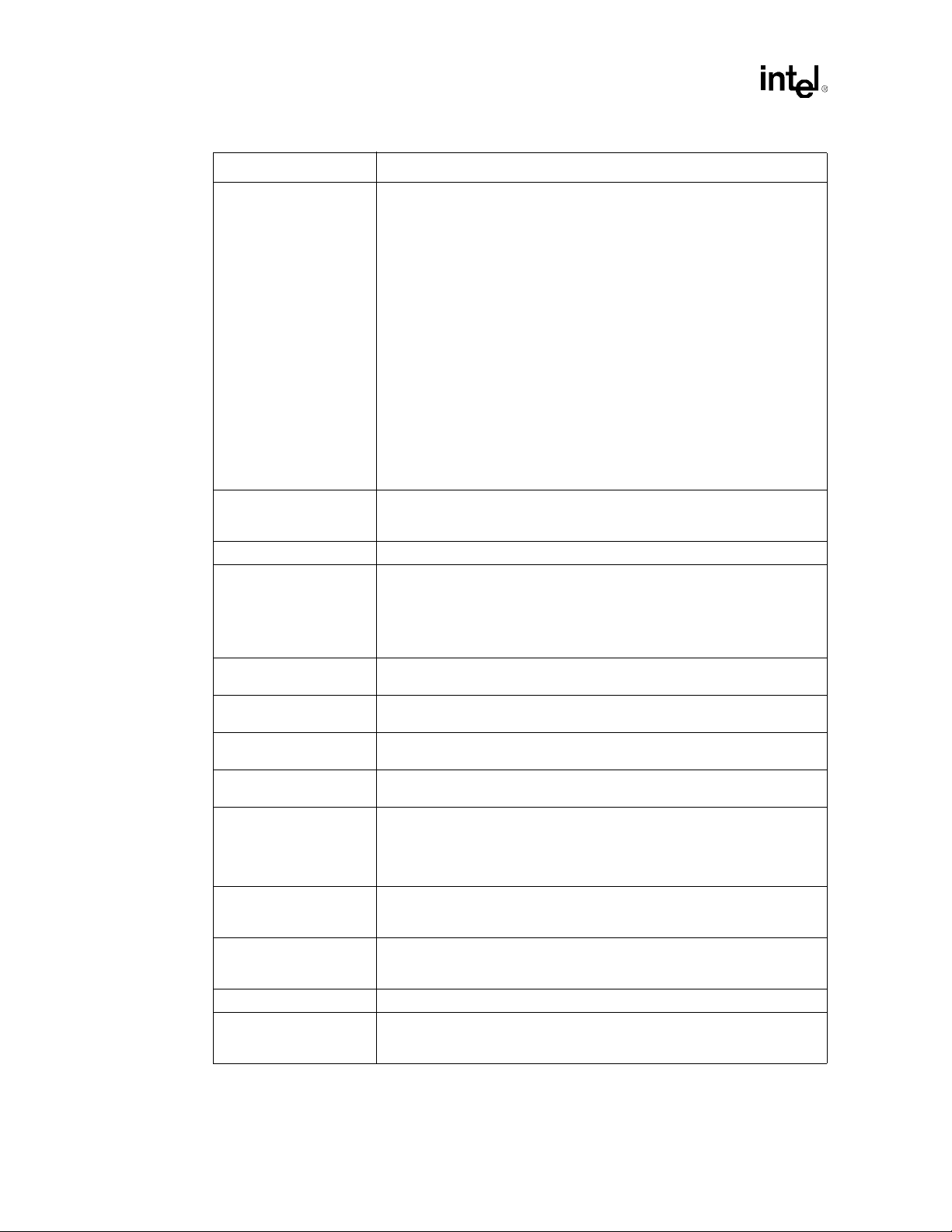

1.3.3 Bandwid th Summary

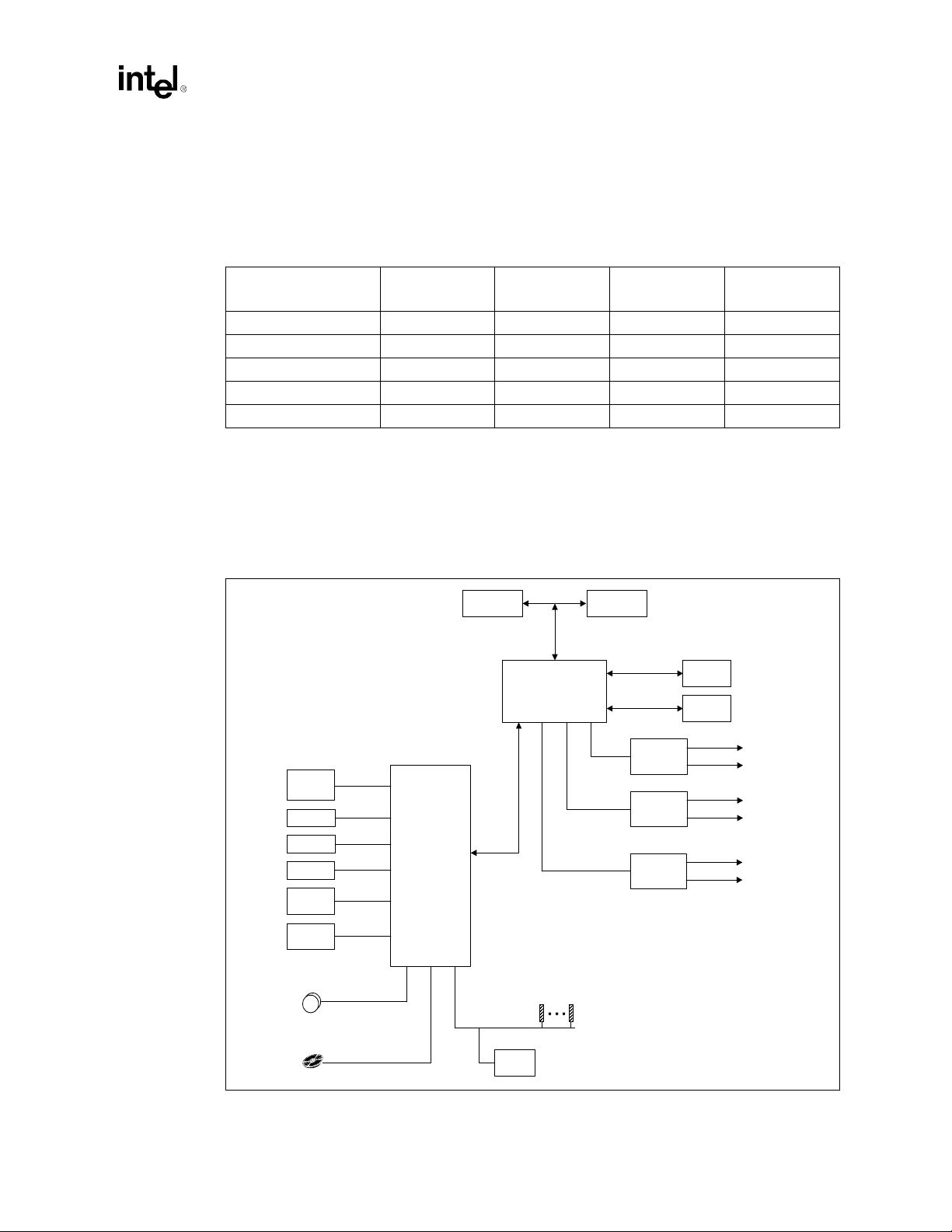

Table 1-3 describes the clock maximum speed, sample rate, and bandwidth for each of the

interfaces in the E7500 chipset based platform.

Table 1-3. Platform Maximum Bandwidth Summary

Introduction

Interface

Clock Speed

(MHz)

Samples per

Clock

Data Width

(Bytes)

System Bus (Data) 100 4 8 3200

DDR Interface 100 2 16 3200

Hub Interface A 66 4 1 266

Hub Interface B, C, D 66 8 2 1066

PCI-X 133 1 8 1066

1.3.4 System Configurations

Figure 1-1 illustrates an example E7500 chipset-based system configuration for server platforms

using Xeon processors.

Figure 1-1. Example Intel® Xeon™ Processor with 512 KB L2 Cache / Intel® E7500 Chipset

Based System Configuration

ProcessorProcessor

System Memory

200 MHz

DDR

200 MHz

DDR

Hot Plug

Hot Plug

Hot Plug

PCI / PCI-X

PCI / PCI-X

PCI / PCI-X

PCI / PCI-X

PCI / PCI-X

PCI / PCI-X

SMBus

Devices

GPIOs

Super I/O

1–4 FWHs

10/100 LAN

Controller

AC '97

Codec(s)

SMBus 1.1

LPC I/F

AC'97 2.1

Intel

ICH3-S

MCH

16-bit

HI 2.0

16-bit

HI 2.0

®

8-bit

HI 1.5

16-bit

HI 2.0

Intel®

P64H2

P64H2

P64H2

Bandwidth

(MB/s)

USB 1.1, 6 Ports

4 IDE Devices

UltraATA/100

PCI Bus

Agent

PCI

PCI

Slots

Design Guide 23

Page 24

Introduction

This page is intentionally left blank.

24 Design Guide

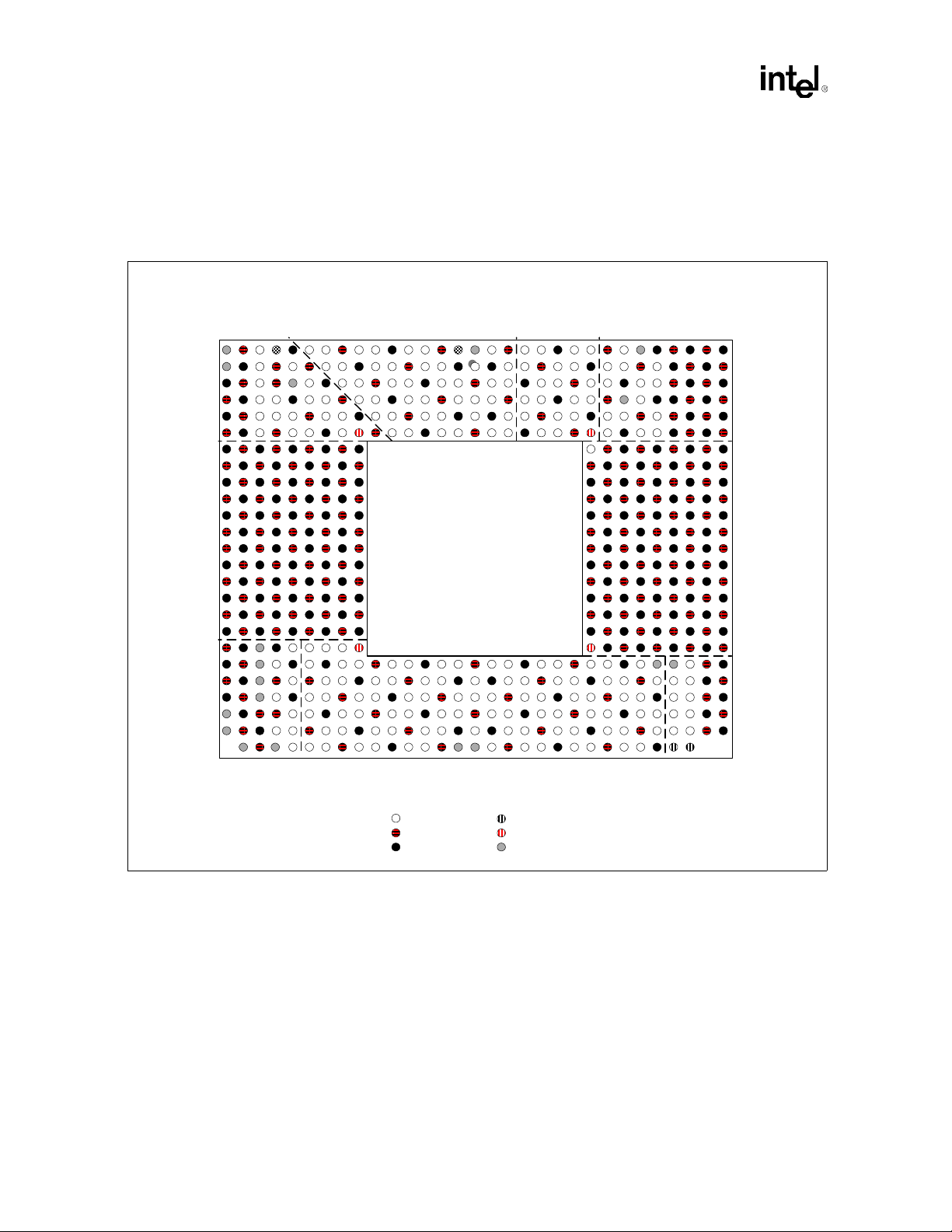

Page 25

Component Quadrant Layout

Component Quadrant Layout 2

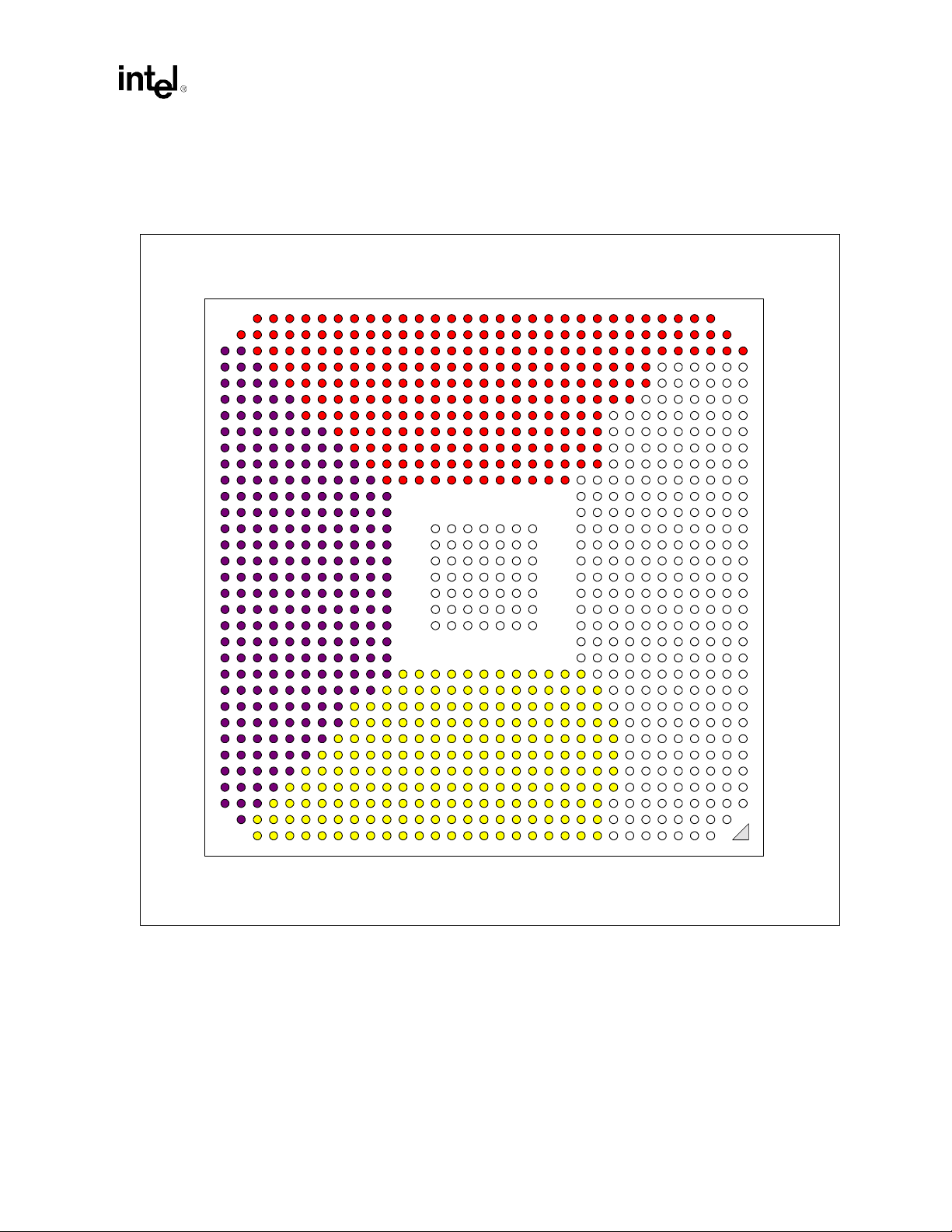

The following figures show only general quadrant information, not exact component ball count.

Designers should use only the exact ball assignment to conduct routing analyses. Reference the

following documents for exact ball assignment information.

®

• Intel

• Intel

• Intel

• Intel

Xeon™ Process or wi th 512 KB L2 Cache at 1.80 G Hz, 2 GH z , a nd 2.2 0 G Hz Dat as heet

®

82801CA I/O Controller Hub 3 (ICH3-S) Datasheet

®

PCI-64 Hub 2 (P64H2) Datasheet

®

E7500 Chipset Memory Controller Hub (MCH) Datasheet

Design Guide 25

Page 26

Component Quadrant Layout

2.1 Intel® Xeon™ Processor with 512 KB L2 Cache Quadrant Layout

Figure 2-1. Intel® Xeon™ Processor with 512 KB L2 Cache Quadrant Layout (Top View)

COMMON

CLOCK

A

B

C

D

E

F

G

H

J

K

L

M

N

Vcc/Vss

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

ADDRESS

3 5 7 9 11 13 15 17 19 21 23 25 27 29 311

2 4 6 8 10 12 14 16 18 20 22 24 26 28

CLOCKS SMBus

DATA

COMMON

CLOCK

Async /

JTAG

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

Vcc/Vss

= Signal

= Power

= Ground = Reserved/NC

= SM_VCC

= GTLREF

26 Design Guide

Page 27

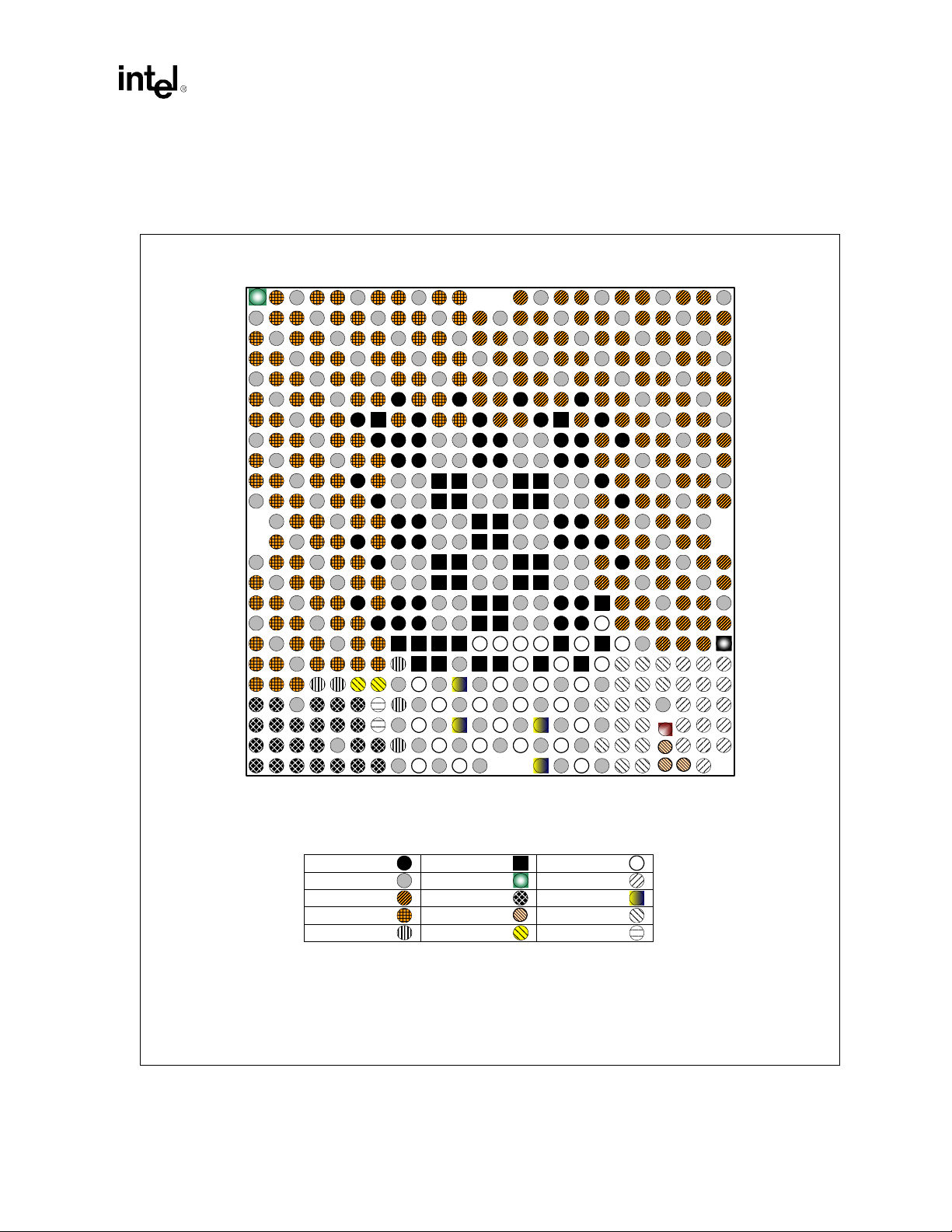

2.2 Intel® E7500 MCH Quadrant Layout

Figure 2-2. Intel® E7500 MCH Quadrant Layout (Top View)