Page 1

8XC196Lx Supplement to

8XC196Kx, 8XC196Jx,

87C196CA User’s Manual

August 2004

Order Number: 272973-003

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

herwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions

ot

of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating

to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability,

or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical,

e saving, or life sustaining applications.

lif

In

tel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined."

Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising

om future changes to them.

fr

The 8XC196Lx, 8XC196Kx, 8XC196Jx and 87C196CA microprocessors may contain design defects or errors known as

errata which may cause the products to deviate from published specifications. Current characterized errata are available on

request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be

obtained by calling 1-800-548-4725 or by visiting Intel’s website at http://www.intel.com.

Copyright © Intel Corporation, 2004

*Third-party brands and names are the property of their respective owners.

Page 3

CONTENTS

CHAPTER 1

GUIDE TO THIS MANUAL

1.1 MANUAL CONTENTS................................................................................................... 1-1

1.2 RELATED DOCUMENTS.............................................................................................. 1-2

CHAPTER 2

ARCHITECTURAL OVERVIEW

2.1 MICROCONTROLLER FEATURES.............................................................................. 2-1

2.2 BLOCK DIAGRAM............................................ ............................................. ...... ..... ..... 2-2

2.3 INTERNAL TIMING........................................................................................................ 2-2

2.4 EXTERNAL TIMING...................................................................................................... 2-5

2.5 INTERNAL PERIPHERALS........................................................................................... 2-6

2.5.1 I/O Ports ........................................... ...... ..... ...... ............................................. ..... .. ....2-7

2.5.2 Synchronous Serial I/O Port .....................................................................................2-7

2.5.3 Event Processor Array .............................................................................................. 2-7

2.5.4 J1850 Communications Controller ............................................................................2-7

2.6 DESIGN CONSIDERATIONS........................................................................................ 2-7

CHAPTER 3

ADDRESS SPACE

3.1 ADDRESS PARTITIONS............................................................................................... 3-1

3.2 REGISTER FILE.................................... ............................................. ..... ...... ...... .......... 3-2

3.3 PERIPHERAL SPECIAL-FUNCTION REGISTERS...................................................... 3-4

3.4 WINDOWING................................................................................................................. 3-6

CHAPTER 4

STANDARD AND PTS INTERRUPTS

4.1 INTERRUPT SOURCES, VECTORS, AND PRIORITIES............................................. 4-1

4.2 INTERRUPT REGISTERS............................................................................................. 4-2

4.2.1 Interrupt Mask Registers ............................. ...... ..... ...... ...... ..... ..................................4-3

4.2.2 Interrupt Pending Registers ............................................... .......................................4-4

4.2.3 Peripheral Transaction Server Registers ..................................................................4-6

CHAPTER 5

I/O PORTS

5.1 I/O PORTS OVERVIEW................................................................................................ 5-1

5.2 INTERNAL STRUCTURE FOR PORTS 1, 2, 5, AND 6 (BIDIRECTIONAL PORTS).... 5-1

5.2.1 Configuring Ports 1, 2, 5, and 6 (Bidirectional Ports) ................................................5-3

5.2.2 Special Bidirectional Port Considerations .................................................................5-4

5.3 INTERNAL STRUCTURE FOR PORTS 3 AND 4 (ADDRESS/DATA BUS).................. 5-5

iii

Page 4

8XC196LX SUPPLEMENT

CHAPTER 6

SYNCHRONOUS SERIAL I/O PORT

6.1 SSIO 0 CLOCK REGISTER........................................................................................... 6-1

6.2 SSIO 1 CLOCK REGISTER........................................................................................... 6-2

CHAPTER 7

EVENT PROCESSOR ARRAY

7.1 EPA FUNCTIONAL OVERVIEW................................................................................... 7-1

7.1.1 EPA Mask Registers .......................................................................... ...... ...... ..... ......7-4

7.1.2 EPA Pending Registers ........ ............................................. ..... ...... ............................7-5

7.1.3 EPA Interrupt Priority Vector Register .......................................................................7-6

CHAPTER 8

J1850 COMMUNICATIONS CONTROLLER

8.1 J1850 FUNCTIONAL OVERVIEW................................................................................. 8-1

8.2 J1850 CONTROLLER SIGNALS AND REGISTERS..................................................... 8-3

8.3 J1850 CONTROLLER OPERATION............................................................................. 8-4

8.3.1 Control State Machine ..............................................................................................8-4

8.3.1.1 Cyclic Redundancy Check Generator ..................................................................8-4

8.3.1.2 Bus Contention .....................................................................................................8-5

8.3.1.3 Bit Arbitration ........................................................................................................8-5

8.3.1.4 Error Detection .....................................................................................................8-5

8.3.2 Symbol Synchronization and Timing Circuitry ...........................................................8-5

8.3.2.1 Clock Prescaler ....................................................................................................8-6

8.3.2.2 Digital Filter ..........................................................................................................8-6

8.3.2.3 Delay Compensation ............................................................................................8-6

8.3.2.4 Symbol Encoding and Decoding ..........................................................................8-6

8.3.3 Bit Arbitration Example .............................................................................................8-7

8.4 MESSAGE FRAMES..................................................................................................... 8-8

8.4.1 Standard Messaging .............................................. ...... ...... .......................................8-9

8.4.1.1 Header .................................................................................................................8-9

8.4.1.2 CRC Byte .............................................................................................................8-9

8.4.1.3 Normalization Bit ..................................................................................................8-9

8.4.1.4 Start and End Message Frame Symbols ............................................................8-10

8.4.2 In-frame Response Me ss agi ng ............................................... ...... ..... .....................8-12

8.4.2.1 IFR Messaging Type 1: Single Byte, Single Responder ....................................8-12

8.4.2.2 IFR Messaging Type 2: Single Byte, Multiple Responders ................................8-12

8.4.2.3 IFR Messaging Type 3: Multiple Bytes, Single Responder ................................8-13

8.5 TRANSMITTING AND RECEIVING MESSAGES....................................................... 8-13

8.5.1 Transmitting Messages ...........................................................................................8-13

8.5.2 Receiving Mess age s ........................ ...... ..... ...... ............................................. .........8-15

8.5.3 IFR Messages .........................................................................................................8-16

iv

Page 5

CONTENTS

8.6 PROGRAMMING THE J1850 CONTROLLER ............................................................ 8-16

8.6.1 Programming the J1850 Command (J_CMD) Register ..........................................8-16

8.6.2 Programming the J1850 Configuration (J_CFG) Register ......................................8-18

8.6.3 Programming the J1850 Delay Compensation (J_DLY) Register ...........................8-19

8.6.4 Programming the J1850 Status (J_STAT) Register ................................................8-21

CHAPTER 9

MINIMUM HARDWARE CONSIDERATIONS

9.1 IDENTIFYING THE RESET SOURCE........................................................................... 9-1

9.2 DESIGN CONSIDERATIONS FOR 8XC196LA, LB, AND LD ....................................... 9-2

CHAPTER 10

SPECIAL OPERATING MODES

10.1 INTERNAL TIMING...................................................................................................... 10-1

10.2 ENTERING AND EXITING ONCE MODE................................................................... 10-2

CHAPTER 11

PROGRAMMING THE NONVOLATILE MEMORY

11.1 SIGNATURE WORD AND PROGRAMMING VOLTAGE VALUES............................. 11-1

11.2 OTPROM ADDRESS MAP.......................................................................................... 11-1

11.3 SLAVE PROGRAMMING CIRCUIT AND ADDRESS MAP......................................... 11-2

11.4 SERIAL PORT PROGRAMMING CIRCUIT AND ADDRESS MAP............................. 11-4

APPENDIX A

SIGNAL DESCRIPTIONS

A.1 FUNCTIONAL GROUPINGS OF SIGNALS................................................................. A-1

A.2 DEFAULT CONDITIONS.............................................................................................. A-7

GLOSSARY

v

Page 6

8XC196LX SUPPLEMENT

FIGURES

Figure Page

2-1 8XC196L

2-2 Clock Circuitry (87C196LA, LB Only)...........................................................................2-3

2-3 Internal Clock Phases (Assumes PLL is Bypassed).....................................................2-4

2-4 Effect of Clock Mode on Internal CLKOUT Frequency.................................................2-5

2-5 Unerasable PROM 1 (USFR1) Register (LA, LB Only)................................................2-6

3-1 Register File Address Map.................. ...... ............................................ ...... ...... ..... ......3-3

4-1 Interrupt Mask (INT_MASK) Register.................................... .......................................4-3

4-2 Interrupt Mask 1 (INT_MASK1) Register......................................................................4-4

4-3 Interrupt Pending (INT_PEND) Register ......................................................................4-5

4-4 Interrupt Pending 1 (INT_PEND1) Register .................................................................4-6

4-5 PTS Select (PTSSEL) Register....................................................................................4-7

4-6 PTS Service (PTSSRV) Register .................................................................................4-8

5-1 Ports 1, 2, 5, and 6 Internal Structure (87C196LA, LB Only) .......................................5-3

5-2 Ports 3 and 4 Internal Structure (87C196LA, LB Only)................................................5-6

6-1 SSIO 0 Clock (SSIO0_CLK) Register...........................................................................6-1

6-2 SSIO 1 Clock (SSIO1_CLK) Register...........................................................................6-2

7-1 EPA Block Diagram (87C196LA, LB Only)...................................................................7-2

7-2 EPA Block Diagram (83C196LD Only).........................................................................7-3

7-3 EPA Interrupt Mask (EPA_MASK) Register.................................................................7-4

7-4 EPA Interrupt Mask 1 (EPA_MASK1) Register.......................... ...... ............................7-4

7-5 EPA Interrupt Pending (EPA_PEND) Register.............................................................7-5

7-6 EPA Interrupt Pending 1 (EPA_PEND1) Register........................................................7-5

7-7 EPA Interrupt Priority Vector Register (EPAIPV)..........................................................7-6

8-1 Integrated J1850 Communications Protocol Solution...................................................8-1

8-2 J1850 Communications Controller Block Diagram.......................................................8-2

8-3 Huntzicker Symbol Definition for J1850........................................................................8-7

8-4 Typical VPW Waveform................................................................................................8-7

8-5 Bit Arbitration Example.................................................................................................8-8

8-6 J1850 Message Frames...............................................................................................8-9

8-7 Huntzicker Symbol Definition for the Normalization Bit..............................................8-10

8-8 Definition for Start and End of Frame Symbols..........................................................8-11

8-9 IFR Type 1 Message Frame.......................................................................................8-12

8-10 IFR Type 2 Message Frame.......................................................................................8-13

8-11 IFR Type 3 Message Frame.......................................................................................8-13

8-13 J1850 Transmit Message Structure............................................................................8-14

8-12 J1850 Transmitter (J_TX) Register............................................................................8-14

8-15 J1850 Receive Message Structure.............................................................................8-15

8-14 J1850 Receiver (J_RX) Register................................................................................8-15

8-16 J1850 Command (J_CMD) Register..........................................................................8-17

8-17 J1850 Configuration (J_CFG) Register......................................................................8-18

8-18 J1850 Delay (J_DLY) Register...................................................................................8-20

8-19 J1850 Status (J_STAT) Register................................................................................8-21

9-1 Reset Source (RSTSRC) Register...............................................................................9-1

10-1 Clock Circuitry (87C196LA, LB Only).........................................................................10-2

x

Block Diagram............................................................................................2-2

vi

Page 7

CONTENTS

FIGURES

Figure Page

11-1 Slave Programming Circuit.........................................................................................11-3

11-2 Serial Port Programming Circuit.................................................................................11-4

A-1 87C196LA 52-pin PLCC Package............................. ...... ...... ......................................A-3

A-2 87C196LB 52-pin PLCC Package............................. ...... ...... ......................................A-5

A-3 83C196LD 52-pin PLCC Package............................................................................... A-7

vii

Page 8

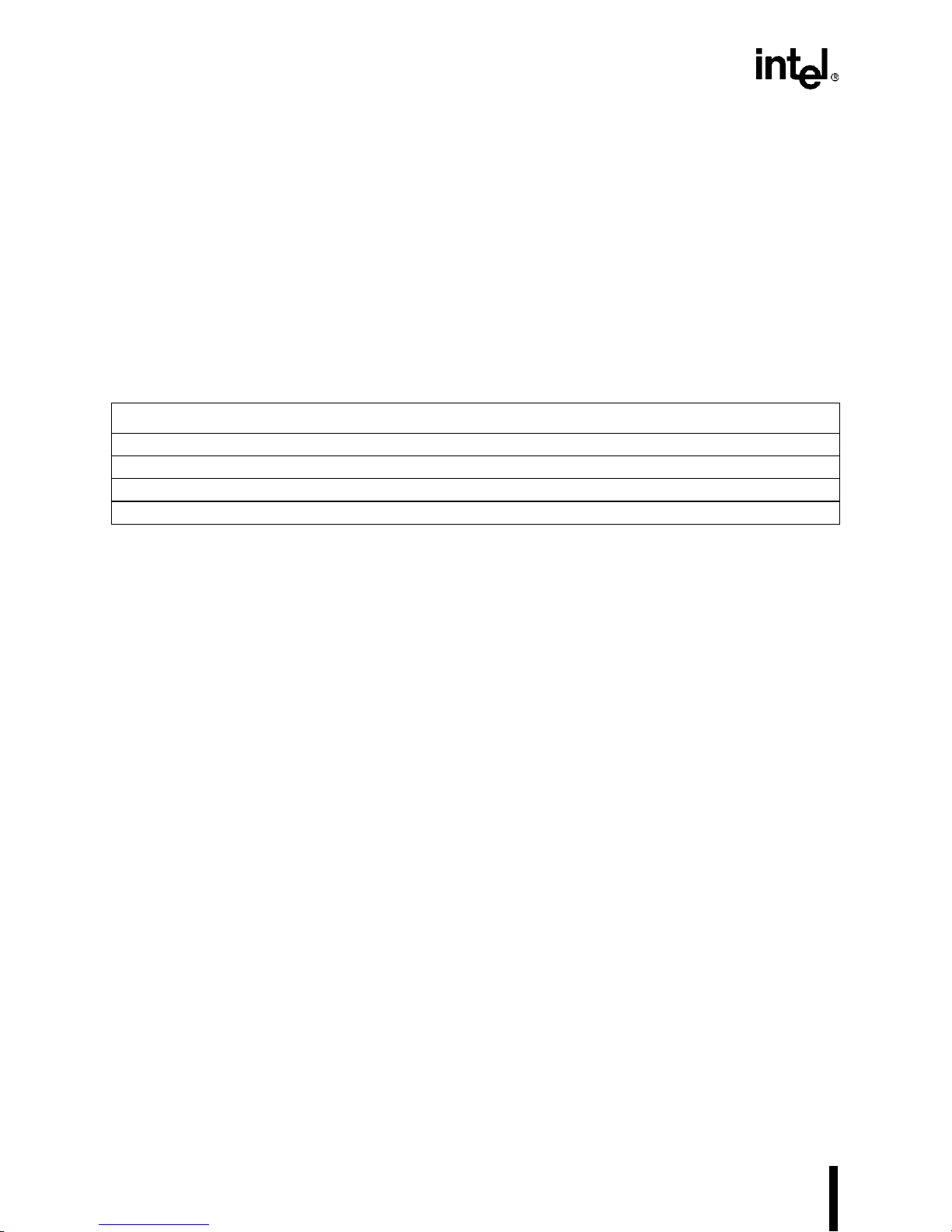

8XC196LX SUPPLEMENT

TABLES

Table Page

1-1 Related Documents......................................................................................................1-2

2-1 Features of the 8XC196Lx and 8XC196Kx Product Famiies.......................................2-1

2-2 State Times at Various Frequencies..................................... ..... ...... ............................2-4

2-3 Relationships Between Input Frequency, Clock Multiplier, and State Times ...............2-5

2-4 UPROM Programming Values and Locations..............................................................2-6

3-1 Address Map................................................................................................................3-1

3-2 Register File Memory Addresses ................................................................................. 3-3

x

3-3 8XC196L

3-4 Windows.......................................................................................................................3-6

4-1 Interrupt Sources, Vectors, and Prioriti es........................ ...... ..... ...... ............................4-2

5-1 Microcontroller Ports.....................................................................................................5-1

7-1 EPA Channels.......................... ..... ...... ...... ............................................ ...... ...... ..... ......7-1

7-2 EPA Interrupt Priority Vectors.......................................................................................7-6

8-1 J1850 Controller Signals ..............................................................................................8-3

8-2 Control and Status Registers .......................................................................................8-3

8-3 Relationships Between Input Frequency, PLL, and Prescaler Bits..............................8-6

8-4 Huntzicker Symbol Timing Characteristics.................................................................8-11

11-1 Signature Word and Programming Voltage Values....................................................11-1

11-2 87C196LA, LB

11-3 Slave Programming Mode Address Map....................................................................11-3

11-4 Serial Port Programming Mode Address Map............................................................11-5

A-1 87C196LA Signals Arranged by Functional Categories..............................................A-2

A-2 87C196LB Signals Arranged by Functional Categories..............................................A-4

A-3 83C196LD Signals Arranged by Functional Categories..............................................A-6

A-4 Definition of Status Symbols .......................................................................................A-7

A-5 87C196LA, LB Default Signal Conditions....................................................................A-8

A-6 83C196LD Default Signal Conditions..........................................................................A-9

Peripheral SFRs.........................................................................................3-4

OTPROM Address Map.....................................................................11-2

viii

Page 9

Guide to This Manual

1

Page 10

Page 11

CHAPTER 1

GUIDE TO THIS MANUAL

This document is a supplement to the 8XC196Kx, 8XC196Jx, 87C 196CA Microcontr oller Family

User’s Manual. It descri bes the differences between the 8XC1 96Lx and the 8XC196 Kx family of

microcontrollers. For information not found in th is supplement, please consult the 8XC196Kx,

8XC196Jx, 87C196CA Microcontroller Family User’s Manual (order number 272258) or the

8XC196Lx datasheets listed in the “Related Documents” section of this chapter.

1.1 MANUAL CONTENTS

This supplement contains several chapters, an appendix, a glossary, and an index. This chapter,

Chapter 1, provides an overview of the supplement. This section summarizes the contents of the

remaining chapters and appendixes. The remainder of this chapter provides references to related

documentation.

Chapter 2 — Architectural Overview — compares the features of the 8XC196Lx microcon-

troller family with those of the 8XC196Kx microcontroller family an d des cri bes t he 87 C19 6LA,

LB internal clock circuitry.

Chapter 3 — Address Space — describes the addressable memory space of the 52-pin

8XC196Lx, lists the peripheral special-function registers (SFRs), and provides tables of WSR

values for windowing higher memory into the lower register file for direct access.

Chapter 4 — Standard and PTS Interrupts — describes the additional interrupts for the

87C196LB’s J1850 communications controller peripheral and the SFRs that support those interrupts.

Chapter 5 — I/O Ports — describes the port differences and explains the change in the port reset

state from a “logic 1” to a “logic 0” on the 87C196LA, LB.

Chapter 6 — Synchronous Serial I/O Port — describes the enhanced synchronous serial I/O

(SSIO) port and explains how to program the two additional p e ripheral SFRs.

Chapter 7 — Event Processor Array — describes the event processor array channel dif ferences.

Chapter 8 — J1850 Communications Controller — describes the 87C196LB’s integrated

J1850 controller and explains how to configure it.

Chapter 9 — Minimum Hardware Considerations — describes device reset options through

the reset source register, and discusses hardware design considerations.

Chapter 10 — Special Operating Modes — illustrates the internal clock control circuitry of the

87C196LA, LB and describes how to enter and exit on-circuit emulation (ONCE) mode.

Chapter 1 1 — Programm ing the Nonvol atile Memo ry — describes the memory maps and rec-

ommended circuits to support programming of the 87C196LA, LB’s 24 Kbytes of OTPROM.

1-1

Page 12

8XC196LX SUPPLEMENT

Appendix A — Signal Descriptions — provides reference information for the 8XC196Lx de-

vice pins, including descript ions of the pin function s, reset status of the I/O and control pi ns, and

package pin assignments.

Glossary — d e fines terms with special meaning used throughout this supp lement.

Index — lists key topics with page number references.

1.2 RELATED DOCUMENTS

T a ble 1-1 lists additional do cumen ts that yo u may fi nd useful in des igning systems inco rporatin g

the 8XC196Lx microcontrollers.

Table 1-1. Related Documents

Title and Description Order Number

8XC196Kx, 8XC196Jx, 87C196CA Microcontroller Family User’s Manual

87C196LA-20 MHz CHMOS 16-Bit Microcontroller Automotive

87C196LB-20 MHz CHMOS 16-Bit Microcontroller Automotive

83C196LD CHMOS 16-Bit Microcontroller Automotive

datasheet 272805

datasheet 272806

datasheet 272807

272258

1-2

Page 13

Architectural

Overview

2

Page 14

Page 15

CHAPTER 2

ARCHITECTURAL OVERVIEW

This chapter describes architectural differences between the 8XC196L x (87C196LA, 8 7C196LB,

and 83C196LD) and the 8XC196Kx (8XC196Kx, 8XC196Jx, and 87C196CA) microcontroller

families. Both the 8XC196Lx and the 8XC196Kx are designed for high-speed calculations and

fast I/O, and share a common architecture and instruction set with few deviations. This chapter

provides a high-level overview of the deviations between the two families.

NOTE

This supplement describes two produc t fami lies within the MCS® 96

microcontroller family. For brevity, the name 8XC196Lx is used when the

discussion applies to all three Lx controllers. Likewise, th e name 8XC196 Kx is

used when the discussion applies to all the Kx, Jx, and CA controllers.

2.1 MICROCONTROLLER FEATURES

Table 2-1 lists the features of the 8XC196Lx and the 8XC196Kx.

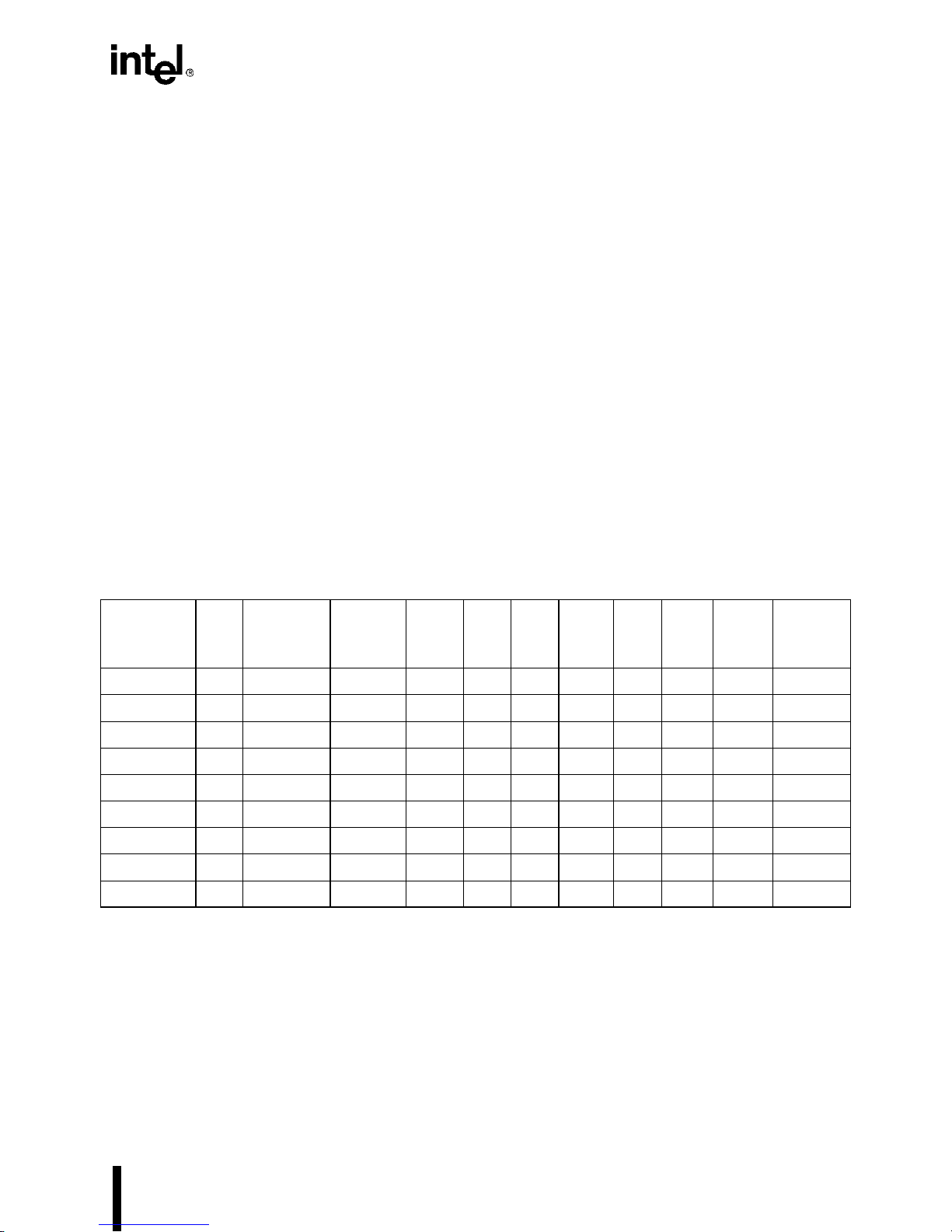

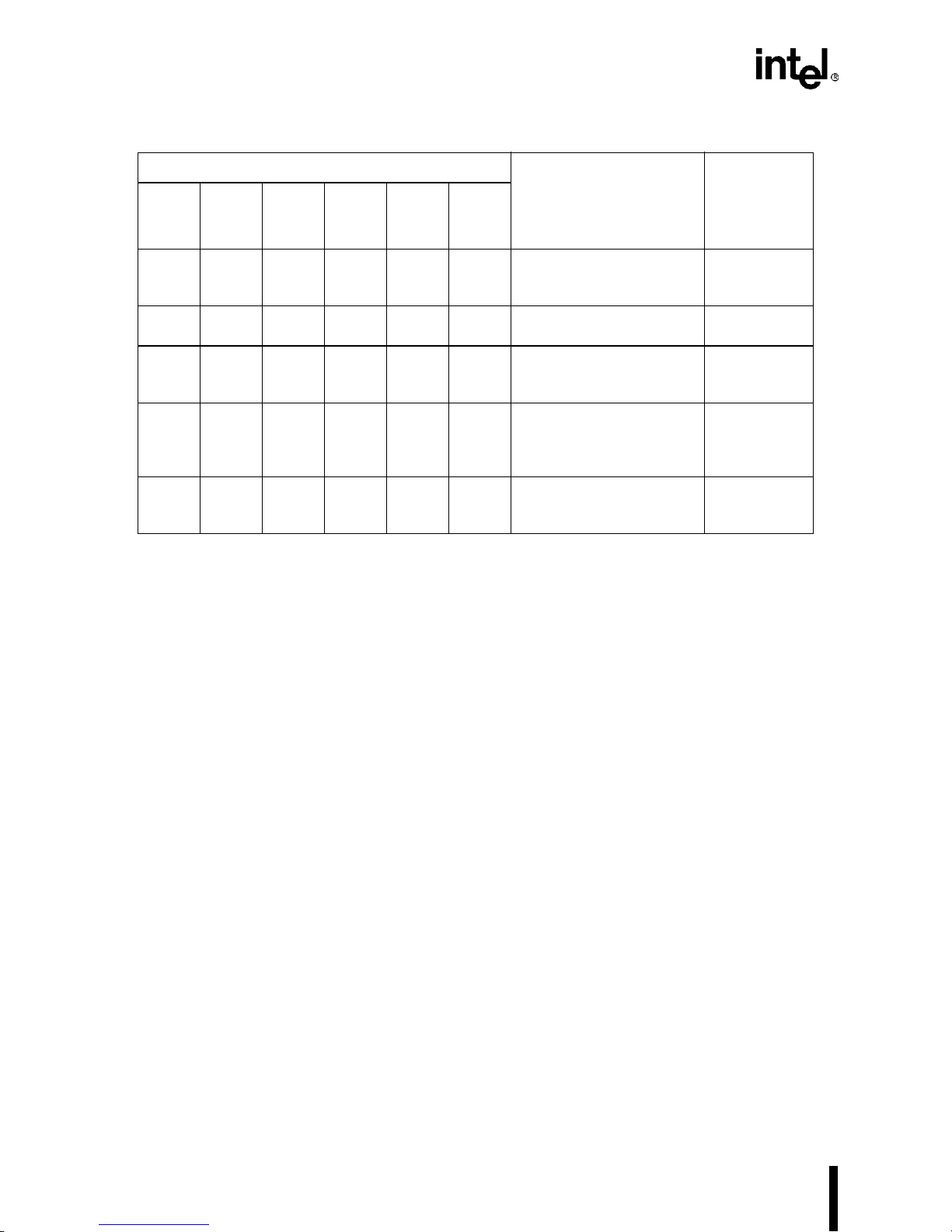

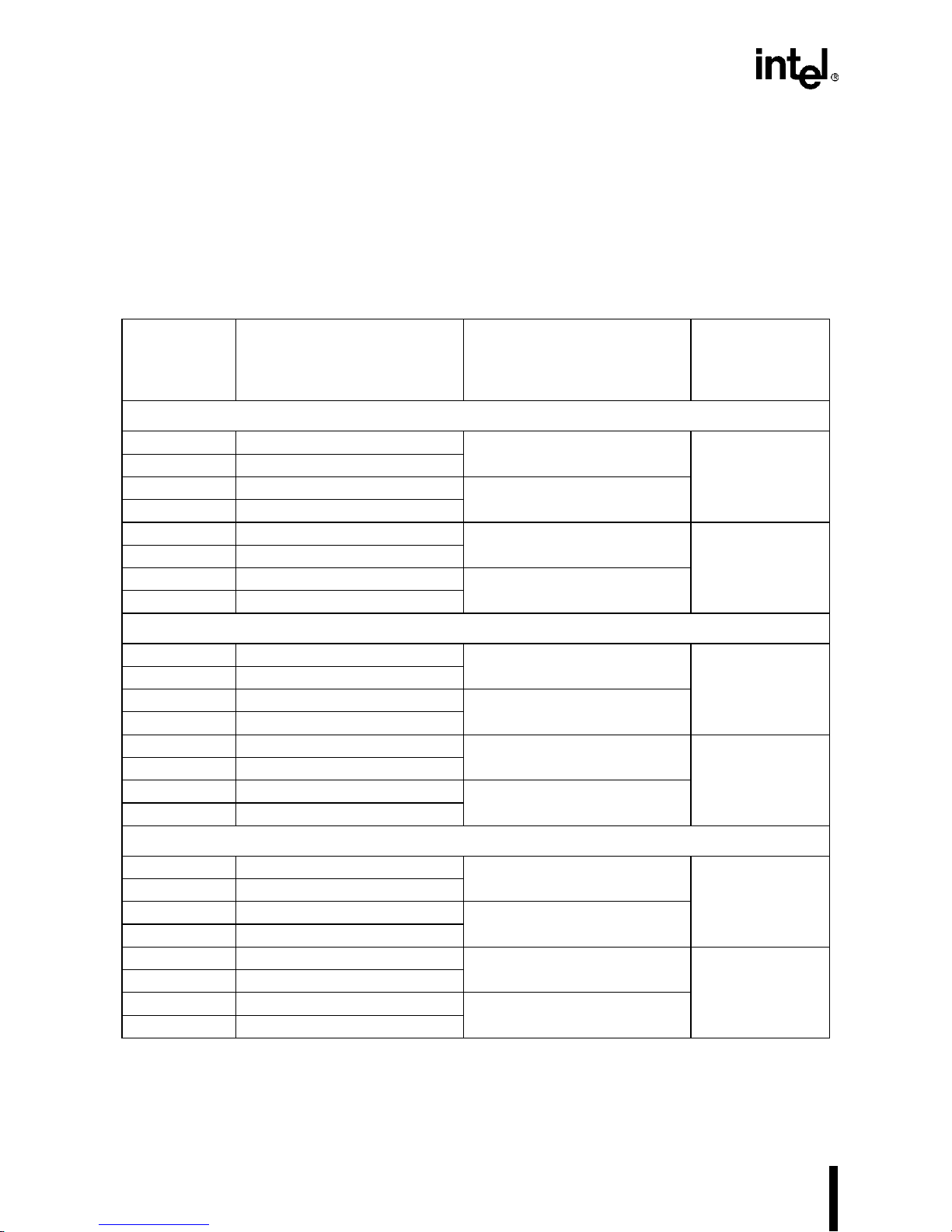

Table 2-1. Features of the 8XC196Lx and 8XC196Kx Product Famiies

OTPROM/

Device Pins

87C196LA 52 24 K 768 —416 3 6— — 1

87C196LB 52 24 K 768 — 41 6 3 6 — 1 1

83C196LD 52 16 K 384 — 41 6 3 — — — 1

8XC196JV 52 48 K 1536 512 41 6 3 6 — — 1

8XC196KT 68 32 K 1024 512 56 10 3 8 — — 2

8XC196JT 52 32 K 1024 512 41 6 3 6 — — 1

87C196CA 68 32 K 1024 256 51 6 3 6 1 — 2

8XC196KR 68 16 K 512 256 56 10 3 8 — — 2

8XC196JR 52 16 K 512 256 41 6 3 6 — — 1

NOTES:

1. Optional. The second character of the device name indicates the presence and type of nonvolatile

memory. 80C196

2. Register RAM amounts include the 24 bytes allocated to core SFRs and the stack pointer.

EPROM/

ROM (1)

xx

= none; 83C196xx = ROM; 87C196xx = OTPROM or EPROM.

Register

RAM (2)

Code

RAM

I/O

Pins

EPA

Pins

SIO/

SSIO

Ports

A/D CAN J1850

Ext.

Interrupt

Pins

2-1

Page 16

8XC196LX SUPPLEMENT

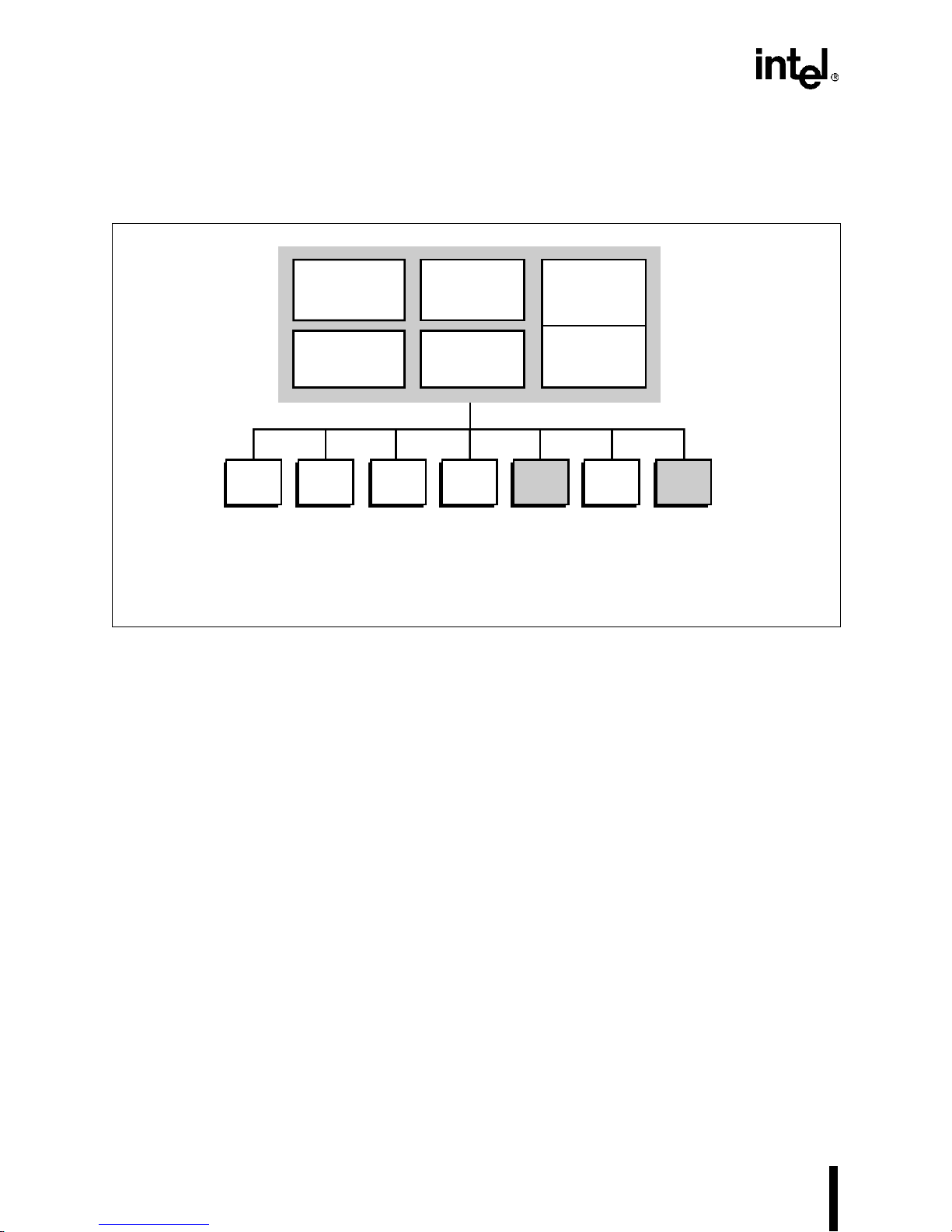

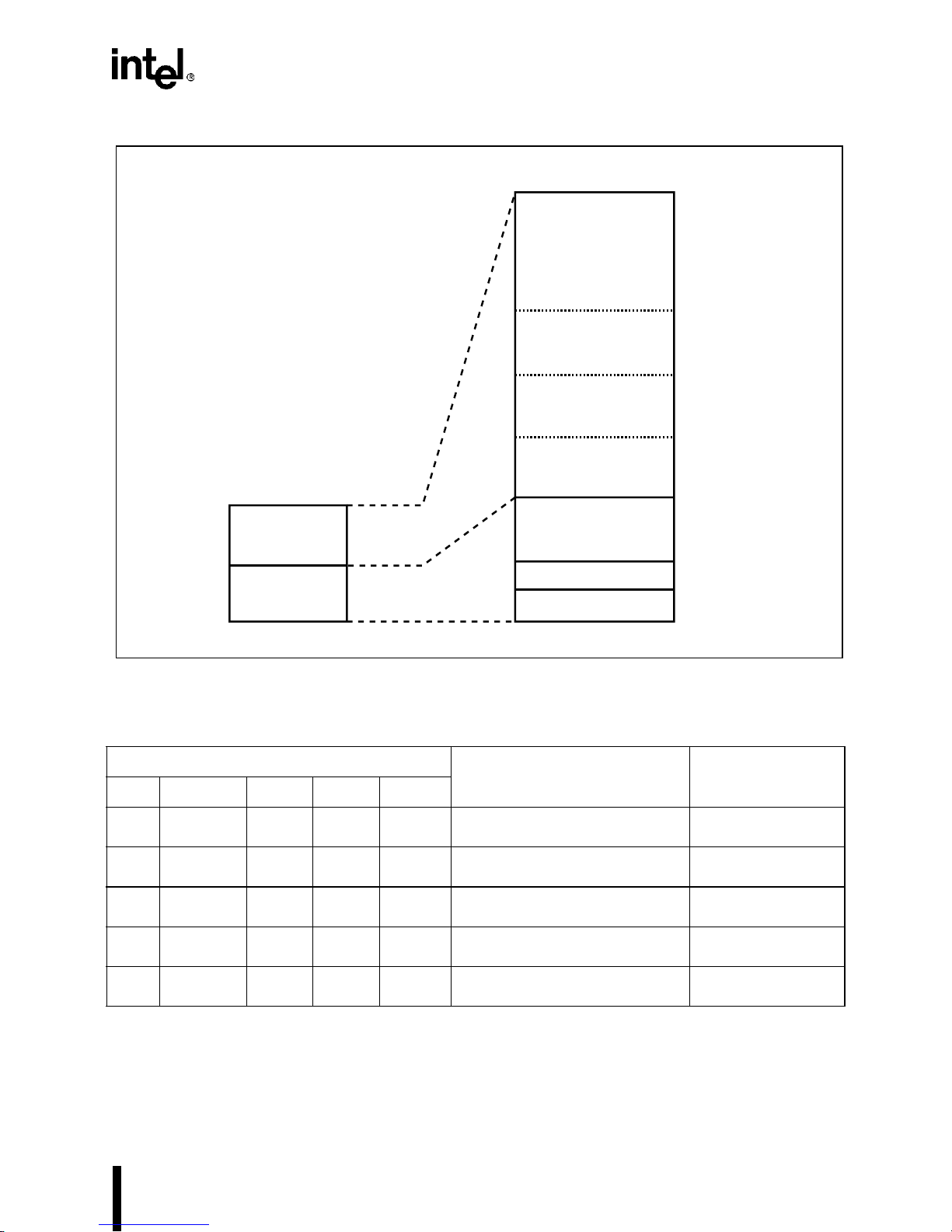

2.2 BLOCK DIAGRAM

Figure 2-1 is a simplified block diagram that shows the major blocks within the microcontroller.

Observe that the slave port peripheral does not exist on the 8XC196Lx.

(CPU, Memory

Controller)

Clock and

Power Mgmt.

SIO

Note:

The J1850 peripheral is unique to the 87C196LB device.

The A/D peripheral is unique to the 87C196LA, LB devices.

2.3 INTERNAL TIMING

Core

Optional

ROM/

OTPROM

Optional

Code/Data

RAM

EPA

Interrupt

Controller

Peripheral

Transaction

A/DSSIOI/O

Server

WDT

Figure 2-1. 8XC196Lx Block Diagram

J1850

A5253-01

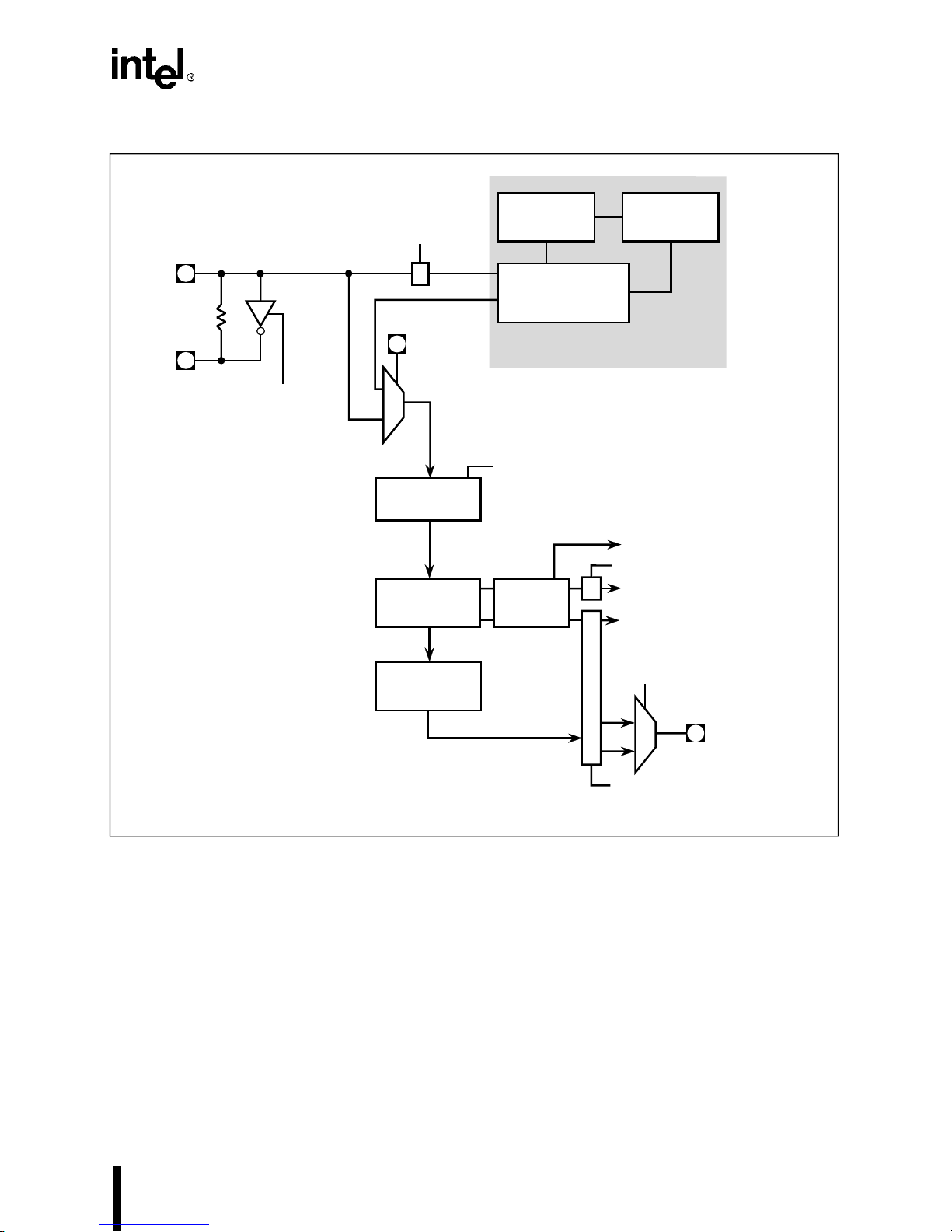

The 87C196LA, LB clock circuitry (Figure 2-2) implem ents a phase-locked loop and clock multiplier circuitry , which can substantially increase the CPU clock rate while using a lower-frequency input clock. The clock circuitry accepts an input clock signal on XTAL1 provided by an

external crystal or os cill at o r. Depending on the value of the PLLEN pin, this frequency is ro ut ed

either through the phase-locked loo p and m ultipl ier or directly to the d ivide -by-two circuit. The

multiplier circuitry can double the input frequency (F

) before the frequency (f) reaches the

XTAL1

divide-by-two circuitry. The clock generators accept the divided input frequency (f/2) from the

divide-by-two circuit and produce two nonoverlapping internal timing signals, PH1 and PH2.

These signals are active when high.

NOTE

This manual uses lowercase “f” to represent the internal clock frequency. For

the 87C196LA and LB, f is equal to either F

XTAL1

or 2F

, depending on th e

XTAL1

clock multiplier mode, which is controlled by the PLLEN input pin.

2-2

Page 17

ARCHITECTURAL OVERVIEW

XTAL1

XTAL2

F

XTAL1

Disable Oscillator

(Powerdown)

XTAL1

F

Disable

PLL

(Powerdown)

PLLEN

XTAL1

1

2F

0

Divide by two

Circuit

Clock

Generators

Phase

Comparator

Phase-locked

Oscillator

Phase-locked Loop

Clock Multiplier

f

Disable Clock Input (Powerdown)

f/2

Clock

Failure

Detection

f/2

Filter

To reset logic

Disable Clocks (Idle, Powerdown)

CPU Clocks (PH1, PH2)

Peripheral Clocks (PH1, PH2)

Programmable

Divider

(CLK1:0)

OSC

0

CLKOUT

1

Disable Clocks (Powerdown)

A5290-01

Figure 2-2. Clock Circuitry (87C196LA, LB Only)

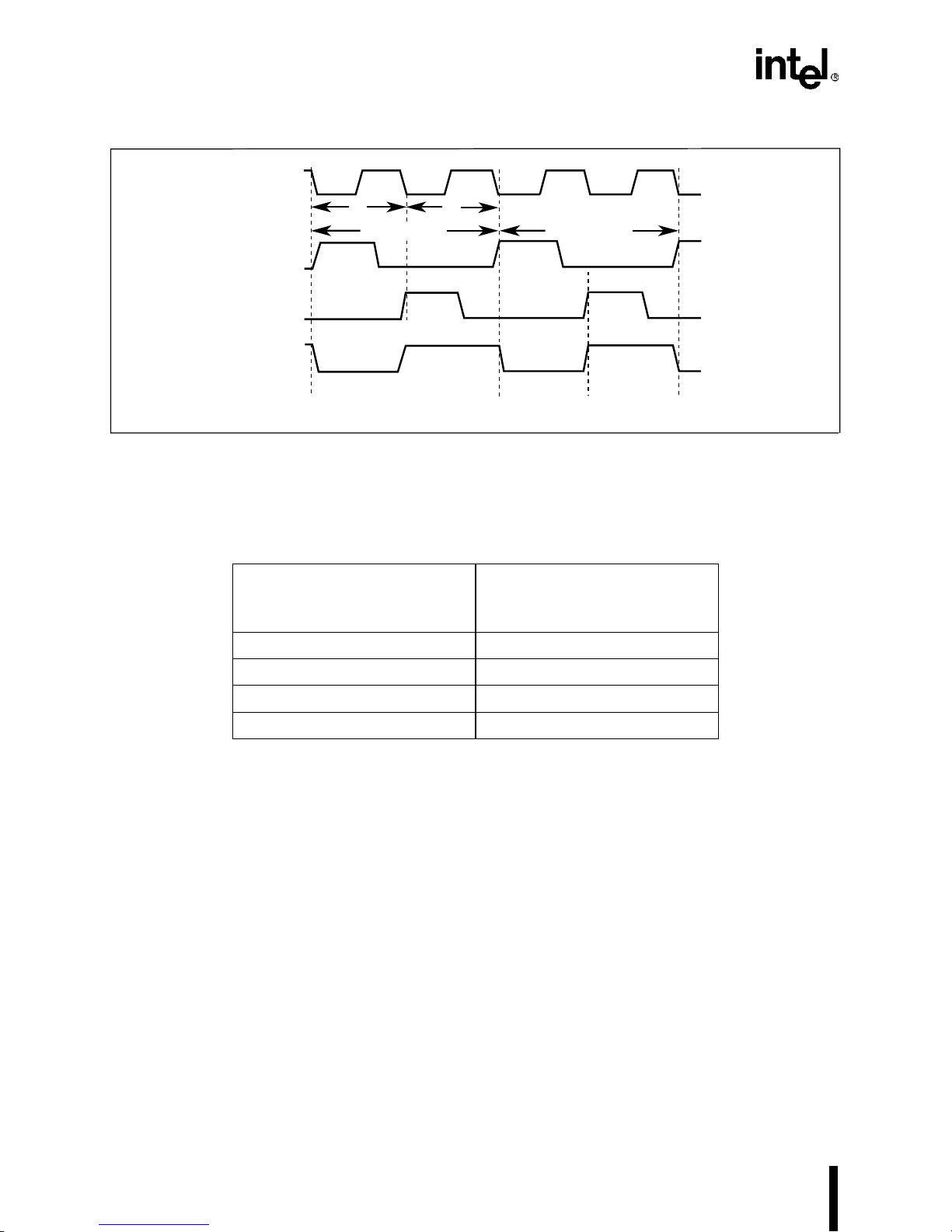

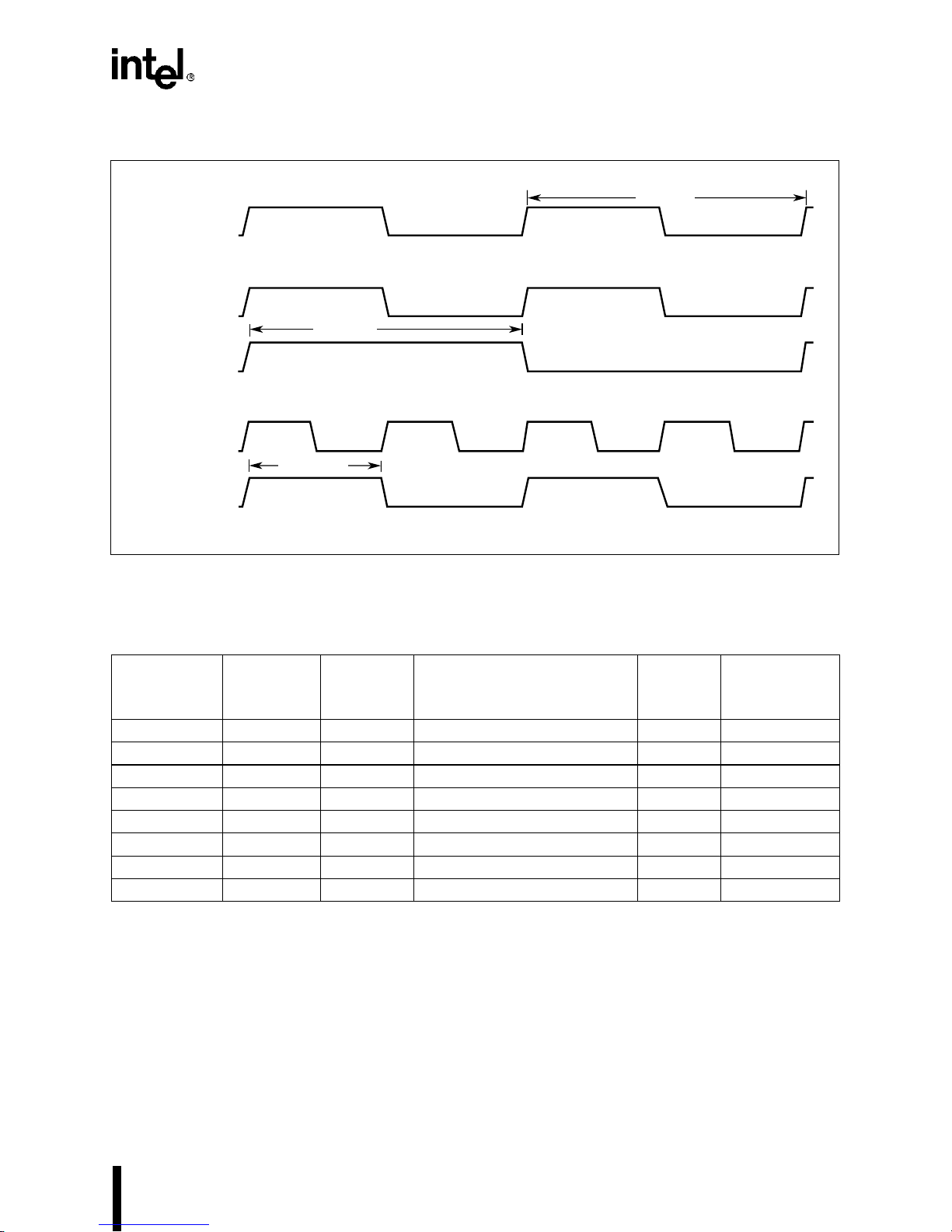

The rising edges of PH1 and PH2 generate the internal CLKOUT signal (Figure 2-3). The clock

circuitry routes separ ate int ernal clock signals t o the CPU and the per ipher als to pr ovid e flexibil ity in power management. It also outputs the CLKOUT signal on the CLKOUT pin. Because of

the complex logic in the clock circuitry, the signal on the CLKOUT pin is a delayed version of

the internal CLKOUT signal. This delay varies with temperature and voltage.

2-3

Page 18

8XC196LX SUPPLEMENT

PH1 (in MHz)

f

2

-- - PH2==

XTAL1

PH1

PH2

CLKOUT

tt

1 State Time

1 State Time

Phase 1 Phase 2

Phase 1 Phase 2

A0805-01

Figure 2-3. Internal Clock Phases (Assumes PLL is Bypassed)

The combined period of phase 1 and phase 2 of the internal CLKOUT signal defines the basic

time unit known as a state time or state. Table 2-2 lists state time durations at various frequencies.

Table 2-2. State Times at Various Frequencies

f

(Frequency Input to the

Divide-by-two Circuit)

8 MHz 250 ns

12 MHz 167 ns

16 MHz 125 ns

20 MHz 100 ns

State Time

The following formulas calculate the frequency of PH1 and PH2, the duration of a state time, and

the duration of a clock period (t).

State Time (in µs)

2

-- -= t

f

1

-- -=

f

Because the device can operate at many frequencies, this manual defines time requirements (such

as instruction execution times) in terms of state times rather than specific measurements.

Datasheets list AC characteristics in terms of clock periods (t; sometimes called T

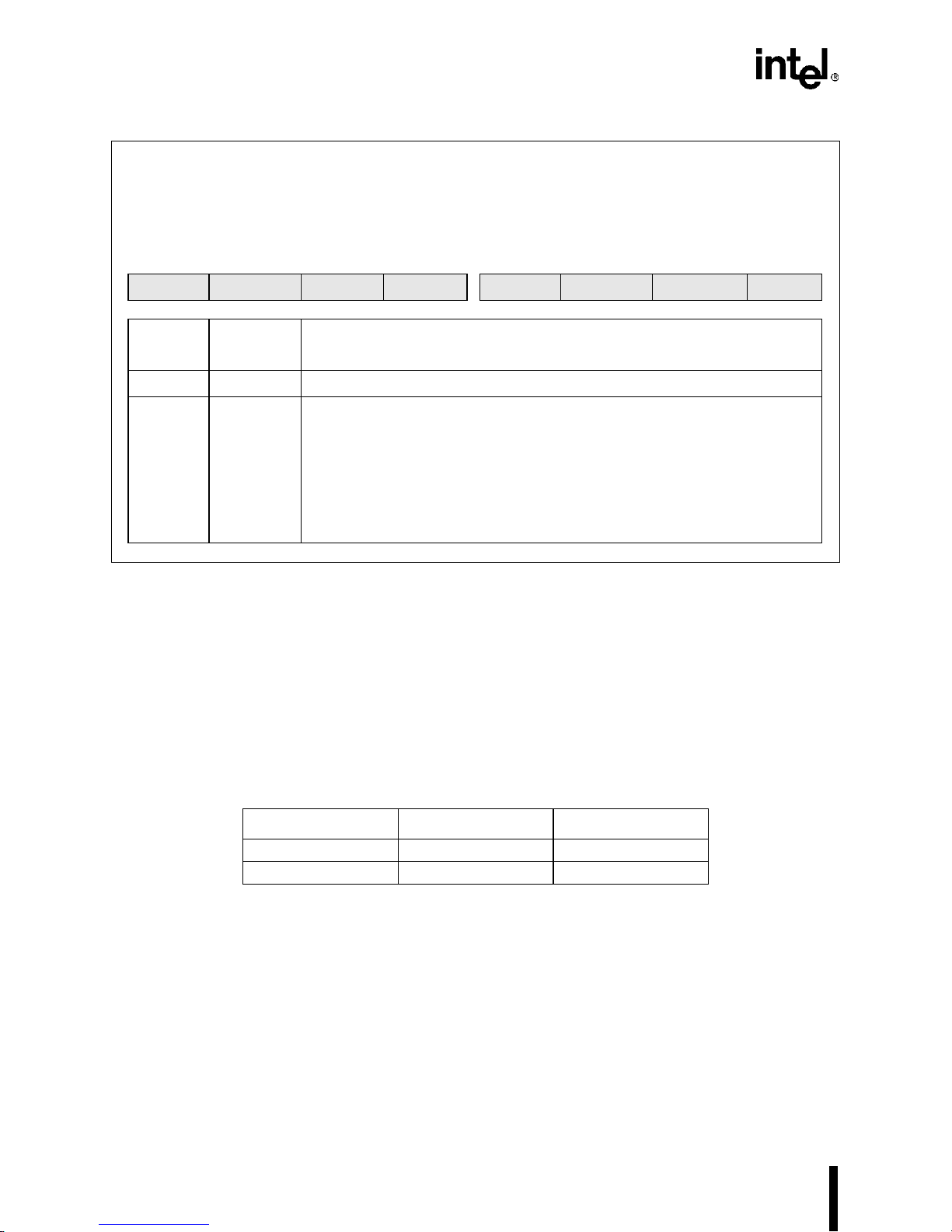

Figure 2-4 illustrates the timing relationships between the input frequency (F

frequency (f), and the CLKOUT signal with each PLLEN pin configuration . Table 2-3 details the

relationships between the input frequency (F

the clock period (t), and state times.

2-4

osc

), the operatin g

XTAL1

), the PLLEN pin, the operating frequency (f),

XTAL1

).

Page 19

XTAL1

(16 MHz)

PLLEN = 0

Internal

CLKOUT

PLLEN = 1

Internal

CLKOUT

ARCHITECTURAL OVERVIEW

T

XHCH

f

t = 62.5ns

f

t = 31.25ns

A3376-01

Figure 2-4. Effect of Clock Mode on Internal CLKOUT Frequency

Table 2-3. Relationships Between Input Frequency, Clock Multiplier, and State Times

F

XTAL1

(Frequency

on XTAL1)

PLLEN Multiplier

(Input Frequency to

the Divide-by-two Circuit)

f

4 MHz 0 1 4 MHz 250 ns 500 ns

8 MHz 0 1 8 MHz 125 ns 250 ns

12 MHz 0 1 12 MHz 83.5 ns 167 ns

16 MHz 0 1 16 MHz 62.5 ns 125 ns

20 MHz 0 1 20 MHz 50 ns 100 ns

4 MHz 1 2 8 MHz 125 ns 250 ns

8 MHz 1 2 16 MHz 62.5 ns 125 ns

10 MHz 1 2 20 MHz 50 ns 100 ns

t

(Clock

Period)

State Time

2.4 EXTERNAL TIMING

You can control the output frequency on the CLKOUT pin by programming two uneraseable

PROM bits. Figure 2-5 illustrates the read-only USFR1, which reflects the state of the unerasable

PROM bits. You can select one of three frequencies: f/2, f/4, or f/8. As Figure 2-2 on page 2-3

shows, the configurable divider accepts the output of the clock generators (f/2) and further divides that frequency to produce the desired output frequ ency . The CLK1:0 bits control the divisor

(divide f/2 by either 1, 2, or 4).

2-5

Page 20

8XC196LX SUPPLEMENT

USFR1 (read only)

The UPROM special-function register 1 (USFR1) reflects the status of unerasable, programmable

read-only memory (UPROM) locations. This read-only register reflects the status of two bits that

control the output frequency on CLKOUT.

7 0

— — — — — — CLK1 CLK0

Bit

Number

7:2 — Reserved.

1:0 CLK1:0 CLKOUT Control

Bit

Mnemonic

Function

These bits reflect the programmed frequency of the CLKOUT signal:

CLK1 CLK0

0 0 divide by 1 (CLKOUT = f/2)

0 1 divide by 2 (CLKOUT = f/4)

1 0 divide by 4 (CLKOUT = f/8)

1 1 divide by 1 (CLKOUT = f/2)

Address:

Reset State:

1FF2H

XXH

Figure 2-5. Unerasable PROM 1 (USFR1) Register (LA, LB Only)

T o pr ogram these bits, write the correct value to the locations show n in Table 2-4 using slav e programming mode. During normal op eration, yo u can determ ine the values of these bits by read ing

the UPROM SFR (Figure 2-5).

You can verify a UPROM bit to make sure it programmed, but you cannot erase it. For this reason, Intel cannot test the bits before shipment. However, Intel does test the features that the UPROM bits enable, so the only und etectable defects are (unlikely ) defects within the UPROM cells

themselves.

Table 2-4. UPROM Programming Values and Locations

T o set this bit Write this value To this location

CLK0 0001H 0768H

CLK1 0002H 0728H

2.5 INTERNAL PERIPHERALS

The internal peripheral modules provide special functions for a variety o f applications. Th is section provides a brief description of the peripherals that differ between the 8XC1 96Lx and the

8XC196Kx fami lies.

2-6

Page 21

ARCHITECTURAL OVERVIEW

2.5.1 I/O Ports

The I/O ports of the 8XC196 Lx are functionall y identical to those of the 8XC196J x. However , o n

the 87C196LA and LB the reset state level of all 41 general-purpose I/O pins has changed from

a weak logic “1” (wk1) to a weak logic “0” (wk0).

2.5.2 Synchronous Serial I/O Port

The synchronous serial I/O (SSIO) port on t he 8XC196Lx has been enhance d, implementing two

new special function registers (SSIO0_CLK and SSIO1_CLK) that allow you to select the operating mode and configure the phase and polarity of the serial clock signals.

2.5.3 Event Processor Array

The 8XC196 Lx’s event processor array (EPA) is functionally identical to that of the 8XC196Jx,

except that it has only two EPA capture/compare chann els without pi ns instead of four. In addition the LD has no compare-only channels.

2.5.4 J1850 Communications Controller

The 87C196LB m icrocontrol ler has a p eripheral not found on the 8XC196Kx microcontrollers or

any other Lx microcontroller, the J1850 peripheral. The J1850 communications controller manages communications between m ultiple network n odes. This integrated p eripheral supports the

10.4 Kb/s VPW (variable pulse-width) medium-speed, class B, in-vehicle network protocol. It

also supports both the standard and in-frame re sponse (IFR) message framing as specified by the

Society of Automotive Engineering (SAE) J1850 (revised May 1994) technical standards.

2.6 DESIGN CONSIDERATIONS

With the exception of a few new multiplexed functions, the 8XC196L x microcontrollers are pin

compatible with the 8 XC196Jx microcontrollers. The 8XC196Jx microcontrollers are 52-lead

versions of 8XC196Kx microcontrollers. For registers that are implemented in both the

8XC196Lx and the 8XC196Jx, configure the 8XC196Lx register as you would for the 8XC196 Jx

unless differences are noted in this supplement.

2-7

Page 22

Page 23

Address Space

3

Page 24

Page 25

CHAPTER 3

ADDRESS SPACE

This chapter describes the differences in the address space of the 8XC196Lx from that of the

8XC196Kx.

3.1 ADDRESS PARTITIONS

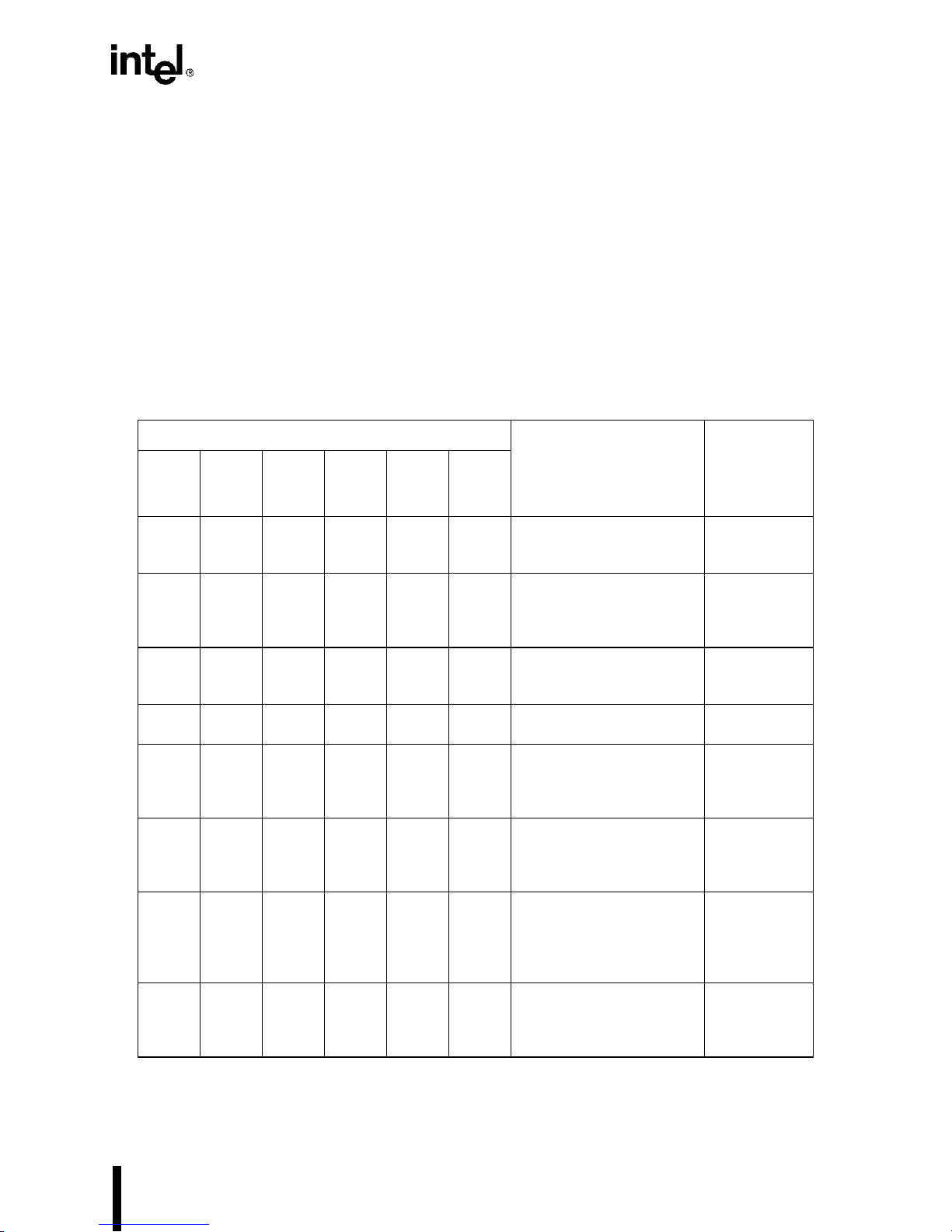

Table 3-1 is an address map of the 8XC196Lx and 8XC196Kx microcontroller family members.

Table 3-1. Address Map

Device and Hex Address Range

Description

CA

FFFF

A000

9FFF

2080

207F

2000

1FFF

1FE0

1FDF

1F00

1EFF

1E00

1DFF

1C00

—————

NOTES:

1. After a reset, the device fetches its first instruction from 2080H.

2. The content or function of these locations may change in future device revisions, in which case

a program that relies on a location in this range might not function properly.

JR, KR

FFFF

6000

5FFF

2080

207F

2000

1FFF

1FE0

1FDF

1F00

—————CAN SFRs

1EFF

1C00

LD

FFFF

6000

5FFF

2080

207F

2000

1FFF

1FE0

1FDF

1F00

1EFF

1C00

LA, LB

FFFF

8000

7FFF

2080

207F

2000

1FFF

1FE0

1FDF

1F00

1EFF

0300

JT, KT

FFFF

A000

9FFF

2080

207F

2000

1FFF

1FE0

1FDF

1F00

1EFF

1C00

JV

FFFF

E000

DFFF

2080

207F

2000

1FFF

1FE0

1FDF

1F00

1EFF

1E00

1DFF

1C00

External device (memory

or I/O) connected to

address/data bus

Program memory

(internal nonvolatile or

external memory); see

Note 1

Special-purpose memory

(internal nonvolatile or

external memory)

Memory-mapped SFRs

Peripheral SFRs

(Includes J1850 SFRs on

87C196LB)

External device (memory

or I/O) connected to

address/data bus;

(future SFR expansion;

see Note 2)

Register RAM

Addressing

Modes

Indirect or

indexed

Indirect or

indexed

Indirect or

indexed

Indirect or

indexed

Indirect,

indexed, or

windowed

direct

Indirect,

indexed, or

windowed

direct

Indirect or

indexed

Indirect,

indexed, or

windowed

direct

3-1

Page 26

8XC196LX SUPPLEMENT

Table 3-1. Address Map (Continued)

Device and Hex Address Range

Description

1BFF

0600

05FF

0400

03FF

0100

00FF

0000

JV

External device (memory

or I/O) connected to

address/data bus

Internal code or data RAM

External device (memory

or I/O) connected to

address/data bus

Upper register file

(general-purpose register

RAM)

Lower register file

(register RAM, stack

pointer, and CPU SFRs)

CA

1BFF

0500

04FF

0400

—

03FF

0100

00FF

0000

NOTES:

1. After a reset, the device fetches its first instruction from 2080H.

2. The content or function of these locations may change in future device revisions, in which case

a program that relies on a location in this range might not function properly.

JR, KR

1BFF

0500

04FF

0400

03FF

0200

01FF

0100

00FF

0000

LD

1BFF

0600

——

05FF

0180

017F

0100

00FF

0000

LA, LB

—

———

02FF

0100

00FF

0000

JT, KT

1BFF

0600

05FF

0400

03FF

0100

00FF

0000

Addressing

Indirect or

indexed

Indirect or

indexed

Indirect or

indexed

Indirect,

indexed, or

windowed

direct

Direct,

indirect, or

indexed

Modes

3.2 REGISTER FILE

Figure 3-1 compares the register file addresses of the 8XC196Lx and 8XC196Kx. The register

file in Figure 3 -1 is divided into an up per regis ter f ile and a lower reg ister file . The u pper reg ister

file consists of general-purpose register RAM. The lower register file contains general-purpose

register RAM along with the stack pointer (SP) and the CPU special-function registers (SFRs).

Table 3-2 lists the register file memory addresses. The RALU accesses the lower register file directly, without the use of the memory controller. It also accesses a windowed location d irectly

(see “Windowing” on page 3-6). The upper register file and the peripheral SFRs can be win-

dowed. Registers in the lower register file and registers being windowed can be accessed with

register-direct addressing.

NOTE

The register file must not contain code. An attempt to execute an instruction

from a location in the register file causes the memory controller to fetch the

instruction from external me mory.

3-2

Page 27

General-purpose

Register RAM

ADDRESS SPACE

Address

03FFH

(CA, JT, JV, KT)

02FFH (LA, LB)

01FFH (JR, KR)

017FH (LD)

Address

03FFH

0100H

00FFH

0000H

Upper

Register File

Lower

Register File

Figure 3-1. Register File Address Map

Table 3-2. Register File Memory Addresses

Device and Hex Address Range

JV CA,JT,KT LA, LB JR, KR LD

1DFF

1C00

03FF

0100

00FF

001A

0019

0018

0017

0000

— — — — Register RAM

03FF

0100

00FF

001A

0019

0018

0017

0000

02FF

0100

00FF

001A

0019

0018

0017

0000

01FF

0100

00FF

001A

0019

0018

0017

0000

017F

0100

00FF

001A

0019

0018

0017

0000

General-purpose

Register RAM

Stack Pointer

CPU SFRs

Description Addressing Modes

Upper register file (register RAM)

Lower register file (register RAM)

Lower register file (stack pointer)

Lower register file (CPU SFRs)

0100H

00FFH

001AH

0019H

0018H

0017H

0000H

A5260-01

Indirect, indexed, or

windowed direct

Indirect, indexed, or

windowed direct

Direct, indirect, or

indexed

Direct, indirect, or

indexed

Direct, indirect, or

indexed

3-3

Page 28

8XC196LX SUPPLEMENT

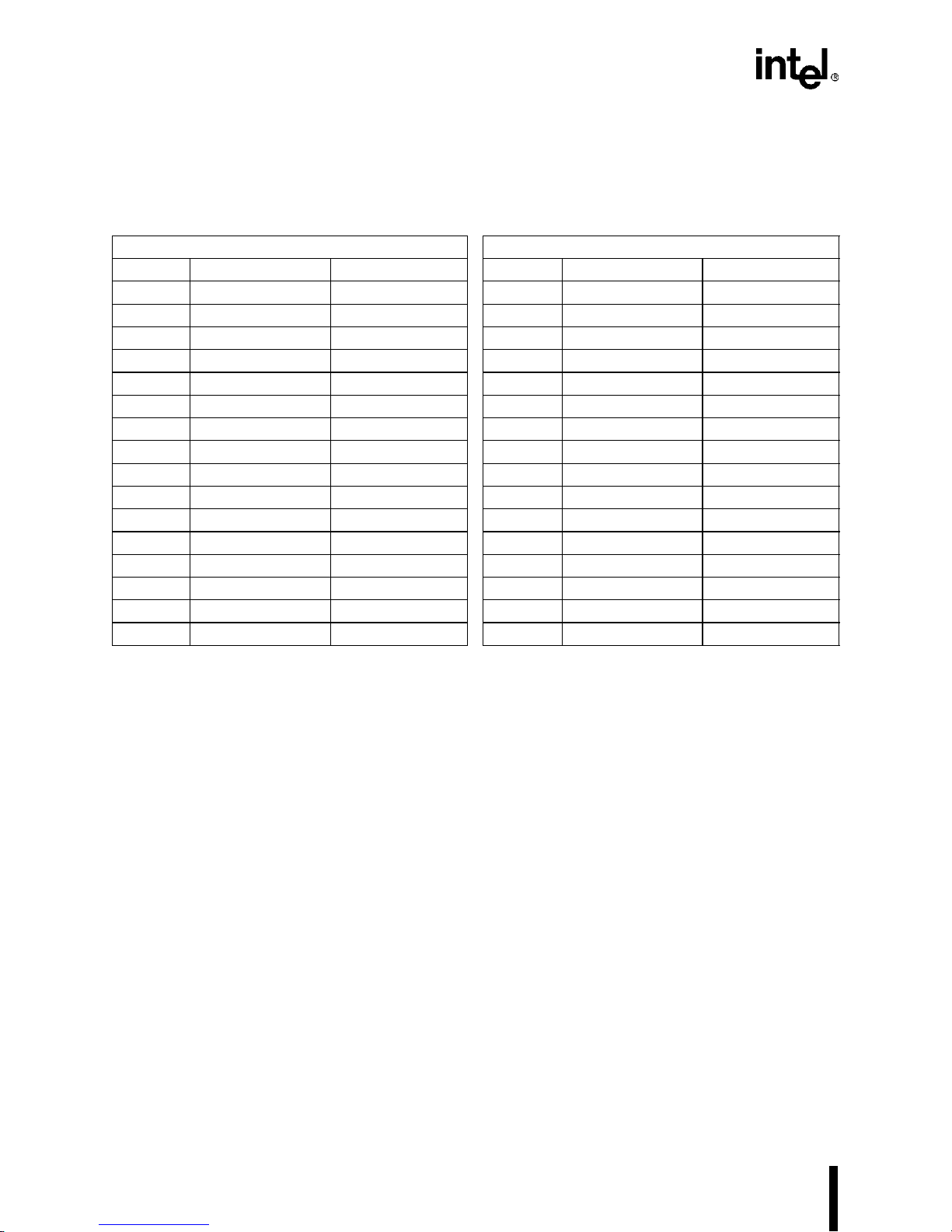

3.3 PERIPHERAL SPECIAL-FUNCTION REGISTERS

T a ble 3- 3 li sts the pe ripheral SFR address es. Hi ghlig hted addr esses are un ique to th e 8XC19 6Lx.

Table 3-3. 8XC196Lx Peripheral SFRs

Ports 3, 4, 5, and UPROM SFRs Ports 0, 1, 2, and 6 SFRs

Address High (Odd) Byte Low (Even) Byte Address High (Odd) Byte Low (Even) Byte

1FFEH P4_PIN P3_PIN 1FDEH Reserved Reserved

1FFCH P4_REG P3_REG 1FDCH Reser ved Reserved

1FFAH SLP_CON SLP_CMD 1FDAH Reserved P0_PIN

1FF8H Reserved SLP_STAT 1FD8H Reserved Reserved

1FF6H P5_PIN USFR 1FD6H P6_PIN P1_PIN

1FF4H P5_REG P34_DRV 1FD4H P6_REG P1_REG

1FF2H P5_DIR USFR1 (LA, LB) 1FD2H P6_DIR P1_DIR

1FF0H P5_MODE Reserved 1FD0H P6_MODE P1_MODE

1FEEH Reserved Reserved 1FCEH P2_PIN Reserved

1FECH Reserved Reserved 1FCCH P2_REG Reserved

1FEAH Reserved Reserved 1FCAH P2_DIR Reserved

1FE8H Reserved Reserved 1FC8H P2_MODE Reserved

1FE6H Reserved Reserved 1FC6H Reserved Reserved

1FE4H Reserved Reserved 1FC4H Reserved Reserved

1FE2H Reserved Reserved 1FC2H Reserved Reserved

1FE0H Reserved Reserved 1FC0H Reserved Reserved

†

Must be addressed as a word.

3-4

Page 29

ADDRESS SPACE

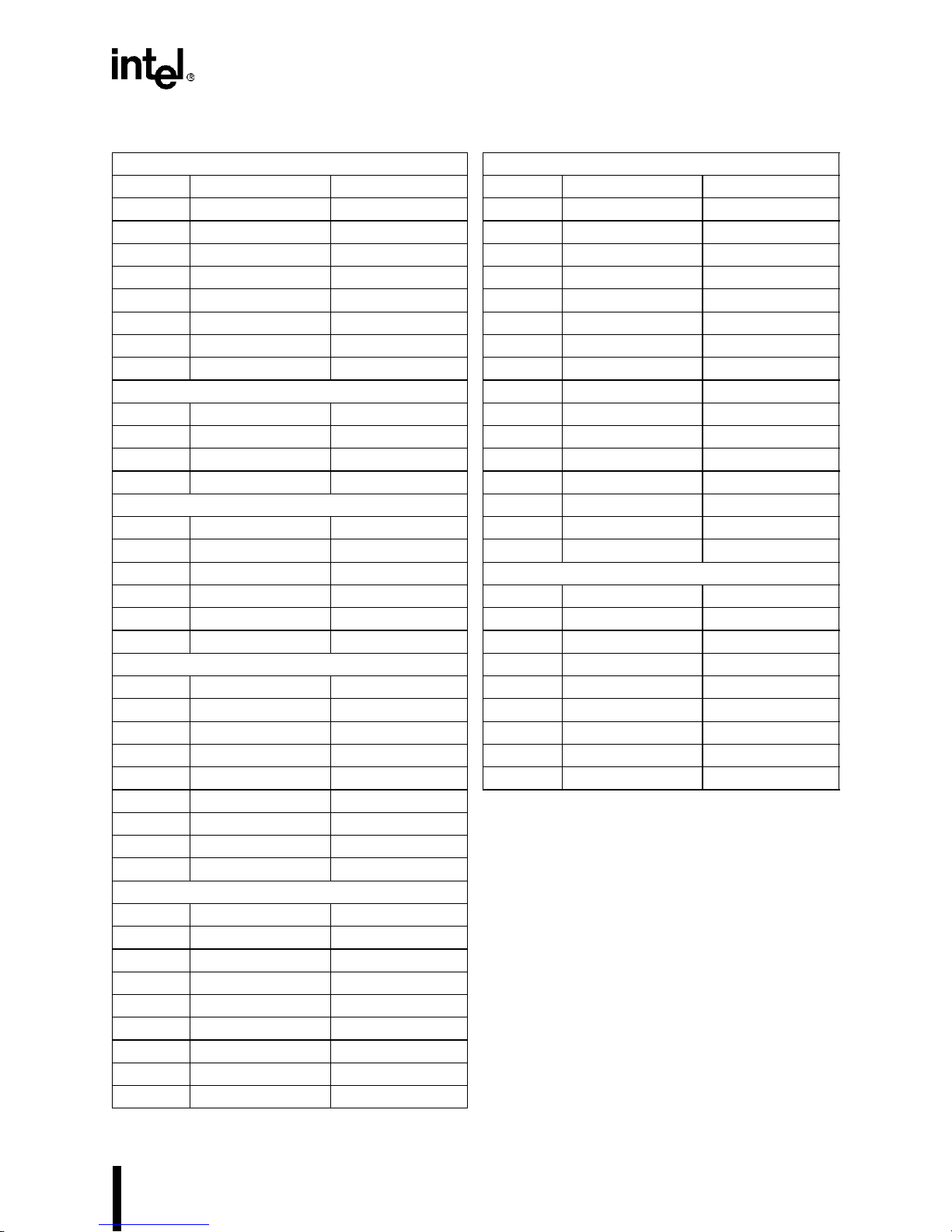

Table 3-3. 8XC196Lx Peripheral SFRs (Continued)

SIO and SSIO SFRs EPA SFRs (Continued)

Address High (Odd) Byte Low (Even) Byte Address High (Odd) Byte Low (Even) Byte

†

1FBEH R eserved Reserved

1FBCH SP_BAUD (H) SP_BAUD (L) 1F7CH Reserved EPA7_CON

1FBAH SP_CON SBUF_TX

1FB8H SP_STATUS S BUF_RX 1F78H Reserved EPA6_CON

1FB6H SSIO1_CLK Reserved

1FB4H SSIO0_CLK SSIO_BAUD 1F74H Reserved EPA5_CON

1FB2H SSIO1_CON SSIO1_BUF

1FB0H SSIO0_CON SSIO0_BUF 1F70H Reserved EPA4_CON

A/D SFRs (LA, LB Only)

Address High (Odd) Byte Low (Even) Byte

1FAEH AD_TIME AD_TEST

1FACH Reserved AD_COMMAND 1F68H Reserved EPA2_CON

1FAAH AD_RESULT (H) AD_RESULT (L)

EPA Interrupt SFRs

Address High (Odd) Byte Low (Even) Byte

1FA8H Reserved E PAIPV 1F60H Reserved EPA0_CON

1FA6H Reserved EPA_PEND1 J1850 SFRs (LB Only)

1FA4H Reserved EPA_MASK1 Address High (Odd) Byte Low (Even) Byte

†

1FA2H EPA_PEND (H) EPA_PEND (L) 1F5EH Reserved Reserved

†

1FA0H EPA_MASK (H) EPA_MASK (L) 1F5CH Reserved Reserv ed

Timer 1, Timer 2, and EPA SFRs 1F5AH Reserved Reserv ed

Address High (Odd) Byte Low (Even) Byte 1F58H Reserved J_DLY

†

1F9EH TIMER2 (H) TIMER2 (L) 1F56H Reserved Reserved

1F9CH Reserved T2CONTROL 1F54H Reserved J_CFG

†

1F9AH TIMER1 (H) TIMER1 (L) 1F52H J_STAT J_RX

1F98H Reserved T1CONTROL 1F50H J_CMD J_TX

1F96H Reserved Reserved

1F94H Reserved Reserved

1F92H Reserved RST_SRC

1F90H Reserved Reserved

EPA SFRs

Address High (Odd) Byte Low (Even) Byte

†

1F8EH COMP1_TIME (H) COMP1_TIME (L)

1F8CH Reserved COMP1_CON

†

1F8AH COMP0_TIME (H) COMP0_TIME (L)

1F88H Reserved COMP0_CON

†

1F86H EPA9_TIME (H) EPA9_TIME (L)

1F84H Reserved EPA9_CON

†

1F82H EPA8_TIME (H) EPA8_TIME (L)

1F80H Reserved EPA8_CON

†

Must be addressed as a word.

1F7EH EPA7_TIME (H) EPA7_TIME (L)

†

1F7AH EPA6_TIME (H) EPA6_TIME (L)

†

1F76H EPA5_TIME (H) EPA5_TIME (L)

†

1F72H EPA4_TIME (H) EPA4_TIME (L)

†

1F6EH EPA3_TIME (H) EPA3_TIME (L)

†

1F6CH EPA3_CON (H) EPA3_CON (L)

†

1F6AH EPA2_TIME (H) EPA2_TIME (L)

†

1F66H EPA1_TIME (H) EPA1_TIME (L)

†

1F64H EPA1_CON (H) EPA1_CON (L)

†

1F62H EPA0_TIME (H) EPA0_TIME (L)

3-5

Page 30

8XC196LX SUPPLEMENT

3.4 WINDOWING

Windowing maps a segment of higher memory (the upper register file or peripheral SFRs) into

the lower register file. The window selection register (WSR) selects a 32-, 64- or 128-byte segment of higher memory to be windowed into the top of the lower register file space. Table 3-4

lists the WSR values for windowing the upper register file for both the 8XC196Lx and

8XC196Kx.

Table 3-4. Windows

Base

Address

Peripheral SFRs

1FE0H 7FH (Note)

1FC0H 7EH

1FA0H 7DH

1F60H 7BH

1F40H 7AH

1F20H 79H

CAN Peripheral SFRs (87C196CA Only)

1EE0H 77H

1EC0H 76H

1EA0H 75H

1E60H 73H

1E40H 72H

1E20H 71H

Register RAM (87C196JV Only)

WSR Value

for 32-byte Window

(00E0–00FFH)

WSR Value

for 64-byte Window

(00C0–00FFH)

3FH (Note)

3EH1F80H 7CH

3DH

3CH1F00H 78H

3BH

3AH1E80H 74H

39H

38H1E00H 70H

WSR Value for

128-byte

Window

(0080–00FFH)

1FH (Note)

1EH

1DH

1CH

1DE0H 6FH

1DC0H 6EH

1DA0H 6DH

1D60H 6BH

1D40H 6AH

1D20H 69H

NOTE: Locations 1FE0–1FFFH contain memory-mapped SFRs that cannot be accessed through a

window. Reading these locations through a window returns FFH; writing these locations

through a window has no effect.

3-6

37H

36H1D80H 6CH

35H

34H1D00H 68H

1BH

1AH

Page 31

Table 3-4. Windows (Continued)

ADDRESS SPACE

Base

Address

Register RAM (87C196JV Only; Continued)

1CE0H 67H

1CC0H 66H

1CA0H 65H

1C60H 63H

1C40H 62H

1C20H 61H

Upper Register File (CA, JT, JV, KT)

03E0H 5FH

03C0H 5EH

03A0H 5DH

0360H 5BH

0340H 5AH

0320H 59H

WSR Value

for 32-byte Window

(00E0–00FFH)

WSR Value

for 64-byte Window

(00C0–00FFH)

33H

32H1C80H 64H

31H

30H1C00H 60H

2FH

2EH0380H 5CH

2DH

2CH0300H 58H

WSR Value for

128-byte

Window

(0080–00FFH)

19H

18H

17H

16H

Upper Register File (CA, JT, JV, KT, LA, LB)

02E0H 57H

02C0H 56H

02A0H 55H

0260H 53H

0240H 52H

0220H 51H

Upper Register File (CA, JR, JT, JV, KR, KT, LA, LB)

01E0H 4FH

01C0H 4EH

01A0H 4DH

NOTE: Locations 1FE0–1FFFH contain memory-mapped SFRs that cannot be accessed through a

window. Reading these locations through a window returns FFH; writing these locations

through a window has no effect.

2BH

2AH0280H 5 4H

29H

28H0200H 50H

27H

26H0180H 4CH

15H

14H

13H

3-7

Page 32

8XC196LX SUPPLEMENT

Table 3-4. Windows (Continued)

Base

Address

Upper Register File (CA, JR, JT, JV, KR, KT, LA, LB, LD)

0160H 4BH

0140H 4AH

0120H 49H

NOTE: Locations 1FE0–1FFFH contain memory-mapped SFRs that cannot be accessed through a

window. Reading these locations through a window returns FFH; writing these locations

through a window has no effect.

WSR Value

for 32-byte Window

(00E0–00FFH)

WSR Value

for 64-byte Window

(00C0–00FFH)

25H

24H0100H 48H

WSR Value for

128-byte

Window

(0080–00FFH)

12H

3-8

Page 33

Standard and PTS

Interrupts

4

Page 34

Page 35

CHAPTER 4

STANDARD AND PTS INTERRUPTS

The interrupt structur e of the 8XC196Lx is the same as that of the 8XC 196Jx. The only diffe rence

is that the slave port interrupts (INT08:06) now support the J1850 controller peripheral.

4.1 INTERRUPT SOURCES, VECTORS, AND PRIORITIES

Table 4- 1 lists the 8XC196Lx’s interrupts sources, default priorities (30 is highest and 0 is lowest), and vector addresses.

4-1

Page 36

8XC196LX SUPPLEMENT

Table 4-1. Interrupt Sources, Vectors, and Priorities

Interrupt Source Mnemonic

Nonmaskable Interrupt NMI

Interrupt Controller

Service

†

Name

†

INT15 203EH 30 ———

Vector

Priority

PTS Servi ce

Name

Vector

EXTINT Pin EXTINT INT14 203CH 14 PTS14 205CH 29

Reserved — INT13 203AH 13 PTS13 205AH 28

SIO Receive RI INT12 2038H 12 PTS12 2058H 27

SIO Transmit TI INT11 2036H 11 PTS11 2056H 26

SSIO Channel 1 Transfer SSIO1 INT10 2034H 10 PTS10 2054H 25

SSIO Channel 0 Transfer SSIO0 INT09 2032H 09 PTS09 2052H 24

J1850 Status (LB only) J1850ST INT08 2030H 08 PTS08 2050H 23

Reserved (LA, LD) — INT08 2030H 08 PTS08 2050H 23

Unimplemented Opcode — — 2012H — — — —

Software TRAP Instruction — — 2010H — — — —

J1850 Receive (LB only) J1850RX INT07 200EH 07 PTS07 204EH 22

Reserved (LA, LD) — INT07 200EH 07 PTS07 204EH 22

J1850 Transmit (LB only) J1850TX INT06 200CH 06 PTS06 204CH 21

Reserved (LA, LD) — INT06 200CH 06 PTS06 204CH 21

A/D Conv. Complete (LA, LB) AD_DONE INT05 200AH 05 PTS05 204AH 20

Reserved (LD) — INT05 200AH 05 PTS05 204AH 20

EPA Capture/Compare 0 EPA0 INT04 2008H 04 PTS04 2048H 19

EPA Capture/Compare 1 EPA1 INT03 2006H 03 PTS03 2046H 18

EPA Capture/Compare 2 EPA2 INT02 2004H 02 PTS02 2044H 17

EPA Capture/Compare 3 EPA3 INT01 2002H 01 PTS01 2042H 16

EPA Capture/Compare 6–9,

x

INT00 2000H 00 PTS00 2040H 15

††

EPA

EPA 0–3, 8–9 Overrun,

†††

EPA Compare 0–1

,

Timer 1 Overflow, &

Timer 2 Overflow

†

The NMI pin is not bonded out on the 8XC196Lx. To protect against glitches, create a dummy interrupt

service routine that contains a RET instruction.

††

These interrupts are individually prioritized in the EPAIPV register. Read the EPA pending registers

(EPA_PEND and EPA_PE ND1) to determine which source caused the interrupt.

†††

87C196LA, LB only. The 83C196LD has no EPA compare-only channels.

Priority

4.2 INTERRUPT REGISTERS

This section describes the changes in the interrupt register bit definitions for the 8XC196Lx family .

4-2

Page 37

STANDARD AND PTS INTERRUPTS

4.2.1 Interrupt Mask Registers

Figures 4-1 and 4-2 illustrate the interrupt mask registers for the 8XC196Lx microcontrollers.

INT_MASK

Address:

Reset State:

0008H

00H

The interrupt mask (INT_MASK) register enables or disables (masks) individual interrupt requests.

(The EI and DI instructions enable and disable servicing of all maskable interrupts.) INT_MASK is the

low byte of the processor status word (PSW). PUSHF or PUSHA saves the contents of this register

onto the stack and then clears this register. Interrupt calls cannot occur immediately following a push

instruction. POPF or POPA restores it.

7 0

LA

— — AD EPA0 EPA1 EPA2 EPA3 EPA

x

7 0

LB

J1850RX J1850TX AD EPA0 EPA1 EPA2 EPA3 EPA

x

7 0

LD

Bit

Number

†

7:0

— — — EPA0 EPA1 EPA2 EPA3 EPA

Function

Setting a bit enables the corresponding interrupt.

x

Bit Mnemonic Interrupt Description

J1850RX J1850 Receive (LB only)

J1850TX J1850 Transmit (LB only)

AD A/D Conversion Complete (LA, LB)

EPA0 EPA Capture/Compare Channel 0

EPA1 EPA Capture/Compare Channel 1

EPA2 EPA Capture/Compare Channel 2

EPA3 EPA Capture/Compare Channel 3

††

x

EPA

††

EPA 6–9 capture/compare channel events, EPA 0–1 compare channel events

Shared EPA interrupt

†††

, EPA

0–3 and 8–9 capture/compare overruns, and timer overflows can generate this

x

multiplexed interrupt. The EPA mask and pending registers decode the EPA

interrupt.

Write the EPA mask registers to enable the interrupt sources; read the EPA pending

registers to determine which source caused the interrupt.

†††

87C196LA, LB only.

†

Bits 6–7 are reserved on the 87C196LA, and bits 5–7 are reserved on the 83C196LD. For

compatibility with future devices, write zeros to these bits.

Figure 4-1. Interrupt Mask (INT_MASK) Register

4-3

Page 38

8XC196LX SUPPLEMENT

INT_MASK1

Address:

Reset State:

0013H

00H

The interrupt mask 1 (INT_MASK1) register enables or disables (masks) individual interrupt requests.

(The EI and DI instructions enable and disable servicing of all maskable interrupts.) INT_MASK1 can

be read from or written to as a byte register. PUSHA saves this register on the stack and POPA

restores it.

7 0

LB

NMI EXTINT — RI TI SSIO1 SSIO0 J1850ST

7 0

LA, LD

Bit

Number

†

7:0

NMI EXTINT — RI TI SSIO1 SSIO0 —

Function

Setting a bit enables the corresponding interrupt.

Bit Mnemonic Interrupt Description

NMI

††

Nonmaskable Interrupt

EXTINT EXTINT Pin

Reserved —

RI SIO Receive

TI SIO Transmit

SSIO1 SSIO1 Transfer

SSIO0 SSIO0 Transfer

J1850ST J1850 Status (LB only)

††

NMI is always enabled. This nonfunctional mask bit exists for design symmetry with the

INT_PEND1 register. Always write zero to this bit.

†

Bit 5 is reserved on the 8XC196Lx devices, and bit 0 is reserved on the 87C196LA and 83C196LD.

For compatibility with future devices, always write zeros to these bits.

Figure 4-2. Interrupt Mask 1 (INT_MASK1) Register

4.2.2 Interrupt Pending Registers

Figures 4-3 and 4-4 illustrate the interrupt pending registers for the 8XC196Lx microcontrollers.

4-4

Page 39

STANDARD AND PTS INTERRUPTS

INT_PEND

Address:

Reset State:

0009H

00H

When hardware detects an interrupt request, it sets the corresponding bit in the interrupt pending

(INT_PEND or INT_PEND1) registers. When the vector is taken, the hardware clears the pending bit.

Software can generate an interrupt by setting the corresponding interrupt pending bit.

7 0

LA

— — AD EPA0 EPA1 EPA2 EPA3 EPA

x

7 0

LB

J1850RX J1850TX AD EPA0 EPA1 EPA2 EPA3 EPA

x

7 0

LD

Bit

Number

†

7:0

— — — EPA0 EPA1 EPA2 EPA3 EPA

Function

Any set bit indicates that the corresponding interrupt is pending. The interrupt bit is cleared

x

when processing transfers to the corresponding interrupt vector.

Bit Mnemonic Interrupt Description

J1850RX J1850 Receive (LB only)

J1850TX J1850 Transmit (LB only)

AD A/D Conversion Complete (LA, LB)

EP A0 EPA Capture/Compare Channel 0

EP A1 EPA Capture/Compare Channel 1

EP A2 EPA Capture/Compare Channel 2

EP A3 EPA Capture/Compare Channel 3

††

x

EPA

††

EPA 6–9 capture/compare channel events, EPA 0–1 compare channel events

Shared EPA Interrupt

†††

, EPA

0–3 and 8–9 capture/compare overruns, and timer overflows can generate this shared

interrupt. Write the EPA mask registersto enable the interrupt sources; read the EPA

pending registers to determine which source caused the interrupt.

†††

87C196LA, LB only.

†

Bits 6–7 are reserved on the 87C196LA, and bits 5–7 are reserved on the 83C196LD. For

compatibility with future devices, write zeros to these bits.

Figure 4-3. Interrupt Pending (INT_PEND) Register

4-5

Page 40

8XC196LX SUPPLEMENT

INT_PEND1

When hardware detects an interrupt request, it sets the corresponding bit in the interrupt pending

(INT_PEND or INT_PEND1) registers. When the vector is taken, the hardware clears the pending bit.

Software can generate an interrupt by setting the corresponding interrupt pending bit.

7 0

LB

LA, LD

Bit

Number

†

7:0

†

Bit 5 is reserved on the 8XC196Lx devices and bit 0 is reserved on the 87C196LA and 83C196LD.

For compatibility with future devices, always write zeros to these bits.

NMI EXTINT — RI TI SSIO1 SSIO0 J1850ST

7 0

NMI EXTINT — RI TI SSIO1 SSIO0 —

Function

Any set bit indicates that the corresponding interrupt is pending. The interrupt bit is cleared

when processing transfers to the corresponding interrupt vector.

Bit Mnemonic Interrupt Description

NMI Nonmaskable Interrupt

EXTINT EXTINT Pin

Reserved —

RI SIO Receive

TI SIO Transmit

SSIO1 SSIO 1 Transfer

SSIO0 SSIO 0 Transfer

J1850ST J1850 Status (LB only)

Address:

Reset State:

0012H

00H

Figure 4-4. Interrupt Pending 1 (INT_PEND1) Register

4.2.3 Peripheral Transaction Server Registers

Figures 4-5 and 4-6 illustrate the PTS interrupt select and service registers for the 8XC196Lx microcontrollers.

4-6

Page 41

STANDARD AND PTS INTERRUPTS

PTSSEL

Address:

Reset State:

0004H

0000H

The PTS select (PTSSEL) register selects either a PTS microcode routine or a standard interrupt

service routine for each interrupt request. Setting a bit selects a PTS microcode routine; clearing a bit

selects a standard interrupt service routine. In PTS modes that use the PTSCOUNT register, hardware

clears the corresponding PTSSEL bit when PTSCOUNT reaches zero. The end-of-PTS interrupt service

routine must reset the PTSSEL bit to re-enable the PTS channel.

15 8

LA

— EXTINT — RI TI SSIO1 SSIO0

—

7 0

— — AD EPA0 EPA1 EPA2 EPA3 EPA

x

15 8

LB

— EXTINT — RI TI SSIO1 SSIO0

J1850ST

7 0

J1850RX J1850TX AD EPA0 EPA1 EPA2 EPA3 EPA

x

15 8

LD

— EXTINT — RI TI SSIO1 SSIO0 —

7 0

— — — EPA0 EPA1 EPA2 EPA3 EPA

x

Bit

Number

†

14:0

Setting a bit causes the corresponding interrupt to be handled by a PTS microcode routine.

Function

The PTS interrupt vector locations are as follows:

Bit Mnemonic Interrupt PTS Vector

EXTINT EXTINT pin 205 CH

Reserved

†

— 205AH

RI SIO Receive 2058H

TI SIO Transmit 2056H

SSIO1 SSIO 1 Transfer 2054H

SSIO0 SSIO 0 Transfer 2052H

J1850ST (LB) J1850 Status 2050H

J1850RX(LB) J1850 Receive 204EH

J1850TX(LB) J1850 Transmit 204CH

AD(LA, LB) A/D Conversion Complete 204AH

EP A0 EPA Capture/Compare Channel 0 2048H

EP A1 EPA Capture/Compare Channel 1 2046H

EP A2 EPA Capture/Compare Channel 2 2044H

EP A3 EPA Capture/Compare Channel 3 2042H

††

x

EPA

††

PTS service is not useful for shared interrupts because the PTS cannot readily

Multiplexed EPA 2040H

determine the source of these interrupts.

†

Bit 13 is reserved on the 8XC196Lx devices and bits 6–8 are reserved on the 87C196LA and

83C196LD. For compatibility with future devices, write zeros to these bits.

Figure 4-5. PTS Select (PTSSEL) Register

4-7

Page 42

8XC196LX SUPPLEMENT

PTSSRV

Address:

Reset State:

0006H

0000H

The PTS service (PTSSRV) register is used by the hardware to indicate that the final PTS interrupt has

been serviced by the PTS routine. When PTSCOUNT reaches zero, hardware clears the corresponding

PTSSEL bit and sets the PTSSRV bit, which requests the end-of-PTS interrupt. When the end-of-PTS

interrupt is called, hardware clears the PTSSRV bit. The end-of-PTS interrupt service routine must set

the PTSSEL bit to re-enable the PTS channel.

15 8

LA

— EXTINT — RI TI SSIO1 SSIO0

—

7 0

— — AD EPA0 EPA1 EPA2 EPA3 EPA

x

15 8

LB

— EXTINT — RI TI SSIO1 SSIO0

J1850ST

7 0

J1850RX J1850TX AD EPA0 EPA1 EPA2 EPA3 EPA

x

15 8

LD

— EXTINT — RI TI SSIO1 SSIO0 —

7 0

— — — EPA0 EPA1 EPA2 EPA3 EPA

x

Bits Function

14:0

†

A bit is set by hardware to request an end-of-PTS interrupt for the corresponding interrupt

through its standard interrupt vector.

The standard interrupt vector locations are as follows:

Bit Mnemonic Interrupt Standard Vector

EXTINT EXTINT pin 203 CH

Reserved

†

— 203AH

RI SIO Receive 2038H

TI SIO Transmit 2036H

SSIO1 SSIO 1 Transfer 2034H

SSIO0 SSIO 0 Transfer 2032H

J1850ST (LB) J1850 Status 2030H

J1850RX (LB) J1850 Receive 202EH

J1850TX (LB) J1850 Transmit 202CH

AD (LA, LB) A/D Conversion Complete 202AH

EP A0 EPA Capture/Compare Channel 0 2028H

EP A1 EPA Capture/Compare Channel 1 2026H

EP A2 EPA Capture/Compare Channel 2 2024H

EP A3 EPA Capture/Compare Channel 3 2022H

††

x

EPA

††

PTS service is not useful for shared interrupts because the PTS cannot readily

Multiplexed EPA 2020H

determine the source of these interrupts.

†

Bit 13 is reserved on the 8XC196Lx devices and bits 6–8 are reserved on the 87C196LA and

83C196LD. For compatibility with future devices, write zeros to these bits.

Figure 4-6. PTS Service (PTSSRV) Register

4-8

Page 43

I/O Ports

5

Page 44

Page 45

CHAPTER 5

I/O PORTS

The I/O ports of the 8XC196 Lx are functionall y identical to those of the 8XC196J x. However , o n

the 87C196LA and LB, the reset state level of all 41 general-purpose I/O pins has changed from

a weak logic “1” (wk1) to a weak logic “0” (wk0). This chapter outlines the diff erences between

the 87C196LA, LB and the 8XC196Kx controllers.

5.1 I/O PORTS OVERVIEW

Table 5-1 provides an overview of the 8XC196Lx and 8XC196Kx I/O ports.

Table 5-1. Microcontroller Ports

Port Pins Type

x

)

Port 0

Port 1

Port 2

Port 3 8 Memory mapped

Port 4 8 Memory mapped

Port 5

Port 6

8 (K

6 (CA, J

x

)

8 (K

4 (CA, J

x

)

8 (K

6 (CA, J

x

)

8 (K

3 (CA, J

x

)

8 (K

6 (CA, J

x, Lx

x, Lx

x, Lx

x, Lx

x, Lx

Standard Input-only

)

Standard

)

Standard

)

Memory mapped

)

Standard

)

Configuration

Options

Complementary

Open-drain

Complementary

Open-drain

Complementary

Open-drain

Complementary

Open-drain

Complementary

Open-drain

Complementary

Open-drain

Associated Peripheral or

System Function

A/D converter

(not supported on LD)

EPA and timers

J1850 (LB only), SIO,

interrupts, bus control, clock

gen.

Address/data bus

Address/data bus

Bus control, slave port

EPA, SSIO

5.2 INTERNAL STRUCTURE FOR PORTS 1, 2, 5, AND 6 (BIDIRECTIONAL

PORTS)

Figure 5-1 shows the logic for driving the output transistors, Q1 and Q2. Consult the datasheet

for specifications on the amount of current that each port can source or sink.

In I/O mode (selected by clearing a port mode register bit), the port data output and the port direction registers are input to the multiplexers. These signals combine to drive the gates of Q1 and

Q2 so that the output is high, low, or high impedance.

In special-function mode (selected by setting a port mode register bit), SFDIR and SFDATA are

input to the multiplexers. These signals combine to drive the gates of Q1 and Q2 so that the output

is high, low, or high impedance. Special-function output signals clear SFDIR; special-function

5-1

Page 46

8XC196LX SUPPLEMENT

input signals set SFD IR. Even if a pi n is to be u sed in special-func tion m ode, you must s till in itialize the pin as an input or output by writing to the port direction register.

Resistor R1 provides ESD protection for the pin. Input signals are buffered. The standard ports

use Schmitt-triggered buffers for improved noise immu nity. Port 5 uses a standa rd input buffer

because of the high speeds required for bu s control functions. The signals are latched into the port

pin register sample latch and output onto the internal bus when the port pin register is read.

The falling edge of RESET# turns on transistor Q3, which remains on for about 300 ns, causing

the pin to change rapidly to its reset state. The active-low level of RESET# turns on transistor Q4,

which weakly holds the pin low . Q4 remains on, weakly holding the pin low, until your software

writes to the port mode register.

NOTE

P2.7 is an exception. After reset, P2.7 carries the CLKOUT signal (half the

crystal input frequency) rather than being held low. When CLKOUT is

selected, it is always a complementary output.

5-2

Page 47

I/O PORTS

Internal Bus

Px_REG

SFDATA

Px_DRV

SFDIR

Px_MODE

Read Port

0

1

0

1

Sample

Latch

Px_PIN

LE

PH1 Clock

V

CC

Q1

I/O Pin

Q2

RESET#

Buffer

DQ

V

SS

150Ω to 200Ω

R1

Medium

Pullup

Q3

V

SS

Weak

Pullup

Q4

V

SS

A5265-01

RESET#

300ns Delay

RESET#

Any Write to Px_MODE

R

Q

S

Figure 5-1. Ports 1, 2, 5, and 6 Internal Structure (87C196LA, LB Only)

5.2.1 Configuring Ports 1, 2, 5, and 6 (Bidirectional Ports)

Using the port mode register, you can individually configure each pin for port 1, 2, 5, and 6 to

operate either as a general-purpose I/O signal (I/O mode) or as a special-fu nction sig nal (specialfunction mode). In either mode, three configurations are possible: complementary output, high-

5-3

Page 48

8XC196LX SUPPLEMENT

impedance input, or open-drain output. The p ort direction an d data outpu t registers sel ect the configuration for each pin. Complementary output means that the microcontroller drives the signal

high or low. High-impedance input means that the microcontroller floats the signal. Open-drain

output means that the microcontroller driv es the signal low or floats it. For I/O mode, the port

data output register determines whether the microcontroller drives the signal hi gh, drives it low,

or floats it. For special-function mode, the on-chip peripheral or system function determines

whether the microcontroller drives the signal high or low for complementary outputs.

The pins for por ts 1, 2, 5, and 6 are weakly pulled low during an d after reset. Initializi ng t he pi n s

by writing to the port mode register turns off the weak pull-downs. To ensure that the ports are

initialized correctly, follow this suggested initialization sequence:

1. Write to Px_DIR to configure the individual pins. Clearing a bit configures a pin as a

complementary output. Setting a bit configures a pin as a high-impedance input or opendrain output.

2. Write to Px_MODE to select either I/O or special-function mode. Writing to Px_MODE

(regardless of the value written) turns off the weak pull-downs. Even if the entire port is to

be used as I/O (its default configuration after reset), you must write to P x_MODE to

ensure that the weak pull-downs are turned off.

3. Write to Px_REG.

For complementary output configurations:

In I/O mode, write the data that is to be driven by the pins to the corresponding Px_REG

bits. In special-function mode, the value is immaterial because the on-chip peripheral or

system function controls the pin. However, you must still write to Px_REG to initialize the

pin.

For high-impedance input or open-drain output configurations:

In I/O mode, write to Px_REG to either float the pin, making it available as a high

impedance input, or pull it low. Setting the corresponding Px_REG bit floats the pin;

clearing the corresponding Px_REG bit pulls the pin low. In special-function mode, if the

on-chip peripheral uses the pin as an input signa l, you must set the cor responding P x_REG

bit so that the pin can be driven externally. If the on-chip peripheral uses the pin as an

output signal, the value of the corresponding Px_REG bit is immaterial because the onchip peripheral or system function controls the pin. However, you must still write to

Px_REG to initialize the pin.

5.2.2 Special Bidirectional Port Considerations

This section outlines special cons ideration for using the pins of port s 1, 2, 5, and 6.

1. After reset, your software must configure the device to match the external system. This

accomplished by writing appropriate configuration data into Px_MODE. Writing to

Px_MODE not only configures the pins but also turns off the transistor that weak ly holds

the pins low. For this reason, even if your port is to be used as it is configured at reset, you

should still write data into Px_MODE.

2. P2.6/TXJ1850 is the enable pin for ONCE mode. Because a high input during reset can

cause the device to enter ONCE mode or a reserved test mode, caution must be exercised

5-4

Page 49

I/O PORTS

in using this pin. Be certain that your syst em meets the VIH specifications during reset to

prevent inadvertent entry into ONCE mode or a test mode.

3. Following reset, P2.7/CLKOUT carries the strongly drive n CLKOUT signal. It is not held

low. When P2.7/CLKOUT is configured as CLKOUT, it is always a complementary

output.

5.3 INTERNAL STRUCTURE FOR PORTS 3 AND 4 (ADDRESS/DATA BUS)

Figure 5-2 shows the logic of ports 3 and 4. Consult the datas heet for specifications o n the amount

of current ports 3 and 4 can source and sink.

During reset, the active-low level of RESET# tu rns off Q1 and Q2 and turns on transistor Q4,

which weakly holds the pin low. Resistor R1 provides ESD protection for the pin. During normal

operation, the device controls the port through BUS CONTROL SELECT , an internal control signal.

When the device needs to acces s external memor y, it clears BUS CONTROL SELECT , selecting

ADDRESS/DATA as the input to the multiplexer. ADDRESS/DATA then drives Q1 and Q2 as

complementary outputs.

When external memory access is not required, the device sets BUS CONTROL SELECT, selecting Px_REG as the input to the multiplexer. Px_REG then drives Q1 and Q2. If P34_DRV is set,

Q1 and Q2 are driven as complementary outputs. If P34_DRV is cleared, Q1 is disabled and Q2

is driven as an open-drain output requiring an external pull-up resistor. With the open-drain configuration (BUS CONTROL SELECT set and P34_DRV cleared) and Px_REG set, the pin can

be used as an input. The signal on the pin is latched in the Px_PIN register . The pins can be read,

making it easy to see which pins are driven low by the device and which are driven high by external drivers while in open-drain mode.

5-5

Page 50

8XC196LX SUPPLEMENT

Internal Bus

Px_REG

Address/Data

Bus Control Select

0 = Address/Data

1 = I/O

P34_DRV

Read Port

1

0

Sample

Latch

Px_PIN

LE

PH1 Clock

V

CC

Q1

I/O Pin

Q2

RESET#

V

SS

150Ω to 200Ω

R1

Buffer

DQ

Medium

300ns Delay

RESET#

Pullup

Q3

V

SS

Weak

Pullup

Q4

V

SS

Figure 5-2. Ports 3 and 4 Internal Structure (87C196LA, LB Only)

A5264-01

5-6

Page 51

Synchronous Serial

I/O Port

6

Page 52

Page 53

CHAPTER 6

SYNCHRONOUS SERIAL I/O PORT

The synchronous serial I/O (SSIO) port on t he 8XC196Lx has been enhance d, implementing two

new special function registers (SSIO0_CLK and SSIO1_CLK) that allow you to select the operating mode and configure the phase and polarity of the serial clock signals.

6.1 SSIO 0 CLOCK REGISTER

The SSIO 0 clock (SSIO_CLK) register selects the phase and polarity for the SC0 clock signal.

In standard mode, SC0 is channel 0’s clock signal. In duplex and channel-select modes, SC0 is

the common clock signal for both SSIO channels.

SSIO0_CLK

The SSIO 0 clock (SSIO0_CLK) register configures the serial clock for channel 0. In standard mode,

the SC0 is channel 0’s clock signal. In duplex and channel-select modes, SC0 is the common clock

signal for both SSIO channels.

7 0

— — — — — — PHAS POLS

Bit

Number

7:2 — Reserved; for compatibility with future devices, write zeros to these bits.

1 PHAS Phase and Polarity Select

0POLS

Bit

Mnemonic

Function

For normal transfers, these bits determine the idle state of the serial

clock and select the serial clock signal edge on which the SSIO samples

incoming data bits or shifts out outgoing data bits. These bits are ignored

for handshaking transfers. Use SSIO0_ CON to select the type of data

transfer (normal or handshaking) for channel 0.

For transmissions

PHAS POLS

0 0 low idle state; shift on falling edges

0 1 high idle state; shift on rising edges

1 0 low idle state; shift on rising edges

1 1 high idle state; shift on falling edges

For receptions

PHAS POLS

0 0 low idle state; sample on rising edges

0 1 high idle state; sample on falling edges

1 0 low idle state; sample on falling edges

1 1 high idle state; sample on rising edges

Address:

Reset State:

1FB5H

00H

Figure 6-1. SSIO 0 Clock (SSIO0_CLK) Register

6-1

Page 54

8XC196LX SUPPLEMENT

For transmissions, SSIO0_CLK determines whether the SSIO shifts out data bits on rising or falling clock edges. For receptions, SSIO0_CLK determines whether the SSIO samples data bits on