Page 1

Intel® Celeron® Processor 1.66 GHz/

1.83 GHz

Datasheet

January 2007

Order Number: 315 876-002

Page 2

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—

Lega l Li nes and Discl a imers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHAT SOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELA TING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for

use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rig h ts that relate to the

present e d subject matter. The furn i shi ng o f do c um ent s and other mate rial s a nd i nfo rm at io n do es n ot provide any license, express or imp lied, by esto ppe l

or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility w hatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate featur es within each processor family, not across different

processor families. See http://www.intel.com/products/processor_number for details.

The Intel® Celero n® Processor 1.66 GHz/1.83 GHz may contain design defects or errors known as errata which may cause the product to deviate fr om

published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a HT Technology enabled

chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/

products/ht/Hyperthreading_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents w hich have an order number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, Dialogic, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486,

Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel

NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside,

MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are

trademarks or register ed trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other na m es and bra nds may be claimed as t he pro perty of others .

Copyright © 2007, Intel Corporation. All Rights Reserved.

®

Celeron® Processor 1.66 GHz/1.83 GHz

Intel

DS January 2007

2 Order Nu mber: 315876 - 00 2

Page 3

Contents—Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz

Contents

1.0 Introduction..............................................................................................................6

1.1 Terminology .......................................................................................................7

1.2 References .........................................................................................................8

1.3 State of Data......................................................................................................9

2.0 Low Power Features................................................................................................10

2.1 Clock Control and Low Power States ....................................................................10

2.2 Enhanced Intel

2.3 Extended Halt State (C1E)..................................................................................13

3.0 Electrical Specifications...........................................................................................15

3.1 Front Side Bus and GTLREF ................................................................................ 15

3.2 Power and Ground Pins......................................................................................15

3.3 Decoupling Guidelines........................................................................................15

3.4 Voltage Identification and Power Sequencing ........................................................16

3.5 Catastrophic Thermal Protection.......................................................................... 18

3.6 Signal Terminations and Unused Pins...................................................................18

3.7 FSB Frequency Select Signals (BSEL[2:0])............................................................18

3.8 FSB Signal Groups.............................................................................................19

3.9 CMOS Signals ...................................................................................................20

3.10 Maximum Ratings..............................................................................................20

3.11 Processor DC Specifications ................................................................................20

4.0 Package Mechanical Specifications and Pin Information..........................................25

4.1 Package Mechanical Specifications.......................................................................25

4.2 Processor Pin-Out and Pin List.............................................................................28

5.0 Thermal Specifications and Design Considerations ..................................................61

5.1 Thermal Specifications .......................................................................................62

®

SpeedStep® Technology (EIST)...................................................13

Figures

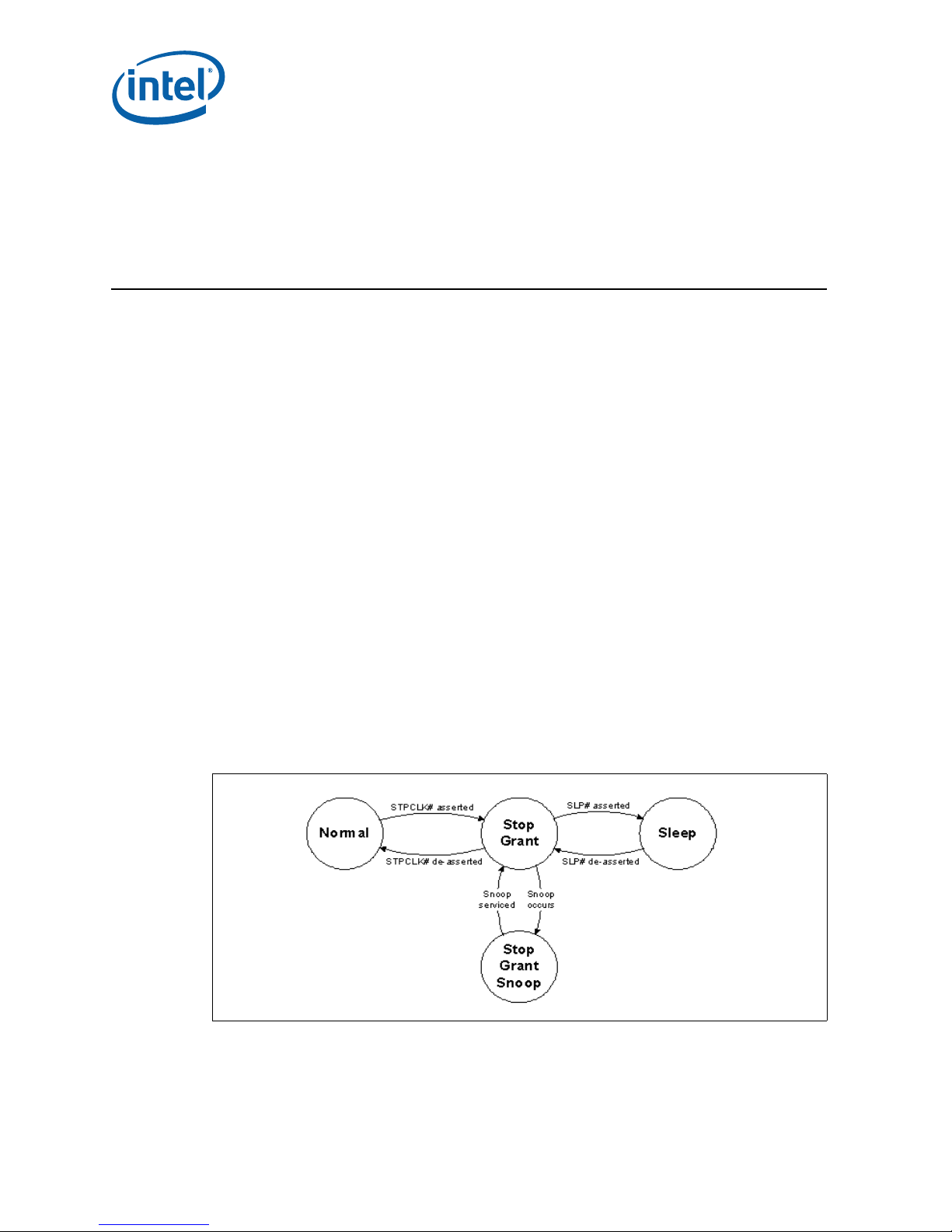

1 Package-Level Low Power States................................................................................10

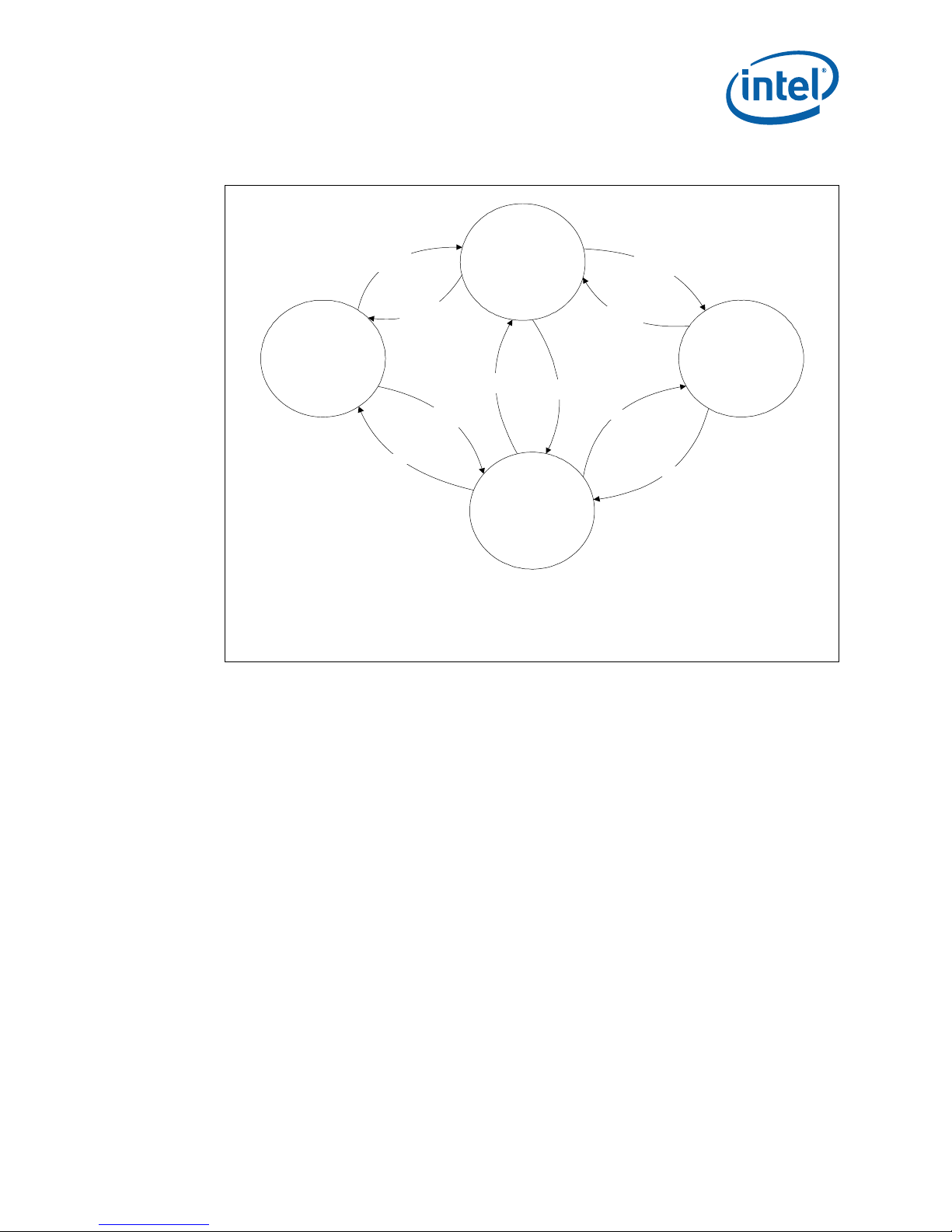

2 Core Low Power States.............................................................................................11

3 Active VCC and ICC Load Line for Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz.............. 22

4 Micro-FCPGA Package Top and Bottom Views...............................................................25

5 Micro-FCPGA Processor Package Drawing (Sheet 1) ................... ...................................26

6 Micro-FCPGA Processor Package Drawing (Sheet 2) ................... ...................................27

7 The Coordinates of the Processor Pins as Viewed From the Top of the Package................. 29

Tables

1 Terminology ..............................................................................................................7

2 References................................................................................................................ 8

3Intel

4 BSEL[2:0] Encoding for BCLK Frequency.....................................................................18

5 FSB Pin Groups........................................................................................................19

6 Processor DC Absolute Maximum Ratings ....................................................................20

7 Voltage and Current Specifications for the Intel

8 AGTL+ Signal Group DC Specifications........................................................................22

9 CMOS Signal Group DC Specifications.........................................................................23

10 Open Drain Signal Group DC Specifications..................................................................24

11 Signal Description....................................................................................................30

January 2007 DS

Order Nu mber: 315876 - 00 2 3

®

Celeron® Processor 1.66 GHz/1.83 GHz VID Map................................................16

®

Celeron® Processor 1.66 GHz/1.83 GHz.. 21

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 4

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Contents

12 Quad-Pumped Signal Groups......................................................................................32

13 DINV[3:0]# Assignment To Data Bus..........................................................................32

14 Alphabetical Signal Listing .........................................................................................37

15 Alphabetical Pin Listing..............................................................................................49

16 Power Specifications for the Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz......................61

17 Thermal Diode Interface............................................................................................63

18 Thermal “Diode” Parameters using Diode Mode.............................................................63

19 Thermal “Diode” n

and Diode Correction Toffset.......................................................64

trim

®

Celeron® Processor 1.66 GHz/1.83 GHz

Intel

DS January 2007

4 Order Nu mber: 315876 - 00 2

Page 5

Revision History—Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz

Revision History

Date Revision Description

November 2006 001 Initial public release.

January 2007 002 Added information for Intel® Celeron® Process o r 1. 83 GHz

January 2007 DS

Order Nu mber: 315876 - 00 2 5

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 6

1.0 Introduction

The Intel® Celeron® Processor 1.66 GHz/1.83 GHz is a single-core, low-power

processor designed for embedded, communications infrastructure and storage

applica ti ons . The pr oces so r is manu fa ct ure d on In te l’ s a dv an ced 65 nanomet er proc es s

technology with copper interconnect.

The following list provides some of the key features on this processor:

•Single core

• Uniprocessor support only

• 36-bit physical addressing

• Address, Data, and Response Parity on the Front Side Bus (FSB)

• Supports Intel Architecture with Dynamic Execution

• On-die, 32 kB Level 1 instruction cache and 32 kB write-back data cache

• On-die, 1 MB, ECC protected, Level 2 cache with Advanced Transfer Cache

Architecture

• Data Prefetch Logic

• Streaming SIMD Extensions 2 (SSE2) and Streaming Single Instruction Multiple

Data (SIMD) Extensions 3 (SSE3)

• 667 MT/s (megatransfers/second), Source-Synchronous FSB

• Digital Thermal Sensor (DTS)

• Intel Thermal Monitor 1 (TM1) and Thermal Monitor 2 (TM2)

• Micro-FCPGA packaging technologies

• Execute Disable Bit support for enhanced security

The Intel

Technology and Streaming SIMD instructions and full compatibility with IA32 software.

The on-die, 32 kB Level 1 instruction and data caches and the 1 MB Level 2 cache with

Advanced Transfer Cach e Archit ectu re enabl e per for ma nce impro vem en t over existi ng

low power processors. The processor’s Data Prefetch Logic speculatively fetches data to

the L2 cache before an L1 ca che request occurs, resulting in reduced bus cycle

penalties and improved performance. The Intel

GHz includes the Data Cache Unit Streamer, which enhances the performance of the L2

prefetcher by requesting L1 warm-ups earlier. In addition, Write Order Buffer depth is

enhanced to help with write-back latency performance.

®

Celeron® Processor 1.66 GHz/1.83 GHz maintains support for MMXTM

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Introduction

®

Celeron® Processor 1.66 GHz/1.83

In addition to supporting all the existing Streaming SIMD Extensions 2 (SSE2), there

are 13 new instructions, which further extend the capabilities of Intel processor

technology. These new instructions are called Streaming SIMD Extensions 3 (SSE3).

These new instructions enhance the performance of optimized applications such as

video, image processing and media compression technology. 3D graphics and other

video intense applications have the opportunity to take advantage of these new

instructions as platforms with the Intel

SSE3 become available.

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

6 Order Nu mber: 315876 - 00 2

®

Celeron® Processor 1.66 GHz/1.83 GHz and

Page 7

Introduction—Intel

The Intel® Celeron® Processor 1.66 GHz/1.83 GHz’s 667 MHz front side bus (FSB)

utilizes a split-transaction, deferred reply protocol. The FSB uses Source-Synchronous

Transfer (SST) of address and data to improve performance by transferring data four

times per bus clock (4X data transf er rate, as in AGP 4X). Along with the 4X data bus,

the address bus can deliver addresses two times per bus clock and is referred to as a

“double-clocked” or 2X address bus. Working together, the 4X data bus and 2X address

bus provide a data bus bandwidth of up to 5.33 GB/second. The FSB uses Advanced

Gunning Transceiver Logic (AGTL+) signaling technology, a variant of GTL+ signaling

technology with low power enhancements.

The processor also features the Auto Halt low power state (Extended Halt State - C1E).

Intel

Grid Array (Micro-FCPGA) package technology. The Micro-FCPGA package plugs into a

478-hole, surface-mount, Zero Insertion Force (ZIF) socket, which is referred to as the

mPGA478 socket.

The processor supports the Execute Disable Bit capability. This feature combined with a

support operating system allows memory to be marked as executable or non

executable. If code attempts to run in non-executable memory the processor raises an

error to the operating system. This feature can prevent some classes of viruses or

worms that exploit buffer overrun vulnerabilities and can thus help improve the overall

security of the system. Refer to the Intel® 64 and IA-32 Architectures Software

Developer's Manuals for more detailed information.

®

Celeron® Processor 1.66 GHz/1.83 GHz

®

Celeron® Processor 1.66 GHz/1.83 GHz utilizes socketable Micro Flip-Chip Pin

Note: The term AGTL+ is used to refer to Assisted GTL+ signaling technology on the

processor.

1.1 Terminology

Table 1. Terminology (Sheet 1 of 2)

Term Definition

A “#” sy mbo l afte r a s ig na l na me r ef e rs to an ac ti v e lo w si gn al, i ndi ca ti n g a s ig na l i s in

the active state when driven to a low level. For example, when RESET# is low, a reset

has been requested. Conversely, when NMI is high, a non-maskable interrupt has

#

AGTL+

Front Side Bus (FSB)

GTLREF

MT/s Megatransfers/second

Overshoot

Pad

Processor A single package that contains one complete execution core

occurred. In the case of signals where the name does not imply an active state but

describes part of a binary sequence (such as address or data), the “#” symbol implies

that the signal is inverted. For example, D[3:0] = “HLHL” refers to a hex ‘A ’, and

D[3:0]# = “LHLH” also refers to a hex “A” (H= High logic level, L= Low logic level).

XXXX means that the specification or value is yet to be determined.

Advanced Gunning Tran sceiver Logic. Used to refer to Assisted GTL+ signaling

technology on the processor

The electrical interface that connects the processor to the chipset. Also referred to as

the processor system bus or the system bus. All memory and I/O transactions as well

as interrupt messages pass between the processor and chipset over the FSB.

A reference voltage level used on the system bus to determine the logical state of a

signal.

The maximum voltage observed for a signal at the device pad, measured with

respect to the buff er ref ere nc e volta ge.

The electrical contact point of a semiconductor die to the package substrate. A pad is

only observable in simulations.

January 2007 DS

Order Nu mber: 315876 - 00 2 7

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 8

Table 1. Terminology (Sheet 2 of 2)

Term Definition

Ringback

Undershoot The minimum voltage extending below VSS observed for a signal at the device pad.

VRD

The voltage to which a sign al transition s to just after reaching its maxi mum

absolute value. Ringback may be caused by reflections, driver oscillations, or

other transmission line phenomena.

Voltage Regulator-Down for the processor that supplies the required voltage and

current to a single processor.

1.2 References

Material and concepts available in the following documents may be beneficial when

reading this document.

Table 2 . References

Dual-Core Intel® Xeon® Processor LV and ULV Specification Update

®

Intel

E7520 Me mory Controller Hub (M CH ) Datas heet

®

Intel

6300ESB I/O Controller Data sheet

Embedded Voltage Regulator-Down (EmVRD) 11.0 Design Guidelines for Embedded

Implementations Supporting PGA478

®

Intel

Celeron® Processor 1.66 GHz/1.83 GHz Thermal Design Guideline for

Embedded Applications

®

Intel

64 and IA-32 Architectures Software Developer's Manuals

Volume 1: Basic Architecture 253665

Volume 2A/2B: Instruction Set Reference

Volu me 3A/3B: System P rogrammin g Guide

®

Intel

Processor Identification and CPUID Instruction application note (AP-485)

1. Order numbers are subject to change

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Introduction

Document Order Number

http://www.intel.com/

design/intarch/

specupdt/311392.htm

ftp://

download.intel.com/

design/chipsets/

datashts/

30300602.pdf

http://

developer.intel.com/

design/intarch/

datashts/300641.htm

http://

developer.intel.com/

design/intarch/

designgd/311395.htm

http://

developer.intel.com/

design/intarch/

designgd/315745.pdf

http://

developer.intel.com/

design/pentium4/

manuals/

index_new.htm

253666

253667

253668

253669

http://www.intel.com/

support/processors/sb/

cs-009861.htm

1

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

8 Order Nu mber: 315876 - 00 2

Page 9

Introduction—Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz

1.3 State of Data

The data contained within this document represents the most accurate information

available by the publication date.

Note: All references to the Intel

apply to the Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz only, unless otherwise

specified.

®

Celeron® Processor 1.66 GHz/1.83 GHz in this document

January 2007 DS

Order Nu mber: 315876 - 00 2 9

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 10

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Low Power Features

2.0 Low Power Features

2.1 Clock Control and Low Power States

The Intel® Celeron® Processor 1.66 GHz/1.83 GHz supports the C1/AutoHALT, C1/

MWAIT, S top G r an t a nd Sl eep s ta tes f or op tima l powe r mana ge men t. C1/ Aut oHALT and

C1/MWAIT are core-level low power states only, they do not have package-level

behavior. Refer to Figure 1 for a visual representation of package level low-power

states for a Intel

Celeron

®

Processor 1.66 GHz/1.83 GHz can enter the C1/AutoHALT/MWAIT at any

time.

Refer to Figure 2 for a visual representation of the core low-power states for the Intel

Celeron

Intel

®

Processor 1.66 GHz/1.83 GHz.

®

Celeron® Processor 1.66 GHz/1.83 GHz implements two software interfaces for

requesting low power states: the I/O mapped ACPI P_BLK register block and the Cstate extens io n to the MW AI T in stru ction . Ei th er int erf ace can b e use d at a ny ti me. The

processor core presents an independent low power state request interface (ACPI P_BLK

or MWAIT). Requests from the software running on the core puts into core-level low

power state. The processor has logic for coordinating low power state requests from

the processor core. This logic puts the Intel

into a package-level low-power state based on the highest core low power state, as

desired.

®

Celeron® Processor 1.66 GHz/1.83 GHz. The single core Intel®

®

Celeron® Processor 1.66 GHz/1.83 GHz

®

If the core encounters a break event while STPCLK# is asserted, it returns to C0 state

by asserting the PBE# output signal. PBE# assertion signals to system logic that the

processor needs to return to the Normal package-level state. This allows that core to

return to the C0 state.

Figure 1. Package-Level Low Power States

®

Celeron® Processor 1.66 GHz/1.83 GHz

Intel

DS January 2007

10 Order Nu mber: 315876 - 00 2

Page 11

Low Power Features—I ntel

®

Celeron® Processor 1.66 GHz/1.83 GHz

Figure 2. Core Low Power States

STPCLK#

asserted

STPCLK#

de-asserted

C1/

MWAIT

Core state break

or MONITOR

MWAIT(C1)

halt br eak = A20M # transition, INIT# , INTR, NMI, PREQ #, RESET#, SMI#, or APIC interrupt

core state br eak = (halt break OR MON IT OR event) AND STPCLK# high (not asserted)

2.1.1 Core Low Power States

STPCLK#

asserted

Stop

Grant

STPCLK#

de-asserted

C0

STPCLK#

asserted

HLT instruction

STPCLK#

de-asserted

Halt break

C1/Auto

Halt

2.1.1.1 C0 State - Normal State

This is the normal operating state for the processor.

2.1.1.2 C1/AutoHALT Powerdown State

AutoHALT is a low power state entered when the processor executes the HALT

instruction. The processor transitions to the Normal state upon the occurrence of SMI#,

BINIT#, INIT#, LINT[1:0] (NMI, INTR), or an interrupt delivered over the system bus.

RESET# causes the processor to immediately initialize itself.

The return from a System Management Interrupt (SMI) handler can be to either

Normal Mode or the AutoHALT Power Down state. Refer to the Intel® 64 and IA-32

Architectures Software Developer's Manuals in Volume 3A/3B: System Programming

Guide for more information.

The system can generate a STPCLK# while the processor is in the AutoHALT Power

Down state. When the system deasserts the STPCLK# interrupt, the processor returns

execution to the HALT state.

While in AutoHALT Power Down state, the processor continues to processes system bus

snoops.

January 2007 DS

Order Nu mber: 315876 - 00 2 11

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 12

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Low Power Features

2.1.1.3 C1/MWAIT Powerdown State

MWAIT is a low power state entered when the processor core executes the MWAIT

instruction. Processor behavior in the MWAIT state is identical to the AutoHALT state

except that there is an addi tional event that can cause the processor core to return to

the C0 state: the Monitor event. Refer to the Intel® 64 and IA-32 Architectures

Software Developer's Manuals in Volume 3A/3 B : Syst em Pro gra mm in g Guide for more

information.

2.1.2 Packag e L o w Power States

The following sections describe all package level low power states for the Intel®

Celeron

®

Processor 1.66 GHz/1.83 GHz.

2.1.2.1 Normal State

This is the normal operating state for the processor. Intel® Celeron® Processor 1.66

GHz/1.83 GHz en te rs the Norm al st ate wh en its core is in the Norm al , AutoH ALT, or

MWAIT state.

2.1.2.2 Stop-Grant State

When the STPCLK# pin is asserted, the Stop-Grant state of the processor is entered 20

bus clocks after the response phase of the processor-issued Stop Grant Acknowledge

special bus cycle. Once the STPCLK# pin has been asserted, the Intel

Processor 1.66 GHz/1.83 GHz, the processor core must be in the Stop Grant state

before the deassert ion of STPCLK #.

Since the AGTL+ signal pins receive power from the system bus, these pins should not

be driven (allowing the level to return to V

termination resistors in this state. In addition, all other input pins on the system bus

should be driven to the inactive state.

BINIT# is not serviced while the processor is in Stop-Grant state. The event is latched

and can be serviced by software upon exit from the Stop Grant state.

RESET# causes the processor to immediately initialize itself, but the processor stays in

Stop-Grant state. A transition back to the Normal state occurs with the de-assertion of

the STPCLK# signal. When re-entering the Stop-Grant state from the Sleep state,

STPCLK# should only be deasserted one or more bus clocks after the deassertion of

SLP#.

®

Celeron®

) for minimum power drawn by the

CCP

A transition to the HALT/Grant Snoop state occurs when the processor detects a snoop

on the system bus A transiti on to the Sle ep sta te occ urs with the asse rti on of the SLP#

signal.

While in the Stop-Grant state, SMI#, INIT#, BINIT# and LINT[1:0] is latched by the

processor, and only serviced when the processor returns to the Normal state. Only one

occurrence of each event is recognized upon return to the Normal state.

While in Stop-Grant state, the processor processes snoops on the system bus and it

latches interrupts delivered on the system bus.

The PBE# signal can be driven when the processor is in Stop-Grant state. PBE# is

asserted if there is any pending interrupt latched within the processor. Pending

interrupts that are blocked by the EFLAGS.IF bit being clear still causes assertion of

PBE#. As serti on of PBE # indica tes to sy stem lo gic that it shou ld ret urn the proce ssor to

the Normal state .

®

Celeron® Processor 1.66 GHz/1.83 GHz

Intel

DS January 2007

12 Order Nu mber: 315876 - 00 2

Page 13

Low Power Features—I ntel

®

Celeron® Processor 1.66 GHz/1.83 GHz

2.1.2.3 Stop Grant Snoop State

The processor responds to snoop or interrupt transactions on the FSB while in StopGrant state. During a snoop or interrupt transaction, the processor enters the Stop

Grant Snoop state. The processor stays in this state until the snoop on the FSB has

been serviced (whether by the processor or another agent on the FSB) or the interrupt

has been latched. After the snoop is serviced or the interrupt is latched, the processor

returns to the Stop-Grant state.

2.1.2.4 Sleep State

The Sleep state is a very low power state in which the processor maintains its context,

maintains the phase-locked loop (PLL), and has stopped most of internal clocks. The

Sleep state can only be entered from Stop-Grant state. Once in the Stop-Grant state,

the processor enters the Sleep state upon the assertion of the SLP# signal. The SLP#

pin has a mini mum assert ion of one BCLK period. The SLP# pin sh ould only be asser ted

when the processor is in the Stop Grant state. For the Intel

GHz/1.83 GHz, the SLP# pin may only be asserted the processor core is in the StopGrant state. SLP# assertions while the processor is not in the Stop-Grant state are out

of specification and may results in illegal operation.

Snoop events that occur while in Sleep state or during a transition into or out of Sleep

state causes unpredictable behavior.

®

Celeron® Processor 1.66

In the Sleep state, the processor is incapable of responding to snoop transactions or

latching interrupt signals. No transitions or assertions of signals (with the exception of

SLP# or RESET#) are allowed on the system bus while the processor is in Sleep state.

Any transition on an input signal before the processor has returned to Stop-Grant state

results in unpredictable behavior.

If RESET# is driven active while the processor is in the Sleep state, and held active as

specified in the RESET# pin specification, then the processor resets itself, ignoring the

transiti on through Sto p-Gran t state. If RESET # is driven acti ve while the processor i s in

the Sleep state, the SLP# and STPCLK# signals should be deasserted immediately after

RESET# is asserted to ensure the processor correctly executes the reset sequence.

When the processor is in Sleep state, it does not respond to interrupts or snoop

transactions.

2.2 Enhanced Intel® SpeedStep® Technology (EIST)

Intel® Celeron® Processor 1.66 GHz/1.83 GHz does not support this feature.

2.3 Extended Halt State (C1E)

The Intel® Celeron® Processor 1.66 GHz/1.83 GHz Extended Halt State (C1E) enables

significant power savings. Extended HALT state is a low power state entered when the

processor core has executed the HALT or MWAIT instructions and Extended HALT state

has been enabled via the BIOS. When the processor core executes the HALT

instruction, the core is halted. The Extended HALT state is a lower power state than the

HALT state or Stop Grant state.

Note: The Extended HALT (C1E) state must be enabled for the processor to remain within its

specifications.

The Extended HALT state requires support for dynamic VID transitions in the platform.

The processor a utomati cally tr ansiti ons to a l ower core frequenc y and vo ltage oper ating

point before entering the Extended HALT state. Note that the processor FSB frequency

January 2007 DS

Order Nu mber: 315876 - 00 2 13

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 14

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Low Power Features

is not altered; only the internal core frequency is changed. When entering the low

power state, the processor first switches to the lower bus to core frequency ratio and

then transition to the lower voltage (VID).

While in the Extended HALT(C1E) state, the processor processes bus snoops. The

processor exits the Extended HALT state when a break event occurs. When the

processor e xi ts the E x tend ed HA LT state, it f irst transitions the VID to th e or igina l value

and then changes the bus to core frequency ratio back to the original value.

®

Celeron® Processor 1.66 GHz/1.83 GHz

Intel

DS January 2007

14 Order Nu mber: 315876 - 00 2

Page 15

Electrical Specifications—Intel

®

Cele r o n® Proc essor 1.66 G Hz/1.83 GHz

3.0 Electrical Specifications

3.1 Front Side Bus and GTLREF

Most Inte l® Celeron® Processor 1.66 GH z/1.8 3 GH z F SB si gn als use Ad v an ced Gu nni ng

Transceiver Logic (AGTL+) signalling technology. This signalling technology provides

improved noise margins and reduced ringing through low-voltage swings and controlled

edge rates. The termination voltage level for the Intel

1.83 GHz AGTL+ signals is V

data and address bus, signal integrity and platform design methods have become more

critical than with previous processor families.

The AGTL+ inputs require a reference voltage (GTLREF) that is used by t he receivers t o

determine if a signal is a logical 0 or a logical 1. GTLREF must be generated on the

system board. Termination resistors are provided on the processor silicon and are

terminated to its I/O voltage (V

The AGTL+ bus depends on incident wave switching. Therefore, timing calculations for

AGTL+ signals are based on flight time as opposed to capacitive deratings. Analog

signal simulation of the FSB, including trace lengths, is highly recommended when

designing a system.

= 1.05 V (nominal). Due to speed improvements to

CCP

).

CCP

®

Celeron® Processor 1.66 GHz/

3.2 Power and Ground Pins

For clean, on-chip power distribution, the Intel® Celeron® Processor 1.66 GHz/1.83

GHz has a large num ber of V

connected to V

power planes while all VSS pins must be connected to system ground

CC

(power) and V

CC

planes. Use of multiple power and ground planes is recommended to reduce IR drop.

The processor V

(Voltage ID) pins.

pins must be supplied with the voltage determined by the VID

CC

3.3 Decoupling Guidelines

Due to its large number of transistors and high internal clock speeds, the processor is

capable of generating large average current swings between low and full power states.

This may cause voltages on power planes to sag below their minimum values if bulk

decoupling is not adequate. Care must be taken in the board design to ensure that the

voltage provided to the processor remains within the specifications listed in Table 7.

Failure to do so can result in timing violations or reduced lifetime of the component.

3.3.1 V

Decoupling

CC

Regulator solutions need to provide bulk capacitance with a low effective series

resistance (ESR) and keep a low interconnect resistance from the regulator to the

socket. Bulk decoupling for the large current swings when the part is powering on, or

entering/exiting low-power states, must be provided by the voltage regulator solution.

For more details on decoupling recommendations, please refer to the Embedded

Voltage Regulator-Down (EmVRD) 11.0 Design Guidelines for Embedded

Implementations Supporting PGA478.

(ground) inputs. All power pins must be

SS

January 2007 DS

Order Nu mber: 315876 - 00 2 15

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 16

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Electrical Specifications

3.3.2 FSB AGTL+ Decoupling

The processor integrates signal termination on the die as well as incorporate high

frequency decoupling capacitance on the processor package. Decoupling must also be

provided by the system motherboard for proper AGTL+ bus operation.

3.3.3 FSB Cloc k ( B C LK [ 1 :0]) and Pro c es sor Clocking

BCLK[01:00] directly controls the FSB interface speed as well as the core frequency of

the processor. As in previous generation processors, the Intel

1.66 GHz/1.83 GHz core frequency is a multiple of the BCLK[01:00] frequency. The

®

Intel

Celeron® Processor 1.66 GHz/1.83 GHz bus ratio multiplier is set at its default

®

Celeron® Processor

ratio at manufacturing. The processor uses a differential clocking implementation.

3.4 Voltage Identification and Power Sequencing

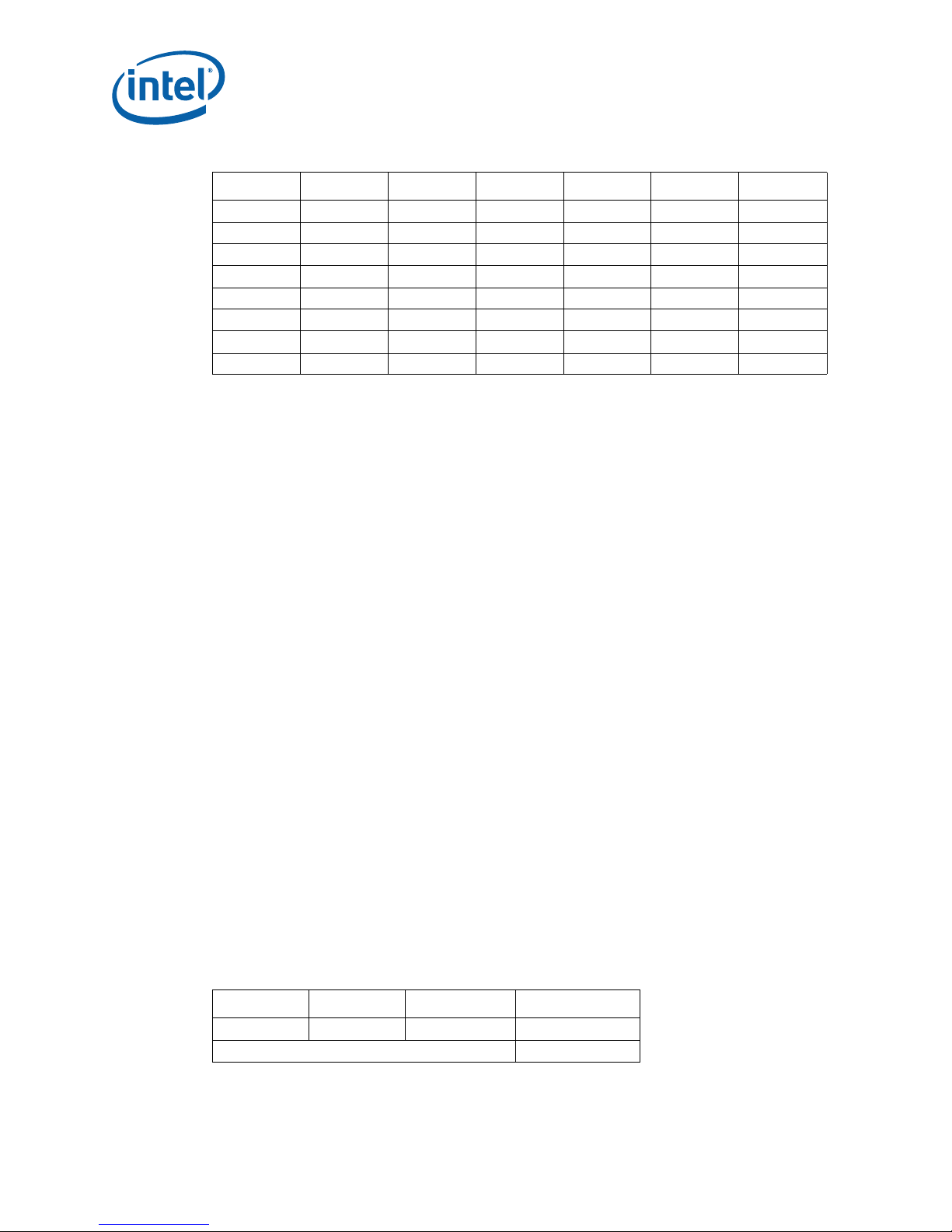

The VID specification for the Intel® Celeron® Processor 1.66 GHz/1.83 GHz is defined

by the Embedded Voltage Regulator-Down (EmVRD) 11.0 Design Guidelines for

Embedded Implementations Supporting PGA478.

The Intel

VID[5:0], to support automatic selection of power supply voltages. The VID pins for

Intel

processor VID circuitry. Table 3 specifies the voltage level corresponding to the state of

VID[5:0]. A ‘1’ in this refers to a high-voltage level and a 0 refers to low-voltage level.

For more details about VR design to support the Intel

1.83 GHz power supply requirements, please refer to the Embedde d Vo ltage Regulat or-

Down (EmVRD) 11.0 Design Guidelines for Embedded Implementations Supporting

PGA478.

Power source characteristics must be stable whenever the supply to the voltage

regulator is stable.

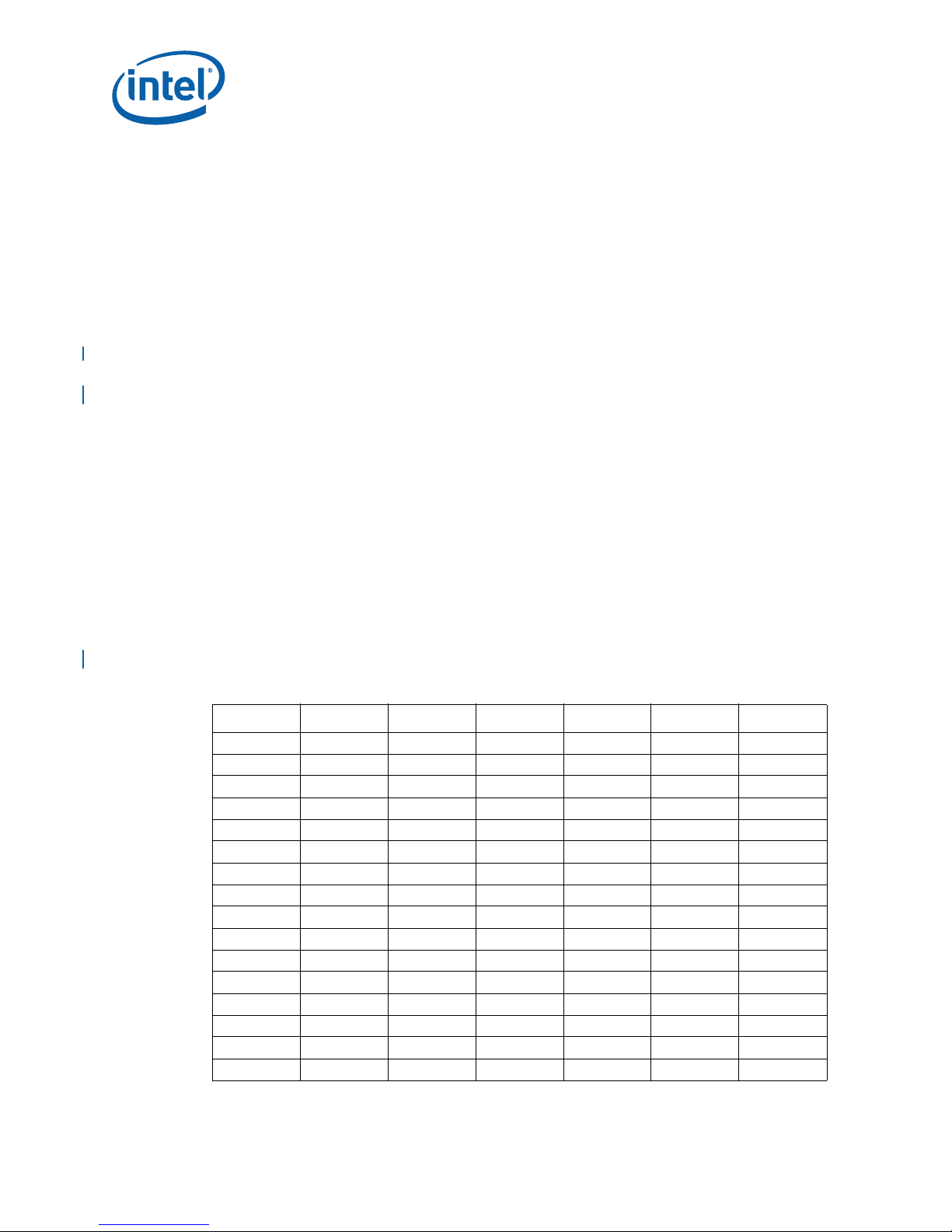

Table 3 . Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz uses six voltage identification pins,

®

Celeron® Processor 1.66 GHz/1.83 GHz are CMOS outputs driven by the

®

Celeron® Processor 1.66 GHz/

®

Celeron® Processor 1.66 GHz/1.83 GHz VID Map (Sheet 1 of 3)

VID5 VID4 VID3 VID2 VID1 VID0 VCC (V)

000000OFF

0000011.6000

0000101.5875

0000111.5750

0001001.5625

0001011.5500

0001101.5375

0001111.5250

0010001.5125

0010011.5000

0010101.4875

0010111.4750

0011001.4625

0011011.4500

0011101.4375

0011111.4250

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

16 Order Nu mber: 315876 - 00 2

Page 17

Electrical Specifications—Intel

®

Cele r o n® Proc essor 1.66 G Hz/1.83 GHz

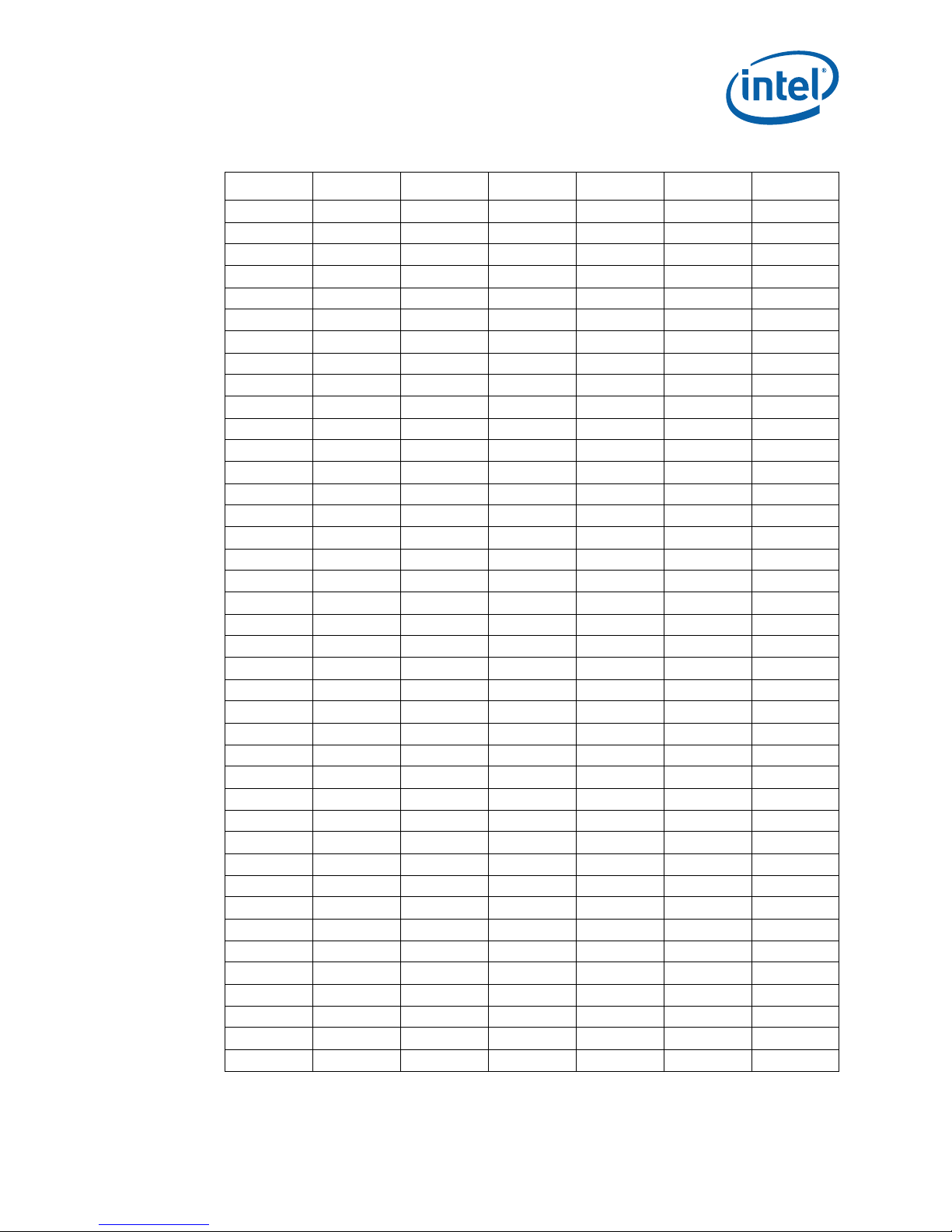

Table 3. Inte l® Celeron® Processor 1.66 GHz/1.83 GHz VID Map ( Sheet 2 of 3)

VID5 VID4 VID3 VID2 VID1 VID0 VCC (V)

0100001.4125

0100011.4000

0100101.3875

0100111.3750

0101001.3625

0101011.3500

0101101.3375

0101111.3250

0110001.3125

0110011.3000

0110101.2875

0110111.2750

0111001.2625

0111011.2500

0111101.2375

0111111.2250

1000001.2125

1000011.2000

1000101.1875

1000111.1750

1001001.1625

1001011.1500

1001101.1375

1001111.1250

1010001.1125

1010011.1000

1010101.0875

1010111.0750

1011001.0625

1011011.0500

1011101.0375

1011111.0250

1100001.0125

1100011.0000

1100100.9875

1100110.9750

1101000.9625

1101010.9500

1101100.9375

1101110.9250

January 2007 DS

Order Nu mber: 315876 - 00 2 17

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 18

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Electrical Specifications

Table 3 . Intel® Celeron® Processor 1.66 GHz/1.83 GHz VID Map (Sheet 3 of 3)

VID5 VID4 VID3 VID2 VID1 VID0 VCC (V)

1110000.9125

1110010.9000

1110100.8875

1110110.8750

1111000.8625

1111010.8500

1111100.8375

1111110.8250

3.5 Catastrophic Thermal Protection

The Intel® Celeron® Processor 1.66 GHz/1.83 GHz supp orts the T HERMTRIP# s ignal for

catastrophic thermal protection. An external thermal sensor should also be used to

protect the processor and the system against excessive temperatures. Even with the

activation of THERMTRIP#, which halts all processor internal clocks and activity,

leakage current can be high enough such that the processor cannot be protected in all

conditions without the removal of power to the processor. If the external thermal

sensor detects a catastrophic processor temperature of approximately 125 °C

(maximum), or if the THERMTRIP# signal is asserted, the V

must be turned of f within 500 ms to prevent p ermanen t sil icon d amage due to therm al

runaway of the processor.

supply to the processor

CC

3.6 Signal Terminations and Unused Pins

All RSVD ( RES ERVE D) pi ns must r emai n unc onn ec ted. Conne c ti on of th es e pi ns t o VCC,

V

, or to any other signal (including each other) can result in component malfunction

SS

or incompatibility with future processors. See Table 15 for a pin listing of the processor

and the location of all RSVD pins.

For reliable operation, always connect unused inputs or bidirectional signals to an

appropriate signal level. Unused active low AGTL+ inputs may be left as no connects if

AGTL+ termination is provided on the processor silicon. Unused active high inputs

should be connected through a resistor to ground (V

unconnected.

). Unused outputs can be left

SS

Note: The TEST1 and TEST2 pins have unique signal termination requirements. It is

mandatory that the TEST2 pin have a 51 Ω +/-5% pull down resistor to V

refer to Table 11 for details.

. Please

SS

3.7 FSB Frequency Select Signals (BSEL[2:0])

The BSEL[2:0] signals are used to select the frequency of the processor input clock

(BCLK[1:0]). The BSEL encoding for BCLK[1:0] is shown in Table 4.

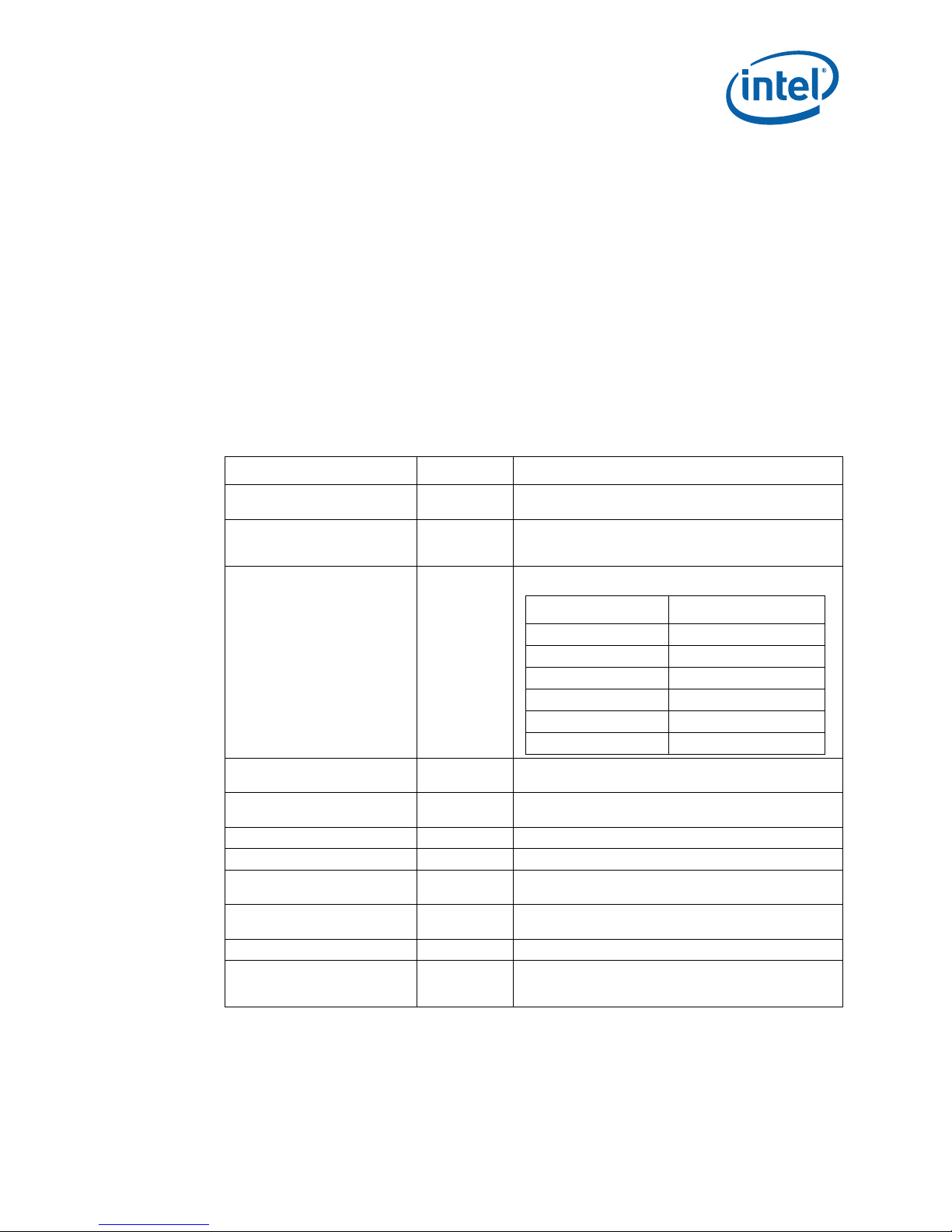

Table 4. BSEL[2:0] Encoding for BCLK Frequency

BSEL[2] BSEL[1] BSEL[0] BCLK frequency

LHH 166MHz

All other combinations RESERVED

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

18 Order Nu mber: 315876 - 00 2

Page 19

Electrical Specifications—Intel

®

Cele r o n® Proc essor 1.66 G Hz/1.83 GHz

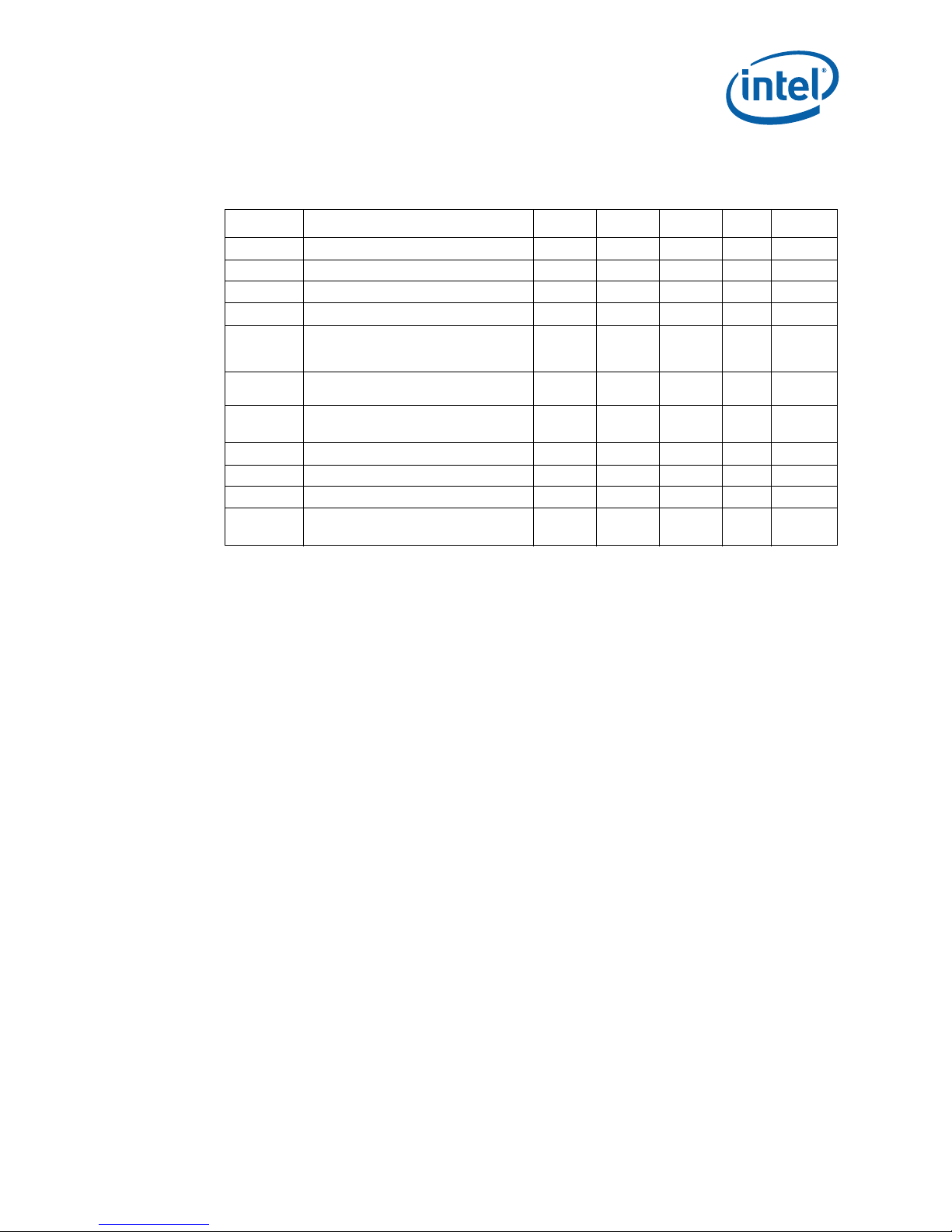

3.8 FSB Signal Groups

In order to simplify the following discussion, the FSB signals have been combined into

groups by buffer type. AGTL+ input signals have differential input buffers, which use

GTLREF as a reference level. In this document, the term "AGTL+ Input" refers to the

AGTL+ input group as well as the AGTL+ I/O group when receiving. Similarly, "AGTL+

Output" refers to the AGTL+ output group as well as the AGTL+ I/O group when

driving.

With the implementation of a source synchronous data bus comes the need to specify

two sets of timing parameters. One set is for common clock signals which are

dependant upon the rising edge of BCLK0 (ADS#, HIT#, HITM#, etc.) and the second

set is for the source synchronous signals which are relative to their respective strobe

lines (data and address) as well as the rising edge of BCLK0. Asychronous signals are

still present (A20M#, IGNNE#, etc.) and can become active at any time during the

clock cycle. Ta ble 5 identifies which signals are common clock, source synchronous,

and asynch r ono u s.

Table 5. FS B Pin Groups

Signal Group Type Signals

AGTL+ Common Clock Input

AGTL+ Common Clock I/O

Synchronous

to BCLK[1:0]

Synchronous

to BCLK[1:0]

1

BPRI#, DEFER#, PREQ#, RESET#, RS[2:0]#, RSP#,

TRDY#

ADS#, AP[1:0]#,BINIT#, BNR#, BPM[3 :0]#

DBSY#, DP[3:0], DRDY#, HIT#, HI TM#, LOCK#,

MCERR#, PRDY#

3

3

, BR[0]#,

Signals Associ ated Strobe

REQ[4:0]#, A[16:3]# ADST B[0]#

AGTL+ Source Synchronous I/O

AGTL+ Strobes

CMOS Input Asynchronous

Open Drain Output Asynchronous FERR#, IERR#, THERMTRIP#, PROCHOT#

CMOS Outp ut Asynchr o no us VI D[5 : 0 ], BSE L[ 2 :0 ]

CMOS Input

Open Drain Output

FSB Clock Clock BCLK[1:0]

Power/Other

Notes:

1. Refer to Chapter 4.0 for signal descriptions and termination requirements.

2. BPM[2:1]# and PRDY# are AGTL+ output only signals.

Synchronous

to assoc.

strobe

Synchronous

to BCLK[1:0]

Synchronous

to TCK

Synchronous

to TCK

A[35:17]# ADSTB[1]#

D[15:0 ]# , DIN V 0 # DSTBP0# , DST BN 0#

D[31:16]#, DINV1# DSTBP1#, DSTBN1#

D[47:32]#, DINV2# DSTBP2#, DSTBN2#

D[63:48]#, DINV3# DSTBP3#, DSTBN3#

ADSTB[1:0]#, DSTBP[3:0]#, DSTBN[3:0]#

A20M#, FORCEPR#, IGNNE#, INIT#, LINT0/INTR, LINT1/

NMI, PWRGOOD, SMI#, SLP#, STPCLK#

TCK, TDI, TMS, TRST#

TDO

COMP[3:0], DBR#

THERMDA, THERMDC, ODTEN, V

V

SS, VSS_SENSE

2

, GTLREF, RSVD, TEST2, TEST1,

, V

, V

CC

CCA

CCP , VCC_SENSE

,

January 2007 DS

Order Nu mber: 315876 - 00 2 19

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 20

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Electrical Specifications

3.9 CMOS Signals

CMOS input signals are shown in Table 5. Legacy output FERR#, IERR# and other nonAGTL+ signals (THERMTRIP# and PROCHOT#) utilize Open Drain output buffers. These

signal s do not ha v e se tu p o r ho ld ti m e sp ec if icat io ns in rel a tion t o BCL K[ 1:0] . Howe ve r,

all of the CMOS signals are required to be asserted for at least three BCLKs in order for

the processor to recognize them. See Section 3.11 for the DC for the CMOS signal

groups.

3.10 Maximum Ratings

Table 6 lists the processor’s maximum environmental stress ratings. The processor

should not receive a clock while subjected to these conditions. Extended exposure to

the maximum ratings may affect device reliability . Furthermore, although the processor

contains protective circuitry to resist damage from Electro-Static Discharge (ESD), one

should always take precautions to avoid high static voltages of electric fields.

Table 6. Processor DC Absolute Maximum Ratings

Symbol Parameter Min Max Unit Notes

STORAGE

T

V

CC

V

inAGTL+

V

inAsynch_CMOS

Notes:

1. For functional operation, all processor electrical, signal quality, mechanical and thermal specifications

2. Excessive overshoot or undershoot on any signal will likely result in permanent damage to the

3. Storage temperature is applicable to storage conditions only. In this scenario, the processor must not

must be satisfied.

processor .

receive a clock, and no pins can be connected to a voltage bias. Storage within these limits will not

affect the long term reliability of the device. For functional operation, please refer to the processor

case temperature specificat ions.

Processor storage

temperature

Any processor supply

voltage with respect to V

AGTL+ buffer DC input

voltage with respect to V

CMOS buffer DC input

voltage with respect to V

SS

SS

SS

-40 85 °C 2

-0.3 1.6 V 1

-0.1 1.6 V 1, 2

-0.1 1.6 V 1, 2

3.11 Processor DC Specifications

Note: Th e p roce s sor DC sp e ci fi cations in this se cti on are de fin ed at the processor core (pa ds )

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

20 Order Nu mber: 315876 - 00 2

unless noted otherwise.

See Table 5 for the pin signal definitions and signal pin assignments. Most of the signals

on the FSB are in the AGTL+ signal group. The DC specifications for these signals are

listed in Table 8. DC specifications for the CMOS group are listed in Table 9.

Table 7 through Table 10 list the DC specifications for the Intel

1.66 GHz/1.83 GHz and are valid only while meeting specifications for junction

temperature, clock frequency, and input voltages. The Highest Frequency Mode (HFM)

and Lowest Frequency Mode (LFM) refer to the highest and lowest core operating

frequencies supported on a particular processor. Active mode load line specifications

apply in all states. V

power up in order to set the VID values. Unless specified otherwise, all specifications

for the Intel

®

Celeron® Processor 1.66 GHz/1.83 GHz are at Tjunction = 100 °C. Care

should be taken to read all notes associated with each parameter.

The Intel

SpeedStep

®

Celeron® Processor 1.66 GHz/1.83 GHz does not support Enhanced Intel

®

Technology (EIST), therefore HFM and LFM transitions are not supported.

CC,BOOT

®

Celeron® Process o r

is the default voltage driven by the voltage regulator at

Page 21

Electrical Specifications—Intel

®

Cele r o n® Proc essor 1.66 G Hz/1.83 GHz

Table 7. Voltage and Current Specifications for the Intel® Celeron® Processor 1. 66

GHz/1.83 GHz

Symbol Parameter Min Typ Max Unit Notes

V

CC

V

CC,BOOT

V

CCP

V

CCA

I

CCDES

I

CC

I

AH,

I

SGNT

I

SLP

dI

CC/DT

I

CCA

I

CCP

Notes:

1. These are VID values. Individual processor VID values may be calibrated during manufacturing such

2. The voltage specifications are assumed to be measured across V

3. Specified at 100 C T

4. Specified at the VID voltage.

5. The I

6. Based on simulations and averaged over the duration of any change in current. Specified by design/

7. Refer to Figure 3 for a waveform illustration of this parameter.

8. Measured at the bulk cap acitors o n the motherboard.

9. V

10. I

11. Specified at the nominal voltage based on the loadline slope.

VCC CPU Core Voltage 1.1125 1.275 V 1, 2

Default V

Voltage for initial power up 1.1 V 2, 7, 9

CC

AGTL+ Termination Voltage 0.997 1.05 1.102 V 2

PLL supply voltage 1.425 1.5 1.575 V 2

ICC for Intel® Celeron® Process o r 1. 66

GHz/1.83 GHz Recommended Design

36 A 5

Target

ICC for Intel® Celeron® Process o r 1. 66

GHz/1.83 GHz

34 A 3,11

ICC Auto-Halt & Stop-Grant 23.2 A 3,4

I

SLP

V

power supply current slew rate 600 A/us 6, 8

CC

ICC for V

ICC for V

for V

I

CC

supply 120 mA

CCA

supply before V

CCP

supply after V

CCP

CC

CC

stable

stable

23.2 A 3,4

6.0

2.5

A10

that two devices at the same speed may have different VID settings. Actual voltage supplied to the

processor should be as specified in the load lines in Figure 3. Adherence to load line specifications is

required to ensure reliable processor operation. Note that this differs from the VID employed by the

processor during a power management event (Thermal Monitor 2 or Extended Halt State).

with a 100 MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1-Mohm minimum

impedance. The maximum length of grou nd wire on the prob e should be less than 5 mm. Ensure

external noise from the system is not coupled in the scope probe.

(max) specification comprehends only Intel® Celeron® Processor 1.66 GHz/ 1.83 GHz HFM

CCDES

frequencies. Platforms should be designed to this specification.

characterization at nominal V

, boot tolerance is shown in Figure 3.

CC

specification refers to the processor package on the front side bus.

CCP

.

J

. Not 100% tested.

CC

CCSENSE

and V

SSSENSE

pins at socket

January 2007 DS

Order Nu mber: 315876 - 00 2 21

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 22

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Electrical Specifications

]

Figure 3. Active VCC and ICC Load Line for Intel® Celeron® Process or 1.66 GHz/1.83 GHz

V

[V]

CC

Slope = -2.1 mV /A at package

VccSense, VssSense pins.

Differential Remote Sense required.

10mV= RIPPLE

V

CC, DC

V

CC, DC

max

V

CC

max

VCC nom

min

V

CC

min

+/-VCC nom * 1.5%

= VR St. Pt. Error

See Note

0

Note: Vcc > 0.82 50 V (VID 111 111)

.

Table 8. AGTL+ Signal Group DC Specifications (Sheet 1 of 2)

Symbol Parameter Min Typ Max Unit

V

CCP

GTLREF Reference Voltage 2/3 V

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. V

3. V

4. V

5. This is the pull down driver resistance. Refer to processor I/O Buffer Models for I/V characteristics.

6. GTLREF should be generated from V

7. R

8. Specified with on die R

9. Cpad includes die capacitance only. No package parasitics are included.

10. R

IL is defined as the maximum voltage level at a receiving agent that is interpreted as a logical low

value.

IH is defined as the minimum voltage level at a receiving agent that is interpreted as a logical high

value.

IH and VOH may experience excursions above V

the signal quality specifications.

Measured at 0.31*V

these specifications is the instantaneous V

is the on-die termination resistance measured at VOL of the AGTL+ output driver. Measured at

TT

0.31*V

characteristics.

for PREQ# is between 1.5kΩ and 6.0kΩ

TT

I/O V o ltage 1.00 1.05 1.10 V

-2% 2/3 V

CCP

. R

TT

. R

CCP

(min) = 0.38*R

ON

is connected to V

and R

TT

CCP

. However , input signal drivers must comply with

CCP

R

(typ) = 0.45*R

TT,

CCP

ON

.

with a 1% tolerance resistor divider. The V

CCP

on die. Refer to processor I/O buffer models for I/V

CCP

are turne d off.

ON

CCP

TT,

2/3 V

R

ON

ICC max

+2% V 6

CCP

(max) = 0.52*R

referred to in

CCP

ICC [A

Notes

TT.

1

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

22 Order Nu mber: 315876 - 00 2

Page 23

Electrical Specifications—Intel

®

Cele r o n® Proc essor 1.66 G Hz/1.83 GHz

Table 8. AGTL+ Signal Group DC Specifications (Sheet 2 of 2)

VIH Input High Voltage GTLREF+100 V

IL Input Low Voltage -100 0 GTLREF-100 mV 2,4

V

VOH Output High Voltage V

R

Te rmination Resistance 45 50 55 Ω 7,10

TT

- 100 V

CCP

RON Buffe r On Resistance 22.3 25.5 28.7 W 5

ILI Input Leakage Current ± 100 µA 8

Cpad Pad Capacitance 1.8 2.3 2.75 pF 9

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. V

3. V

4. V

5. This is the pull down driver resistance. Refer to processor I/O Buffer Models for I/V characteristics.

6. GTLREF should be generated from V

7. R

8. Specified with on die R

9. Cpad includes die capacitance only. No package parasitics are included.

10. R

.

IL is defined as the maximum voltage level at a receiving agent that is interpreted as a logical low

value.

IH is defined as the minimum voltage level at a receiving agent that is interpreted as a logical high

value.

IH and VOH may experience excursions above V

the signal quality specifications.

Measured at 0.31*V

these specifications is the instantaneous V

is the on-die termination resistance measured at VOL of the A G TL+ out put driver. Mea sured at

TT

0.31*V

characteristics.

TT

. R

CCP

TT

for PREQ# is between 1.5kΩ and 6.0kΩ

. R

(min) = 0.38*R

CCP

ON

is connected to V

and R

TT

with a 1% tolerance resistor divider. The V

CCP

on die. Refer to processor I/O buffer models for I/V

CCP

are turned off.

ON

CCP

TT,

CCP

R

ON

.

CCP

. However, input signal drivers must comply with

(typ) = 0.45*R

Table 9. CMOS Signal Group DC Specifications

Symbol Parameter Min Typ Max Unit Notes

V

CCP

V

IL

IH Input High Voltage 0.7 1.05 1.20 V 2

V

VOL Output Low Voltage -0.1 0 0. 11 V 2

OH Output High Voltage 0.9 V

V

IOL Output Low Current 1.3 4.1 mA 4

IOH Output High Current 1.3 4.1 mA 5

I

LI

Cpad1 Pad Capacitance 1.8 2.3 2.75 pF 7

Cpad2

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. The V

3. Refer to the processor I/O Buffer Models for I/V characteristics.

4. Measured at 0.1*V

5. Measured at 0.9*V

6. For Vin between 0V and V

7. Cpad1 includes die capacitance only for PWRGOOD. No package parasitics are included.

8. Cpad2 includes die capacitance for all other CMOS input signals. No package parasitics are included.

I/O Voltage 0.997 1.05 1.102 V

Input Low Voltage

CMOS

-0.1 0 0.3 3 V 2, 3

CCP

Leakage Current ± 100 µA 6

Pad Capacitance for CMOS

Input

referred to in these specifications refers to instantaneous V

CCP

.

CCP

.

CCP

. Measured when the driv er is tristated.

CCP

0.95 1.2 1.45 pF 8

V

+100 mV 3,6

CCP

CCP

R

(max) = 0.52*R

TT,

ON

1.2 V 2

.

CCP

mV 6

TT.

referred to in

CCP

1

January 2007 DS

Order Nu mber: 315876 - 00 2 23

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 24

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Electrical Specifications

Table 10. Open Drain Signal Group DC Specifications

Symbol Parameter Min Typ Max Unit Notes

VOH Output High Voltage 1.0 1.05 1.10 V 3

VOL Output Low Voltage 0 0.20 V

IOL Output Low Current 11.4 50 mA 2

I

LEAK

Cpad Pad Capacitance 1.8 2.3 2.75 pF 5

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. Measured at 0.2 V

3. V

4. For Vin between 0 V and V

5. Cpad includes die capacitance only. No package parasitics are included.

Leakage Current ± 200 µA 4

is determined by value of the external pull-up resistor to V

OH

OH

.

CCP

1

.

®

Celero n® Processor 1.66 GHz/1. 83 GHz

Intel

DS January 2007

24 Order Nu mber: 315876 - 00 2

Page 25

Package Mechanical Specifications and Pin Information—Intel

1.83 GHz

®

Celeron® Processor 1.66 GHz/

4.0 Package Mechanical Specifications and Pin

Information

4.1 Package Mechanical Specifications

The Intel® Celeron® Processor 1.66 GHz/1.83 GHz is available in 478-pin Micro-FCPGA

(Micro- Flip Chip PGA) package.

4.1.1 Package Mechanical D r awings

Different views of the Micro-FCPGA package are shown in Figure 4, Figure 5, and

Figure 6.

Figure 4. Micro-FCPGA Pac k a ge Top and Bottom Views

January 2007 DS

Order Nu mber: 315876 - 00 2 25

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 26

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Package Mechanical Specifications and Pin

Figure 5. Micro-FCPGA Processor Package Drawing (Sheet 1)

Information

Note: All dimensions are in millimeters [inches]. Values shown for reference only.

®

Intel

Celero n® Processor 1.66 GHz/1. 83 GHz

DS January 2007

26 Order Nu mber: 315876 - 00 2

Page 27

Package Mechanical Specifications and Pin Information—Intel

1.83 GHz

®

Celeron® Processor 1.66 GHz/

Figure 6. Micro-FCPGA Processor Pack a ge Drawing (She et 2)

Note: All dimensions are in millimeters [inches]. Values shown for reference only.

4.1.2 Processor Component Keep-Out Zones

The processor may contain components on the substrate that define component keepout zone requi re ments. A the rmal and me chani cal sol uti on d esi gn m ust n ot in trud e i nto

the required keep-out zones. Decoupling capacitors are typically mounted in the keepout areas. The location and quantity of the capacitors may change, but remains within

the component keep-in. Refer to Figure 4, Figure 5, an d Figure 6 for keep-out zones.

January 2007 DS

Order Nu mber: 315876 - 00 2 27

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 28

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Package Mechanical Specifications and Pin

4.1.3 Package Loading Specifications

Maximum mechanical package loading specifications are given in Figure 5. These

specifications are static compressive loading in the direction normal to the processor.

This maximum load limit should not be exceeded during shipping conditions, standard

use condition, or by thermal solution. In addition, there are additional load limitations

against transient bend, shock, and tensile loading. These limitations are more platform

specific, and should be obtained by contacting your field support. Moreover, the

processor package substrate should not be used as a mechanical reference or loadbearing surface for thermal and mechanical solution.

4.1.4 Processor Mass Specifications

The typical mass of the processor is given in Figure 6. This mass includes all the

components that are included in the package.

4.2 Processor Pin-Out and Pin List

Figure 7 shows the top view pinout of the Intel® Celeron® Processor 1.66 GHz/1.83

GHz. The alphabetical pin listing is shown in Table 14. The alphabetical signal listing is

shown in Table 15.

Information

®

Intel

Celero n® Processor 1.66 GHz/1. 83 GHz

DS January 2007

28 Order Nu mber: 315876 - 00 2

Page 29

Package Mechanical Specifications and Pin Information—Intel

1.83 GHz

®

Celeron® Processor 1.66 GHz/

Figure 7. The Coordinates of the Processor Pins as Viewed From the Top of the Package

AF AE AD AC AB AA Y W V U T R P N M L K J H G F E D C B A

VID

SKT

1

[5]

OCC

VID

VID

2

[3]

[4]A[31]

VID

VID

3

[1]

[2]A[32]A[33]

PREQ#VID

4

5 VSS

6

BPM

[0]#

[0]

BPM

[3]#

VSS

7 VCC VCC VCC VCC

8 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

9 VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

10 VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

11 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

12 VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

A

VSS

[35]A[34]

VSS

VSS

A

[27]A[21]

VSS

[26]A[20]

VSS TDI TDO VSS

PRD

VSS TMS TCK VSS

Y#

BPM

[1]#

BPM

[2]#

VSS

VSS

SEN

TRS

T#

VCC

SEN

A

A

[29]A[30]

VSS

[28]A[25]

VSS

RSP#AP

[1]#

BINIT#AP

V

VSS V

CCP

A

VSS

[14]A[10]

VSS

A

[23]A[24]

VSS

[22]A[19]

VSS

[0]#

CCPVCCP

A

A

VSS

A

[13]A[12]

A

VSS

[16]A[9]#

VSS

A

RSV

[18]

D

ADSTBRSV

VSS

COMPCOMPA

VSS

[15]A[11]

VSS

[8]#

RSV

D

RSVDA[6]

VSS

A

A

[17]

ADSTBADS

VSS

D

VSS

BR0

#

VSS

A

VSS

[5]#A[4]#

REQ

[0]#A[7]#

VSS

#

MCE

VSS

RR#

BR1#BPRI

#

VSS

#

VSS

REQ

[3]#

HIT

M#

VSS

DEF

ER#

VSS

[3]#RS[0]#

REQ

REQ

[2]#

[4]#

REQ

VSS

[1]#

VSS

[2]#

TRDY#DRD

DBS

VSS

Y#

A

RS

Y#

VSS

RS

VSS

[1]#

BNR#HIT

LOC

VSS

K#

SMI#INIT

VSS

ODTENIGN

NE#

VCC VCC

#

RSVDRSV

D

RES

VSS

ET#

RSVDRSV

VSS

STP

RSVDLINT0PWR

CLK

VSS

#

A20M#LINT

VSS

RSVDSLP

#

RSVDFOR

CEP

VSS

D

GOO

FERR#THE

RMT

VSS

1

VCC VCC

13 VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC

14 VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS VCC VSS

15 VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

16 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

17 VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

18 VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC

19 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

BSE

20 VCC VCC VCC VCC V

21 VSS V

22 V

CCPVCCP

23 V

CCP

24 VSS

25 V

CCP

26 V

CCP

CCPVCCP

VSS

[60]D[59]

RSV

VSS

D

D

VSS V

VSS V

D

V

[63]

VSS

VSS

[57]D[46]

GTL

REFD[58]

CCP

CCP

D

CCPVCCP

D

CCP

[62]

D

VSS

[61]

DINVD

VSS

D

[56]D[47]

VSS

D

VSS

[44]D[42]

DSTBPDST

VSS

D

[54]D[53]

VSS

[55]

D

VSS

[43]D[41]

D

[45]D[40]

VSS

VSS

BN

D

VSS

[48]D[49]

D

[51]D[52]

VSS

D

VSS

[38]D[39]

DINVD

[35]

DSTBPDST

BN

VSS

D

VSS

[37]D[32]D[31]

D

RSV

[50]

D

VSS

COMPCOMPD

VSS

VSS

D

[33]

VSS

DP

[2]#

DSTBPDST

BN

D

VSS

[24]D[15]

VSS

D

[36]DP[3]#

DP

VSS

[1]#D[30]

VSS

[34]

DSTBPDST

VSS

VSS

D

[14]D[12]

D

VSS

[25]D[26]

VSS

DP

[0]#D[28]

VSS

BN

D

[11]D[10]

D

VSS

[13]D[9]#

VSS

D

DIN

[29]

V

D

VSS

[27]D[22]

VCC VCC

D

[5]#D[2]#

D

VSS

[6]#D[3]#

VSS

D

[23]D[20]

D

VSS

[21]D[18]

VSS

VSS

D

[8]#D[7]#

VSS

D

[19]D[16]

L[1]

D

[0]#

VSS

D

[17]

VSS

BSE

L[0]

IERR

#

D

[1]#

VSS

DIN

V

D

[4]#

VSS

VCC VCC

BSE

VSS

L[2]

THR

THR

MDA

MDC

TEST2VCC

TES

VSS

T1

PRO

VSS

CHO

BCL

BCL

K[0]

K[1]

A

January 2007 DS

Order Nu mber: 315876 - 00 2 29

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 30

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Package Mechanical Specifications and Pin

4.2.1 Alphabet i c al Si g na l s Re fer ence

Table 11. Signal Description (Sheet 1 of 7)

Name Type Description

A[35:3]# (Address) define a 2

phase 1 of the address phase, these pins transmit the address of a transaction.

A[35:3]#

Input/

Output

A20M# Input

ADS#

Input/

Output

In sub-phase 2, these pins transmit transaction type information. These signals

must connect the appropriate pins of both agents on the Intel

Processor 1.66 GHz/1.83 GHz FSB. A[35:3]# are source synchronous signals

and are latched into the receiving buffers by ADSTB[1:0]#. Address signals are

used as straps which are sampled before RESET# is deasserted.

If A20M# (Address-20 Mask) is asserted, the processor masks physical address

bit 20 (A20#) before looking up a line in any internal cache and before driving a

read /write transaction on the bus. Asserti ng A20M# emulates the 8086

processor's address wrap-around at the 1-Mbyte boundary. Assertion of A20M#

is only supported in real mode.

A20M# is an asynchronous signal. However, to ensure recognition of this signal

following an Input/Output write instruction, it must be valid along with the

TRDY# assertion of the corresponding Input/Output Write bus transaction.

ADS# (Address Strobe) is asserted to indicate the validity of the transaction

address on the A[31:3]# and REQ[4:0]# pins. All bus agents observe the ADS#

activation to begin parity checking, protocol checking, address decode, internal

snoop, or deferred reply ID match operations associated with the new

transaction.

Address strobes are used to latch A[31:3]# and REQ[4:0]# on their rising and

falling edges. Strobes are associated with signals as shown below.

Information

36

-byte physical memory address space. In sub-

®

Celeron®

ADSTB[1:0]#

AP[1:0]#

Input/

Output

Input/

Output

BCLK[1:0] Input

Signals Associated Strobe

REQ[4:0]#, A[16:3]# ADSTB[0]#

A[35:17]# ADSTB[1]#

AP[1:0]# (Address Parity) are driven by the request initiator along with ADS#,

A[31:3]#, and the transaction type on the REQ[4:0]# pins. A correct parity

signal is high if an even number of covered signals are low and low if an odd

number of covered signals are low. This allows parity to be high when all the

covered signals are high. AP[1:0]# should connect the appropriate pins of all

front side bus agents. The following table defines the coverage model of these

signals.

Request Signals Subphas e 1 Subphase 2

A[35:24]# AP0# AP1#

A[23:3]# AP1# AP0#

REQ[4:0]# AP1# AP0#

The differential pair BCLK (Bus Clock) determines the FSB frequency. All FSB

agents must receive these signals to drive their outputs and latch their inputs.

All external timing parameters are specified with respect to the rising edge of

BCLK0 crossing V

CROSS

.

®

Intel

Celero n® Processor 1.66 GHz/1. 83 GHz

DS January 2007

30 Order Nu mber: 315876 - 00 2

Page 31

Package Mechanical Specifications and Pin Information—Intel

1.83 GHz

Table 11. Signal Description (Sheet 2 of 7)

Name Type Description

BINIT# (Bus Initialization) may be observed and driven by all processor front

side bus agents and if used, must connect the appropriate pins of all such

agents. If the BINIT# driver is enabled during power on configuration, BINIT# is

asserted to signal any bus condition that prevents reliable future information.

If BINIT# observation is enabled during power-on configuration and BINIT# is

BINIT#

BNR#

BPM[2:1]#

BPM[3,0]#

Input/

Output

Input/

Output

Output

Input/

Output

BPRI# Input

BR0#

Input/

Output

BSEL[2:0] Output

COMP[3:0] Analog

sampled asserted, symm et ric agents reset their bus LOCK# activit y and bus

request arbitration state machines. The bus agents do not reset their IOQ and

transaction tracking state machines upon observation of BINIT# assertion. Once

the BIN IT# assertion has been observed, the bus agents re- a rbitrate f o r the

front side bus and attempt completion of their bus queue and IOQ entries.

If BINIT# observation is disabled during power-on configuration, a central agent

may ha ndle an assertion of BINIT# as appropriate to the error handling

architecture of the system.

BNR# (Block Next Request) is used to assert a bus stall by any bus agent who is

unable to accept new bus transactions. During a bus stall, the current bus owner

cannot issue any new transactions.

BPM[3:0]# (Breakpoint Monitor) are breakpoint and performance monitor

signals. They are outputs from the processor which indicate the status of

breakpoints and programmable counters used for monitoring processor

performance. BPM[3:0]# should connect the appropriate pins of all Intel

®

Celeron

performan ce moni t ori ng tools.

BPRI# (Bus Priority Request) is used to arbitrate for ownership of the FSB. It

must connect the appropriate pins of all FSB agents. Observing BPRI# active (as

asserted by the priority agent) causes the other agent to stop issuing new

requests, unless such requests are part of an ongoing locked operation. The

priority agent keeps BPRI# asserted until all of its requests are completed, then

releases the bus by deasserting BPRI#.

The BR0# (Bus Request 0) pin drives the BREQ[0]# signals in the system. The

BREQ[0]# signal is directly connected to the processor (symmetric agent) and

the Memory Controller Hub - MCH (priority agent).

BSEL[2:0] (Bus Select) are used to select the processor input clock frequency.

T a ble 3 defines the possible combinations of the signals and the frequency

associated with each combination. The required frequency is determined by the

processor, chipset and clock synthesizer. All agents must operate at the same

frequency. The Intel

MHz system bus frequency (166 MHz BCLK[2:0] frequency respectively).

COMP[3:0] must be terminated on the system board using precision (1%

toleran ce) resistors.

Processor 1.66 GHz/1. 83 GHz FSB agents.T his includes debug or

®

Celeron® Processor 1.66 GHz/

®

Celeron® Process o r 1.66 GHz/1.83 GHz operates at 667

®

January 2007 DS

Order Nu mber: 315876 - 00 2 31

Intel® Celeron® Process or 1.66 GHz/1.83 GHz

Page 32

Intel® Celeron® Processor 1.66 GHz/1.83 GHz—Package Mechanical Specifications and Pin

Table 11. Signal Description (Sheet 3 of 7)

Name Type Description

D[63:0]# (D ata) are the dat a signals. Thes e signals provi de a 64-bit data path

between the FSB agents, and must connect the appropriate pins on both agents.

The data driver asserts DRDY# to indicate a valid data transfer .

D[63:0]# are quad-pumped signals and is thus be driven four times in a

common clock period. D[63:0]# are latched off the falling edge of both

DSTBP[3:0]# and DSTBN[3:0]#. Each group of 16 data signals correspond to a

pair of one DSTBP# and one DSTBN#. The following table shows the grouping of

data signals to data strobes and DINV#.

Table 12. Qu ad-Pu mped Signal Groups

Information

D[63:0]#

DBSY#

DEFER# Input

DP[3:0]#

Input/

Output

Input/

Output

Input/

Output

Data Group

D[15:0]# 0 0

D[31:16]# 1 1

D[47:32]# 2 2

D[63:48]# 3 3

Furthermore, the DINV# pins determine the polarity of the data signals. Each

group of 16 data signals corresponds to one DINV# signal. When the DINV#

signal is active, the corresponding data group is inverted and therefore sampled

active hig h .

DBSY# (Data Bus Busy) is asserted by the agent responsible for driving data on

the FSB to indic ate that the data bus is in use. The data bus i s released after

DBSY# is deasserted. This signal must connect the appropriate pins on both FSB

agents.

DEFER # is asserted by an agent to indicate that a transaction cannot be

guaranteed in-order completion. Assertion of DEFER# is normally the

responsibility of the addressed memory or Input/Output agent. This signal must

connect the appropriate pins of all FSB agents.

DP[3:0]# (Data Parity) provide parity protection for the D[63:0]# signals. They

are driven by the agent responsible for driving D[63:0]#, and must connect the

appropriate pins of all processor front side bus agents.

DINV[3:0]# (Data Bus Inversion) are source synchronous and indicate the

polarity of the D[63:0]# signals. The DINV[3:0]# signals are activated when the

data on the data bus is inverted. The bus agent inverts the data bus signals if

more than half the bits, within the covered group, change level in the next cycle.

DSTBN#/

DSTBP#

DINV#

Table 13. DINV[3:0]# Assignmen t To Da ta Bu s

DINV[3:0]#

DRDY#

®

Intel

Celero n® Processor 1.66 GHz/1. 83 GHz

DS January 2007

32 Order Nu mber: 315876 - 00 2

Input/

Output

Input/

Output

Bus Signal Data Bus Signals

DINV[3]# D[63:48]#

DINV[2]# D[47:32]#

DINV[1]# D[31:16]#

DINV[0]# D[15:0]#

DRDY# (Data Ready) is asserted by the data driver on each data transfer,

indicating valid data on the data bus. In a multi-common clock data transfer,

DRDY# may be deasserted to insert idle clocks. This signal must connect the

appropriate pins of both FSB agents.

Page 33

Package Mechanical Specifications and Pin Information—Intel

1.83 GHz

Table 11. Signal Description (Sheet 4 of 7)

Name Type Description

Data st robe used to latc h in D[63:0]#.

Signals Associated Stro be

D[15:0]#, DINV[0 ]# DSTBN [0]#

D[31:16]#, DINV[1]# DSTBN[1]#

D[47:32]#, DINV[2]# DSTBN[2]#

D[63:48]#, DINV[3]# DSTBN[3]#

Data st robe used to latc h in D[63:0]#.

Signals Associated Stro be