Page 1

A

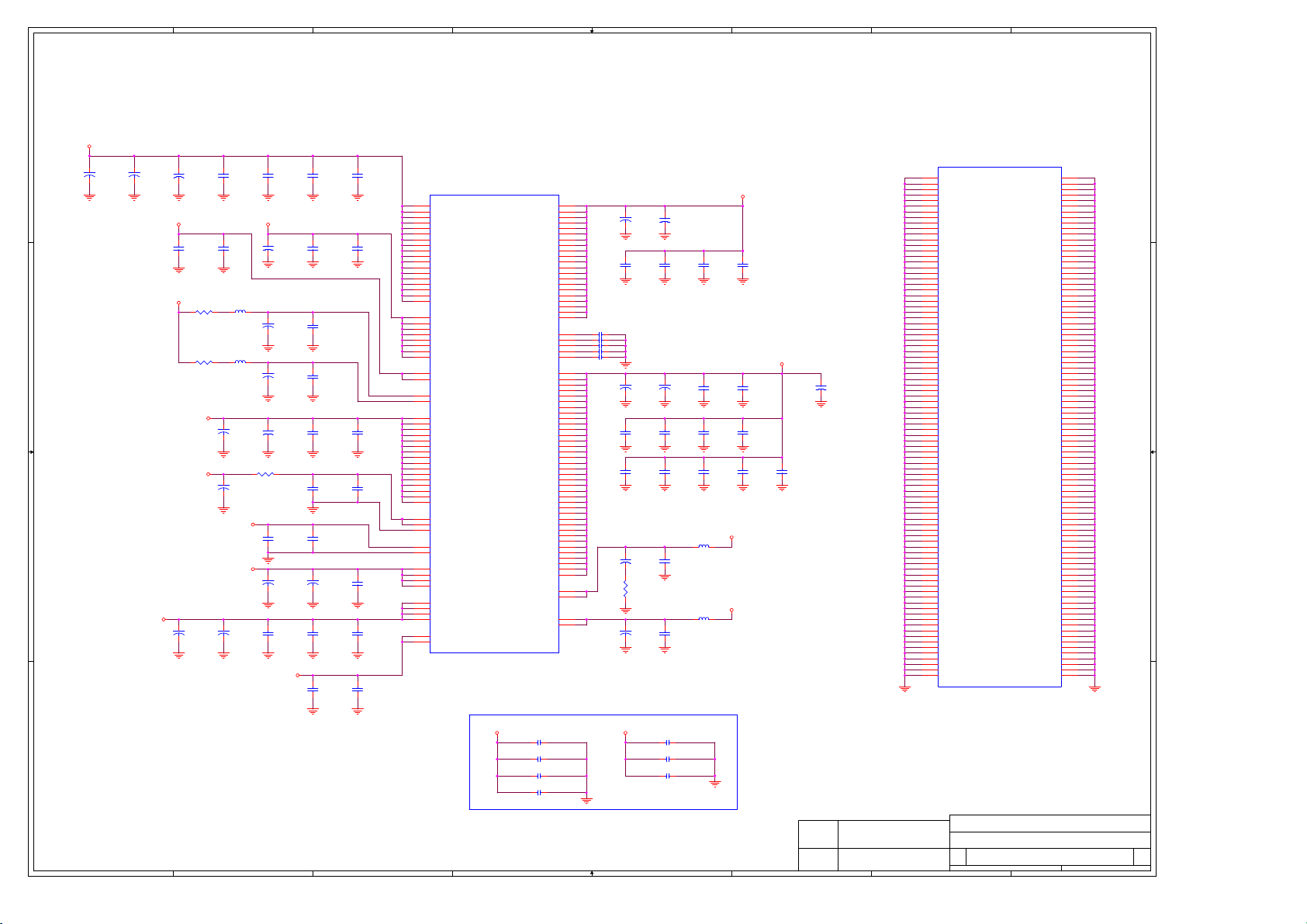

INTEL(R) 852GME REFERENCE DESIGN

B

PEB-7710VLA-R2

C

D

E

F

G

H

TITLE

A A

B B

C C

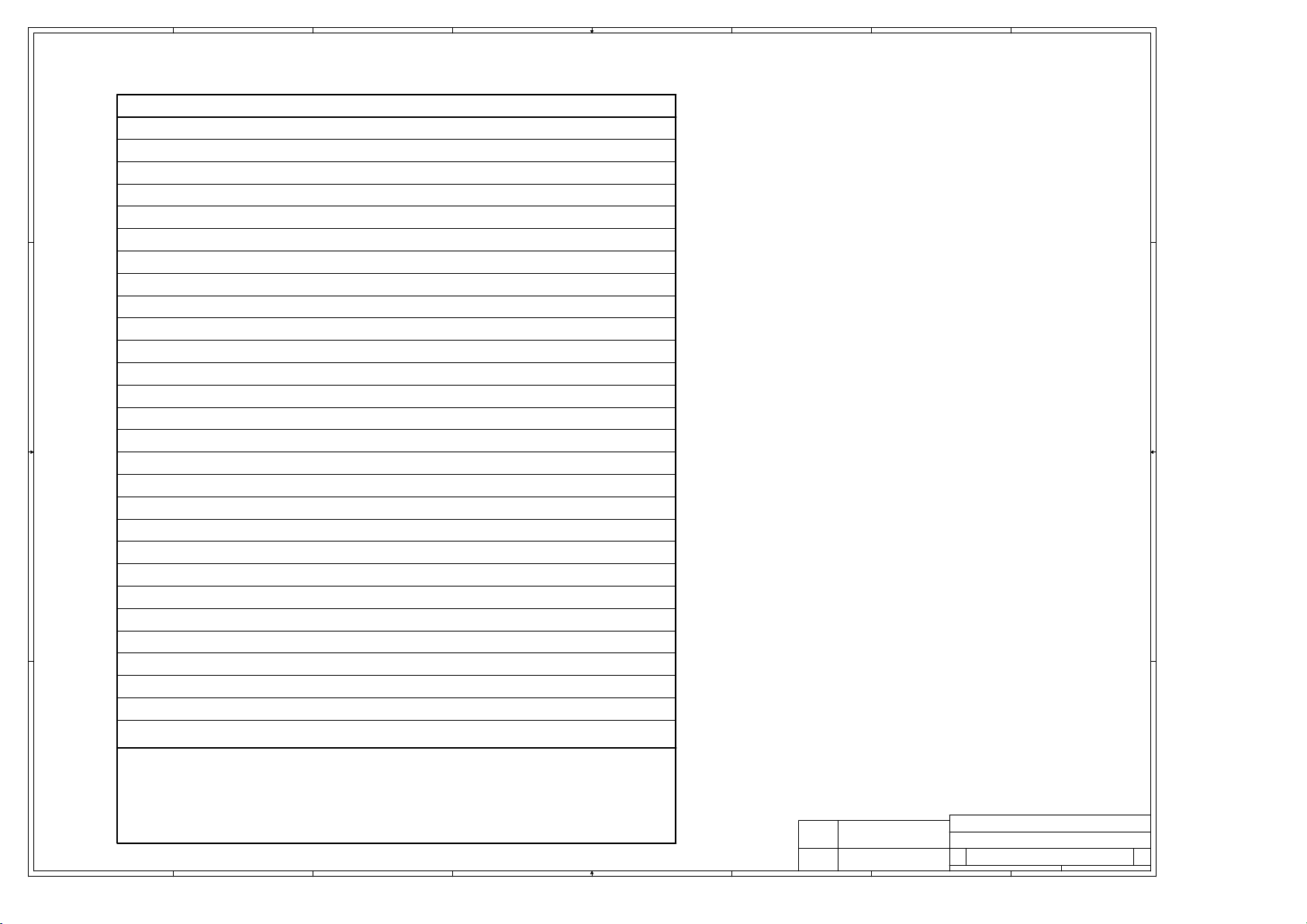

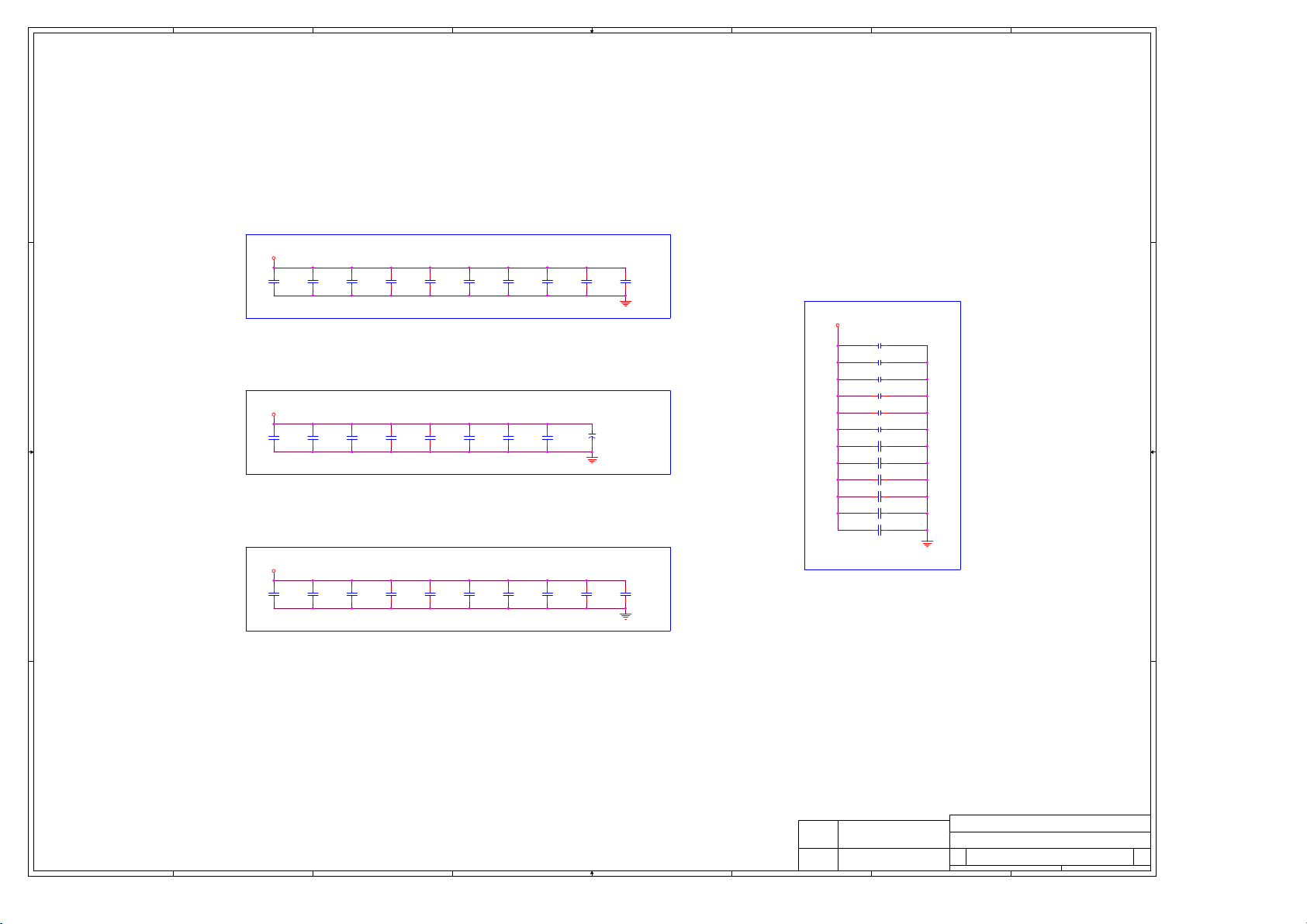

COVER SHEET

BLOCK DIAGRAM

PENTIUM(R) 4 PROCESSOR PART A & B & C

CLOCK SYNTHESIZER

852GME PART A & B & C

DDR-SERIES-TERMINATION_1&2

DIMM_1 & DIMM_2

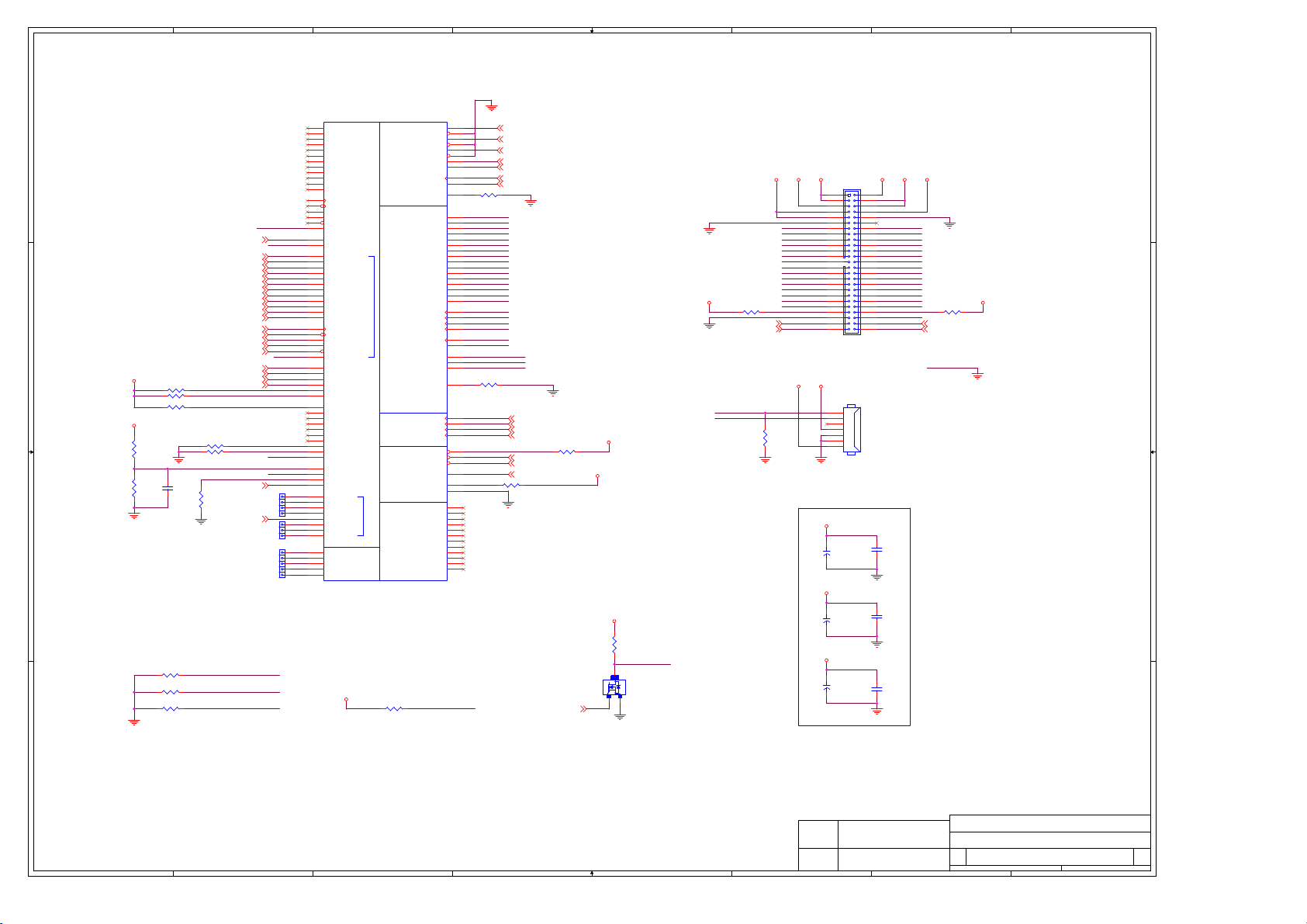

82801DB PART 1 & 2 & 3

FWH & IDE

LPC-W83627_1

LPC-W83627_2

H/W MONITOR & FAN CONN.

COM1 & COM2

COM3 & COM4

PRN & K/B & M/S & IR

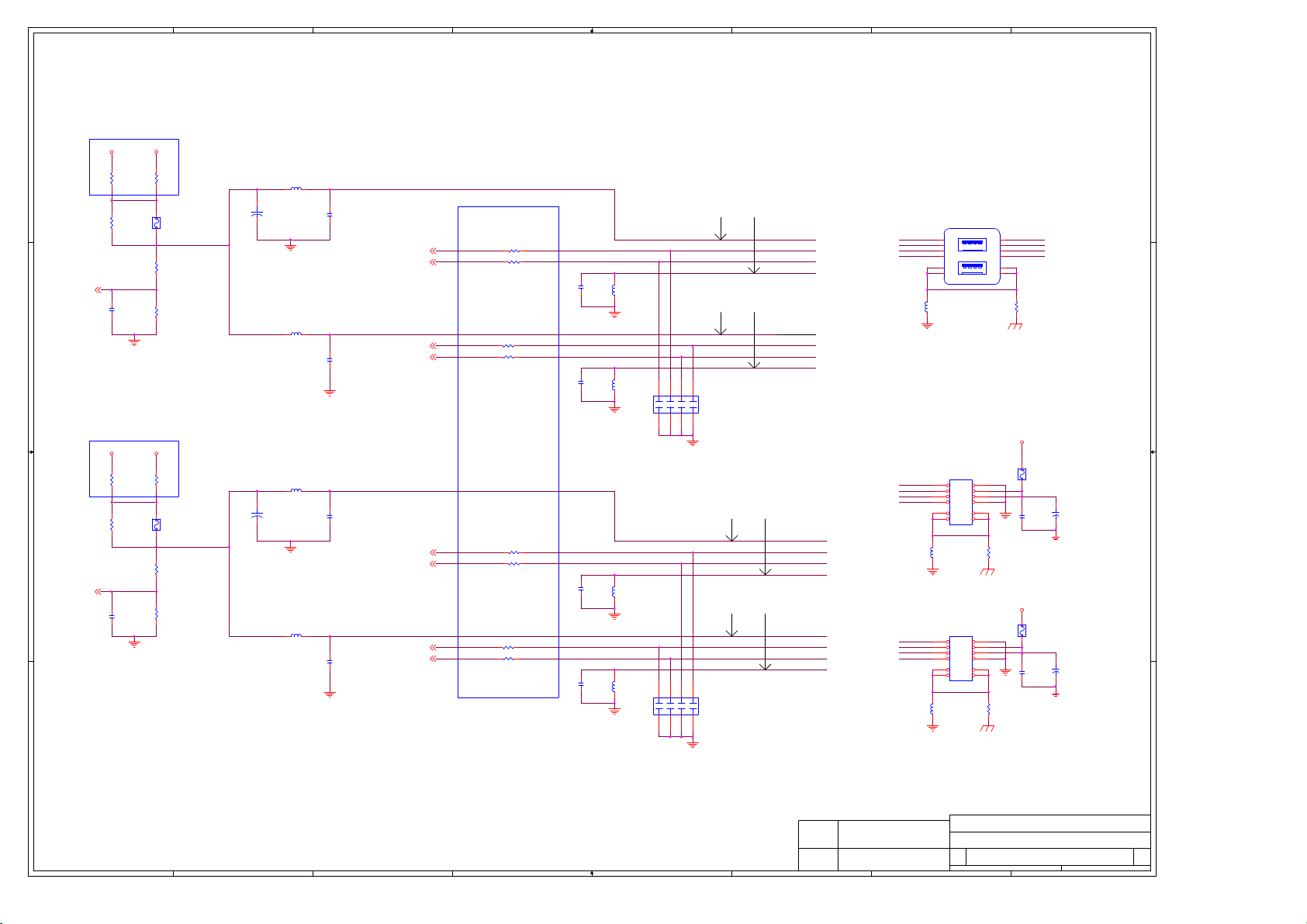

USB_1-6

AUDIO

CRT CONN.

DVI CONN.

LAN 82540/551/562EX

LAN CONN.

PCI RISER

PAGE

1

2

3,4,5

6

7,8,9

10,11

12

13,14,15

16

17

18

19

20

21

22

23,24

25

26

27

28

29

30

31CPU POWER

DDR POWER

32

33MISC. POWER

GMCH POWER

MISC. CONN. & PWROK

DECOUPLING

34

35

36

D D

Naming Rule for Part Value :

/6 0603 Package size /1 1% resistor

/8 0805 Package size /X Not stuffed

/10 1210 Package size

/12 1206 Package size

/18 1812 Package size

A

B

C

Note : Qualities of all Ceramic capacitors

used in this schematic should be equal or

better than X5R grade.

D

Revised

E

Issued

F

Title

COVER SHEET

Size Document Number Rev

Date: Sheet of

G

1 36Sunday, October 12, 2003

H

Page 2

A

INTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

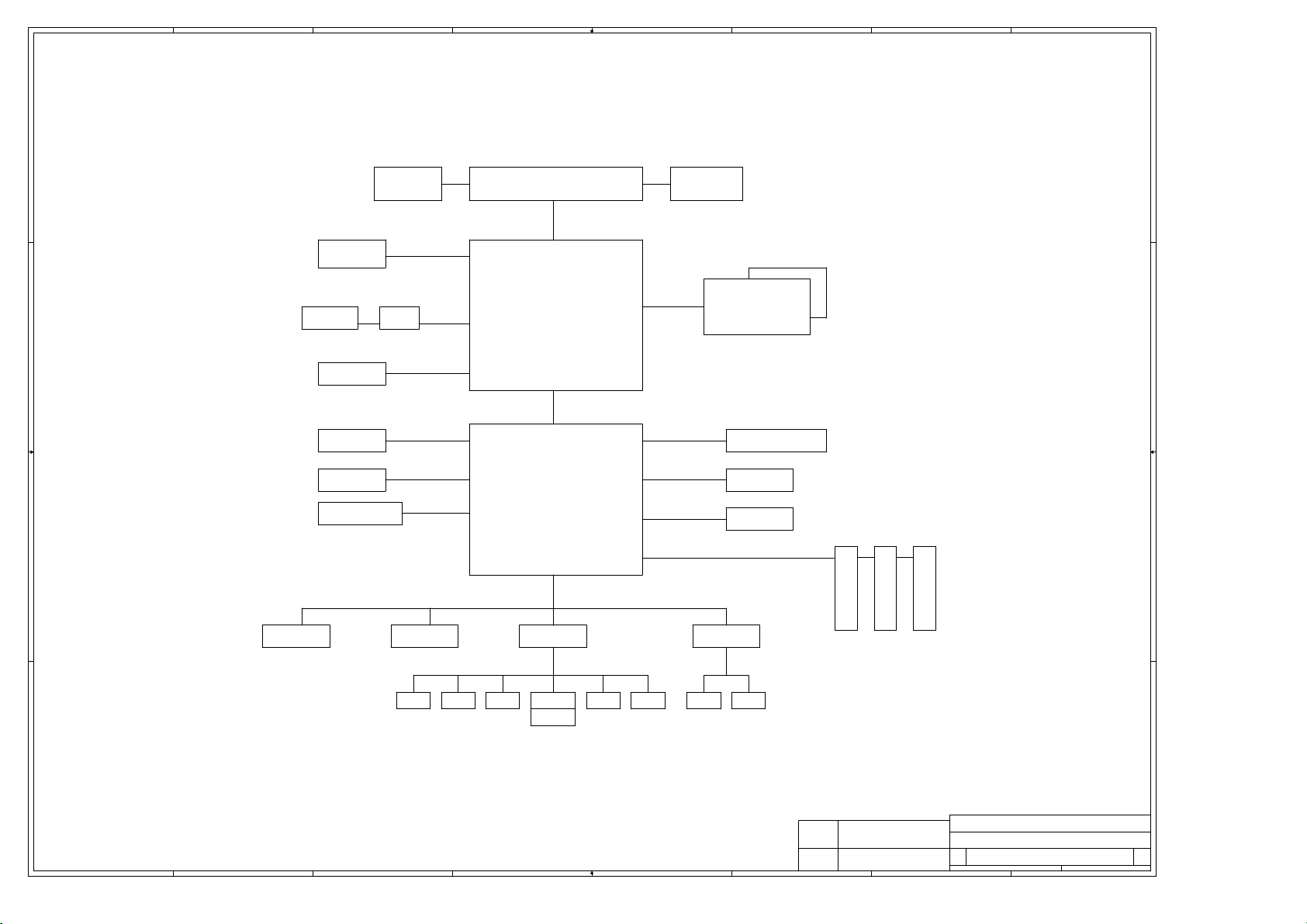

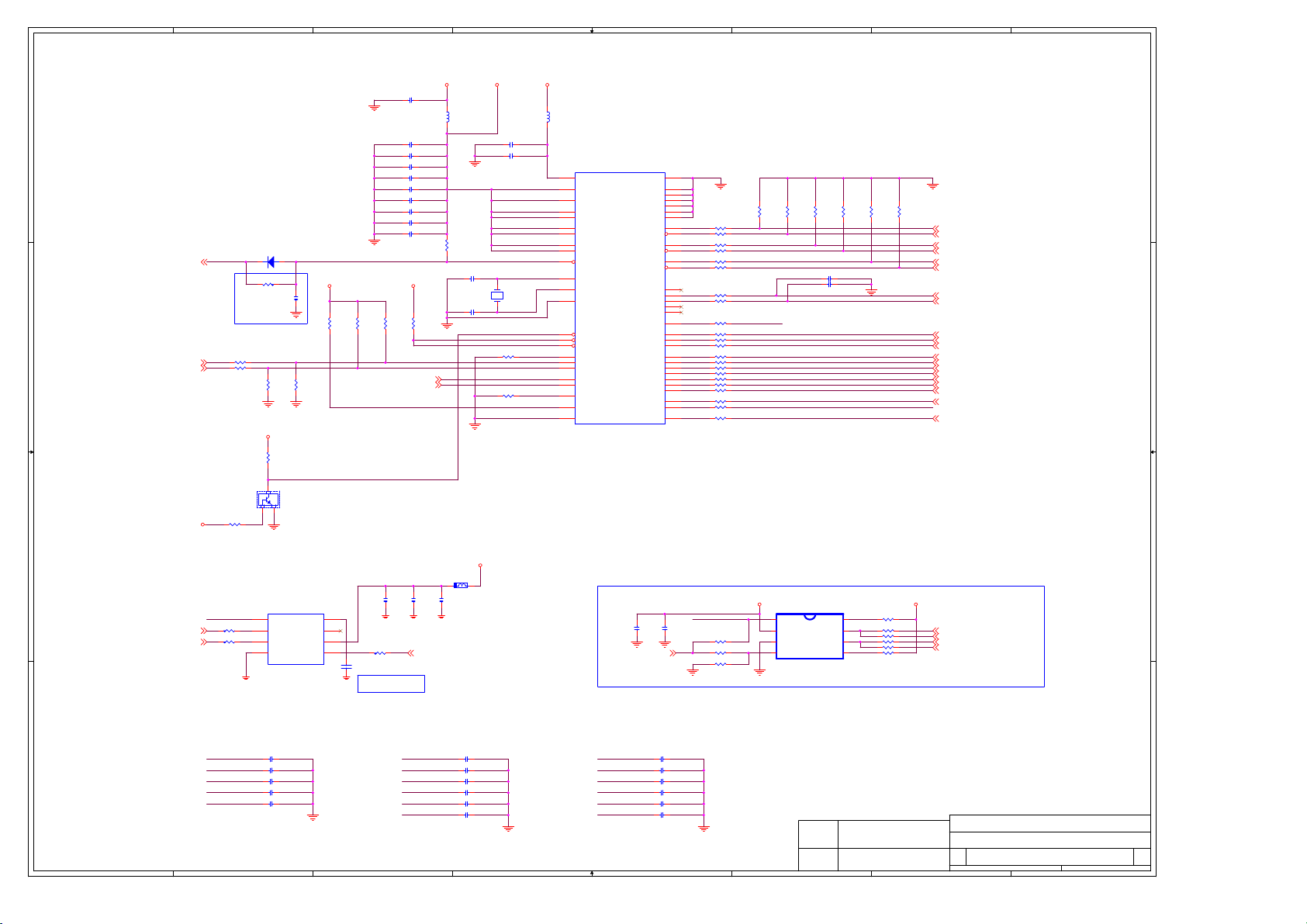

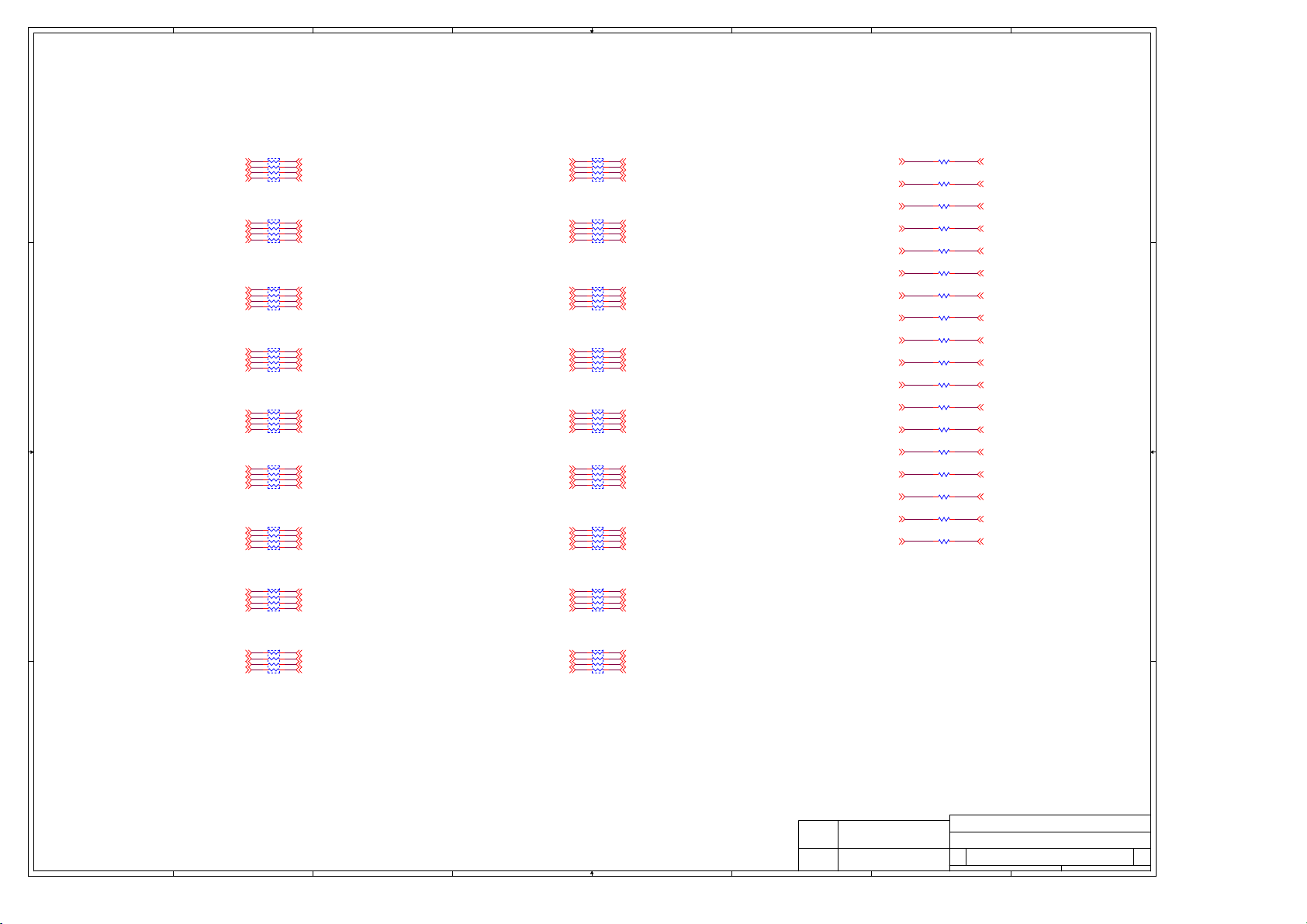

BLOCK DIAGRAM

A A

PENTIUM (R) 4 PROCESSORVRM 10.0 CK_408

P.3.4.5 P.06

LVDS-CONN.

P.31

P.08

DDR200/266/333

DVI-CONN.

B B

15-Pin D-Sub

ATA100 X 2

SiI-164

P.27

P.26

DVOB

P.27

852GME

P.7.8.9

HUB 1.5

PCI BUS

USB 2.0 X 4

PowerUSB X 2

C C

82801DB

PCU BUS

P.13.14.15

LPC

Modules

LAN_540/551/562EZ

AC97-ALC201

LM85

P.12

PCI RISER SLOT

Slot_1

Slot_2

Slot_3

TPM

D D

FWH W83627-1 W83627-2

IrDA

Keyboard Serial_3Floppy

Mouse

Serial_2

Serial_1Parallel Serial_4

AD:31 AD:29

A

C

F

G

Revised

A

B

C

D

E

Issued

F

AD:27

C

F

F

G

G

A

A

C

Title

BLOCK DIAGRAM

Size Document Number Rev

Date: Sheet of

G

2 36Sunday, October 12, 2003

H

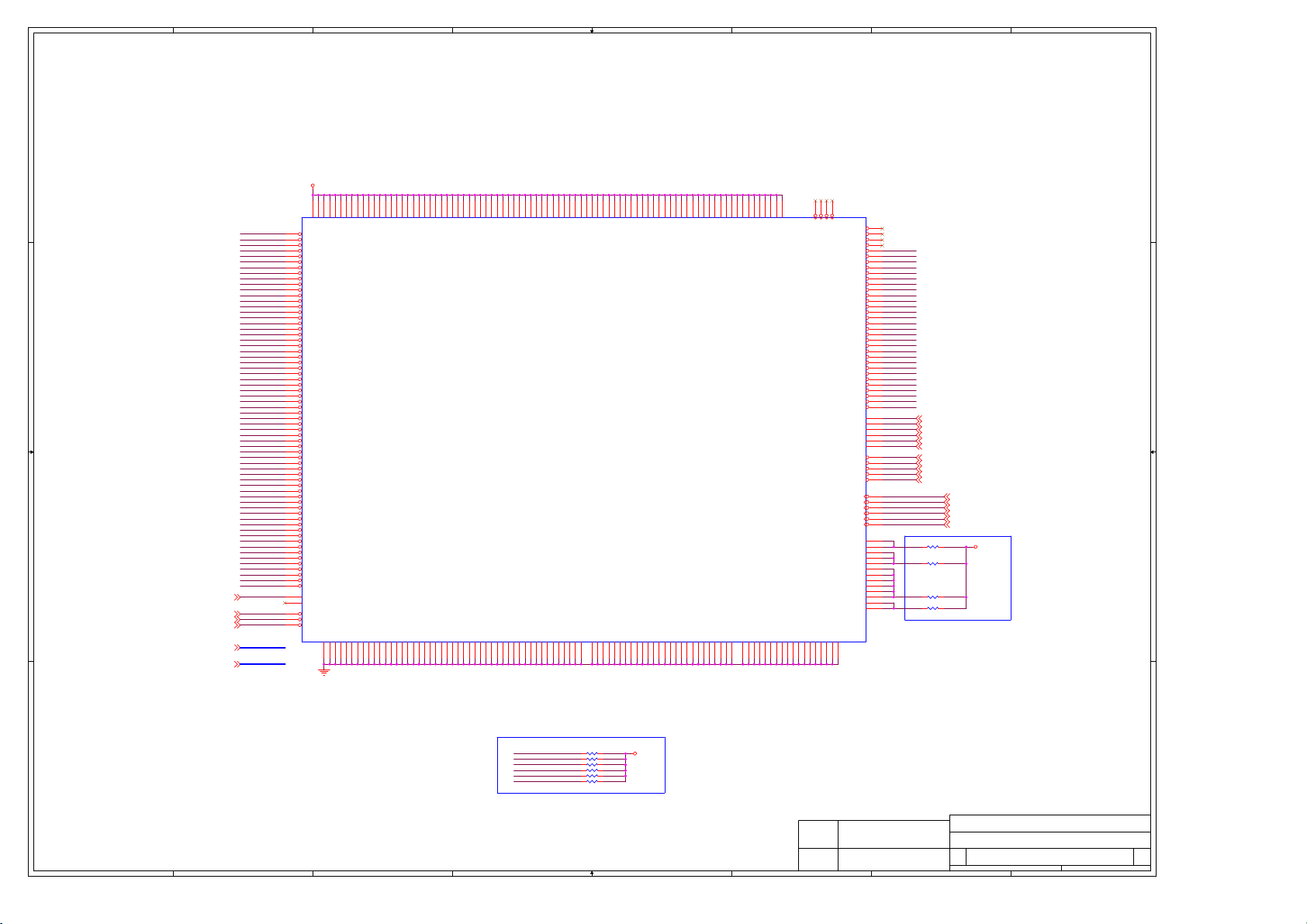

Page 3

A

INTEL(R) 852GME REFERENCE DESIGN

A A

B

C

D

E

F

G

H

VCCP

J26

K25

K26

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

E20E8F11

F13

F15

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9 H_A#25

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

B B

C C

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

BOOTSEL31

H_RS0#7

H_RS1#7

H_RS2#7

H_D#[0..63]

H_D#[0..63]7

H_A#[3..31]7

H_A#[3..31]

W26

W25

AA25

AA22

AA24

AD1

AF26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

AF18

VSS

AF20

VSS

VCC

VSS

VSS

VSS

VSS

VSS

AF6

AF8

B10

B12

B14

B21

D0

B22

D1

A23

D2

A25

D3

C21

D4

D22

D5

B24

D6

C23

D7

C24

D8

B25

D9

G22

D10

H21

D11

C26

D12

D23

D13

J21

D14

D25

D15

H22

D16

E24

D17

G23

D18

F23

D19

F24

D20

E25

D21

F26

D22

D26

D23

L21

D24

G26

D25

H24

D26

M21

D27

L22

D28

J24

D29

K23

D30

H25

D31

M23

D32

N22

D33

P21

D34

M24

D35

N23

D36

M26

D37

N26

D38

N25

D39

R21

D40

P24

D41

R25

D42

R24

D43

T26

D44

T25

D45

T22

D46

T23

D47

U26

D48

U24

D49

U23

D50

V25

D51

U21

D52

V22

D53

V24

D54

D55

Y26

D56

D57

Y23

D58

Y24

D59

Y21

D60

D61

D62

D63

BOOTSEL

SKTOCC#

F1

RS0

G5

RS1

F4

RS2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H1H4H23

H26

A11

A13

VSS

A15

A17

A19

A21

A24

A26A3A9

PENTIUM (R) 4 PROCESSOR (478-PIN)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA26

VSS

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AB18

VSS

AB20

VSS

AB21

VSS

VSS

AB24

U20A

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC2

AC22

AC25

AC5

AC7

AC9

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

VSS

AE7

AE9

AF1

AF10

AF12

AF14

AF16

L25

F17

F19

VCC

VCC

F9

VCC

DEP3

DEP2

DEP1

DEP0

REQ4

REQ3

REQ2

REQ1

REQ0

BPM5

BPM4

BPM3

BPM2

BPM1

BPM0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

VID0

VID1

VID2

VID3

VID4

VID5

AB1

A35

Y1

A34

W2

A33

V3

A32

H_A#31

U4

A31

H_A#30

T5

A30

H_A#29

W1

A29

H_A#28

R6

A28

H_A#27

V2

A27

H_A#26

T4

A26

U3

A25

H_A#24

P6

A24

H_A#23

U1

A23

H_A#22

T2

A22

H_A#21

R3

A21

H_A#20

P4

A20

H_A#19

P3

A19

H_A#18

R2

A18

H_A#17

T1

A17

H_A#16

N5

A16

H_A#15

N4

A15

H_A#14

N2

A14

H_A#13

M1

A13

H_A#12

N1

A12

H_A#11

M4

A11

H_A#10

M3

A10

H_A#9

L2

A9

H_A#8

M6

A8

H_A#7

L3

A7

H_A#6

K1

A6

H_A#5

L6

A5

H_A#4

K4

A4

H_A#3

K2

A3

AE5

AE4

AE3

AE2

AE1

AD3

H3

J3

J4

K5

J1

AB4

AA5

Y6

AC4

AB5

AC6

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

H_BPRM5_PREQ#

H_BPRM4_PRDY#

H_BPM3

H_BPM2

H_BPM1

H_BPM0

R253 51/6

R277 51/6

R256 51/6

R234 51/6

CPUVID0 19,31

CPUVID1 19,31

CPUVID2 19,31

CPUVID3 19,31

CPUVID4 19,31

CPUVID5 31

H_REQ#4 7

H_REQ#3 7

H_REQ#2 7

H_REQ#1 7

H_REQ#0 7

H_BPRM5_PREQ# 4

H_BPRM4_PRDY# 4

H_BPM3 4

H_BPM2 4

H_BPM1 4

H_BPM0 4

VCCP

Close to CPU

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B16

B18

B20

B23

B26B4B8

VSS

C11

C13

C15

C17

C19

C2

Close to CPU

H_BPRM5_PREQ#

H_BPRM4_PRDY#

H_BPM3

D D

A

B

C

H_BPM2

H_BPM1

H_BPM0

D

R266 51/6

R216 51/6

R211 51/6

R222 51/6

R221 51/6

R215 51/6

VCCP

Revised

E

Issued

F

Title

P4-478PIN_A

Size Document Number Rev

Date: Sheet of

G

3 36Sunday, October 12, 2003

H

R2

Page 4

A

INTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

GTLREF GENERATION CIRCUITS

R326

49.9/6/1

C356

1U/6

62/6/X

R369 0/6

Near ICH4

C288

0.1U/6

R300

100/6/1

VCCP

H_FERR# 13

H_STPCLK# 13

H_INIT# 13,16

H_DBSY# 7

H_DRDY# 7

H_TRDY# 7

H_ADS# 7

H_LOCK# 7

H_BREQ0# 7

H_BNR# 7

H_HIT# 7

H_HITM# 7

H_BPRI# 7

H_DEFER# 7

H_IGNNE# 13

H_SMI# 13

H_A20M# 13

H_SLP# 13

H_PWRGD 13

H_CPURST# 7

C_TEMP 19

C_TEMP# 19

THERMTRIP# 14

H_BSEL0 6

H_BSEL1 6

CPU_VCCVID 33

F6

IERR

MCERR

FERR

STPCLK

GTLREF3

BINIT

DBSY

DRDY

TRDY

LOCK

HITM

BPRI

DEFER

TRST

TDO

PROCHOT

IGNNE

A20M

RESET

THERMDA

THERMDC

BSEL0

BSEL1

VCCVID

VSS

VSS

VSS

R1

R23

R26

RSP

ADS

BR0

BNR

TCK

TMS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C345

220P/6

AC3

R653

V6

B6

Y4

AA3

W5

INIT

AB2

H5

H2

J6

G1

G4

H_BREQ0#

H6

G2

F3

HIT

E3

D2

E2

H_TCK

D4

H_TDI

C1

TDI

H_TMS

F7

H_TRST

E6

H_TDO

D5

C3

B2

B5

SMI

C6

AB26

SLP

H_PWRGD

AB23

H_CPURST#

AB25

B3

C4

A2

AD6

AD5

AC1

AP0

V5

AP1

AF4

AF3

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

A A

F20

AA6

C25C5C7C9D10

D12

D14

D16

D18

VCCIOPLL

AE23

VCCIOPLL

VCCA H_FERR#

AD20

VSSA

VCCP

R262 51/6/X

R257 51/6/X

H_DBI3#7

H_DBI2#7

H_DBI1#7

H_DBI0#7

H_ADSTB1#7

H_ADSTB0#7

RESET14,35

CPUHCLK0#6

B B

C C

CPUHCLK06

H_DSTBP3#7

H_DSTBP2#7

H_DSTBP1#7

H_DSTBP0#7

H_DSTBN3#7

H_DSTBN2#7

H_DSTBN1#7

H_DSTBN0#7

H_NMI13

H_INTR13

R235 330/6/X

D35 RB751V-40/S

R284 51.1/6/1

R328 51.1/6/1

VCCSENSE31

VSSSENSE31

AD22

AC26

AD26

V21

P26

G25

E21

R5

L5

DBRESET#

AE25

E5

D1

AF23

AF22

P1

L24

W23

P23

J23

F21

W22

R22

K22

E22

A5

A4

E11

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

F8

G21

G24

G3 R4

VSS

VCCA

VSSA

ITP_CLK0

ITP_CLK1

DB#3

DB#2

DB#1

DB#0

ADSTB1

ADSTB0

DBRESET

LINT1

LINT0

BCLK1

BCLK0

PENTIUM (4) PROCESSOR (478-PIN)

COMP1

COMP0

STBP3

STBP2

STBP1

STBP0

STBN3

STBN2

STBN1

STBN0

VCC_SENSE

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS

VSS

VSS

J2

J22

J25J5K21

G6

VSS

VSS

VSS

VSS

VSS

U20B

VSS

VSS

VSS

VSS

VSS

K24K3K6L1L23

VSS

VSS

L26L4M2

VSS

VSS

VSS

VSS

D20

VSS

VSS

D21

VSS

VSS

M22

D24D3D6

VSS

VSS

VSS

VSS

M25M5N21

D8

E1

C22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N24N3N6P2P22

AA21

GTLREF0

VSS

VSS

P25

GTLREF2

GTLREF1

PWRGOOD

THERMTRIP

VCCVIDPRG

VSS

VSS

P5

CPU SIGNAL TERMINATION

H_BREQ0#

R329 220/6

H_PWRGD

R275 300/6

CLOSE TO CPU

H_TDI

H_TRST

R352 150/6

R367 680/6

VCCP

CLOSE TO CPU

ITP/TAP TERMINATION

H_TMS

R345 39/6/1

R263 51/6

H_CPURST#

R368 75/6/1

H_TDO

R349 27.4/6/1

H_TCK

R254 150/6

DBRESET#

VCCPVCCP

VCCP

+V3.3

ITP Debug Port

J28

H_BPM0 DBA#

H_BPM03

H_BPM1

H_BPM13

H_BPM2

H_BPM23

H_BPM3

H_BPM33

VCCP

L5

4.7UH/8

L6

D D

4.7UH/8

1) Capacitors should be within 600mils of VCCA & VSSA pins

2) Traces > 12mils

3) L should be close to C

4) VCCA parallel & next to VSSA route (Minimize loop area)

BC1

0.1U/6

BC2

0.1U/6

1

+

+

EC39

47U/2.5V

EC42

47U/2.5V

1

VCCA

VSSA

VCCIOPLL

H_BPRM4_PRDY#3

H_BPRM5_PREQ#3

H_BPRM4_PRDY#

H_BPRM5_PREQ#

H_CPURST#

ITPCLK

ITPCLK6

ITPCLK#

ITPCLK#6

R542 150/6

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

Header_2X13

DBRESET#

H_TDI

H_TMS

H_TRST

H_TCK

ITP_STPWR

H_TDO

Revised

A

B

C

D

E

Issued

F

R574

VCCP

150/6

R573

VCCP

1K/6

Title

P4-478PIN_B

Size Document Number Rev

Date: Sheet of

G

4 36Sunday, October 12, 2003

H

Page 5

A

INTEL(R) 852GME REFERENCE DESIGN

A A

B

C

D

E

F

G

H

Put the cap on the North side of the processor

VCCP

C262

10U/12

C272

10U/12

C440

10U/12

C434

10U/12

C433

10U/12

C281

10U/12

C344

10U/12

C379

10U/12

C438

10U/12

C264

10U/12

Reserve on CPU bottom side

VCCP

B B

Put the cap in the processor cavity

VCCP

1

C273

10U/12

C284

10U/12

C435

10U/12

C280

10U/12

C274

10U/12

C263

10U/12

C436

10U/12

C347

10U/12

+

EC48

220U/4V

Put the cap on the sourth side of the processor

C C

VCCP

C282

10U/12

C285

10U/12

C437

10U/12

C439

10U/12

C279

10U/12

C261

10U/12

C380

10U/12

C348

10U/12

C283

10U/12

C286

10U/12

C697 0.1U/6/X

C698 0.1U/6/X

C699 0.1U/6/X

C700 0.1U/6/X

C701 0.1U/6/X

C702 0.1U/6/X

C703

10U/12/X

C705

10U/12/X

C707

10U/12/X

C709

10U/12/X

C711

10U/12/X

C712

10U/12/X

D D

Revised

A

B

C

D

E

Issued

F

Title

P4 CAPACITORS

Size Document Number Rev

Date: Sheet of

G

5 36Sunday, October 12, 2003

H

Page 6

A

INTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

+V3.3

CK_VDD

+V3.3

C787 1U/6

FB53

300/2012/3A

A A

SLP_S3#14,17,18,32,33

B B

H_BSEL04

H_BSEL14

D16 RB751V-40/S

R308 10K/6/X

Delay > 5 PCICLKs

R213

0/6

R622 0/6/X

C349

1U/6/X

R623

1K/6/X

R202

1K/6/X

CK_VDD

R333

10K/6

R338

1K/6

C363

C366

C372

C364

C365

C317

C318

C319

C362

R322

1.5K/6

+V3.3

0.1U/6

10U/12

1U/6

0.1U/6

0.1U/6

0.1U/6

0.1U/6

0.1U/6

0.1U/6

R313

1K/6

R280

4.7K/6

C338

C277

NPO

NPO

10P/6

10P/6

VTT_PWRGD#

C321

C316

Y1

14.318Mhz

R332

SMBDATA12,14,17,18,19,28 LAN_CLK 28

SMBCLK12,14,17,18,19,28

R317 475/6/1

CK_VDD

R219

10K/6

Q19

2N3904

132

VCCP

R220

220/6

10U/12

0.1U/6

1K/6

FB50

300/2012/3A

U19

ICS950201AF

26 27

VDDA VSSA

37

VDD48

1

VDDREF

8

VDDPCI

14

VDDPCI

19

VDD3V66

32

VDD3V66

46

VDDCPU

50

VDDCPU

25

PWRDN#

2

X1

3

X2

4

VSS

28

VTT_PWRGD#

53

CPU_STOP#

34

PCI_STOP#

40

SEL_2

55

SEL_1

54

SEL_0

29

SDATA

30

SCLK

42

IREF

43

MULT_0

41

VSSIREF

VSS3V66

VSS3V66

VSSCPU

CPUCLK_0

CPUCLK_0#

CPUCLK_1

CPUCLK_1#

CPUCLK_2

CPUCLK_2#

3V66_2/66BUF_0

3V66_3/66BUF_1

3V66_4/66BUF_2

3V66_5/66IN

3V66_1/48

DOT_48MHZ

USB_48MHZ

VSS48

VSSPCI

VSSPCI

3V66_0

PCIF_0

PCIF_1

PCIF_2

PCI_0

PCI_1

PCI_2

PCI_3

PCI_4

PCI_5

PCI_6

REF_0

36

9

15

20

31

47

52

R290 33/6/1

51

R286 33/6/1

49

R321 33/6/1

48

R320 33/6/1

45

R319 33/6/1

44

R318 33/6/1

33

21

R243 33/6

22

R242 33/6

23

24

35

R314 33/6

5

R276 33/6

6

R252 33/6

7

R251 33/6

10

R250 33/6

11

R249 33/6

12

R248 33/6

13

R247 33/6

16

R246 33/6

17

R245 33/6

18

R244 33/6/X

38

R315 33/6

39

R316 33/6

56

R323 33/6

R291

49.9/6/1

CLK_66SSC

R287

49.9/6/1

C292

C291

R337

49.9/6/1

10P/6/X

10P/6/X

R336

49.9/6/1

R335

49.9/6/1

PCK_ICH

FWHPCLK

LPC33A

PCLK_4

PCLK_5

PCLK_6

PCLK_7

LAN_CLK

LPC33B

TPM_CLK

DOTCLK

48MCLK

ICH_CK14

R334

49.9/6/1

CPUHCLK0 4

CPUHCLK0# 4

GMCH_CLK 7

GMCH_CLK# 7

ITPCLK 4

ITPCLK# 4

ICH_3V66 14

GH_3V66 8

PCK_ICH 13

FWHPCLK 16

LPC33A 17

PCLK_4 30

PCLK_5 30

PCLK_6 30

PCLK_7 30

LPC33B 18

TPM_CLK 18

DOTCLK 8

ICH_CK14 14

FB54

BC5

10U/12

C299

C298

C297

C296

C295

C793

+V3.3

300/2012/3A

10P/6/X

10P/6/X

10P/6/X

10P/6/X

10P/6/X

10P/6/X

Spread Spectrum Clock Generator for LVDS Display PLL

+V3.3

U22

ICS91718/X

1

CLKIN

2

VDD

3

GND

4

CLKOUT

SCLK

SDATA

48MHZ

8

PD#

7

6

5

DOTCLK

USBCLK

LPC48A

LPC48BLPC33B

ICH_CK14

48MCLK

CLK_66SSC48MCLK

C795

C794

0.1U/6/X

1U/6/X

DREFSSCLK8

C395

C375

C376

C413

C396

C776

10P/6/X

10P/6/X

10P/6/X

10P/6/X

10P/6/X

10P/6/X

R624

R307

R627

0/6

33/6/XR355 33/6

10K/6/X

Revised

D

E

Issued

F

R607 10K/6/X

R356 0/6/X

R357 0/6/X

R360 0/6/X

R625 10K/6/X

+V3.3

LCLKCTLA 8

SMBCLK 12,14,17,18,19,28

LCLKCTLB 7,8

SMBDATA 12,14,17,18,19,28

Title

CLOCK SYNTHESIZER

Size Document Number Rev

Date: Sheet of

G

6 36Sunday, October 12, 2003

H

C C

BC3

U21

ICS9112-16

1

REF

LPC48A17

R306 33/6 R359 0/6/X

R305 33/6

USBCLK14

PCK_ICH

D D

FWHPCLK

LPC33A PCLK_6

TPM_CLK

A

2

CLK2

3

CLK1

4 5

GND CLK3

10P/6/X

C340

10P/6/X

C301

10P/6/X

C300

10P/6/X

C294

10P/6/X

C293

B

CLKOUT

CLK4

VDD

8

7

6

C406

33/6

Change to 33 Ohm for

eliminating EMI issue

0.01U/6/X

C

BC4

0.1U/6

LPC48B 18

PCLK_4

PCLK_5

PCLK_7

LAN_CLK

CLK_66SSC

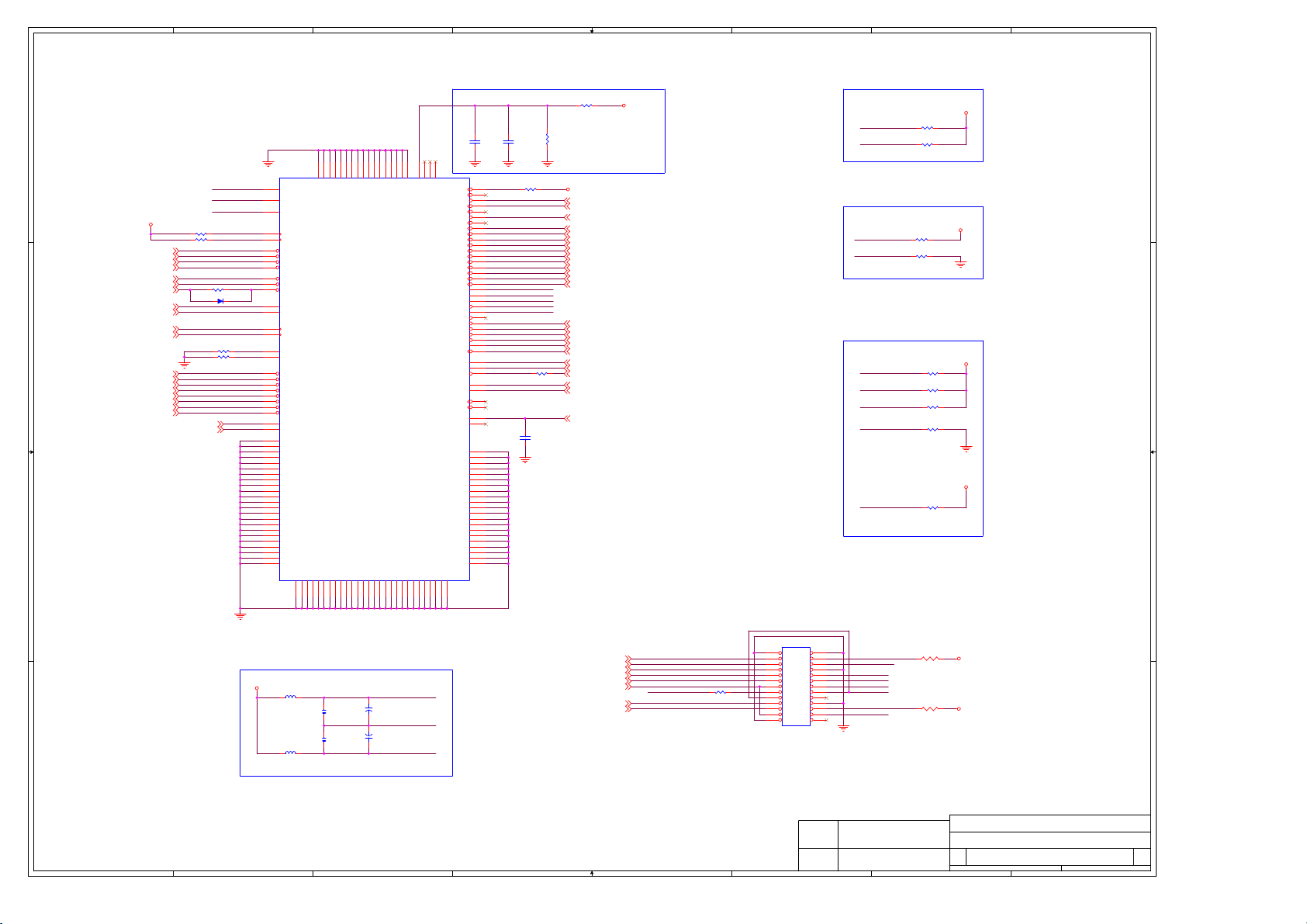

Page 7

A

INTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

852GME_A

H_D#[0..63]

C389

0.1U/6

MCH_HDVREF

C397

1U/8/10V

VCCP

R348

R353 100/6/1

C386

VCCP

R361

R358

C407

VCCP

R363

R366

C796

H_D#[0..63]3

C398

0.1U/6

49.9/6/1

H_A[3..31]

C402

1U/6

MCH_HCCVREF

MCH_HAVREF

MCH_HDVREF

H_DSTBP0#4

H_DSTBP1#4

H_DSTBP2#4

H_DSTBP3#4

H_CPURST#4

GMCH_CLK6

GMCH_CLK#6

C404

0.1U/6

C418

0.1U/6

H_DSTBN0#4

H_DSTBN1#4

H_DSTBN2#4

H_DSTBN3#4

C405

1U/6

C414

0.1U/6

H_A#[3..31]3

1U/6

Not in CRB

49.9/6/1

MCH_HCCVREF

100/6/1

1U/6

MCH_HAVREF

49.9/6/1

100/6/1 C477

1U/6

A

B

A A

B B

C C

GMCH Compensation & Reference Voltages

D D

U24A

H_D#0

K22

AE29

AD29

H27

K25

G28

H25

K23

G27

K26

H26

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

C27

E22

D18

K27

D26

E21

E18

K21

Y28

Y22

L24

J27

L27

L23

L25

J24

J23

J28

F15

J21

J17

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

CPURST#

BCLK

BCLK#

HDVREF0

HDVREF1

HDVREF2

HCCVREF

HAVREF

HADSTB0#

HADSTB1#

HOST

HYRCOMP

HYSWING

HXRCOMP

HXSWING

HUB

HLRCOMP

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HLOCK#

BREQ0#

BNR#

BPRI#

DBSY#

DINV0#

DINV1#

DINV2#

DINV3#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HLSTB

HLSTB#

PSWING

HLVREF

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19 H_A#22

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26 H_A#29

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

MONTARA-GML

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HIT#

RS0#

RS1#

RS2#

HI10

H_A#3

P23

H_A#4

T25

H_A#5

T28

H_A#6

R27

H_A#7

U23

H_A#8

U24

H_A#9

R24

H_A#10

U28

H_A#11

V28

H_A#12

U27

H_A#13

T27

H_A#14

V27

H_A#15

U25

H_A#16

V26

H_A#17

Y24

H_A#18

V25

H_A#19

V23

H_A#20

W25

H_A#21

Y25

AA27

H_A#23

W24

H_A#24

W23

H_A#25

W27

H_A#26

Y27

H_A#27

AA28

H_A#28

W28

AB27

H_A#30

Y26

H_A#31

AB28

T26

AA26

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

J25

E25

B25

G19

R28

P25

R23

R25

T23

N23

P26

M27

H28

K28

B20

B18

HI0

U7

HI0

HI1

U4

HI1

HI2

U3

HI2

HI3

V3

HI3

HI4

W2

HI4

HI5

W6

HI5

HI6

V6

HI6

HI7

W7

HI7

HI8

T3

HI8

HI9

V5

HI9

HI10

V4

W3

V2

HLZCOMP

T2

MCH_PSWING

U2

MCH_HLVREF

W1

C411

0.01U/6

System Menory Hub Interface

VCCP

VCCP

301/6/1

R272

R273 150/6/1

R301 301/6/1

150/6/1

R312

R274 27.4/6/1

R311 27.4/6/1

MCH_HXSWING

MCH_HYSWING

MCH_HXRCOMP

MCH_HYRCOMP

C

H_ADSTB0# 4

H_ADSTB1# 4

H_ADS# 4

H_TRDY# 4

H_DRDY# 4

H_DEFER# 4

H_HITM# 4

H_HIT# 4

H_LOCK# 4

H_BREQ0# 4

H_BNR# 4

H_BPRI# 4

H_DBSY# 4

H_DBI0# 4

H_DBI1# 4

H_DBI2# 4

H_DBI3# 4

H_REQ#0 3

H_REQ#1 3

H_REQ#2 3

H_REQ#3 3

H_REQ#4 3

H_RS0# 3

H_RS1# 3

H_RS2# 3

MCH_HYRCOMP

MCH_HYSWING

MCH_HXRCOMP

MCH_HXSWING

HI[0..10] 13

HUB_PSTRB 13

HUB_PSTRB# 13

C408

0.01U/6

+V2.5DDR

C421

0.1U/6

+V2.5DDR

+V2.5DDR

C334

C359

0.1U/6

0.1U/6

R375 60.4/6/1

R379 60.4/6/1

R394 150/6/1

R395 604/6/1

0.1U/6

C476

604/6/1

R397

150/6/1

R396

0.1U/6

D

+V3.3

+V3.3

MCH_SMVSWINGH

MCH_SMVSWINGL

+V1.5

R282 1K/6

R281 1K/6

R626 1K/6

R655 1K/6

R702 1K/6/X

Use to instead jumper 7-8

E

AG4

AG5

AG7

AG8

AG10

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ24

JGST1

JGST0

GST2 8

LCLKCTLB 6,8

GM 49.9/6/1

GME 86.6/6/1

GM 243/6/1

GME 324/6/1

Revised

Issued

F

U24B

AF2

SDQ0

AE3

SDQ1

AF4

SDQ2

AH2

SDQ3

AD3

SDQ4

AE2

SDQ5

SDQ6

AH3

SDQ7

AD6

SDQ8

SDQ9

SDQ10

AE8

SDQ11

AF5

SDQ12

AH4

SDQ13

AF7

SDQ14

AH6

SDQ15

AF8

SDQ16

SDQ17

AH9

SDQ18

SDQ19

AH7

SDQ20

AD9

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

SMVREF_0

C3

GST1

C4

GST0

MONTARA-GML

MCH_PSWING

MCH_HLVREF

AG2

SDQS0

AH5

SDQS1

AH8

SDQS2

AE12

SDQS3

AH17

SDQS4

AE21

SDQS5

AH24

SDQS6

AH27

SDQS7

AD15

SDQS8

AC18

SMA_A0

AD14

SMA_A1

AD13

SMA_A2

AD17

SMA_A3

AD11

SMA_A4

AC13

SMA_A5

AD8

SMA_A6

AD7

SMA_A7

AC6

SMA_A8

AC5

SMA_A9

AC19

SMA_A10

AD5

SMA_A11

AB5

SMA_A12

AD16

SMA_B1

AC12

SMA_B2

AF11

SMA_B4

AD10

SMA_B5

AC7

SCKE0

AB7

SCKE1

AC9

SCKE2

AC10

SCKE3

AD23

SCS0#

AD26

SCS1#

AC22

SCS2#

AC25

SCS3#

AD22

SBA0

AD20

SBA1

AC21

SRAS#

AC24

SCAS#

AD25

SWE#

DDR SYSTEM MEMORY

SCMD_CLK0#

SCMD_CLK1#

SCMD_CLK2#

SCMD_CLK3#

SCMD_CLK4#

SCMD_CLK5#

RCVEN_OUT#

SCMD_CLK0

SCMD_CLK1

SCMD_CLK2

SCMD_CLK3

SCMD_CLK4

SCMD_CLK5

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SDM8

RCVEN_IN#

SMRCOMP

SMVSWINGL

SMVSWINGH

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

AC15

AC16

AB1

AJ22

AJ19

+V1.2S

R354 27.4/6/1

Title

Size Document Number Rev

Date: Sheet of

G

R391 0/6/X

MCH_SMRCOMP

MCH_SMVSWINGL

MCH_SMVSWINGH

C465

0.1U/6

GM 27.4/6/1

GME 48.7/6/1

HLZCOMPMCH_SMRCOMP

852GME_A

DM_SDQS0 10

DM_SDQS1 10

DM_SDQS2 10

DM_SDQS3 10

DM_SDQS4 10

DM_SDQS5 10

DM_SDQS6 10

DM_SDQS7 10

DM_SDQS8 10

RM_MAA0 11,12

RM_MAA1 11,12

RM_MAA2 11,12

RM_MAA3 11,12

RM_MAA4 11,12

RM_MAA5 11,12

RM_MAA6 11,12

RM_MAA7 11,12

RM_MAA8 11,12

RM_MAA9 11,12

RM_MAA10 11,12

RM_MAA11 11,12

RM_MAA12 11,12

RM_MAB1 11,12

RM_MAB2 11,12

RM_MAB4 11,12

RM_MAB5 11,12

RM_CKE0 11,12

RM_CKE1 11,12

RM_CKE2 11,12

RM_CKE3 11,12

RM_SCS0 11,12

RM_SCS1 11,12

RM_SCS2 11,12

RM_SCS3 11,12

RM_BS0 11,12

RM_BS1 11,12

RM_RAS# 11,12

RM_CAS# 11,12

RM_WE# 11,12

MEMCLK0 12

MEMCLK0# 12

MEMCLK1 12

MEMCLK1# 12

MEMCLK2 12

MEMCLK2# 12

MEMCLK3 12

MEMCLK3# 12

MEMCLK4 12

MEMCLK4# 12

MEMCLK5 12

MEMCLK5# 12

DM_SDM0 10

DM_SDM1 10

DM_SDM2 10

DM_SDM3 10

DM_SDM4 10

DM_SDM5 10

DM_SDM6 10

DM_SDM7 10

DM_SDM8 10

C463

0.1U/6

7 36Sunday, October 12, 2003

H

DM_MD0

DM_MD010

DM_MD1

DM_MD110

DM_MD2

DM_MD210

DM_MD3

DM_MD310

DM_MD4

DM_MD410

DM_MD5

DM_MD510

DM_MD6

DM_MD610

DM_MD7

DM_MD710

DM_MD8

DM_MD810

DM_MD9

DM_MD910

DM_MD10

DM_MD1010

DM_MD11

DM_MD1110

DM_MD12

DM_MD1210

DM_MD13

DM_MD1310

DM_MD14

DM_MD1410

DM_MD15

DM_MD1510

DM_MD16

DM_MD1610

DM_MD17

DM_MD1710

DM_MD18

DM_MD1810

DM_MD19

DM_MD1910

DM_MD20

DM_MD2010

DM_MD21

DM_MD2110

DM_MD22

DM_MD2210

DM_MD23

DM_MD2310

DM_MD24

DM_MD2410

DM_MD25

DM_MD2510

DM_MD26

DM_MD2610

DM_MD27

DM_MD2710

DM_MD28

DM_MD2810

DM_MD29

DM_MD2910

DM_MD30

DM_MD3010

DM_MD31

DM_MD3110

DM_MD32

DM_MD3210

DM_MD33

DM_MD3310

DM_MD34

DM_MD3410

DM_MD35

DM_MD3510

DM_MD36

DM_MD3610

DM_MD37

DM_MD3710

DM_MD38

DM_MD3810

DM_MD39

DM_MD3910

DM_MD40

DM_MD4010

DM_MD41

DM_MD4110

DM_MD42

DM_MD4210

DM_MD43

DM_MD4310

DM_MD44

DM_MD4410

DM_MD45

DM_MD4510

DM_MD46

DM_MD4610

DM_MD47

DM_MD4710

DM_MD48

DM_MD4810

DM_MD49

DM_MD4910

DM_MD50

DM_MD5010

DM_MD51

DM_MD5110

DM_MD52

DM_MD5210

DM_MD53

DM_MD5310

DM_MD54

DM_MD5410

DM_MD55

DM_MD5510

DM_MD56

DM_MD5610

DM_MD57

DM_MD5710

DM_MD58

DM_MD5810

DM_MD59

DM_MD5910

DM_MD60

DM_MD6010

DM_MD61

DM_MD6110

DM_MD62

DM_MD6210

DM_MD63

DM_MD6310

M_CB0

M_CB010

M_CB1

M_CB110

M_CB2

M_CB210

M_CB3

M_CB310

M_CB4

M_CB410

M_CB5

M_CB510

M_CB6

M_CB610

M_CB7

M_CB710

DDRVREF12,33

J32

H4X2/2.0mm

2

4

6

8

C466

0.1U/6

1

3

5

7

+V1.2S

R350 49.9/6/1

R347 100/6/1

0.1U/6

C390

+V1.2S

R382 243/6/1

R389 100/6/1

0.1U/6

C455

Page 8

A

INTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGNINTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

852GME_B

U24C

R3

DVOBD0

R5

DVOBD1

DVOBCINTR#

DVOCFLDSTL

MDDCCLK

MDDCDATA

SUSCLK#

AGPBUSY#

GST2

R6

R4

P6

P5

N5

P2

N2

N3

M1

M5

P3

P4

T6

T5

L2

M2

G2

M3

K5

K1

K3

K2

J6

J5

H2

H1

H3

H4

H6

G3

J3

J2

K6

L5

L3

H5

K7

N6

N7

M6

P7

T7

E5

F5

E3

E2

G5

F4

G6

F6

L7

D5

F1

F7

D1

Y3

F2

F3

B2

B3

C2

D2

D3

L4

AA5

D7

F12

D12

B12

DVOBD2

DVOBD3

DVOBD4

DVOBD5

DVOBD6

DVOBD7

DVOBD8

DVOBD9

DVOBD10

DVOBD11

DVOBCLK

DVOBCLK#

DVOBHSYNC

DVOBVSYNC

DVOBBLANK#

DVOBFLDSTL

DVOBCINTR#

DVOBCCLKINT

DVOCD0

DVOCD1

DVOCD2

DVOCD3

DVOCD4

DVOCD5

DVOCD6

DVOCD7

DVOCD8

DVOCD9

DVOCD10

DVOCD11

DVOCCLK

DVOCCLK#

DVOCHSYNC

DVOCVSYNC

DVOCBLANK#

DVOCFLDSTL

MI2CCLK

MI2CDATA

MDVICLK

MDVIDATA

MDDCCLK

MDDCDATA

ADDIN0

ADDIN1

ADDIN2

ADDIN3

ADDIN4

ADDIN5

ADDIN6

ADDIN7

DVODETECT

DPMS

GVREF

AGPBUSY#

DVORCOMP

GCLKIN

GSBSTB

GSBSTB#

GGNT#

GREQ#

GST[2]

GWBF#

GRBF#

GCBE#[2]

RVSD0

RVSD10

RSVD12

RSVD13

RSVD14

MONTARA-GML

+V3.3

GT

GT

R628

DVO

DACLVDSCLKSMISCNC

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

A A

DVOBFLDSTL

DVOBCINTR#27

DVOCD027

DVOCD127

DVOCD227

DVOCD327

DVOCD427

DVOCD527

DVOCD627

DVOCD727

DVOCD827

DVOCD927

DVOCD1027

DVOCD1127

DVOCCLK27

DVOCCLK#27

DVOCHSYNC27

2.2K/6

2.2K/6

8.2K/6/X

DVOCVSYNC27

DVOCBLANK#27

MI2C_CLK27

MI2C_DATA27

MDDC_CLK27

MDDC_DATA27

B B

+V1.5

R342

R346

R289

+V1.5

1K/6

R351

R344

R269

C373

0.1U/6

100K/6

100K/6

100K/6

R647

R330

R295

40.2/6/1

330/6/X

GH_3V666

GST27

DVOBCCLKINT

DVOBFLDSTL

DVOCFLDSTL

TP9

TP10

TP1

TP2

TP5

TP6

TP12

TP13

TP7

TP11

TP8

TP3

R325

1K/6/1

R310

1K/6/1

C C

BLUE

BLUE#

GREEN

GREEN#

RED#

HSYNC

VSYNC

DDCACLK

DDCADATA

REFSET

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM3

IYBP0

IYBP1

IYBP2

IYBP3

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

DPWR#

DPSLP#

RSTIN#

PWROK

EXTTS0

VSS182

NC10

NC11

NC12

8.2K/6

RED

LIBG

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

AGPBUSY#

C9

D9

C8

D8

A7

A8

H10

J9

B6

G9

E8

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

B4

C5

G8

F8

A5

A10

B7

B17

H9

C6

AA22

Y23

AD28

J11

D6

AJ1

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

BLUE 26,27

GREEN 26,27

RED 26,27

HSYNC 26

VSYNC 26

DDCA_CLK 26

DDCA_DATA 26

R285 127/6/1

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1DVOBCCLKINT

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM3

IYBP0

IYBP1

IYBP2

IYBP3

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

1.5K/6/1

R271

R270

DOTCLK 6

DREFSSCLK 6

LCLKCTLA 6

LCLKCTLB 6,7

R362

H_DPSLP# 13

CHIPRST- 16,17,18,27

PWROK 17,35

10K/6

SUSCLK14

1K/6/X

+V3.3

VCCP

+V1.5

G S

LVDS & Backlight Conn.

+V12 +V12 +V5+V5 +V3.3+V3.3

LVDS1

1 2

384

6

7

9510

11 12

IYAP0 IYAM0

13 14

VSS_SHIELD

15 16

IYAM1

17 18

IYAP2

19 20

VSS_SHIELD

21 22

IYAM3

23 24

25 26

VSS_SHIELD

27 28

IYBM0

29 30

IYBP1

31 32

VSS_SHIELD

33 34

IYBM2

35 36

IYBP3

37 38

VSS_SHIELD

39 40

ICLKBM

R648 2.2K/6

LGPIO313

41 42

DDCPCLK DDCPDATA

43 44

45 46

LGPIO1

47 48

LGPIO3

49 50

BOX_25X2

+V12 +V3.3

J17

PANELBKLTEN

PANELBKLTCTL

R409

100K/6

R660

1K/6

SUSCLK#

3

D

Q62

2N7002

2

1

7

6

5

4

3

2

1

Near LVDS CONN.

+V3.3

1

+

EC36

220U/6.3V

+V12

1

+

EC24

470U/16V

+V5

1

+

EC34

220U/10V

inverter

7

6

5

4

3

2

1

IYAP1

VSS_SHIELD

IYAM2

IYAP3

VSS_SHIELD

ICLKAMICLKAP

IYBP0

VSS_SHIELD

IYBM1

IYBP2

VSS_SHIELD

IYBM3

ICLKBP

VSS_SHIELD

PANELVDDEN

LGPIO2

LGPIO4

C245

0.1U/6

C265

0.1U/6

C271

0.1U/6

R649 2.2K/6

LGPIO2 13LGPIO113

LGPIO4 13

VSS_SHIELD

+V3.3+V3.3

D D

Revised

A

B

C

D

E

Issued

F

Title

852GME_B

Size Document Number Rev

Date: Sheet of

G

8 36Sunday, October 12, 2003

H

Page 9

A

INTEL(R) 852GME REFERENCE DESIGN

852GME_C

B

C

D

E

F

G

H

A A

B B

C C

+V1.2S

12

+

EC52

220U/6.3V

12

+

EC58

220U/6.3V

+V2.5DDR

+V1.2S

+V1.2S

12

+

C456

10U/12

C351

0.1U/6

R230

1/8

R231

1/8L80.1UH/8

+V1.5

+V1.5

EC62

47U/6.3V

C141

0.1U/6

C358

0.1U/6

L7

0.1UH/8

12

+

EC43

220U/6.3V

12

+

EC82

220U/6.3V/X

Should be connected

to R641 Pin2

+V1.5

+V1.5

12

+

EC61

22U/6.3V

+V1.2S

12

+

12

+

R641

0/8

12

+

C140

0.1U/6

C450

10U/12

EC46

220U/6.3V

EC44

220U/6.3V

C322

10U/12

C331

0.1U/6

EC47

47U/6.3V

C240

0.1U/6

+V3.3

C755

0.01U/6

12

+

C100

0.1U/6

C409

0.1U/6

C328

0.1U/6

C333

0.1U/6

C403

0.1U/6

C388

0.1U/6

EC49

22U/6.3V

C233

0.1U/6

C327

10U/12

C232

0.1U/6

C415

0.1U/6

C329

0.1U/6

C361

0.01U/6

C332

0.1U/6

C234

0.1U/6

C326

0.1U/6

AA15

AA17

AA19

W21

J15

P13

T13

N14

R14

U14

P15

T15

N16

R16

U16

P17

T17

H14

V1

Y1

W5

U6

U8

W8

V7

V9

D29

Y2

A6

B16

E1

J1

N1

E4

J4

M4

E6

H7

J8

L8

M8

N8

R8

K9

M9

P9

A9

B9

B8

A11

B11

G13

B14

J13

B15

F9

B10

D10

A12

A3

A4

U24D

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCCHL0

VCCHL1

VCCHL2

VCCHL3

VCCHL4

VCCHL5

VCCHL6

VCCHL7

VCCAHPLL

VCCAGPLL

VCCADPLLA

VCCADPLLB

VCCDVO_0

VCCDVO_1

VCCDVO_2

VCCDVO_3

VCCDVO_4

VCCDVO_5

VCCDVO_6

VCCDVO_7

VCCDVO_8

VCCDVO_9

VCCDVO_10

VCCDVO_11

VCCDVO_12

VCCDVO_13

VCCDVO_14

VCCDVO_15

VCCADAC0

VCCADAC1

VSSADAC

VCCALVDS

VSSALVDS

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCDLVDS3

VCCTXLVDS0

VCCTXLVDS1

VCCTXLVDS2

VCCTXLVDS3

VCCGPIO_0

VCCGPIO_1

MONTARA-GML

POWER

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCASM1

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

A22

A24

H29

M29

V29

AC1

AG1

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

AJ6

AJ8

AD1

AF1

C335 0.1U/6

C336 0.1U/6

C383 0.1U/6

C401 0.1U/6

C410 0.1U/6

12

+

EC45

220U/6.3V

C422

0.1U/6

12

+

EC64

220U/6.3V

C427

0.1U/6

C445

0.1U/6

C469

10U/12

R392

1/8

12

+

EC54

220U/6.3V

C312

10U/12

C352

0.1U/6

12

+

EC65

220U/6.3V

C464

0.1U/6

C444

0.1U/6

C459

0.1U/6

C431

0.1U/6

C337

0.01U/6/X

Not in CRB Not in CRB

C756

0.1U/6

C467

0.1U/6

C460

0.1U/6

+V2.5DDR

L10

0.68UH/8

+V1.2S

L11

1UH/8

VCCP

C374

0.01U/6/X

C757

0.1U/6

C428

0.1U/6

C461

0.1U/6

+V2.5DDR

C462

0.1U/6

C495

10U/12

Not in CRB

AG3

AC4

AG6

AC8

AG9

AA10

AE10

AB11

AC11

AJ11

AA12

AG12

AB13

AE13

AA14

AC14

AB15

AG15

AA16

AE16

C1

G1

L1

U1

AA1

AE1

R2

AJ3

D4

G4

K4

N4

T4

W4

AA4

AE4

B5

U5

Y5

Y6

C7

E7

G7

J7

M7

R7

AA7

AE7

AJ7

H8

K8

P8

T8

V8

Y8

E9

L9

N9

R9

U9

W9

AB9

C10

J10

D11

F11

H11

J12

A13

D13

F13

H13

N13

R13

U13

J14

P14

T14

D15

H15

N15

R15

U15

F16

J16

P16

A17

D17

H17

U24E

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS85

VSS86

VSS87

VSS88

VSS89

MONTARA-GML

VSS

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS176VSS84

VSS177

VSS178

VSS179

VSS180

VSS181

N17

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

W29

AA29

AJ10

AJ12

AJ18

AJ20

C22T16

D28

E28

L6

T9

AJ26

Reserve on GMCH bottom side

+V1.2S +V2.5DDR

C734 0.1U/6/X

D D

C735 0.1U/6/X

C736 0.1U/6/X

C737 0.1U/6/X

C731 0.1U/6/X

C732 0.1U/6/X

C733 0.1U/6/X

A

Not in CRB

Revised

B

C

D

E

Issued

F

Title

852GME_C

Size Document Number Rev

Date: Sheet of

G

9 36Sunday, October 12, 2003

H

Page 10

A

INTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

A A

RM_MD1411,12

RM_MD1511,12

RM_MD1011,12

RM_MD1111,12

B B

C C

RM_MD1211,12

RM_MD1311,12

RM_MD1811,12

RM_MD2211,12

RM_MD1911,12

RM_MD2311,12

RM_MD1611,12

RM_MD2011,12

RM_MD1711,12

RM_MD2111,12

RM_MD2411,12

RM_MD2811,12

RM_MD2911,12

RM_MD2511,12

RM_MD3011,12

RM_MD2611,12

RM_MD2711,12

RM_MD3111,12

RN17

10/8P4R

1

3

5

7

RN16

10/8P4R

1

3

5

7

RN19

10/8P4R

1

3

5

7

RN18

10/8P4R

1

3

5

7

RN21

10/8P4R

1

3

5

7

RN20

10/8P4R

1

3

5

7

RN22

10/8P4R

1

3

5

7

RN23

10/8P4R

1

3

5

7

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

DM_MD2 7

DM_MD6 7

DM_MD7 7

DM_MD3 7

DM_MD4 7

DM_MD0 7

DM_MD5 7

DM_MD1 7

DM_MD14 7

DM_MD15 7

DM_MD10 7

DM_MD11 7

DM_MD8 7

DM_MD9 7

DM_MD12 7

DM_MD13 7

DM_MD18 7

DM_MD22 7

DM_MD19 7

DM_MD23 7

DM_MD16 7

DM_MD20 7

DM_MD17 7

DM_MD21 7

DM_MD24 7

DM_MD28 7

DM_MD29 7

DM_MD25 7

DM_MD30 7

DM_MD26 7

DM_MD27 7

DM_MD31 7

RM_MD211,12

RM_MD611,12

RM_MD711,12

RM_MD311,12

RM_MD411,12

RM_MD011,12

RM_MD511,12

RM_MD111,12

RM_MD811,12

RM_MD911,12

RN25

10/8P4R

1

3

5

7

RN26

10/8P4R

1

3

5

7

RN27

10/8P4R

1

3

5

7

RN28

10/8P4R

1

3

5

7

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

DM_MD32 7

DM_MD36 7

DM_MD37 7

DM_MD33 7

DM_MD34 7

DM_MD38 7

DM_MD39 7

DM_MD35 7

DM_MD44 7

DM_MD40 7

DM_MD45 7

DM_MD41 7

DM_MD42 7

DM_MD43 7

DM_MD46 7

DM_MD47 7

RM_MD3211,12

RM_MD3611,12

RM_MD3711,12

RM_MD3311,12

RM_MD3411,12

RM_MD3811,12

RM_MD3911,12

RM_MD3511,12

RM_MD4411,12

RM_MD4011,12

RM_MD4511,12

RM_MD4111,12

RM_MD4211,12

RM_MD4311,12

RM_MD4611,12

RM_MD4711,12

RM_SDQS011,12

RM_SDQS111,12

RM_SDQS211,12

RM_SDQS311,12

RM_SDQS411,12

RM_SDQS511,12

RM_SDQS611,12

RM_SDQS711,12

RM_SDQS811,12

RM_SDM011,12

RM_SDM111,12

RN30

10/8P4R

1

3

5

7

RN29

10/8P4R

1

3

5

7

RN32

10/8P4R

1

3

5

7

RN31

10/8P4R

1

3

5

7

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

DM_MD54 7

DM_MD50 7

DM_MD55 7

DM_MD51 7

DM_MD48 7

DM_MD49 7

DM_MD52 7

DM_MD53 7

DM_MD62 7

DM_MD58 7

DM_MD63 7

DM_MD59 7

DM_MD60 7

DM_MD56 7

DM_MD61 7

DM_MD57 7

RM_MD5411,12

RM_MD5011,12

RM_MD5511,12

RM_MD5111,12

RM_MD4811,12

RM_MD4911,12

RM_MD5211,12

RM_MD5311,12

RM_MD6211,12

RM_MD5811,12

RM_MD6311,12

RM_MD5911,12

RM_MD6011,12

RM_MD5611,12

RM_MD6111,12

RM_MD5711,12

RM_SDM211,12

RM_SDM311,12

RM_SDM411,12

RM_SDM511,12

RM_SDM611,12

RM_SDM711,12

RM_SDM811,12

R421

R422

R424

R432

R439

R445

R448

R450

R435

R420

R423

R425

R433

R440

R446

R447

R449

R436

10/6

DM_SDQS0 7

10/6

DM_SDQS1 7

10/6

DM_SDQS2 7

10/6

DM_SDQS3 7

10/6

DM_SDQS4 7

10/6

DM_SDQS5 7

10/6

DM_SDQS6 7

10/6

DM_SDQS7 7

10/6

DM_SDQS8 7

10/6

DM_SDM0 7

10/6

DM_SDM1 7

10/6

DM_SDM2 7

10/6

DM_SDM3 7

10/6

DM_SDM4 7

10/6

DM_SDM5 7

10/6

DM_SDM6 7

10/6

DM_SDM7 7

10/6

DM_SDM8 7

RN24

10/8P4R

1

M_CB17

M_CB07

M_CB57

M_CB47

D D

A

2

M_CB_R1 11,12

3

4

M_CB_R0 11,12

5

6

M_CB_R5 11,12

7

8

M_CB_R4 11,12

B

C

M_CB77

M_CB37

M_CB67

M_CB27

D

RN33

10/8P4R

1

3

5

7

2

4

6

8

M_CB_R7 11,12

M_CB_R3 11,12

M_CB_R6 11,12

M_CB_R2 11,12

Revised

E

Issued

F

Title

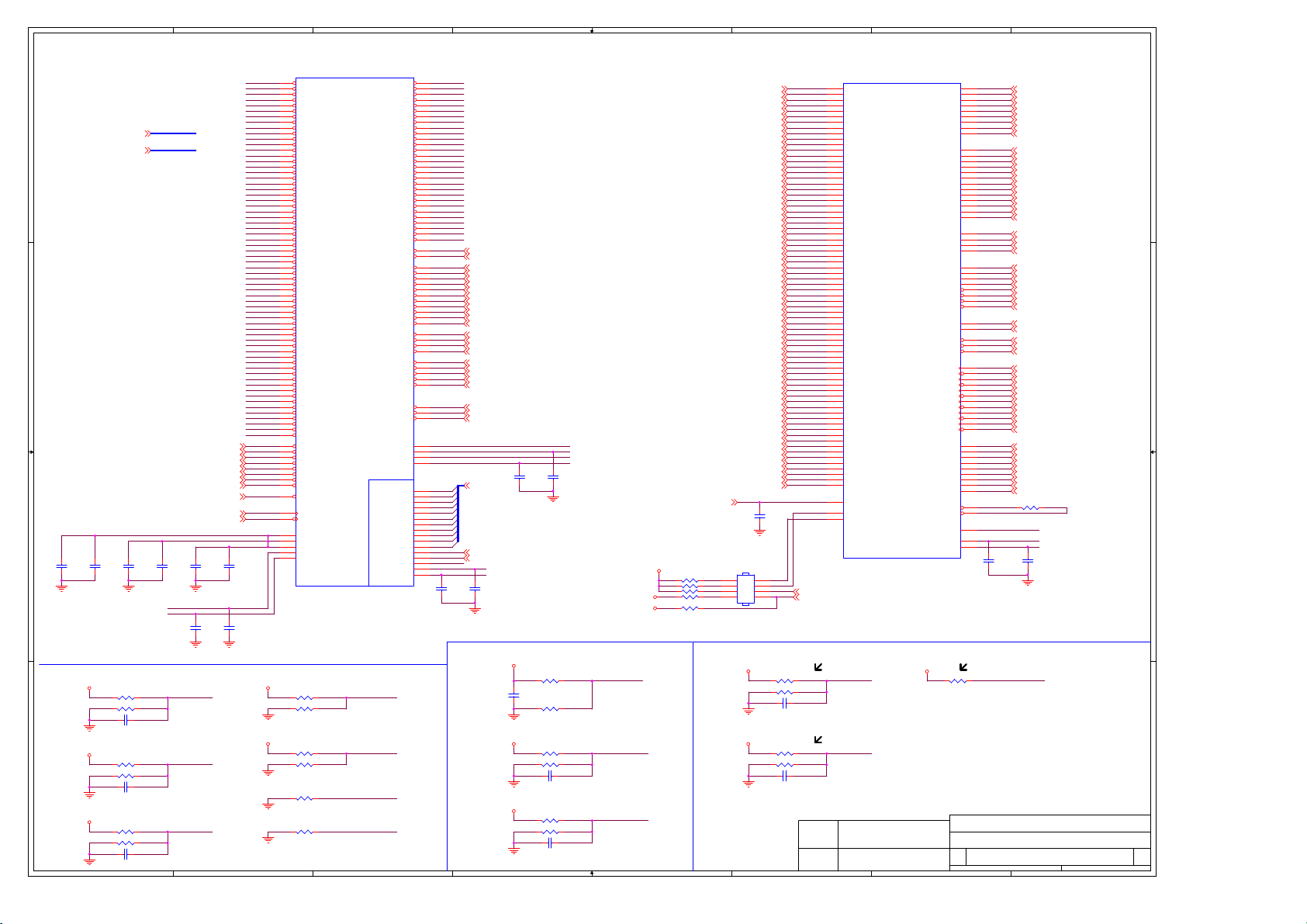

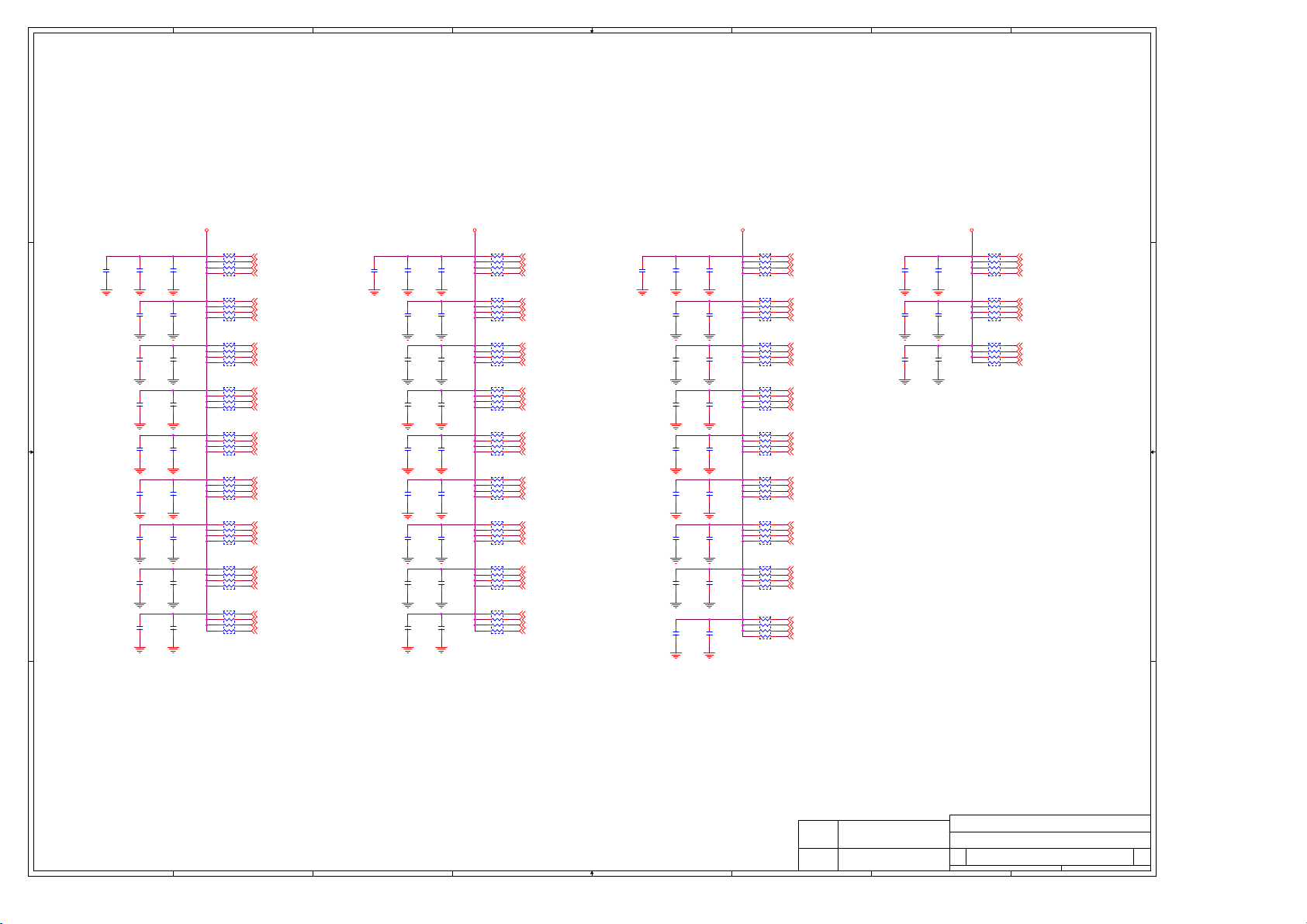

DDR-SERIES-TERMINATION_1

Size Document Number Rev

Date: Sheet of

G

10 36Sunday, October 12, 2003

H

Page 11

A

INTEL(R) 852GME REFERENCE DESIGN

A A

B

C

D

E

F

G

H

+V1.25DDR

RN35

56/8P4R

1

2

RM_SDQS0 10,12

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

RN34

56/8P4R

RN39

56/8P4R

RN36

56/8P4R

RN43

56/8P4R

RN41

56/8P4R

RN46

56/8P4R

RN47

56/8P4R

RN49

56/8P4R

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

RM_SDM0 10,12

RM_MD2 10,12

RM_MD6 10,12

RM_MD4 10,12

RM_MD0 10,12

RM_MD5 10,12

RM_MD1 10,12

RM_CKE0 7,12

RM_MD10 10,12

RM_MD20 10,12

RM_MD11 10,12

RM_MD7 10,12

RM_MD3 10,12

RM_MD12 10,12

RM_MD13 10,12

RM_MAA8 7,12

RM_MD23 10,12

RM_MD19 10,12

RM_MAA6 7,12

RM_MAA11 7,12

RM_MD17 10,12

RM_SDQS2 10,12

RM_SDM2 10,12

RM_SDQS3 10,12

RM_SDM3 10,12

RM_MAA3 7,12

RM_MD30 10,12

RM_MD26 10,12

RM_MD27 10,12

RM_MD31 10,12

M_CB_R4 10,12

M_CB_R0 10,12

M_CB_R5 10,12

M_CB_R1 10,12

RM_SDQS8 10,12

C544

10U/12

B B

C C

C550

C549

0.1U/6

0.1U/6

12

12

C547

C548

0.1U/6

0.1U/6

12

12

C557

C558

0.1U/6

0.1U/6

12

12

C551

C552

0.1U/6

0.1U/6

12

12

C565

C566

0.1U/6

0.1U/6

12

12

C561

C562

0.1U/6

0.1U/6

12

12

C571

C572

0.1U/6

0.1U/6

12

12

C573

C574

0.1U/6

0.1U/6

12

12

C577

C578

0.1U/6

0.1U/6

12

12

C484

10U/12

12

12

12

12

12

12

12

12

12

C585

0.1U/6

C583

0.1U/6

C589

0.1U/6

C595

0.1U/6

C601

0.1U/6

C599

0.1U/6

C605

0.1U/6

C603

0.1U/6

C579

0.1U/6

12

C586

0.1U/6

12

C584

0.1U/6

12

C590

0.1U/6

12

C596

0.1U/6

12

C602

0.1U/6

12

C600

0.1U/6

12

C606

0.1U/6

12

C604

0.1U/6

12

C580

0.1U/6

+V1.25DDR

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

+V1.25DDR

RN53

56/8P4R

2

RM_MD33 10,12

4

RM_MD38 10,12

6

RM_MD34 10,12

8

RM_SDQS4 10,12

RN52

56/8P4R

2

RM_MD36 10,12

4

RM_MD37 10,12

6

RM_MD32 10,12

8

RM_SDM4 10,12

RN55

56/8P4R

2

RM_MD40 10,12

4

RM_MD35 10,12 RM_MD48 10,12

6

RM_MD45 10,12

8

RM_WE# 7,12

RN58

56/8P4R

2

RM_MD42 10,12

4

RM_MD43 10,12

6

RM_MD46 10,12

8

RM_MD47 10,12

RN61

56/8P4R

2

RM_MD50 10,12

4

RM_MD61 10,12

6

RM_MD60 10,12

8

RM_MD51 10,12

RN60

56/8P4R

2

RM_SDM6 10,12

4

RM_MD54 10,12

6

RM_MD55 10,12

8

RM_SDQS6 10,12

RN63

56/8P4R

2

RM_MD57 10,12

4

RM_MD58 10,12

6

RM_SDQS7 10,12

8

RM_MD59 10,12

RN62

56/8P4R

2

RM_SDM7 10,12

4

RM_MD56 10,12

6

RM_MD63 10,12

8

RM_MD62 10,12

RN50

56/8P4R

2

RM_MAA0 7,12

4

RM_SDM8 10,12

6

M_CB_R2 10,12

8

RM_MAA10 7,12

C543

10U/12

12

12

C563

0.1U/6

12

12

C591

0.1U/6

12

12

C587

0.1U/6

12

12

C593

0.1U/6

12

12

C553

0.1U/6

12

12

C569

0.1U/6

12

12

C559

0.1U/6

12

12

C567

0.1U/6

12

12

C575

0.1U/6

C564

0.1U/6

C592

0.1U/6

C588

0.1U/6

C594

0.1U/6

C554

0.1U/6

C570

0.1U/6

C560

0.1U/6

C568

0.1U/6

C576

0.1U/6

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

RN42

56/8P4R

RN56

56/8P4R

RN54

56/8P4R

RN57

56/8P4R

RN37

56/8P4R

RN45

56/8P4R

RN40

56/8P4R

RN44

56/8P4R

RN48

56/8P4R

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

RM_MAA9 7,12

RM_MD22 10,12

RM_MAA7 7,12

RM_MD18 10,12

RM_SCS2 7,12

RM_SCS0 7,12

RM_MD41 10,12

RM_CAS# 7,12

RM_MD39 10,12

RM_MD44 10,12

RM_BS0 7,12

RM_RAS# 7,12

RM_SCS3 7,12

RM_SCS1 7,12

RM_SDQS5 10,12

RM_SDM5 10,12

RM_MD9 10,12

RM_MD8 10,12

RM_SDM1 10,12

RM_MD14 10,12

RM_MD24 10,12

RM_MD28 10,12

RM_MD25 10,12

RM_MD29 10,12

RM_CKE2 7,12

RM_MAA12 7,12

RM_MD16 10,12

RM_MD21 10,12

RM_MAA5 7,12

RM_MAB4 7,12

RM_MAB5 7,12

RM_MAA4 7,12

RM_MAB2 7,12

RM_MAA2 7,12

RM_MAB1 7,12

RM_MAA1 7,12

+V1.25DDR

1

12

C581

0.1U/6

12

C555

0.1U/6

12

C597

0.1U/6

3

12

5

C582

7

0.1U/6

1

3

12

5

C556

7

0.1U/6

1

3

12

5

C598

7

0.1U/6

RN51

56/8P4R

RN38

56/8P4R

RN59

56/8P4R

2

4

6

8

2

4

6

8

2

4

6

8

M_CB_R6 10,12

M_CB_R3 10,12

RM_BS1 7,12

M_CB_R7 10,12

RM_SDQS1 10,12

RM_CKE1 7,12

RM_MD15 10,12

RM_CKE3 7,12

RM_MD52 10,12

RM_MD49 10,12

RM_MD53 10,12

D D

Revised

A

B

C

D

E

Issued

F

Title

DDR-SERIES-TERMINATION_2

Size Document Number Rev

Date: Sheet of

G

11 36Sunday, October 12, 2003

H

Page 12

A

INTEL(R) 852GME REFERENCE DESIGN

B

C

D

E

F

G

H

+V2.5DDR

A A

RM_MAA07,11

RM_MAA17,11

RM_MAA27,11

RM_MAA37,11

RM_MAA47,11

RM_MAA57,11

RM_MAA67,11

RM_MAA77,11

RM_MAA87,11

RM_MAA97,11

RM_MAA107,11

RM_MAA117,11

RM_MAA127,11

RM_BS07,11

RM_BS17,11

RM_SCS07,11

RM_SCS17,11

RM_SDM010,11

RM_SDM110,11

RM_SDM210,11

RM_SDM310,11

RM_SDM410,11

RM_SDM510,11

RM_SDM610,11

B B

RM_SDM710,11

RM_SDM810,11

RM_WE#7,11

RM_CAS#7,11

RM_RAS#7,11

RM_CKE07,11

RM_CKE17,11

MEMCLK27

MEMCLK2#7

MEMCLK07

MEMCLK0#7

MEMCLK17

MEMCLK1#7

RM_SDQS010,11

RM_SDQS110,11

RM_SDQS210,11

RM_SDQS310,11

RM_SDQS410,11

RM_SDQS510,11

RM_SDQS610,11

RM_SDQS710,11

RM_SDQS810,11

SMBDATA6,14,17,18,19,28

SMBCLK6,14,17,18,19,28

RM_MAA0

RM_MAA1

RM_MAA2

RM_MAA3

RM_MAA4

RM_MAA5

RM_MAA6

RM_MAA7

RM_MAA8

RM_MAA9

RM_MAA10

RM_MAA11

RM_MAA12

RM_BS0

RM_BS1

RM_SCS0

RM_SCS1

RM_SDM0

RM_SDM2

RM_SDM3

RM_SDM4

RM_SDM5

RM_SDM6

RM_SDM7

RM_SDM8 RM_SDM8

RM_WE#

RM_CAS#

RM_RAS#

RM_CKE0

RM_CKE1

MEMCLK2

MEMCLK2#

MEMCLK0

MEMCLK0#

MEMCLK1 MEMCLK4

MEMCLK1#

RM_SDQS0

RM_SDQS1

RM_SDQS2

RM_SDQS3

RM_SDQS4

RM_SDQS5

RM_SDQS6

RM_SDQS7

RM_SDQS8 RM_SDQS8

SMBDATA

SMBCLK

+V2.5DDR

DDRVREF7,33

C C

C521

0.1U/6

R475

R477

+V3.3

R654 0/6/X

10K/6

0/6

DDRVREF

VDDID1

VDDSPD

130

125

122

141

118

115

103

113

157

158

163

107

119

129

149

159

169

177

140

154

111

137

138

181

182

183

184

101

102

173

167

48

43

41

37

32

29

27

59

52

71

97

63

65

21

16

17

76

75

5

14

25

36

56

67

78

86

47

91

92

1

82

9

10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

CS0

CS1

NC/CS2

NC/CS3

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0/DNU

CK0/DNU

CK1

CK1

CK2/DNU

CK2/DNU

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VDDID

VDDSPD

NC

NC

NC

NC

NC

NC/FETEN

15223054627796

104

112

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

3111826344250586674818993

128

VDDQ

GND

136

VDDQ

VDDQ

GND

GND

143

156

VDDQ

VDDQ

DIMM1

GND

GND

164

VDDQ

GND

172

180738467085108

VDD

VDDQ

VDDQ

GND

GND

GND

GND

100

116

DIMM1

120

148

168

R474

10K/6

R419

49.9/6/1/X

RM_MAA0

RM_MAB1

RM_MAB2

RM_MAA3

RM_MAB4

RM_MAA6

RM_MAA7

RM_MAA8

RM_MAA9

RM_MAA10

RM_MAA11

RM_MAA12

RM_BS0

RM_BS1

RM_SCS2

RM_SCS3

RM_WE#

RM_CAS#

RM_RAS#

RM_CKE2

RM_CKE3

MEMCLK5

MEMCLK5#

MEMCLK3

MEMCLK3#

MEMCLK4#

VDDID2

VDDSPD

RM_SDM0

RM_SDM1

RM_SDM2

RM_SDM3

RM_SDM4

RM_SDM5

RM_SDM6

RM_SDM7

RM_SDQS0

RM_SDQS1

RM_SDQS2

RM_SDQS3

RM_SDQS4

RM_SDQS5

RM_SDQS6

RM_SDQS7

SMBDATA

SMBCLK

DDRVREF

R418

49.9/6/1/X

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

124

132

139

145

152

160

RM_MD0

VDD

VDD

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

WP

GND

SL_DDR184P

176

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40