Page 1

inter

iAPX 432

Interface Processor

Architecture Reference

Manual

171863-001

Page 2

iAPX

432

INTERFACE

INTEL

P~OR

Manual Orner

Release

Number

1.1

171863-001

Oamponents

Intel

Cb~right

Corporation,

3065

(C)

Bowers

1981,

Intel

Avenue, Santa

Corporation

Clara,

California

95051

Page 3

Additional

obtained

oopies

from:

of

this

manual

or

other

Intel

literature

may

be

Literature

Intel

3065

Santa

The

information

Intel

material,

Corporation

BCMers

Clara,

Corporation

including,

merchantability

Corporation

in

this

oor

to

keep

Intel

Corporation

circuitry

other

Intel

circuit

software

property

subject

defined

assumes

document.

current

other

of

Intel

to

restrictions

in

ASPR

Department

Avenue

CA

95051

in

this

makes no

but

and

no

Intel

the

assumes no

than

patent

licenses

products

Corporation.

7-104.9

document

is

warranty

not

limited

fitness

for

responsibility

Corporation

information

responsibility

circuitry

are

are

oopyr

stated

(a)

(9).

in

subject

of

any

to,

a

particular

for

makes

oontained

embodied

~lied.

ighted

Use,

duplication,

Intel's

to

change

kind

the

any

errors

00

in

in

an

by

and

software

with

inplied

p..1rpose.

camti

this

for

the

Intel

shall

or

without

regard

warranties

that

may

trnent

to

document.

use

product.

remain

disclosure

license,

notice.

to

this

of

Intel

appear

update

of

any

No

the

or

as

is

No

part

by

any means

The

following

am

may

BXP

CREDIT

iR

ICE

iCS

~

INSITE

Intel

intelR

and

the

numerical

of

this

document

without

are

be

used

only

R

combination

suffix.

may

the

prior

trademarks

to

identify

Intelevision

Intellec

iRMX

iSBC

iSBX

Library

M:SR

Megachassis

Micromainframe

of

lCE,- iCS,

be

copied

written

of

Intel

Intel

R

Manager

i~,

or

reproduced

consent

of

Corporation

products:

iSBC,

iSBX,

in

any form

Intel

and

Corporation.

its

affiliates

Micrornap

Multibus

MultiIOOdule

Plug-A-Bubble

PROMPT

Promware

~/80

System 2000

UPI

uSoope

~,

or

R

RMX

or

R

and a

ii

Page 4

PREFACE

Understanding

432,

requires

information.

432

Interface

general

these

432

prerequisites.

o The

the

introduction

o The

171821,

features

o The

Manual,

information

Processor

rrost

the

This

Rather

in

references

are

IP

(IP),

manual

similar

than

the

companion documents,

common

are

presented

for

among

appropriate.

any complex comp.lting

the

Before

Processor,

concepts.

INTEL

broad

Introduction

iAPX

important

Interface

describes

in

duplicate

descr

assimilation

reading

this

the

Intel

offers

432 System Summary, Order

picture

to

restricts

which

432

Order

on

(GOP).

of

the

the

432

to

the

discussion

distinguish

General

Number

one

type

Its

terminology

Processor

many

iptions

another

respects

all

of

432

the

of

processors.

and

oontrasted

system,

of

manual on

reader

432.

system.

iAPX

the

Data

Processor

171860-001,

of

glossary

which

manual.

processor,

to

a

general

this

features

Unique

a

great

should

three

It

should

432

Architecture,

to

432.

432

processor,

is a concise

is

GOP

and

432

manual

of

features

with

those

such

the

as

the

Intel

deal

of

architecture

have conmand

documents which

Number

171867,

be

read

as a first

Order

general

Archi

architecture

tecure

provides

a

General

surrmary

required

the

Interface

different

when

in

information

relies

432

am

00

archi

tecture

functions

of

the

the

iAPX

technical

of

the

of

the

provide

provides

Number

Reference

detailed

Data

of

the

reading

Processor

others.

oontained

above

which

of

the

GOP

when

Chapters 1 through 6 of

the

Interface

Processor,

cx:x>peration between an

logical

for

interrupts,

the

I/O

processor

objects,

am

descriptions

initialization

this

IP

for

manual

allowing

and

Peripheral

a 432

of

may

are

the

system.

windCMs

be

foum

oomposedof

reader

to

Subsystems

Detailed

and

functions,

in

the

apperrlices.

descriptions

understand

in

forming a

the

representations

faults,

iii

of

Page 5

TABLE

OF

CCNl'ENI'S

TITLE

1.

KE'Y'

1-1.

1-2.

1-3.

1-4.

1-5.

crncEP'l'S

Peripheral

Basic

Peripheral

...•.....•.•..•....••.....•••.•••••••••...•..•..

Subsystems

I/O

~e1

Subsystem

Peripheral

Attached Processor

Interface

Peripheral

I/O

Controller

Execution Environments

Wind~

Functions

I/O

lv1OO.el

Data

I/O

StmmaI"Y

Flow

EKaII1J?le

GOP

Process

Printer

Printer

Printer

Supplementary

Physical

Reference

Interconnect

••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••••••

Interface

Subsystem

Interface

•••••••••••••••••••••••••••

Hardware

•••••••••••••••

•••••••••••••••••••••••••••••••••

Processor

Subsystem

Interface

Software

•••••••••••••••

••••••••••••••••••••••••••••••••••

•••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••••

Summary

•••••••••••••••••••••••••••••••••••••••••••

Server Task

Task (Device Task)

Reply Task

Interface

Access

•••••••••••••••••••••••••••

Perspective

••••••••••••••••••••••••••••

Perspective

Perspective

Perspective

Processor

r.t:>de

•••••••••••••••••••••••••••••••

Facilities

•••••••••••••••••••••••••••••••••••

••••••••••••••••••••

•••••••••••••

•••••••••••••••••••••

•••••••••••••

~

•••••••••

-

•••

PAGE

1-1

1-1

1-4

l-7

1-7

1-7

1-9

1-10

1-10

1-11

1-11

1-13

1-14

1-14

1-16

1-19

1-21

1-21

1-21

1-22

1-22

1-22

2.

CB.:JEX::!'IS

2-1.

2-2.

2-3.

2-4.

2-5.

2-6.

2-7.

2-8.

iv

.ANI) OPERAroRS

S~y

Envi romnent

IP

C>]?er

Obj

ect

Addressing and Global

Of

Interface

ators

•••••••••••••••••••••••••••••••••••••••

Processor

•••••••••••••••••••••••••••••••••••••••••••

Facilities

••••••••••••••••••••••••••••••••••••••••••

Storage

Objects For Program Environments

Facilities

Processes

Process

Facilities

For Asynchronous Communication

and I£x::al Storage Resource

Scheduling and Dispatching

For Object

Management

Context Environment Manipulation

The

Four

Direct

Oi:>ject

vs.

Selectors

Entering

Entering

Entry

an Access Segment

the

Access Segments

Indirect

Accessibility

•••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••

Global Access Segment

••••••••••••••••

Management

••••••••••

•••••••••••••••••••••••••

••••••••••••••••

Management

••••••••••

•••••••••••••••••••••••

•••••••••••••••••••••••••

•••••••••••••••••••••••••

••••••••••••••••••••••••

•••••••••••••••••••••

II

••••••

••••••••••••••••••••

2-1

2-1

2-2

2-3

2-7

2-7

2-8

2-8

2-8

2-8

2-9

2-9

2-10

2-12

2-12

2-12

Page 6

3.

~

3-1.

3-2.

3-3.

3-4.

3-5.

•••••••••••••••••••••••••••••••••••••••••••••••••••••

WindCM

WindCM

Random

Block Mode.Data

Interconnect

AttribJtes

Wioo~

Subrange Base Address

Object

Direction

Transfer

Transfer

O\Terlay

Address Recognition

Consistency

Block

Block

Block

Block

Block

Status

Reference

............................................

Status

Mode

•••••••••••••••••••••••••••••••••••••••••••••••

Operation

Check

Mode

Data

Mode

Mode

MOde

r.1c>de

Mode

Transfers

Transfer

Transfer

Attributes

Consistency

Operation

Termination

Addressing

••••••••••••••.•••••••••••••••••••••••••••

arrl

Subrange

•••••••••••••••••••••••••••••••••••••••

Size

.

.........................................

•••••••••••••••••••••••••••••••••••••••••

•••••••••••••••••••••••••••••••••••

.....................................

· ............................... .

Check

••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••

· ............................... .

•••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••

3-1

3-2

3-2

3-4

3-5

3-6

3-6

3-6

3-7

3-9

3-9

3-9

3-12

3-14

3-14

3-15

3-15

3-16

3-17

3-20

4.

FtJNCI'IOOS

4-1.

4-2.

4-3.

4-4.

5 •

PIIY'S

5-1.

5-2.

5-3.

6.

FAULTS

6-1.

6-2.

•••••••••••••••••••••••••••••••••••••••••••••••••••

Function

Function

Process

Function

Function

Function

Function

ICAI..

Reference

Physical

Physical

Facility

Requests

Selection

Opcodes

Operands

~ecu

Completion

REF'ERmCE:

Reference

Reference

tion

Mode

Interface

••••••••••••••••••••••••••••••••••••••••

•••••••••••••••••••••••••••••••••••••

. ............................ .

......................................

.....................................

•••••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••

lvDDE

Switching

•••••••••••••••••••••••••••••••••••••

· ............................... .

MOde

Addressing

Mode

Functions

. ...................... .

......................................................

Fault

Fault

Reporting

Physical

Wgical

Categories

Window-Mapped

Mode

Context-level

Process-level

Processor-level

Haooling . ......................................... .

..........................................

Mode

.........................................

..........................................

of

Logical

Data

Mode

Faults

Faults

Faults

Transfer

Faults

•••••••••••••••••••••••••••••

•••••••••••••••••••••••••••

•••••••••••••••••••••

4-1

4-1

4-4

4-4

4-4

4-6

4-9

4-9

5-1

5-1

5-2

5-2

6-1

6-1

6-2

6-2

6-2

6-3

6-3

6-4

6-4

6-6

v

Page 7

APPENDICES

APPENDICES

A.

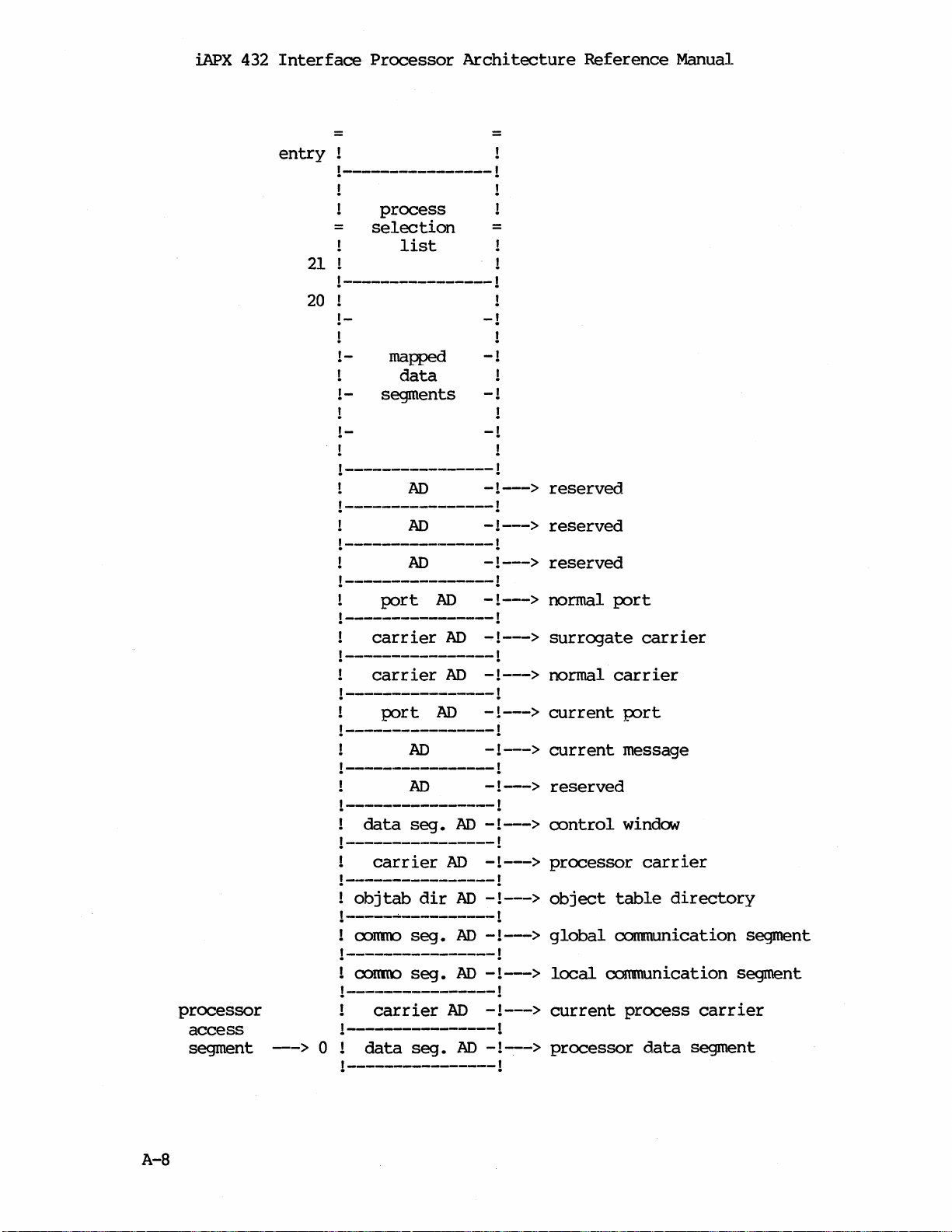

SYS'm1

A-I.

A-2.

A-3.

B.

FUNCTICN

c.

FA~T

C-l.

C-2.

C-3.

C-4.

D. IN'lERRlJP'r

E.

SYS'I'm

E-l.

E-2.

E-3.

F.

INTERPRX!ESS

~

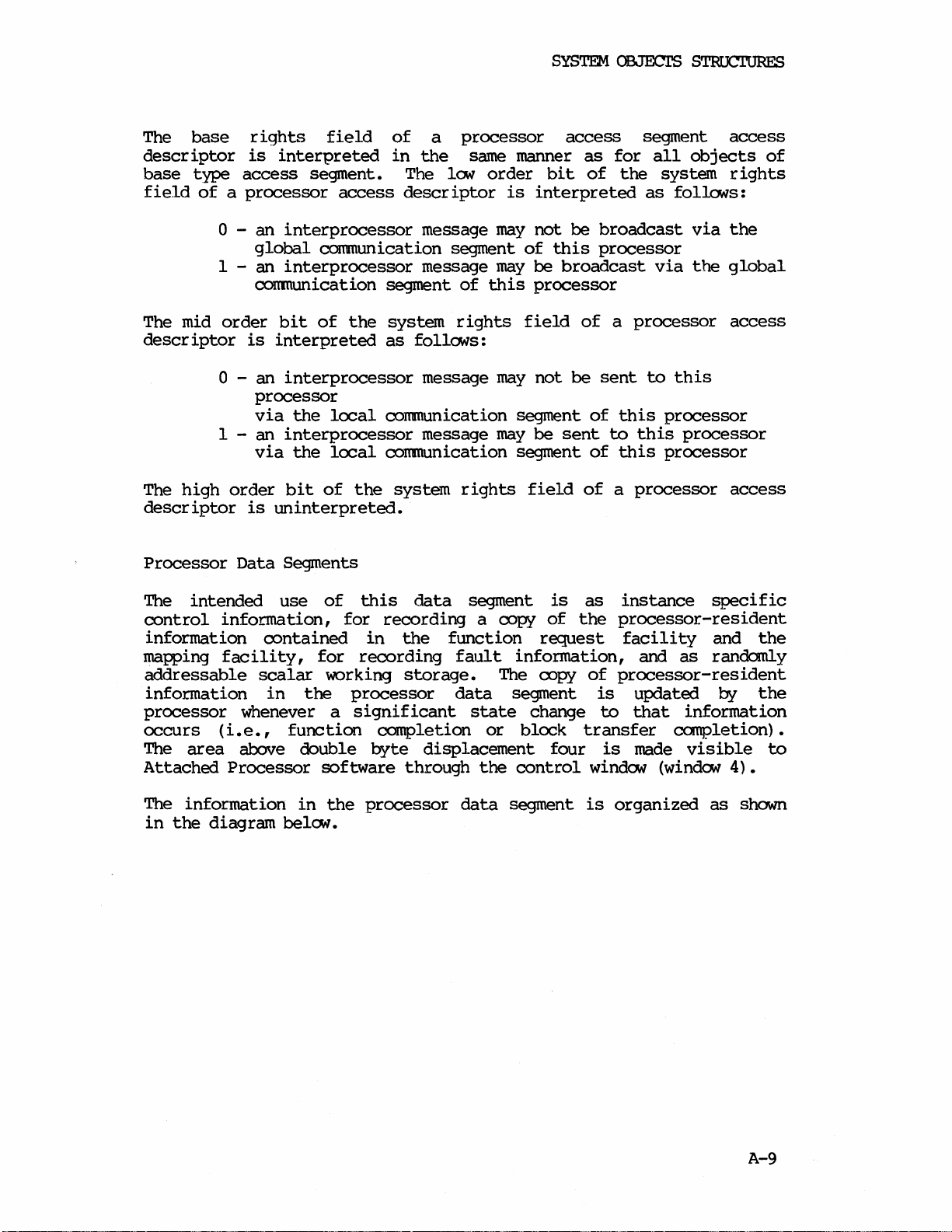

Context

Process

Processor

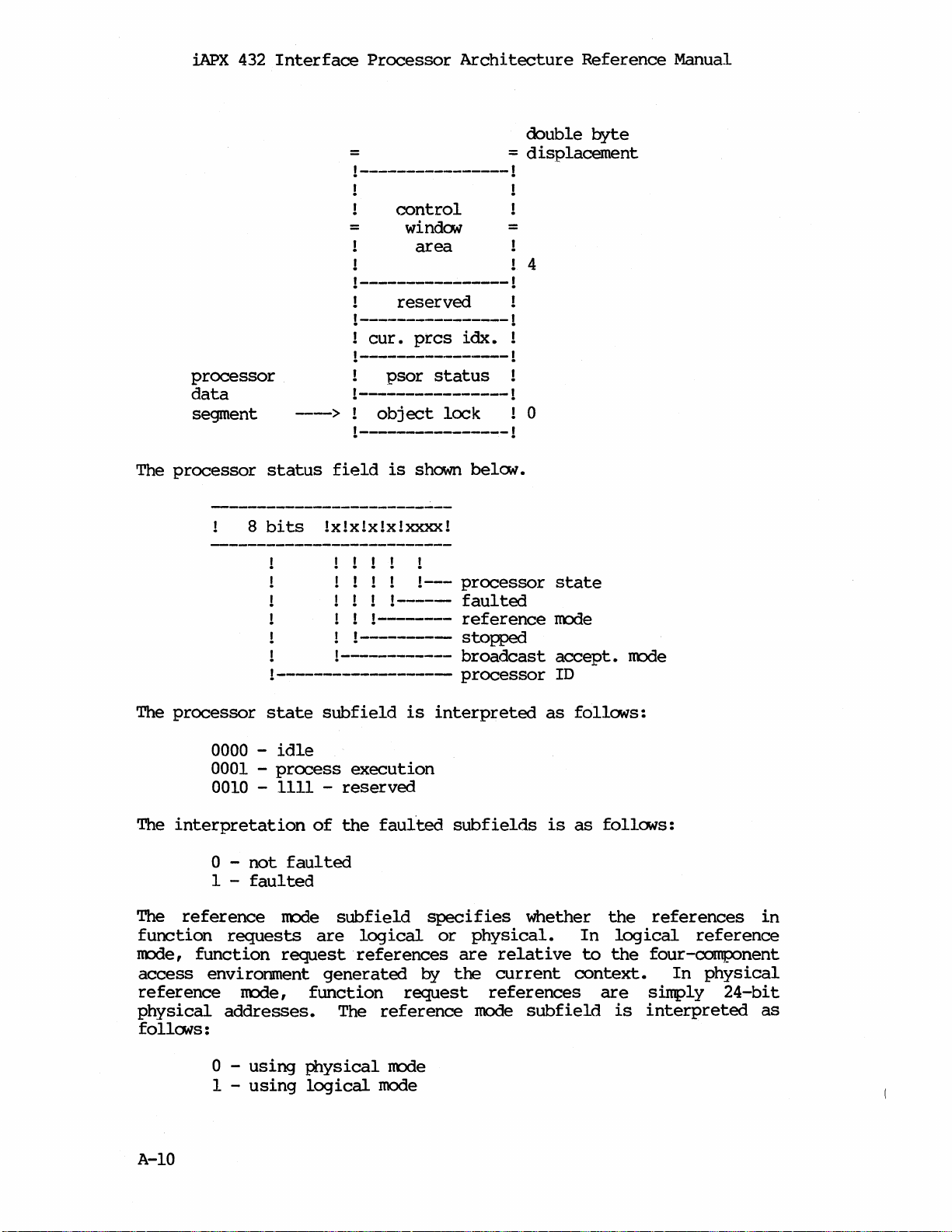

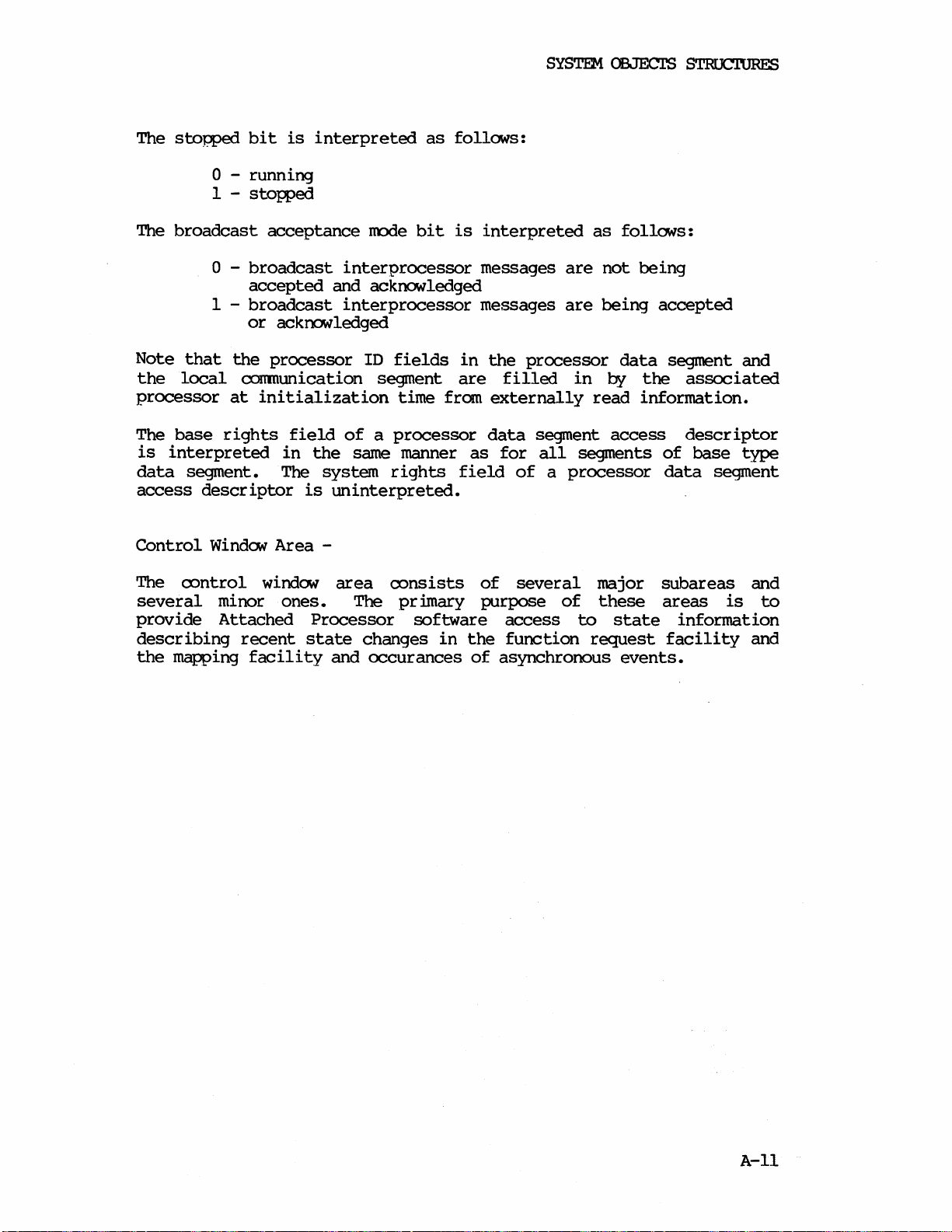

S~y

Fault

Fault

Object

Non-Instruction

INITIAl.JIZATlOO

System Reset

Establishing

System

S~

Objects

Objects

Objects

S~Y

Reporting ..........................................

Information

Level

lIAN'DLING...........................................

............................................

•••••••••••••••••••••••••••••••

Operator

•••••••••••••••••••••••••••••••••••••••

.

.........................................

........................................

"

Areas

Interface

..................................

Faults

•••••••••••••••••••••••.••••••••••••••••

•••••••••••••••••••••••••••••

Faults

•••••••••••••••••••••••••

•••••••

e._

•••••••

.

.............................................

an

Startup

~CATICN

Execution

...........................................

Environment

AND

DISPATCHING

••••••••••••••••••••

EXAMPLE

••••••••••

Page

A-l

A-I

A-3

A-7

B-1

C-l

C-l

C-l

C-5

C-IO

D--1

E-l

E-l

E-2

E-5

F-l

vi

Page 8

TABLES

TITLE

1-1.

2-1.

2-2.

2-3.

3-1.

B-1.

B-2.

B-3.

D-l.

E-l.

Printer

IP/GDP

IP/GDP

Example Legend

System Object Comparison

Operator Comparison

Direct/Indirect

Window

Attribute

Alphabetical

IP

Function

IP Function

Interrupt

Window

Configuration

Summary

Summary

Sources

Accessibility

Summary

Index

to

by Function

by Operator

••••••••••••••••••••••••••••••••••••••••

Following

•••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••

•••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••

•••••••••••••••••••••••••••••••••

IP Functions

•••••••••••••••••••••••

Code

ID

INIT

•••••••••••••••••••••

•••••••••••••••••••••••

••••••••••••••••••••••

PAGE

1-18

2-3

2-5

2-11

3-3

B-2

B-3

B-4

0-4

E-7

vii

Page 9

FIGURES

TITLE

1-1.

1-2.

1-3.

1-4.

1-5.

1-6.

1-7.

1-8.

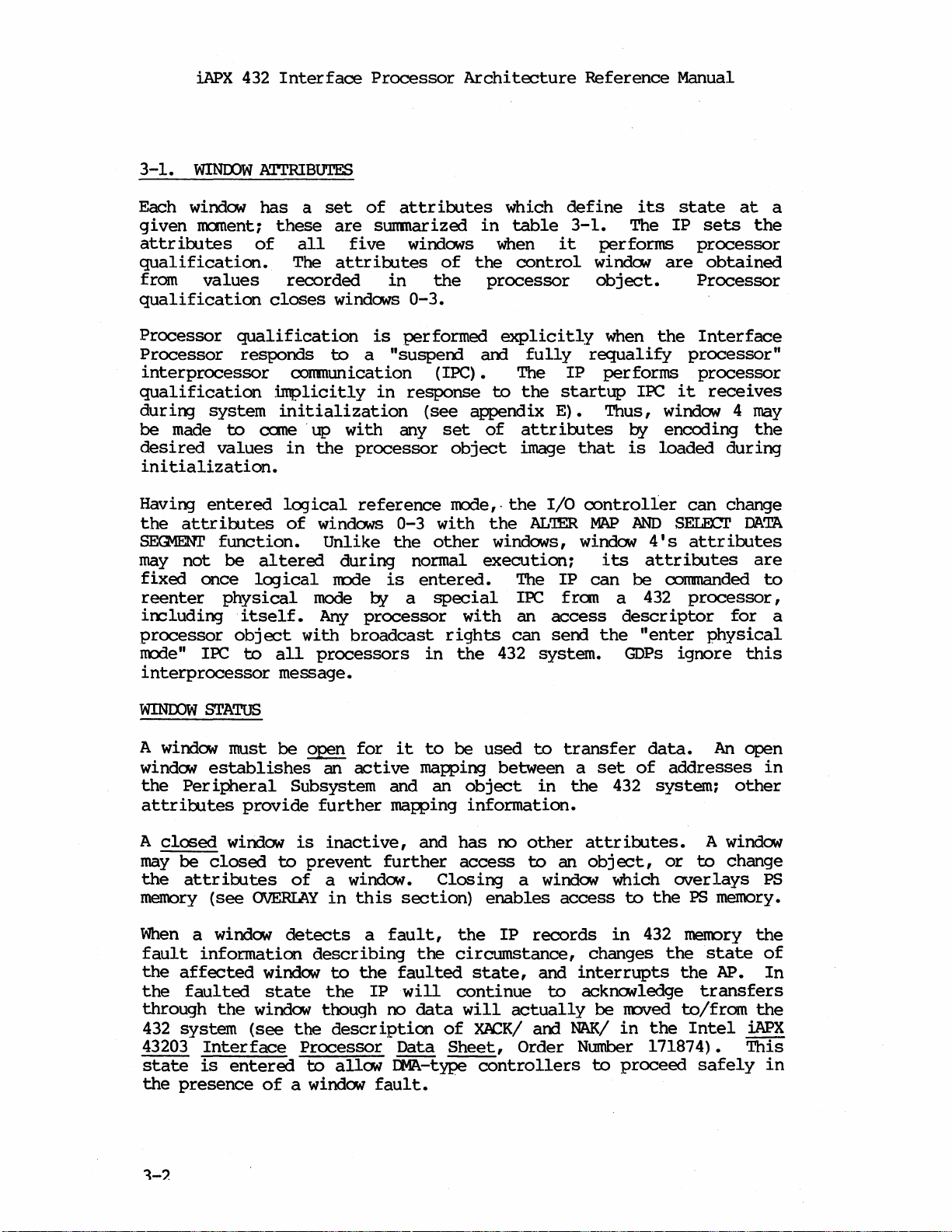

3-1.

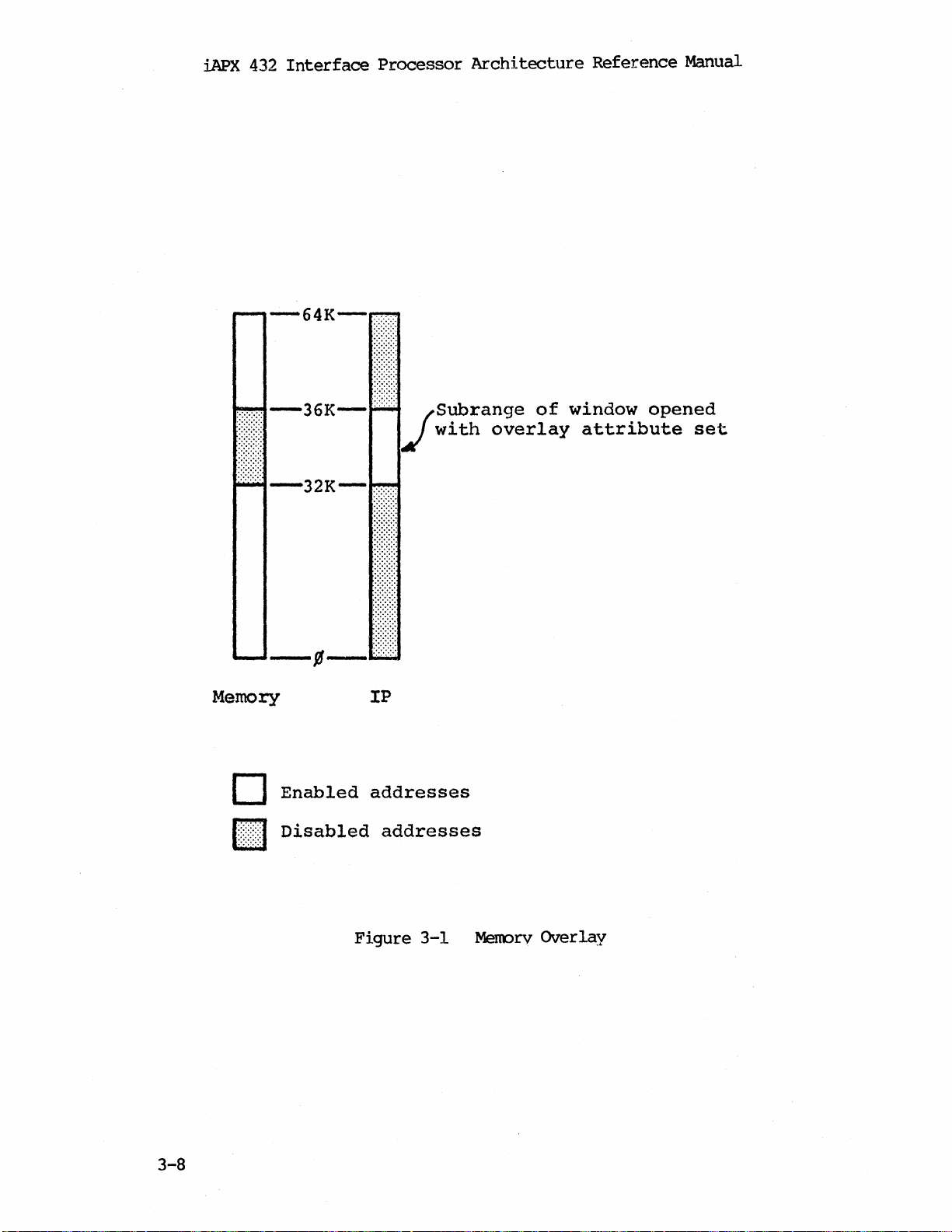

3-2.

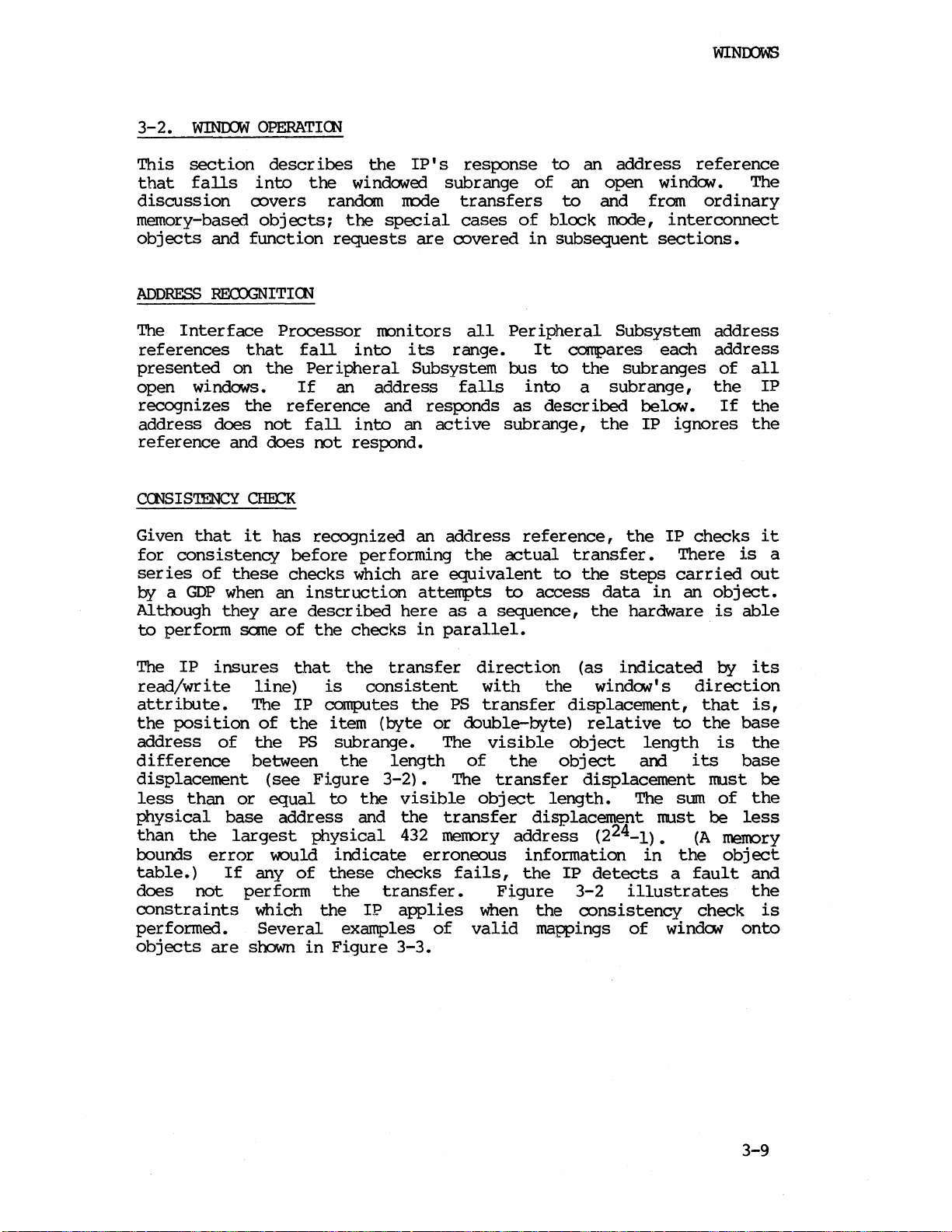

3-3.

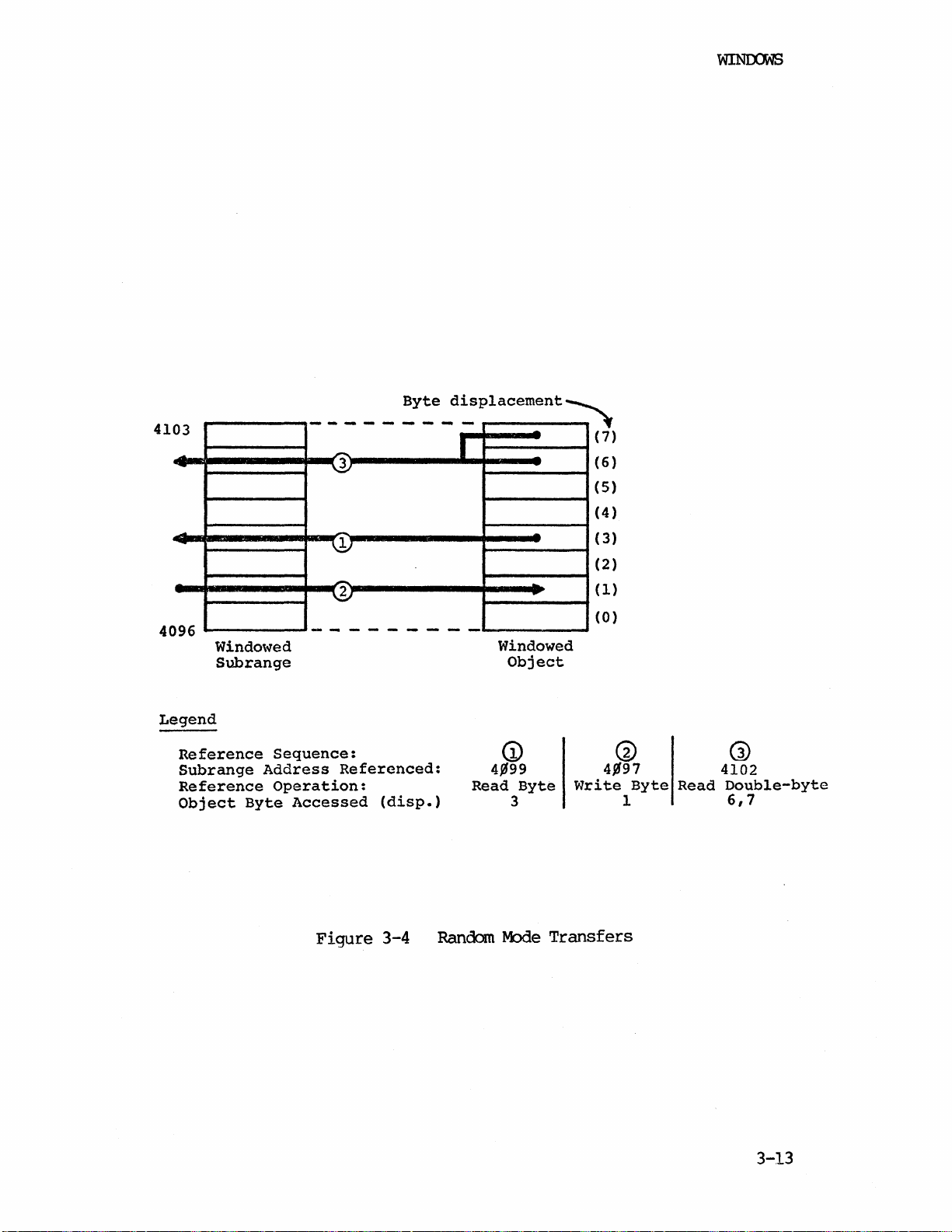

3-4.

3-5.

3-6.

4-1.

4-2.

4-3.

4-4.

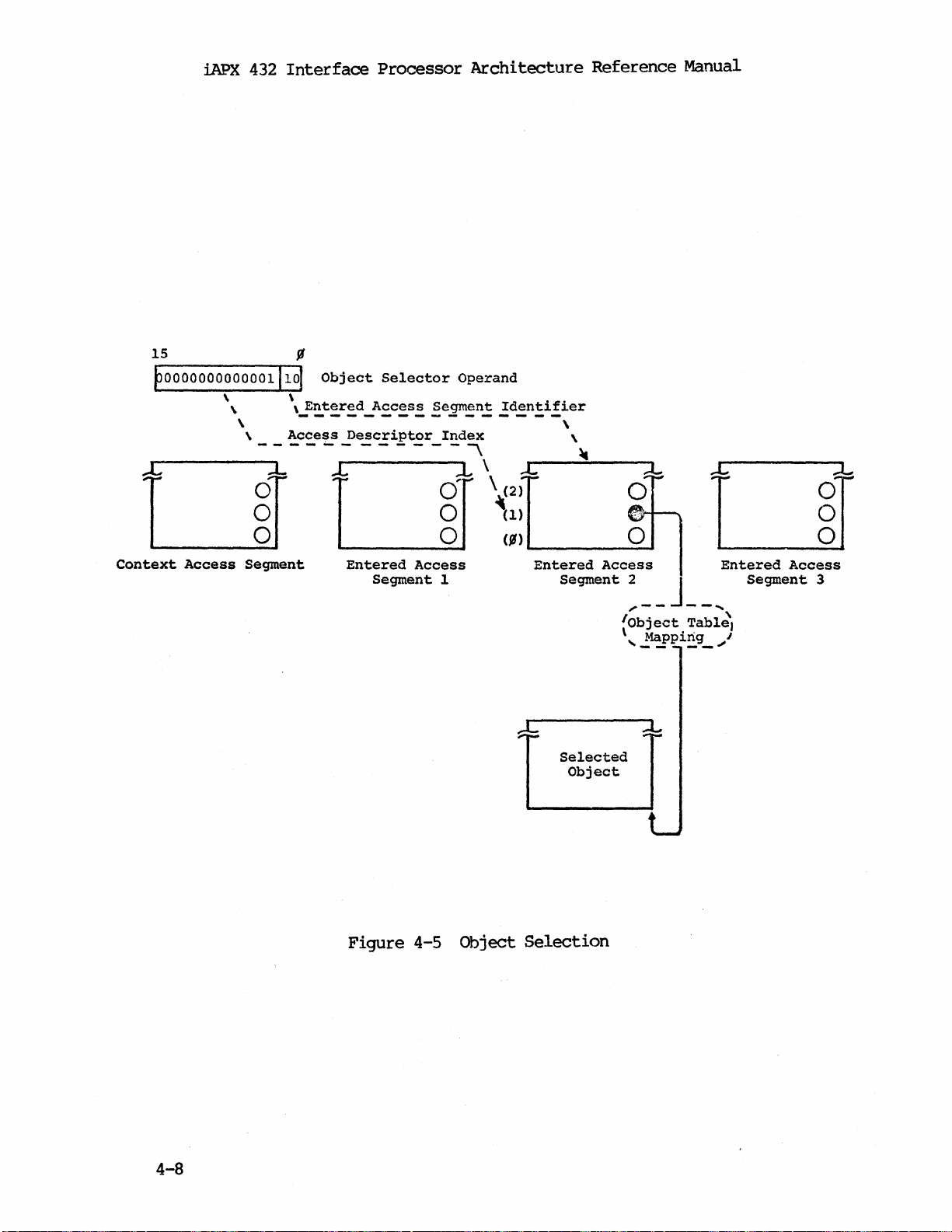

4-5.

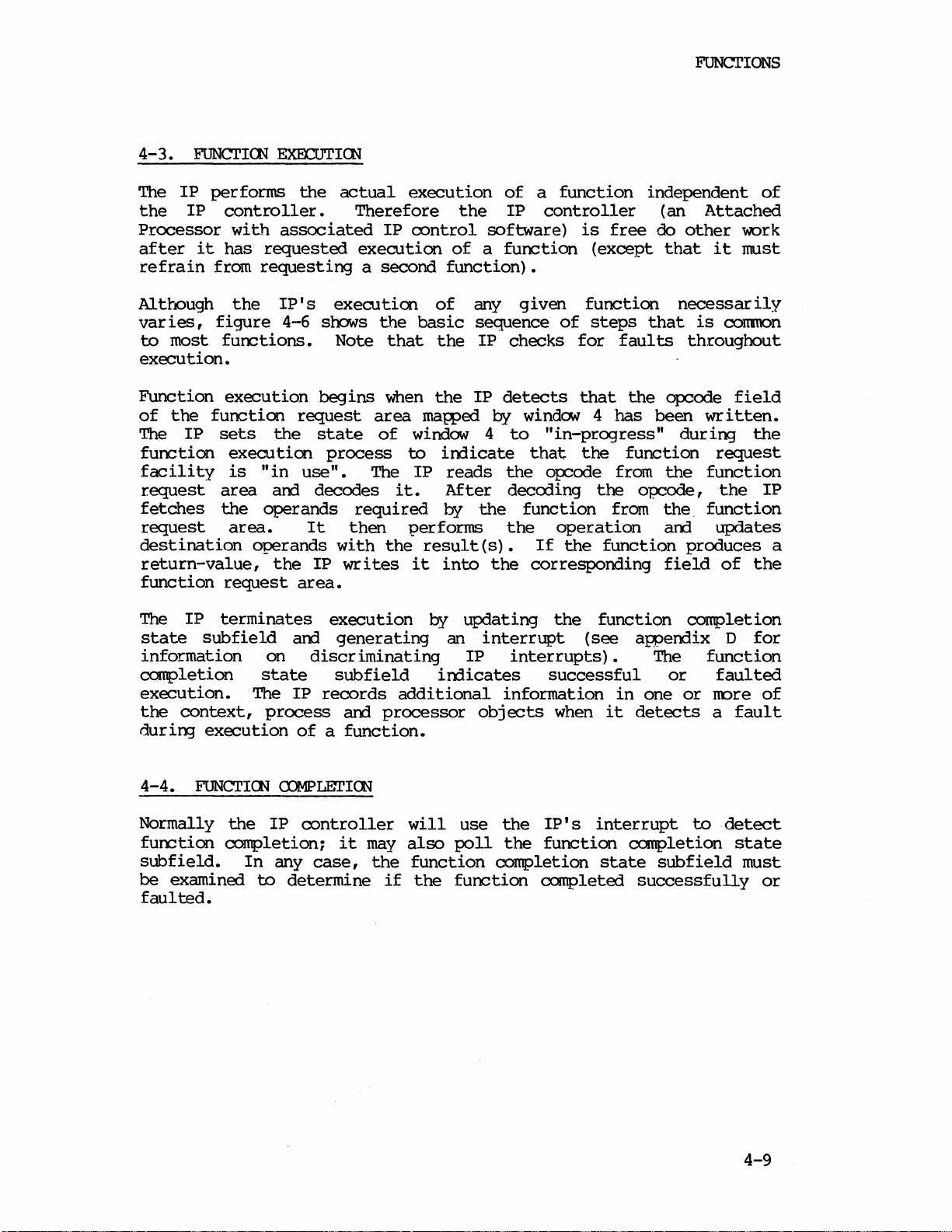

4-6.

6-1.

0-1.

E-l.

F-l.

F-2.

F-3.

F-4.

F-5.

F-6

432

System

Basic I/O Service Cycle

Peripheral

Peripheral

Interface

I/O Data

Pr

inter

~aInple

~ry

Subrange/Window

Valid

Window/Object

Random

Block

Block

Mode

Mode

Function Request Area

Function

and

Peripheral

Subsystems

••••••••••••••••••••••••••••••••••

Subsystem

Subsystem

Processor

Flow

E::KaInple

Pr

int

Over

lay

Summary

Object

•••••••••••••••••••••••••••••••••••••••••••

Interface

Interface

Window

••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••••••

......................................

Attributes

Mapping

Mode

Transfers

••••••••••••••••••••••••••••••••••••

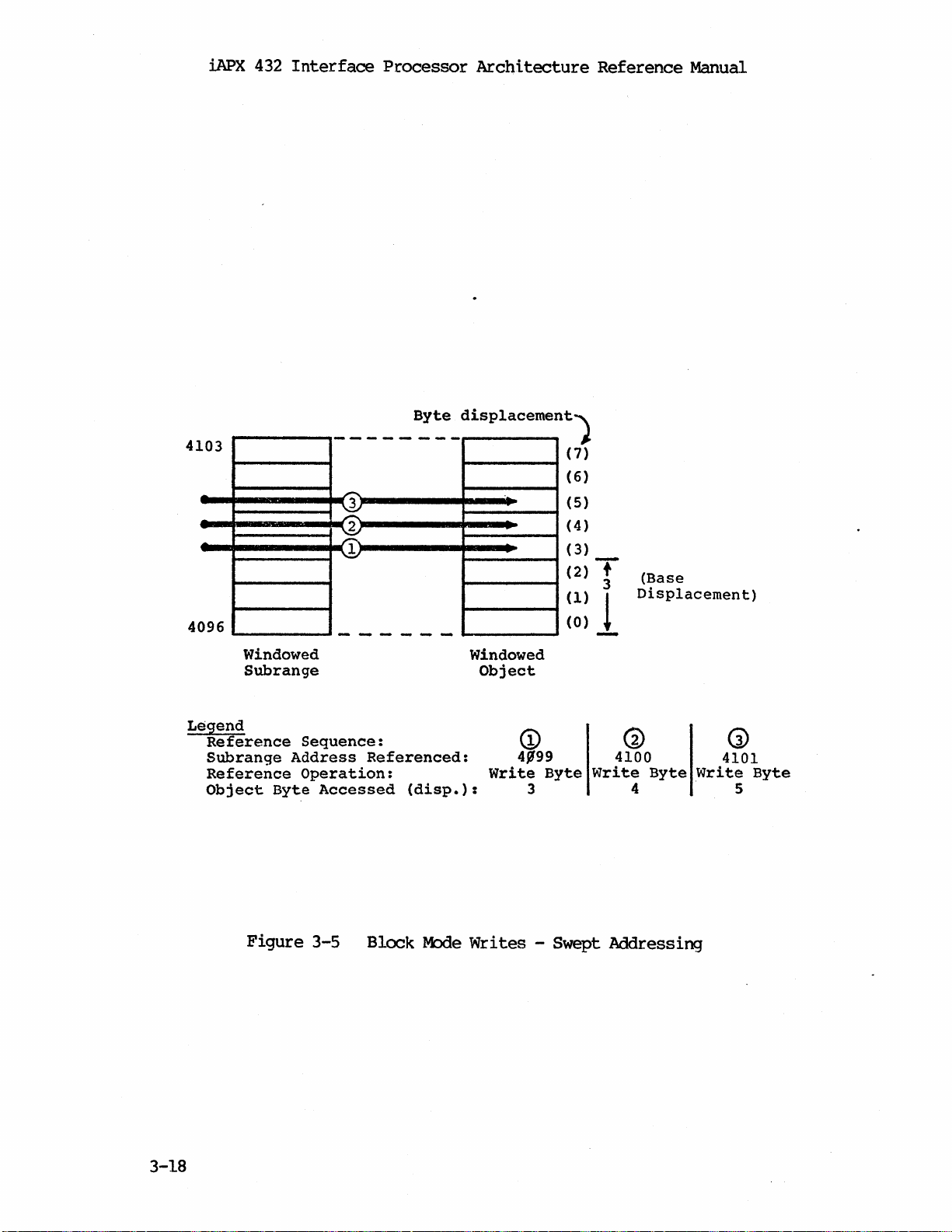

Writes--Swept Addressing

Reads--Source Addressing

••••••••••••••••••••••••••••••••••••

~arrple

•••••••••••••••••••••••••••••••••••••••••

•••••••••••••••••••••••••••••••

(Logical

••••••••••••••••••••••••••••••

Function Performance Phases-AP

Furl.ction Operand 'I'ypes

Object

Selection

•••••••••••••••••••••••••••••••••••••••••

Basic IP Function Execution

Fault

Interrupt

Reporting

Handler

State

Processor Object Location

Print

~ample

Objects

IP Performs Blocking

GOP

~ecutes

IP

Responds

Window

Print

Manipulation

Reply

SEND

to

and

IOC

••••••••••••••••••••••••••••••••••••••••••••••

•••••••••••••••••••••••••••••••••••

Flow

••••••••••••••••••••••••••••••••••••

. ...................................... .

••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••

RECEIVE

Unblocks

•••••••••••••••••••••••••••••••••••••••

••••••••••••••••••••••••••••••••••••••

•••••••••••••••••••••

•••••••••••••••••••••••••••

Hardware

••••••••••••••••••

Mode)

••••••••••••••••

••••••••••••••••••••••

••••••••••••••••••••••

View

••••••••••••••••••••••

•••••••••••••••••••••••••

•••••••••••••••••••••••••••••

REX:EIVE

•••••••••••••••••••

PAGE

1-2

1-5

1-6

1-8

1-12

1-15

1-17

1-20

.

3-8

3-10

3-11

3-13

3-18

3-19

4-2

4-3

4-5

4-7

4-8

4-10

6-5

D-2

E-3

F-2

F-ll

F-12

F-13

F-14

F-15

viii

Page 10

CHAPTER

KEY

CCNCEPTS

1

This

connection

Peripheral

Section

Peripheral

of

chapter

chapter

first

I/O

four

operations,

Interface

reviews

for

an

the

simple

example

with

Subsystems

Processors

the

interface

1-3

Subsystem

IP.

introduces

addressing,

special

1-1.

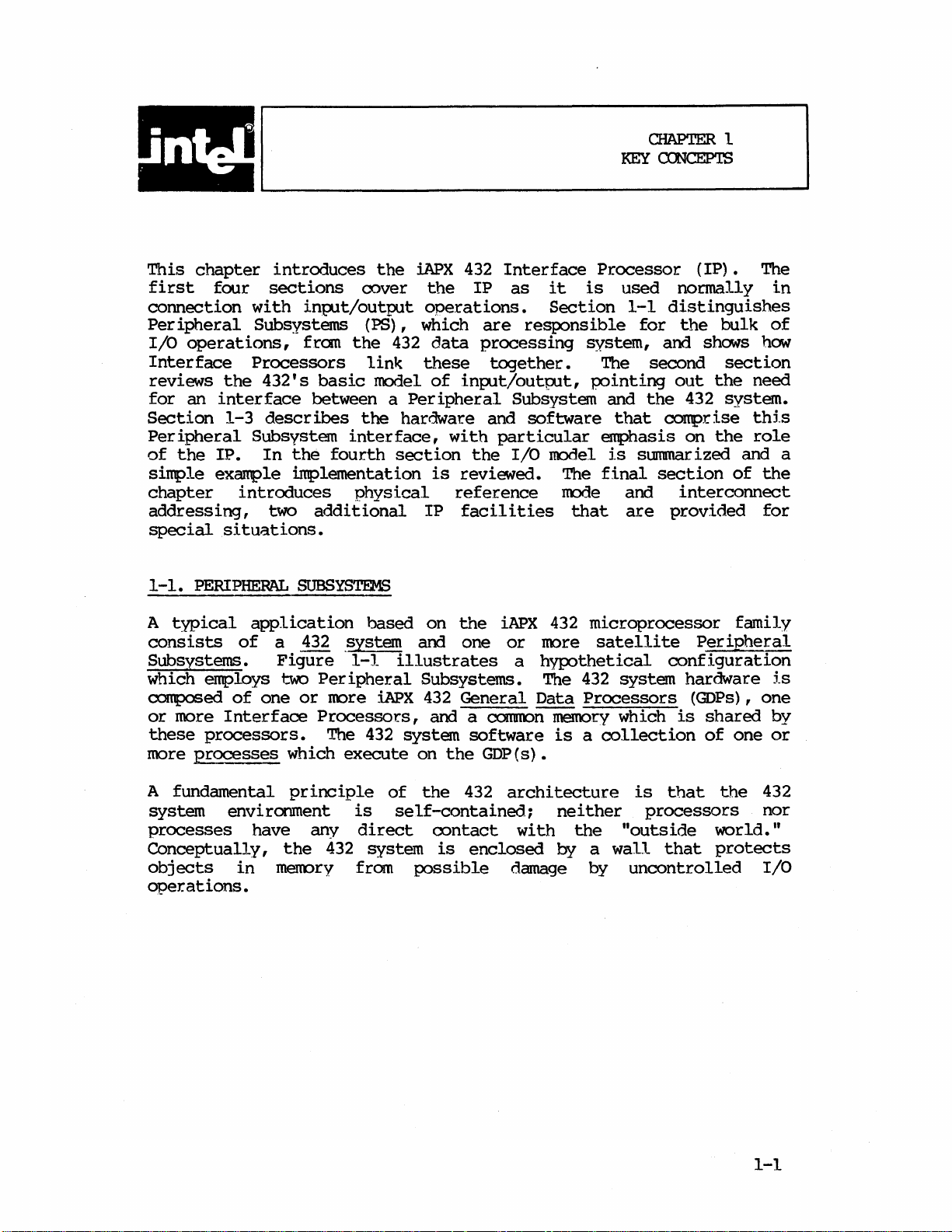

A

typical

consists

situations.

PERIPHERAL

application

of

Subsystems.

which employs

composed

or

more

these

more

of

one

Interface

processors.

processes

introduces

sections

inIXlt/output

fran

432' s

basic

between a

descr

In

ibes

the

fourth

~lementation

two

additional

the

iAPX

cover

(PS),

the

432

link

model

Peripheral

the

hardware and

interface,

section

physical

the

operations.

which

data

these

of

with

is

reviewed.

reference

IP

SUBSYSTEMS

based

on

the

a 432 .system and one

Figure

two

or

which

1-1

illustrates

Per

ipheral

more

iAPx

Processors,

The 432

system

execute

Subsystems. The 432 system hardware

432

General

and a

on

the

432

Interface

IP

as

it

Section

are

responsible

processing

together.

inp.lt/outp,lt,

Subsystem and

software

particular

the

I/O

roc>del

The

m::>de

facilities

iAPX

432

or

more

a

hypothetical

Data

COII1I'OC>n

software

memory

is a collection

GDP(s).

Processor

is

used

1-1

distinguishes

for

system,

and shows how

The second

pointing

the

that

conpr

emphasis on

i.s

summar

final

section

and

that

are

provid.ed

microprocessor

satellite

configuration

Processors

which

(IP).

The

normally

the

bulk

section

out

the

need

432

system.

ise

this

the

role

ized

and a

of

the

interconnect

for

family

Peripheral

(GDPs),

is

shared

of

one

one

in

of

is

by

or

A fundamental

system

processes

environment

have any

Conceptually,

objects

in

oper.ations.

principle

the

432 system

memory

of

is

direct

from

the

432

se

If-contained.;

oontact

is

enclosed

possible

architecture

nei

ther

with

by

the

a

damage by

is

that

processors

"outside

wall

that

uncontrolled

the

432

nor

world."

protects

I/O

1-1

Page 11

iAPX

432

Interface

Processor

Architecture

Reference Manual

432

System/Peripheral

Figure

1-1

Memory

Subsystem

432

System and

432

Boundary

Peripheral

SljbSystems

1-2

Page 12

In

a 432-based

inplt/out];Xlt

includes

A

Peripheral

memory,

software.

application

number

number

A

Peripheral

that

executes

channel,

complement

device

I/O

The number

depems

may

be

of

GDPs

it

assumes

in

however, each

of

application

system

that

microcooputer

a

432

Peripheral

A

Peripheral

iAPX

Interface

these

very

and

432

is

general

16-bit

Interface

Processor

the

microcomputer

system,

operations

control,

Subsystem

devices

var

ied

in

the

is

am

of

on

the

with

system.

the

bulk

is

delegated

timing,

an autonomous computer system

controllers,

Peripheral

I/O-intensiveness

changing

Subsystem resembles a

responsibility

parallel

with

for

432 system

Peripheral

hardware and

cost

can

bus,

am

oonmunicate

such

performance

as

Intel's

software

Subsystem.

Subsystem

is

attached

Processor

presents

standard

interface

432

that

two

processor

can

buses.

of

processing

to

Peripheral

interrupt

at

handling

least

Subsystems employed

of

needs,

and

conventional

l~level

I/O

processor(s).

Subsystem

can

resources

requirements.

over

a

standard

Multibus'IM

to

the

432

(IP).

separate

be

At

packet

adapted

the

bus

bus and

to

required

Subsystems;

and

one

processor,

the

application;

is

independent

mainframe

device

Unlike a simple

be

configured

that

precisely

In

8-

design,

system

by

hardware

interfaces.

the

nost

traditional

KEY

CCHE?TS

to

support

buffer

with

in

its

any

channel

su~rt

general,

or

may

serve

means

level,

One

other

this

ing

given

of

with

fits

l6-bi

of

is

•

own

and

the

the

in

and

a

any

t

as

an

an

of

a

8-

The

Interface

'lb

sUQ?Ort

separates

the

a

Peripheral

provides a set

expose a

its

single

contents

Subsystem. Tb

protection

with

windowed

mechanisms

segment.

An

Interface

which

are

operation

considerably,

be

manipulated

system

processes

Processor

also

of

they

Processor

is

transfer

Subsystem from

of

software-controlled

object

may

(data

be

transferred

preserve

in

the

access

to

432

additionally

invoked

these

by

Peripheral

functions

generally

as

enti

ties,

and

software

driven

of

information

structure)

the

integrity

432

system,

objects

(and

permit

and

executing

by

Peripheral

through

the

432

windows. A window

in

432

system

to

or

from

of

the

the

IP

only

which

provides

Subsystem

the

objects

enable

are

of

a

software.

returned

in

432 system

conmunication between 432

in a Peripheral

Subsystem

the

software.

wall

system,

is

memory

the

Peri.pheral

capability-based

provides

system

set

of

functions,

type

While

results)

memory

Subsystem.

that

the

used

so

that

the

data

varies

IP

to

PS

the

to

1-3

Page 13

iAPX

It

is

~rtant

utilize

and

protection

object,

Subsystem

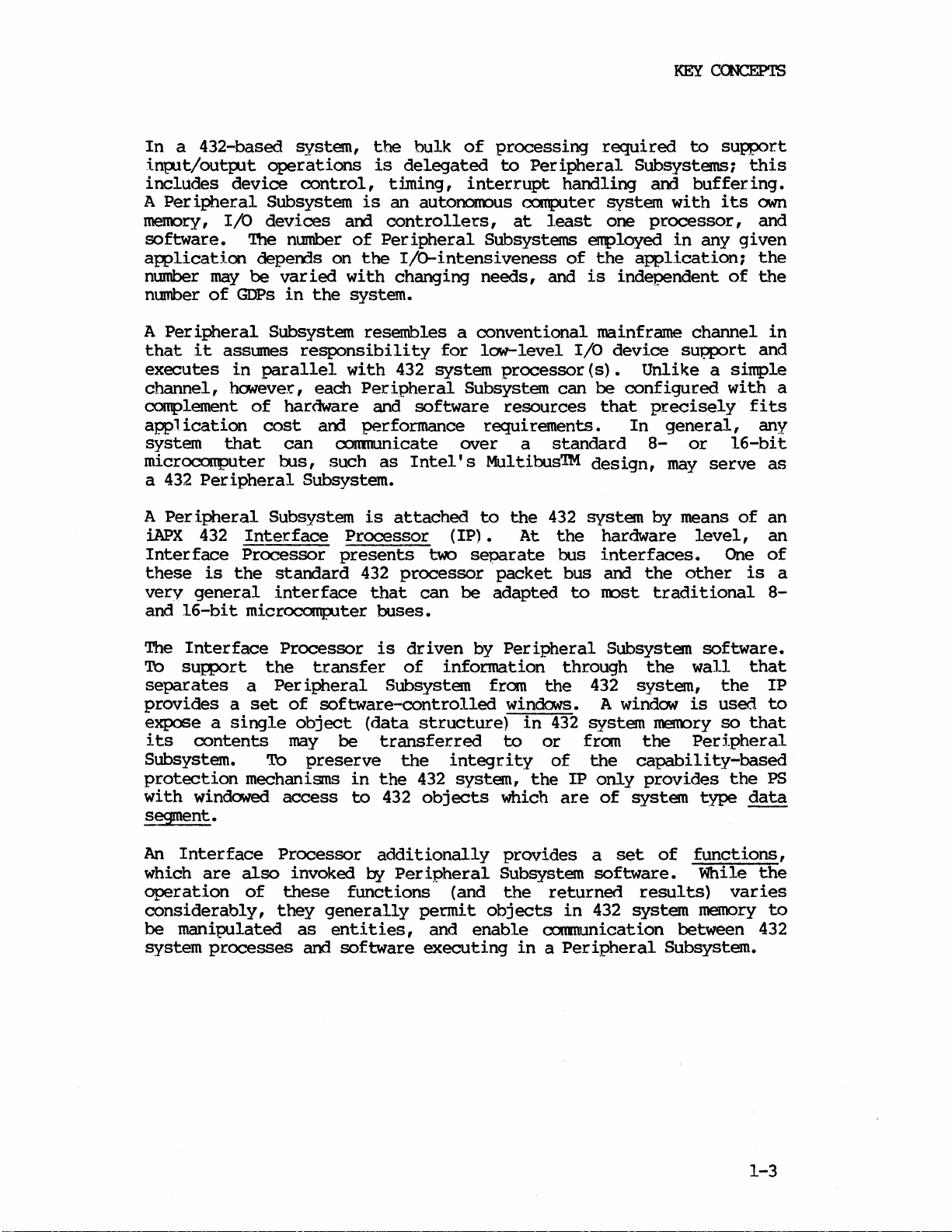

1-2.

As

figure

are

and a

software

BASIC

based

processes

this

software

manual, a

in

managing an

consumer

device

or

(e.

spc:x>ler).

432

Interface

to

strictly

systems.

function

I/O

MODEL

1-2

illustrates,

on

the

and

device

device

the

I/O

device.

producer

9

.,

a

Processor

note

that

enforce

Thus, a window

provides

to

interact

notion

of

tasks

task

Peripheral

An

of

data.

terminal),

Architecture

both

the

the

window and

standard

provides

a

E.rotected

with

input/output

passing

located

is

the

432

operations

messages between 432 system

in a Peripheral

consi.dered

Subsystem which

I/O

device

is

Thus an

a

file,

or

Reference

function

432

protected

way

system.

to

be

the

is

considered

I/O

device

a

pseudo-device

Manual

facilities

addressing

access

for

Peripheral

in

a 432

Subsystem.

hardware and

responsible

to

be

either

may

be

a

(e.

and

to

an

system

In

for

a

real

g.,

a

A message

contains

"read

carries

the

device

process.

acknowledge

A

very

between

Peripheral

but

in

with

the

the

subsystem boundary,

system

sent

information

file

XYZ"). The

out

the

task

The

completion

general

processes

Subsystem may,

any

case,

432's.

can

be

from a

operation.

returns

device

and

By

made

compatible

GOP

that

describes

device

the

task

may

of a request.

very

is

such a

powerful

inherent

or

may

facility

inter:PQsing a

the

standard

process

If

an

data

also

in

not,

with

which

the

requested

task

interprets

operation

as

a message

return

mechanism

the

432

have

will

not

Peripheral

432

any

device

requests

operation

the

generates

to

a message

for

passing

architecture.

its

own message

be

directly

Subsystem

interprocess

task

(see

I/O

service

(e.g.,

message and

input

the

originating

to

posi

ti

messages

A

facility,

compatible

interface

comnunication

figure

1-3).

data,

vel

y

given

at

1-4

Page 14

432

System

Service

Order

Messaqe

Peripheral

KEY

Subayatem

CONCEP'IS

-------------------

Procesa

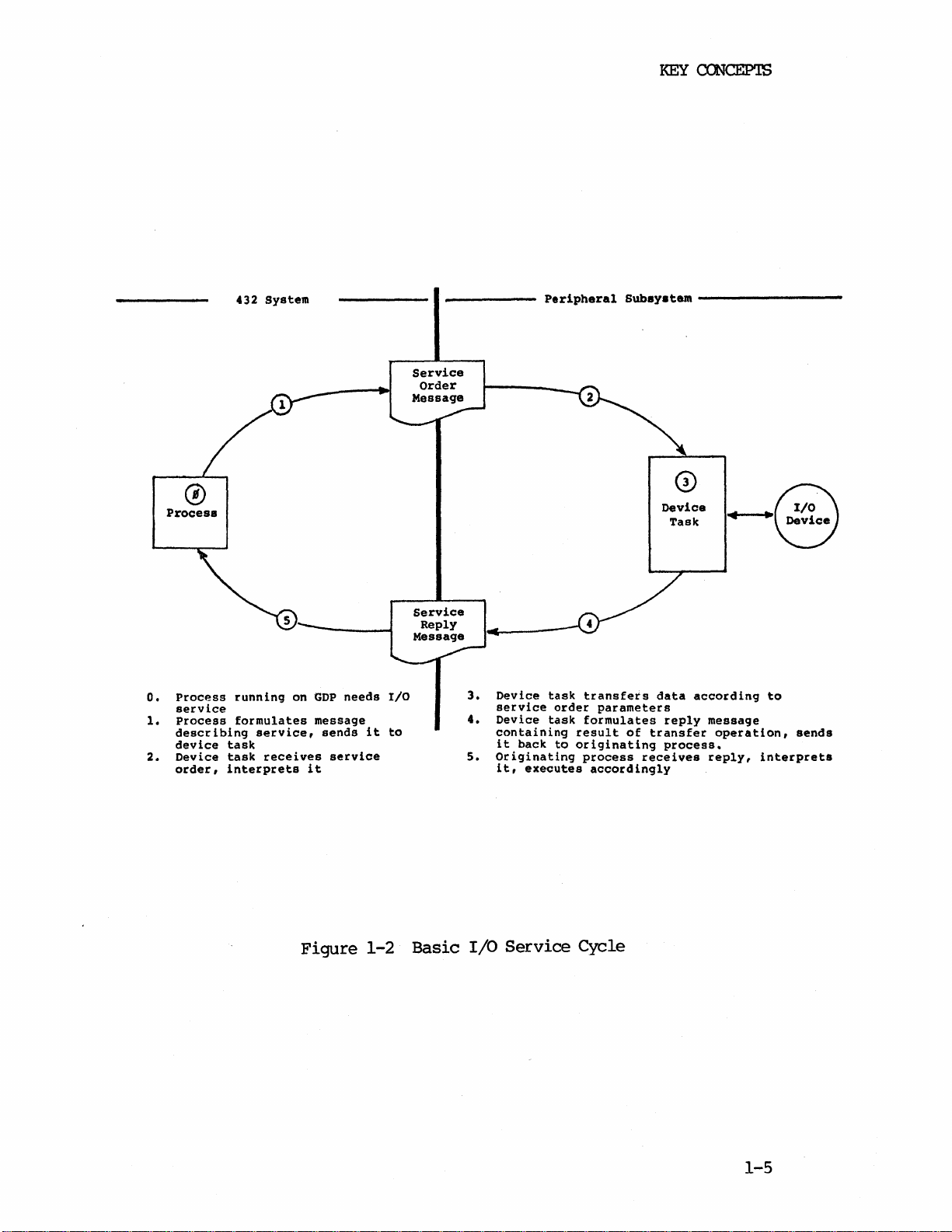

O.

1.

2.

order,

o

Process

service

Process

describing

device

Device

task

task

interprets

running

formulates

service,

receives

on

GDP

message

sends

service

it

Figure

needs

it

1-2

I/O

to

Service

Reply

Message

Basic

3.

Device

service

4.

Device

containing

it

5.

Originating

it,

I/O

task

order

task

back

to

executes

Service

transfers

parameters

formulates

result

originating

of

process

accordingly

Cycle

Device

Task

data

reply

transfer

process.

receives

-V

according

message

operation,

reply,

(:;'\

to

sends

interprets

1-5

Page 15

iAPX

432

432

Interface

System

Processor

-------Peripheral

Architecture

Reference

Subsystem

Manual

------------

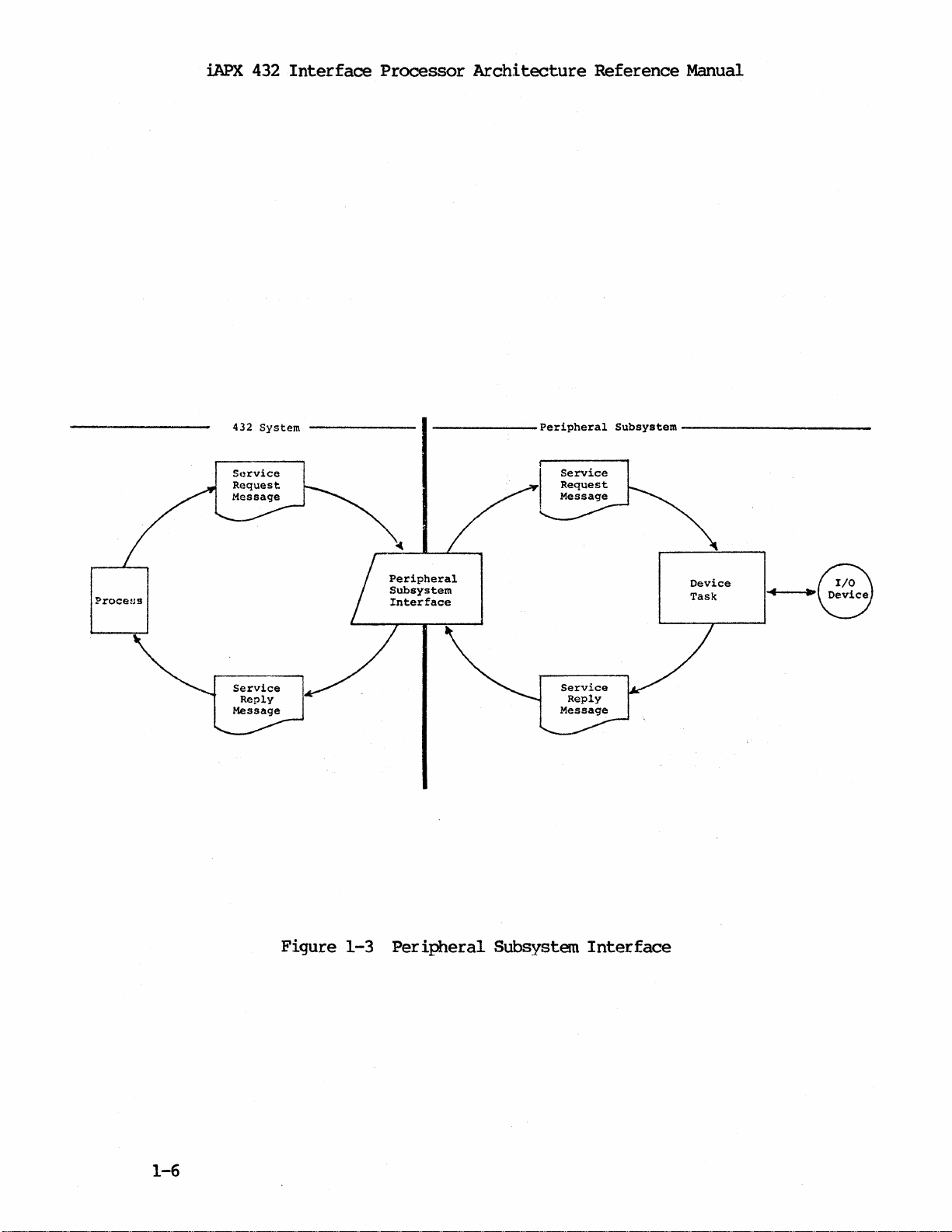

Figure

1-3

Peripheral Subsystem

Interface

Device

Task

f

1-6

Page 16

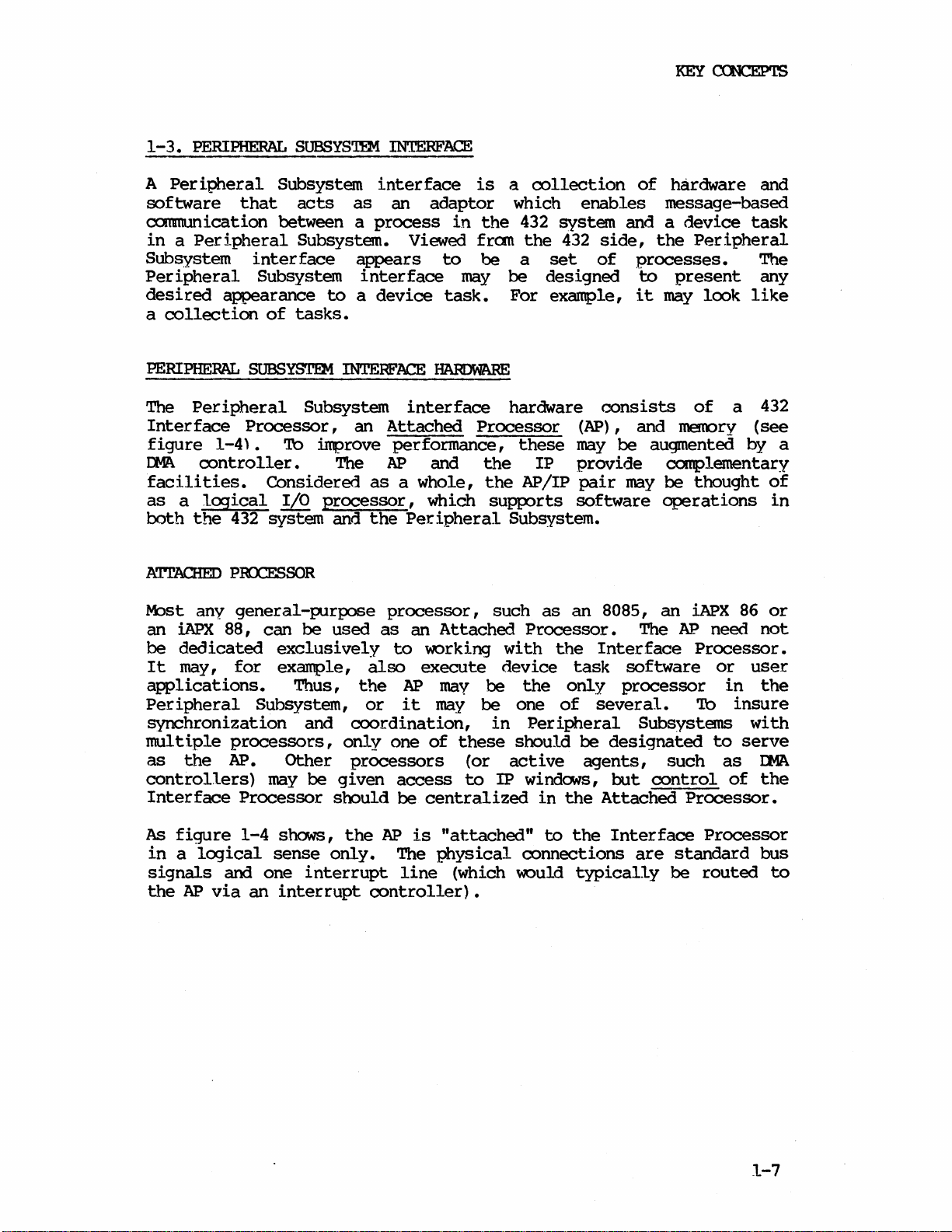

1-

3.

PERIPHERAL

A

Peripheral

software

that

SUBSYS'lm

Subsystem

acts

as

oammunication between a

in a Peripheral

Subsystem

Peripheral

desired

a

collection

appearance

Subsystem. Viewed from

interface

Subsystem

to a device

of

tasks.

INTERFACE

interface

is

an ad.aptor which

process

appears

interface

to

in

be

may

task.

a

collection

enables

the

432 system and a

the

432

a

set

be

designed

For example,

side,

of

processes.

it

of

hardware and

message-based

device

the

Peripheral

to

present

may

look

task

The

any

like

PERIPHERAL

The

Peripheral

Interface

figure

~

controller.

facili

as

a

both

ATrACHED

the

Most any

an

iAPX

be

dedicated

It

may,

SUBSYSTEM

Processor,

1-4).

ties.

Considered

logical

432

system and

PIU:X'3SOR

general-purpose

88,

can

for

applications.

Peripheral

Subsystem,

synchronization

multiple

as

controllers)

Interface

the

processors,

AP.

may

Processor

INTERFACE

Subsystem

an

To

improve

The

I/O

processor,

be

used

exclusively

example,

Thus,

the

or

and

coordination,

only

Other

processors ( or

be

given

should

HARDWARE

interface

Attached

performance,

AP

and

as

a whole,

which

the

Peripheral

processor,

as

an

Attached

to

working

also

AP

it

one

execute

may

may

of

access

be

centralized

hardware

Processor

the

the

supports

Subsystem.

such

with

device

be

be

one

in

these

should

active

to

IP windows,

(AP), and

these

AP

IP

/IP

may

provide

pair

software

as

an

Processor.

the

task

the

only

of

Peripheral

be

agents,

in

the

consists

be

augmented by a

complementary

may

be

operations

8085,

an

The

Interface

software

processor

several.

Subsystems

designated

such

but

control

Attached

of

a 432

tnem:)ry

thought

iAPX

AP

86

need

Processor.

or

in

'lb

insure

to

serve

as

of

Processor.

(see

of

in

or

not

user

the

with

IJ.V\.

the

As

figure

1-4

in a logical

signals

the

AP

and one

via

shows,

sense

an

interrupt

the

only.

interrupt

controller).

AP

is

The

line

"attached"

physical

connections

(which would

to

the

typically

Interface

are

standard

be

Processor

bus

routed

to

1-7

Page 17

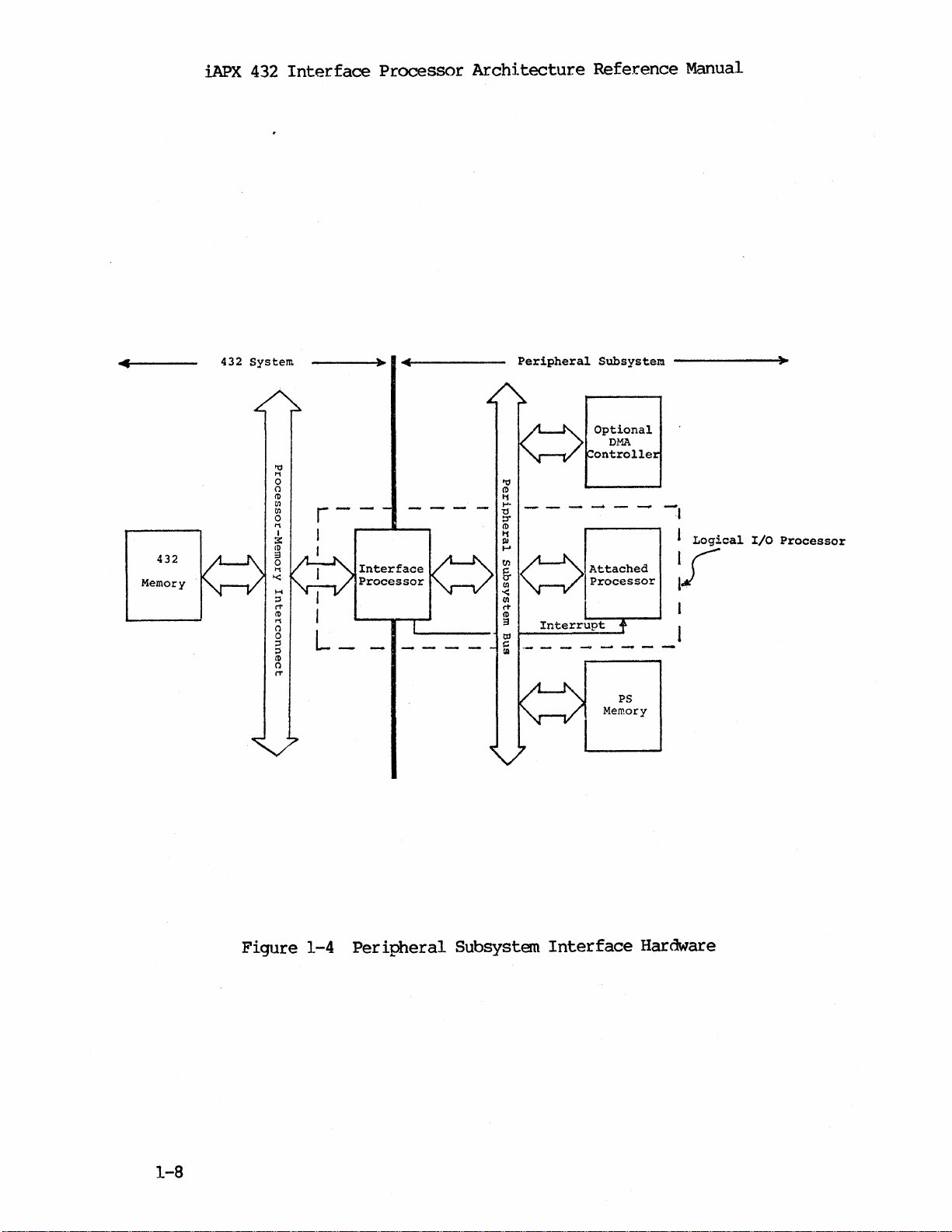

iAPX

432

Interface

Processor

Architecture

Reference Manual

432

Memory

432

System

"tt

H

o

(1

en

UI

UI

o

H

I

3:

(1)

:I

o

H

'<

H

::s

rt

en

H

(1

o

::s

::s

(1)

n

rt

--------.~

~~~---------

'-------01

Peripheral

"tt

co

t1

~.

~----

:J"

(1)

t1

I»

I-'

~

~Attached

~

~Iprocessor

rt'

(1)

EJ

to

I-----~--'

;

.....

-

Optional

ontrolle

.....

.........

Subsystem

DMA

---.

-...~-

PS

Memory

-,

J

Logical

:)

I/O

Processor

1-8

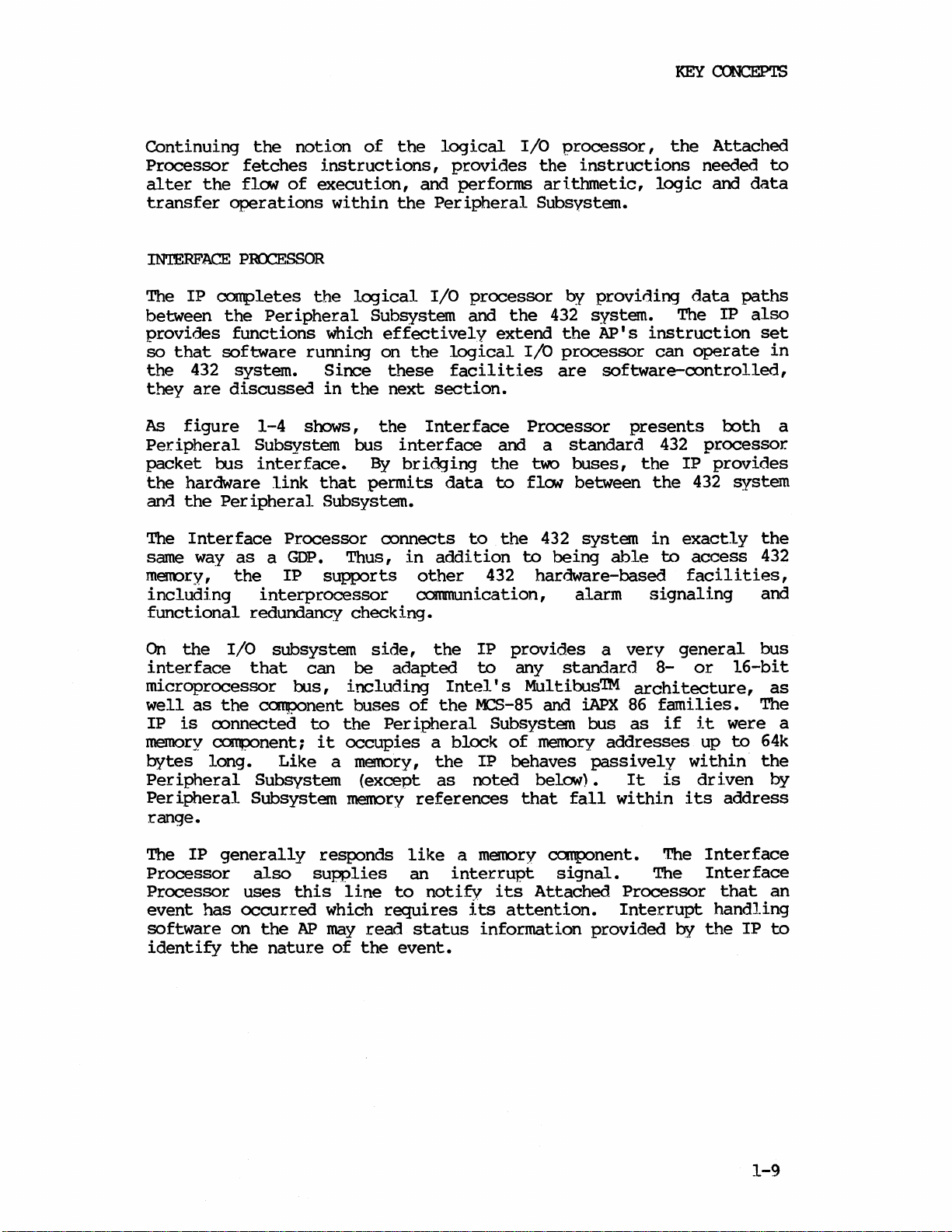

Figure 1-4

Peripheral

Subsystem

Interface

Hardware

Page 18

KEY

COOCEPTS

Continuing

Processor

alter

transfer

the

operations

INTERFACE

The

IP

completes

between

the

provides

so

that

the

they

As

software

432

are

figure

discussed

Peripheral

packet

the

and

The

bus

hardware

the

Peripheral

Interface

same way

memory,

including

functional

the

notion

fetches

flow

P~SSOR

instructions,

of

execution,

the

Peripheral

functions

which

running

system.

Since

in

1-4

shows,

Subsystem bus

interface.

link

that

Subsystem.

Processor

as a GDP.

the

IP

supports

interprocessor

redundancy

of

the

within

the

logical

Subsystem and

effectively

on

the

these

the

next

the

interface

By

br

permits

connects

Thus,

in

checking.

logical

I/O

provides

and

performs

Peripheral

I/O

processor

the

extend

logical

I/O

facilities

section.

Interface

idging

data

to

addition

other

Processor

and a

the

two

to

flOll between

the

to

432

hardware-based

comnunication,

processor,

the

instructions

arithmetic,

Subsystem.

by

providing

432

system.

the

AP's

processor

are

software-controlled,

standard

buses,

432

system

being

able

alarm

the

logic

data

The

instruction

can

operate

presents

432

the

IP

the

432

in

exactly

to

access

facilities,

signaling

Attached

needed

and

to

data

paths

IP

also

set

in

both

processor

provides

system

the

432

and

a

On

the

I/O

interface

that

microprocessor

well

as

the

component

IP

is

oonnected

memory

bytes

Peripheral

Peripheral

component;

long.

Subsystem

Subsystem

range.

The

IP

generally

Processor

Processor

event

has

software

identify

also

uses

occurred

on

the

the

subsystem

can

bus,

to

it

Like

a menory,

responds

supplies

this

which

AP

may

nature

of

side,

be

including

buses

the

Peripheral

the

adapted

Intel's

of

the

IP

to

MCS-8S

occupies a blOCK

the

IP

(except

memory

line

requires

read

the

as

references

like

an

to

notify

status

event.

noted

a

memory

interrupt

fts

information

provides

any

standard

Multibus'lM

and

Subsystem

of

memory

behaves

below).

that

canponent.

signal.

its

Attached

attention.

a

iAPX

bus

addresses

passively

fall

within

Processor

Interrupt

provided

very

general

8-

or

architecture,

86

families.

as

if

it

up

within

It

is

driven

its

The

Interface

The

Interface

handling

by

the

bus

16-bit

as

The

were a

to

64k

the

by

address

that

an

IP

to

1-9

Page 19

iAPx

To

sunmar

interact

the

AP and

Processor

Subsystem

access

to

432

ize,

with

interrupts

respoms

agents

432

Interface

the

Attached

each

other

(bus

system

Processor

by means

generated

to

memory

masters),

memory

Processor

of

references,

such

via

the

Architecture

and

the

address

by

the

IP.

other

as

~

IP's

windows.

Reference

Interface

references

Since

active

controllers,

Manual

Processor

generated

the

Interface

Peripheral

may

by

obtain

PERIPHERAL

I/O

CCNrroLIER

The Per

this

manual

executes

by

the

system and

432

hardware

controller.

modification,

collection

operating

iRMX-86'lM)

message-based

the

432' s

this

approach

SUBSYSTEM

ipheral

refers

on

the

AP and

the

inposes

implementors

of

system (such

•

This

conmunication

intr

INTERFACE

Subsystem

to

Attached

the

IP

to

Peripheral

00

Tb

tasks

help

running under

type

insic

to

interprocess

the

device

as

system-wide conmunication

I/O

controller

oqrnpletely

synchronous

form

of

parameters.

am

between

application-defined.

procedure

calis,

SOFIWARE

interface

the

I/O

Processor

control

the

Subsystem.

constraints

simplify

may

wish

as

of

organization

within

oommunication

task

nndel.

the

I/O

It

with

is

managed

controller.

and

uses

flay

on

of

the

software

to

consider

the

control

iRMX-80™,

the

I/O

by

software,

The

the

facilities

data

between

structure

organization

organizing

of

iRMX-88™,

supports

controller,

I/O

controller

of

a

multitasking

asynchronous

similar

facility.

as

well

results

in

a

consistent,

Havever, corrmunication wi

controller

may

"messages"

also

am

be

being

device

~lemented

tasks,

passed

which

provided

the

432

the

I/O

and

it

as

a

or

to

Extending

thin

the

is

via

in

the

However

it

is

system through

There

windows,

are

am

three

fuoctions.

1-10

structured,

facilities

of

the

these

I/O

controller

provided

facilities:

by

interacts

the

Interface

execution

with

the

432

Processor.

environments,

Page 20

The

Interface

within

the

controller

of

system

t~e,

obj

is

the

ects

am

represented

controlling

is

analogous

environment

and

conmunication

Processor

provides

432 system which

in

the

432

system.

objects

I/O

associated

software

to

that

controller

by a

processor

like

the

environment

·"are

is

context

this

provides a standard

within

the

a

supports

This

used

and

represented

obj

ects.

object.

creates

of a process

framework

432

system.

process

the

addressing

operation

environment

manipulated

in

432

Like a GOP,

Representing

an

execution

running

for

is

embodied

by

the

memory

by

the

the

environment

on a

addressing,

KEY

CXNCEP'IS

environment

of

the

as a set

IP.

IP

IP

IP

At any

process

itself

and

that

GOP.

This

protection

I/O

its

Like a GOP,

controller

executed.

an

selects

This

environments

Peripheral

executing

controller,

processes

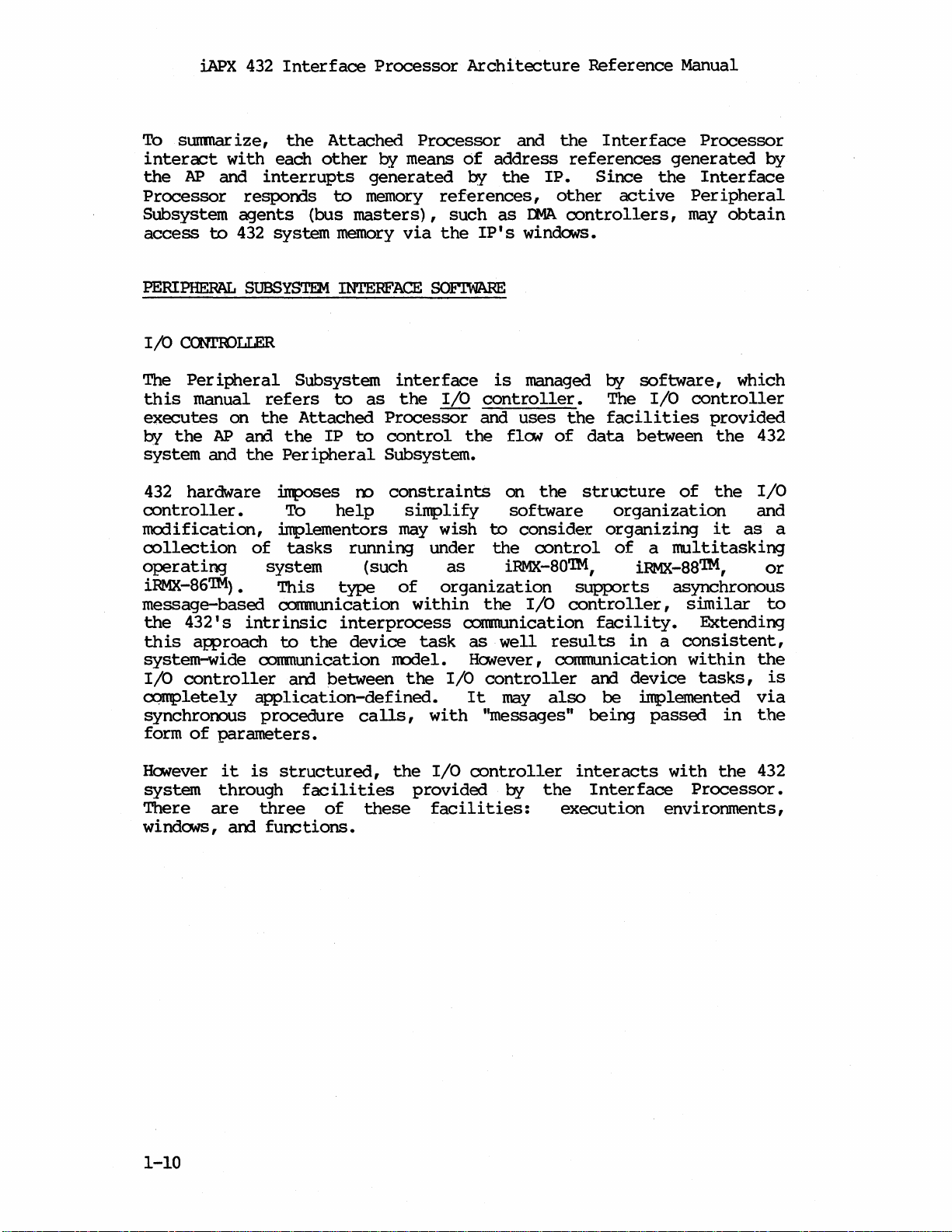

Every

Subsystem

Subsystem.

a

that

associated

transfer

is

correspondence,

Peripheral

occupied

system

Subsystem

obtains

address

object.

address

reference.

writing

Subsystem

by

the

memory

(e.

data

transfers

The

to

the

As

menory.

IP

suworts

the

environment

permits,

corresponding

If

function

error

on

is

with

of

data

performed

or

mapping, between a

memory

IP) and

(see

g • ,

from

action

system

far

the

data

figure

IP

the

from

of

object,

as

an

associated

the

it

multiple

for

example,

to

individual

an

error

behalf

confined

other

device

between

via

an

addresses

object

1-5).

controller)

the

Peripheral

IP,

in

is

transparent

is

concerned,

process

in

which a

the

environments.

establishment

device

occurs

of

to

the

IP

while

one

the

tasks

432

the

device

associated

are

system

window. A window

subrange

(within

of

system

When

reads

object;

an

the

type

agent

a windowed

writing

Subsystem

mapping

it

the

Peripheral

to

the

is

function

processes

IP

task

not

affected.

and a

of

range

data

in

into

to

agent

simply

is

of

separate

controller

of

process,

Peripheral

defines

consecutive

of

addresses

segment

the

Peripheral

address,

a windowed

the

windowed

Subsystem

making

reading

The

in

the

in

to

I/O

be

the

is

I/O

and

a

432

it

the

or

1-11

Page 21

iAPX

432

Interface

Processor

Architecture

Reference Manual

-f-Peripheral

Local

Interface

Subsystem

Memory

Processor

Memory

Addresses

space---"I

.....

----

Subrange

~

...

I

I

0,

432

System

IP

window maps a

of

peripheral

onto

(

-

---

an

Object

object

Memory

subrange

subsystem

in

Space

432 memory

--.

addresses

windowed

Memory

Reference"~"~

Figure

1-5

....

.....

----+

Interface

mm=-"ED"~~

- - - -

~

.......

Processor

..................

~

_--_

Window

....

1-12

Page 22

KEY

CCNCEPTS

Since a windCM

may

be

between

register,

appealing

with

caution.

and an

propagating

the

subsystem

complicate

number

scarce

means

buffered

simplest

windows

There

objects.

to

obtain

subranges

in

the

and a

to

the

were

accessing

or

from

object

the

error

of

windCMs,

resources

that

are

in

to

to

transfer.

four

at

PS

buffer

The

access

may

Peripheral

J:I.1A

controller

same

bus

is

referenced

an

obj

an

object

the

standpoint

Using a

in

real-time

boundary

recovery

JOOst

which

least

memory

all

data

IP

windows which

I/O

controller

to

be

interleaved

Subsystem.

arbitration

memory.

ect

and

and

windCM

432

into

as

applications

will

some

until

I/O

between

different

may

be

like

PS

an

of

memory

constraints

well.

memory, any

memory,

I/O

device.

"efficiency,"

to

directly

has

imposed by

the

432

Finally,

will

not

I/O

always

device

be

a windoo becomes

device

may

transfers

PS

memory

may

alter

be

objects.

and

may

be

For

example,

driving

transfers

constraints

an

object

"connect"

the

undesirable

system.

since

need

instantly

transfers

and 432

mapped

the

windCMS

References

driven

the

that

individual

and a

The

rut

it

latter

should

an

the

device

It

may

there

to

manage them

available.

will

available.

in

memory, and

system

onto

four

during

by

different

Attached

concurrently,

would

apply

transfer

PS

processor

may

be

used

I/O

device

effect

beyond

seriously

is a finite

This

have

It

to

may

use

memory.

different

execution

to

windowed

agents

Processor

subject

if

they

be

of

as

be

be

the

FUNCrICNS

A

fifth

access

IP

oontroller

operands

windCM's

window,

to

the

and

subrange.

comnands and

floppy

disk

interrupts

controller

to

transfer

a

function.

may

be

oontrol

can

interleaved

window.

the

Interface

requests

an

opcode

data

controller).

the

AP

read

requests

In

addition,

control

windCM,

Processor's

the

execution

into

This

to

procedure

a memory-roapped

Up:>n

and

provides

through

to

the

the

other

data

wi.th

function

provides

_function

of

predefined

is

CC>11pletion

status

control

four

windows

transfers

request

the

request

an

IP

function

locations

very

similar

peripheral

of

the

information

window. The

while

through

windows 0

sequences

IP

controller

facility.

in

the

controller

function,

which

IP

can

it

is

through

by

wr i

control

to

writing

(e.g.,

the

the

respond

executing

through

with

The

ting

IP

IP

3

the

1-13

Page 23

The

iAPX

IP's

o

432

function

alter

Interface

windows;

o exchange messages

the

standard

facility;

o

manitulate

set

permits

432

objects.

Processor

the

I/O

with

GOP

processes

interprocess

Architecture

controller

via

communication

Reference

to:

Manual

These

functions

Processor's

operate

The

in

the

combination

instruction

Peripheral

designing

powerful

the

432

by

utilizing

simple

1-4

•.

I/O

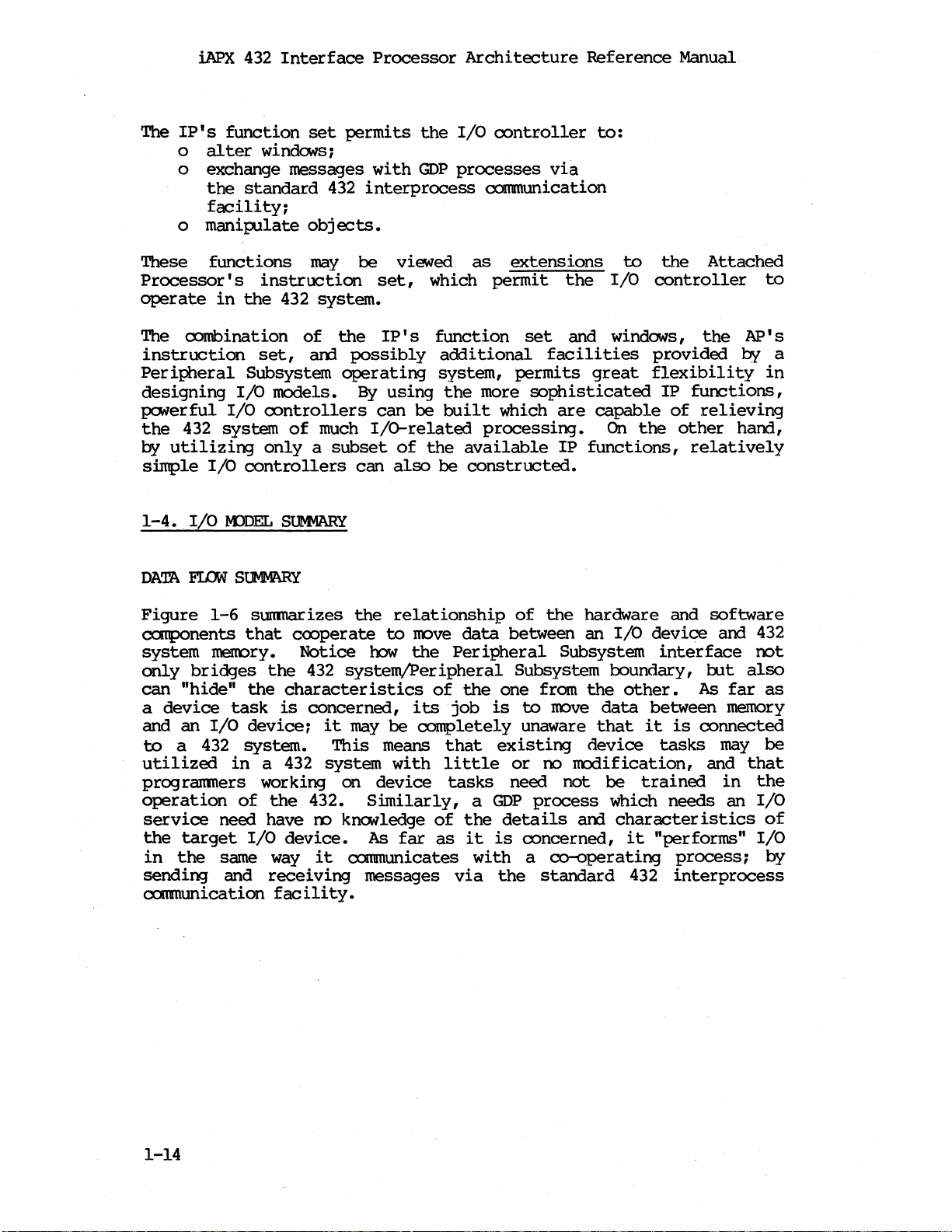

DATA

E'I1m

Figure

components

system

only

can

a

and

to

bridges

"hide"

device

an

a 432

utilized

Subsystem

I/O

I/O

system

I/O

controllers

IDDEL

SUMMARY

1-6

summarizes

that

menory.

the

task

I/O

device;

system.

in

progranmers

operation

service

the

target

in

the

sending

of

need have

I/O

same

and

communication

may

be

instruction

432

system.

of

the

set,

am

possibly

operating

models.

By

controllers

of

much

only a subset

can

Sur-MARY

the

cooperate

Notice

the

432

system/peripheral

characteristics

is

concerned,

it

may

This

a 432

system

working on

the

432.

no

knowledge

device.

way

it

communicates

receiving

messages

facility.

viewed

set,

which

IP' s function

additional

system,

using

can

be

the

built

I/O-related

of

the

available

also

be

constructed.

relationship

to

how

be

means

with

device

I1'Ove

the

its

data

Peripheral

of

the

job

completely

that

little

tasks

Similarly,

of

the

As

far

as

it

via

as

extensions

permit

set

facilities

permits

more

sophisticated

which

processing.

of

the

between

Subsystem

one from

is

to

unaware

existing

or

no

need

a

GOP

process

details

is

concerned,

with

the

a

standard

to

the

I/O

and windows,

great

are

capable

On

the

IP

functions,

hardware and

an

I/O

Subsystem

boundary,

the

other.

I1'Ove

data

that

it

device

m:Xiification,

not

be

trained

which

and

characteristics

it

co-operating

432

the

Attached

controller

the

provided

flexibility

IP

functions,

of

relieving

other

to

AP' s

by

a

in

hand,

relatively

software

device

interface

and 432

rut

As

far

not

also

as

between memory

is

connected

tasks

needs

may

and

in

an

be

that

the

I/O

of

"performs"

process;

I/O

by

interprocess

1-14

Page 24

_

Peripheral

Input

---

Sub8

8tem_l_

Y

......

~.

Peripheral

Subsystem

Interface

<

KEY

--lI-1

0+-

Port

Object>

I

I

CONCEPTS

System

432

(1)

~.~-----output

-.

~

____

Action

Data

Location

_____

&.S.I/0

~~~~~!in9

::::;n9

'DeViCe

J~--"··~_B_u_~_~_e_r_~··IIf-----1·"O""4:l------I"·1(M~~~:~!)I""-----I··O

C_o_p.Y

spac~

Device

Controller/

Notes:

__

D_a_ta

Task

Figure

____

(P.S.

Message

1

.... 1 ___

C_O_p_Y_D_a_t_a

Memory

I

~1

___________

(2)

I I

(1)

Only

(2)

Supporting

may

be AP, a

DMA

May

controller.

also

(3)

1-6

I

object

processor

include a DMA

I/O

Data

0 0

__

....

11

Copy

Re f erence

~1

______________

I_p

__

C_o_n_t_ro_l_le_r

AP

+

IP

(3)

reference

separate

is

is

processor,

FICM

moved

defined

controller.

Surnnary

4_3_2_S~y_s_t_em_._M_e_rn_D_r_Y

______________

to

and from

by

application;

may

II

~1

I

include

Copy

____________

~1

____

G_D_p

... I ____

port.

a

Re

fer

ence

__

p_r_o_c_e_s_s

GD_P

____

___

I

.J

~

--'

1-15

Page 25

iAPx 432

I/O

EXAMPLE

To

illustrate

this

output

one

the

section

might

of

many

example does

implementation,

to

and from a number

In

this

example,

implemented

multitasking

cornnunicate

432

interprocess

the

OS

are

operator.

mailboxes

or

messages

Interface

the

operation

provides

be implemented. Of

possible

not

with

of

all

Peripheral

as a collection

operating

with

one

another

corrmunication

messages,

Messages

are

queue

waiting

are

structures

for

moves a message from a

fran

not,

a message

to

and

a

mailbox

the

task

432

ports

RECEIVE

to

is

to

the

and

operators.

the

queued

mailbox.

TRANSMIT

Processor

of

a

simple

awroaches

show

the

Peripheral

devices

of

system.

in

mailboxes,

arbitrary

tasks.

task

to a mailbox

issuing

at

the

In

and

Architecture

the

432

I/O

Reference

model more

example which shows

course,

that

all

the

might

the

be

detail

Subsystem

example

taken.

supporting

concurrently.

Subsystem

tasks

This

a

fashion

OS

facility.

a

TRANSMIT

data

that

hold

When

task

mailbox

other

ACCEPT

running

if

words,

software

under

is

assumed

that

The mechanisms

operator

structures

tasks

executed

and

waiting

by

ACCEPT

a message

until

another

mailboxes

are

analogous

Manual

specifically,

how

line

describes

Furthermore,

of

a

is

assumed

the

control

to

allow

is

analogous

provided

and

an

in

memory, and

for

a

task,

moves a message

is

available;

task

are

to

the

printer

only

typical

transfers

to

be

of

a

tasks

to

to

the

by

ACCEPT

messages

TRANSMIT

if

TRANSMITs

analogous

432

SEND

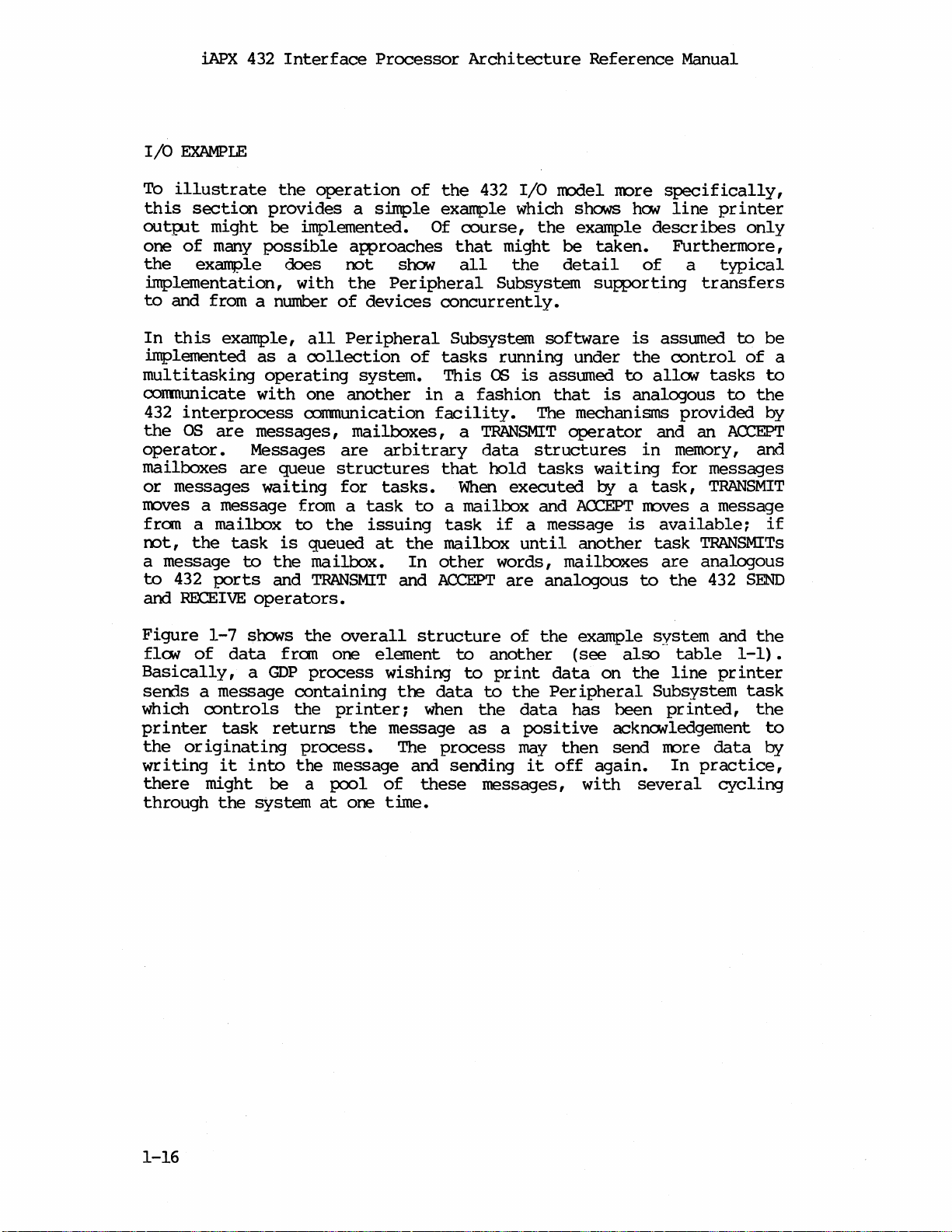

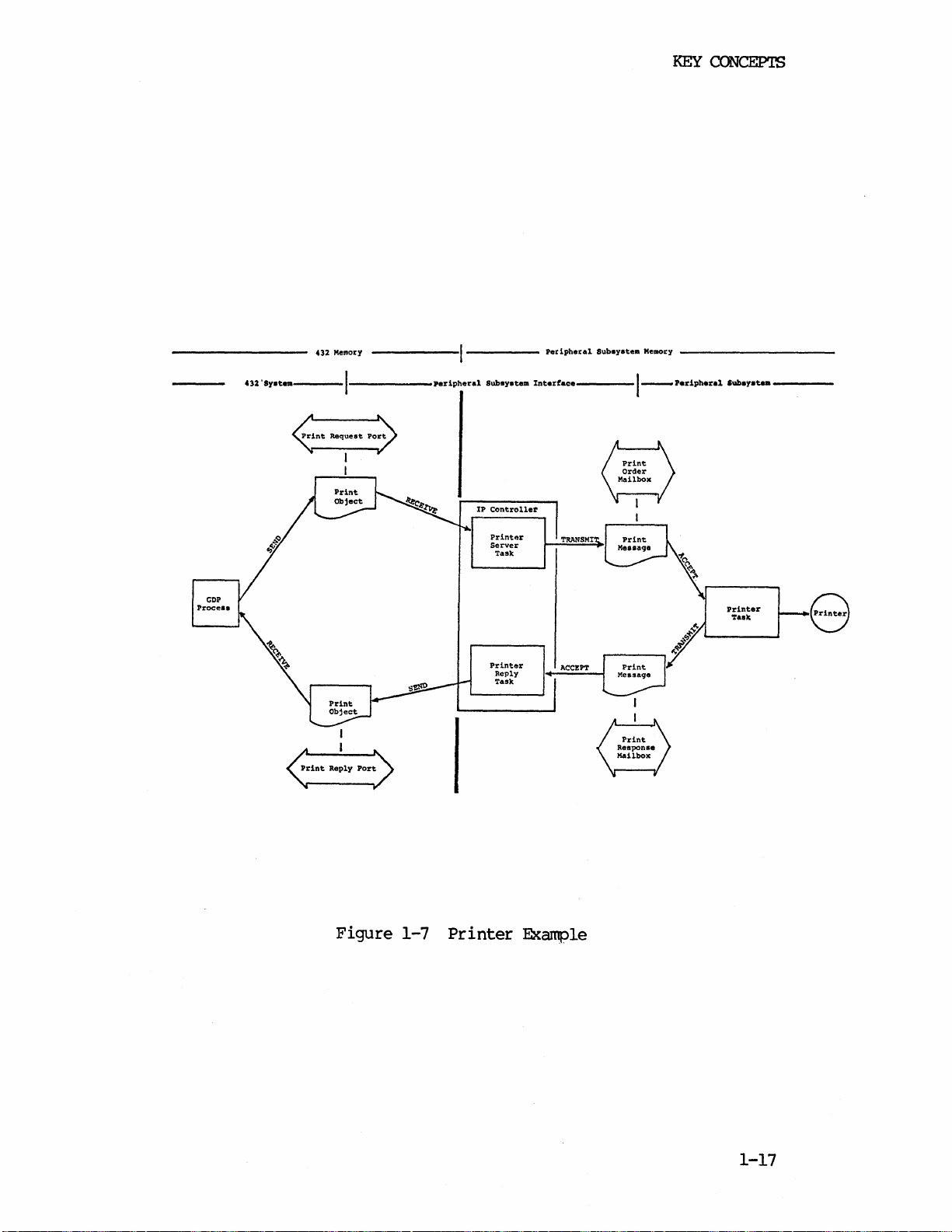

Figure

flON

1-7

of

Basically,

sends

which

a message

controls

printer

the

originating

writing

there

might

through

data

task

it

the

shows

fran

a

GOP

returns

into

be

system

the

overall

one

process

containing

the

printer;

the

process.

the

message and

a

pool

at

one

structure

element

wishing

the

when

message

The

of

these

tbne.

to

to

data

to

the

as

process

sending

messages,

of

the

another

pr

int

the

data

a

positive

may

it

example

(see

data

also

on

Peripheral

has

been

acknowledgement

then

off

send more

again.

with

system

table

the

line

Subsystem

printed,

In

several

and

the

1-1).

pr

inter

task

the

data

practice,

cycling

to

by

1-16

Page 26

KEY

CONCEPTS

CDP

Proeeaa

432

'Syat_----

432

Memory

---

____

.eripheral

Subayatelll

Peripheral

Intertace-----I_

subayatem

Memory

.eripheral

.ubayaUIII

'rinter

Task

____

_

8

Figure

1-7

Printer

EKarnple

1-17

Page 27

iAPX

432

Interface

Processor

Architecture

Reference Manual

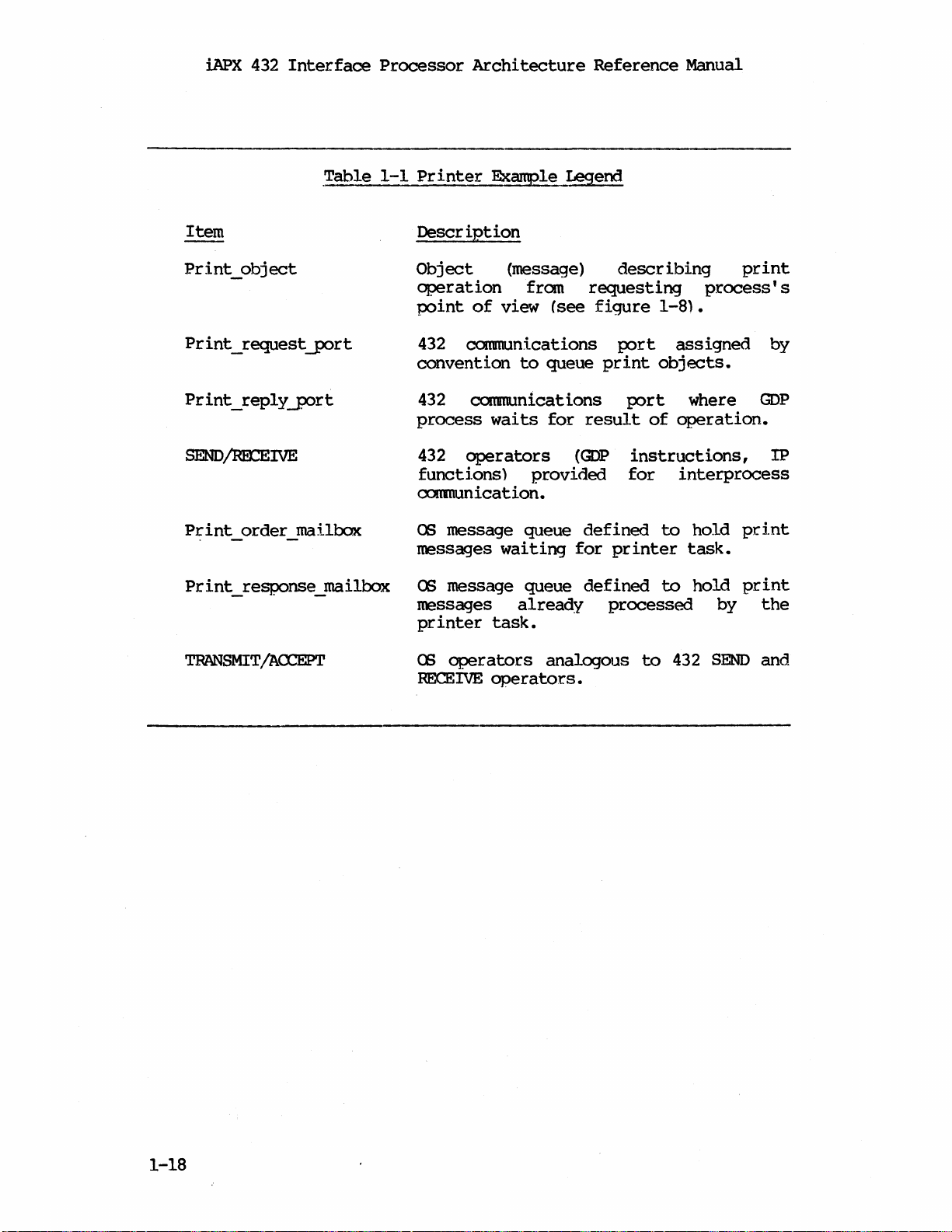

.Table

1-1

Item

SEND,/R:ErnIVE

P:t;int order_mailbaK

Print_response_mailbox

Pr

inter

Example Legend

Description

Object (message)

operation

point

432

of

communications

convention

432

communicat

process

432

operators

fram

view (see

to

queue

waits

for

requesting

figure

ions

result

(GOP

functi.ons) provided

cxmnunication.

03

message queue

messages

03

message queue

waiting

messages

printer

task.

already

defined

for

defined

descr

ibing

process's

1-8).

port

print

port

assigned by

objects.

where

of

operation.

instructions,

for

printer

interprocess

to

hold

task.

to

hold

processed by

pr

int

GOP

IP

pri.nt

print

the

TRANSMIT/ACCEPT

Cl3

operators

RECEIVE

analogous

operators.

to

432

SEND

and

1-18

Page 28

KEY

<XNCEPTS

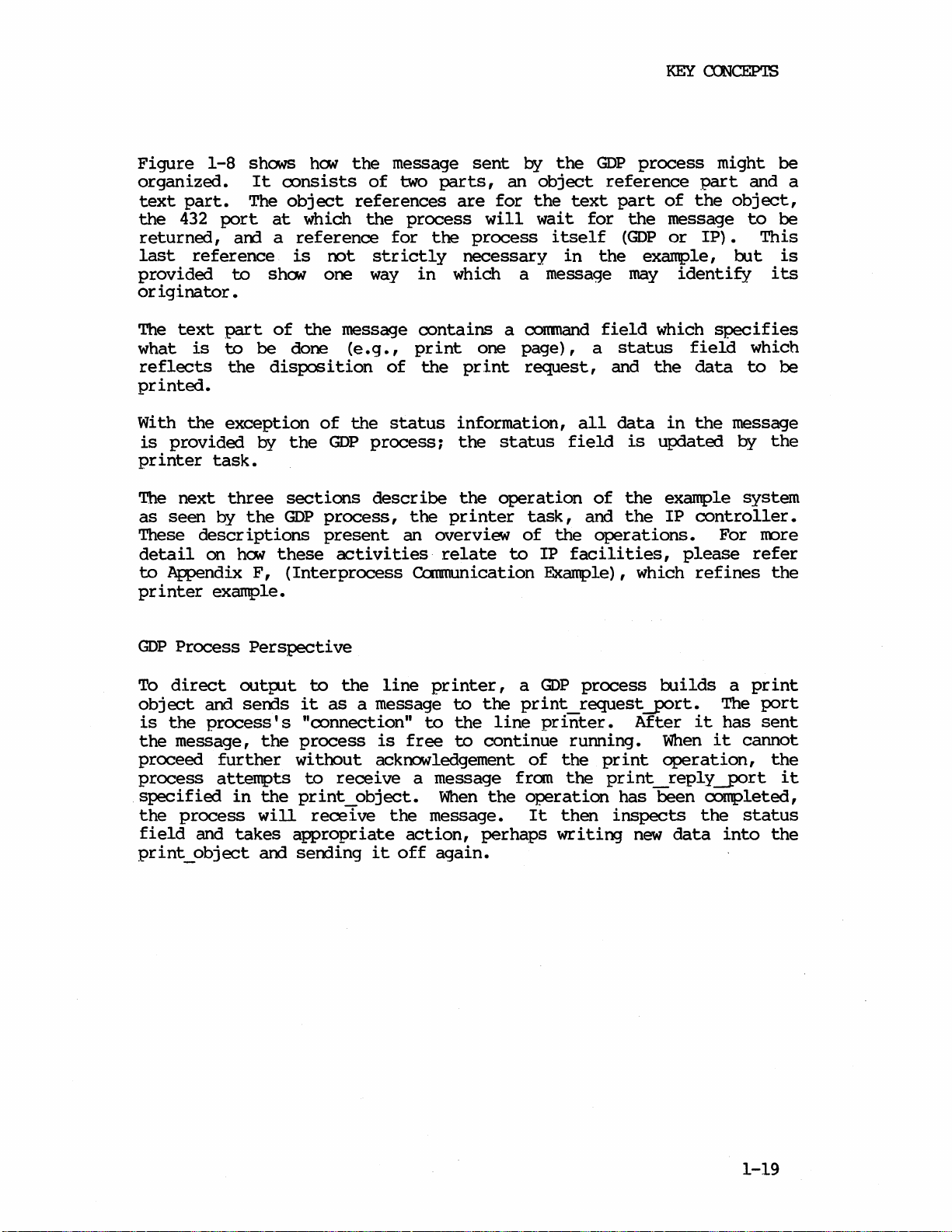

Figure

1-8

organized.

text

part.

the

432

returned,

last

reference

provided

originator.

The

text

what

is

reflects

printed.

With

printer

The

as

These

detail

to

printer

is

provided

next

seen

Appendix

the

task.

by

descriptions

on

example.

shows

It

oonsists

The

object

port

at

arrl a

to

shOil one

part

to

be

the

of

disposition

exception

by

the

three

hOil

sections

the

GOP

these

F,

(Interprocess

hOil

the

which

reference

is

not

the

message

done

of

(e.g.,

the

GOP

process,

present

acti

message

of

two

parts,

references

the

process

for

the

strictly

way

in

oontains a command

print

of

the

status

process i the

descr

ibe

the

an

overview

vi

ties·

relate

Cbmmunication Example), which

sent

are

process

necessary

an

for

will

by

object

the

wait

itself

the

text

for

in

which a message

one

page),

print

request,

information,

status

the

operation

printer

task,

of

to

IP

a

all

field

of

and

the

operations.

facilities,

GOP

process

reference

part

the

(GOP

the

example,

may

field

which

status

and

the

data

is

the

the

part

of

the

message

or

IP).

identify

specifies

field

data

in

the

updated

example

IP

controller.

please

refines

might

and a

object,

to

This

but

which

to

message

by

system

For

nnre

refer

be

be

is

its

be

the

the

GOP

Process

To

direct

object

is

the

proceed

process

and

the

process's

message,

further

attempts

specified

the

process

field

and

print_object

Perspective

outp.1t

serrls

it

"oonnection"

the

process

without

to

in

the

print_object.

will

takes

appropriate

and

serrling

to

the

as

a message

receive

receive

line

is

printer,

to

free

to

the

the

to

continue

line

acknowledgement

a message

it

the

action,

off

When

message.

again.

the

perhaps

a

GOP

process

builds

print_request..J?Ort.

pr

inter.

running.

of

the

fran

the

operation

It

then

writing

After

When

print

operation,

print_replY'-port

has

been

inspects

new

data

a

print

The

port

it

has

sent

it

cannot

oompleted,

the

status

into

the

it

the

1-19

Page 29

iAPX

432

Interface

Processor

Text~

Architecture

Reference

Manual

CI

Object

Print

References".,.;;

Text

Figure 1-8

__

Example

Print

Print

Status

Command

Object

Data

1-20

Page 30

KEY

CONCEPTS

Printer

The

printer

pr

inter

by

the

printer

1.

2.

3.

4.

5.

6.

7.

Printer

The

printer

steps:

1.

2.

3.

4.

5.

6.

Server

task

GOP

server

RECEIVE

When

object

Using

Task

server

which

process

loops

a message from

the

selector

the

Perspective

task

is

responsible

into

through

message (a

object

text.

Copy

the

Close

TRANSMIT

the

Repeat from

the

open

windON.

the

printer

message

window.

a message

task.

step

Task (Device Task)

task

ACCEPT

Interpret

Transfer

care

Update

result

TRANSMIT

runs

a message from

the

message; - - -

the

data

of

all

device

the

status

of

the

operation;

the

updated

mailbox;

Repeat from

step

may

the

form

the

print

for

the

selector,

text

with

1.

Perspective

in

an

from

control

field

1.

be

viewed

for

translating

expected

following

the

print_request-POrt.

object)

message

text.

open

from 432

a

endless

the

print

the

memory

reference

loop

order

message

(e.g.,

of

the

pr

int

_message

as

a

"front

by

the

printer

steps:

is

received,

a windoo

to

to

the

repeating

mailbox;

to

the

interrupts);

print

--

to

the

end"

the

message

onto

PS

the

memory

pr

int

the

printer,

message

pr

int

to

the

sent

task.

The

obtain

message

through

text

following

taking

with

the

_response

an

to

Printer

The

printer

task.

1.

1.

2.

3.

4.

5.

Reply Task

reply

I t

runs

ACCEPT

Open a

Perspective

task

in

an

a message from

windON

Formulate a print

object

Close

SEND

through

the

the

print

window.

system.

Repeat from

may

endless

onto

the

object

-

step

1.

be

viewed

loop

the

reply

as

follows:

the

print

print

object

message and

open windON.

to

the

as

a "back end"

response

in

deposit

printer

mailbox.

the

reply

432

it

port

to

the

system.

in

in

printer

the

the

print

432

1-21

Page 31

iAPX

1-5.

SUPPLEMENTARY

The

preceding

is

used

capabilities

exceptional

interconnect

432

Interface

INTERFACE

sections

most

of

which

are

circumstances.

access.

Processor

have

the

typically

ProcESSOR

described

time.

These

Architecture

FACILITIES

the

The

used

are

IP

less

physical

Reference

Interface

provides

frequently,

reference

Manual

Processor

two

additional

often

nnde and

as

only

it

in

PHYSICAL

An

IP

characterized

system.

utilizes

segment.

because

REFERENCE

oormally

When

an

object

There

the

by

an

logical-to-physical

are

damaged).

reference

An

IP

nnde.

which

protection

between

m<rle.

Windows

(rather

selects

data

The

map

than

a segment

establishes

references

This

s~le

traditional

Physical

initialization

into

432 memory. Once

processors

lDgical

mode

reference

In

is

operating

mechanisms

segments and

IP

provides

directly

obj

a window. The

as

l6-bit

base-plus-displacement

computer

to

can

cannot

logical-to-physical

loaded

into

432 memory.

r-DDE

operates

its

IP

running

selector

are

times

objects

address

these

of

onto

ect

structures