Page 1

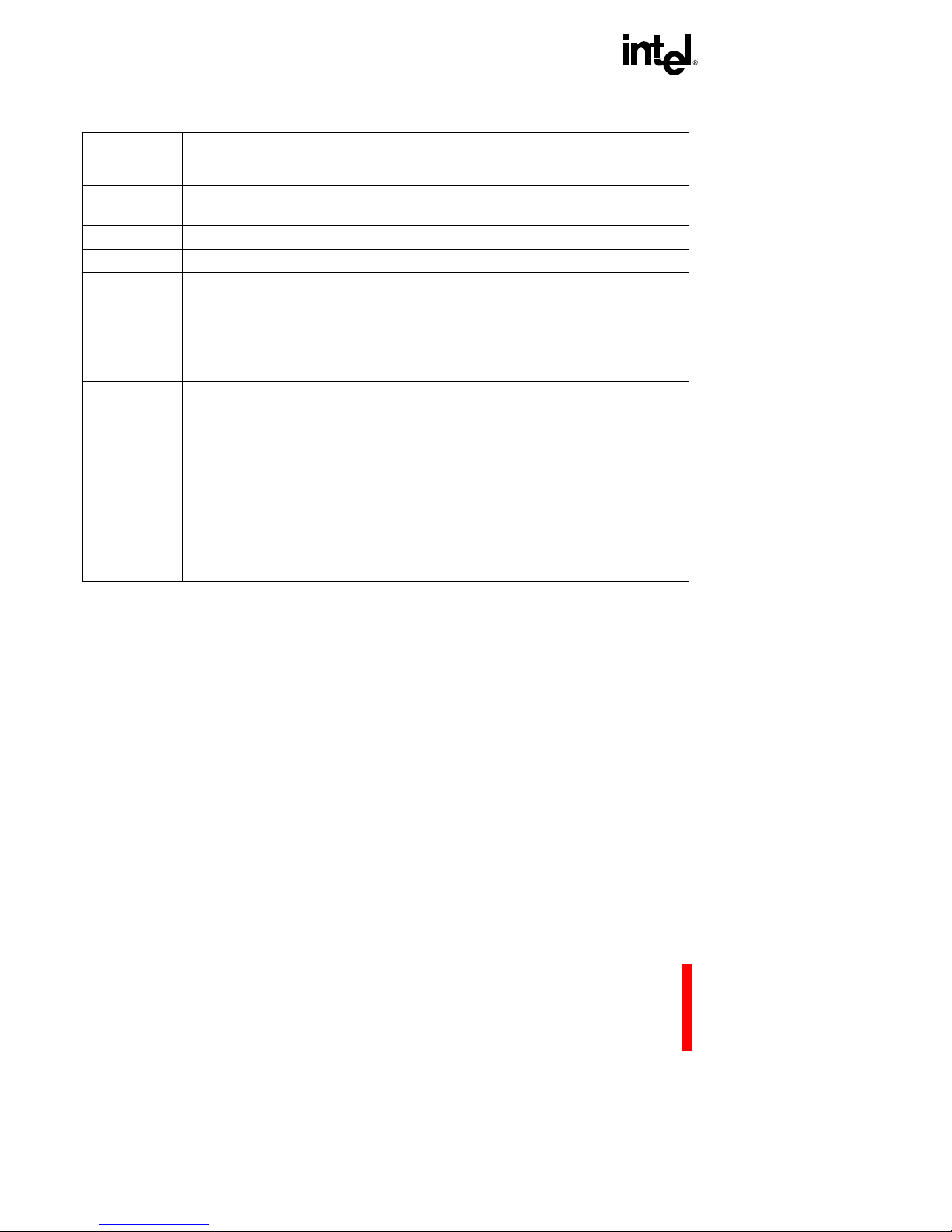

i960® Jx Microprocessor

Developer’s Manual

Release Date: December, 1997

Order Number: 272483-002

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale

and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel

reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future

changes to them.

®

The i960

Jx Processor may contain design defects or errors known as errata which may cause the product to deviate from

published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be

obtained by calling 1-800-548-4725 or by visiting Intel’s website at http://www.intel.com.

Copyright © Intel Corporation, 1997

*Third-party brands and names are the property of their respective owners.

ii May, 19 98 272483 - 0 02

Page 3

iii

i960® Jx Microprocessor

Developer’s Manual

CHAPTER 1

INTRODUCTION

1.1 Product Features...................................... ............ ............ .. ............ .. ............................. 1-4

1.1.1 Instruc t io n C a ch e ....... ... ......... .......... .......... .. .......... .......... ......... .......... .......... .......... 1-4

1.1.2 Data Cache ............................................................................................................. 1-4

1.1.3 On-chip (Internal) Data RAM ................................................................................... 1-4

1.1.4 Local Register Cache .............................................................................................. 1-5

1.1.5 Interru p t C on t ro ller ... .......... ......... .......... .......... ......... ... .......... ......... .......... .......... ..... 1-5

1.1.6 Timer Su pp o r t ...... .......... ......... .......... ... ......... .......... .......... ......... .......... .......... .. ........ 1-6

1.1.7 Memory-Mapped Control Registers (MMR) ............................................................. 1-6

1.1.8 External Bus ............................................................................................................ 1-6

1.1.9 Complete Fault Handl ing and Debug Capabilities .......... ............ ........... ............ ...... 1-7

1.2 ABOUT THIS MANUAL................................................................................................. 1-7

1.3 NOTATION AND TERMINOLOGY................................................................................ 1-8

1.3.1 Reserved and Preserved ........................... ........................ ............ .. ........................ 1-8

1.3.2 Specifying Bit and Signal Values ............................................................................. 1-9

1.3.3 Represe n ting Numb e rs ............. .......... ......... ... ......... .......... .......... .......... ......... ........ 1-9

1.3.4 Regist e r N am es ..... ... .......... ......... .......... .......... ......... .......... ... ......... .......... .......... ..... 1-9

1.4 Related Documents..................................................................................................... 1-10

CHAPTER 2

DATA TYPES AND MEMORY ADDRESSING MODES

2.1 DATA TYPES............. .. ............... .. ............... .. ............... ............... .. ............... ............... . 2-1

2.1.1 Integers ................................................................................................................... 2-2

2.1.2 Ordinals ................................................................................................................... 2-2

2.1.3 Bits and Bit Fields .................................................................................................... 2-3

2.1.4 Triple- and Quad- Wo rds ......................... .. .................................. ........... ............ .. .... 2-3

2.1.5 Register Data Alignment ......................................................................................... 2-3

2.1.6 Literal s ............ ............ .......... ............ ............ .......... ............ ............ ............. ........ .... 2-4

2.2 BIT AND BYTE ORDERING IN MEMORY.................................................................... 2-4

2.2.1 Bit Ordering ...... ... .......... ......... .......... .......... .......... .. .......... ......... .......... .......... .......... 2-4

2.2.2 Byte Ordering .......................................................................................................... 2-4

2.3 MEMORY ADDRESSING MODES............................................................................... 2-6

2.3.1 Absolute .................................................................................................................. 2-7

2.3.2 Regist e r In d ire c t .. .. .......... .......... .......... .. .......... ......... .......... .......... .......... ......... ... ..... 2-7

2.3.3 Index with Displacement ......................................................................................... 2-8

2.3.4 IP with Displaceme nt ..... .. ... ......... .......... .......... ......... .......... ... ......... .......... .......... ..... 2-8

2.3.5 Addressing Mode Examples .................................................................................... 2-8

Page 4

iv

CHAPTER 3

PROGRAMMING ENVIRONMENT

3.1 OVERVIEW ................................................................................................................... 3-1

3.2 REGISTERS AND LITERALS AS INSTRUCTION OPERANDS.................. ................. 3-1

3.2.1 Global Regist ers .................... .. ............ ............ ........... ............ .. ............ ................... 3-2

3.2.2 Local Reg isters . ... ......... .......... .......... .......... ......... .......... .. .......... .......... .......... ......... . 3-3

3.2.3 Register Scoreboarding ........................................................................................... 3-4

3.2.4 Literals ..................................................................................................................... 3-4

3.2.5 Register and Literal Addressing and Alignment ....................................................... 3-4

3.3 MEMORY-MAPPED CONTROL REGISTERS.............................................................. 3-6

3.3.1 Memory-Mapped Registers (MMR) ......................................................................... 3-6

3.3.1.1 Restrictions on Instructions that Access Memory-Mapped Registers .............. 3-6

3.3.1 .2 Access F a ul ts . .. ... .......... ......... .......... .......... .......... .. .......... ......... .......... .......... ... 3-7

3.4 ARCHITECTURALLY DEFINED DATA STRUCTURES.............. .. .. ............... .. .......... 3-11

3.5 MEMORY ADDRESS SPACE..................................................................................... 3-13

3.5.1 Memory Requireme nts ...................... .. ............ ........... ............ ............ .. ............ ..... 3-14

3.5.2 Data and Instruction Alignment in the Address Space .......................................... 3-15

3.5.3 Byte, Word and Bit Addr essing ........................... .. ............ ........... ............ .............. 3-15

3.5.4 Internal Data RAM ................................................................................................. 3-16

3.5.5 Instruc t io n C a ch e ........ .......... ......... ... .......... ......... .......... .......... ......... .......... ... ........ 3-16

3.5.6 Data Cache ............................................................................................................ 3-17

3.6 LOCAL REGISTER CACHE........................................................................................ 3-17

3.7 PROCESSOR-STATE REGISTERS ........................................................................... 3-17

3.7.1 Instruction Pointer (IP) Register ............................................................................ 3-17

3.7.2 Arithmetic Controls (AC) Register .......................................................................... 3-18

3.7.2.1 Initializing and Modifying the AC Register ...................................................... 3-18

3.7.2.2 Condition Code (AC. cc) ....................................... ............ ............ .. ............ ..... 3-19

3.7.3 Process Controls (PC) Register ............................................................................. 3-21

3.7.3.1 Initializing and Modifying the PC Register ...................................................... 3-22

3.7.4 Trace Controls (TC) Register ................................................................................. 3-23

3.8 USER-SUPERVISOR PROTECTION MODEL ........................................................... 3-23

3.8.1 Supervisor Mode Resources ........ ............ ............ ............................................. .... 3-23

3.8.2 Using the User-Supervisor Protection M odel ................................... ............ .......... 3-24

CHAPTER 4

CACHE AND ON-CHIP DATA RAM

4.1 INTERNAL DATA RAM ................................................................................................. 4-1

4.2 LOCAL REGISTER CACHE.......................................................................................... 4-2

4.3 BIG ENDIAN ACCESSES TO INTERNAL RAM AND DATA CACHE........................... 4-4

4.4 INSTRUCTION CACHE ................................................................................................ 4-4

4.4.1 Enabling and Disabling the Instruction Cache ......................................................... 4-4

4.4.2 Operation While the Instruction Cache Is Disabled ................................................. 4-5

4.4.3 Loading and Locking Instructions in the Instruction Cache ..................................... 4-5

Page 5

v

4.4.4 Instruc t io n C a ch e Vi s ib ility .......... ... ......... .......... .......... .......... ......... .......... ... ......... ... 4- 5

4.4.5 Instruc t io n C a ch e C ohe re n cy ......... ......... .......... .......... .......... .. .......... .......... ......... ... 4-5

4.5 DATA CACHE............................................................................................................... 4-6

4.5.1 Enabling and Disabling the Data Cache .................................................................. 4-6

4.5.2 Multi-Word Data Accesses that Partially Hit the Data Cache .................................. 4-7

4.5.3 Data Cache Fill Policy ............................................................................................. 4-8

4.5.4 Data Cache Write Policy ......................................................................................... 4-8

4.5.5 Data Cache Coherency and Non-Cacheable Accesses ......... ............ .. ............ ....... 4-9

4.5.6 External I/O and Bus Masters and Cache Coherency ........................................... 4-10

4.5.7 Data Cache Visibility ............................................................................................. 4-10

CHAPTER 5

INSTRUCTION SET OVERVIEW

5.1 INSTRUCTION FORMATS........................................................................................... 5-1

5.1.1 Assembly Langua ge Format .......................... .. ............ .. ............ ........... ............ ...... 5-1

5.1.2 Instruction Encoding Formats .................................................................................. 5-2

5.1.3 Instruction Operands ............................................................................................... 5-3

5.2 INSTRUCTION GROUPS.. .. .. ....................................................................................... 5-4

5.2.1 Data Movement ....................................................................................................... 5-5

5.2.1.1 Load and Store Instructions ................. ............ .. ................................. ............ . 5-5

5.2.1 .2 Move ......... .......... .......... .......... ......... .......... .......... .. .......... .......... .......... ......... ... 5-6

5.2.1.3 Load Address ................................................................................................... 5-6

5.2.2 Select Condit ional ............... .. ............ ............ ............................................. ............ . 5-6

5.2.3 Arithmetic ................................................................................................................ 5-7

5.2.3.1 Add, Subtract, Mu lt iply, Divide, Conditio nal Add, Conditional Subtract ........... . 5-8

5.2.3.2 Remainder and Modulo ........................ .. ............ ........... ............ ............ .. ......... 5-8

5.2.3.3 Shift, Rotate and Extended Shift ......................... ............ .. ............ ................... 5-9

5.2.3.4 Extended Arith me ti c ............................................................................ ........... 5-10

5.2.4 Logical .................................................................................................................. . 5-10

5.2.5 Bit, Bit Field and Byte Operations ......................................................................... 5-11

5.2.5 .1 Bit Opera tions .......... .......... .......... ......... .......... .. .......... .......... .......... ......... ...... 5-11

5.2.5.2 Bit Field Operations ........................................................................................ 5-11

5.2.5.3 Byte Operations ............................................................................................. 5-11

5.2.6 Compar ison ...... ............... ............... ...................... .............. ............ ............... ........ 5-1 2

5.2.6.1 Compare and Conditional Compare ............. .. ............ ............ .. ...................... 5-12

5.2.6.2 Compare and Increment or Decrement .......................................................... 5-13

5.2.6.3 Test Condition Codes ..................................................................................... 5-13

5.2.7 Branch ................................................................................................................... 5-14

5.2.7.1 Unconditional Branch ................. ........................ ........... ............ ............ .. ....... 5-14

5.2.7.2 Conditional Branch ............ .. ............ ............ ........................ ........... ............ .. .. 5-15

5.2.7.3 Compare and Branch ...................... .. .................................. ........... ............ .. .. 5-15

5.2.8 Call/R et u rn ....... ... .......... ......... .......... .......... .. .......... .......... ......... .......... .......... ........ 5-1 6

5.2.9 Faults .... ..... ... .... ..... ... ..... ..... .... ... ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... ..... .. .... .. 5-17

5.2.1 0 Debug . ....... .......... .......... ......... ........ ......... .......... ....... .......... .......... ....... .......... ....... . 5-18

5.2.11 Atomic Instructions ................................................................................................ 5-18

Page 6

vi

5.2.12 Processor Management ........................................................................................ 5-19

5.3 PERFORMANCE OPTIMIZATION.............................................................................. 5-20

5.3.1 Instruc t io n O p ti m iz a tio ns ........ .......... .......... ......... .......... .......... .. .......... .......... ........ 5-20

5.3.1.1 Load / Store Execution M odel ..................... ............ .. ................................. .... 5-20

5.3.1.2 Compare Operations ...................................................................................... 5-20

5.3.1.3 Microcoded Instructions ................................................................................. 5-21

5.3.1 .4 Multip ly -D iv id e U ni t Instructions ..... .. .......... .......... ......... ... ......... .......... .......... . 5-21

5.3.1.5 Multi-Cycle Register Operations ..................................................................... 5-21

5.3.1 .6 Simple C on t ro l T ra n sf er ............ .......... ......... ... ......... .......... .......... .......... ........ 5-22

5.3.1.7 Memory Instructions ....................................................................................... 5-22

5.3.1.8 Unaligned Memory Accesses ......................................................................... 5-23

5.3.2 Miscellaneous Optimizations ................................................................................. 5-23

5.3.2.1 Masking of Integer Overflow ........................................................................... 5-23

5.3.2.2 Avoid Using PFP, SP, R3 As Destinati ons for MDU Instructions ................... 5-23

5.3.2.3 Use Global Regist ers (g0 - g14) As Destinations for MDU Instructions ......... 5-23

5.3.2.4 Execute in Imprecise Fault Mode ................................................................... 5-24

CHAPTER 6

INSTRUCTION SET REFERENCE

6.1 N OTATION.................................................................................................................... 6-1

6.1.1 Alphabetic Reference .............................................................................................. 6-2

6.1.2 Mnemonic ................................................................................................................ 6-2

6.1.3 Format ..................................................................................................................... 6-2

6.1.4 Descri ption ... ... ..... .... ... ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... ... ..... ..... 6-3

6.1.5 Action .... ..... ..... .. ..... ..... .. ..... ..... ... .... ..... ..... ... .... ..... ... ..... .... ... ..... ..... .... ... ..... ..... .. .... .... 6-3

6.1.6 Faults ......... .......... ....... .......... ......... ........ ......... .......... .......... ....... .......... .......... ...... .... 6-5

6.1.7 Exampl e ....... ........ .... ........ ....... ..... ....... ........ .... ........ ....... ....... ..... ....... ........ ..... ....... ... 6-5

6.1.8 Opcode and Instruction Format .......................... .. ............ ........... ............ .. ............ .. 6-6

6.1.9 See Also .... .. .......... .......... .......... ......... ... ......... .......... .......... .......... ......... .......... ....... . 6-6

6.1.10 Side Effects ............................................................................................................. 6-6

6.1.11 Notes ....................................................................................................................... 6-6

6.2 INSTRUCTIONS............................................................................................................ 6-6

6.2.1 ADD<cc> ................................................................................................................. 6-7

6.2.2 addc . .......... .......... ....... .......... ......... ........ ......... .......... .......... ....... .......... .......... ...... .. 6-10

6.2.3 addi, addo ................. ................................. ............ .. ............ ............ .. .................... 6-11

6.2.4 alterbi t ........ ....... .......... .......... ......... ........ ......... .......... ....... .......... .......... ....... ........ ... 6-12

6.2.5 and, andnot ............................................................................................................ 6-13

6.2.6 atadd ... ....... ....... ..... ....... ........ ....... ..... ....... ....... ..... ........ ....... ..... ....... ....... ........ ..... ... 6-14

6.2.7 atmod .. .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... ... .... ..... ..... ... .... ..... ... ..... .... ... ..... ..... ..... .. . 6-15

6.2.8 b, bx ....................................................................................................................... 6-16

6.2.9 bal, balx ................................................................................................................. 6-17

6.2.1 0 bbc, bbs ....... ... ......... .......... ... ......... .......... .......... .......... ......... .......... .. .......... ........... 6-19

6.2.11 BRANCH<cc> ........................................................................................................ 6-21

6.2.12 bswap .................................................................................................................... 6-23

6.2.13 call ........................................................................................................................ . 6-24

Page 7

vii

6.2.14 calls ....................................................................................................................... 6-25

6.2.15 callx ....................................................................................................................... 6-27

6.2.1 6 chkbit .... ............... ............... ............ .............. ............... ...................... .................... 6-29

6.2.1 7 clrbit . ........ ......... .......... .......... ....... .......... .......... ....... .......... ......... ........ .......... .......... 6-30

6.2.18 cmpdeci, cmpdeco ................................................................................................ 6-31

6.2.19 cmpinci, cmpinco ................................................................................................... 6-32

6.2.20 COMPARE ............................................................................................................ 6-33

6.2.21 COMPARE AND BRANCH<cc> ................................... .. ............... .. ............... .. ..... 6-35

6.2.22 concmpi, concmpo ................................................................................................ 6-38

6.2.2 3 dcctl ...... ............... ............ ............... .............. ...................... ...................... ............. 6-40

6.2.24 divi, divo ................................................................................................................ 6-47

6.2.2 5 ediv ....... ............ .......... ............ ............. ......... ............ ............. ............ .......... .......... 6-48

6.2.2 6 em ul . ..... ... ..... .... ... ..... ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... ... .... ... ... 6-49

6.2.27 eshro ..................................................................................................................... 6-50

6.2.2 8 ext rac t ... ... ..... .... ... ..... ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... ... .... ... ... 6-51

6.2.29 FAULT<cc> ........................................................................................................... 6-52

6.2.3 0 flus hre g . ..... ... .... ..... ... ..... ..... .... ... ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... .. .... .. 6-54

6.2.31 fmark ..................................................................................................................... 6-55

6.2.3 2 hal t . ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... ... .... ..... ..... ... .... ..... ... ..... ..... .. ... ..... 6-56

6.2.33 icctl ........................................................................................................................ 6-58

6.2.3 4 intctl ...... ............ ............... ............... ...................... .............. ............ ............... ........ 6-66

6.2.35 intdis ...................................................................................................................... 6-68

6.2.3 6 inte n . ... ..... ..... .... ... ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... ... ..... .... .. .... 6-69

6.2.3 7 LO AD .. .. ..... ..... .. ..... ..... ... ..... .... ..... ... ..... .... ... ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... ..... .. . 6-70

6.2.3 8 lda .... ... ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... ... .... ..... ..... ... .... ..... ... ..... ..... .... . ..... 6-73

6.2.39 mark ...................................................................................................................... 6-74

6.2.4 0 mo dac ... ..... ..... .. ..... ..... ... ..... .... ..... ... ..... .... ... ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... . 6-75

6.2.4 1 mo di . ..... ... ..... .... ... ..... ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... ..... ..... ... .... ... ... 6-76

6.2.4 2 modify ........ .......... .......... ....... .......... ......... ........ ......... .......... ....... .......... .......... ...... .. 6-77

6.2.4 3 mo dpc ... ..... ..... .. ..... ..... ... ..... .... ..... ... ..... .... ... ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... .. ..... . 6-78

6.2.4 4 mo dtc .... ..... ... .... ..... ... ..... ..... .... ... ..... ..... .. ..... ..... .. ..... ..... ..... .. ..... ..... .. ..... ..... ..... .. .... .. 6-80

6.2.4 5 MOVE . .......... ....... .......... ......... .......... ....... .......... .......... ....... .......... .......... ....... ........ 6-81

6.2.46 muli, mulo .............................................................................................................. 6-84

6.2.47 nand ...................................................................................................................... 6-85

6.2.48 nor ......................................................................................................................... 6-86

6.2.4 9 not, not and ....... .......... .......... .......... ......... .......... .......... .......... .. .......... .......... ......... . 6-87

6.2.5 0 notb it ........ ..... ....... ....... ........ .... ........ ....... ..... ....... ....... ........ ..... ....... ....... ..... ....... ...... 6-88

6.2.51 notor ...................................................................................................................... 6-89

6.2.52 or, ornot ................................................................................................................. 6-90

6.2.53 remi, remo ............................................................................................................. 6-91

6.2.54 ret .......................................................................................................................... 6-92

6.2.55 rotate ..................................................................................................................... 6-94

6.2.56 scanbit ................................................................................................................... 6-95

6.2.57 scanbyte ................................................................................................................ 6-96

Page 8

viii

6.2.5 8 SEL<cc> . ............... ............... ............ .............. ............... ...................... ............... ... 6-97

6.2.59 setbit ...................................................................................................................... 6-99

6.2.60 SHIFT .................................................................................................................. 6-100

6.2.61 spanbit ................................................................................................................. 6-103

6.2.62 STORE ................................................................................................................ 6-104

6.2.6 3 subc ...... ............... .............. ............ ............... ............... ..................... ................... 6-108

6.2.64 SUB<cc> ............................................................................................................. 6-109

6.2.65 subi, subo ............................................................................................................ 6-112

6.2.66 syncf .................................................................................................................... 6-113

6.2.67 sysctl .................................................................................................................... 6-114

6.2.68 TEST<cc> ............................................................................................................ 6-118

6.2.69 xnor, xor ............................................................................................................... 6-120

CHAPTER 7

PROCEDURE CALLS

7.1 CALL AND RETURN MECHANISM.............................................................................. 7-2

7.1.1 Local Registers and the Procedure Stack ............................................................... 7-2

7.1.2 Local Register and Stack Management ............ .. ............ ............ ............................. 7-4

7.1.2.1 Frame Pointer ................................................................................................... 7-4

7.1.2 .2 Stack Po in te r ....... .. .......... .......... .......... ......... .......... .. .......... .......... .......... ......... . 7-4

7.1.2.3 Considerations When Pushing Data onto the Stack ........................................ 7-4

7.1.2.4 Considerati ons When Popping Data off the Stack .............. ............ ........... ...... 7-5

7.1.2.5 Previous Frame Pointer .................................................................................... 7-5

7.1.2.6 Return Type Field ............................................................................................. 7-5

7.1.2 .7 Return Instruction Poin te r ..... .. .......... ... ......... .......... .......... ......... .......... .......... .. . 7-5

7.1.3 Call and Return Action ............................................................................................. 7-5

7.1.3 .1 Call Oper a tio n ....... .......... .......... .......... ......... .......... .. .......... .......... .......... ......... . 7-6

7.1.3 .2 Return O pe r a tio n . .......... ......... .......... .......... .......... .. .......... ......... .......... .......... ... 7-7

7.1.4 Caching Local Register Sets ................................................................................... 7-7

7.1.4.1 Reserving Local Register Sets for High Priority Interrupts ............................... 7-8

7.1.5 Mapping Local Registers to the Procedure Stack .................................................. 7-11

7.2 MODIFYING THE PFP REGISTER............................................................................. 7-11

7.3 PARAMETER PASSING. .. ............... .. ............... ............... ............................... .. .......... 7-12

7.4 LOCAL CALLS ............................................................................................................ 7-14

7.5 SYSTEM CALLS ........ .. .. ............... ............... .. ............... .. ............... .. ............... .. .......... 7-15

7.5.1 System Procedure Table ....................................................................................... 7-15

7.5.1 .1 Proce dure Entrie s ..... .. ... ......... .......... .......... .......... ......... .......... .. .......... .......... . 7-17

7.5.1.2 Supervisor Stack Pointer ................................................................................ 7-17

7.5.1.3 Trace Control Bit ............................................................................................ 7-17

7.5.2 System Call to a Local Procedure ......................................................................... 7-18

7.5.3 System Call to a Supervisor Procedure ................................................................. 7-18

7.6 USER AND SUPERVISOR STACKS .......................................................................... 7-19

7.7 INTERRUPT AND FAULT CALLS............................................................................... 7-19

7.8 RETURNS................................................................................................................... 7-20

Page 9

ix

7.9 BRANCH-AND-LINK................................................................................................... 7-21

CHAPTER 8

FAULTS

8.1 F A ULT H A N DLING OVE R V IE W.......... .. ... ......... .......... .......... ......... .......... .......... .. ........ 8-1

8.2 FAULT TYPES.............................................................................................................. 8-3

8.3 F A ULT T A B LE ..... .......... .......... ......... .......... .. .......... .......... .......... ......... .......... .......... ..... 8-4

8.4 STACK USED IN FAULT HANDLING........................................................................... 8-6

8.5 F A ULT R E C OR D ........ .......... .......... .. .......... .......... ......... .......... .......... .......... .. .......... ..... 8-6

8.5.1 Fault Record Description ......................................................................................... 8-7

8.5.2 Fault Record Location ............................................................................................. 8-8

8.6 MULTIPLE AND PARALLEL FAULTS.......................................................................... 8-9

8.6.1 Multiple Non-Trace Faults on the Same Instruction ................................................ 8-9

8.6.2 Multiple Trace Fault Conditions on the Same Instruction ........................................ 8-9

8.6.3 Multiple Trace and Non-Trace Fault Conditio ns on the Same Instruction ........ ....... 8-9

8.6.4 Parallel Faults .......................................................................................................... 8-9

8.6.4.1 Faults on Multiple Instructions Executed in Parallel ....................................... 8-10

8.6.4.2 Fault Record for Parallel Faults ...................................................................... 8-11

8.6.5 Overri de F aults .... .. ... .......... ......... .......... .......... ......... ... .......... ......... .......... .......... ... 8-11

8.6.6 System Error ......................................................................................................... 8-12

8.7 FAULT HANDLING PROCEDURES ........................................................................... 8-12

8.7.1 Possible Fault Handling Procedure Actions .......................................................... 8-13

8.7.2 Program Resumption Following a Fault ................................................................ 8-13

8.7.2.1 Faults Happening Before Instruction Execution ............................................. 8-13

8.7.2.2 Faults Happening During Instruction Execution ............ ............ .. ............ .. ..... 8-14

8.7.2.3 Faults Happening After Instruction Execution ....... .. ............ ........................... 8-14

8.7.3 Return Instruction Poin te r (R I P ) .. ... .. .......... .......... ......... .......... .......... .. .......... ........ 8-14

8.7.4 Returning to th e Point in the Program Where the Fault Occurred ........ ................. 8-15

8.7.5 Returning to a Point in the Program Other Than Where the Fault Occ urred ......... 8-15

8.7.6 Fault Controls ........................................................................................................ 8-15

8.8 F A ULT H A N DLING ACT IO N........... .......... .. .......... ......... .......... .......... .......... ......... ...... 8-16

8.8.1 Local Fault Call ...................................................................................................... 8-17

8.8.2 System-Local Fault Call ........................................................................................ 8-17

8.8.3 System-Supervisor Fault Call ................................................................................ 8-17

8.8.4 Faults and Inte rrupts ............... ........... ............ ........................ ............ .. ............ ..... 8-18

8.9 PRECISE AND IMPRECISE FAULTS ........................................................................ 8-19

8.9.1 Precise Faults ........................................................................................................ 8-19

8.9.2 Imprecise Faults .................................................................................................... 8-19

8.9.3 Asynchronous Faults ............................................................................................. 8-19

8.9.4 No Imprecise Faults (AC.nif) Bit ............................................................................ 8-20

8.9.5 Controlling Fault Precision .................................................................................... 8-20

8.10 FAULT R E F E RE N C E............ .......... .......... ......... .......... .. .......... .......... .......... ......... ...... 8-21

8.10.1 ARITHMETIC Faults .............................................................................................. 8-22

8.10. 2 CONST R A INT Fa u lts ......... ......... .......... .......... ......... .......... .......... .. .......... .......... ... 8-23

Page 10

x

8.10. 3 OPERA T IO N F au lts . ... .......... ......... .......... ... ......... .......... .......... ......... .......... .......... . 8-24

8.10. 4 OVERR ID E F au lts ........ .......... .......... .......... ......... .......... .. .......... .......... .......... ........ 8-26

8.10. 5 PARAL LE L Fau lts .. .......... .......... .. .......... ......... .......... .......... .......... ......... ... .......... ... 8-2 7

8.10. 6 PROTE C T ION F au lts ........ .......... .......... ......... .......... .......... .. .......... .......... .......... ... 8-2 8

8.10.7 TRACE Faults ........................................................................................................ 8-29

8.10.8 TYPE Faults ........... ......................... .. .............. ............. .............. ............. .............. 8-32

CHAPTER 9

TRACING AND DEBUGGING

9.1 TRACE CONTROLS ..................................................................................................... 9-1

9.1.1 Trace Controls (TC) Register ................................................................................... 9-2

9.1.2 PC Trace Enable Bit and Trace- Fault-Pending Flag ...... ......................... .. .............. 9-3

9.2 TRACE MODES ............................................................................................................ 9-3

9.2.1 Instruc t io n T ra c e .. ......... .......... .......... .. .......... .......... ......... .......... .......... .......... ......... . 9-3

9.2.2 Branc h Tra c e ....... .. .......... .. .......... .......... ......... .......... .......... .......... .. .......... .......... ..... 9-4

9.2.3 Call Trace ......... .......... .......... ......... .......... .......... .. .......... .......... ......... .......... .......... ... 9-4

9.2.4 Return Tr a ce ..... .......... .......... .. .......... .......... ......... .......... .......... ......... ... .......... ......... . 9-4

9.2.5 Prereturn Trace ....................................................................................................... 9-4

9.2.6 Supervisor Trace ..................................................................................................... 9-5

9.2.7 Mark Trace .............................................................................................................. 9-5

9.2.7 .1 Software Break p oi nt s .... .. .......... .......... .. .......... ......... .......... .......... .......... ......... . 9-5

9.2.7.2 Hardware Breakpoints ...................................................................................... 9-5

9.2.7.3 Requesting Mod if ication Rights to Hardware Breakpoint Resources ............... 9-6

9.2.7.4 Breakpoint Control Register ............................................................................. 9-7

9.2.7.5 Data Address Breakpoint (DAB) Registers ....................................................... 9-9

9.2.7.6 Instruction Breakpoint (IPB) Registers ........................................................... 9-10

9.3 GENERATING A TRACE FAULT................................................................................ 9-11

9.4 HANDLING MULTIPLE TRACE EVENTS................... ............................... .. ............... 9-11

9.5 TRACE FAULT HANDLING PROCEDURE ............. .. ............... .. ............... ............... .. 9-12

9.5.1 Tracing and Interrupt Procedures .......................................................................... 9-12

9.5.2 Tracing on Calls and Returns ................................................................................ 9-12

9.5.2.1 Tracing on Explicit Call ................................................................................... 9-13

9.5.2.2 Tracing on Implicit Call ................................................................................... 9-14

9.5.2.3 Tracing on Return from Explicit Call ............................................................... 9-15

9.5.2.4 Tracing on Return from Implicit Call: Fault Case ............................................ 9-15

9.5.2.5 Tracing on Return from Implicit Call: Interrupt Case ...................................... 9-16

CHAPTER 10

TIMERS

10.1 TIMER R E GIS T E R S .. ......... .......... .......... .......... ......... ... ......... .......... .......... .......... ........ 10-2

10.1.1 Timer Mode Registers (TMR0, TMR1) .................................................................. 10-3

10.1.1.1 Bit 0 - Terminal Count Status Bit (TMRx.t c) .............. ......................... .. .......... 10-4

10.1.1.2 Bit 1 - Timer Enable (TMRx.enable) ............................................................... 10-4

10.1.1.3 Bit 2 - Timer Auto Reload Enable (TMRx.reload) ........................................... 10-5

10.1.1.4 B it 3 - Timer Register Supervisor Read/Write Control (TMRx .sup) ................ 10-5

Page 11

xi

10.1.1.5 Bits 4, 5 - Timer Input Clock Select (TMRx.csel1:0) ....................................... 10-6

10.1.2 Timer Count Register (TCR0, TCR1) .................................................................... 10-6

10.1. 3 Timer Re lo a d R e g is te r (T R R 0 , T R R1) ................. ......... .......... .. .......... .......... ........ 10-7

10.2 TIMER O P ER A T IO N........... ......... .......... .......... .......... ......... ... ......... .......... .......... ........ 10-7

10.2. 1 Basic Tim e r O p e ra tion .......... .......... ......... .......... .......... .. .......... .......... .......... ......... . 10-7

10.2.2 Load/Store Access Latency for Timer Registers ................................................... 10-9

10.3 TIMER INTERRUPTS............................................................................................... 10-11

10.4 POWERUP/RESET INITIALIZATION ....................................................................... 10-11

10.5 UNCOMMON TCRX AND TRRX CONDITIONS....................................................... 10-12

10.6 TIMER STATE DIAGRAM......................................................................................... 10-13

CHAPTER 11

INTERRUPTS

11.1 OVERV IE W.......... .. .......... .......... .......... .. .......... .......... ......... .......... .......... .......... .. ........ 11-1

11.1.1 The i960

®

Jx Processor Interrupt Controller .......................................................... 11-2

11.2 SOFTWARE REQUIREMENTS FOR INTERRUPT HANDLING...... .. .. ...................... 11-3

11.3 INTERRUPT PRIORITY................ ............... .. ............... .. ............... .. ............... ............ 11-3

11.4 INTERRUPT TABLE....... .. ............... .. ............... .. ............... ............... .. ............... ......... 11-4

11.4.1 Vector Entries ........................................................................................................ 11-5

11.4. 2 Pending In te rrupts ......... .. .......... .......... ......... .......... .......... .. .......... .......... ......... ...... 11-5

11.4.3 Caching Portions of the Interrupt Table ................................................................. 11-6

11.5 INTERRUPT STACK AND INTERRUPT RECORD.................................................... 11-7

11.6 MANAGING INTERRUPT REQUESTS...................................................................... 11-8

11.6.1 External Interrupts ................................................................................................. 11-8

11.6.2 Non-Mask able Interrupt (NMI

) ........ ............ ............ .......... ............ ............ ............ . 11-8

11.6.3 Timer Interrupts ..................................................................................................... 11-9

11.6. 4 Software Interru p ts ........ .. .......... .......... ......... .......... .. .......... .......... .......... ......... ...... 11-9

11.6.5 Posting Interrupts .................................................................................................. 11-9

11.6.5.1 Posting Software Interrupts via sysctl ............................................................ 11-9

11.6.5.2 Posting Software Interrupts Directly in the Interrupt Table ........................... 11-11

11.6.5.3 Posting External Interrupts ........................................................................... 11-11

11.6.5.4 Posting Hardware Interrupts ........................................................................ 11-11

11.6.6 Resolving Interrupt Priority .................................................................................. 11-11

11.6.7 Sampling Pending Interrupts in the Int errupt Table ......... ............ ............ .. .......... 11-12

11.6.8 Interrupt Controller Modes ................................................................................... 11-14

11.6.8.1 Dedicated Mode ........................................................................................... 11-14

11.6.8.2 Expanded Mode ........................................................................................... 11-15

11.6.8.3 M ixed Mode ............... ............ ....................................................................... 11-17

11.6.9 Saving the Interrupt Mask ................................................................................... 11-17

11.7 EXTERNAL INTERFACE DESCRIPTION ................................................................ 11-18

11.7.1 Pin Descriptions .................................................................................................. 11-18

11.7.2 Interrupt Detection Options ................................................................................. 11-19

11.7.3 Memory- Mapped Control Registers ............... ............................................. ......... 11- 21

11.7.4 Interrupt Control Register (ICON) ........................................................................ 11-22

Page 12

xii

11.7.5 Interrupt Mapping Registers (IMAP0-IMAP2) ...................................................... 11-23

11.7.5.1 Interrupt Mask (IMSK) and Inter rupt Pending (IPND) Registers .... .. ............. 11-25

11.7.5.2 Interrupt Control ler Register Access Require me nts ..... .. ............ ........... ....... 11-27

11.7.5.3 Default and Reset Register Values .............................................................. 11-28

11.8 INTERRUPT OPERATION SEQUENCE........... .. ............... ............... ........................ 11-28

11.8.1 Setting Up the Interrupt Controller ....................................................................... 11-31

11.8.2 Interrupt Service Routines ................................................................................... 11-31

11.8.3 Interrupt Context Switch ...................................................................................... 11-32

11.8.3.1 Servicing an Interrupt from Executing State ................................................. 11-32

11.8.3.2 Servicing an Interrupt from Interrupted State ............................................... 11-33

11.9 OPTIMIZING INTERRUPT PERFORMANCE........................... .. ............... .. ............. 11-33

11.9.1 Interrupt Service Latency ..................................................................................... 11-35

11.9.2 Features to Improve Interrupt Performance ......................................................... 11-35

11.9.2.1 Vector Caching Option ................................................................................. 11-35

11.9.2.2 C aching Interrupt Rout ines and Reserving Register Fra me s ....................... 11-36

11.9.2.3 Caching the Interrupt Stack .......................................................................... 11-36

11.9.3 Base Interrupt Latency ........................................................................................ 11-37

11.9.4 Maximum Interrupt Latency ................................................................................. 11-38

11.9.4.1 Avoiding Certain Destinations for MDU Operations ..................................... 11-42

11.9.4.2 Masking Integer Overflow Faults for syncf ................................................... 11-42

CHAPTER 12

INITIALIZATION AND SYSTEM REQUIREMENTS

12.1 OVERV IE W ..... .. .......... .......... .......... .. .......... ......... .......... .......... .......... ......... ... .......... ... 12-1

12.2 INITIA L IZ A T ION ............ .......... .......... .......... ......... ... .......... ......... .......... .......... .......... ... 12 -2

12.2.1 Reset State Operation ........................................................................................... 12-3

12.2.2 Self Test Function (STEST, FAIL

) ......... ......... .......... .......... .. .......... .......... .......... ... 12- 6

12.2. 2. 1 The S T EST P in ........ .. .......... .......... ......... .......... .......... .......... ......... ... .......... ... 12- 7

12.2.2.2 External Bus Confidence Test ........................................................................ 12-7

12.2.2.3 The Fail Pin (FAIL

) ......................................................................................... 12-7

12.2.2.4 IMI Alignment Check and System Error ......................................................... 12-8

12.2.2.5 FAIL

Code ......... ............. .............. ............. .............. .. ......................... .. .......... 12-8

12.3 Architecturally Reserved Memory Space .................................................................... 12-9

12.3.1 Initial Memory Image (IMI) ................................................................................... 12-10

12.3.1.1 Initialization Boot Record (IBR) .................................................................... 12-13

12.3.1.2 Process Control Block (PRCB) ..................................................................... 12-16

12.3.2 Process PRCB Flow ............................................................................................ 12-18

12.3.2.1 AC Initial Image ............................................................................................ 12-19

12.3.2.2 Fault Configuration Word ............................................................................. 12-19

12.3.2.3 Instruction Cache Configuration Word ......................................................... 12-19

12.3.2.4 Register Cache Configuration Word ............................................................. 12-19

12.3.3 Control Table ....................................................................................................... 12-20

12.4 DEVICE IDENTIFICATION ON RESET..................... ............... .. ............... .. ............. 12-22

12.4.1 Reinit ial izing and Relocating Data St ructures .............................. ............ .. .......... 12-22

12.5 Startup Code Example .............................................................................................. 12-23

Page 13

xiii

12.6 SYSTEM REQUIREMENTS........... ............................... .. ............... .. ............... .......... 12- 34

12.6.1 Input Cloc k (CLKIN) ................ ........... ............ .. ............ ............ .. ......................... 12-34

12.6.2 Power and Ground Requirements (V

CC

, VSS) ..................................................... 12-34

12.6.3 V

CC5

Pin Requirements ....................................................................................... 12-35

12.6.4 Power and Ground Planes ......... .. ............ ........... ............ ............ .. ............ .......... 12-35

12.6.5 Decoupling Capacitors ..... ........................ ........... ............ ............ .. ............ .......... 12-36

12.6.6 I/O Pin Characteristics ......................................................................................... 12-36

12.6.6.1 Output Pins .................................................................................................. 12-37

12.6.6.2 Input Pins ................ .. ............ .............................................. ........... ............ .. 12-37

12.6.7 High Frequency Design Considerations .............. ............ ........................ ............ 12-38

12.6.8 Line Termination .................................................................................................. 12-38

12.6.9 Latchup ................................................................................................................ 12-39

12.6.10 Interference ......................................................................................................... 12-40

CHAPTER 13

MEMORY CONFIGURATION

13.1 Memory Attributes ....................................................................................................... 13-1

13.1.1 Physical Memory Attributes ................................................................................... 13-1

13.1.2 Logical Memory Attributes ..................................................................................... 13-2

13.2 Differences With Previous i960 Processors................................................................ 13-3

13.3 Programming the Physical Memory Attributes (PMCON Registers)........................... 13-4

13.3.1 Bus Width .............................................................................................................. 13-5

13.4 Physical Memory Attributes at Initialization................................................................. 13-5

13.4.1 Bus Control (BCON) Register ................................................................................ 13-6

13.5 Boundary Conditions for Physical Memory Regions................................................... 13-7

13.5.1 Internal Memory Locations .................................................................................... 13-7

13.5.2 Bus Transactions Across Region Boundaries .... ............ ....................................... 13-7

13.5.3 Modifying the PMCON Registers ........................................................................... 13-7

13.6 Programming the Logical Memory Attribute s........... ............ ............ ........... ............ .. .. 13-8

13.6.1 Defining the Effective Range of a Logical Data Template ................................... 13-11

13.6.2 Selecting the Byte Order ..................................................................................... 13-12

13.6.3 Data Caching Enable .......................................................................................... 13-12

13.6.4 Enabling the Logical Memory Template ........... ............ .. ............ ........... ............ .. 13-12

13.6. 5 Init ializati on ..... ....... ..... ........ ....... ..... ....... ....... ........ .... ........ ....... ..... ....... ........ ....... . 13-13

13.6.6 Boundary Conditions for Logical Memory Templates .......................................... 13-13

13.6.6.1 Internal Memory Locations ........................................................................... 13-13

13.6.6.2 O verlapping Logical Dat a T emplate Ranges ......................... .. .................... 13-13

13.6.6.3 A ccesses Across LMT Boundaries ................ .. ............ ............ ........... ......... 13- 14

13.6.7 Modifying the LMT Registers ............................................................................... 13-14

13.6.8 Dynamic Byte Order Changing ............. .. ............ ........................ ........... ............ .. 13-14

CHAPTER 14

EXTERNAL BUS

14.1 OVERV IE W.......... .. .......... .......... .......... .. .......... .......... ......... .......... .......... .......... .. ........ 14-1

Page 14

xiv

14.2 BUS OPERATION....................................................................................................... 14-1

14.2. 1 Basic Bus S ta te s ........ .......... ......... .......... ... ......... .......... .......... ......... .......... .......... . 14-2

14.2.2 Bus Signal Types ................................................................................................... 14-4

14.2.2.1 Clock Signal ................................................................................................... 14-4

14.2.2.2 A ddress/Data Signal Defi nitions ......... ............ ............ .. ............ .. .................... 14-4

14.2.2.3 Control/Status Signal Definitions .................................................................... 14-4

14.2. 3 Bus Acce s se s ........ .. ... .......... ......... .......... .......... .......... ......... ... ......... .......... .......... . 14-6

14.2. 3. 1 Bu s Wid th ......... .......... .......... .......... ......... .......... ... ......... .......... .......... .......... ... 14- 7

14.2. 3. 2 Ba si c B us Acc e sses ........... .. .......... .. .......... .......... ......... .......... .......... .......... .. . 14-9

14.2.3.3 Burst Transactions ....................................................................................... 14-11

14.2.3.4 Wait States ................................................................................................... 14-17

14.2.3.5 Recovery States ........................................................................................... 14-19

14.2.4 Bus and Control Signals During Recovery and Idle States ................................. 14-22

14.2.5 Data Alignment .................................................................................................... 14-22

14.2.6 Byte Orderi ng and Bus Accesses ......... ............ .. ............ ........................ ............. 14-28

14.2.7 Atomic Bus Transactions ..................................................................................... 14-30

14.2.8 Bus Arbitration ..................................................................................................... 14-31

14.2.8.1 HOLD/HOLDA Protocol ................................................................................ 14-32

14.2.8.2 BSTAT Signal ............................................................................................... 14-33

14.3 BUS APPLICATIONS......................... .. ............... .. ............... .. ............... .. ............... ... 14-34

14.3.1 System Block Diagrams ...................................................................................... 14-34

14.3.1.1 Memory Subsystems .................................................................................... 14-37

14.3.1.2 I/O Subsystems ............................................................................................ 14-37

CHAPTER 15

TEST FEATURES

15.1 ON-CIRCUIT EMULATION (ONCE)............................................................................ 15-1

15.1.1 Entering/Exiting ONCE Mode ......... ......................... .. ......................... .. ................. 15-1

15.2 BOUNDARY SCAN (JTAG)......................................................................................... 15-2

15.2.1 Boundary Scan Architecture ....................................... ............ .. ............ ............ ..... 15-2

15.2.1.1 TAP Controller ................................................................................................ 15-2

15.2. 1. 2 Ins truction R e g is te r ....... ......... ... .......... ......... .......... .......... ......... .......... ... ........ 15-2

15.2.1.3 Test Data Registers ........................................................................................ 15-2

15.2.1.4 TAP Elements ................................................................................................ 15-3

15.3 TAP REGISTERS........................................................................................................ 15-5

15.3. 1 Instruc t io n R e g is te r (IR) ... .. .......... .......... ......... .......... .......... .......... .. .......... .......... ... 15- 5

15.3.2 TAP Test Data Registers ....................................................................................... 15-6

15.3.2.1 Device Identification Register ......................................................................... 15-6

15.3.2.2 Bypass Register ............................................................................................. 15-6

15.3.2.3 RUNBIST Register ................... .. .. ......................... .. ......................... .. ............ 15-7

15.3.2.4 B oundary-Scan Register ............... ............ .. ............ .. ........... ............ .. ............ 15-7

15.3.3 Boundary Scan Instruction Set .............................................................................. 15-8

15.3.4 IEEE Required Instructions ................................................................................... 15-8

15.3.5 TAP Controller ....................................................................................................... 15-9

15.3.5.1 Test Logic Reset State ................................................................................. 15-10

15.3.5.2 Run-Test/Idle State ...................................................................................... 15-10

Page 15

xv

15.3.5.3 Select-DR-Scan State .................................................................................. 15-10

15.3.5.4 Capture-DR State ......................................................................................... 15-10

15.3.5.5 Shift-DR State .............................................................................................. 15-11

15.3.5.6 Exit1-DR State ............................................................................................. 15-11

15.3.5.7 Pause-DR State ........................................................................................... 15-11

15.3.5.8 Exit2-DR State ............................................................................................. 15-11

15.3.5.9 Update-DR State .......................................................................................... 15-12

15.3.5.10 Select-IR Scan State .................................................................................... 15-12

15.3.5.11 Capture-IR State .......................................................................................... 15-12

15.3.5.12 Shift-IR State ................................................................................................ 15-12

15.3.5.13 Exit1-IR State ............................................................................................... 15-13

15.3.5.14 Pause-IR State ............................................................................................. 15-13

15.3.5.15 Exit2-IR State ............................................................................................... 15-13

15.3.5.16 Update-IR State ........................................................................................... 15-13

15.3.6 Boundary-Scan Register ............... .. ............ ............ .. ................................. ......... 15- 14

15.3.6.1 Example ....................................................................................................... 15-15

15.3.7 Boundary Scan Description Language Examp le ............. ............ .. ............ .......... 15-18

APPENDIX A

CONSIDERATIONS FOR WRITING PORTABLE CODE

A.1 CORE ARCHITECTURE..................................................................................... .... .. ....... A-1

A.2 ADDRESS SPACE RESTRICTIONS............................................................................... A-2

A.2.1 Reserved Me m o ry ........ ... ......... .......... .......... .......... .. .......... ......... .......... .......... .......... A-2

A.2.2 Initialization Boot Record ........................................................................................... A-2

A.2.3 Internal Data RAM ..................................................................................................... A-2

A.2.4 Instruction Cache ...................................................................................................... A-2

A.3 Data and Data Structure Alignment.................................................................................. A-3

A.4 RESERVED LOCATIONS IN REGISTERS AND DATA STRUCTURES......................... A-4

A.5 INSTRUCTION SET......................................................................................................... A-4

A.5.1 Instruction Timing ...................................................................................................... A-4

A.5.2 Implemen t a tio n -S p e c ific Instru ct ions ......... .......... .......... .......... ......... ... .......... ......... ... A-5

A.6 EX T E N D ED R E G IS T E R S E T. ......... .......... .......... .. .......... .......... ......... .......... .......... .......... A-5

A.7 I NIT IALIZA TI O N ...... .......... .......... .. .......... ......... .......... .......... .......... ......... ... .......... ......... ... A-5

A.8 MEMORY CONFIGURATION.......................................................................................... A-6

A.9 INTERRUPTS .................................................................................................................. A-6

A.10 OTHER i960 Jx PROCESSOR IMPLEMENTATION-SPECIFIC FEATURES........... ....... A-6

A.10.1 Data Control Peripher al Units ............................... ............. .. .............. ............. ........... A-7

A.10.2 Timers ....................................................................................................................... A-7

A.10. 3 Fault Impleme n ta tion .... .......... .......... ......... .......... .......... .......... .. .......... .......... ......... ... A-7

A.11 BREAKPOINTS................................................................................................................ A-7

APPENDIX B

OPCODES AND EXECUTION TIMES

B.1 INSTRUCTION REFERENCE BY OPCODE ................. .... ................................. .. .. .. ....... B-1

Page 16

xvi

APPENDIX C

MACHINE-LEVEL INSTRUCTION FORMATS

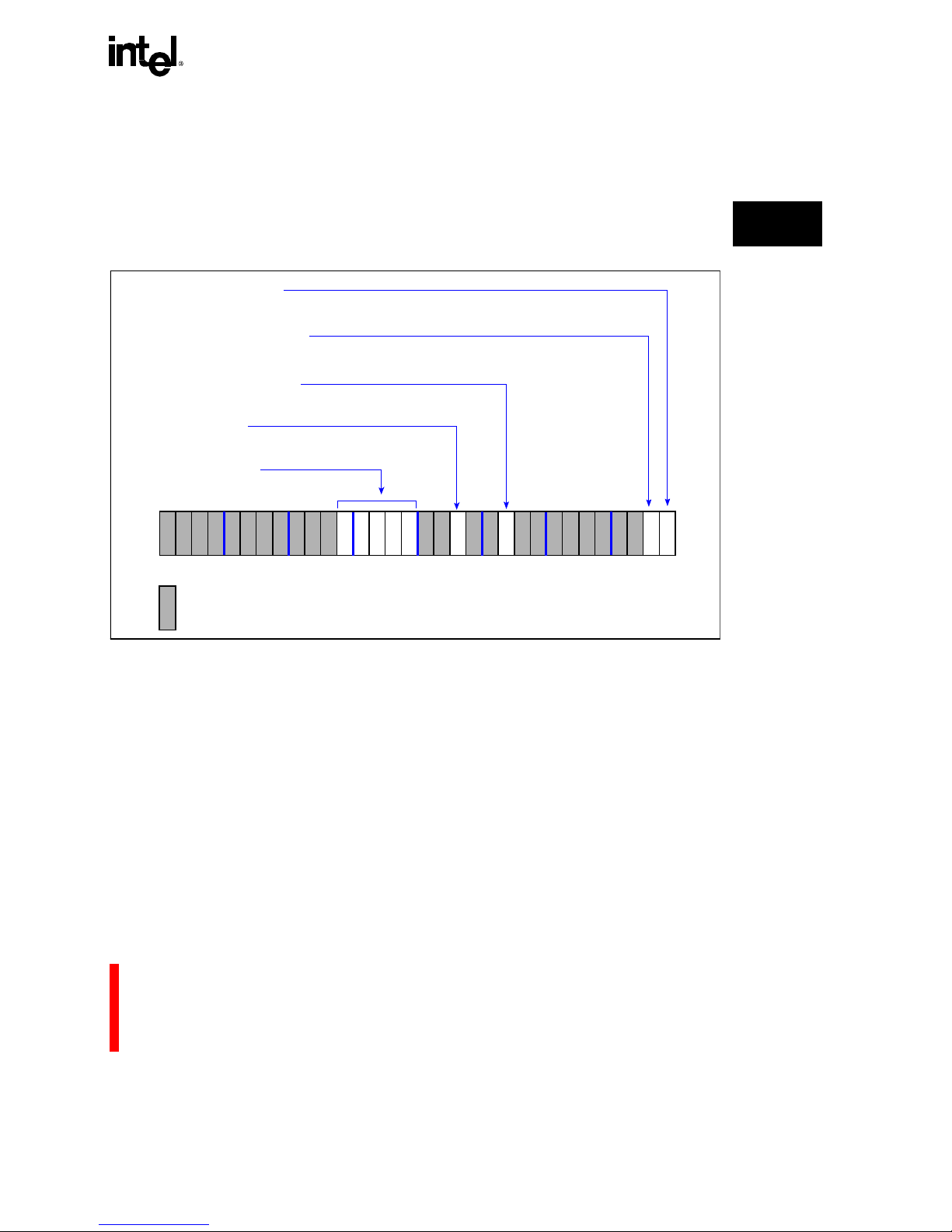

C.1 GENERAL INSTRUCTION FORMAT............................................. ...................... ........... C-1

C.2 REG FORMAT................................................................................................................. C-2

C.3 COBR FORMAT .............................................................................................................. C-3

C.4 CTRL FORMAT............................................................................................................... C-4

C.5 MEM FORMAT ................................................................................................................ C-4

C.5.1 MEMA Format Addressing ........................................................................................ C-5

C.5.2 MEMB Format Addressing ........................................................................................ C-6

APPENDIX D

REGISTER AND DATA STRUCTURES

D.1 REGISTERS.................................................................................................................... D-3

GLOSSARY

INDEX

Page 17

xvii

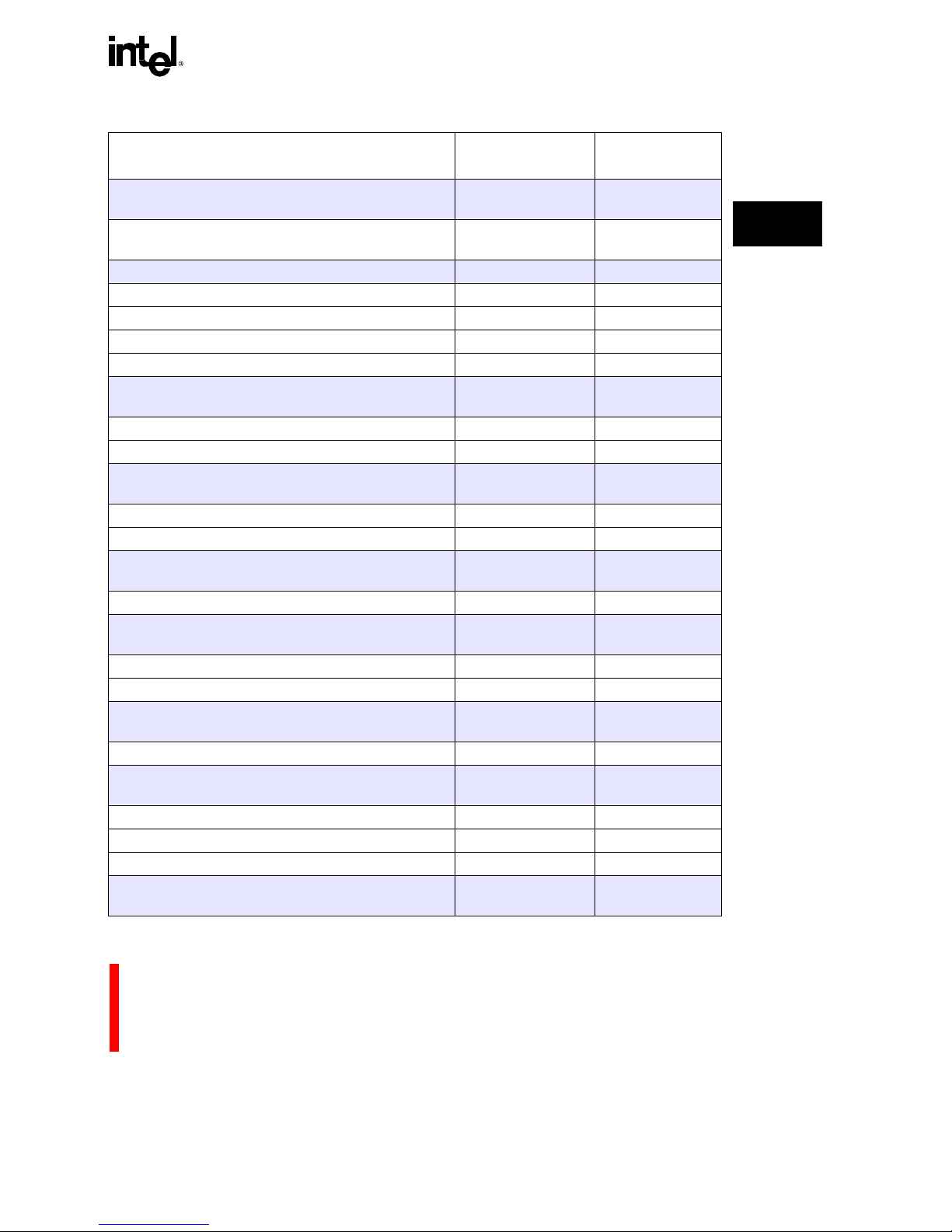

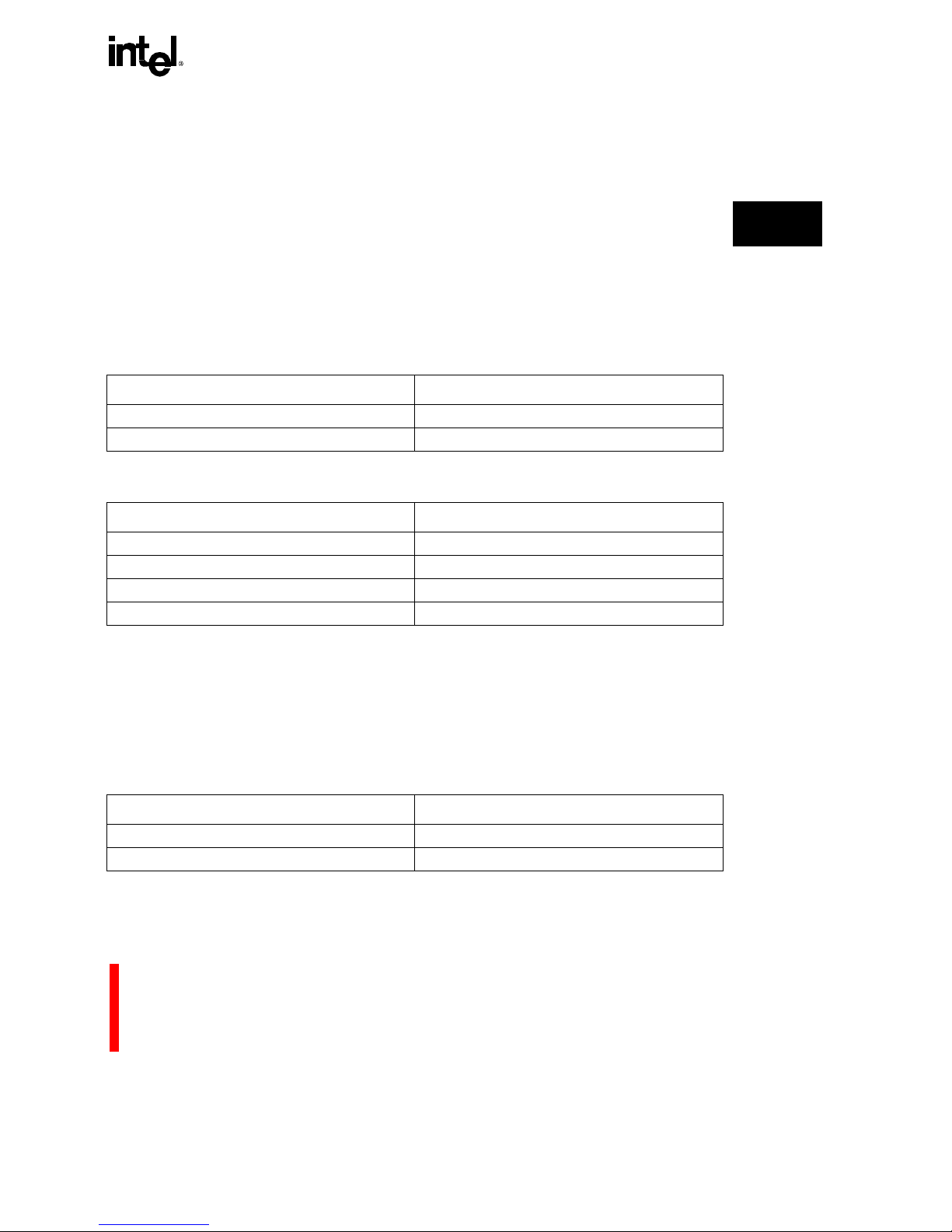

FIGURES

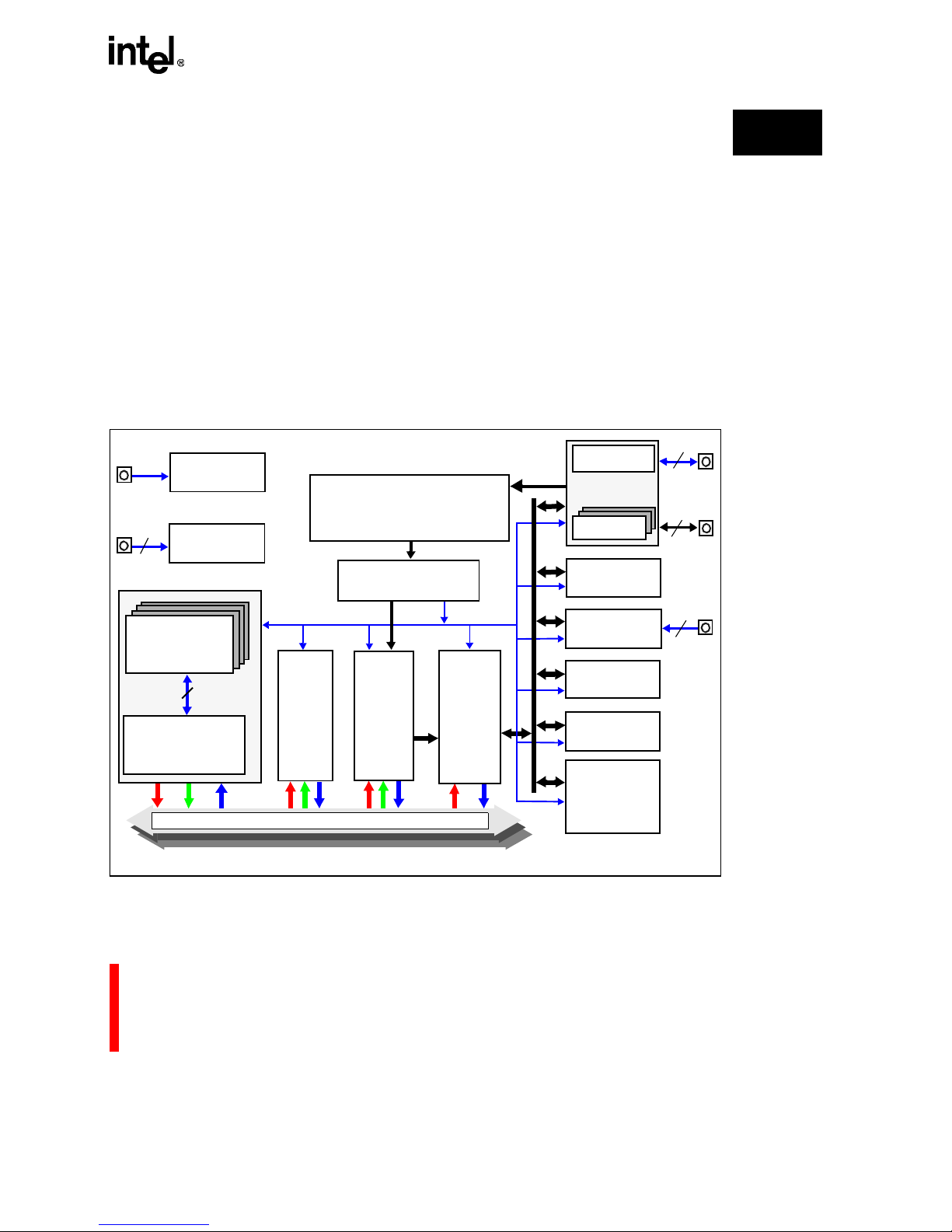

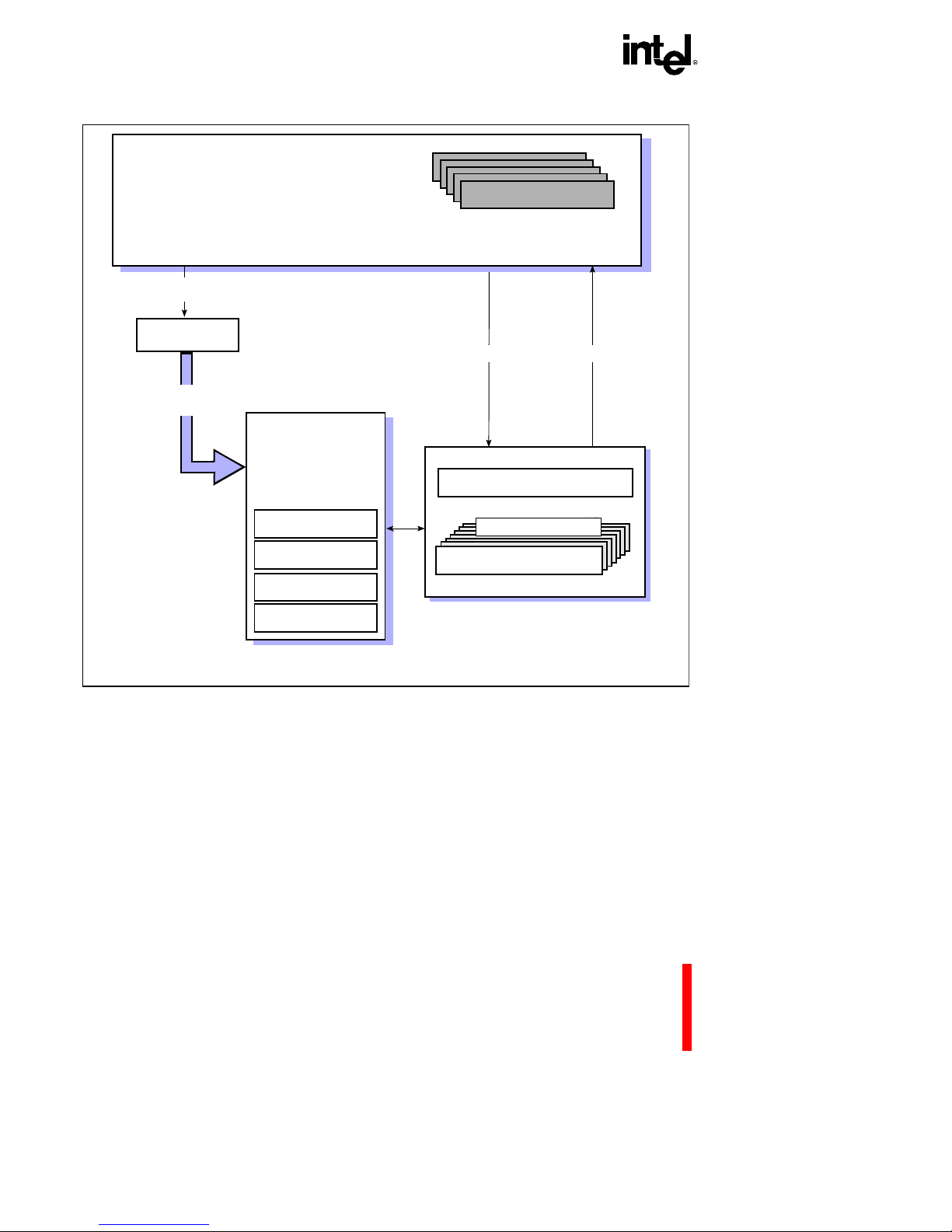

Figure 1-1. i960

®

Jx Microprocessor Functional Block Dia gram.......... ............ ........... ........... 1-3

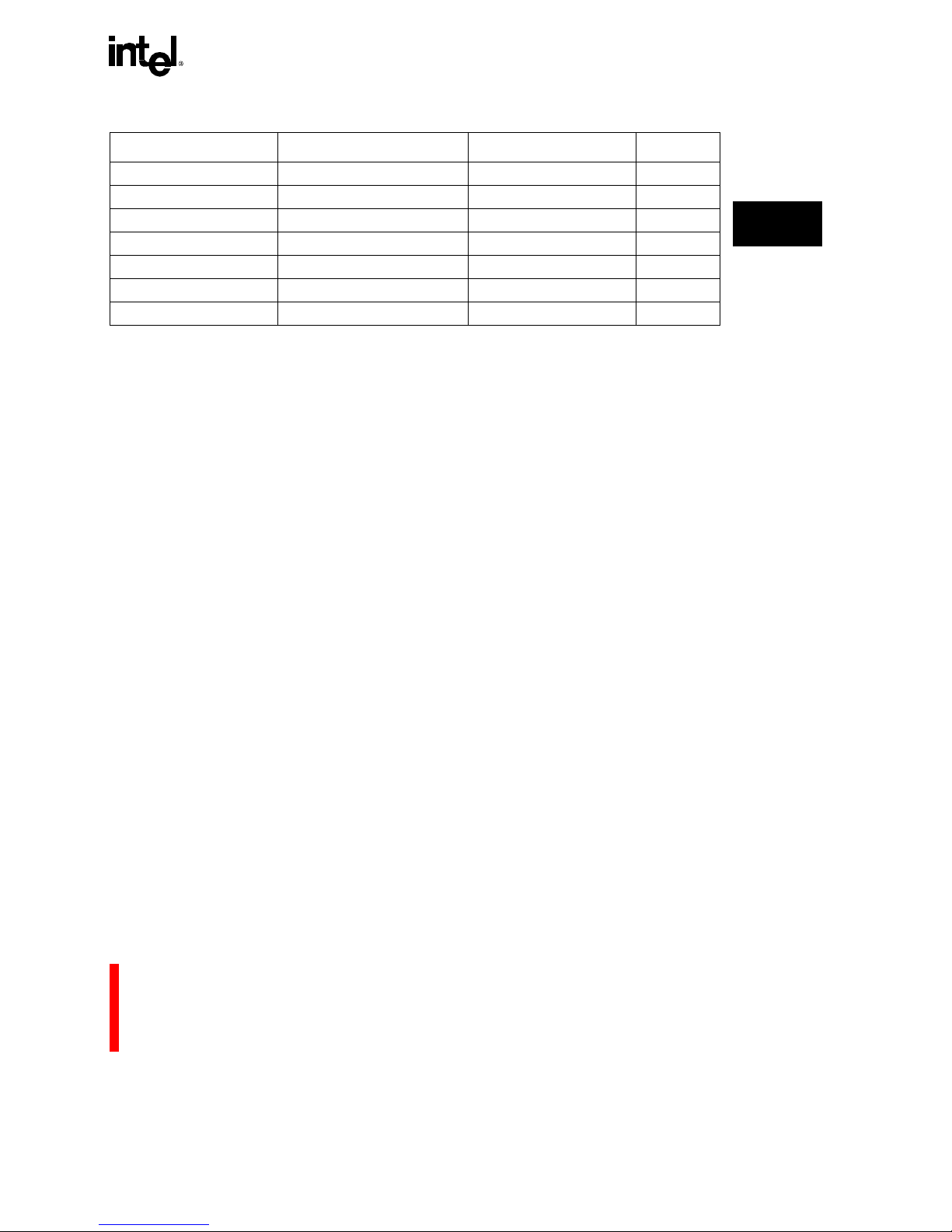

Figure 2-1. Data Types and Ranges......... .. ............ ............ ............................................. ...... 2-1

Figure 2-2. Data Placement in Registers ............................................................................... 2-6

Figure 3-1. i960

®

Jx Processor Programming Environment Elements .................................. 3-2

Figure 3-2. Memory Address Space .................................................................................... 3-13

Figure 3-3. Arithmetic Controls (AC) Register...................................................................... 3-18

Figure 3-4. Process Controls (PC) Register......................................................................... 3-21

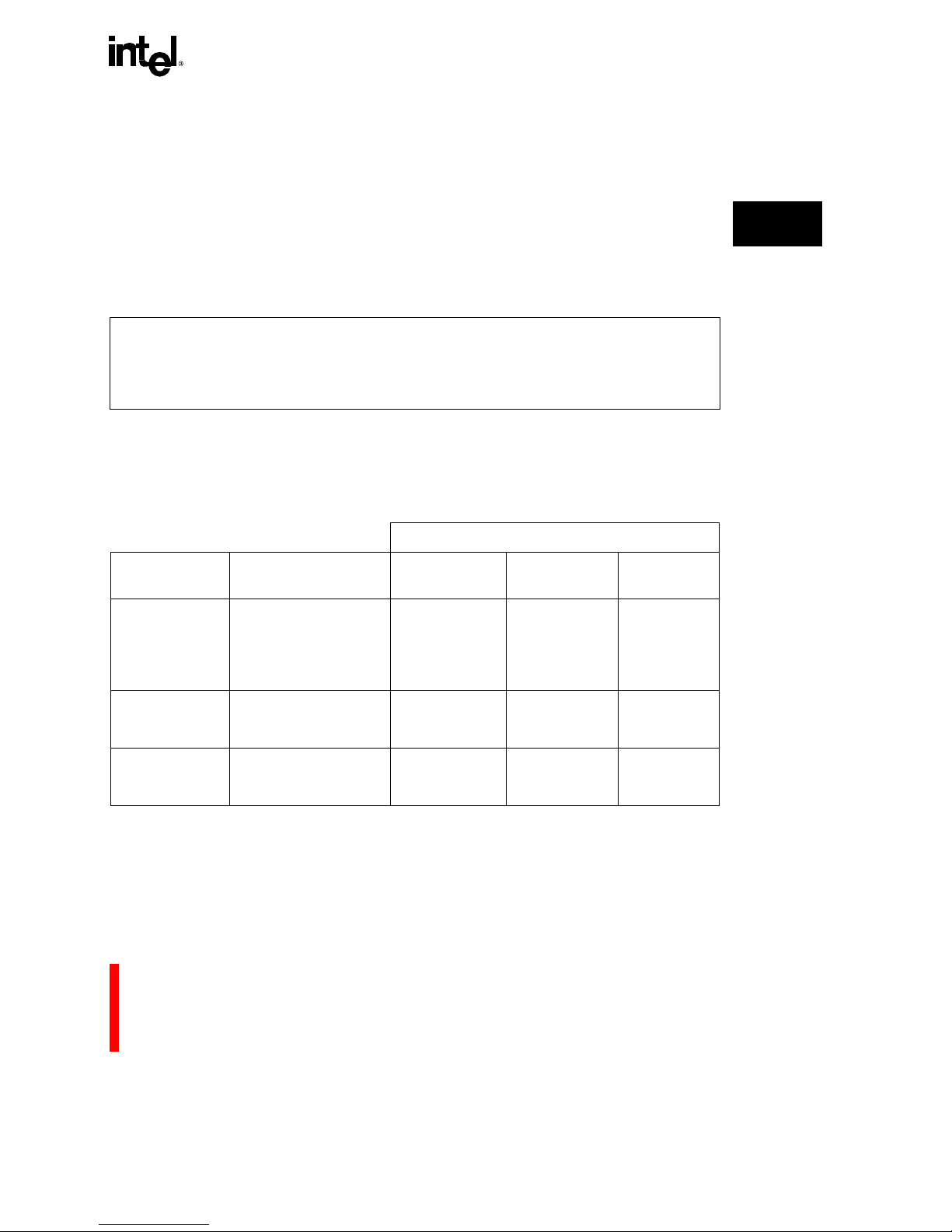

Figure 4-1. Internal Data RAM and Register Cache ............................. .. .. ......................... .. .. 4-2

Figure 5-1. Machine-Level Instruction Formats...................................................................... 5-3

Figure 6-1. dcctl

src1

and

src/dst

Formats........................................................................... 6-41

Figure 6-2. Store Data Cache to Memory Output Format .................................................... 6-42

Figure 6-3. D-Cache Tag and Valid Bit Formats.................................................................. 6-43

Figure 6-4. icctl

src1

and

src/dst

Formats............................................................................ 6-59

Figure 6-5. Store Instruction Cache to Memory Output Format........................................... 6-61

Figure 6-6. I-Cache Set Data, Tag and Valid Bit Formats.................................................... 6-62

Figure 6-7. Src1 Operand Inter pretation... .. ............ ........................ ........... ............ ............ 6-114

Figure 6-8.

src/dst

Interpretation for Breakpoint Resource Request.................................. 6-115

Figure 7-1. Procedure Stack St ructure and Local Registers............ ............ .. ............ ............ 7-3

Figure 7-2. Frame Spill........................................................................................................... 7- 9

Figure 7-3. Frame Fill........................................................................................................... 7-10

Figure 7-4. System Procedure Table ................................................................................... 7-16

Figure 7-5. Previous Frame Pointer Register (PFP) (r0)...................................................... 7-20

Figure 8-1. Fault-Handlin g Data Str uctures ............. .. .. ......................... .. .............. ............. .... 8-1

Figure 8-2. Fault Table and Fault Table Entries....................... ........................ ........... ........... 8-5

Figure 8-3. Fault Record ........................................................................................................ 8-7

Figure 8-4. Storage of the Fault Record on the Stack............ .. ............ .................................. 8-8

Figure 9-1. 80960Jx Trace Controls (TC) Register................................................................ 9-2

Figure 9-2. Breakpoint Control Register (BPCON)................................................................. 9-8

Figure 9-3. Data Address Breakpoint (DAB) Register Format ............................................. 9-10

Figure 9-4. Instruction Breakpoint (IPB) Register Format .................................................... 9-10

Figure 10-1. Timer Functional Diagram ................................................................................. 10-1

Figure 10-2. Timer Mode Register (TMR0, TMR1) ................................................................ 10-3

Figure 10-3. Timer Count Register (TCR0, TCR1)................................................................. 10-6

Figure 10-4. Timer Reload Register (TRR0, TRR1)............................................................... 10-7

Figure 10-5. Timer Unit State Diagram ................................................................................ 10-13

Figure 11-1. Interrupt Handling Data Structures .................................................................... 11-2

Figure 11-2. Interrupt Table ................................................................................................... 11-4

Figure 11-3. Storage of an Interrupt Record on the Interrupt Stack............... ............ .. .......... 11-7

Figure 11-4. Dedicated Mode............................................................................................... 11-14

Page 18

xviii

Figure 11-5. Expanded Mode .............................................................................................. 11-15

Figure 11-6. Implementation of Expanded Mode Sources................................................... 11-16

Figure 11-7. Interrupt Sampling ........................................................................................... 11-20

Figure 11-8. Interrupt Control (ICON) Register.................................................................... 11-22

Figure 11-9. Interrupt Mapping (IMAP0-IMAP2) Registers.................................................. 11-24

Figure 11-10. Interrupt Pending (IPND) Register................................................................... 11-25

Figure 11-11. Interrupt Mask (IMSK) Registers ..................................................................... 11-26

Figure 11-12. Interrupt Controller........................................................................................... 11-30

Figure 11-13. Interrupt Service Flowchart.............................................................................. 11-34

Figure 12-1. Processor Initialization Flow.............................................................................. 12-2

Figure 12-2. Cold Reset Waveform ....................................................................................... 12-4