Page 1

GD82559ER Fast Ethernet**

PCI Controller

Networking Silicon

Product Features

Datasheet

■ Optimum Integration for Lowest Cost

Solution

—Integrated IEEE 802.3 10BASE-T and

100BASE-TX compatible PHY

—Glueless 32-bit PCI master interface

—128 Kbyte Flash interface

—Thin BGA 15mm

—ACPI and PCI Power Management

—Power management e v en t on

“interesting” packets and link status

change support

—Test Access Port

2

package

■ High Performance Networking Functions

—Chained memory structure similar to the

82559,82558, 82557, and 82596

—Improved dynamic transmit chaining

with multiple priorities transmit queues

—Full Duplex support at both 10 and 100

Mbps

—IEEE 802.3u Auto-Negotiation support

—3 Kbyte transmit and 3 Kbyte receive

FIFOs

—Fast back-to-back transmission support

with minimum interframe spacing

—IEEE 802.3x 100BASE-TX Flow

Control support

—Low Power Features

—Low power 3.3 V device

—Efficient dynamic stan dby mode

—Deep power down support

—Clockrun protocol support

Document Number: 714682-001

Revision 1.0

March 1999

Page 2

GD82559ER - Networking Silicon

Revision History

Revision

Date

Revision Description

Mar. 1999 1.0 First release.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82559 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright © Intel Corporation, 1999

* Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM.

** Third-party brands and names are the property of their respective owners.

ii

Datasheet

Page 3

Networking Silicon — GD82559ER

Contents

1. INTRODUCTION .............................................................................................................................1

1.1 GD82559ER Overview .......................................................................................................1

1.2 Suggested Reading ............................................................................................................1

2. GD82559ER ARCHITECTURAL OVERVIEW................................................................................3

2.1 Parallel Subsystem Overview... .......................................................... ....... ...... ....... ...... ......3

2.2 FIFO Subsystem Overview.................................................................................................4

2.3 10/100 Mbps Serial CSMA/CD Unit Overview....................................................................5

2.4 10/100 Mbps Physical Layer Unit.......................................................................................5

3. SIGNA L DESCRIP TIO NS .................................. ....... .......................................................... ...... . .....7

3.1 Signal Type Definitions.......................................................................................................7

3.2 PCI Bus Interface Signals...................................................................................................7

3.2.1 Address and Data Signals.................. ...... ....... ...................................................7

3.2.2 Interface Control Signals ....................................................................................8

3.2.3 System and Power Management Signals...........................................................9

3.3 Local Memory Interface Signals.........................................................................................9

3.4 Testability Port Signals.....................................................................................................10

3.5 PHY Signals .....................................................................................................................11

4. GD82559ER MEDIA ACCESS CONTROL FUNCTIONAL DESCRIPTION.................................13

4.1 82559ER Initialization.......................................................................................................13

4.1.1 Initialization Effects on 82559ER Units ............................................................13

4.2 PCI Interface.....................................................................................................................14

4.2.1 82559ER Bus Operations.................................................................................14

4.2.2 Clockrun Signal ............... .......................................................... ...... ....... ...... ....2 2

4.2.3 Power Management Event Signal....................................................................22

4.2.4 Power States....................................................................................................23

4.2.5 Wake-up Events...............................................................................................27

4.3 Parallel Flash Interface............. ....... ...... ....... ...... ...... ....... ...... ....... ...... ..............................28

4.4 Serial EEPROM Interface.................................................................................................28

4.5 10/100 Mbps CSMA/CD Unit............................................................................................30

4.5.1 Full Duplex .......................................................................................................31

4.5.2 Flow Control .....................................................................................................31

4.5.3 Address Filtering Modifications.........................................................................31

4.5.4 Long Frame Reception.....................................................................................31

4.6 Media Independent Interface (MII) Management Interface...............................................32

5. GD82559ER TEST PORT FUNCTIONALITY...............................................................................33

5.1 Introduction.......................................................................................................................33

5.2 Asynchronous Test Mode.................................................................................................33

5.3 Test Function Description.................................................................................................33

5.4 85/85.................................................................................................................................33

5.5 TriState.............................................................................................................................34

5.6 Nand - Tree ......................................................................................................................34

6. GD82559ER PHYSICAL LAYER FUNCTIONAL DESCRIPTION................................................37

6.1 100BASE-TX PHY Unit ....................................................................................................37

6.1.1 100BASE-TX Transmit Clock Generation ........................................................37

Datasheet

iii

Page 4

GD82559ER — Networking Silicon

6.1.2 100BASE-TX Transmit Blocks .................... ....... ..............................................37

6.1.3 100BASE-TX Receive Blocks ............................ ...... ........................................40

6.1.4 100BASE-TX Collision Detection ................ ....... ...... ....... ...... ....... ...... ....... .......41

6.1.5 100BASE-TX Link Integrity and Auto-Negotiati on Sol ution.......... ...... ....... ...... .41

6.1.6 Auto 10/100 Mbps Speed Selection.................................................................41

6.2 10BASE-T Functionality ...................................................................................................41

6.2.1 10BASE-T Transmit Clock Generation.............................................................41

6.2.2 10BASE-T Transmit Blocks..............................................................................42

6.2.3 10BASE-T Receive Blocks...............................................................................42

6.2.4 10BASE-T Collision Detection..........................................................................43

6.2.5 10BASE-T Link Integrity...................................................................................43

6.2.6 10BASE-T Jabber Control Function.................................................................43

6.2.7 10BASE-T Full Duplex .....................................................................................43

6.3 Auto-Negotiation Functionalit y.................................................. ....... ...... ....... ....................43

6.3.1 Description ...................................... ...... ...... .....................................................44

6.3.2 Parallel Detect and Auto-Negotiation...............................................................44

6.4 LED Description................................................................................................................45

7. PCI CONFIGURATION REGISTERS ...........................................................................................47

7.1 LAN (Ethernet) PCI Configuration Space.........................................................................47

7.1.1 PCI Vendor ID and Device ID Registers ..........................................................47

7.1.2 PCI Command Register ...................................................................................48

7.1.3 PCI Status Register..........................................................................................49

7.1.4 PCI Revision ID Register..................................................................................50

7.1.5 PCI Class Code Register .................................................................................50

7.1.6 PCI Cache Line Size Register..........................................................................50

7.1.7 PCI Latency Timer............................................................................................51

7.1.8 PCI Header Type..............................................................................................51

7.1.9 PCI Base Address Registers............................................................................51

7.1.10 PCI Subsystem Vendor ID and Subsystem ID Registers.................................53

7.1.11 Capability Pointer .............................................................................................53

7.1.12 Interrupt Line Register......................................................................................53

7.1.13 Interrupt Pin Register .......................................................................................54

7.1.14 Minimum Grant Register ..................................................................................54

7.1.15 Maximum Latency Register..............................................................................54

7.1.16 Capability ID Register.......................................................................................54

7.1.17 Next Item Pointer......... ....... ...... ....... .......................................................... ...... .54

7.1.18 Power Management Capabilities Register.......................................................54

7.1.19 Power Management Control/Status Register (PMCSR)...................................55

7.1.20 Data Register ...................................................................................................56

8. CONTROL/STATUS REGISTERS................................................................................................57

8.1 LAN (Ethernet) Control/Status Registers..........................................................................57

8.1.1 System Control Block Status Word..................................................................58

8.1.2 System Control Block Command Word............................................................59

8.1.3 System Control Block General Pointer.............................................................59

8.1.4 PORT ...............................................................................................................59

8.1.5 Flash Control Register......................................................................................59

8.1.6 EEPROM Control Register...............................................................................59

8.1.7 Management Data Interface Control Register..................................................59

8.1.8 Receive Direct Memory Access Byte Count.....................................................60

8.1.9 Early Receive Interrupt.....................................................................................60

iv

Datasheet

Page 5

Networking Silicon — GD82559ER

8.1.10 Flow Control Register.......................................................................................60

8.1.11 Power Management Driver Register................................................................60

8.1.12 General Control Register..................................................................................61

8.1.13 General Status Register...................................................................................61

8.2 Statistical Counters...........................................................................................................62

9. PHY UNIT REGISTERS................................................................................................................65

9.1 MDI Registers 0 - 7............. ...... ....... ...... .......................................................... ....... ...... .. ..6 5

9.1.1 Register 0: Control Register Bit Definitions .....................................................65

9.1.2 Register 1: Status Register Bit Definitions .......................................................66

9.1.3 Register 2: PHY Identifier Register Bit Definitions ...........................................67

9.1.4 Register 3: PHY Identifier Register Bit Definitions ...........................................67

9.1.5 Register 4: Auto-Negotiation Advertisement Register Bit Definitions ..............67

9.1.6 Register 5: Auto-Negotiation Link Partner Ability Register Bit Definitions .......67

9.1.7 Register 6: Auto-Negotiation Expansion Register Bit Definitions ....................68

9.2 MDI Registers 8 - 15........... ...... ....... ...... .......................................................... ....... ...... ... .68

9.3 MDI Register 16 - 31 ... ....... ...... ....... ...... .......................................................... ....... ...... ....68

9.3.1 Register 16: PHY Unit Status and Control Register Bit Definitions .................68

9.3.2 Register 17: PHY Unit Special Control Bit Definitions .....................................69

9.3.3 Register 18: PHY Address Register.................................................................70

9.3.4 Register 19: 100BASE-TX Receive False Carrier Counter Bit Definitions ......70

9.3.5 Register 20: 100BASE-TX Receive Disconnect Counter Bit Definitions .........70

9.3.6 Register 21: 100BASE-TX Receive Error Frame Counter Bit Definitions ........70

9.3.7 Register 22: Receive Symbol Error Counter Bit Definitions ............................70

9.3.8 Register 23: 100BASE-TX Receive Premature End of Frame Error Counter

Bit Definitions ..................................................................................................71

9.3.9 Register 24: 10BASE-T Receive End of Frame Error Counter Bit Definitions .71

9.3.10 Register 25: 10BASE-T Transmit Jabber Detect Counter Bit Definitions ........71

9.3.11 Register 26: Equalizer Control and Status Bit Definitions ................................71

9.3.12 Register 27: PHY Unit Special Control Bit Definitions .....................................71

10. ELECTRICAL AND TIMING SPECIFICATIONS ..........................................................................73

10.1 Absolute Maximum Ratings..............................................................................................73

10.2 DC Specifications ............................................................................................................73

10.3 AC Specifications ............... ...... ....... ...... ....... ...... ...... ........................................................76

10.4 Timing Specifications........................................................................................................77

10.4.1 Clocks Specifications .......................................................................................77

10.4.2 Timing Parameters ...........................................................................................78

12. PACKAGE AND PINOUT INFORMATION...................................................................................85

12.1 Package Information.........................................................................................................85

12.2 Pinout Information ............................................................................................................86

12.2.1 GD82559ER Pin Assignments ........................................................................86

12.2.2 GD82559ER Ball Grid Array Diagram .............................................................88

Datasheet

v

Page 6

GD82559ER — Networking Silicon

vi

Datasheet

Page 7

g

1. Introduction

g

1.1 GD82559ER Overview

The 82559ER is part of Intel's second generation family of fully integrated 10BASE-T/100BASETX LAN solutions. The 82559ER consists of both the Media Access Controller (MAC) and the

physical layer (PHY) combined into a single component solution. 82559 family members build on

the basic functionality of the 82558 and contain power management enhancements.

The 82559ER is a 32-bit PCI controller that features enhanced scatter-gather bus mastering

capabilities which enables the 82559ER to perform high-speed data transfers over the PCI bus.The

82559ER bus master capabilities enable the compo nent to process high-level commands and

perform multiple operations, thereby off-loading communication tasks from the system CPU. Two

large transmit and receive FIFOs of 3 Kbytes each help prevent data underruns and overruns,

allowing the 82559ER to transmit data with minimum interframe spacing (IFS).

The 82559ER can operate in either full duplex or half duplex mode. In full duplex mode the

82559ER adheres to the IEEE 802.3x Flow Control specification. Half duplex performance is

enhanced by a proprietary collision reductio n mechanism.

Networkin

Silicon — GD82559ER

The 82559ER includes a simple PHY interface to the wire transformer at rates of 10BASE-T and

100BASE-TX, and Auto-Negotiation capability for speed, duplex, and flow con trol. These features

and others reduce cost, real estate, and design complexity.

The 82559ER also includes an interface to a serial (4-pin) EEPROM and a parallel interface to a

128 Kbyte Flash memory. The EEPROM provides power-on initialization for hardware and

software configuration parameters

1.2 Suggested Readin

The 82559 family of devices are designed to be compliant with PC industry power management

initiatives. This includes the ACPI, PCI Power Management Specification, Network Device Class

specification, etc. See the following publicaitons for more information about these topics.

•

PCI Specification, PCI Special Interest Group.

•

Network Device Class Reference, Revision 1.0, In tel Corpor atio n, Micros oft Corp oration , and

Toshiba.

•

Advanced Configuration and Power Interface (ACPI) Specification, Intel Corporation,

Microsoft Corporation, Toshiba.

•

Advanced Power Management (APM) Specification, Intel Corporation and Microsoft

Corporation.

•

82559 Fast Ethernet Multifunction PCI/CardBus Controller Datasheet, Intel Corporation.

•

LAN On Motherboard (LOM) Design Guide Application Note (AP-391), Intel Corporation.

•

Test Access Port Applications Note (AP-393), Intel Corporation.

Datasheet

1

Page 8

GD82559ER — Networking Silicon

2

Datasheet

Page 9

Networkin

g

g

(

)

g

(

)

y

y

2. GD82559ER Architectural Overview

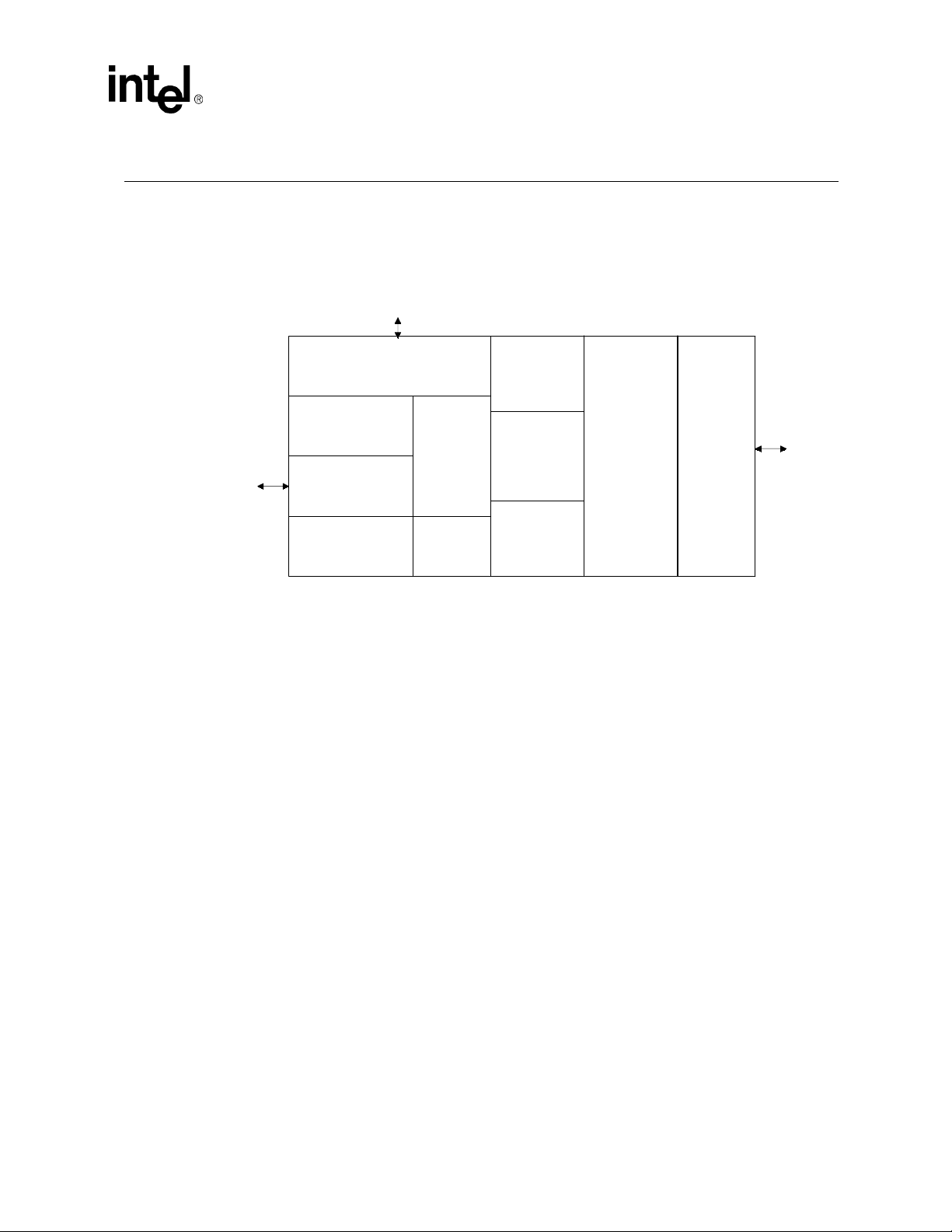

Figure 1 is a high level block diagram of the 82559ER. It is divided into four main subsystems: a

parallel subsystem, a FIFO subsystem, the 10/100 Mbps Carrier-Sense Multiple Access with

Collision Detect (CSMA/CD) unit, and the 10/10 0 Mbps physical layer (PHY) unit.

Local Memory

Interface

Silicon — GD82559ER

PCI Target and

Flash/EEPROM

Interface

PCI

Interface

Four Channel

Addressin

Interface Unit

Data Interface Unit

DMA

PCI Bus

BIU

DIU

Unit -

Micro-

machine

Dual

Ported

FIFO

Fi

ure 1. 82559ER Block Diagram

FIFO Control

2.1 Parallel Subsystem Overview

The parallel subsystem is broken down into several functional blocks: a PCI bus master interface, a

micromachine processing unit and its corresponding microcode ROM, and a PCI Target Control/

Flash/EEPROM interface. The parallel subsystem also interfaces to the FIFO subsystem, passing

data (such as transmit, receive, and configuration data) and command and status parameters

between these two blocks.

The PCI bus master interface provides a complete glueless interface to a PCI bus and is compliant

with the PCI Bus Specification, Revision 2.2. The 82559ER provides 32 bits of addressing and

data, as well as the complete control interface to operate on a PCI bus. As a PCI target, it follows

the PCI configuration format which allows all accesses to the 82559ER to be automatically

mapped into free memory and I/O space upon initialization of a PCI system. For processing of

transmit and receive frames, the 82559ER operates as a master on the PCI bus, initiating zero wait

state transfers for accessing these data parameters.

3 Kb

te

Tx FIFO

te

3 Kb

Rx FIFO

10/100 Mbps

CSMA/CD

100BASE-TX/

10BASE-T

PHY

TPE

Interface

The 82559ER Control/Status Register Block is part of the PCI target element. The Control/Status

Register block consists of the following 82559ER internal control registers: System Control Block

(SCB), PORT, Flash Control, EEPROM Control, and Management Data Interface (MDI) Control.

The micromachine is an embedded processing unit contained in the 82559ER. The micromachine

accesses the 82559ER microcode ROM working its way through the opcodes (or instructions)

contained in the ROM to perform its function s. Parameters acce ssed from memory such as po inters

to data buffers are also used by the micromachine during the processing of transmit or receive

frames by the 82559ER. A typical micromachine function is to transfer a data buffer pointer field

to the 82559ER DMA unit for direct access to the data buffer. The micromachine is divided into

two units, Receive Unit and Command Unit which includes transmit functions. These two units

Datasheet

3

Page 10

GD82559ER — Networking Silicon

operate independently. Control is switched between the two units according to the microcode

instruction flow . The indepe ndence of the Receive and Command units in the micromachine allows

the 82559ER to interleave commands and receive incoming frames, with no real-time CPU

intervention.

The 82559ER contains an interface to an external Flash memory, and external serial EEPROM.

These two interfaces are multiplexed. The Flash interface, which could also be used to connect to

any standard 8-bit device, provides up to 128 Kbytes of addressing to the Flash. Both read and

write accesses are supported. The Flash may be used for remote boot functions, network statistical

and diagnostic s functions, and manage ment functions. The Fl ash is mapped into host system

memory (anywhere within the 32-bit memory address space) for software accesses. It is also

mapped into an available boot expansion ROM location during boot time of the system. More

information on the Flash interface is detailed in Section 4.3, “Parallel Flash Interface” on page 28.

The EEPROM is used to store relevant information for a LAN connection such as node address, as

well as board manufacturing and configuration information. Both read and write accesses to the

EEPROM are supported by the 82559ER. Information on the EEPROM interface is detailed in

Section 4.4, “Serial EEPROM Interface” on page 28.

2.2 FIFO Subsystem Overview

The 82559ER FIFO subsystem consists of a 3 Kbyte transmit FIFO and 3 Kbyte receive FIFO.

Each FIFO is unidirectional and independent of the other. The FIFO subsystem serves as the

interface between the 82559ER parallel side an d the serial CSMA/CD unit. It provides a temporary

buffer storage area for frames as they are either being received or transmitted by the 82559ER,

which improves performance:

•

Transmit frames can be queued within the transmit FIFO, allowing back-to-back transmission

within the minimum Interframe Spacing (IFS).

•

The storage area in the FIFO allows the 82559ER to withstand long PCI bus latencies without

losing incoming data or corrupting outgoing data.

•

The 82559ER transmit FIFO threshold allows the transmit start threshold to be tuned to

eliminate underruns while concurrent transmits are being performed (i.e. pending transmits

will not be affected by the change in FIFO threshold).

•

The FIFO subsection allows extended PCI burst accesses with zero wait states to or from the

82559ER for both transmit and receive frames. This is because such the transfer is to the FIFO

storage area, rather than directly to the serial link.

•

Transmissions resulting in errors (collision detection or data underrun) are retransmitted

directly from the 82559ER FIFO, therey increasing performance and eliminating the need to

re-access this data from the host system.

•

Incoming runt receive frames (frames that are less than the legal minimum frame size) can be

discarded automatically by the 82559ER without transferri ng this faulty data to the host

system, and without host intervention.

•

Bad Frames resolution can be selectively left to the 82559ER, or under software control.

4

Datasheet

Page 11

Networkin

g

2.3 10/100 Mbps Serial CSMA/CD Unit Overview

The CSMA/CD unit of the 82559ER all ows it t o be conn ect ed to either a 10 or 100 Mbps Ethern et

network. The CSMA/CD unit performs all of the functions of the 802.3 protocol such as frame

formatting, frame stripping, collision handling, deferral to link traf fic, etc. The CSMA/CD unit can

also be placed in a full-duplex mode, which allows simultaneous transmission and reception of

frames.

2.4 10/100 Mbps Physical Layer Unit

The Physical Layer (PHY) unit of the 82559ER allows connection to either a 10 or 100 Mbps

Ethernet network. The PHY unit supports Auto-Negotiation for 100BASE-TX Full Duplex,

100BASE-TX Half Duplex, 10BASE-T Full Duplex, and 10BASE-T Half Duplex. It also supports

three LED pins to indicate link status, network activity, and speed.The 82559ER does not support

external PHY devices and does not expose its internal MII bus.

Silicon — GD82559ER

Datasheet

5

Page 12

GD82559ER — Networking Silicon

6

Datasheet

Page 13

g

3. Signal Descriptions

g

y

g

y

g

g

y

g

g

g

y

y

y

y

g

g

y

g

g

y

y

y

y

g

3.1 Signal Type Definitions

Type Name Description

IN Input The input pin is a standard input onl

OUT Output

T/S Tri-State The tri-state pin is a bidirectional, input/output pin.

S/T/S Sustained Tri-State

O/D Open Drain

A/I Analo

A/O Analo

B Bias The bias pin is an input bias.

Input The analog input pin is used for analog input signals.

Output The analog output pin is used for analog output signals.

The output pin is a Tot em Pole Output pin and is a standard

active driver.

The sustained tri-state pin is an active low tri-state si

and driven b

S pin low must drive it hi

floatin

one clock c

owner.

The open drain pin allows multiple devices to share this si

as a wired-OR.

Networkin

one agent at a time. The agent asserting the S/T/

h at least one clock cycle before

the pin. A new agent can only assert an S/T/S signal low

cle after it has been tri-stated by the previous

Silicon —GD82559ER

signal.

nal owned

nal

3.2 PCI Bus Interface Si

3.2.1 Address and Data Signals

Symbol Type Name and Function

Address and Data.

the same PCI pins. A bus transaction consists of an address phase

followed b

AD[31:0] T/S

C/BE[3:0]# T/S

PAR T/S

address and data lines contain the 32-bit ph

this is a b

address. The 82559ER uses little-endian b

words, AD[31:24] contain the most si

contain the least si

and data lines contain data.

Command and Byte Enable.

nals are multiplexed on the same PCI pins. During the address

si

phase, the C/BE# lines define the bus command. Durin

phase, the C/BE# lines are used as B

are valid for the entire data phase and determine which b

meaningful data.

carr

Parity.

and valid one clock after the address phase. For data phases, PAR is

stable and valid one clock after either IRDY# is asserted on a write

transaction or TRDY# is asserted on a read transaction.Once PAR is

valid, it remains valid until one clock after the completion of the current

data phase. The master drives PAR for address and write data

phases; and the tar

nals

The address and data lines are multiplexed on

one or more data phases. During the address phase, the

te address; for configuration and memory, it is a Dword

nificant byte). During the data phases, the address

The bus command and b

Parit

is even across AD[31:0] and C/BE[3:0]# lines. It is stable

et, for read data phases.

sical address. For I/O,

te ordering (in other

nificant byte and AD[7:0]

te enable

the data

te Enables. The Byte Enables

te lanes

Datasheet

7

Page 14

GD82559ER — Networking Silicon

y

g

g

y

y

g

y

(

g

y

y (

y

(

g

y

y

g

y

g

y

g

g

g

q

g

y

g

g

g

g

gg

y

y

g

y

g

y

g

y

y

3.2.2 Interface Control Signals

Symbol Type Name and Function

Cycle Frame.

FRAME# S/T/S

IRDY# S/T/S

TRDY# S/T/S

STOP# S/T/S

IDSEL IN

DEVSEL# S/T/S

REQ# T/S

GNT# IN

INTA# O/D

SERR# O/D

PERR# S/T/S

to indicate the be

asserted to indicate the start of a transaction and de-asserted durin

the final data phase.

Initiator Ready.

abilit

with the tar

clock cycle where both IRDY# and TRDY# are sampled asserted

an

low) simultaneously.

Target Ready.

abilit

with the initiator read

clock cycle where both IRDY# and TRDY# are sampled asserted

an

low) simultaneously.

Stop.

that it wishes to stop the current transaction. As a bus slave, STOP# is

driven b

transaction. As a bus master, STOP# is received b

stop the current transaction.

Initialization Device Select.

used b

and write transactions. This si

stems.

s

Device Select.

it has detected its address. As a bus master , the DEVSEL# is an input

nal to the 82559ER indicating whether any device on the bus has

si

been selected. As a bus slave, the 82559ER asserts DEVSEL# to

indicate that it has decoded its address as the tar

transaction.

Request.

82559ER desires use of the bus. This is a point-to-point si

ever

Grant.

the 82559ER that access to the bus has been

to-point si

Interrupt A.

the 82559ER. This is an active low, level tri

System Error.

parit

le PCI clock.

sin

Parity Error.

durin

is asserted two clock c

receivin

data phase where an error is detected. A device cannot report a parit

error until it has claimed the access b

completed a data phase.

The c

cle frame signal is driven by the current master

inning and duration of a transaction. FRAME# is

to complete the current data phase and is used in conjunction

to complete the current data phase and is used in conjunction

The stop si

the 82559ER as a chip select during PCI configuration read

bus master has its own REQ#.

The

errors. When an error is detected, SERR# is driven low for a

all PCI transactions except a Special Cycle. The parity error pin

The initiator read

et ready (TRDY#) signal. A data phase is completed on

et ready signal indicates the selected device’s

The tar

IRDY#) signal. A data phase is completed on

nal is driven by the target to indicate to the initiator

the 82559ER to inform the bus master to stop the current

The device select si

The re

uest signal indicates to the bus arbiter that the

rant signal is asserted by the bus arbiter and indicates to

nal and every master has its own GNT#.

The interrupt A si

The s

stem error signal is used to report address

The parit

data. The minimum duration of PERR# is one clock for each

error signal is used to report data parity errors

cles after the error was detected by the device

signal indicates the bus master’s

the 82559ER to

The initialization device select si

nal is provided by the host in PCI

nal is asserted by the target once

et of the current

nal and

ranted. This is a point-

nal is used to request an interrupt by

ered interrupt signal.

asserting DEVSEL# and

nal is

8

Datasheet

Page 15

g

3.2.3 System and Power Management Signals

g

g

g

g

g

g

g

g

g

g

q

g

g

g

y

g

(

(

)

g

g

g

y

y

g

y

y

g

y

y

g

g

g

g

g

g

g

g

Symbol Type Name and Function

CLK IN

CLKRUN#

RST# IN

PME# O/D

ISOLATE# IN

ALTRST# IN

VIO

IN/OUT

O/D

B

IN

The Clock si

Clock.

and is an input si

PCI Clock si

nominal operation. The 82559ER supports Clock si

the Clockrun protocol.

usin

Clockrun.

down the PCI Clock si

disable suspension of the PCI Clock si

When the Clockrun si

an external pull-down resistor.

Reset.

se

asserted, all PCI output si

Power Management Event.

indicates that a power mana

stem.

s

Isolate.

PCI bus. When Isolate is active

PCI outputs

and RST#

source, the ISOLATE# pin should be pulled hi

throu

Alternate Reset.

82559ER on power-up. In s

suppl

Otherwise, ALTRST# should be tied to V

Voltage Input/Output.

PCI interface. This pin should be connected to 5V ± 5% in a 5 volt PCI

stem and 3.3 volts in a 3.3 volt PCI system. Be sure to install a 10K

s

pull-up resistor. This resistor acts as a current limit resistor in s

where the VIO bias volta

82559ER ma

The Clockrun si

The PCI Reset si

uencers, and signals into a consistent state. When RST# is

The Isolate si

. If the 82559ER is not powered by an auxiliary power

h a 4.7K-62K resistor.

, ALTRST# should be connected to a power-up detection circuit.

nal provides the timing for all PCI transactions

nal to every PCI device. The 82559ER requires a

nal (frequency greater than or equal to 16 MHz) for

nal is used by the system to pause or slow

nal. It is used by the 82559ER to enable or

nal is not used, this pin should be connected to

nal is used to place PCI registers,

nals will be tri-stated.

nal is used to isolate the 82559ER from the

except PME#) or sample its PCI inputs (including CLK

The Alternate Reset si

stems that support an auxiliary power

The VIO pin is the a volta

e maybe shutdown. In this cases the

consume additional current without a resistor.

Networkin

nal or restart of the PCI clock.

The Power Mana

ement event has occurred in a PCI bus

low), the 82559ER does not drive its

Silicon —GD82559ER

nal suspension

ement Event signal

h to the bus Vcc

nal is used to reset the

.

cc

e bias pin for the

stem

3.3 Local Memory Interface Signals

Symbol Type Name and Function

FLD[7:0] T/S

FLA[16]/

CLK25

FLA[15]/

EESK

FLA[14]/

EEDO

OUT

OUT

IN/OUT

Flash Data Input/Output.

interface.

Flash Address[16]/25 MHz Clock.

b

the status of the Flash Address[7] (FLA[7]) pin. If FLA[7] is left

, this pin is used as FLA[16]; otherwise, if FLA[7] is connected

floatin

to a pull-up resistor, this pin is used as a 25 MHz clock.

Flash Address[15]/EEPROM Data Output.

this multiplexed pin acts as the Flash Address [15] output si

EEPROM accesses, it acts as the serial shift clock output to

Durin

the EEPROM.

Flash Address[14]/EEPROM Data Output.

this multiplexed pin acts as the Flash Address [14] output si

EEPROM accesses, it acts as serial input data to the EEPROM

Durin

Data Output si

nal.

Datasheet

These pins are used for Flash data

This multiplexed pin is controlled

Durin

Flash accesses,

Durin

Flash accesses,

nal.

nal.

9

Page 16

GD82559ER — Networking Silicon

g

g

g

g

y

g

g

g

(

)

y

g

(

y

g

g

g

(

y

g

g

y

g

y

g

y

g

y

g

Symbol Type Name and Function

FLA[13]/

EEDI

FLA[12:8] OUT

FLA[7]/

CLKENB

FLA[6:2] OUT

FLA[1]/

AUXPWR

FLA[0] T/S

EECS OUT

FLCS# OUT

FLOE# OUT

FLWE# OUT

OUT

T/S

T/S

Durin

Flash Address[13]/EEPROM Data Input.

this multiplexed pin acts as the Flash Address [13] output si

EEPROM accesses, it acts as serial output data to the

Durin

EEPROM Data Input si

Flash Address[12:8].

to support 128 Kb

Flash Address[7]/Clock Enable.

as the Flash Address[7] output si

the PCI RST# si

FLA[16]/CLK25 output si

a pull-up resistor

FLA[16]/CLK25 output; otherwise, it is used as FLA[16] output.

Flash Address[6:2].

to support 128 Kb

Flash Address[1]/Auxiliary Power.

Flash Address[1] output si

low), it acts as the power supply indicator. If the 82559ER is fed

active

PCI power, this pin should be connected to a pull-down resistor; if the

82559ER is fed b

pull-up resistor.

Flash Address [0].

nal during nominal operation.

si

EEPROM Chip Select.

assert chip select to the serial EEPROM.

Flash Chip Select.

Flash.

Flash Output Enable.

read) to the Flash memory.

control

Flash Write Enable.

control to the Flash memor

nal.

These pins are used as Flash address outputs

te Flash addressing.

This is a multiplexed pin and acts

nal is active, this pin acts as input control over the

Ω

3.3 K

These pins are used as Flash address outputs

te Flash addressing.

auxiliary power, this pin should be connected to a

This pin acts as the Flash Address[0] output

The EEPROM Chip Select si

The Flash Chip Select si

This pin provides an active low output enable

This pin provides an active low write enable

nal during nominal operation. When

nal. If the FLA[7]/CLKEN pin is connected to

, a 25 MHz clock signal is provided on the

This multiplexed pin acts as the

nal during nominal operation. When RST is

.

Flash accesses,

nal.

nal is used to

nal is active during

3.4 Testability Port Signals

Symbol Type Name and Function

If this input pin is hi

TEST IN

TCK IN

TI IN

TEXEC IN

TO OUT

10

Test.

nominal operation this pin should be connected to a pull-down

Durin

resistor.

Testability Port Clock.

nal.

si

Testability Port Data Input.

Data Input si

Testability Port Execute Enable.

Port Execute Enable si

Testability Port Data Output.

Data Output si

nal.

h, the 82559ER will enable the test port.

This pin is used for the Testabilit

This pin is used for the Testabil it

This pin is used for the Testabilit

nal.

This pin is used for the Testabilit

nal.

Port Clock

Port

Port

Datasheet

Page 17

g

3.5 PHY Signals

y

g

y

y

(

y

y

g

(

(

g

(

g

y

y

y

g

g

g

q

g

g

q

g

g

Symbol Type Name and Function

X1 A/I

X2 A/O

TDP

TDN

RDP

RDN

ACTLED# OUT

LILED# OUT

SPEEDLED# OUT

RBIAS100 B

RBIAS10 B

VREF B

A/O

A/I

Networkin

Crystal Input One.

stal. Otherwise, X1 may be driven by an external metal-oxide

MHz cr

semiconductor

Crystal Input Two.

stal. Otherwise, X1 may be driven by an external MOS level

MHz cr

25 MHz oscillator when X2 is left floatin

Analog Twisted Pair Ethernet Transmit Differential Pair.

pins transmit the serial bit stream for transmission on the Unshielded

Twisted Pair

two-level

on the mode of operation. These si

isolation transformer.

Analog Twisted Pair Ethernet Receive Differential Pair.

receive the serial bit stream from the isolation transformer. The bit

stream can be two-level

si

Activity LED.

activit

activit

Link Integrity LED.

If the link is valid in either 10 or 100 Mbps, the LED is on; if link is

invalid, the LED is off.

Speed LED.

will be on at 100 Mbps and off at 10 Mbps .

Reference Bias Resistor (100 Mbps).

envelope of the 82559ERER when transmittin

via the use of a pull-down resistor to

down resistor is ade

Reference Bias Resistor (10 Mbps).

envelope of the 82559ER when transmittin

the use of a pull-down resistor to

resistor is ade

Voltage Reference.

volta

source, this pin should be left floatin

10BASE-T) or three-level (100BASE-TX) signals depending

nals depending on the mode of operation.

. When activity is present, the activity LED is on; when no

is present, the activity LED is off.

e reference generator. To use the internal voltage reference

X1 and X2 can be driven b

MOS) level 25 MHz oscillator when X2 is left floating.

X1 and X2 can be driven b

UTP) cable. The current-driven differential driver can be

nals interface directly with an

10BASE-T) or three-level (100BASE-TX)

The Activit

The Speed LED pin indicates the speed. The speed LED

uate is most applications.

LED pin indicates either transmit or receive

The Link Inte

uate is most applications.

This pin is connected to a 1.25 V ± 1% external

rity LED pin indicates link integrity.

This pin controls the out

round. A value of 619 Ω pull-

This pin controls the out

round. A value of 549 Ω pull-down

.

Silicon —GD82559ER

an external 3.3 V 25

an external 3.3 V 25

.

These

These pins

in the 10 Mbps mode

in the 10 Mbps mode via

619 Ω and 549 Ω for the RBIAS100 and RBIAS10, respectivel

NOTE:

should be fine tuned for various desi

ns.

Datasheet

, are only a recommended values and

11

Page 18

GD82559ER — Networking Silicon

12

Datasheet

Page 19

Networkin

g

g

y

g

g

g

y

y

Silicon — GD82559ER

4. GD82559ER Media Access Control Functional

Description

4.1 82559ER Initialization

The 82559ER has four sources for initialization. They are listed according to their precedence:

1. ALTRST# Signal

2. PCI RST# Signal

3. Software Reset (Software Command)

4. Selective Reset (Software Command)

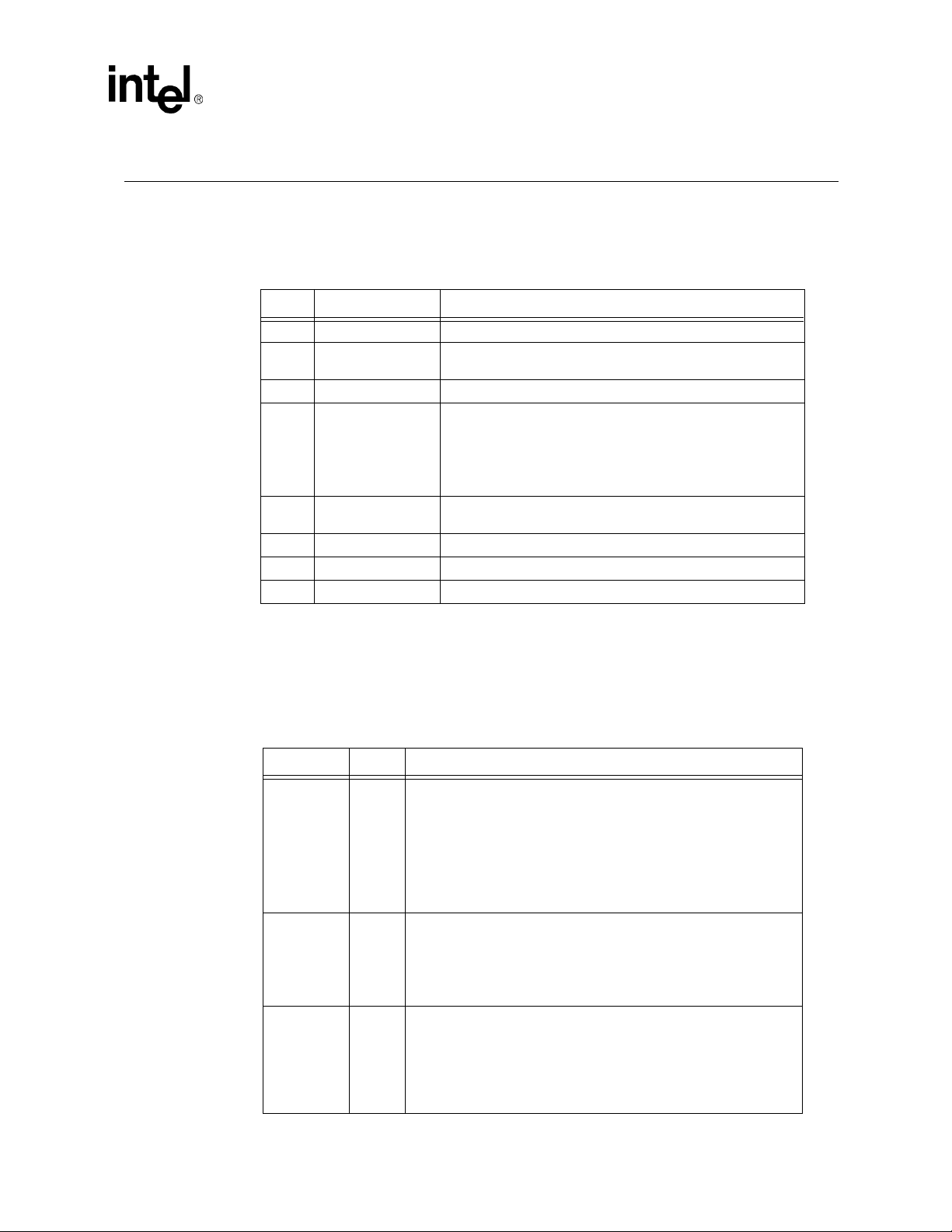

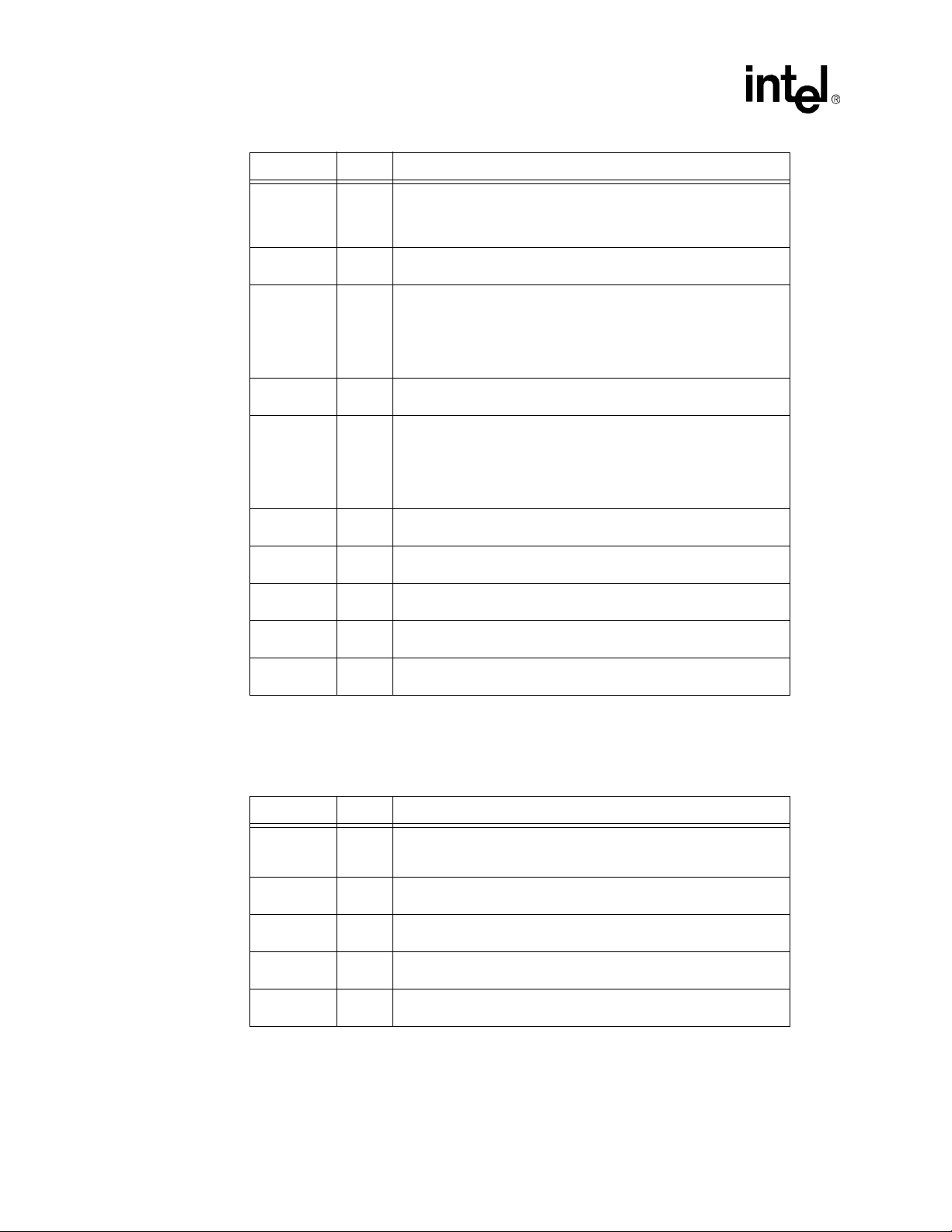

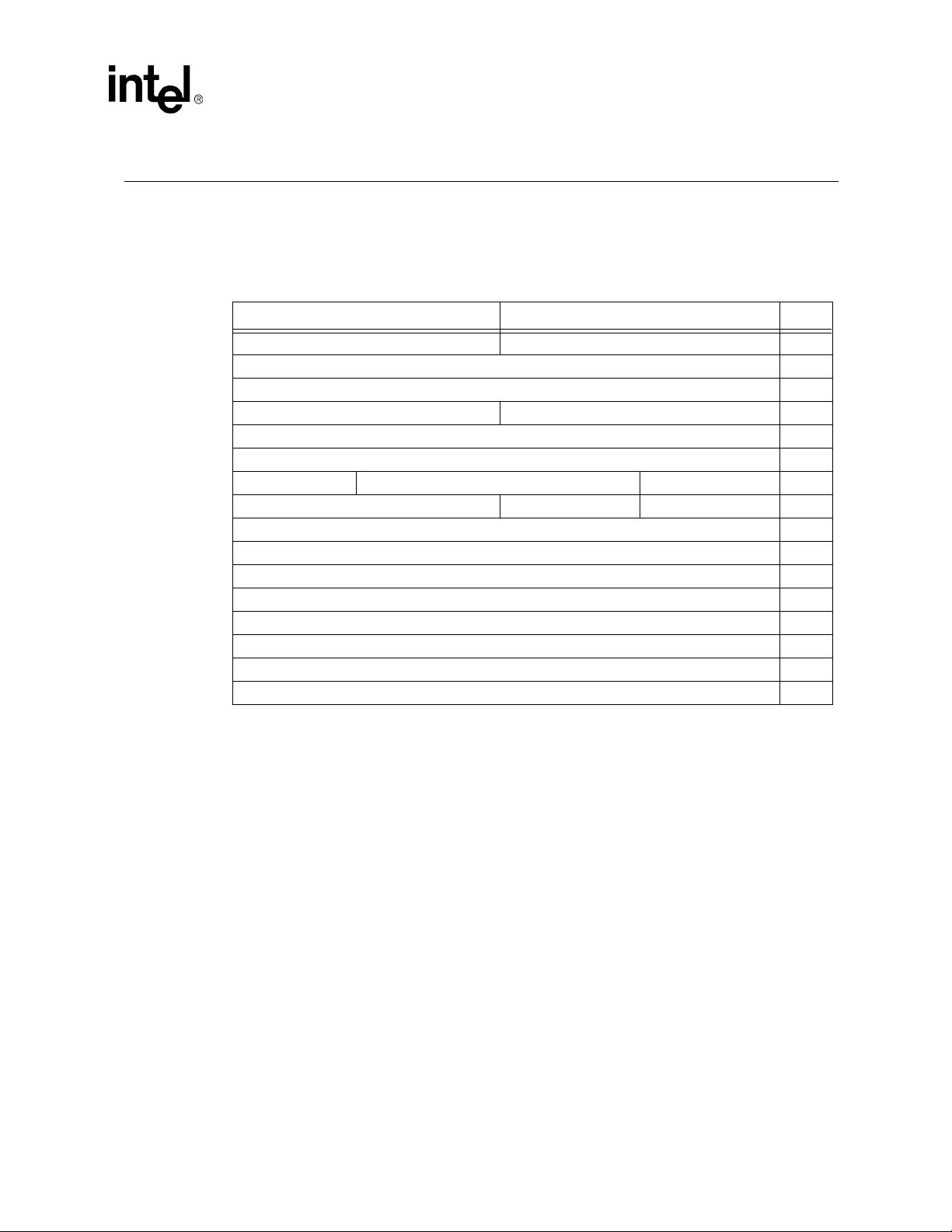

4.1.1 Initialization Effects on 82559ER Units

The following table shows the effect of each of the different initialization sources on major

portions of the 82559ER. The initialization sources are listed in order of precedence. For example,

any resource that is initialized by the Software Reset is also initialized by the D3 to D0 transition

and ALTRST# and PCI RST# but not necessarily by the selective reset.

EEPROM read and

initialization

Loadable microcode

decoded/reset

MAC confi

multicast hash

Memor

mircomachine state reset

PCI Confi

reset

PHY confi

Power mana

reset

Statistic counters reset

uration reset and

pointers and

uration register

uration reset

ement event

ALTRST# PCI RST#

333

33

33333

33

3333

33

Clear onl

3

33

if no

auxiliar

power

present

ISOLATE#D3 to D0

--

--

-- -- -- --

-- -- -- --

--

Transition

-- -- --

33

333

33

Software

Reset

-- --

Selective

Reset

--

--

--

Datasheet

13

Page 20

GD82559ER — Networking Silicon

4.2 PCI Interface

4.2.1 82559ER Bus Operations

After configuration, the 82559ER is ready for normal operation. As a Fast Ethernet controller, the

role of the 82559ER is to access transmitted data or deposit received data. In both cases the

82559ER, as a bus master device, will initiate memory cycles via the PCI bus to fetch or deposit

the required data.

To perform these actions, the 82559ER is controlled and examined by the CPU via its control and

status structures and registers. Some of these control and status structures reside in the 82559ER

and some reside in system memory. For access to the 82559ER’s Control/Status Registers (CSR),

the 82559ER acts as a slave (in other words, a target device). The 82559ER serves as a slave also

while the CPU accesses its 128 Kbyte Flash buffer or its EEPROM. Section 4.2.1.1 describes the

82559ER slave operati o n. It is followed by a description of the 82559E R o perat ion as a bus master

(initiator) in Section 4.2.1.2, “82559ER Bus Master Operation” on page 18.

4.2.1.1 82559ER Bus Slave Operation

The 82559ER serves as a target device in one of the following cases:

•

CPU accesses to the 82559ER System Control Block (SCB) Control/Status Registers (CSR)

•

CPU accesses to the EEPROM through its CSR

•

CPU accesses to the 82559ER PORT address via the CSR

•

CPU accesses to the MDI control register in the CSR

•

CPU accesses to the Flash control register in the CSR

•

CPU accesses to the 128 Kbyte Flash

The CSR and the Flash buffer are considered by the 82559ER as two totally separated memory

spaces. The 82559ER provides separate Base Address Registers (BAR s) in the configu ration space

to distinguish between them. The size of the CSR memory space is 4 Kbyte in the memory space

and 64 bytes in the I/O space. The 82559ER treats accesses to these memory spaces differently.

4.2.1.1.1 Control/Status Register (CSR) Accesses

The 82559ER supports zero wait-state single-cycle memory or I/O-mapped accesses to its CSR

space. Separate BARs request 4 Kbytes of memory space and 64 bytes of I/O space to accomplish

this. Based on its needs, the software driver will use either memory or I/O mapping to access these

registers. The 4 Kbytes of CSR space the 82559ER requests include the following elements:

•

System Control Block (SCB) reg isters

•

PORT register

•

Flash control register

•

EEPROM control register

•

MDI control register

•

Flow control registers

14

Datasheet

Page 21

Networkin

g

g

g

Silicon — GD82559ER

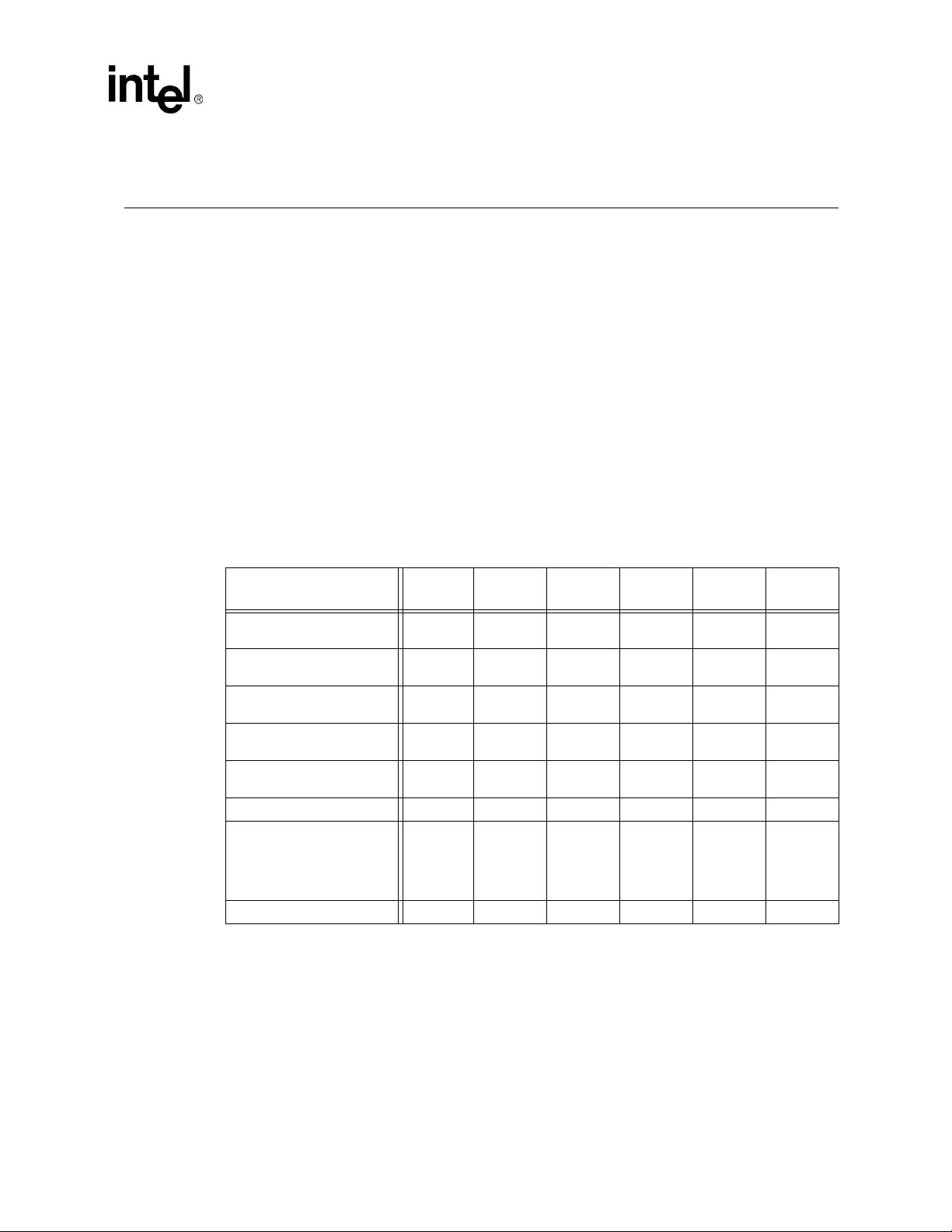

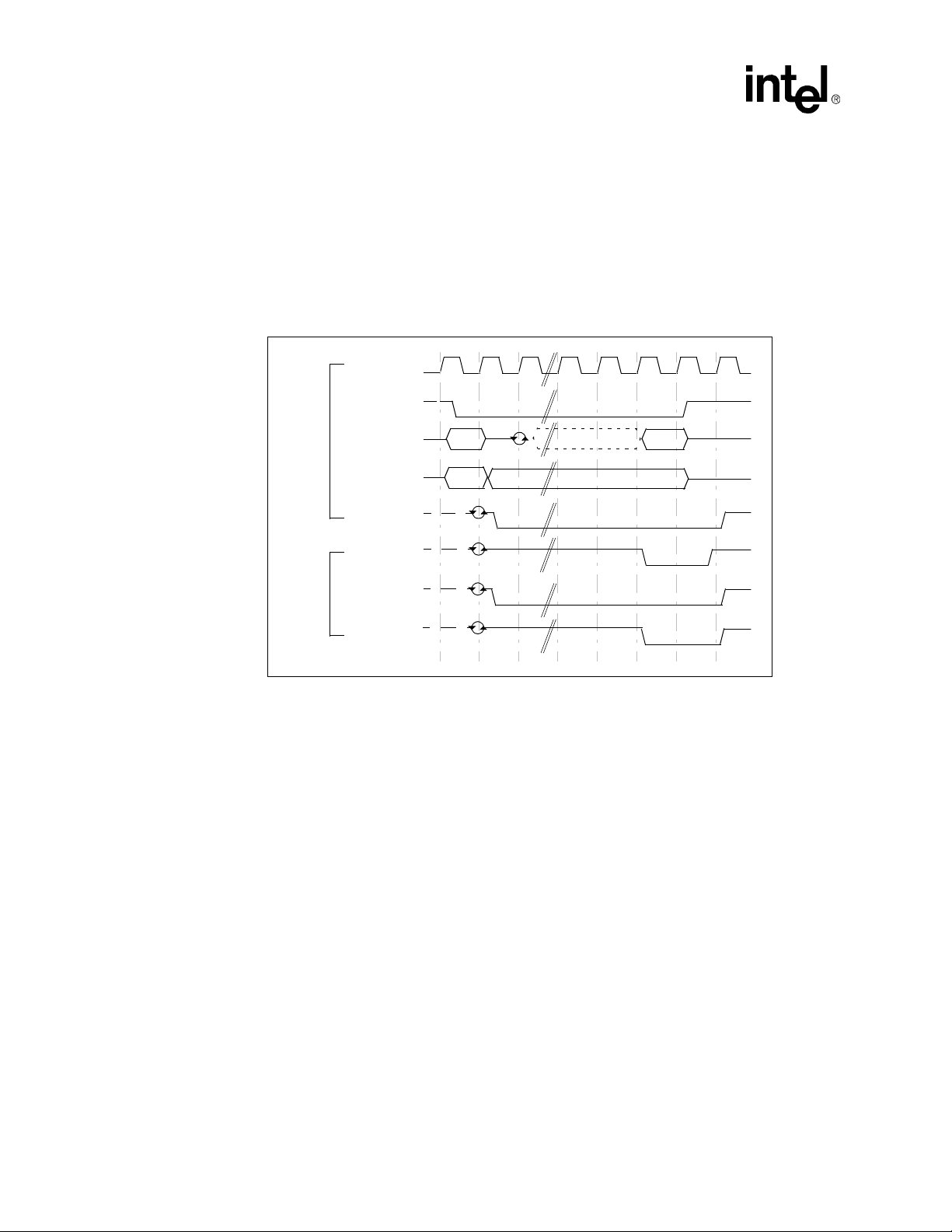

The figures below show CSR zero wait-state I/O read and write cycles. In the case of accessing the

Control/Status Registers, the CPU is the initiator and the 82559ER is the target of the transaction.

SYSTEM

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR

I/O RD BE#

3421 56789

DATA

82559ER

STOP#

Fi

ure 2. CSR I/O Read Cycle

Read Accesses:

The CPU, as the initiator, drives address lines AD[31:0], the command and byte

enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. As a slave, the 82559ER

controls the TRDY# signal and provides valid data on each data access. The 82559ER allows the

CPU to issue only one read cycle when it accesses the Control/Status Registers, generating a

disconnect by asserting the STOP# signal. The CPU can insert wait states by de-asserting IRDY#

when it is not ready.

SYSTEM

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR DATA

I/O WR BE#

3421 56789

82559ER

STOP#

Fi

ure 3. CSR I/O Write Cycle

Write Accesses:

The CPU, as the initiator, drives the address lines AD[31:0], the command and

byte enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. It also provides the

82559ER with valid data on each data access immediately after asserting IRDY#. The 82559ER

Datasheet

15

Page 22

GD82559ER — Networking Silicon

g

controls the TRDY# signal and asserts it from the data access. The 82559ER allows the CPU to

issue only one I/O write cycle to the Control/Status Registers, generating a disconnect by asserting

the STOP# signal. This is true for both memory mapped and I/O mapped accesses.

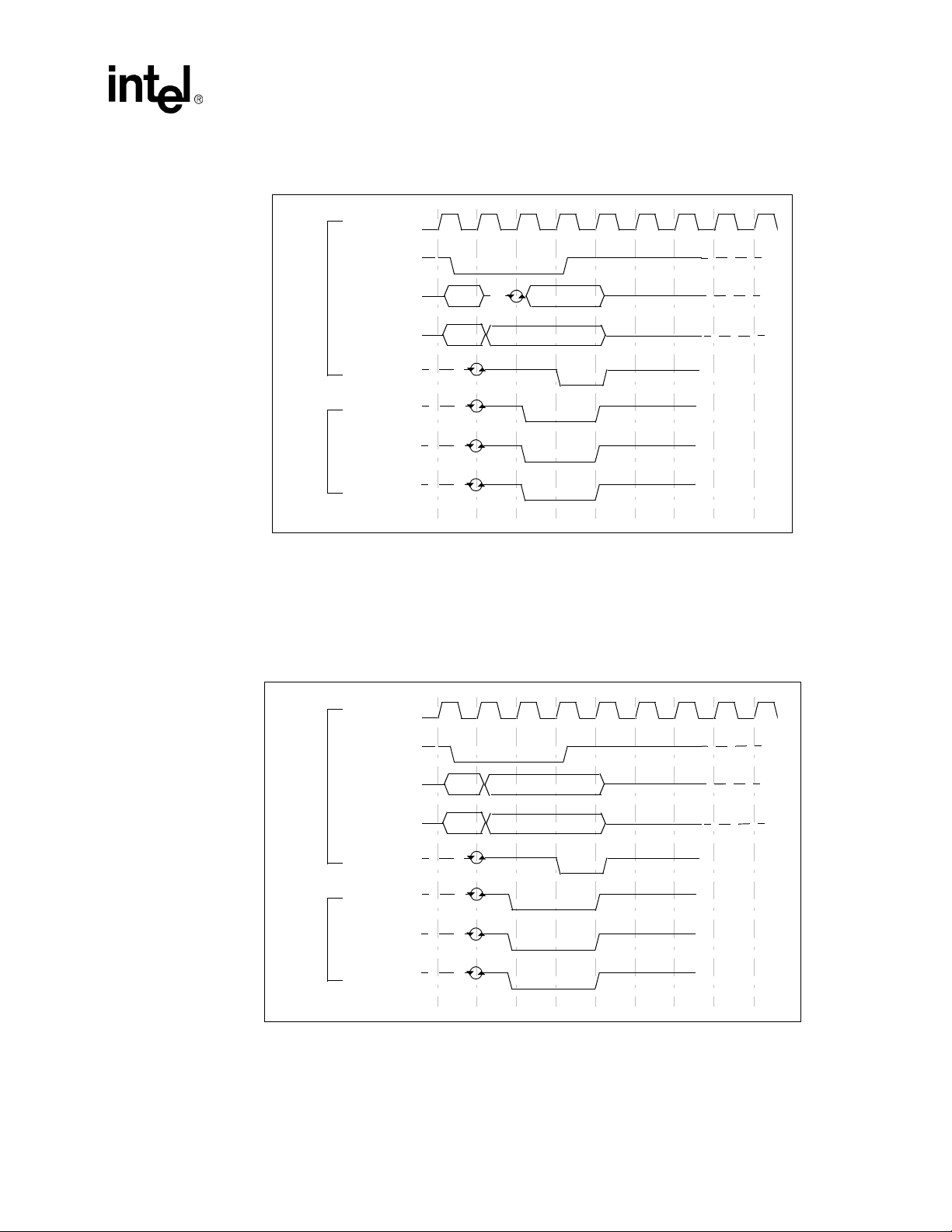

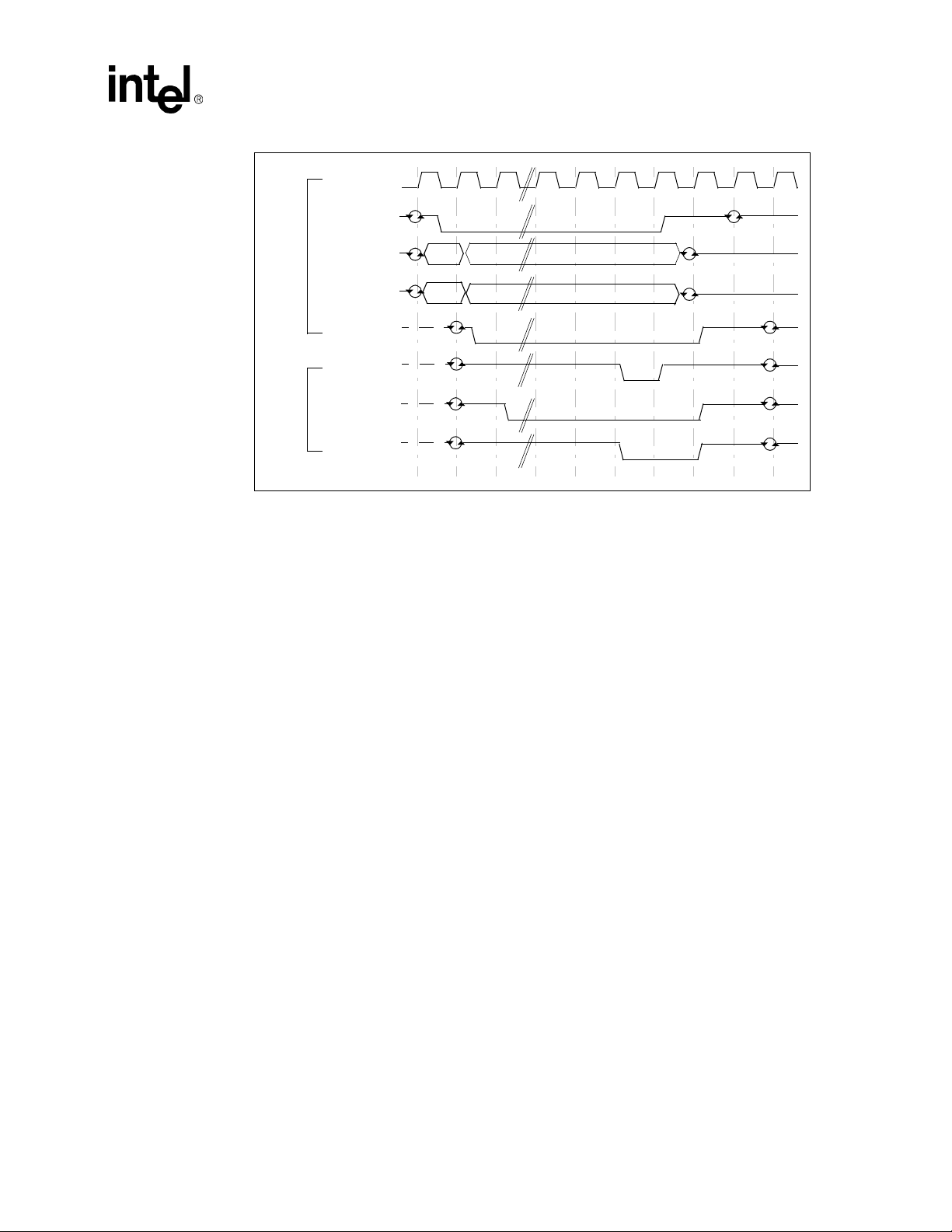

4.2.1.1.2 Flash Buffer Accesses

The CPU accesses to the Flash buffer are very slow. For this reason the 82559ER issues a targetdisconnect at the first data access. The 82559ER asserts the STOP# signal to indicate a targetdisconnect. The figures below illustrate memory CPU read and write accesses to the 128 Kbyte

Flash buffer. The longest burst cycle to the Flash buffer contains one data access only.

CLK

FRAME#

SYSTEM

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR DATA

MEM RD BE#

82559ER

STOP#

ure 4. Flash Buffer Read Cycle

Fi

Read Accesses:

The CPU, as the initiator, drives the address lines AD[31:0], the command and

byte enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. The 82559ER controls

the TRDY# signal and de-asserts it for a certain number of clocks until valid data can be read from

the Flash buffer. When TRDY# is asserted, the 82559ER drives valid data on the AD[31:0] lines.

The CPU can also insert wait states by de-asserting IRDY# until it is ready. Flash buffer read

accesses can be byte or word length.

16

Datasheet

Page 23

g

g

CLK

FRAME#

Networkin

Silicon — GD82559ER

SYSTEM

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

ADDR

MEM WR BE#

DATA

82559ER

STOP#

Fi

ure 5. Flash Buffer Write Cycle

Write Accesses:

byte enable lines

The CPU, as the initiator, drives the address lines

C/BE#[3:0] and

the control lines

IRDY#

82559ER with valid data immediately after asserting

and

IRDY#

FRAME#

AD[31:0],

. It also provides the

the command and

. The 82559ER controls the

TRDY#

signal and de-asserts it for a certain number of clocks until valid data is written to the Flash buffer.

By asserting

TRDY#

, the 82559ER signals the CPU that the current data access has completed.

Flash buffer write accesses can be byte length only.

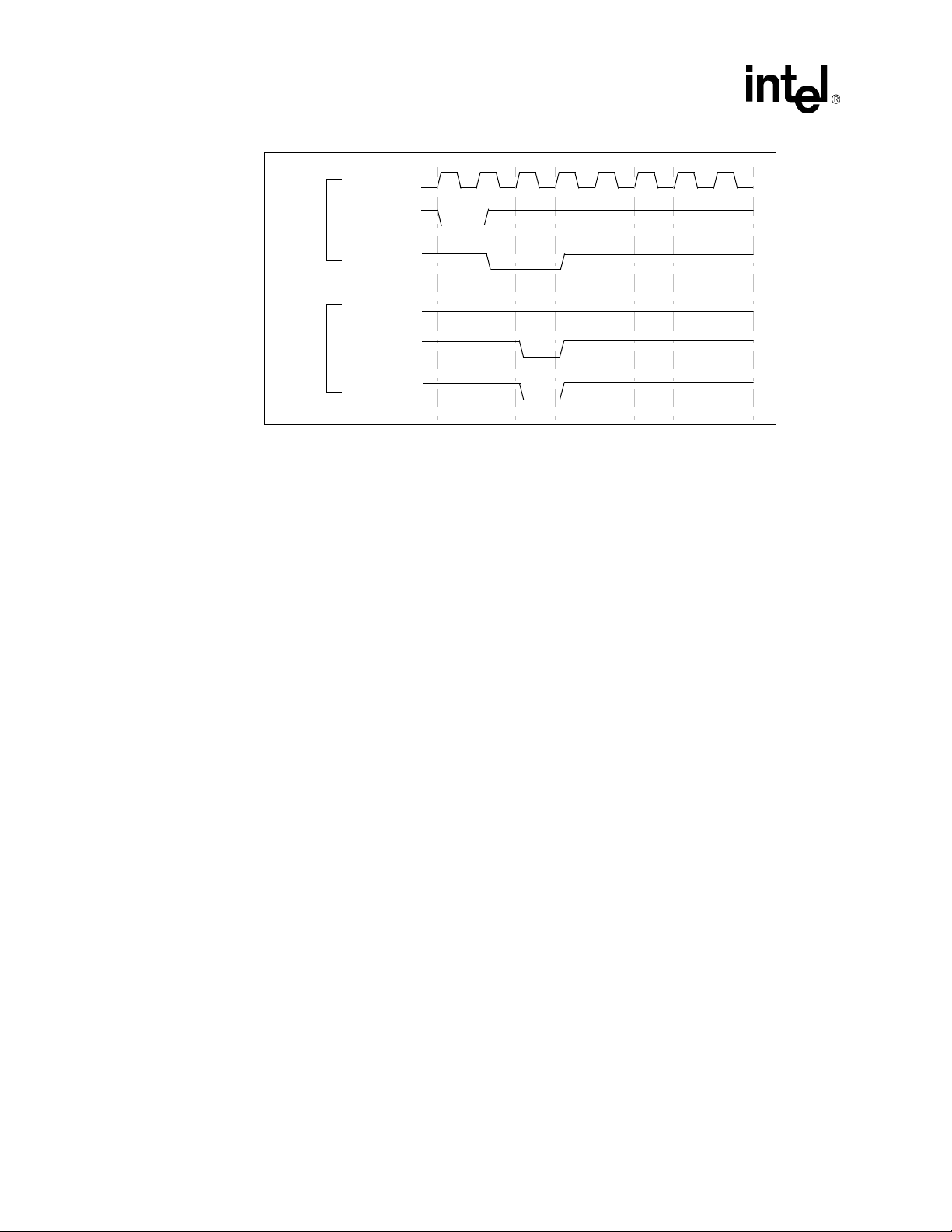

4.2.1.1.3 Retry Premature Accesses

The 82559ER responds with a Retry to any configuration cycle accessing the 82559ER before the

completion of the automatic read of the EEPROM. The 82559ER m a y continue to Retry any

configuration accesses until the EEPROM read is complete. The 82559ER does not enforce the

rule that the retried master must attempt to access the same address again to complete any delayed

transaction. Any master access to the 82559ER after the completion of the EEPROM read will be

honored. Figure 6 depicts the operation of a Retry cycle.

Datasheet

17

Page 24

GD82559ER — Networking Silicon

g

g

SYSTEM

82559ER

CLK

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

ure 6. PCI Retry Cycle

Fi

Note:

The 82559ER is considered the target in the above diagram; thus, TRDY# is not asserted.

4.2.1.1.4 Error Handlin

Data Parity Errors:

transaction. If an error was detected, the 82559ER always sets the Detected Parity Error bit in the

PCI Configuration Status register, bit 15. The 82559ER also asserts PERR#, if the Parity Error

Response bit is set (PCI Co nfigu ration Com mand regis ter, bit 6). The 82559ER does not attempt to

terminate a cycle in which a parity error was detected. This gives the initiator the option of

recovery.

Target-Disconnect:

•

After accesses to the Flash buffer

•

After accesses to its CSR

•

After accesses to the configuration space

System Error:

the SERR# Enable bit in the PCI Configuration Command register or the Parity Error Response bit

are not set, the 82559ER only sets the Detected Parity Error bit (PCI Configuration Status register,

bit 15). If SERR# Enable and Parity Error Response bits are both set, the 82559ER sets the

Signaled System Error bit (PCI Configuration Status register, bit 14) as well as the Detected Parity

Error bit and asserts SERR# fo r one clock.

The 82559ER, when detecting system error, will claim the cycle if it was the target of the

transaction and continue the transaction as if the address was correct.

The 82559ER checks for data parity errors while it is the target of the

The 82559ER prematurely terminate a cycle in the following cases:

The 82559ER reports pari ty error duri ng t he address phase usi ng th e SERR # pin. If

Note:

The 82559ER will report a system error for any parity error during an address phase, whether or

not it is involved in the current transaction.

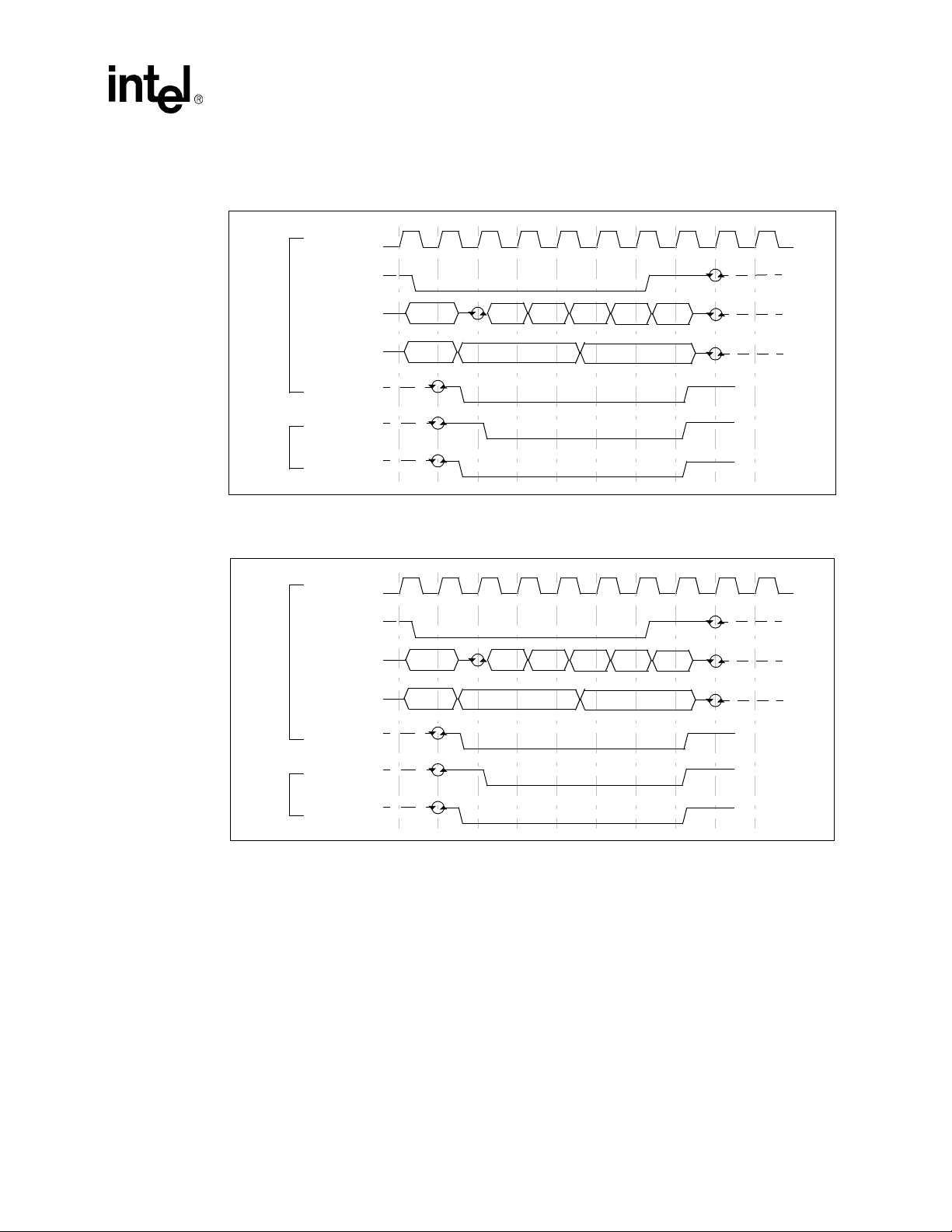

4.2.1.2 82559ER Bus Master Operation

As a PCI Bus Master, the 82559ER initiates memory cycles to fetch data for transmission or

deposit received data and for accessing the memory resident control structures. The 82559ER

performs zero wait state burst read and write cycles to the host main memory. Figure 7 and Figure

18

Datasheet

Page 25

Networkin

g

g

g

Silicon — GD82559ER

8 depict memory read and write burst cycles. For bus master cycles, the 82559ER is the initiator

and the host main memory (or the PCI host bridge, depending on the configuration of the system) is

the target.

82559ERSYSTEM

82559ERSYSTEM

CLK

FRAME#

AD

C/BE#

IRDY#

TRDY#

DEVSEL#

CLK

FRAME#

AD

3421 5678910

ADDR

MR BE# BE#

ADDR

DATA

DATA

DATA

DATA

Fi

ure 7. Memory Read Burst Cycle

3421 5678910

DATA

DATA

DATA

DATA

DATA

DATA

C/BE#

MW BE# BE#

IRDY#

TRDY#

DEVSEL#

Fi

ure 8. Memory Write Burst Cycle

The CPU provides the 82559ER with action commands and pointers to the data buffers that reside

in host main memory. The 82559ER independently manages these structures and initiates burst

memory cycles to transfer data to and from them. The 82559ER uses the Memory Read Multiple

(MR Multiple) command for burst accesses to data buffers and the Memory Read Line (MR Line)

command for burst accesses to control structures. For all write accesses to the control structure, the

82559ER uses the Memory Write (MW) command. For write accesses to data structure, the

82559ER may use either the Memory Write or Memory Write and Invalidate (MWI) commands.

Read Accesses:

The 82559ER performs block transfers from host system memory to perform

frame transmission on the serial link. In this case, the 82559ER initiates zero wait state memory

read burst cycles for these accesses. The length of a burst is bounded by the system and the

82559ER’s internal FIFO. The length of a read burst may also be bounded by the value of the

Transmit DMA Maximum Byte Count in the Configure command. The Transmit DMA Maximum

Datasheet

19

Page 26

GD82559ER — Networking Silicon

Byte Count value indicates the maximum number of transmit DMA PCI cycles that will be

completed after an 82559ER internal arbitration. (Details on the Configure command are described

Software Developer’s Manual

in the

The 82559ER, as the initiator, drives the address lines AD[31:0], the command and byte enable

lines C/BE#[3:0] and the control lines IRDY# and FRAME#. The 82559ER asserts IRDY# to

support zero wait state burst cycles. The target signals the 82559ER that valid data is ready to be

read by asserting the TRDY# signal.

.)

Write Accesses:

reception. In this case, the 82559ER in itiates memory write burst cycles to deposit the data, usually

without wait states. The length of a burst is bounded by the system and the 82559ER’s internal

FIFO threshold. The length of a write burst m ay also be bo unded by the value of th e Receive DMA

Maximum Byte Count in the Configure command. The Receive DMA Maximum Byte Count value

indicates the maximum number of receive DMA PCI transfers that will be completed before the

82559ER internal arbitration. (Details on the Configure command are described in the

Developer’s Manual

The 82559ER, as the initiator, drives the address lines AD[31:0], the command and byte enable

lines C/BE#[3:0] and the control lines IRDY# and FRAME#. The 82559ER asserts IRDY# to

support zero wait state burst cycles. The 82559ER also drives valid data on AD[31:0] lines during

each data phase (from the first clock and on ). The target controls the length and signals completion

of a data phase by de-assertion and assertion of TRDY#.

Cycle Completion:

following cases:

Normal Complet i on

•

(for example, host main memory).

Backoff

•

82559ER by the arbiter, indicating that the 82559ER has been preempted by another bus

master.

Transmit or Receive DMA Maximum Byte Count

•

length specified in the Transmit or Receive DMA Maximum Byte Count field in the Configure

command block. (Details relating to this field and the Configure command are described in the

Software Dev eloper’s Manual

Target Termination

•

disconnect, target-retry, or target-abort. In the first two cases, the 82559ER initiates the cycle

again. In the case of a target-abort, the 82559ER sets the Received Target-Abort bit in the PCI

Configuration Status field (PCI Configuration Status register, bit 12) and does not re-initiate

the cycle.

Master Abort

•

82559ER (in other words, DEVSEL# has not been asserted). The 82559ER simply de-asserts

FRAME# and IRDY# as in the case of normal completion.

Error Condition

•

completes its current initiated transaction. Any further action taken by the 82559ER depends

on the type of error and other conditions.

The 82559ER performs block transfers to host system memory during frame

Software

.)

The 82559ER completes (terminates) its initiated memory burst cycles in the

: All transaction data has been transferred to or from the target device

: Latency Timer has expi red and the bus grant signal (GNT#) was removed from the

: The 82559ER burst has reached the

.)

: The target may request to terminate the transaction with a target-

: The target of the transaction has not responded to the address initiated by the

: In the event of parity or any other system error detection, the 82559ER

20

4.2.1.2.1 Memory Write and Invalidate

The 82559ER has four Direct Memory Access (DMA) channels. Of these four channels, the

Receive DMA is used to deposit the large number of data bytes received from the link into system

memory. The Receive DMA uses both the Memory Write (MW) and the Memory Write and

Invalidate (MWI) commands. To use MWI, the 82559ER must guarantee the following:

Datasheet

Page 27

Networkin

g

1. Minimum transfer of one cache line

2. Active byte enable bits (or BE#[3:0] are all low) during MWI access

3. The 82559ER may cross the cache line boundary only if it intends to transfer the next cache

line too.

To ensure the above conditions, the 82559ER may use the MWI command only if the following

conditions hold:

1. The Cache Line Size (CLS) written in the CLS register during PCI configuration is 8 or 16

Dwords.

2. The accessed address is cache line aligned.

3. The 82559ER has at least 8 or 16 Dwords of data in its receive FIFO.

4. There are at least 8 or 16 Dwords of data space left in the system memory buffer.

5. The MWI Enable bit in the PCI Configuration Co mman d register, bit 4, should is set to 1b.

6. The MWI Enable bit in the 82559ER Config ure command should is set to 1b. (Details on the

Configure command are described in the

If any one of the above conditions does not hold, the 8 2559ER will use the MW command. If a

MWI cycle has started and one of the conditions is no longer valid (for example, the data space in

the memory buffer is now less than CLS), then the 82559ER terminates the MWI cycle at the end

of the cache line. The next cycle will be either a MW or MWI cycle depending on the conditions

listed above.

Software Developer’s Manual

Silicon — GD82559ER

.)

If the 82559ER started a MW cycle and reached a cache line boundary, it either continues or

terminates the cycle depending on the Terminate Write on Cache Line configuration bit of the

82559ER Configure command (byte 3, bit 3). If this bit is set, the 82559ER terminates the MW

cycle and attempts to start a new cycle. The new cycle is a MWI cycle if this bit is set and all of the

above listed conditions are met. If the bit is not set, the 82559ER continues the MW cycle across

the cache line boundary if required. (Details on the Configure command are described in the

Software Developer’s Manual

.)

4.2.1.2.2 Read Align

The Read Align feature enhances the 82559ER’s performance in cache line oriented systems. In

these particular systems, starting a PCI transaction on a non-cache line aligned address may cause

low performance.

T o resolve this performance anomaly, the 82559ER attempts to terminate transmit DMA cycles on

a cache line boundary and start the next transaction on a cache line aligned address. This feature is

enabled when the Read Align Enable bit is set in the 82559ER Configure command (by te 3 , bit 2).

(Details on the Configure command are described in the

If this bit is set, the 82559ER operates as follows:

•

When the 82559ER is almost out of resources on the transmit DMA (that is, the transmit FIFO

is almost full), it attempts to terminate the read transaction on the nearest cache line boundary

when possible.

•

When the arbitration counter’s feature is enabled (in other words, the Transmit DMA

Maximum Byte Count value is set in the Configure command), the 82559ER switches to other

pending DMAs on the cache line boundary only.

Software Developer’s Manual

.)

Datasheet

Note the following:

21

Page 28

GD82559ER — Networking Silicon

g

•

This feature is not recommended for use in non-cache line oriented systems since it may cause

shorter bursts and lower performance.

•

This feature should be used only when the CLS register in PCI Configuration space is set to 8

or 16 Dwords.

•

The 82559ER reads all control data structures (including Receive Buffer Descriptors) fr om the

first Dword (even if it is not required) to maintain cache line alignment.

4.2.1.2.3 Error Handlin

Data Parity Errors:

during a transaction. If the Parity Error Response bit is set (P CI Configuration Command register,

bit 6), the 82559ER also asserts PERR# and sets the D a ta Parity Detected bit (PCI Configuration

Status register, bit 8). In addition, if the error was detected by the 82559ER during read cycles, it

sets the Detected Parity Error bit (PCI Configuration Status register, bit 15).

4.2.2 Clockrun Signal

The CLKRUN# signal is used to control the PCI clock as defined in the PCI Mobile design guide

and is compliant with the PCI Mobile design guide. The Clockrun signal is an open drain I/O

signal. It is used as a bidirectional channel between the host and the devices.

•

The host de-asserts the CLKRUN# signal to indicate that the PCI clock is about to be stopped

or slowed down to a non-operational frequency.

•

The host asserts the CLKRUN# signal when the interface clock is either running at a normal

operating frequency or about to be started.

•

The 82559ER asserts the CLKRUN# signal to indicate that it needs the PCI clock to prevent

the host from stopping the PCI clock or to request that the host restore the clock if it was

previously stopped.

Proper operation requires that the system latency from the nominal PCI CLK to CLKRUN#

assertion should be less than 0.5 µs. If the system latency is longer than 0.5 µs, the occurrence of

receive overruns increases. For use in these types of systems, the Clockrun functionality should be

disabled (see Section 8.1.12, “General Control Register” on page 61). In this case, the 82559ER

will claim the PCI clock even during idle time. If the CLKRUN# signal is not used , it sh ould be

connected to a pull-down resistor (62KΩ). The value of the resistor selected is dependent on the

ND-TREE set-up used (i.e. the test fixture must be able to overdrive pull-down).

As an initiator, the 82559ER checks and detects data parity errors that occur

4.2.3 Power Management Event Signal

The 82559ER supports power management indications in the PCI mode. The PME# output pin

provides an indication of a power management event to the system. PCI Power Management

In addition to the base functionality of the 82558 B-step, the 82559 family supports a larger set of

wake-up packets and the capability to wake th e sy stem on a link status change from a low power

state. The 82559ER enables the host system to be in a sleep state and remain virtually connected to

the network. After a power management event or link status change is detected, the 82559ER will

wake the host system. The sections below describe these events, the 82559ER power states, and

estimated power consumption at each power state.

22

Datasheet

Page 29

g

4.2.4 Pow er States

The 82559ER’s power management register implements all four power states as defined in the

Power Management Network Device Class Reference Specification, Revision 1.0. The four states,

D0 through D3, vary from maximum power consumption at D0 to the minimum power

consumption at D3. PCI transactions are only allowed in the D0 state, except for host accesses to

the 82559ER’s PCI configuration registers. The D1 and D2 power management states enable

intermediate power savings while providing the system wake-up capabilities. In the D3

the 82559ER can provide wake-up capabilities only if auxiliary power is supplied. Wake-up

indications from the 82559ER are provided by the Power Management Event (PME#).

4.2.4.1 D0 Power State

As defined in the Network Device Class Reference Specification , the dev ice is fully functional in

the D0 power state. In this state, the 82559ER receives full power and should be providing full

functionality. In the 82559ER the D0 state is partitioned into two substates, D0 Uninitialized (D0u)

and D0 Active (D0a).

D0u is the 82559ER’s initial power state following a PCI RST#. While in the D0u state, the

82559ER has PCI slave functionality to support its initialization by the host and supports wake up

events. Initialization of the CSR, Memory, or I/O Base Address Registers in the PCI Configuration

space switches the 82559ER from the D0u state to the D0a state.

Networkin

Silicon — GD82559ER

state,

cold

In the D0a state, the 82559ER provides its full functionality and consumes its nominal power. In

addition, the 82559ER supports wake on link status change (see Section 4.2.5, “Wake-up Events”

on page 27). While it is activ e, the 825 59E R requires a nominal P CI cloc k signal (in oth er word s, a

clock frequency greater than 16 MHz) for proper operation. During idle time, the 82559ER

supports a PCI clock signal suspension using the Clockrun signal mechanism. The 82559ER

supports a dynamic standby mode. In this mode, the 82559ER is able to save almost as much

power as it does in the static power-down states. The trans ition to or from standby is done

dynamically by the 82559ER and is transparent to the software.

4.2.4.2 D1 Power State

In order for a device to meet the D1 power state requirements, as specified in the Advanced

Configuration and Power Interface (ACPI) Specification, Revision 1.0, it must not allow bus

transmission or interrupts; however, bus reception is allowed. Therefore, device context may be

lost and the 82559ER does not initiate any PCI activity. In this state, the 82559ER responds only to

PCI accesses to its configuration space and system wake-up events.

The 82559ER retains link integrity and monitors the link for any wake-up events such as wake-up

packets or link status change. Following a wake-up ev ent, the 82559ER asserts the PME# signal to

alert the PCI based system.

4.2.4.3 D2 Power State

The ACPI D2 power state is similar in functionality to the D1 power state. If the bu s is in the B2

state, the 82559ER will consume less current than it does in the D1 state. In addition to D1

functionality, the 82559ER can provide a lower power mode with wake-on-link status change

capability. The 82559ER may enter this mode if the link is down while the 82559ER is in the D2

state. In this state, the 82559ER monitors the link fo r a transitio n from an invalid link to a valid

link. The 82559ER will not attempt to keep the link alive by transmitting idle symbols or link

integrity pulses.

configuration bit in the Power Management Driver Register (PMDR).

1

The sub-10 mA state due to an invalid link can be enabled or disabled by a

Datasheet

23

Page 30

GD82559ER — Networking Silicon

4.2.4.4 D3 Power State

In the D3 power state, the 82559ER has the same capabilities and consumes the same amount of

power as it does in the D2 state. However, it enables the PCI system to be in the B3 state. If the PCI

system is in the B3 state (in other words , no PCI power is present ), the 825 59ER pro vides wake-up

capabilities if it is connected to an auxiliary power source in the system. If PME is disabled, the

82559ER does not provide wake-up capability or maintain link integrity. In this mode the 82559ER

consumes its minimal power.

The 82559ER enables a system to be in a sub-5 watt state (low power state) and still be virtually

connected. More specifically, the 82559ER supports full wake-up capabilities while it is in the

D3

state. The 82559ER can be connected to an auxiliary power source (V

cold

to provide wake-up functionality while the PCI power is off. The typical current consumption of

the 82559ER is 125 mA at 3.3 V. Thus, a dual power plane is not required. If connected to an

auxiliary power source, the 82559ER receives all of its power from the auxiliary source in all

power states.

4.2.4.5 Understanding Power Requirements

When running the 82559ER off a 3.3V_standby power source, the actual power consumption will

scale with network traffic. In other words, if the 82559ER is monitoring the network for ACPI

“Interesting Packets” only the PCI bus specific circuitry will be disabled. As an a example the

8259ER will typically draw approximately 120mA, in D1-D3 under a full Ethernet load. In the D0

state, the 82559ER will typically consume 125mA under the same load conditions.

), which enables it

AUX

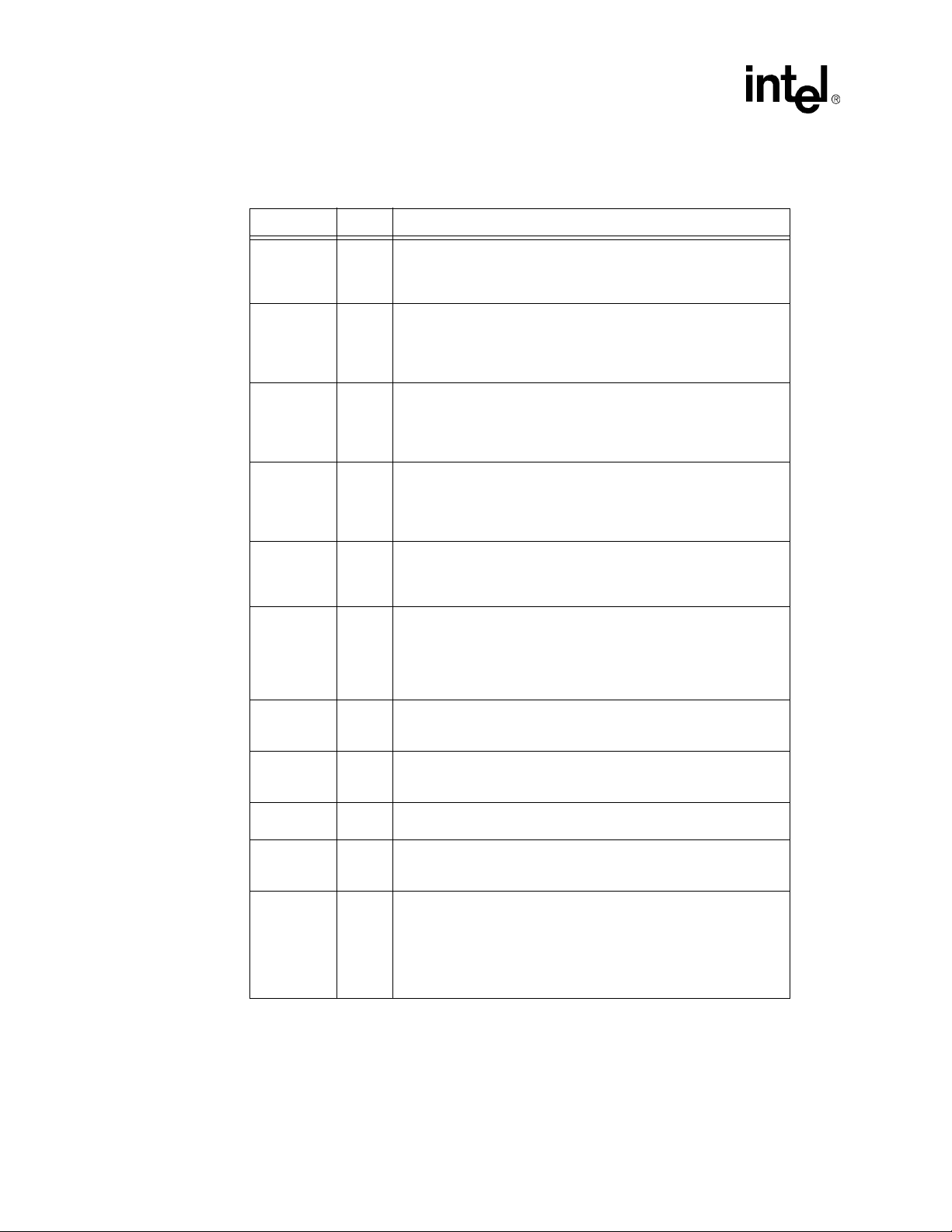

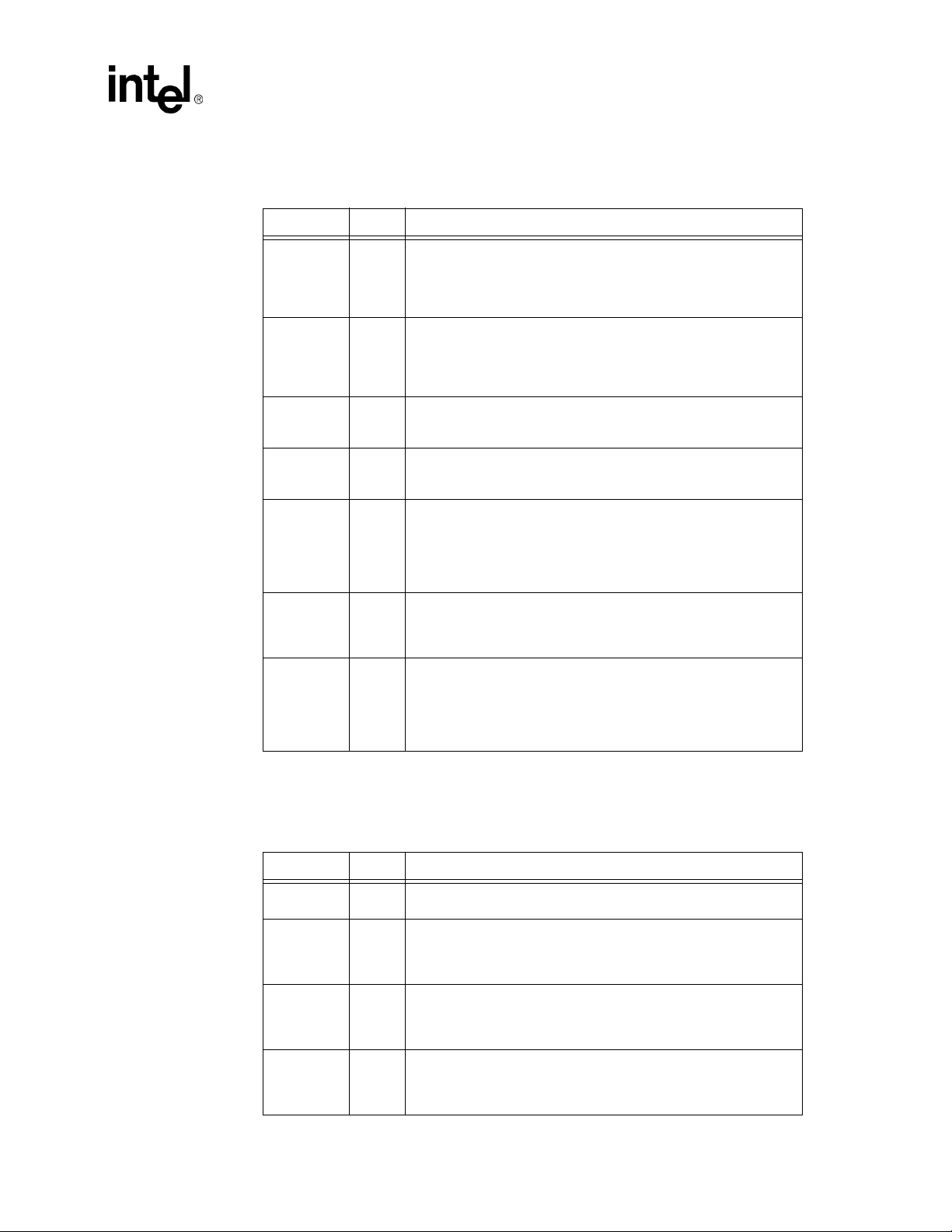

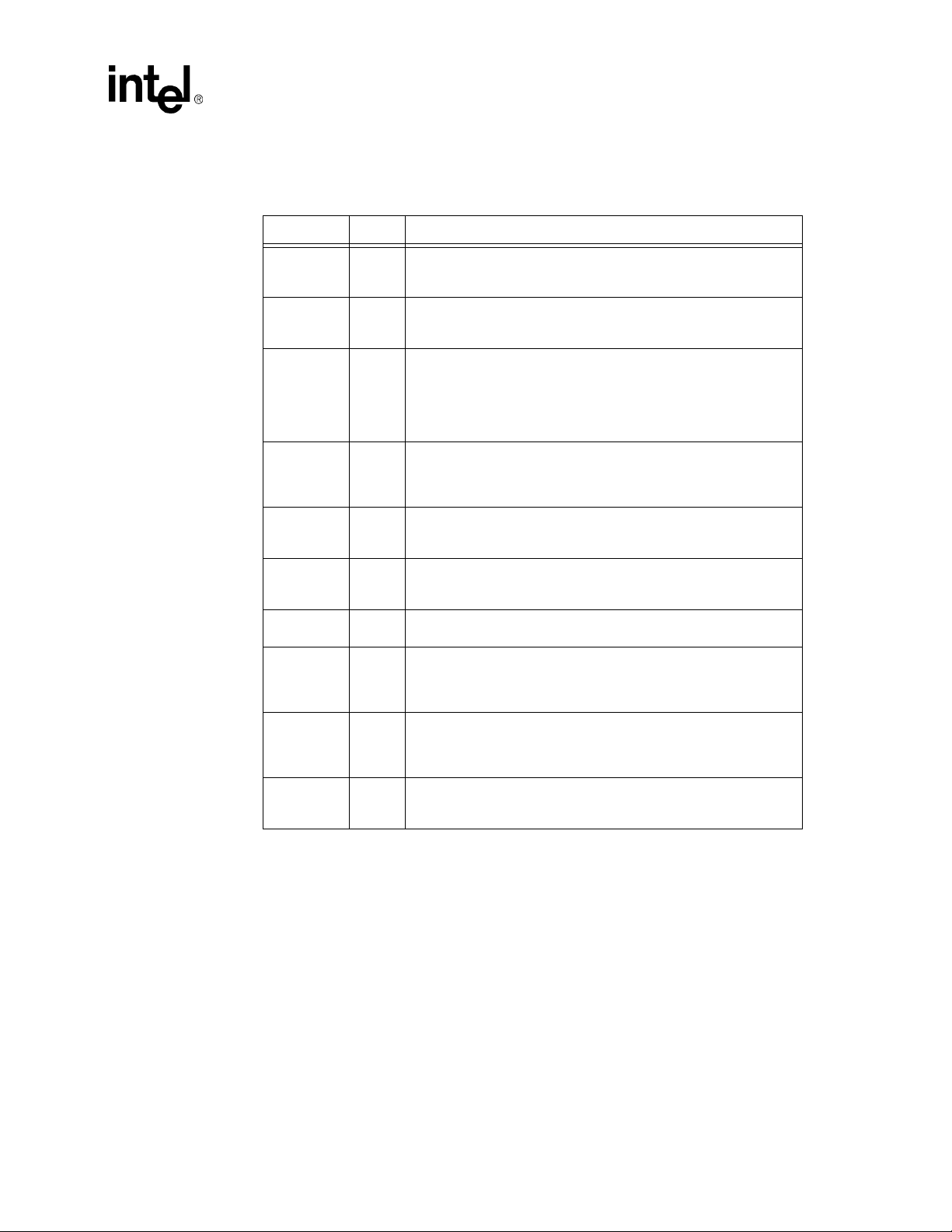

The tables below summarizes the 82559ER’s functionality and power consumption at the different

power states

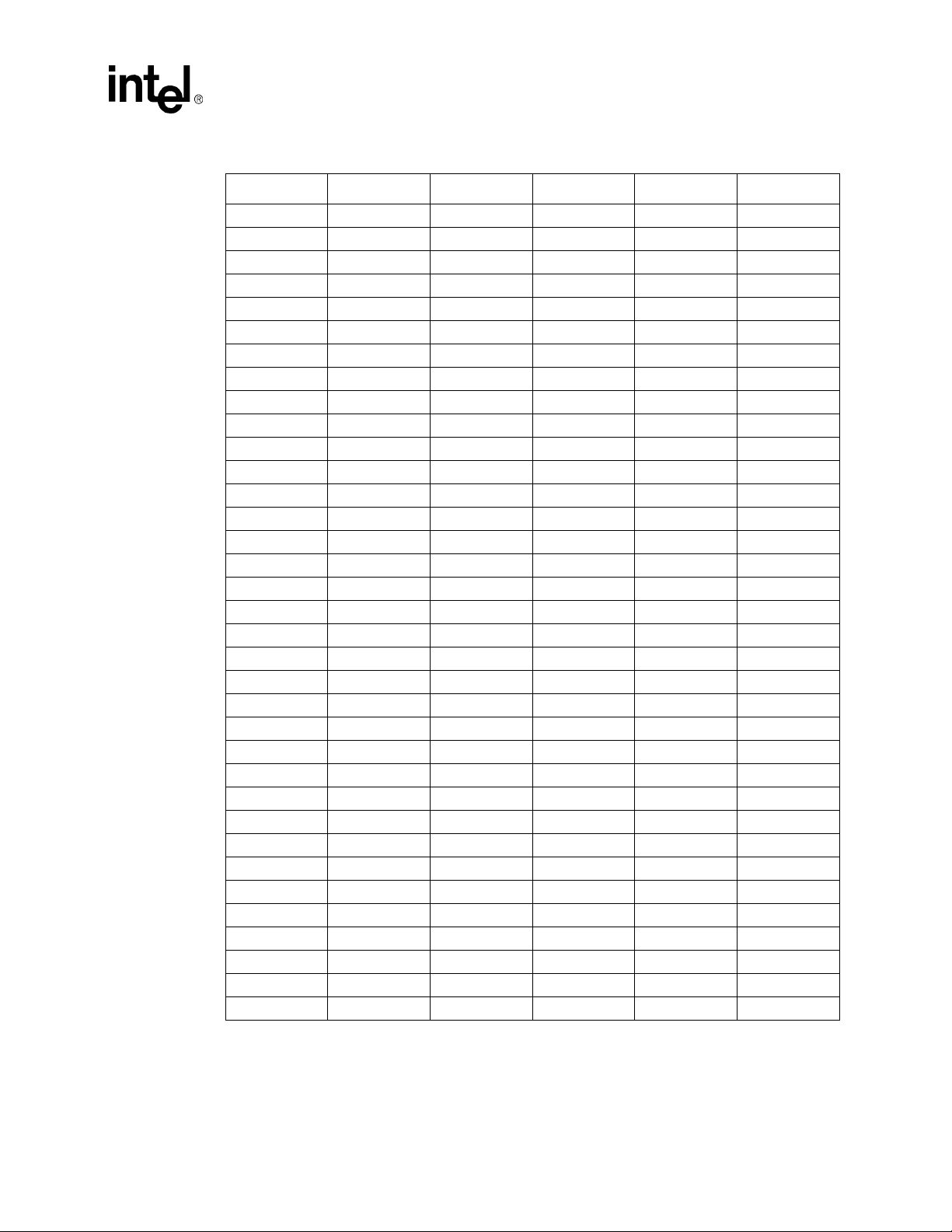

Power State Conditions 100 Mbs 10 Mbs

D0 Maximum 175 mA 140 mA

D0 Average (5 Mbs) 125 mA 115 mA

D0

D2/D3 (link

down)

Dx (x>0 with

PME# disabled)

NOTE:

All values shown for the D3 state assume the availability of 3.3 V Standby available to the

Dynamic standby