Page 1

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

Updated for Intel® Quartus® Prime Design Suite: 18.0

Subscribe

Send Feedback

AN-796 | 2018.06.18

Latest document on the web: PDF | HTML

Page 2

Contents

Contents

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC

FPGAs........................................................................................................................ 4

1.1. The SoC FPGA Designer’s Checklist.......................................................................... 5

1.2. Overview of HPS Design Guidelines for SoC FPGA design.............................................7

1.3. Overview of Board Design Guidelines for SoC FPGA Design..........................................8

1.4. Overview of Embedded Software Design Guidelines for SoC FPGA Design...................... 9

2. Background: Comparison between Cyclone V SoC FPGA and Arria V SoC FPGA HPS

Subsystems............................................................................................................. 10

2.1. Guidelines for Interconnecting the HPS and FPGA.....................................................10

2.1.1. HPS-FPGA Bridges....................................................................................10

2.1.2. FPGA-to-HPS SDRAM Access......................................................................12

2.1.3. Connecting Soft Logic to HPS Component....................................................14

3. Design Guidelines for HPS portion of SoC FPGAs...........................................................15

3.1. Start your SoC-FPGA design here...........................................................................15

3.1.1. Recommended Starting Point for HPS-to-FPGA Interface Design..................... 15

3.1.2. Determining your SoC FPGA Topology......................................................... 15

3.2. Design Considerations for Connecting Device I/O to HPS Peripherals and Memory.........16

3.2.1. HPS Pin Assignment Design Considerations..................................................17

3.2.2. HPS I/O Settings: Constraints and Drive Strengths.......................................18

3.3. HPS Clocking and Reset Design Considerations........................................................ 19

3.3.1. HPS Clock Planning.................................................................................. 20

3.3.2. Early Pin Planning and I/O Assignment Analysis........................................... 20

3.3.3. Pin Features and Connections for HPS JTAG, Clocks, Reset and PoR ............... 20

3.3.4. Internal Clocks........................................................................................ 21

3.4. HPS EMIF Design Considerations............................................................................21

3.4.1. Considerations for Connecting HPS to SDRAM.............................................. 21

3.4.2. HPS SDRAM I/O Locations.........................................................................23

3.4.3. Integrating the HPS EMIF with the SoC FPGA Device.....................................23

3.4.4. HPS Memory Debug................................................................................. 23

3.5. DMA Considerations............................................................................................. 24

3.5.1. Choosing a DMA Controller........................................................................ 24

3.5.2. Optimizing DMA Master Bandwidth through HPS Interconnect........................ 24

3.5.3. Timing Closure for FPGA Accelerators......................................................... 24

3.6. Managing Coherency for FPGA Accelerators............................................................. 25

3.6.1. Cache Coherency..................................................................................... 25

3.6.2. Coherency between FPGA Logic and HPS: Accelerator Coherency Port (ACP).... 25

3.6.3. Data Size Impacts ACP Performance...........................................................25

3.6.4. FPGA Access to ACP via AXI or Avalon-MM...................................................26

3.6.5. Data Alignment for ACP and L2 Cache ECC accesses..................................... 26

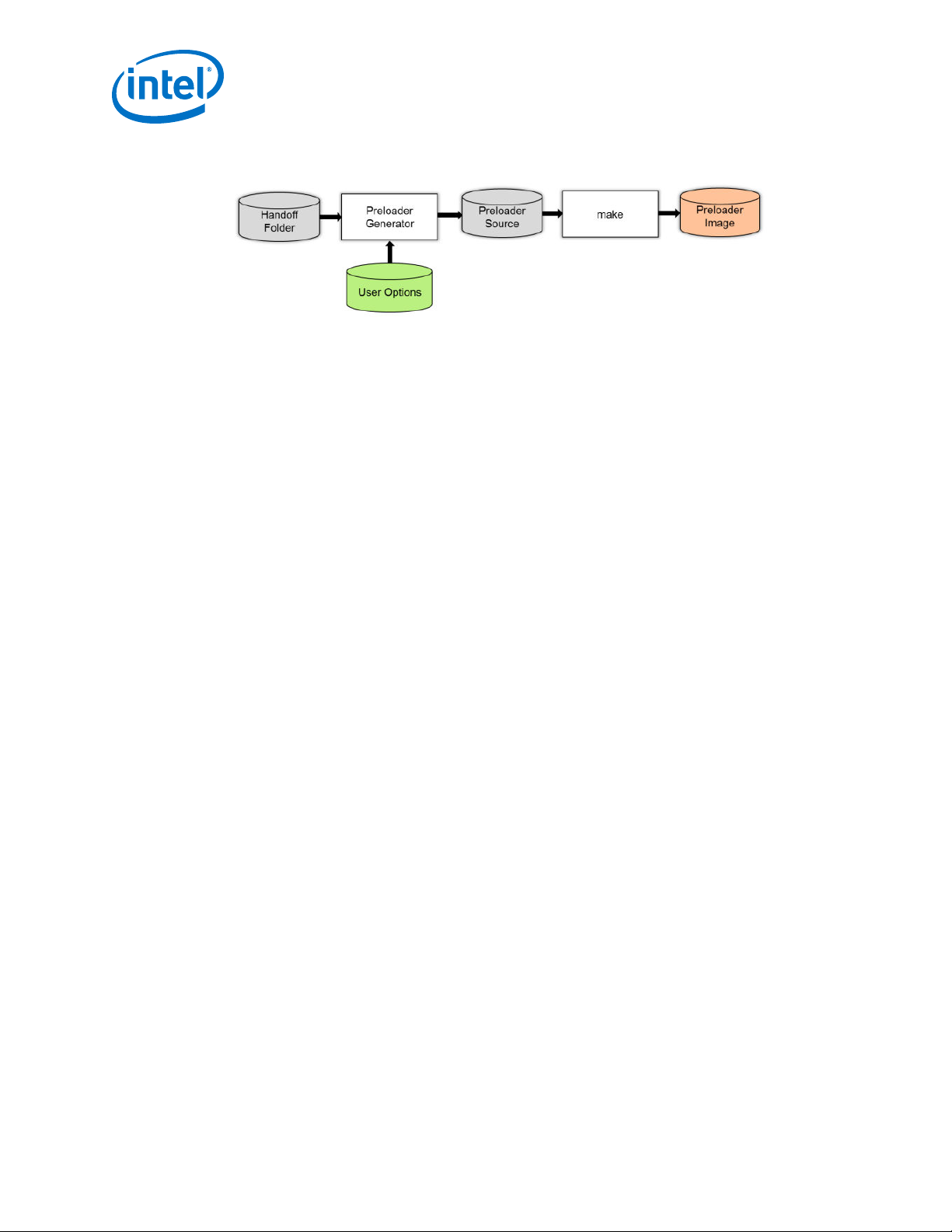

3.7. IP Debug Tools.................................................................................................... 26

4. Board Design Guidelines for SoC FPGAs........................................................................ 28

4.1. Board Bring Up Considerations...............................................................................28

4.1.1. Reserved BSEL Setting............................................................................. 28

4.2. Boot and Configuration Design Considerations......................................................... 28

4.2.1. Boot Design Considerations....................................................................... 28

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

2

Page 3

Contents

4.2.2. Configuration.......................................................................................... 32

4.2.3. Reference Materials..................................................................................32

4.3. HPS Power Design Considerations.......................................................................... 32

4.3.1. Early System and Board Planning...............................................................33

4.3.2. Design Considerations for HPS and FPGA Power Supplies for SoC FPGA

devices...................................................................................................34

4.3.3. Pin Connection Considerations for Board Designs..........................................34

4.3.4. Power Analysis and Optimization................................................................35

4.4. Boundary Scan for HPS.........................................................................................36

4.5. Design Guidelines for HPS Interfaces...................................................................... 36

4.5.1. HPS EMAC PHY Interfaces......................................................................... 36

4.5.2. USB Interface Design Guidelines................................................................ 43

4.5.3. QSPI Flash Interface Design Guidelines....................................................... 44

4.5.4. SD/MMC and eMMC Card Interface Design Guidelines................................... 45

4.5.5. NAND Flash Interface Design Guidelines......................................................46

4.5.6. UART Interface Design Guidelines...............................................................46

4.5.7. I2C Interface Design Guidelines..................................................................47

4.5.8. SPI Interface Design Guidelines................................................................. 47

5. Embedded Software Design Guidelines for SoC FPGAs.................................................. 49

5.1. Embedded Software for HPS: Design Guidelines.......................................................49

5.1.1. Assembling the Components of Your Software Development Platform.............. 49

5.1.2. Selecting an Operating System for Your Application...................................... 52

5.1.3. Assembling your Software Development Platform for Linux............................53

5.1.4. Assembling a Software Development Platform for a Bare-Metal Application...... 57

5.1.5. Assembling your Software Development Platform for a Partner OS or RTOS..... 58

5.1.6. Choosing Boot Loader Software................................................................. 58

5.1.7. Selecting Software Tools for Development, Debug and Trace.......................... 60

5.2. Flash Device Driver Design Considerations.............................................................. 61

5.3. HPS ECC Design Considerations............................................................................. 61

5.3.1. General ECC Design Considerations............................................................ 62

5.3.2. System-Level ECC Control, Status and Interrupt Management........................62

5.3.3. ECC for L2 Cache Data Memory................................................................. 62

5.3.4. ECC for Flash Memory.............................................................................. 63

5.4. HPS SDRAM Considerations...................................................................................63

5.4.1. Using the Preloader To Debug the HPS SDRAM............................................. 63

5.4.2. Access HPS SDRAM via the FPGA-to-SDRAM Interface...................................67

A. Support and Documentation......................................................................................... 69

A.1. Support..............................................................................................................69

A.2. Software Documentation.......................................................................................70

B. Additional Information................................................................................................. 71

B.1. Cyclone V and Arria V SoC Device Guidelines Revision History....................................71

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

3

Page 4

AN-796 | 2018.06.18

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

The purpose of this document is to provide a set of design guidelines and

recommendations, as well as a list of factors to consider, for designs that use the

Cyclone V SoC and Arria V SoC FPGA devices. This document assists you in the

planning and early design phases of the SoC FPGA design, Platform Designer

(Standard) sub-system design, board design and software application design.

Note: This application note does not include all the Cyclone V/Arria V Hard Processor System

(HPS) device details, features or information on designing the hardware or software

system. For more information about the Cyclone V or Arria V HPS features and

individual peripherals, refer to the respective Hard Processor System Technical

Reference Manual.

Design guidelines for the FPGA portion of your design are provided in the Arria V and

Cyclone V Design Guidelines.

Related Information

• Arria V Hard Processor System Technical Reference Manual

• Cyclone V Hard Processor System Technical Reference Manual

• Intel MAX 10 FPGA Design Guidelines

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 5

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

AN-796 | 2018.06.18

1.1. The SoC FPGA Designer’s Checklist

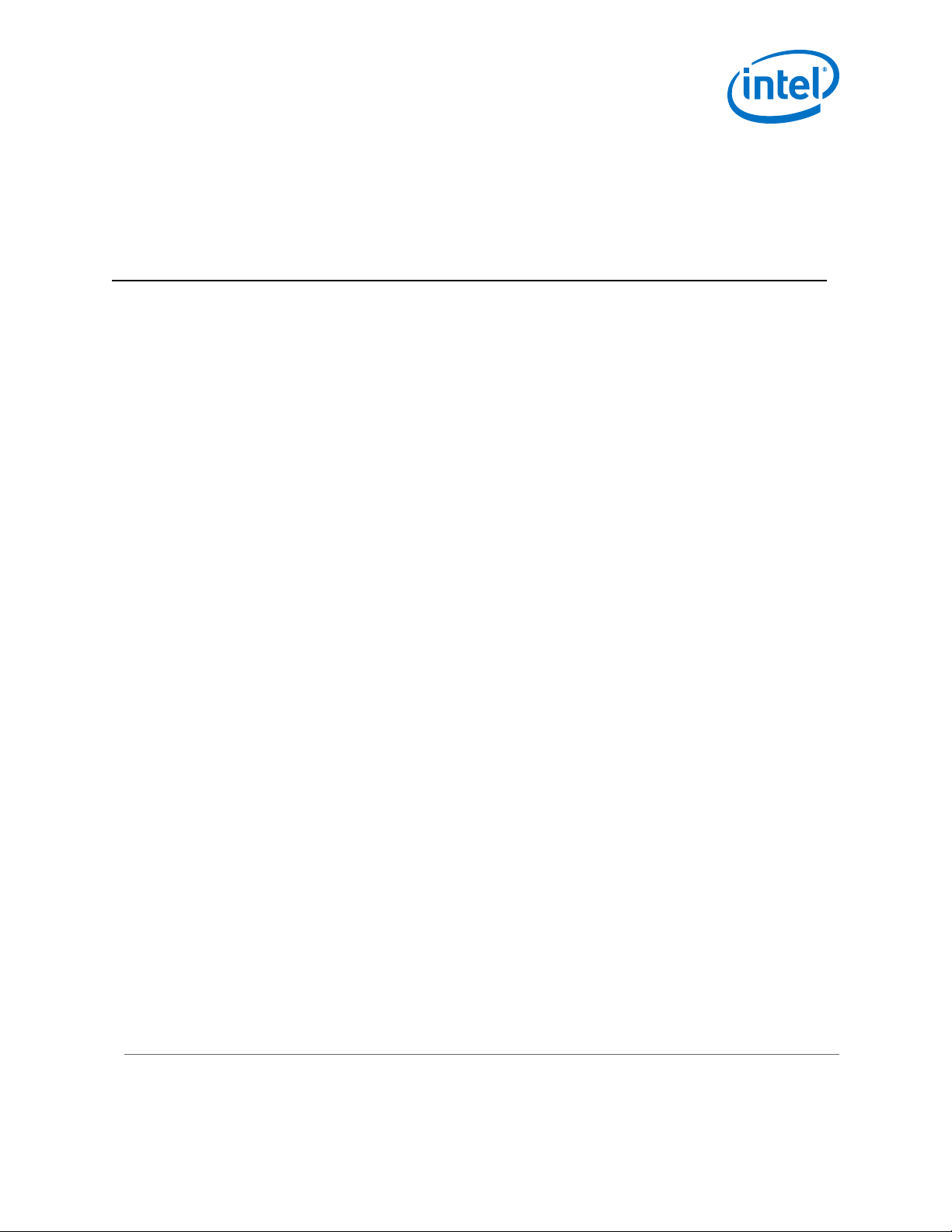

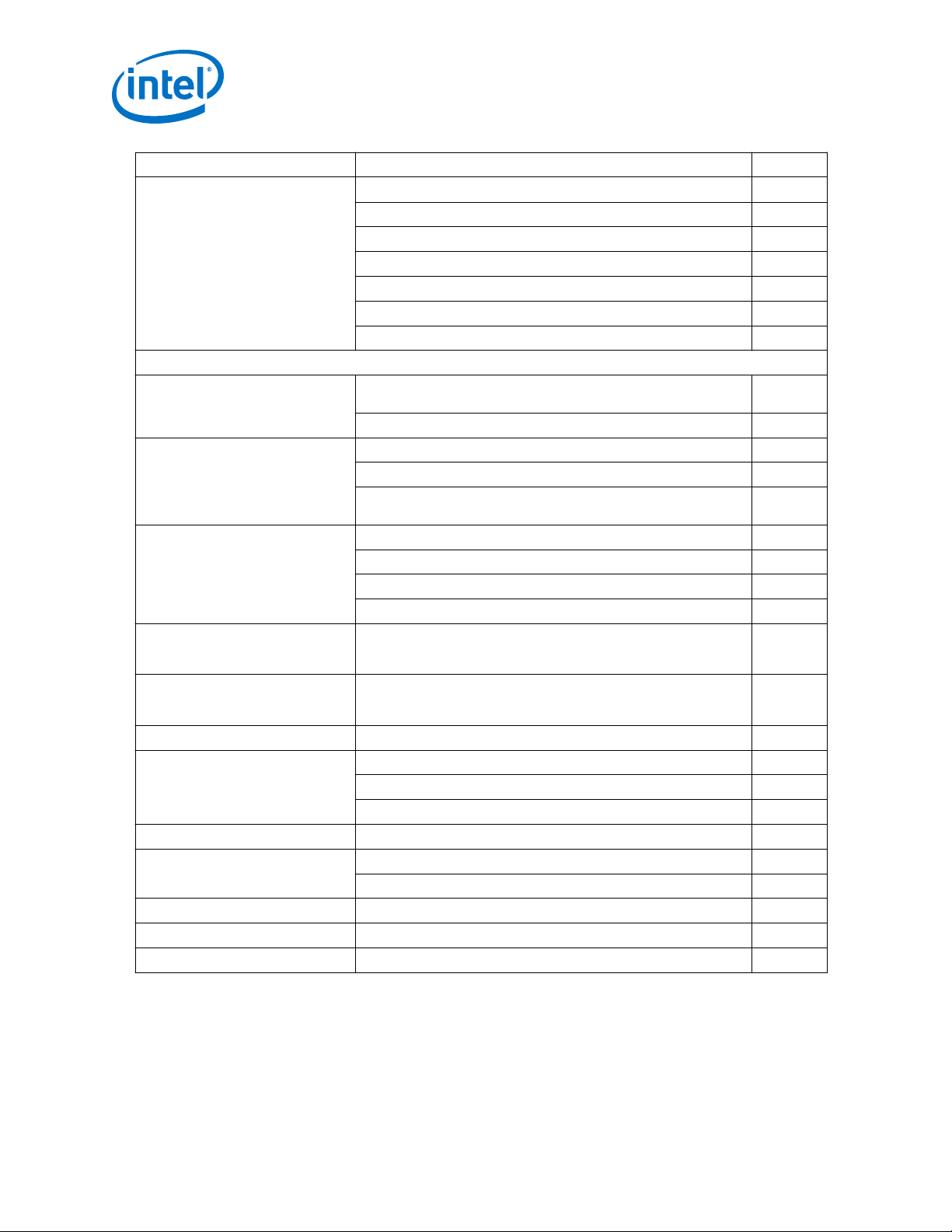

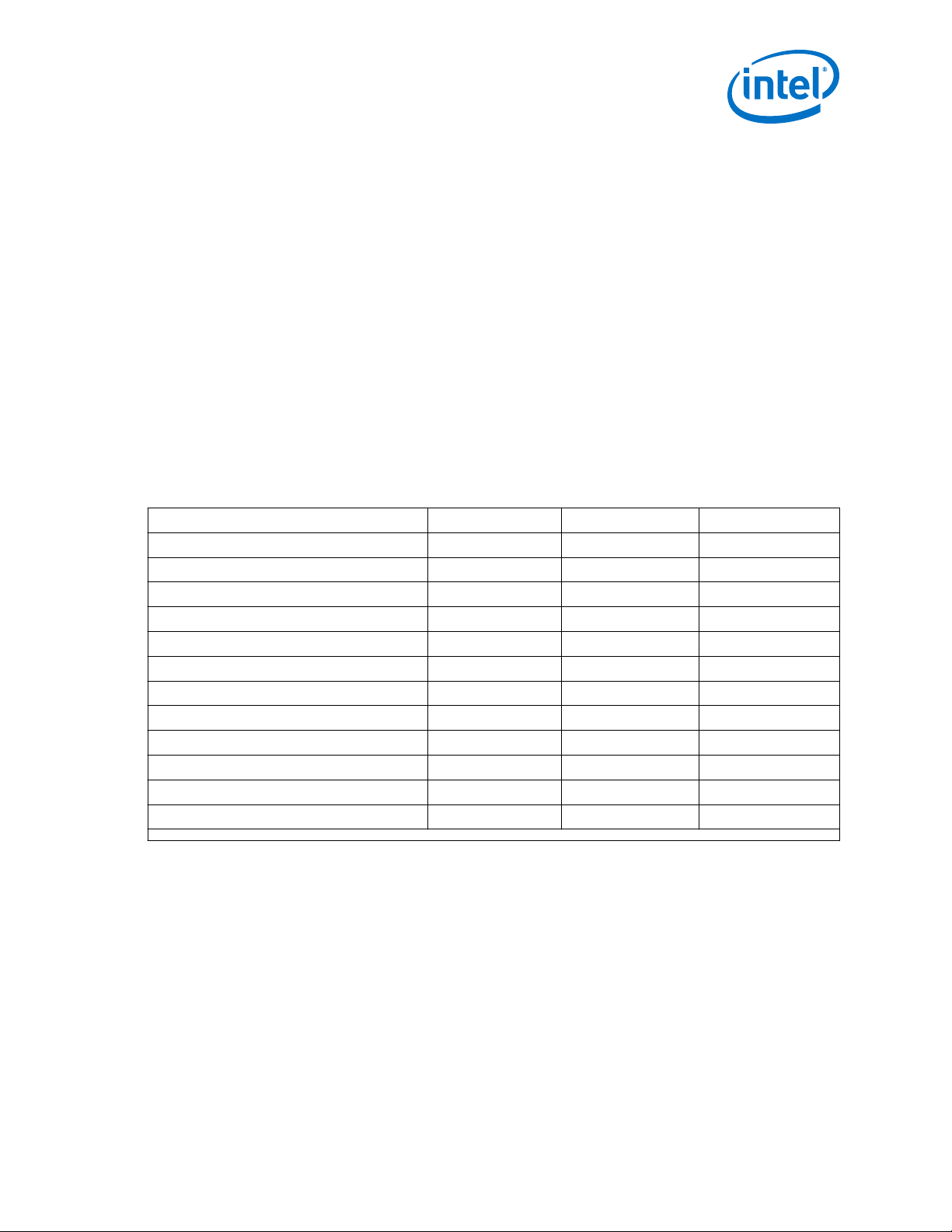

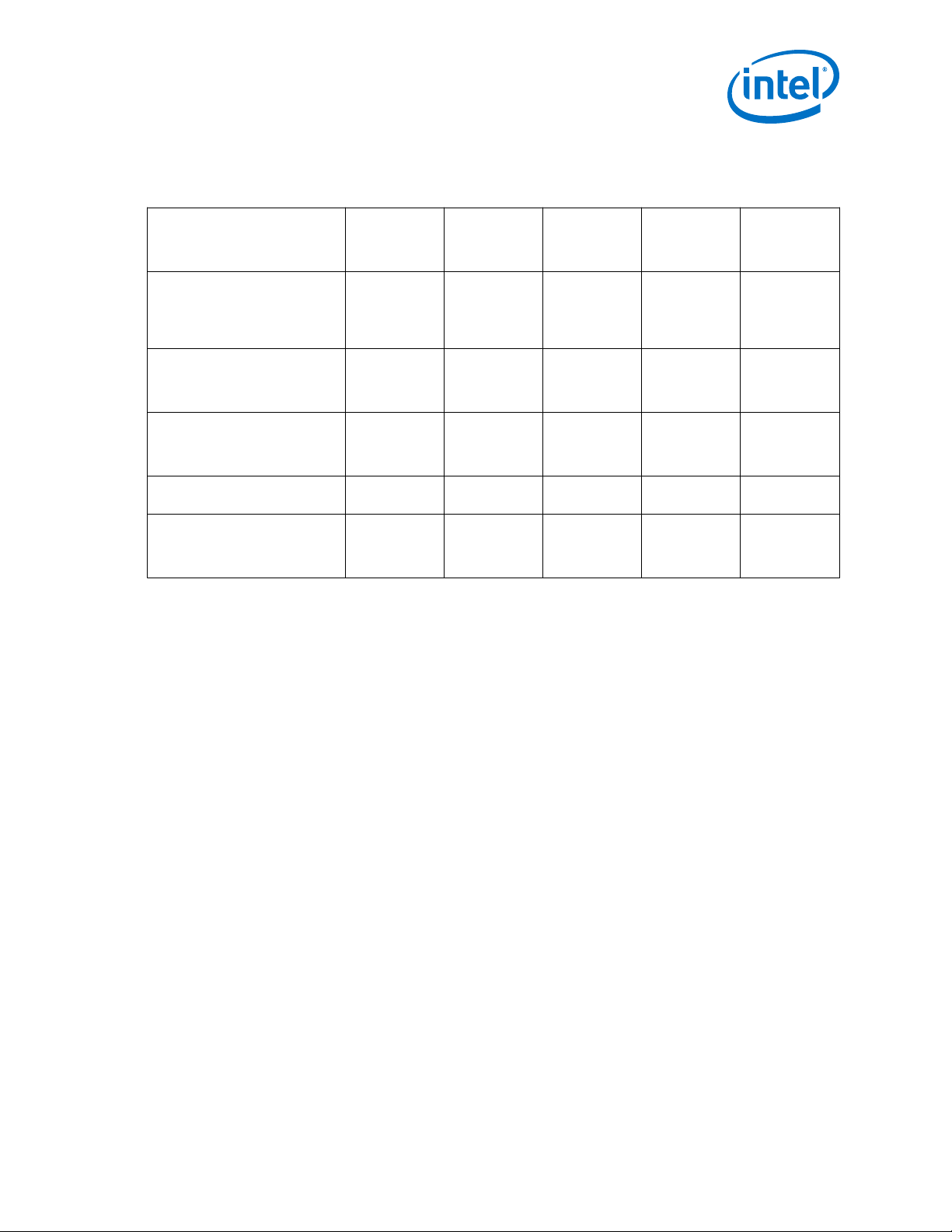

Table 1. The SoC FPGA Designer's Checklist

Step Title Links Check (X)

HPS Designer's Checklist for SoC FPGAs

Start your SoC FPGA Design here Start your SoC-FPGA design here on page 15

Determining your SoC FPGA Topology on page 15

Design Considerations for Connecting

Device I/O to HPS Peripherals and

Memory

HPS Clocking and Reset Design

Considerations

HPS EMIF Design Considerations Considerations for Connecting HPS to SDRAM on page 21

DMA Considerations Choosing a DMA Controller on page 24

Managing Coherency for FPGA

Accelerators

IP Debug Tools IP Debug Tools on page 26

HPS Power Design Considerations Early System and Board Planning on page 33

Boundary Scan for HPS Boundary Scan for HPS on page 36

Design Guidelines for HPS Interfaces HPS EMAC PHY Interfaces on page 36

HPS Pin Assignment Design Considerations on page 17

HPS I/O Settings: Constraints and Drive Strengths on page 18

HPS Clock Planning on page 20

Early Pin Planning and I/O Assignment Analysis on page 20

Pin Features and Connections for HPS JTAG, Clocks, Reset and PoR

on page 20

Internal Clocks on page 21

HPS SDRAM I/O Locations on page 23

Integrating the HPS EMIF with the SoC FPGA Device on page 23

HPS Memory Debug on page 23

Optimizing DMA Master Bandwidth through HPS Interconnect on page

24

Timing Closure for FPGA Accelerators on page 24

Cache Coherency on page 25

Coherency between FPGA Logic and HPS: Accelerator Coherency Port

(ACP) on page 25

Data Size Impacts ACP Performance on page 25

FPGA Access to ACP via AXI or Avalon-MM on page 26

Data Alignment for ACP and L2 Cache ECC accesses on page 26

Board Designer's Checklist for SoC FPGAs

Early Power Estimation on page 33

Design Considerations for HPS and FPGA Power Supplies for SoC

FPGA devices on page 34

Pin Connection Considerations for Board Designs on page 34

Device Power-Up on page 34

Power Analysis and Optimization on page 35

continued...

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

5

Page 6

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

Step Title Links Check (X)

USB Interface Design Guidelines on page 43

QSPI Flash Interface Design Guidelines on page 44

SD/MMC and eMMC Card Interface Design Guidelines on page 45

NAND Flash Interface Design Guidelines on page 46

UART Interface Design Guidelines on page 46

I2C Interface Design Guidelines on page 47

SPI Interface Design Guidelines on page 47

Embedded Software Designer's Checklist for SoC FPGAs

Assemble the components of your

Software Development Platform

Select an Operating System (OS) for

your application

Assemble your Software

Development Platform for Linux

Assemble your Software

Development Platform for Bare-metal

Application

Assemble your Software

Development Platform for Partner

OS/RTOS Application

Choose the Boot Loader Software Choosing Boot Loader Software on page 58

Selecting Software Tools for

Development, Debug and Trace

Board Bring Up Considerations Board Bring Up Considerations on page 28

Boot and Configuration Design

Considerations

Flash Device Driver Considerations Flash Device Driver Design Considerations on page 61

HPS ECC Design Considerations HPS ECC Design Considerations on page 61

HPS SDRAM Considerations HPS SDRAM Considerations on page 63

Assembling the Components of Your Software Development Platform

on page 49

Golden Hardware Reference Design on page 50

Linux or RTOS on page 52

Bare Metal on page 52

Using Symmetrical vs. Asymmetrical Multiprocessing (SMP vs. AMP)

Modes on page 53

Golden System Reference Design (GSRD) for Linux on page 54

GSRD for Linux Development Flow on page 54

GSRD for Linux Build Flow on page 55

Linux Device Tree Design Considerations on page 56

Assembling a Software Development Platform for a Bare-Metal

Application on page 57

Assembling your Software Development Platform for a Partner OS or

RTOS on page 58

Select Software Build Tools on page 60

Select Software Debug Tools on page 60

Select Software Trace Tools on page 61

Boot Design Considerations on page 28

Configuration on page 32

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

6

Page 7

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

AN-796 | 2018.06.18

1.2. Overview of HPS Design Guidelines for SoC FPGA design

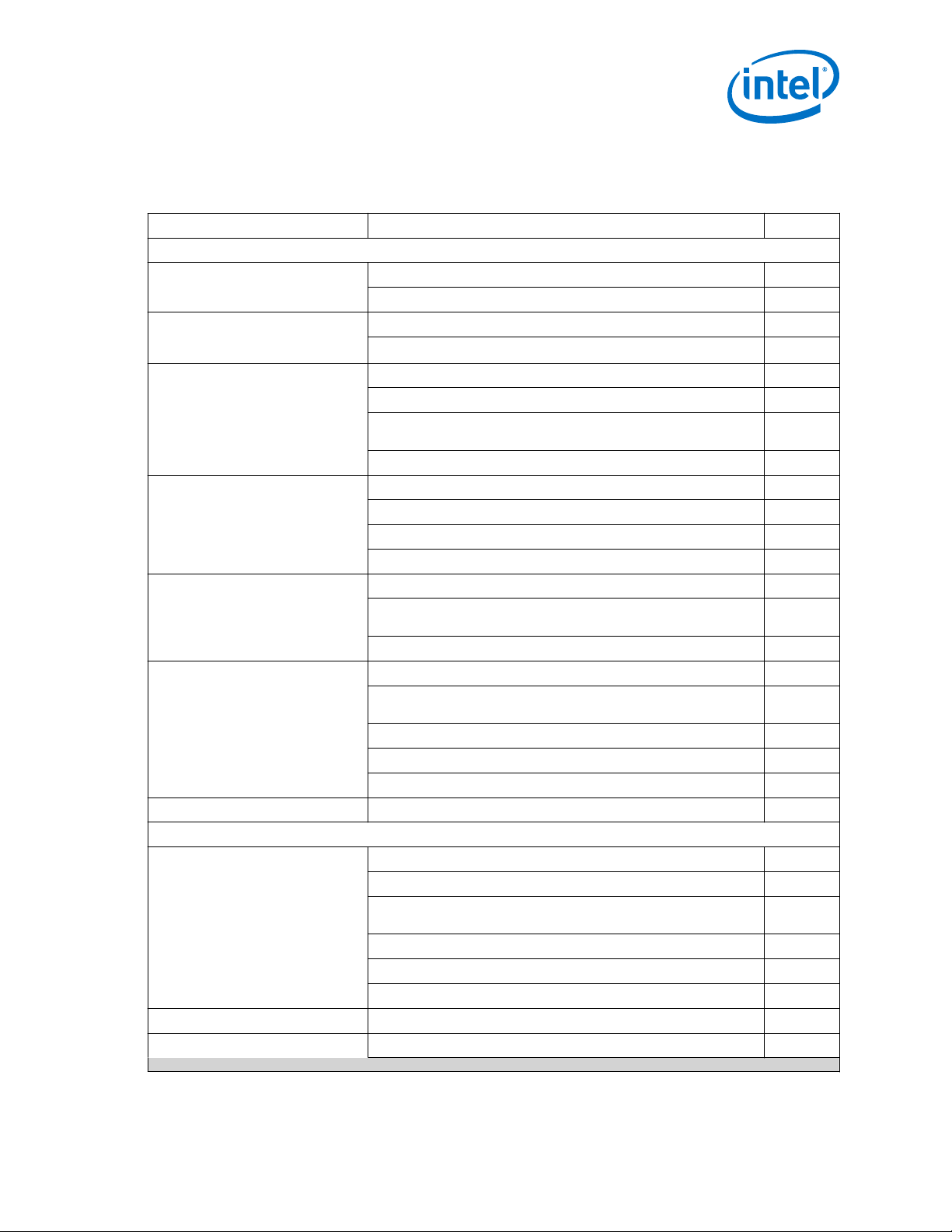

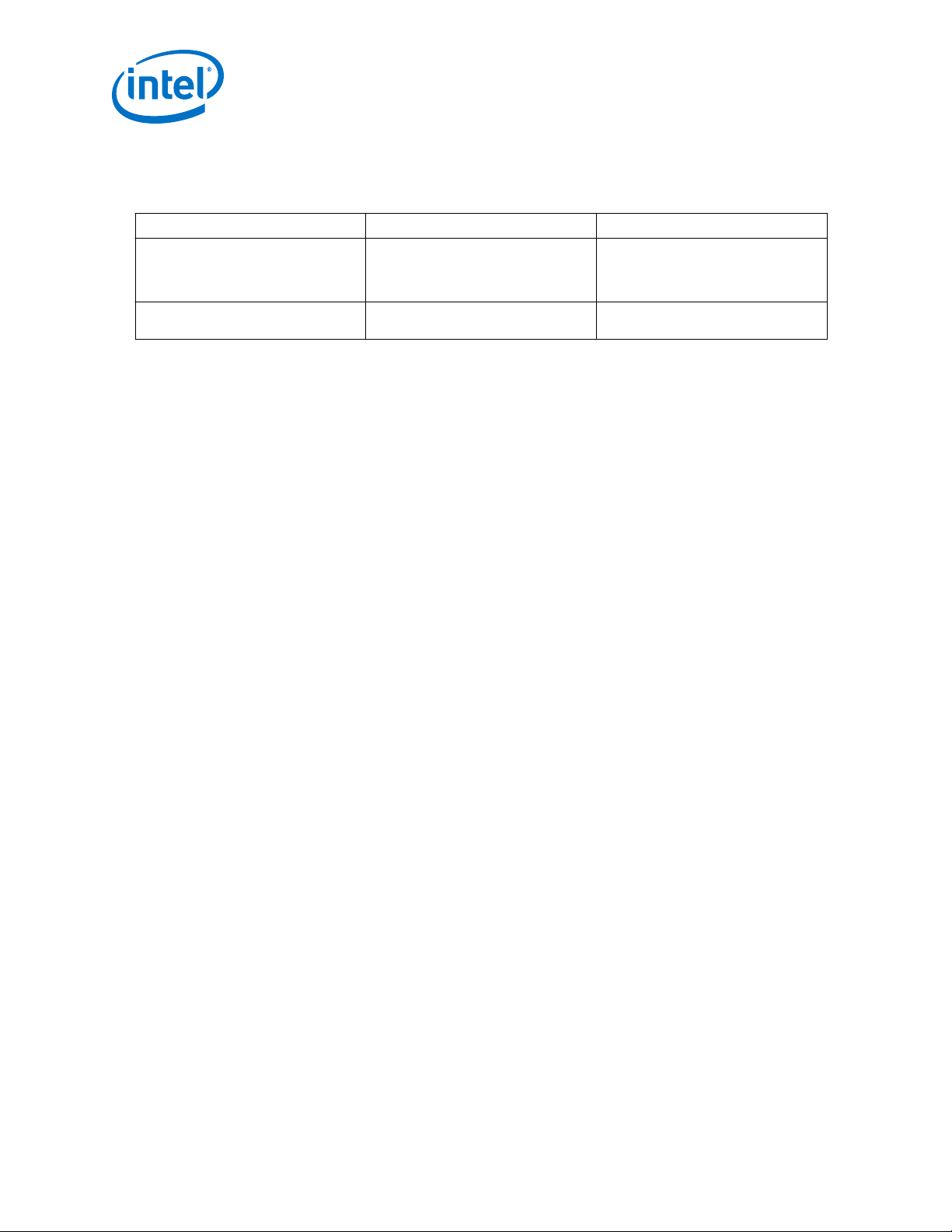

Table 2. HPS Design Guidelines Overview

Stages of the HPS Design Flow Guidelines Links

Hardware and Software Partitioning Determine your system topology and

HPS Pin Multiplexing and I/O

Configuration Settings

HPS Clocks and Reset Considerations HPS clocks and cold and warm reset

HPS EMIF Considerations Usage of the HPS EMIF controller and

FPGA Accelerator Design

Considerations

Recommended Tools for IP

Development

use it as a starting point for your HPS

to FPGA interface design.

Plan configuration settings for the HPS

system including I/O multiplexing

options, interface to FPGA and SDRAM,

clocks, peripheral settings

considerations

related considerations

Design considerations to manage

coherency between FPGA accelerators

and the HPS

Signal Tap II, BFMs, System Console IP Debug Tools on page 26

Guidelines for Interconnecting the HPS

and FPGA on page 10

Design Considerations for Connecting

Device I/O to HPS Peripherals and

Memory on page 16

HPS Clocking and Reset Design

Considerations on page 19

HPS EMIF Design Considerations on

page 21

DMA Considerations on page 24

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

7

Page 8

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

AN-796 | 2018.06.18

1.3. Overview of Board Design Guidelines for SoC FPGA Design

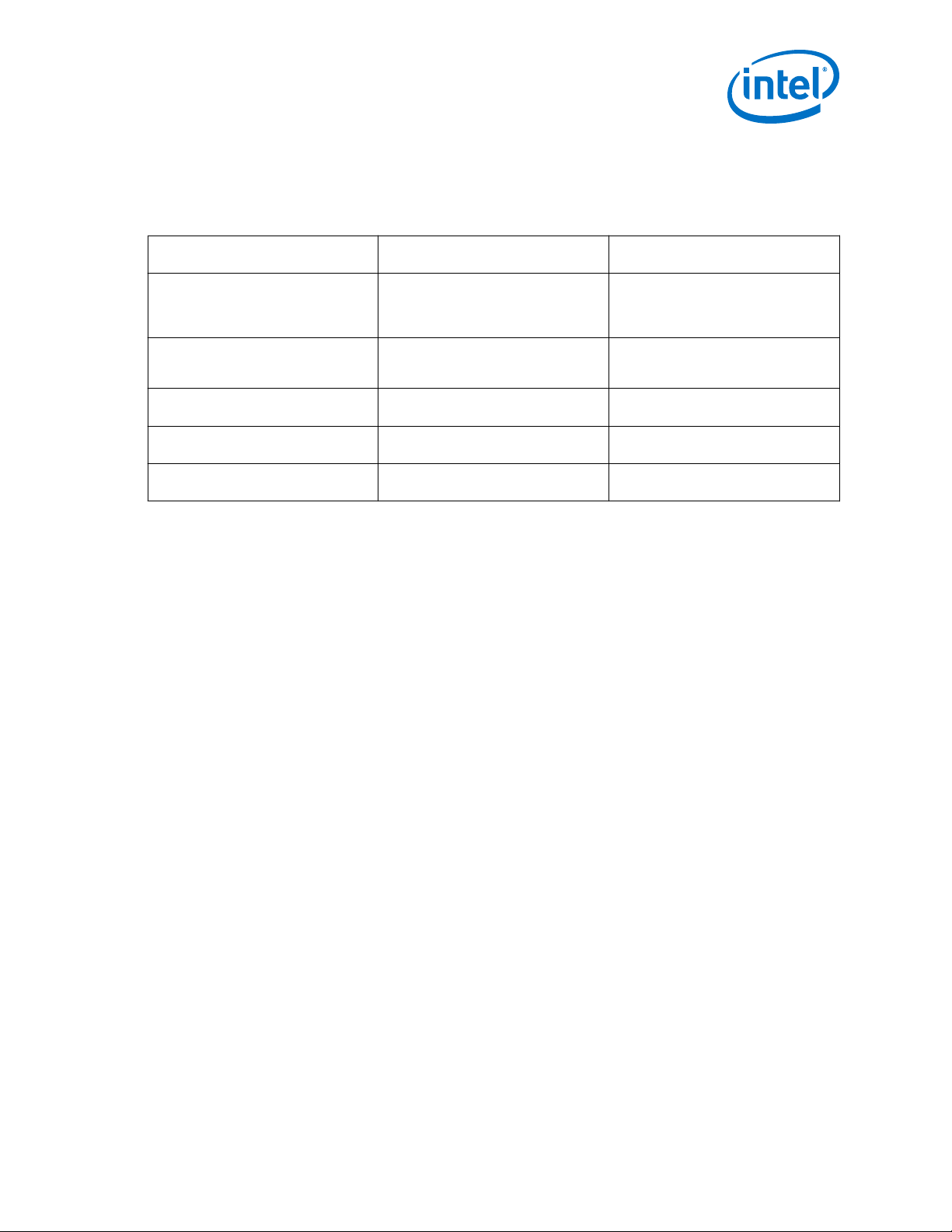

Table 3. Board Design: Design Guidelines Overview

Stages of the Board Design Flow Guidelines Links

HPS Power design considerations Power on board bring up, early power

Board design guidelines for HPS

interfaces

estimation, design considerations for

HPS and FPGA power supplies, power

analysis and power optimization

Includes EMAC, USB, QSPI, SD/MMC,

NAND, UART and I2C

HPS Power Design Considerations on

page 32

Design Guidelines for HPS Interfaces

on page 36

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

8

Page 9

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

AN-796 | 2018.06.18

1.4. Overview of Embedded Software Design Guidelines for SoC FPGA Design

Table 4. Embedded Software: Design Guidelines Overview

Stages of the Embedded Software

Operating System (OS) considerations OS considerations to meet your

Boot Loader considerations Boot loader considerations to meet

Boot and Configuration Design

Considerations

HPS ECC Considerations ECC for external SDRAM interface, L2

HPS SDRAM Considerations Using Preloader to debug HPS SDRAM,

Design Flow

application needs, including real time,

software reuse, support and ease of

use considerations

your application needs. including GPL

requirements, and features.

Boot source, boot clock, boot fuses,

configuration flows

cache data memory, flash memory

Accessing the HPS SDRAM

Guidelines Links

Selecting an Operating System for Your

Application on page 52

Choosing Boot Loader Software on

page 58

Boot and Configuration Design

Considerations on page 28

HPS ECC Design Considerations on

page 61

HPS SDRAM Considerations on page

63

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

9

Page 10

AN-796 | 2018.06.18

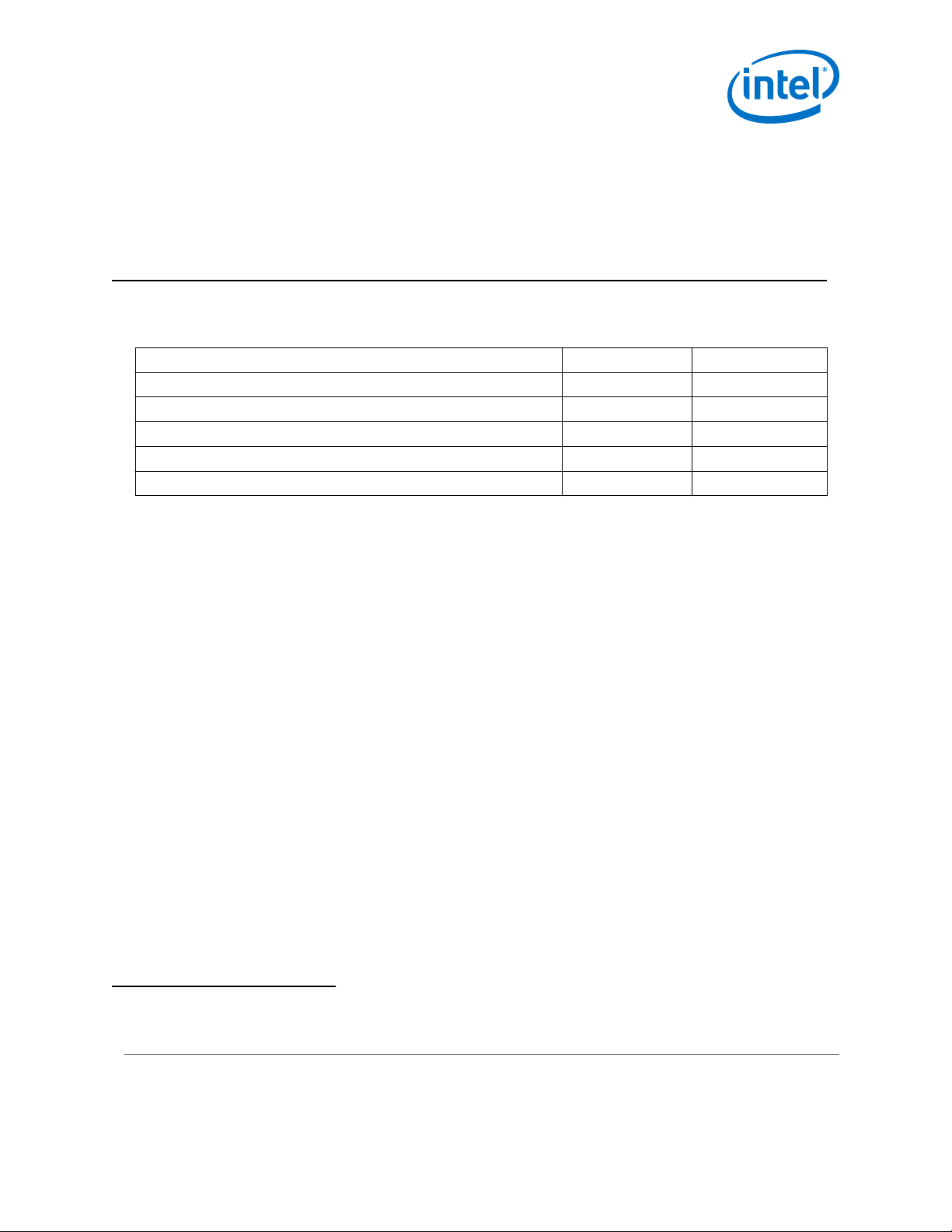

2. Background: Comparison between Cyclone V SoC FPGA and Arria V SoC FPGA HPS Subsystems

While the HPS subsystems in Cyclone V SoC and Arria V SoC are architecturally

similar, there are a few differences in features as listed below.

HPS Features

Maximum MPU Frequency Up to 925 MHz Up to 1.05 GHz

Controller Area Network (CAN) Yes No

Total HPS Dedicated I/O with Loaner capability Up to 67 94

Automotive Grade Option Yes No

Maximum supported DDR3 Frequency for HPS SDRAM 400 MHz 533 MHz

Cyclone V SoC Arria V SoC

Related Information

Differences Among Intel SoC Device Families

2.1. Guidelines for Interconnecting the HPS and FPGA

The memory-mapped connectivity between the HPS and the FPGA fabric is a crucial

tool to maximize the performance of your design.

Design guidelines for the FPGA portion of your design are provided in the Arria V and

Cyclone V Design Guidelines.

Related Information

Arria V and Cyclone V Design Guidelines

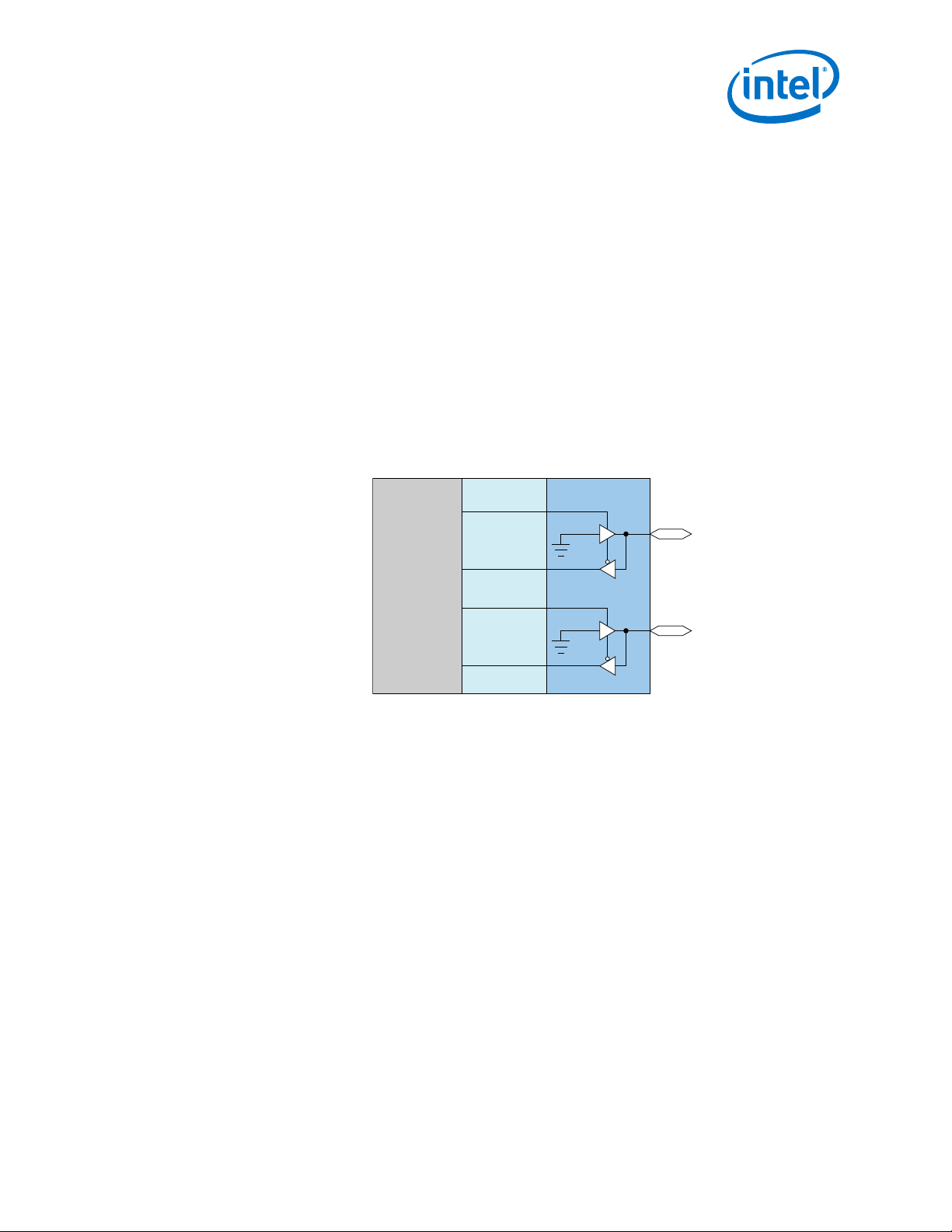

2.1.1. HPS-FPGA Bridges

(1)

The HPS has three bridges that use memory-mapped interfaces to the FPGA based on

the Arm* Advanced Microcontroller Bus Architecture (AMBA*) Advanced eXtensible

Interface (AXI*). Their purpose determines the direction of each bridge.

(1)

You can only assign a maximum of 71 HPS I/O as Loaner I/O to the FPGA. For a detailed

comparison between the HPS subsystem for Cyclone V SoC and Arria V SoC, refer to

Differences Among Intel SoC Device Families.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 11

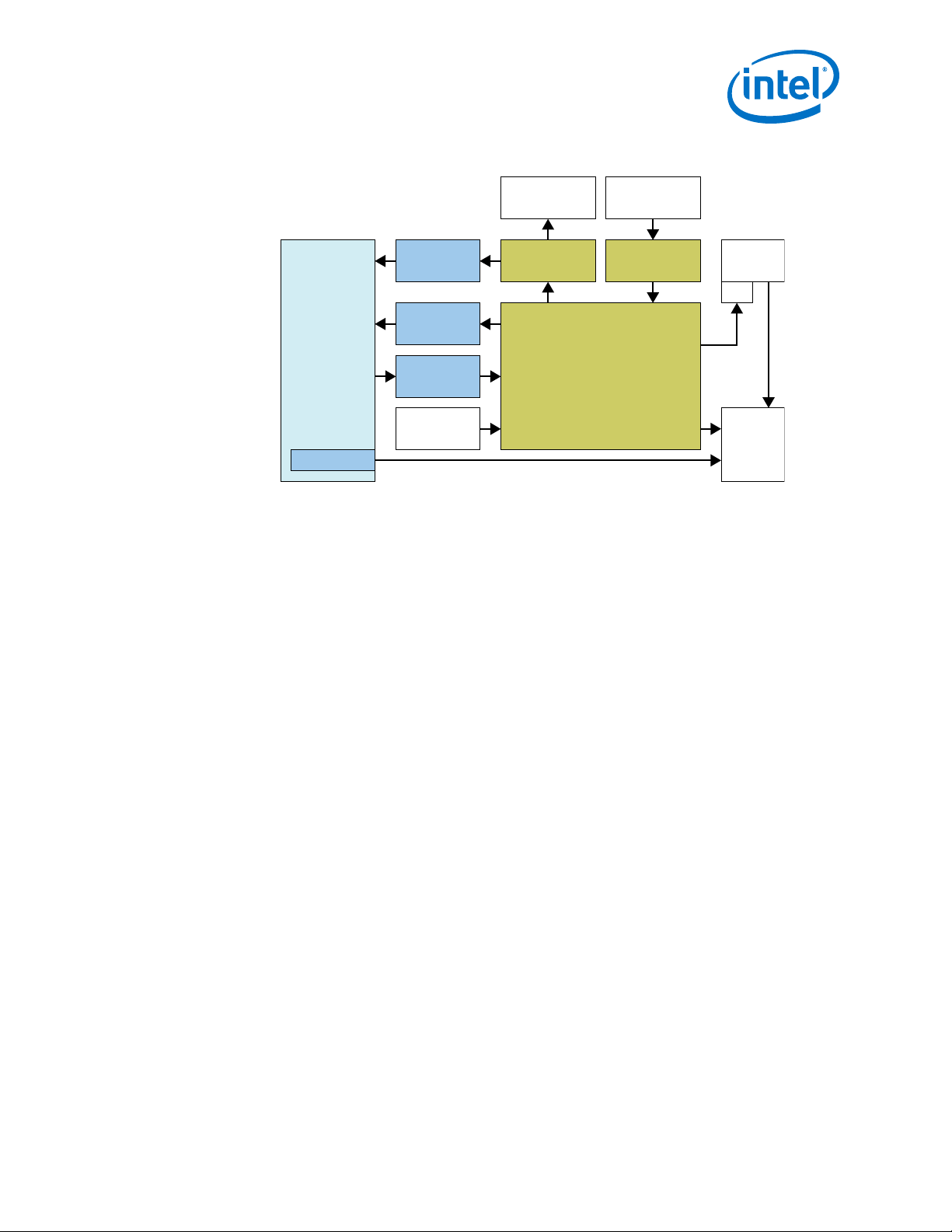

LWH2F Bridge

32 bit

H2F Bridge

32/64/128 bit

F2H Bridge

32/64/128 bit

DMA

L3 Slave

Peripheral Switch

All Other

L3 Slaves

L3 Master

Peripheral Switch

All Other

L3 Masters

L3 Interconnect

Main Switch

FPGA Fabric

F2S Interface

MPU

SRAM

Controller

ACP

Key:

H2F: HPS-to-FPGA

LWH2F: Lightweight HPS-to-FPGA

F2H: FPGA-to-HPS

F2S: FPGA-to-SDRAM

2. Background: Comparison between Cyclone V SoC FPGA and Arria V SoC FPGA HPS Subsystems

AN-796 | 2018.06.18

Figure 1. HPS-FPGA Bridges

2.1.1.1. Lightweight HPS-to-FPGA Bridge

GUIDELINE: Use the lightweight HPS-to-FPGA bridge to connect IP that

needs to be controlled by the HPS.

The lightweight HPS-to-FPGA bridge allows masters in the HPS to access memorymapped control slave ports in the FPGA portion of the SoC device. Typically, only the

MPU inside the HPS accesses this bridge to perform control and status register

accesses to peripherals in the FPGA.

GUIDELINE: Do not use the lightweight HPS-to-FPGA bridge for FPGA

memory. Instead use the HPS-to-FPGA bridge for memory.

When the MPU accesses control and status registers within peripherals, these

transactions are typically strongly ordered (non-posted). By dedicating the lightweight

HPS-to-FPGA bridge to register accesses, the access time is minimized because

bursting traffic is routed to the HPS-to-FPGA bridge instead.

The lightweight HPS-to-FPGA bridge has a fixed 32-bit width connection to the FPGA

fabric, because most IP cores implement 32-bit control and status registers. However,

Platform Designer (Standard) can adapt the transactions to widths other than 32 bits

within the FPGA-generated network interconnect.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

11

Page 12

2. Background: Comparison between Cyclone V SoC FPGA and Arria V SoC FPGA HPS Subsystems

2.1.1.2. HPS-to-FPGA Bridge

GUIDELINE: Use the HPS-to-FPGA bridge to connect memory hosted by the

FPGA to the HPS.

The HPS-to-FPGA bridge allows masters in the HPS such as the microprocessor unit

(MPU), DMA, or peripherals with integrated masters to access memory hosted by the

FPGA portion of the SoC device. This bridge supports 32, 64, and 128-bit datapaths,

allowing the width to be tuned to the largest slave data width in the FPGA fabric

connected to the bridge. This bridge is intended to be used by masters performing

bursting transfers and should not be used for accessing peripheral registers in the

FPGA fabric. Control and status register accesses should be sent to the lightweight

HPS-to-FPGA bridge instead.

GUIDELINE: If memory connected to the HPS-to-FPGA bridge is used for HPS

boot, ensure that its slave address is set to 0x0 in Platform Designer

(Standard).

When the HPS BSEL pins are set to boot from FPGA (BSEL = 1) the processor

executes code hosted by the FPGA residing at offset 0x0 from the HPS-to-FPGA

bridge. This is the only bridge that can be used for hosting code at boot time.

2.1.1.3. FPGA-to-HPS Bridge

AN-796 | 2018.06.18

GUIDELINE: Use the FPGA-to-HPS bridge for cacheable accesses to the HPS

from masters in the FPGA.

The FPGA-to-HPS bridge allows masters implemented in the FPGA fabric to access

memory and peripherals inside the HPS. This bridge supports 32, 64, and 128-bit

datapaths so that you can adjust it to be as wide as the widest master implemented in

the FPGA.

GUIDELINE: Use the FPGA-to-HPS bridge to access cache-coherent memory,

peripherals, or on-chip RAM in the HPS from masters in the FPGA.

Although this bridge has direct connectivity to the SDRAM subsystem, the main intent

of the bridge is to provide access to peripherals and on-chip memory, as well as

provide cache coherency with connectivity to the MPU accelerator coherency port

(ACP).

To access the HPS SDRAM directly without coherency you should connect masters in

the FPGA to the FPGA-to-SDRAM ports instead, because they provide much more

bandwidth and lower-latency access.

2.1.2. FPGA-to-HPS SDRAM Access

In addition to the FPGA-to-HPS bridge, FPGA logic can also use the FPGA-to-SDRAM

interface to access the HPS SDRAM.

GUIDELINE: Use the FPGA-to-SDRAM ports for non-cacheable access to the

HPS SDRAM from masters in the FPGA.

The FPGA-to-SDRAM ports allow masters implemented in the FPGA fabric to directly

access HPS SDRAM without the transactions flowing through the L3 interconnect.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

12

Page 13

2. Background: Comparison between Cyclone V SoC FPGA and Arria V SoC FPGA HPS Subsystems

AN-796 | 2018.06.18

These interfaces connect only to the HPS SDRAM subsystem so it is recommended to

use them in your design if the FPGA needs high-throughput, low-latency access to the

HPS SDRAM. The exception to this recommendation is if the FPGA requires cache

coherent access to SDRAM.

The FPGA-to-SDRAM interfaces cannot access the MPU ACP slave; so if you require a

master implemented in the FPGA to access cache coherent data, ensure that it is

connected to the FPGA-to-HPS bridge instead.

The FPGA-to-SDRAM interface has three port types that are used to create the AXI

and Avalon-MM interfaces:

• Command ports—issue read and/or write commands, and for receive write

acknowledge responses

• 64-bit read data ports—receive data returned from a memory read

• 64-bit write data ports—transmit write data

There is a maximum of six command ports, four 64-bit read data port and four 64-bit

write data port. The table below shows the possible port utilization.

Table 5. FPGA-to-HPS SDRAM Port Utilization

Bus Protocol Command Ports Read Data Ports Write Data Ports

32- or 64-bit AXI 2 1 1

128-bit AXI 2 2 2

256-bit AXI 2 4 4

32- or 64-bit Avalon-MM 1 1 1

128-bit Avalon-MM 1 2 2

256-bit Avalon-MM 1 4 4

32- or 64-bit Avalon-MM write-only 1 0 1

128-bit Avalon-MM write-only 1 0 2

256-bit Avalon-MM write-only 1 0 4

32- or 64-bit Avalon-MM read-only 1 1 0

128-bit Avalon-MM read-only 1 2 0

256-bit Avalon-MM read-only 1 4 0

For more information about the FPGA-to-HPS SDRAM interface, refer to the "SDRAM

Controller Subsystem" chapter of the Cyclone V or Arria V SoC Hard Processor System

Technical Reference Manual.

Note: To access the HPS SDRAM via the FPGA-to-SDRAM interface, follow the guidelines in

Access HPS SDRAM via the FPGA-to-SDRAM Interface on page 67.

Related Information

• SDRAM Controller Subsystem - Cyclone V Hard Processor System Technical

Reference Manual

• SDRAM Controller Subsystem - Arria V Hard Processor System Technical Reference

Manual

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

13

Page 14

2. Background: Comparison between Cyclone V SoC FPGA and Arria V SoC FPGA HPS Subsystems

AN-796 | 2018.06.18

2.1.3. Connecting Soft Logic to HPS Component

Designers can connect soft logic components to the HPS using the Cyclone V/Arria V

HPS component in Platform Designer (Standard).

Note: Refer to the "Introduction to the HPS Component" and "Instantiating the HPS

Component" chapters of the appropriate Hard Processor System Technical Reference

Manual to understand the interface and available options. To connect a FPGA soft IP

component to the HPS, Platform Designer (Standard) provides the component editor

tool. For more information, refer to the "Creating Platform Designer (Standard)

Components" chapter of the Intel® Quartus® Prime Standard Edition Handbook,

Volume 1: Design and Synthesis.

Note: When designing and configuring high bandwidth DMA masters and related buffering in

the FPGA core, refer to the DMA Considerations on page 24 section of this document.

The principles covered in that section apply to all high bandwidth DMA masters (for

example Platform Designer (Standard) DMA Controller components, integrated DMA

controllers in custom peripherals) and related buffering in the FPGA core that access

HPS resources (for example HPS SDRAM) through the FPGA-to-SDRAM and FPGA-toHPS bridge ports, not just tightly coupled Arm CPU accelerators.

Related Information

• Introduction to the HPS Component - Cyclone V Hard Processor System Technical

Reference Manual

• Instantiating the HPS Component - Cyclone V Hard Processor System Technical

Reference Manual

• Introduction to the HPS Component - Arria V Hard Processor System Technical

Reference Manual

• Instantiating the HPS Component - Arria V Hard Processor System Technical

Reference Manual

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

14

Page 15

AN-796 | 2018.06.18

3. Design Guidelines for HPS portion of SoC FPGAs

3.1. Start your SoC-FPGA design here

3.1.1. Recommended Starting Point for HPS-to-FPGA Interface Design

Depending on your topology, you can choose one of the two hardware reference

designs as a starting point for your hardware design.

GUIDELINE: Use the Golden System Reference Design (GSRD) as a starting

point for a loosely coupled system.

The Golden Hardware Reference Design (GHRD) has the optimum default settings and

timing that you can use as a basis for your "getting started" system. After initial

evaluation, you can move on to the Cyclone V HPS-to-FPGA Bridge Design Example

reference design to compare performance among the various FPGA-HPS interfaces.

Refer to "Golden Hardware Reference Design" for more information.

GUIDELINE: Use the Cyclone V HPS-to-FPGA Bridge Design Example

reference design to determine your optimum burst length and data-width for

accesses between FPGA logic and HPS.

The Cyclone V FPGA-to-HPS bridge design example contains modular SGDMAs in the

FPGA logic that allow you to program the burst length for data accesses from the FPGA

logic to the HPS.

Related Information

Golden Hardware Reference Design on page 50

3.1.2. Determining your SoC FPGA Topology

To determine which system topology best suits your application, you must first

determine how to partition your application into hardware and software.

GUIDELINE: Profile your software to identify functions for hardware

acceleration.

Use any good profiling tool (such as DS-5 streamline profiler) to identify functions that

are good candidates for hardware acceleration, and isolate functions that are best

implemented in software.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 16

Bank 8A HPS Column I/O

Bank 3B Bank 4ABank 3A

Bank 5B HPS Row I/OBank 5A

Transceiver Block

HPS Core

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

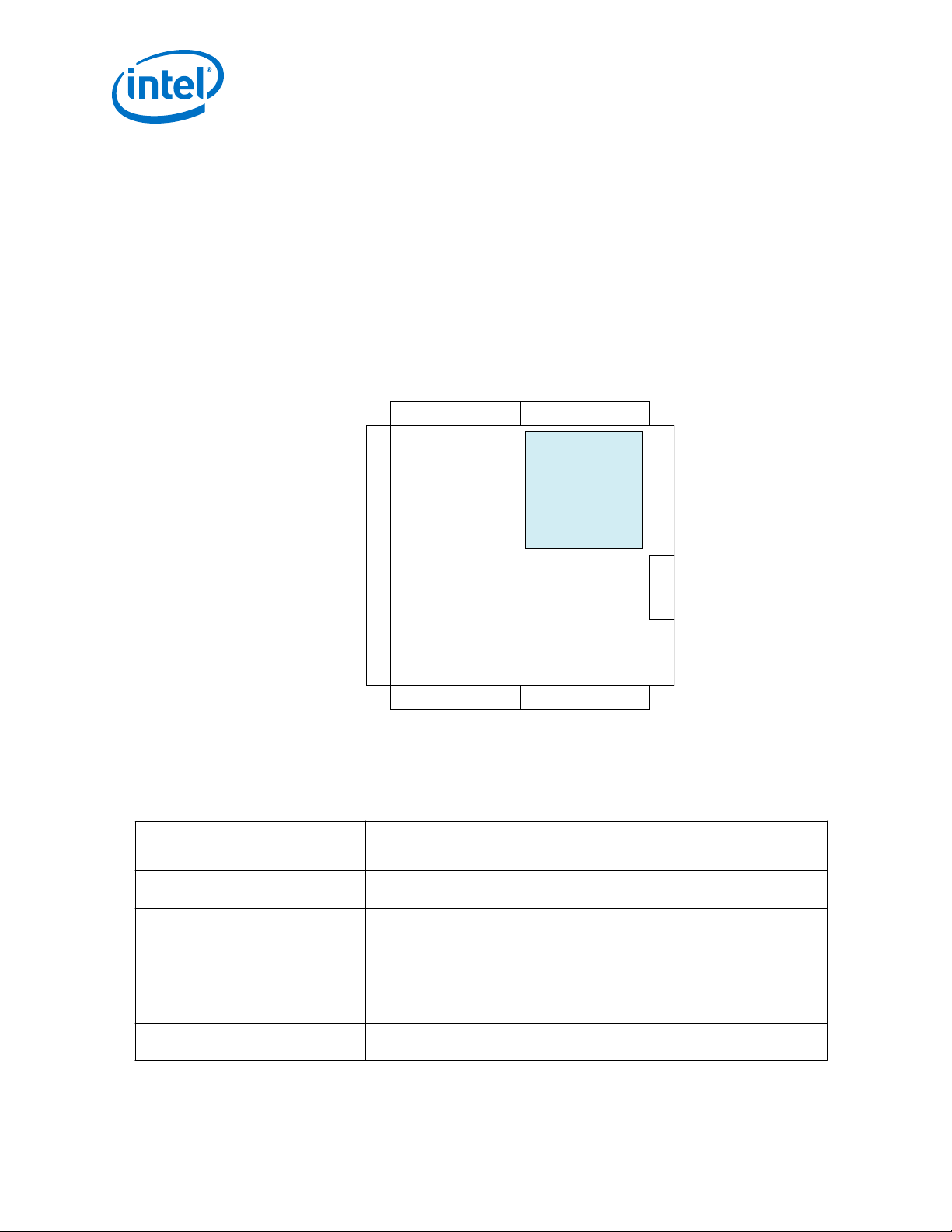

3.2. Design Considerations for Connecting Device I/O to HPS Peripherals and Memory

One of the most important considerations when configuring the HPS is to understand

how the I/O is organized in the Cyclone V/Arria V SoC devices. The HPS I/O is

physically divided into:

• HPS Column I/O: Contains the HPS Dedicated Function Pins and HPS Dedicated

I/O with loaner capability

• HPS Row I/O: Contains the HPS External Memory Interface (EMIF) I/O and HPS

General Purpose Input (GPI) pins

Figure 2. Example layout for HPS Column I/O and HPS Row I/O in Cyclone V SX and ST

device

Note: For more information regarding the I/O pin layout, refer to the appropriate "I/O

Features" chapter in the Cyclone V or Arria V Device Handbook, Volume 1: Device

Interfaces and Integration.

Table 6. HPS I/O Pin Type Summary

Pin Type Purpose

HPS Dedicated Function Pins Each I/O has only one function and cannot be used for other purposes.

HPS Dedicated I/O with loaner

capability

HPS External Memory Interface (EMIF)

I/O

HPS General Purpose Input (GPI) Pins These pins are also known as HLGPI pins. These input-only pins are located in

FPGA I/O These are general purpose I/O that can be used for FPGA logic and FPGA

These I/Os are primarily used by the HPS, but can be used on an individual basis

by the FPGA if the HPS is not using them.

These I/Os are used for connecting to the HPS external memory interface

(EMIF). Refer to the "External Memory Interface in Cyclone V Devices" or

"External Memory Interface in Arria V Devices" chapter in the respective device

handbook for more information regarding the layout of these I/O pins.

the same bank as the HPS EMIF I/O. Note that the smallest Cyclone V SoC

package U19 (484 pins) does not have any HPS GPI pins.

External Memory Interfaces.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

16

Page 17

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

The table below summarizes the characteristics of each I/O type.

Table 7. I/O Types

HPS Dedicated

Function Pins

Number of Available I/O 11 Up to 67

Voltages Supported 3.3V, 3.0V,

2.5V, 1.8V,

1.5V

Purpose Clock, Reset,

HPS JTAG

Timing Constraints Fixed Fixed Fixed for legal

Recommended Peripherals JTAG QSPI, NANDx8,

HPS Dedicated

I/O with

loaner

capability

(Cyclone V

SoC) and 94

(Arria V SoC)

3.3V, 3.0V,

2.5V, 1.8V,

1.5V

Boot source,

High speed

HPS

peripherals

eMMC, SD/

MMC, UART,

USB, EMAC

HPS External

Memory

Interface

Up to 86 14 (except for

LVDS I/O for

DDR3, DDR2

and LPDDR2

protocols

Connect to

SDRAM

combinations

DDR3, DDR2

and LPDDR2

SDRAM

HPS General

Purpose Input

Cyclone V SoC

U19 package )

Same as the

I/O bank

voltage used

for HPS EMIF

General

Purpose Input

Fixed User defined

GPI Slow speed

FPGA I/O

Up to 288

(Cyclone V

SoC) and Up to

592 (Arria V

SoC)

3.3V, 3.0V,

2.5V, 1.8V,

1.5V, 1.2V

General

Purpose I/O

peripherals

(I2C, SPI,

EMAC-MII)

Note: You can access the timing information to perform off-chip analysis by reviewing the

HPS timing in the Cyclone V Device Datasheet or Arria V Device Datasheet.

Related Information

• I/O Features in Cyclone V Devices

Chapter in the Cyclone V Device Handbook, Volume 1: Device Interfaces and

Integration

• I/O Features in Arria V Devices

Chapter in the Arria V Device Handbook, Volume 1: Device Interfaces and

Integration

3.2.1. HPS Pin Assignment Design Considerations

Because the HPS contains more peripherals than can all be connected to the HPS

Dedicated I/O, the HPS component in Platform Designer (Standard) offers pin

multiplexing settings as well as the option to route most of the peripherals into the

FPGA fabric. Any unused pins for the HPS Dedicated I/O with loaner capability

meanwhile can be used as general purpose I/O by the FPGA.

Note that a HPS I/O Bank can only support a single supply of either 1.2V, 1.35V, 1.5V,

1.8V, 2.5V, 3.0V, or 3.3V power supply, depending on the I/O standard required by the

specified bank. 1.35V is supported for HPS Row I/O bank only.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

17

Page 18

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

GUIDELINE: Ensure that you route USB, EMAC and Flash interfaces to HPS

Dedicated I/O first, starting with USB.

It is recommended that you start by routing high speed interfaces such as USB,

Ethernet, and flash to the HPS Dedicated I/O first. USB must be routed to HPS

Dedicated I/O because it is not available to the FPGA fabric. The flash boot source

must also be routed to the HPS dedicated I/O (and not any FPGA I/O) since these are

the only I/Os that are functional before the FPGA I/Os have been configured.

Note: For Cyclone V SoC U19 package (484 pin count) only one USB controller (instead of

two) is usable due to reduced number of available HPS I/O. For more information,

refer to Why can't I map USB0 to HPS IO in my Cyclone V SoC U19 package (484 pin

count)? in the Knowledge Base.

GUIDELINE: Enable the HPS GPI pins in the Platform Designer (Standard)

HPS Component if needed

By default, the HPS GPI interface is not enabled in Platform Designer (Standard). To

enable this interface, you must select the checkbox "Enable HLGPI interface" in the

Platform Designer (Standard) HPS Component for Cyclone V/Arria V. These pins are

then exposed as part of the Platform Designer (Standard) HPS Component Conduit

Interface and can be individually assigned at the top level of the design.

3.2.2. HPS I/O Settings: Constraints and Drive Strengths

GUIDELINE: Ensure that you have I/O settings for the HPS Dedicated I/O

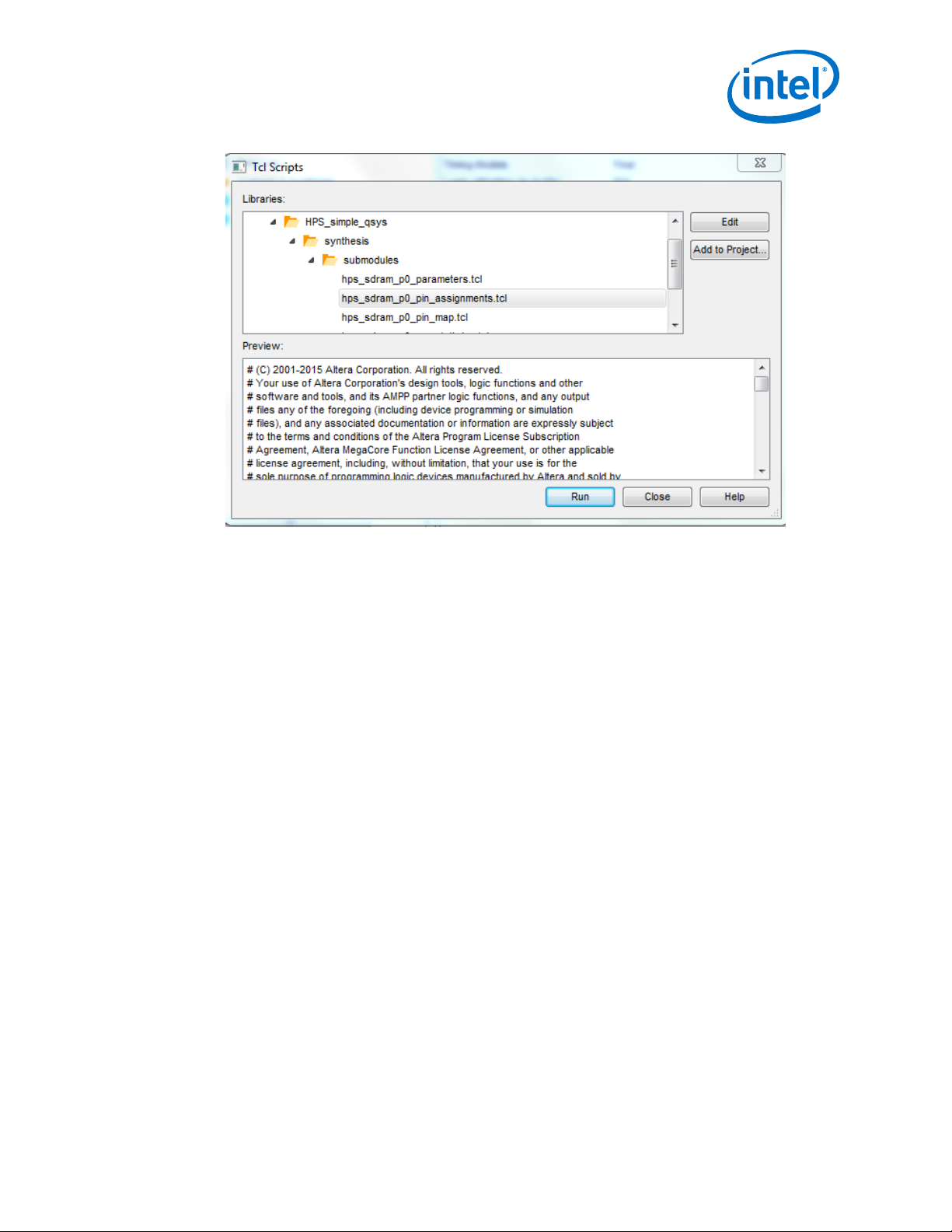

(drive strength, I/O standard, weak pull-up enable, etc.)

The HPS pin location assignments are managed automatically when you generate the

Platform Designer (Standard) system containing the HPS. As for the HPS SDRAM, the

I/O standard and termination settings are done once you run the

“hps_sdram_p0_pin_assignments.tcl” script that is created once the Platform

Designer (Standard) HPS Component has been generated.

Note:

You can locate the script “hps_sdram_p0_pin_assignments.tcl” in the following

directory once the Platform Designer (Standard) HPS Component has been generated:

<Quartus project directory>\<Platform Designer (Standard) file

name>\synthesis\submodule. Shown below is an example of selecting the script in

Intel Quartus Prime.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

18

Page 19

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

The only HPS I/O constraints you must manage are for HPS Dedicated Function Pins

and HPS Dedicated I/O. Constraints such as drive strength, I/O standards, and weak

pull-up enables are added to the Intel Quartus Prime project just like FPGA constraints

and are applied to the HPS at boot time when the second stage bootloader configures

the I/O. For FPGA I/O, the I/O constraints are applied to the FPGA configuration file.

Note: During power up, the HPS Dedicated I/O required for boot flash devices are configured

by the Boot ROM, depending on the BSEL values.

3.3. HPS Clocking and Reset Design Considerations

The main clock and resets for the HPS subsystem are HPS_CLK1, HPS_CLK2,

HPS_nPOR, HPS_nRST and HPS_PORSEL. HPS_CLK1 sources the Main PLL that

generates the clocks for the MPU, L3/L4 sub-systems, debug sub-system and the

Flash controllers. It can also be programmed to drive the Peripheral and SDRAM PLLs.

HPS_CLK2 meanwhile can be used as an alternative clock source to the Peripheral and

the SDRAM PLLs.

HPS_nPOR provides a cold reset input, and HPS_nRST provides a bidirectional warm

reset resource. As for the HPS_PORSEL, it is an input pin that can be used to select

either a standard POR delay or a fast POR delay for the HPS block.

Note: Refer to the Cyclone V Device Family Pin Connection Guidelines or Arria V GT, GX, ST,

and SX Device Family Pin Connection Guidelines for more information on connecting

the HPS clock and reset pins.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

19

Page 20

3. Design Guidelines for HPS portion of SoC FPGAs

3.3.1. HPS Clock Planning

GUIDELINE: Verify MPU and peripheral clocking using Platform Designer

(Standard)

Use Platform Designer (Standard) to initially define your HPS component

configuration. Set the HPS input clocks, and peripheral source clocks and frequencies.

Note any Platform Designer (Standard) warning or error messages. You can address

them by modifying clock settings. In some cases you might determine that a

particular warning condition does not impact your application.

3.3.2. Early Pin Planning and I/O Assignment Analysis

GUIDELINE: Choose an I/O voltage level for the HPS Dedicated Function I/O

HPS_CLK1, HPS_CLK2, HPS_nPOR and HPS_nRST are powered by

VCCRSTCLK_HPS. These HPS Dedicated Function Pins are LVCMOS/LVTTL at either

3.3V, 3.0V, 2.5V or 1.8V. The I/O signaling voltage for these pins are determined by

the supply level applied to VCCRSTCLK_HPS.

AN-796 | 2018.06.18

Note:

HPS_PORSEL can be connected to either VCCRSTCLK_HPS (for fast HPS POR delay) or

GND (for standard HPS POR delay).

Note:

VCCRSTCLK_HPS can share the same power and regulator with VCCIO_HPS and

VCCPD_HPS if they share the same voltage requirement. The functionality of powering

down the FPGA fabric, while keeping the HPS running, is not needed.

3.3.3. Pin Features and Connections for HPS JTAG, Clocks, Reset and PoR

GUIDELINE: With the HPS in use (powered), supply a free running clock on

HPS_CLK1 for SoC device HPS JTAG access.

Access to the HPS JTAG requires an active clock source driving HPS_CLK1.

GUIDELINE: When daisy chaining the FPGA and HPS JTAG for a single device,

ensure that the HPS JTAG is first device in the chain (located before the FPGA

JTAG).

Placing the HPS JTAG before the FPGA JTAG allows the ARM DS-5 debugger to initiate

warm reset to the HPS. However, in case of cold reset the entire JTAG chain is broken

until the cold reset completes, as discussed in the next section.

GUIDELINE: Consider board design to isolate HPS JTAG interface

The HPS Test Access Port (TAP) controller is reset on a cold reset. If the HPS JTAG and

FPGA JTAG are daisy-chained together, the entire JTAG chain is broken until the cold

reset completes. If access to the JTAG chain is required during HPS cold reset, design

the board to allow HPS JTAG to be bypassed.

GUIDELINE: HPS_nRST is an open-drain, bidirectional dedicated warm reset

I/O.

HPS_nRST is an active low, open-drain-type, bidirectional I/O. Externally asserting a

logic low to the HPS_nRST pin initiates a warm reset of the HPS subsystem. HPS warm

and cold reset can also be asserted from internal sources such as software-initiated

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

20

Page 21

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

resets and reset requests from the FPGA fabric. When the HPS is internally placed in a

warm reset state, the HPS component becomes a reset source and drives the

HPS_nRST pin low, resetting any connected board-level components.

GUIDELINE: Observe the minimum assertion time specifications of HPS_nPOR

and HPS_nRST.

Reset signals on the HPS_nPOR and HPS_nRST pins must be asserted for a minimum

number of HPS_CLK1 cycles as specified in the HPS section of the Cyclone V Device

Datasheet or Arria V Device Datasheet.

3.3.4. Internal Clocks

GUIDELINE: Avoid cascading PLLs between the HPS and FPGA

Cascading PLLs between the FPGA and HPS has not been characterized. Unless you

perform the jitter analysis, do not chain the FPGA and HPS PLLs together as a stable

clock coming out of the last PLL in the FPGA cannot be guaranteed. Output clocks from

the HPS are not intended to be fed into PLLs in the FPGA.

3.4. HPS EMIF Design Considerations

A critical component of the HPS subsystem is the external SDRAM memory. For

Cyclone V and Arria V SoC device, the HPS has a dedicated SDRAM Subsystem that

interfaces with the HPS External Memory Interface I/O.

Review the following guidelines to properly design the interface between the memory

and the HPS. These guidelines are essential to successfully connecting external

SDRAM to the HPS.

The External Memory Interface Handbook, Volume 3: Reference Material includes the

functional description of the HPS memory controller. The supported interface options

are listed for DDR3, DDR2 and LPDDR2.

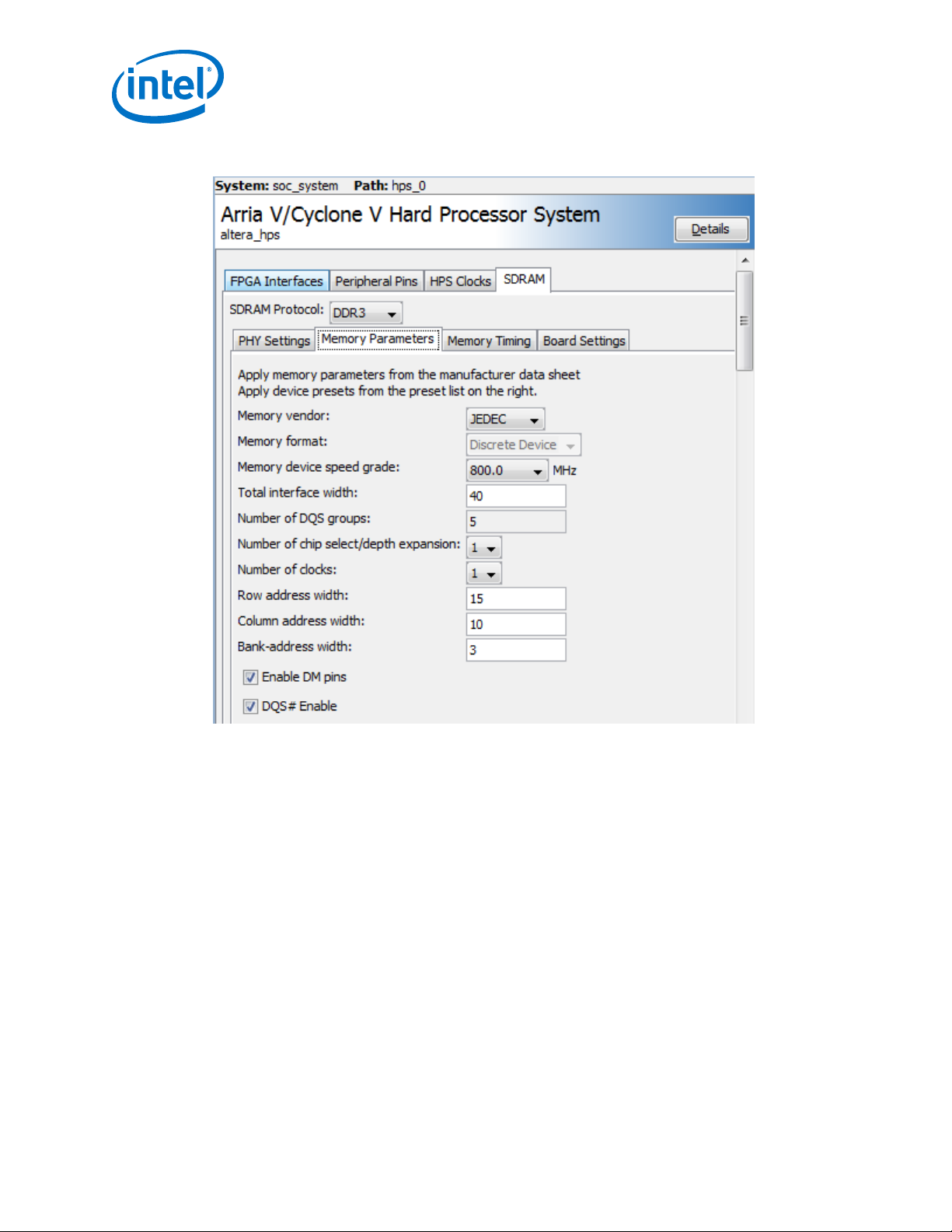

3.4.1. Considerations for Connecting HPS to SDRAM

GUIDELINE: Ensure that the HPS memory controller Data Mask (DM) pins are

enabled

In the HPS Component in Platform Designer (Standard), ensure that the checkbox to

enable the data mask pins is enabled. If this control is not enabled, data corruption

occurs any time a master accesses data in SDRAM that is smaller than the native word

size of the memory.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

21

Page 22

3. Design Guidelines for HPS portion of SoC FPGAs

Figure 3. Setting the Enable DM Pins Option in HPS Component

AN-796 | 2018.06.18

Determine your SDRAM Memory type and bit width. Cyclone V and Arria V SoC devices

offer DDR3, DDR2 and LPDDR2 SDRAM support for the HPS.

GUIDELINE: Ensure that you choose only DDR3, DDR2, or LPDDR2

components or modules in configurations supported by the Cyclone V or Arria

V HPS EMIF for your specific device/package combination.

The External Memory Interface Spec Estimator, available on the External Memory

Interface page, is a parametric tool that allows you to compare supported external

memory interface types, configurations and maximum performance characteristics in

Intel FPGA and SoC devices.

First, filter the “Family” to select only Cyclone V /Arria V SoC device. Then, follow on

by using the filter on “Interface Type” to choose only “HPS Hard Controller”

GUIDELINE: Ensure that in the HPS Component, the Memory Clock Frequency

is supported by the device speed grade.

To obtain the maximum supported memory clock frequency for the device speed

grade, refer to the External Memory Interface Spec Estimator, available on the

External Memory Interface page.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

22

Page 23

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

3.4.2. HPS SDRAM I/O Locations

The Cyclone V and Arria V SoC HPS External Memory Interface I/O locations are fixed,

depending on the type of memory used. You can refer to the device Pin Out files,

under the “HMC Pin Assignment for DDR3/DDR2” and “HMC Pin Assignment

for LPDDR2” for exact I/O pins used by the respective memory interface pins.

Note: Unused HPS External Memory Interface I/O Pins cannot be assigned to HPS

Peripherals, or used by the FPGA as Loaner IO.

Note: The smallest Cyclone V SoC package U19 (484 pin count) has narrower HPS SDRAM

width (32-bit) compared to larger packages (40-bit). Refer to the "External Memory

Interfaces in Cyclone V Devices" chapter in Cyclone V Device Handbook Volume 1:

Device Interfaces and Integration for more information.

Related Information

Documentation: Pin-Out Files for Intel FPGA Devices

3.4.3. Integrating the HPS EMIF with the SoC FPGA Device

Consider the following when integrating the Cyclone V or Arria V SoC HPS EMIF with

the rest of the SoC system design.

GUIDELINE: Follow the guidelines for optimizing bandwidth for all masters

accessing the HPS SDRAM

Accesses to SDRAM connected to the HPS EMIF go through the L3 Interconnect

(except for FPGA-to-SDRAM bridge). When designing and configuring high bandwidth

DMA masters and related buffering in the FPGA core, refer to DMA Considerations on

page 24. The principles covered in that section apply to all high bandwidth DMA

masters (for example DMA controller components, integrated DMA controllers in

custom peripherals) and related buffering in the FPGA core that access HPS resources

(for example HPS SDRAM) through the FPGA-to-SDRAM and FPGA-to-HPS bridge

ports, not just tightly-coupled HPS hardware accelerators.

3.4.4. HPS Memory Debug

The Cyclone V / Arria V HPS EMIF do not support the external memory interface

toolkit. To debug the HPS EMIF, you can change the settings inside the preloader

software to enable Runtime Calibration Report and Debug Level info. In addition, you

can use the preloader software to check the status of HPS SDRAM PLL.

Refer to Using the Preloader To Debug the HPS SDRAM on page 63 for more

information.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

23

Page 24

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

3.5. DMA Considerations

3.5.1. Choosing a DMA Controller

Choose the DMA implementation best suited to your design

When DMA is required to improve system performance, you have the option to use the

DMA integrated into the HPS or a soft DMA module in the FPGA. When making the

choice of which option to use, you should consider the following:

• HPS DMA: primarily used to move data to and from other slow-speed HPS

modules, such as SPI and I2C, as well as to do memcopy functions to and from

HPS memories.

• Soft DMAs: primarily used to move data to and from peripherals in the FPGA.

3.5.2. Optimizing DMA Master Bandwidth through HPS Interconnect

FPGA DMA masters have access to HPS resources through the FPGA-to-HPS Bridge

and FPGA-to-SDRAM Interface, configurable in the HPS Platform Designer (Standard)

Component. The HPS SDRAM controller multi-port-front end (MPFE) provides

arbitration for these resources and enforce Quality of Service (QoS) settings. When

planning for and designing DMA masters and related buffering that access resources

through the HPS interconnect, study the architecture of the HPS interconnect and

consider the following guidance and resources available for optimizing bandwidth

through the interconnect.

GUIDELINE: Utilize the Cyclone V FPGA-to-HPS Bridge Design Example to

tune for performance

The Cyclone V FPGA-to-HPS Bridge Design Example is a useful platform for modeling

specific data traffic access patterns between the FPGA and HPS resources.

The example design includes a utility that can select the datapaths between

endpoints, select transaction characteristics (for example, burst lengths), and report

transfer bandwidth. This utility runs on the ARM Cortex* A-9 processor in the HPS.

3.5.3. Timing Closure for FPGA Accelerators

The HPS bridges and FPGA-to-SDRAM interfaces exposed to the FPGA are synchronous

and clock crossing is performed within the interface itself. As a result, you only need

to ensure that both the FPGA-facing logic and your user design close timing in Timing

Analyzer. Interrupts are considered asynchronous by the HPS, and as a result the HPS

logic resynchronizes them to the internal HPS clock domain so there is no need to

close timing for them.

Conduits carry signals that do not fit into any standard interface supported by

Platform Designer (Standard). Examples of these are HPS peripheral external

interfaces routed into the FPGA fabric or the HPS DMA peripheral request interfaces.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

24

Page 25

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

3.6. Managing Coherency for FPGA Accelerators

Data shared between the HPS and the FPGA logic can be modified at any time, by

either the HPS or the FPGA. Many applications require data coherency, which means

that changes are propagated throughout the system, so that every master accesses

the most up-to-date data value.

When you design for data coherency, first you must determine which data transfers

need to be coherent. By default all access between the FPGA and HPS are assumed to

be non-coherent unless coherency is explicitly managed by software or using coherent

hardware features of the HPS (SCU and ACP).

To determine if peripherals in the FPGA need coherent access to HPS memory, answer

the follow questions:

• Does the MPU need to access data generated by my FPGA peripheral?

• Does the FPGA peripheral need to access data generated by the MPU?

If the answer to either question is "Yes", the data must be coherent. You can use the

ACP to keep the FPGA coherent with cacheable data in the HPS.

3.6.1. Cache Coherency

There are several mechanisms via which coherency are maintained through the

system:

The HPS maintains cache coherency at a level 1 memory subsystem level within the

MPU subsystem. The snoop control unit (SCU) built into the MPU subsystem maintains

cache coherency between the two L1 data caches using the modified-exclusiveshared-invalid (MESI) coherency protocol.

3.6.2. Coherency between FPGA Logic and HPS: Accelerator Coherency Port (ACP)

The accelerator coherency port (ACP) of the SCU provides a means for other masters

in the system, including logic implemented in the FPGA fabric, to perform cache

coherent accesses. Accesses to the ACP are only unidirectional in terms of cache

coherency meaning at the time of the access the data is up to date, but the SCU is not

responsible for maintaining coherency of that data over time. For example, if a master

in the FPGA reads data from the ACP and then a processor updates that same data in

memory, then the FPGA no longer contains the most up to date copy of the data.

3.6.3. Data Size Impacts ACP Performance

Performance explorations of accelerators using ACP show that as size of packets

transferred by AXI master via the ACP port increases the accelerator performance

increases but only up to a point. After that point, it is no longer possible to cache the

entire data packet, and the accelerator suffers performance degradation.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

25

Page 26

3. Design Guidelines for HPS portion of SoC FPGAs

GUIDELINE: Use ACP for managing coherency for small data size accesses,

manage coherency for large data in software.

3.6.4. FPGA Access to ACP via AXI or Avalon-MM

The AXI protocol allows masters to issue cacheable accesses whereas the Avalon-MM

protocol does not support this feature. For an FPGA master to perform a cacheable

access, the master must adhere to the AXI protocol and be able to perform cacheable

accesses, with ARCACHE[1] or AWCACHE[1] set to 1 and ARUSER[0] or AWUSER[0]

set to 1.

3.6.5. Data Alignment for ACP and L2 Cache ECC accesses

The L2 cache performs error detection and correction in groups of 64 bits without the

use of byte enables.

GUIDELINE: Accesses to the ACP must be 64-bit aligned, full 64-bit accesses,

and no byte lanes can disabled on write.

The main L3 switch and the ACP port are both 64 bits wide, so it is only necessary to

provide 64-bit aligned cache coherent accesses that are 64 bits wide after resizing.

Data resizing can occur in the L3 interconnect between requesting master and the

ACP. As a result, a 32-bit access can be compatible with the L2 cache ECC logic if the

access is aligned to 8-byte boundaries and the master performs bursts of size 2, 4, 8,

or 16. Data resizing can also occur within the FPGA-to-HPS bridge.

AN-796 | 2018.06.18

GUIDELINE: The simplest way to ensure that accesses from the FPGA meets

the L2 cache ECC requirements is to implement 64-bit masters in the FPGA

fabric and configure the FPGA-to-HPS bridge to expose a 64-bit slave port.

This ensures that no resizing of AXI transactions is necessary. Full 64-bit

accesses have to be made by the logic in the FPGA as well.

3.7. IP Debug Tools

The Intel Quartus Prime Design Software includes many IP and system-level debug

tools used in FPGA hardware designs.

The following tools are commonly used for system and IP debug in embedded

systems:

• Signal Tap - On-chip logic analyzer constructed from FPGA resources

• Bus functional models

— Avalon-MM v2 protocol

— AXI v3 protocol

• System console - Services-based API for controlling soft logic and moving data to/

from the FPGA

Each debug tool is introduced at different stages of the hardware design. In a typical

hardware design flow, the developer follows these high-level verification steps:

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

26

Page 27

3. Design Guidelines for HPS portion of SoC FPGAs

AN-796 | 2018.06.18

1. IP Creation in RTL

2. Testbench and BFM verification of the IP

3. In silicon testing of the IP using system console to drive stimuli into memorymapped or streaming interface

4. In silicon testing of the IP using low level software run on the processor in the HPS

In the case of Signal Tap and system console, if both use the FPGA JTAG interface to

communicate data then they can be used simultaneously. For example, you may

instrument a trigger condition in Signal Tap and cause the trigger condition to occur

via the JTAG-to-Avalon bridge IP controlled by System console. These tools are also

capable of being used simultaneously with the HPS tools that communicate over JTAG.

There are two JTAG interfaces on the Cyclone V/Arria V SoC device. The first interface

is connected to the FPGA side of the device, while the second interface is connected to

the HPS debug access port (DAP).

Related Information

• "Design Debugging Using In-System Sources and Probes" chapter of the Intel

Quartus Prime Standard Edition Handbook Volume 3: Verification

Description of Signal Tap

• Avalon-MM v2 protocol

• AXI v3 protocol

• "System Debugging Tools Overview" chapter of the Intel Quartus Prime Standard

Edition Handbook Volume 3: Verification

Description of System Console

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

27

Page 28

AN-796 | 2018.06.18

4. Board Design Guidelines for SoC FPGAs

4.1. Board Bring Up Considerations

This section describes the considerations that are useful for board bring up.

4.1.1. Reserved BSEL Setting

During initial stages of bring-up, if a JTAG connection cannot be established to the

target, it may be beneficial to set BSEL to 0x0 “Reserved” setting to prevent the

BootROM from trying to boot from a specific boot source. Then a test program could

be downloaded and ran with a debugger.

4.2. Boot and Configuration Design Considerations

4.2.1. Boot Design Considerations

4.2.1.1. Boot Source

GUIDELINE: Determine which boot source is to be supported.

The HPS side of the Cyclone V SoC / Arria V SoC can be booted from a variety of

sources, as selected by the BSEL pins:

• SD/MMC Flash

• QSPI Flash

• NAND Flash

• FPGA Fabric

Each possible boot source has its own strengths:

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 29

4. Board Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

• SD cards are cheap, universally available, and have large storage capacities.

Industrial versions available, with improved reliability. They are managed NAND

flash, so wear leveling and bad block management are performed internally.

• eMMC devices have smaller packages, are available in large capacities, and can be

more reliable than SD. They are not removable, with can be a plus, allowing a

more rugged operation.

• QSPI devices are very reliable, typically with a minimum 100,000 cycles of erase

cycles per sector. However, they have less capacity than the other options. They

are typically used as a boot source, but not as an application filesystem.

• NAND devices are available in large sizes, but they are unmanaged NAND, which

means that techniques such as wear leveling and bad block management need to

be implemented in software.

• FPGA boot allows HPS to boot without the need of an external Flash device. The

FPGA boot memory can be synthesized our of FPGA resources (typically preinitialized embedded memory blocks) or can be memory connected to the FPGA

such as an external SRAM or SDRAM. To boot from FPGA, the FPGA must be

configured using a traditional configuration mechanism.

4.2.1.2. Select Desired Flash Device

GUIDELINE: Select the boot flash device.

When choosing a flash device to incorporate with SoC FPGA devices, it is important to

consider the following:

• Is the flash device compatible with the HPS boot ROM ?: The HPS can only

boot from flash devices supported in the boot ROM.

• Is the device verified to work and supported by software like Preloader,

U-Boot and Linux ?: For supported devices, Intel provides the Preloader, U-Boot

and Linux software. For other devices, this software must be developed by the

user.

• Is the flash device supported by the HPS Flash Programmer?: The HPS

Flash Programmer enables writing to flash using a JTAG connection, primarily to

program the initial pre-loader/bootloader image. If the device is not supported by

the HPS Programmer, other flash programming methods may be used, such as

using the HPS to program flash. For example, the flash programming capabilities

of U-Boot can be used.

Refer to Supported Flash Devices for Cyclone V SoC and Arria V SoC for more

information.

4.2.1.3. BSEL Options

GUIDELINE: Configure the BSEL pins for the selected boot source.

The boot source is selected by means of BSEL pins.

It may be beneficial to change the boot source for debugging purposes, even if the

board does not have available another boot source. For example, on a board booting

from QSPI it may be beneficial to select the reserved boot so that BootROM would not

do anything. Or select boot from FPGA and put a test image in the FPGA fabric.

If the system allows it (space constraints etc.) plan to provide either switches or at

least resistors to be able to change BSEL as needed.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

29

Page 30

4. Board Design Guidelines for SoC FPGAs

4.2.1.4. Boot Clock

GUIDELINE: Determine boot clock source.

The boot clock influences the boot duration. Consider your system boot speed

requirement as the primary factor in choosing the book clock. The system boot time

requirement depends on how fast the FPGA needs to be configured for an appropriate

response time, and how quickly the HPS software must be booted. The HPS software

boot speed is influenced by the following factors:

•

Value of external clock to the HPS (i.e. OSC1 clock)

• Boot flash source interface operation frequency

Boot clock configurations are selected with the CSEL pins. Available combinations are

described in the appropriate Hard Processor System Technical Reference Manual.

Note: CSEL pins are not used when booting from FPGA fabric.

Related Information

• Cyclone V Hard Processor System Technical Reference Manual

• Arria V Hard Processor System Technical Reference Manual

AN-796 | 2018.06.18

4.2.1.5. CSEL Options

GUIDELINE: Provide a method to configure CSEL options.

For debugging purposes, it may be beneficial to allow setting of various CSEL values

even if the end product requires just one CSEL setting. If possible, design the board in

such a way that the CSEL configuration can be varied even if a single value will

eventually be used. This configurability may be useful for debugging and could be

done by resistors, jumpers or switches.

4.2.1.6. Selecting NAND Flash Devices

GUIDELINE: Select a NAND flash that is ONFI 1.0 compliant.

When booting from NAND, ensure that the selected device is ONFI 1.0 compliant.

The NAND device used for booting must also have a ×8 interface, and only a single

pair of ce# and rb# pins.

Although some non-ONFI 1.0 compliant devices are compatible with the BootROM, the

HPS Flash Programmer only supports ONFI compliant devices.

4.2.1.7. Determine Flash Programming Method

GUIDELINE: Ensure that the board is configured properly to support flash

programming.

The HPS Flash Programmer is a tool provided with SoC EDS that can be used to

program QSPI and NAND flash devices on Cyclone V / Arria V SoC boards. The tool is

intended to write relatively small amounts of data (for example the preloader) since it

works over JTAG and has a limited speed.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

30

Page 31

4. Board Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

If the HPS Flash Programmer tool is to be used, confirm that it supports the device

you are planning to use. The supported devices are listed in the Intel SoC FPGA

Embedded Development Suite User Guide.

Other ways to program the flash devices are:

• Program Flash using a debugger (for example DS-5)

• Program Flash from U-Boot

• Program Flash from Linux (or other OS) console

• Program Flash by means of dedicated hardware

Related Information

Intel® SoC FPGA Embedded Development Suite User Guide

4.2.1.8. For QSPI and SD/MMC/eMMC Provide Flash Memory Reset

GUIDELINE: Ensure that the QSPI and SD/MMC/eMMC devices have a

mechanism to be reset when the HPS is reset.

The QSPI and SD/MMC/eMMC flash devices can potentially be put in a state by

software where the BootROM cannot access them successfully, which may trigger a

boot failure on the next reset. This problem can occur because the HPS is reset, but

the flash part is not reset.

It is therefore required to reset the QSPI and SD/MMC/eMMC boot flash devices each

time there is an HPS reset (warm or cold).

Note that some devices do not have a reset pin. In such a case, you must power-cycle

the flash by other means, for example with a MOSFET. Pay attention to minimum

required reset pulse duration.

4.2.1.9. Selecting QSPI Flash Devices

GUIDELINE: For bare-metal applications, avoid using a QSPI flash device

larger than 16 MB

QSPI flash devices of 16 MB or less always support three-byte addressing. Therefore,

they are accessible to the HPS Boot ROM. With such devices, you do not need to reset

or power-cycle the flash when the HPS undergoes cold or warm reset.

GUIDELINE: With a QSPI device larger than 16 MB, use QSPI extended 4-byte

addressing commands if supported by the device

Some QSPI flash devices support an extended command set, allowing the master to

use four-byte addressing without switching to four-byte addressing mode. If you use

the extended command set, you can leave the flash device in three-byte addressing

mode, so that the Boot ROM can access it on the next reset cycle without resetting or

power-cycling the flash device.

For detailed information about booting from QSPI, refer to CV SoC and AV Soc QSPI

Boot on RocketBoards.org.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

31

Page 32

4.2.2. Configuration

The Cyclone V / Arria V SoC devices support two main type sof configuration flows:

• Traditional FPGA configuration

• HPS-initiated FPGA configuration

HPS-initiated configuration uses fast passive parallel (FPP) mode allowing the HPS to

configure the FPGA using storage locations accessible to the HPS such as QSPI,

SD/MMC and NAND flash. The FPGA configuration flows for the Cyclone V/Arria V SoC

are the same for the Cyclone V/Arria V FPGA devices where an external configuration

data source is connected to the control block in the FPGA.

4.2.2.1. Traditional Configuration

The traditional FPGA configuration flow is where the FPGA is configured by an external

source such as JTAG, active serial or fast passive parallel.

4.2.2.2. HPS Initiated Configuration

When the device is powered and the HPS begin executing the software in the boot

ROM, all the device I/O default to an input tri-state mode of operation. The boot ROM

configures the dedicated boot I/O based on the sampled BSEL pins.

4. Board Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

4.2.3. Reference Materials

Refer to the following reference materials for additional information.

Related Information

• Intel® SoC FPGA Embedded Development Suite User Guide

• Support tab on Cyclone V SoCs

Cyclone V SoC documentation

• Support tab on Arria V SoCs

Arria V SoC documentation

• SoC Embedded Development Suite Getting Started Guides

• Golden System Reference Design (GSRD) User Manuals

• AN-709: HPS SoC Boot Guide - Cyclone V SoC Development Kit

4.3. HPS Power Design Considerations

For design considerations and recommendations on power consumption and thermal

analysis, SoC device pin connections, supply design and decoupling, refer to the Arria

V and Cyclone V Design Guidelines.

The following sections are supplemental for SoC devices.

Related Information

Arria V and Cyclone V Design Guidelines

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

32

Page 33

4. Board Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

4.3.1. Early System and Board Planning

4.3.1.1. Early Power Estimation

Follow the guidelines in the Early Power Estimation website for using the PowerPlay

Early Power Estimation (EPE) spreadsheets.

In addition, consider the following guidelines for Cyclone V and Arria V SoC devices

when using the EPE spreadsheet.

GUIDELINE: Use the Main worksheet to select “Maximum” for the Power

Characteristics setting.

When estimating power consumption for the purposes of designing an adequate power

supply that can meet the maximum power requirements across process, voltage and

temperature (PVT), use the device maximum power characteristics.

GUIDELINE: Use the I/O worksheet to add HPS peripherals assigned to FPGA

I/O.

This tab is where you describe the various configurations of I/O Elements (IOEs) in

your application. Use the IO-IP tab to describe the controller IP behind each set of I/O.

For HPS peripherals assigned to FPGA I/O, add rows to the spreadsheet as necessary

to describe the different HPS peripheral I/O characteristics in your design.

GUIDELINE: Use the HPS worksheet to select the Frequency, Application, and

if applicable, the Application Mode for each CPU.

The Application/Application Mode settings for each CPU allow you to select from a list

of industry standard benchmarks to model CPU utilization in your application. You can

also select “Custom” for defining a unique set of CPU utilization parameters across the

ALUs and cache memories.

GUIDELINE: Use the HPS worksheet to update the HPS SDRAM Type,

Frequency and Width.

Note that the selection of SDRAM type also updates the I/O voltage for Bank 6A to 6B.

GUIDELINE: Use the HPS worksheet to update the HPS I/O Bank Voltage and

Peripheral Usage

Before you select Peripheral voltage from the drop-down list, ensure that you have at

least one HPS I/O Bank that is configured to the same voltage.

GUIDELINE: For Cyclone V SoC with L power option, apply the appropriate

multiplication factor when calculating the total static power.

There is no L-power option in the EPE for Cyclone V, hence you need to calculate the

total static power using the following steps:

1. Key in the design and resource utilization using the standard (non-L) part number.

2. Once total static power is obtained, apply a multiplication factor of 0.7 (for 25K-LE

and 40K-LE devices) or 0.8 (for 85K-LE and 110K-LE devices) to calculate the

lower static power for the L-power option devices.

Note:

The multiplication factor only applies to total static power and not dynamic power.

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

33

Page 34

4. Board Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

Related Information

Early Power Estimators (EPE) and Power Analyzer