Page 1

Intel® Arria® 10 SDI II IP Core

Design Example User Guide

Updated for Intel® Quartus® Prime Design Suite: 17.0

Subscribe

Send Feedback

UG-20076 | 2017.05.08

Latest document on the web: PDF | HTML

Page 2

Contents

Contents

1 SDI II Design Example Quick Start Guide........................................................................ 3

1.1 Directory Structure................................................................................................. 3

1.2 Hardware and Software Requirements.......................................................................6

1.3 Generating the Design.............................................................................................7

1.4 Simulating the Design............................................................................................. 8

1.5 Compiling and Testing the Design ............................................................................ 8

1.5.1 Connection and Settings Guidelines...............................................................9

1.5.2 Design Limitations for Serial Loopback Design...............................................11

2 SDI II Design Example Detailed Description.................................................................. 13

2.1 Parallel Loopback Design Examples......................................................................... 14

2.2 Serial Loopback Design Examples............................................................................18

2.3 Design Components.............................................................................................. 22

2.4 Clocking Scheme Signals....................................................................................... 25

2.5 Interface Signals...................................................................................................28

2.6 Video Pattern Generator Parameters........................................................................ 39

2.7 Hardware Setup....................................................................................................40

2.8 Simulation Testbench............................................................................................ 41

A SDI II IP Core Design Example User Guide Archives......................................................44

B Revision History for SDI II IP Core Design Example User Guide................................... 45

Intel® Arria® 10 SDI II IP Core Design Example User Guide

2

Page 3

Design

Example

Generation

Compilation

(Simulator)

Functional

Simulation

Compilation

(Quartus Prime)

Hardware

Testing

UG-20076 | 2017.05.08

1 SDI II Design Example Quick Start Guide

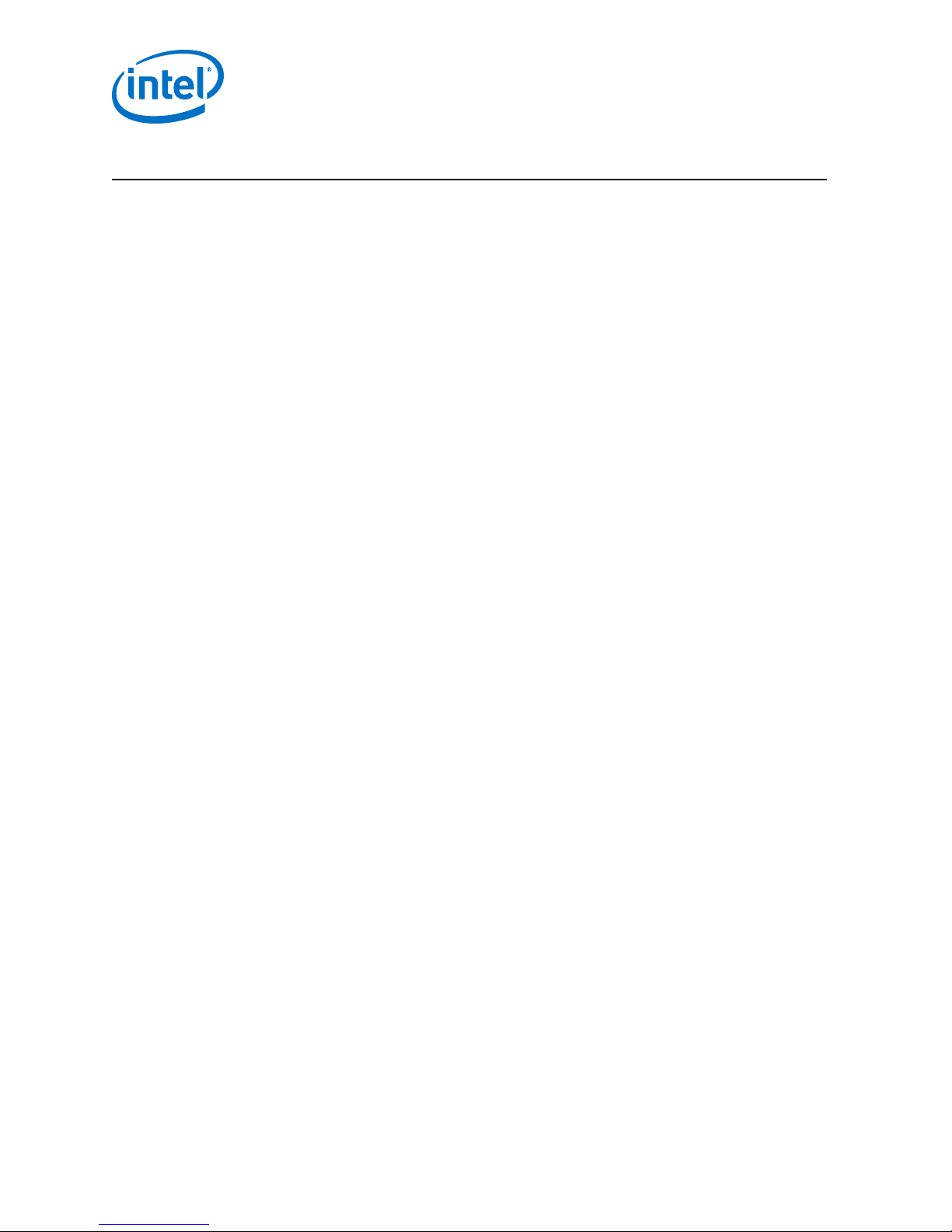

The SDI II IP core design examples for Intel® Arria® 10 devices feature a simulating

testbench and a hardware design that supports compilation and hardware testing.

When you generate a design example, the parameter editor automatically creates the

files necessary to simulate, compile, and test the design in hardware.

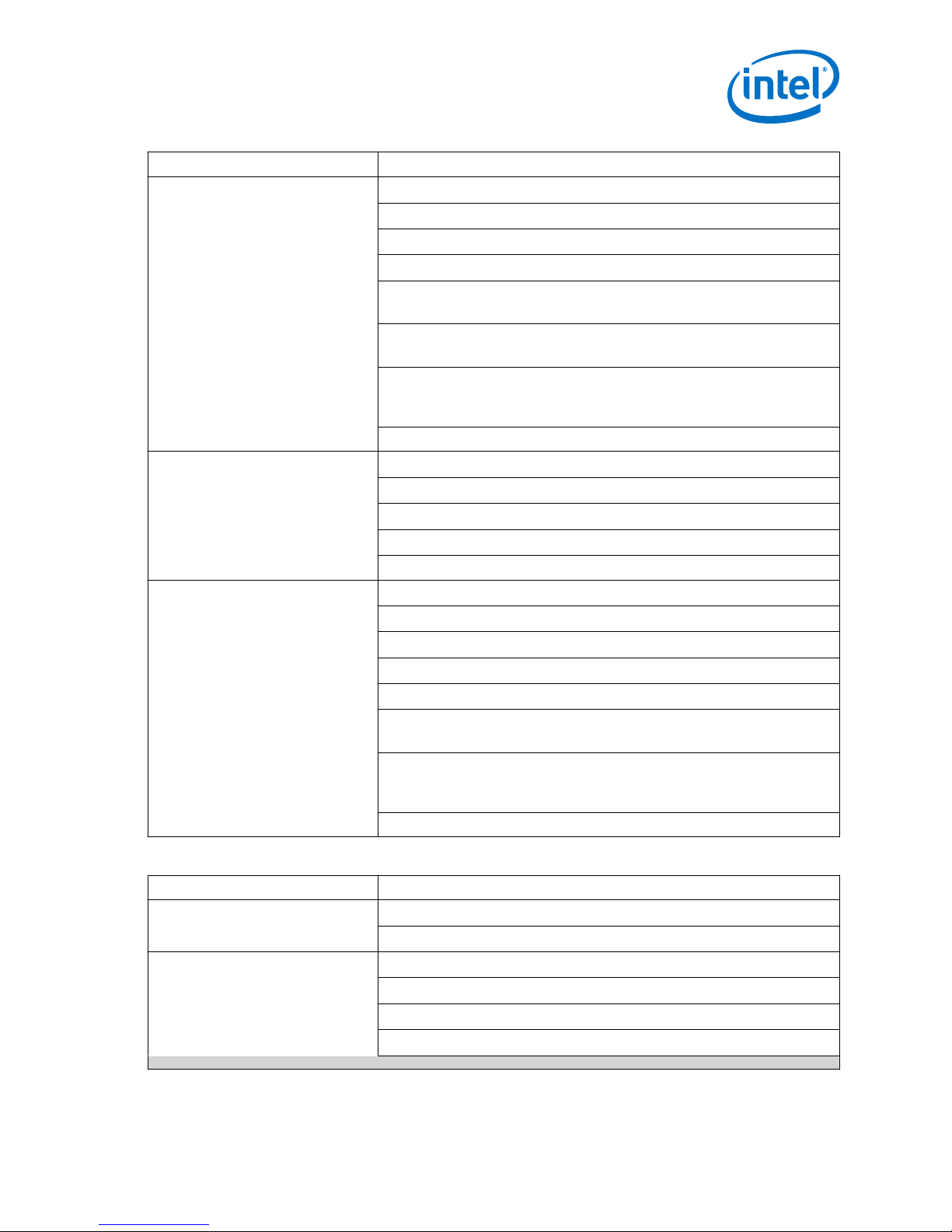

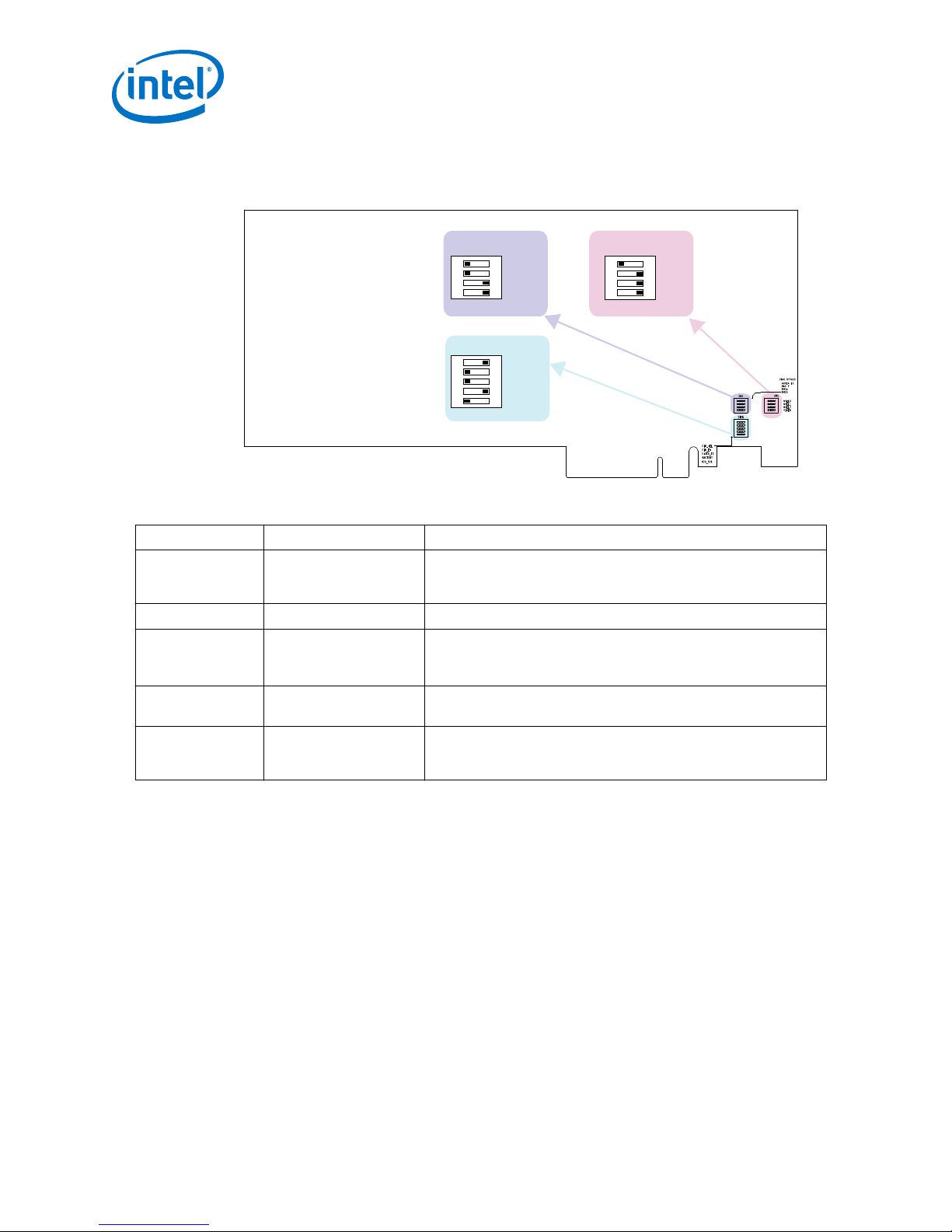

Figure 1. Development Steps

Related Links

• SDI II IP Core User Guide

• SDI II IP Core Design Example User Guide Archives on page 44

Provides a list of user guides for previous versions of the SDI II IP core design

examples.

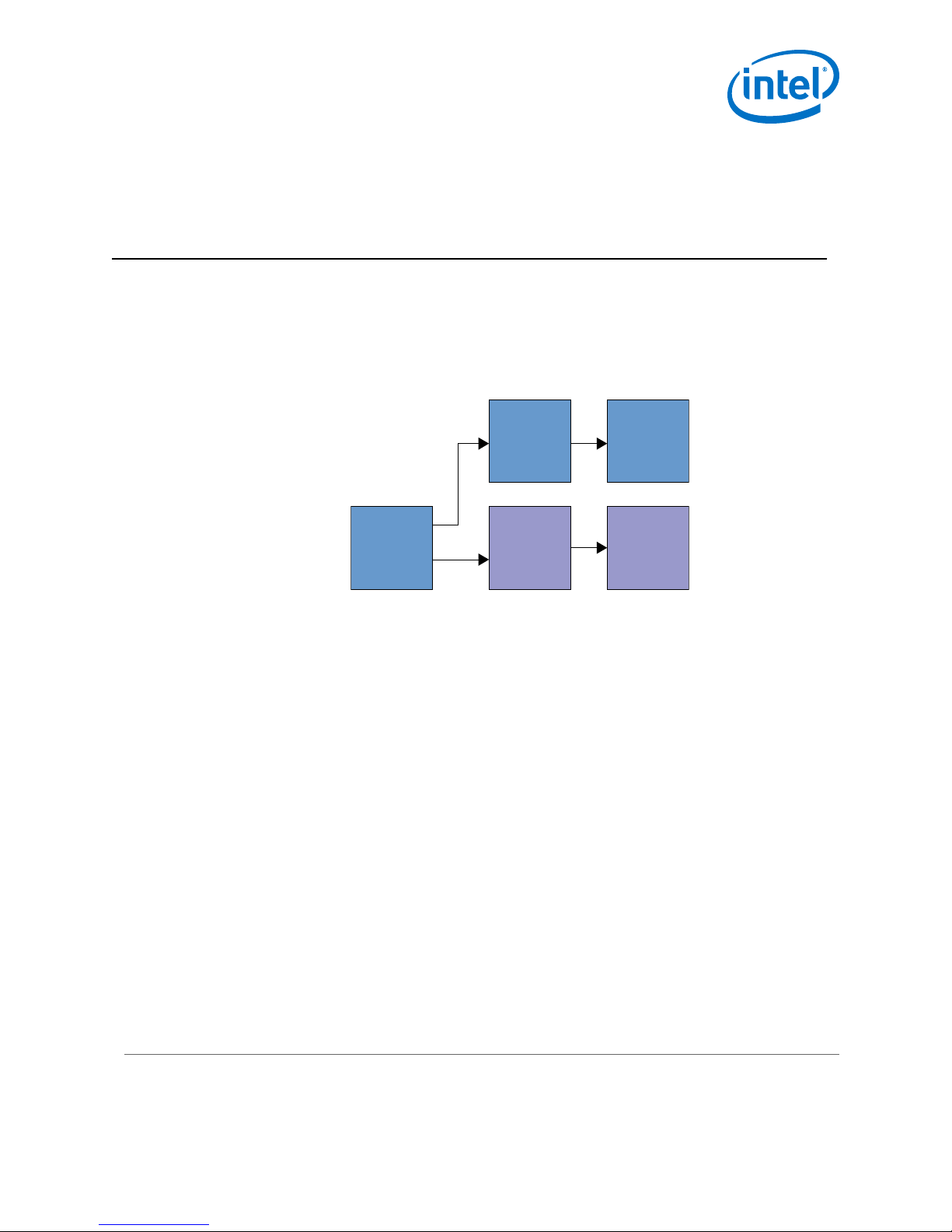

1.1 Directory Structure

The directories contain the generated files for the design examples.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2008

Registered

Page 4

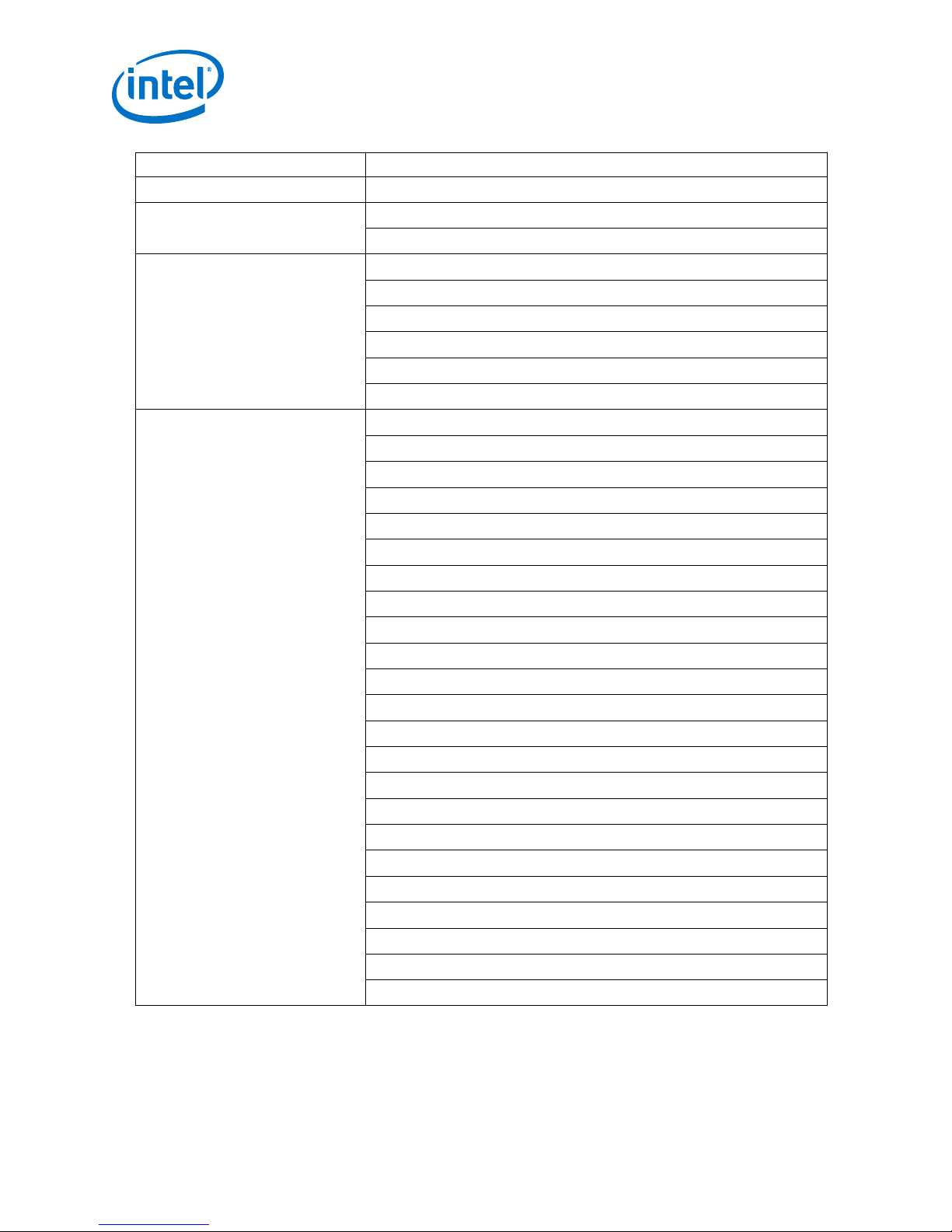

Figure 2. Directory Structure for the Design Examples

<Design Example>

db/qdb

quartus

sdi_ii_a10_demo.qpf

sdi_ii_a10_demo.qsf

rtl

sdi_ii_a10_demo.v

sdi_ii_a10_demo.sdc

edge_detector.sv

clock_heartbeat.sv

a10_reconfig_arbiter.sv (optional)

vid_pattgen (for serial loopback design)

rx (for simplex mode design)

tx (for simplex mode design)

du (for duplex mode design)

loopback (for parallel loopback design)

<clk_ctrl.qsys generated>(optional)

<pll_148 qsys generated> (optional)

clk_ctrl.qsys (optional)

pll_148.qsys (optional)

aldec

cadence

mentor

simulation

synopsys

testbench

tpg.ctrl.tcl (optional)

hwtest

(for serial loopback design)

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

Table 1. Other Generated Files in RTL Folder

Folders Files

vid_pattgen /sdi_ii_colorbar_gen.v

loopback /loopback_top.v

Intel® Arria® 10 SDI II IP Core Design Example User Guide

4

du /du_top.v

/sdi_ii_ed_vid_pattgen.v

/sdi_ii_makeframe.v

/sdi_ii_patho_gen.v

/jtag.sdc

/pattgen_ctrl.qsys

<qsys generated folder>

/fifo/sdi_ii_ed_loopback.sdc

/fifo/sdi_ii_ed_loopback.v

/pfd/clock_crossing.v (optional)

/pfd/pfd.sdc (optional)

/pfd/pfd.v (optional)

/reclock/sdi_reclock.v (optional)

/reclock/pid_controller.v (optional)

/sdi_ii_rx_rcfg_a10.sv (optional)

/rcfg_sdi_cdr.sv (optional)

continued...

Page 5

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

Folders Files

rx /rx_top.v

tx /tx_top.v

/rcfg_pll_sw.sv (optional)

/rcfg_refclk_sw.sv (optional)

/sdi_ii_tx_rcfg_a10.sv (optional)

/sdi_du_sys.qsys

•

/sdi_rx_phy.qsys (Quartus Prime Standard Edition)

•

/sdi_rx_phy.ip (Quartus Prime Pro Edition)

•

/tx_pll.qsys (Quartus Prime Standard Edition)

•

/tx_pll.ip (Quartus Prime Pro Edition)

•

/tx_pll_alt.qsys (Quartus Prime Standard Edition)

•

/tx_pll_alt.ip (Quartus Prime Pro Edition)

(optional)

<qsys generated folder>

/sdi_ii_rx_rcfg_a10.sv (optional)

/rcfg_sdi_cdr.sv (optional)

/sdi_rx_sys.qsys

<qsys generated folder>

/rcfg_pll_sw.sv (optional)

/rcfg_refclk_sw.sv (optional)

/sdi_ii_tx_rcfg_a10.sv (optional)

/sdi_tx_sys.qsys

•

/tx_pll.qsys (Quartus Prime Standard Edition)

•

/tx_pll.ip (Quartus Prime Pro Edition)

•

/tx_pll_alt.qsys (Quartus Prime Standard Edition)

•

/tx_pll_alt.ip (Quartus Prime Pro Edition)

(optional)

<qsys generated folder>

Table 2. Other Generated Files in Simulation Folder

Folders Files

aldec /aldec.do

cadence /cds.lib

/rivierapro_setup.tcl

/hdl.var

/ncsim.sh

/ncsim_setup.sh

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

5

Page 6

1 SDI II Design Example Quick Start Guide

Folders Files

<cds_libs folder>

mentor /mentor.do

/msim_setup.tcl

synopsys /vcs/filelist.f

/vcs/vcs_setup.sh

/vcs/vcs_sim.sh

/vcsmx/synopsys_sim_setup

/vcsmx/vcsmx_setup.sh

/vcsmx/vcsmx_sim.sh

testbench tb_top.v

rx_checker/sdi_ii_tb_rx_checker.v

rx_checker/tb_data_compare.v

rx_checker/tb_dual_link_sync.v

rx_checker/tb_fifo_line_test.v

rx_checker/tb_frame_locked_test.sv

rx_checker/tb_rxsample_test.v

rx_checker/tb_trs_locked_test.sv

rx_checker/tb_txpll_test.sv

rx_checker/tb_vpid_check.v

tb_control/sdi_ii_tb_control.v

tb_control/tb_clk_rst.v

tb_control/tb_data_delay.v

tb_control/tb_serial_delay.sv

tb_control/tb_tasks.v

tb_checker/sdi_ii_tb_tx_checker.v

tb_checker/tb_serial_check_counter.v

tb_checker/tb_serial_descrambler.v

tb_checker/tb_tx_clkout_check.v

vid_pattgen/sdi_ii_colorbar_gen.v

vid_pattgen/sdi_ii_ed_vid_pattgen.v

vid_pattgen/sdi_ii_makeframe.v

vid_pattgen/sdi_ii_patho_gen.v

UG-20076 | 2017.05.08

1.2 Hardware and Software Requirements

Intel uses the following hardware and software to test the design examples:

Intel® Arria® 10 SDI II IP Core Design Example User Guide

6

Page 7

Start Parameter

Editor

Specify IP Variation

and Select Device

Select

Design Parameters

Initiate

Design Generation

Specify

Example Design

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

Hardware

• Intel Arria 10 GX FPGA Development Kit

• SDI Signal Generator

• SDI Signal Analyzer

• SubMiniature version B (SMB) to Bayonet Neill–Concelman (BNC) cables for

single-rate and triple-rate designs, or BNC to BNC cables for multi-rate designs

• VIDIO™ FMC Development Module VIDIO-12G-A (Nextera 12G SDI FMC daughter

card) for multi-rate designs

Software

• Intel Quartus Prime (for hardware testing)

• ModelSim* - Intel FPGA Edition, ModelSim-SE, NCSim (Verilog only), Riviera-Pro,

or VCS (Verilog only)/VCS-MX simulator

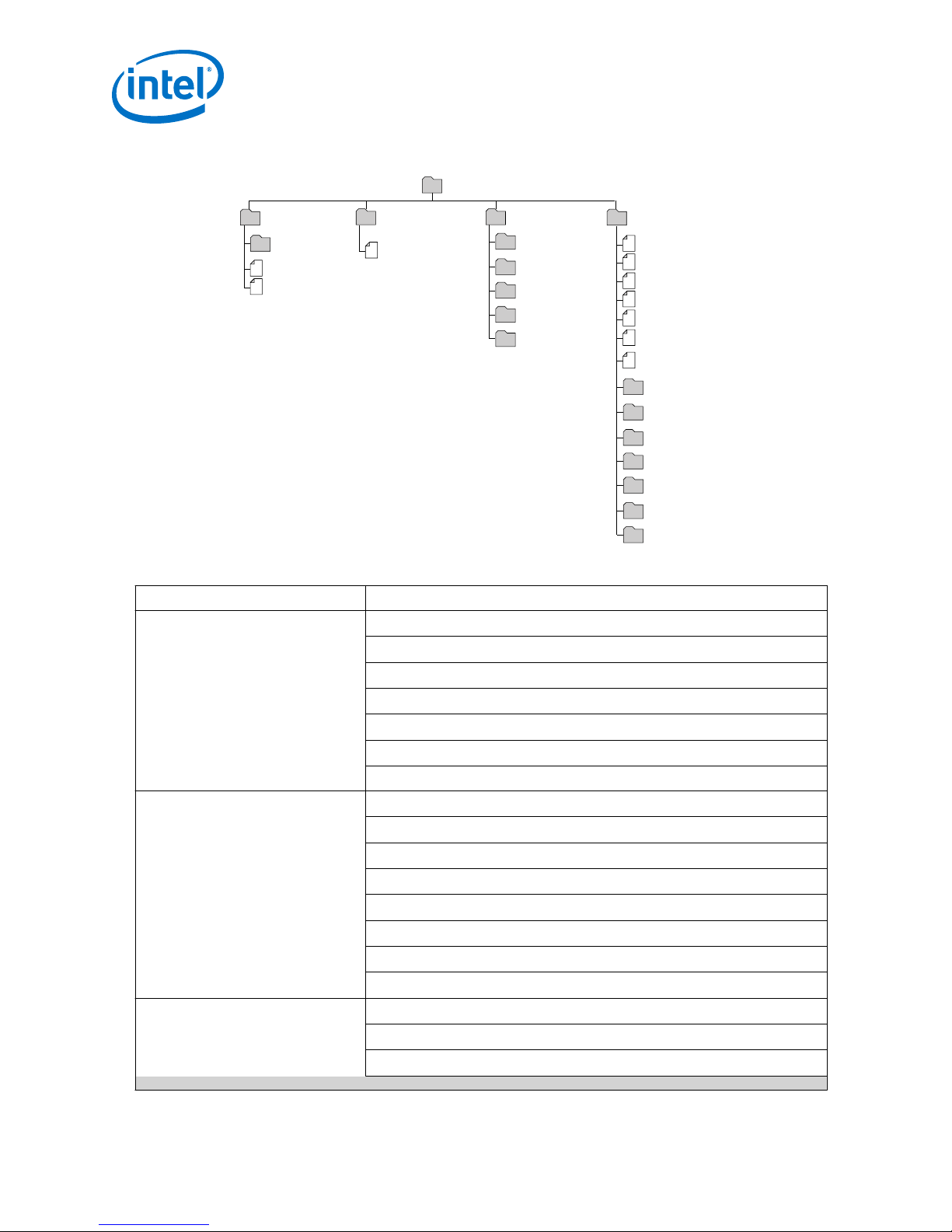

1.3 Generating the Design

Use the SDI II parameter editor in the Quartus Prime software to generate the design

examples.

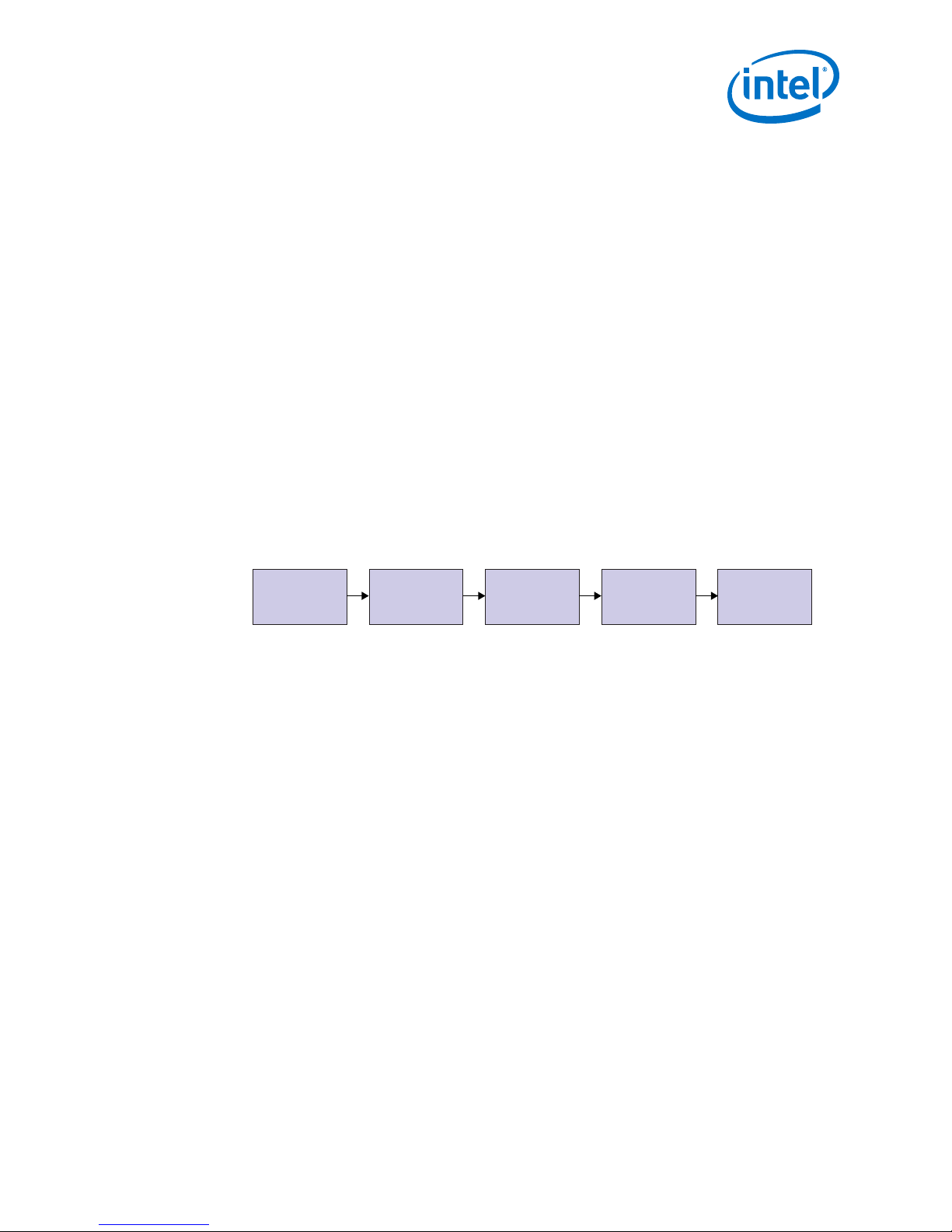

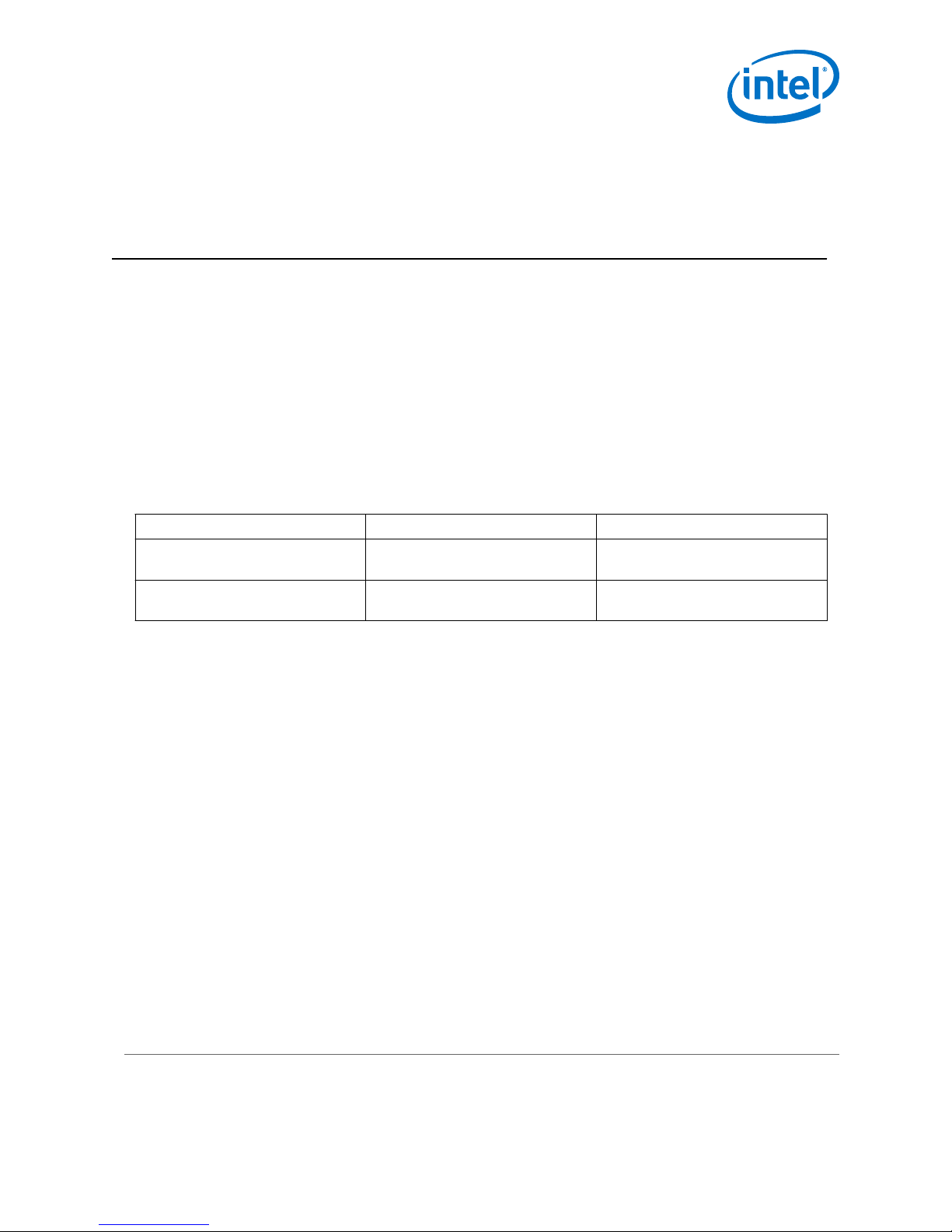

Figure 3. Generating the Design Flow

1. Create a project targeting Arria 10 device family and select the desired device.

2. In the IP Catalog, locate and double-click SDI II IP Core. The New IP Variant

or New IP Variation window appears.

3. Specify a top-level name for your custom IP variation. The parameter editor saves

the IP variation settings in a file named <your_ip>.ip or <your_ip>.qsys.

4. Click OK. The parameter editor appears.

5. On the IP tab, select your desired IP settings. The generated design example will

be based on your settings.

6. On the Design Example tab, select Simulation to generate the testbench, and

select Synthesis to generate the hardware design example.

You must select at least one of these options to generate the design example files.

7. For Generate File Format, select Verilog or VHDL.

8. For Target Development Kit, select Arria 10 GX FPGA Development Kit. You

may change the target device using the Change Target Device parameter if your

board revision does not match the grade of the default targeted device.

9. Click Generate Example Design.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

7

Page 8

Change to

<Simulator>

Directory

Run

<Simulation Script>

Analyze

Results

Compile Design

in Quartus Prime

Software

Set Up Hardware Program Device

Test Design

in Hardware

1 SDI II Design Example Quick Start Guide

1.4 Simulating the Design

The SDI II design example testbench simulates one channel serial loopback design

with TX instance connected to an internal video pattern generator. The serial output

from the TX instance connects to the RX instance in the testbench. The testbench also

includes checkers and control mechanisms.

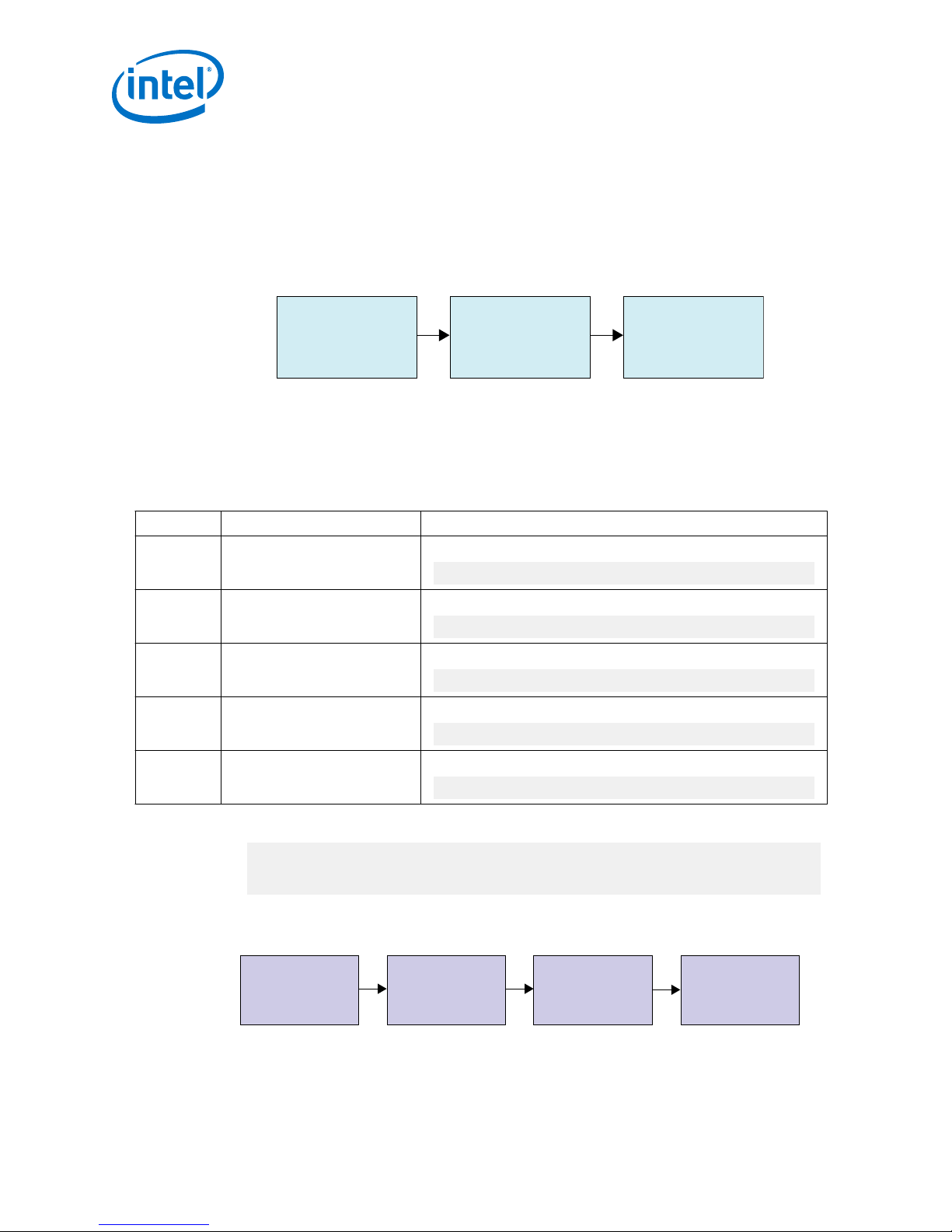

Figure 4. Design Simulation Flow

1. Navigate to the simulation folder of your choice.

2. Run the simulation script for the supported simulator of your choice. The script

compiles and runs the testbench in the simulator.

3. Analyze the results.

Table 3. Steps to Run Simulation

Simulator Working Directory Instructions

Riviera-Pro

/simulation/aldec

In the GUI, type:

do aldec.do

UG-20076 | 2017.05.08

NCSim

ModelSim

VCS

VCS-MX

/simulation/cadence

/simulation/mentor

/simulation/synopsys/vcs

/simulation/synopsys/

vcsmx

In the command line, type:

source ncsim.sh

In the GUI, type:

do mentor.do

In the command line, type:

source vcs_sim.sh

In the command line, type:

source vcsmx_sim.sh

A successful simulation ends with the following message:

#### TRANSMIT TEST COMPLETED SUCCESSFULLY! ####

#

#### Channel 1: RECEIVE TEST COMPLETED SUCCESSFULLY! ####

1.5 Compiling and Testing the Design

Intel® Arria® 10 SDI II IP Core Design Example User Guide

8

Page 9

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

To compile and run a demonstration test on the hardware design example, follow

these steps:

1. Ensure that the hardware design example generation is complete.

2. Open quartus/sdi_ii_a10_demo.qpf.

3.

Click Processing ➤ Start Compilation.

4. If you turn on the Dynamic Tx clock switching parameter in the Design

Example parameter editor, set the frequency for CLK2 or CLK3 in the Si5338

(U14) tab of the Clock Control GUI.

• For HD/3G-SDI single-rate and triple-rate designs, set CLK3 to 148.3516 MHz.

• For multi-rate designs, set CLK2 to 296.7033 MHz.

5.

After successful compilation, the Quartus Prime software generates a .sof file in

your specified directory.

6. Configure the selected Arria 10 device on the development board using the

generated .sof file (Tools

7. For serial loopback designs, open the System Console to control the internal video

pattern generator. Click Tools ➤ System Debugging Tools ➤ System Console.

Note: Close the Clock Control GUI and the Programmer window before you open

the System Console.

8.

After the initialization, type source ../hwtest/tpg_ctrl.tcl in the System

Console to open the pattern generator control user interface. Select your desired

video format.

➤

Programmer ).

Related Links

Setting Up Environment Variables

Provides information about setting up the Clock Control application.

1.5.1 Connection and Settings Guidelines

Before programing with the .sof file, ensure that the connections and settings are

correct.

Connections and Settings for HD/3G-SDI Single Rate and Triple Rate Designs

• For parallel loopback design, the on-board SMB RX connector (J20) connects to an

external video source and the on-board SMB TX connector (J21) connects to a

video analyzer.

• For serial loopback design, the on-board SMB TX connector (J21) connects to an

on-board SMB RX connector (J20) or a video analyzer.

• Ensure all switches on the development board are in default position.

• The SDI video analyzer displays the video generated from the source.

Note: For parallel loopback designs, you may need to switch the Si516_FS

(SW6.3) at the back of the board if you are switching between fractional

frame rate and integer frame rate video format.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

9

Page 10

SW5

ON

1 2 3 4

MSEL0

MSEL1

MSEL2

VIDEN

SW4

CLK_SEL

CLK_EN

Si516_FS

FACTORY

RZQ_B2K

ON

1

1 0 1 0

2 3 4

ARRIA 10

MAX V

FMCA

FMCB

SW6

ON

1 2 3 4 5

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

Figure 5. Switch Settings on the Arria 10 Development Board

Table 4. SW6 DIP Switch Default Settings (Board Button)

Switch Board Label Description

1 CLK_SEL • ON for 100 MHz on-board clock oscillator selection (Default

2 CLK_EN

3 SI516_FS •

4 FACTORY • ON to load factory from flash (Default position)

5 RZQ_B2K • ON for setting RZQ resistor of Bank 2K to 99.17 ohm

position)

• OFF for SMA input clock selection

OFF for setting CLK_ENABLE high to the MAX V

ON for setting the SDI REFCLK frequency to 148.35 MHz

•

OFF for setting the SDI REFCLK frequency to 148.5 MHz (Default

position)

• OFF to load user hardware from flash

• OFF for setting RZQ resistor of Bank 2K to 240 ohm (Default

position)

Intel® Arria® 10 SDI II IP Core Design Example User Guide

10

Page 11

Pin 2 - 3

296.7 MHz

Open

Pin 1 - 2

SDI Mode

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

Connections and Settings for Multi Rate Design

• A VIDIO™ FMC Development Module VIDIO-12G-A (Nextera 12G SDI FMC

daughter card) connects to the FMC Port B on the development board.

• For parallel loopback design, the BNC RX connector (J1/12G In) connects to an

external video source and the TX connector (J2/12G Out) connects to a video

analyzer.

• For serial loopback design, the BNC TX connector (J2/12G Out) connects to the

BNC RX connector (J1/12G In) or a video analyzer.

• Ensure all switches on the development board are in default position.

• The SDI video analyzer displays the video generated from the source.

Note: Change the jumper (J8) position before switching between fractional frame

rate and integer frame rate video formats. Press the push button (PB0) to

trigger a device (LMK03328) power cycling through the PDN pin every time

you change the jumper (J8) position.

Figure 6. Jumper Settings on Nextera 12G-SDI FMC Daughter Card

Refer to these settings to change the jumper (J8) position.

Table 5. Jumper Settings

Jumper Block Description

J7 Programming header

J8 To switch the generated clock frequency for the TX channel:

• Pin 1–2 = 297 MHz

• Pin 2–3 = 297/1.001 MHz

J9 To select SDI or IP mode:

• Pin 1–2 = SDI mode

• Pin 2–3 = IP mode

Related Links

Intel Arria 10 FPGA Development Kit User Guide

1.5.2 Design Limitations for Serial Loopback Design

The serial loopback design example has the following limitations:

Intel® Arria® 10 SDI II IP Core Design Example User Guide

11

Page 12

1 SDI II Design Example Quick Start Guide

UG-20076 | 2017.05.08

• You may encounter certain problems with the 12G-SDI 2160p59.94 in the serial

loopback design that cannot be detected on the Omnitek Ultra 4K analyzer

(software v2.1).

• Serial loopback design is mainly for image and TX clock switching demonstrations

only. To get a more accurate jitter performance with the daughter card

components, use the parallel loopback design and connect it to a clean video

source.

• To allow segmented frame video format (1080sF30, 1080sF25) and interlaced

video format (1080i60, 1080i50) to be correctly differentiated in the external

analyzer, Payload ID has to be inserted in the serial loopback design.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

12

Page 13

UG-20076 | 2017.05.08

2 SDI II Design Example Detailed Description

The SDI II IP core includes three design examples for Arria 10 devices.

• Parallel loopback with external VCXO

• Parallel loopback without external VCXO

• Serial loopback

Features

• For HD/3G-SDI single rate and triple rate designs, you can choose either CMU or

fPLL as the TX PLL.

• All designs use LED status for early debugging stage.

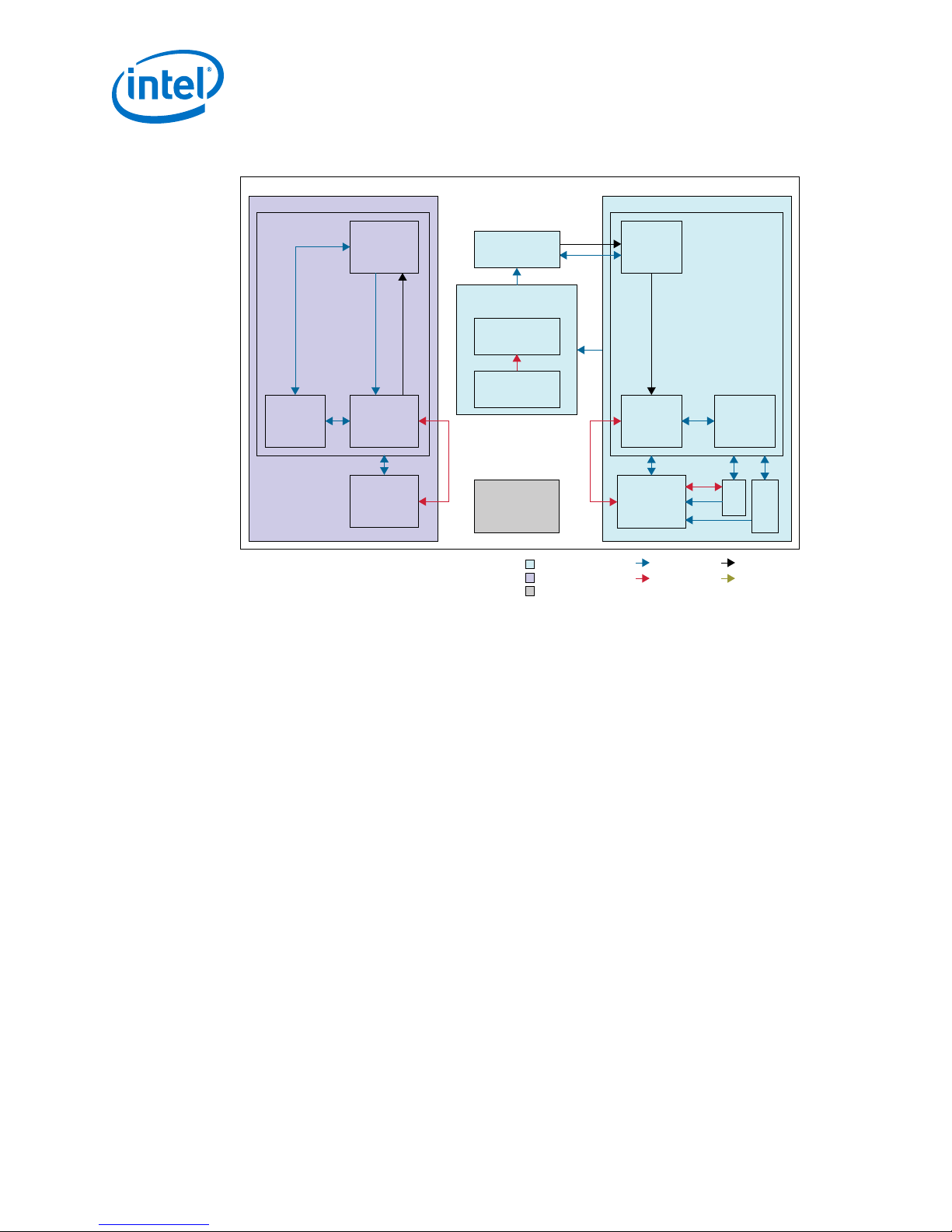

• The simplex serial loopback designs include RX and TX options. To use RX or TX

only components, remove the irrelevant blocks from the designs.

User Requirement Preserve Remove

RX Only RX Top — TX Top

— Transceiver Arbiter

TX Only TX Top — RX Top

— Transceiver Arbiter

Note: You can directly connect the Avalon-MM pins at the RX or TX Top as shown

in the diagram below.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2008

Registered

Page 14

Top

RX Top

SDI II

RX

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(RX)

RX

Reconfiguration

Management

Transceiver

Arbiter

Pattern Generator Control

SDI RX System

TX Top

SDI II

TX

Transceiver

PHY Reset

C ontroller (RT)

Transceiver

Native PHY

(TX)

SDI TX System

TX

PLL

Alt

Pattern Generator

Control PIO

Parallel Data

Serial Data

Control/Status

Avalon-MM

JTAG to Avalon

Master Bridge

Video Pattern

Generator

TX

PLL

TX

Reconfiguration

Management

TX Only Components

RX Only Components

Removed Blocks

2 SDI II Design Example Detailed Description

Figure 7. Components Required for TX or RX Only Design

UG-20076 | 2017.05.08

2.1 Parallel Loopback Design Examples

The parallel loopback design examples demonstrate simplex and duplex channel

modes with and without external VCXO.

Note: For parallel loopback duplex designs, do not share the TX PLL reference clock with the

RX transceiver reference clock. The design logic tunes the TX PLL clock to match the

RX recovered clock frequency. For the parallel loopback with external VCXO designs

(single-rate and triple-rate), use the only 148.5 MHz on-board oscillator as the TX PLL

reference clock. For the RX reference clock, use a 270 MHz clock from another onboard oscillator.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

14

Page 15

Top

RX Top

SDI II

RX

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(RX)

RX

Reconfiguration

Management (3)

Transceiver

Arbiter (3)

Loopback Top

SDI RX System

TX Top

SDI II

TX

Transceiver

PHY Reset

Controller (TX)

Transceiver

Native PHY

(TX)

SDI TX System

TX PLL

Loopback

FIFO

PFD (1)

Reclock (2)

(4)

Parallel Data

Serial Data

Control/Status

Avalon-MM

(1) Generate up/down control signal to on-board Si516 for clock synchronization purpose.

(2) Block/Connection only required for parallel loopback without external VCXO designs.

(3) Block/Connection only required for triple-rate/multi-rate designs.

(4) FVH video sync signals to LMH1983 for clock synchronization purpose.

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Parallel Loopback with Simplex Mode

Figure 8. Parallel Loopback with Simplex Mode Block Diagram

Intel® Arria® 10 SDI II IP Core Design Example User Guide

15

Page 16

Top

RX Top

SDI II

RX

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(RX)

RX

Reconfiguration

Management (3)

Transceiver

Arbiter

Loopback Top

SDI RX System

TX Top

SDI II

TX

Transceiver

PHY Reset

Controller (TX)

Transceiver

Native PHY

(TX)

SDI TX System

TX PLL

Loopback

FIFO

PFD (1)

Reclock (2)

TX PLL Reference Clock

TX Transceiver clkout

TX PLL Serial Clock

RX Reference Clock

RX Transceiver clkout

Management Clock

RX Reference

Clock

Management

Clock

TX PLL

Reference

Clock

(1) Block/Connection only required for parallel loopback with external VCXO designs.

(2) Block/Connection only required for parallel loopback without external VCXO designs.

(3) Block/Connection only required for triple-rate/multi-rate designs.

2 SDI II Design Example Detailed Description

Figure 9. Parallel Loopback with Simplex Mode Clocking Scheme

UG-20076 | 2017.05.08

Intel® Arria® 10 SDI II IP Core Design Example User Guide

16

Page 17

Top

Duplex Top

SDI II

Duplex

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(Duplex)

RX

Reconfiguration

Management (3)

Transceiver

Arbiter (3)

Loopback Top

SDI Duplex System

TX PLL

Loopback

FIFO

PFD (1)

Reclock (2)

Parallel Data

Serial Data

Control/Status

Avalon-MM

(4)

Transceiver

PHY Reset

C ontroller (TX)

(1) Generate up/down control signal to on-board Si516 for clock synchronization purpose.

(2) Block/Connection only required for parallel loopback without external VCXO designs.

(3) Block/Connection only required for triple-rate/multi-rate designs.

(4) FVH video sync signals to LMH1983 for clock synchronization purpose.

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Parallel Loopback with Duplex Mode

Figure 10. Parallel Loopback with Duplex Mode Block Diagram

Intel® Arria® 10 SDI II IP Core Design Example User Guide

17

Page 18

Top

Duplex Top

SDI II

Duplex

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(Duplex)

RX

Reconfiguration

Management (3)

Transceiver

Arbiter (3)

Loopback Top

SDI Duplex System

TX PLL

Loopback

FIFO

PFD (1)

Reclock (2)

Transceiver

PHY Reset

Controller (TX)

TX PLL Reference Clock

TX Transceiver clkout

TX PLL Serial Clock

RX Reference Clock

RX Transceiver clkout

Management Clock

RX Reference

Clock

Management

Clock

TX PLL

Reference

Clock

(1) Block/Connection only required for parallel loopback with external VCXO designs.

(2) Block/Connection only required for parallel loopback without external VCXO designs.

(3) Block/Connection only required for triple-rate/multi-rate designs.

2 SDI II Design Example Detailed Description

Figure 11. Parallel Loopback with Duplex Mode Clocking Scheme

UG-20076 | 2017.05.08

2.2 Serial Loopback Design Examples

The serial loopback design examples demonstrate simplex and duplex channel modes.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

18

Page 19

Top

RX Top

SDI II

RX

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(RX)

RX

Reconfiguration

Management (1)

Transceiver Arbiter

(1), (2)

Pattern Generator Control

SDI RX System

TX Top

SDI II

TX

Transceiver

PHY Reset

Controller (TX)

Transceiver

Native PHY

(TX)

SDI TX System

TX

PLL

Alt (2)

Pattern Generator

Control PIO

Parallel Data

Serial Data

Control/Status

Avalon-MM

(1) Block/Connection only required for triple-rate/multi-rate designs.

(2) Block/Connection only required for triple-rate/multi-rate for TX PLL switching designs.

(3) Block/Connection only required for triple-rate/multi-rate for TX PLL reference clock switching designs.

JTAG to Avalon

Master Bridge

Video Pattern

Generator

(1) (2)

(1)

(1)

TX

PLL

TX Reconfiguration

Management

(2), (3)

(2)

(2)

(2)

(2)

(3)

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Serial Loopback with Simplex Mode

Figure 12. Serial Loopback with Simplex Mode Block Diagram

Intel® Arria® 10 SDI II IP Core Design Example User Guide

19

Page 20

Top

RX Top

SDI II

RX

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(RX)

RX

Reconfiguration

Management (1)

Transceiver Arbiter

(1), (2)

Pattern Generator Control

SDI RX System

TX Top

SDI II

TX

Transceiver

PHY Reset

Controller (TX)

Transceiver

Native PHY

(TX)

SDI TX System

TX

PLL

Alt (2)

Pattern Generator

Control PIO

JTAG to Avalon

Master Bridge

Video Pattern

Generator

TX

PLL

TX Reconfiguration

Management

(2), (3)

TX PLL Reference Clock

TX Transceiver clkout

TX PLL Serial Clock

RX Reference Clock

RX Transceiver clkout

Management Clock

(1) Block/Connection only required for triple-rate/multi-rate designs.

(2) Block/Connection only required for triple-rate/multi-rate for TX PLL switching designs.

(3) Block/Connection only required for triple-rate/multi-rate for TX PLL reference clock switching designs.

Management

Clock

RX Reference

Clock

TX PLL Alt

Reference

Clock (2), (3)

TX PLL

Reference

Clock

(1) (2)

(3)

(3)

2 SDI II Design Example Detailed Description

Figure 13. Serial Loopback with Simplex Mode Clocking Scheme

UG-20076 | 2017.05.08

Intel® Arria® 10 SDI II IP Core Design Example User Guide

20

Page 21

Top

Duplex Top

SDI II

Duplex

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(Duplex)

RX

Reconfiguration

Management (1)

Transceiver Arbiter

(1), (2)

Pattern Generator Control

SDI Duplex System

Pattern Generator

Control PIO

Parallel Data

Serial Data

Control/Status

Avalon-MM

(1) Block/Connection only required for triple-rate/multi-rate designs.

(2) Block/Connection only required for triple-rate/multi-rate for TX PLL switching designs.

(3) Block/Connection only required for triple-rate/multi-rate for TX PLL reference clock switching designs.

JTAG to Avalon

Master Bridge

Video Pattern

Generator

Transceiver

PHY Reset

Controller (TX)

TX

PLL

Alt (2)

TX

PLL

TX Reconfiguration

Management

(2), (3)

(2)

(2)

(3)

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Serial Loopback with Duplex Mode

Figure 14. Serial Loopback with Duplex Mode Block Diagram

Intel® Arria® 10 SDI II IP Core Design Example User Guide

21

Page 22

Top

Duplex Top

SDI II

Duplex

Transceiver

PHY Reset

Controller (RX)

Transceiver

Native PHY

(Duplex)

RX

Reconfiguration

Management (1)

Transceiver Arbiter

(1), (2)

Pattern Generator Control

SDI Duplex System

Pattern Generator

Control PIO

JTAG to Avalon

Master Bridge

Video Pattern

Generator

Transceiver

PHY Reset

Controller (TX)

TX

PLL

Alt (2)

TX

PLL

TX Reconfiguration

Management

(2), (3)

(2)

(3)

(3)

TX PLL Reference Clock

TX Transceiver clkout

TX PLL Serial Clock

RX Reference Clock

RX Transceiver clkout

Management Clock

TX PLL Alt

Reference

Clock (2), (3)

TX PLL

Reference

Clock

RX

Reference

Clock

Management

Clock

(1) Block/Connection only required for triple-rate/multi-rate designs.

(2) Block/Connection only required for triple-rate/multi-rate for TX PLL switching designs.

(3) Block/Connection only required for triple-rate/multi-rate for TX PLL reference clock switching designs.

2 SDI II Design Example Detailed Description

Figure 15. Serial Loopback with Duplex Mode Clocking Scheme

UG-20076 | 2017.05.08

2.3 Design Components

The SDI II IP core design examples require the following components.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

22

Page 23

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Table 6. Device Under Test (DUT) Components

Design Component Description

SDI II IP Core • TX

— The TX core receives the video data from the top level and encodes the

necessary information, (e.g. line number (LN), cyclical redundancy check

(CRC), payload ID), into the data stream(s).

— In a multi-rate design, the TX core oversamples the received data up to

11.88 Gbps data rate for every video standard. Specify the assignment of

the parallel data interface (tx_parallel_data) to the transceiver based

on the 11.88 Gbps data rate settings.

• RX

— The RX core receives the parallel data from the Transceiver Native PHY IP

core and decodes information. This information includes descrambling,

realigning data, and extracting the necessary information for user.

— For a multi-rate design, due to the difference in data widths recovered for

different video standards, rearrange rx_parallel_data from the

transceiver before passing the data back to the protocol block.

Transceiver Native PHY IP Core • TX

Hard transceiver block that receives parallel data from the SDI II IP core and

serializes the data before transmission.

— For HD/3G-SDI single-rate and triple-rate designs, enable the simplified

data interface option to connect parallel data directly to the tx_dataout

signal of the SDI II IP core.

— For a multi-rate design, disable this option due to the limitation in the

12G-SDI transceiver PHY settings.

• RX

Hard transceiver block that receives serial data from an external video

source.

— For HD/3G-SDI single-rate and triple-rate designs, enable the simplified

data interface option to connect parallel data directly to the rx_datain

signal of SDI II IP core.

— For a multi-rate design, disable this option due to the limitation in the

12G-SDI transceiver PHY settings.

You must connect the rx_analogreset_ack output signal from this block to

the RX Reconfiguration Management module to indicate that the transceiver is

in reset.

Note: For the duplex mode transceiver (SDI triple-rate parallel loopback with

external VCXO design example), generate a dummy RX only PHY

(sdi_rx_phy.qsys) to get the transceiver configuration files

(*_CFG0.sv, *_CFG1.sv, …) for RX reconfiguration. The generated

configuration files from the duplex mode transceiver may contain some

TX registers. You don't need to reconfigure the registers because only the

SDI RX core requires transceiver reconfiguration.

Transceiver PHY Reset Controller • TX

— The reset input of this controller is triggered from the top level.

— The controller generates the corresponding analog and digital reset signal

to the Transceiver Native PHY block, according to the reset sequencing

inside the block.

—

Use the tx_ready output signal from the block as a reset signal to the TX

core to indicate that the transceiver is up and running, and ready to

receive data from the core.

• RX

— The reset input of this controller is triggered by the SDI II IP core.

— The controller generates the corresponding analog and digital reset signal

to the Transceiver Native PHY block according to the reset sequencing

inside the block.

RX Reconfiguration Management RX transceiver reconfiguration management block that reconfigures the

Transceiver Native PHY block to receive different data rates from SD-SDI to 12GSDI standards.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

23

Page 24

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Design Component Description

To indicate the status of the transceiver, connect rx_cal_busy and

rx_analogreset_ack from the transceiver to this block.

TX Reconfiguration Management TX PLL or transceiver reconfiguration management block that reconfigures the TX

TX PLL/TX PLL Alt Transmitter PLL block that provides the serial fast clock to Transceiver Native

PLL or Transceiver Native PHY block to change the TX clock dynamically for

switching between integer and fractional frame rates.

The block requires tx_cal_busy, pll_cal_busy, and tx_analogreset_ack

from the transceiver, and the PLLs to indicate the status of the transceiver in a

TX PLL switching design.

PHY.

• For TX PLL switching design, TX PLL is always configured to generate integer

frame rate while TX PLL Alt is configured to generate fractional frame rate.

• For TX PLL reference clock switching design, TX PLL is configured to have

reference clock 0 to generate integer frame rate and reference clock 1 to

generate fractional frame rate.

• For single-rate and triple-rate designs, this PLL can be either CMU PLL or

fPLL.

• For multi-rate designs, CMU PLL is not recommended for 12G data rate. Use

fPLL instead.

Move the TX PLL out from the TX top if you want to merge the PLL between

multiple channels.

Table 7. Loopback Components

Component Description

Loopback FIFO This block contains a dual-clock FIFO (DCFIFO) buffer to handle the data

Phase Frequency Detector (PFD) You require this soft PFD block when you use the Arria 10 GX FPGA development

Reclock The parallel loopback without external VCXO design requires this module. Similar

transmission across asynchronous clock domains—the receiver recovered clock

and transmitter clock out.

• The receiver sends the decoded RX data to the transmitter through this FIFO

buffer.

• When the receiver locks, the RX data is written to the FIFO buffer.

• The transmitter starts reading, encoding, and transmitting the data when half

of the FIFO buffer is filled.

kit on-board Si516 VCXO for a parallel loopback design.

• This block compares the phase between the receiver and transmitter parallel

clocks, and generates an up or down signal, that connects to the Si516 VCXO.

• These up/down signals control the voltage of the VCXO, so that the

frequencies of both clock domains can be tuned as close as possible to each

other.

Note: Applicable only for parallel loopback with external VCXO designs.

to the PFD block, this block compares the phase between the receiver and

transmitter parallel clocks.

The output interfaces of this block connect to the reconfiguration Avalon

Memory-Mapped (Avalon-MM) interfaces of an fPLL. If there is any difference in

the frequencies between the clock domains, this module generates the necessary

signals to reconfigure the fPLL to match the clock frequencies as close as

possible.

Note: Applicable only for parallel loopback without external VCXO designs.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

24

Page 25

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Table 8. Video Pattern Generator Components

Component Description

Video Pattern Generator Basic video pattern generator which supports SD-SDI up to 12G-SDI video

Pattern Gen Control PIO Provides a memory-mapped interface for controlling the video pattern generator.

JTAG to Avalon Master Bridge Provides System Console host access to the Parallel I/O (PIO) IP core in the

formats with 4:2:2 YCbCr. The generator enables you to select static video with

colorbar pattern or pathological pattern.

design through the JTAG interface.

Table 9. Common Block

Component Description

Transceiver Arbiter This generic functional block prevents transceivers from recalibrating

simultaneously when either RX or TX transceivers within the same physical

channel require reconfiguration. The simultaneous recalibration impacts

applications where RX and TX transceivers within the same channel are assigned

to independent IP implementations.

This transceiver arbiter is an extension to the resolution recommended for

merging simplex TX and simplex RX into the same physical channel. This

transceiver arbiter also assists in merging and arbitrating the Avalon-MM RX and

TX reconfiguration requests targeting simplex RX and TX transceivers within a

channel as the reconfiguration interface port of the transceivers can only be

accessed sequentially. The transceiver arbiter is not required when only either RX

or TX transceiver is used in a channel.

The transceiver arbiter identifies the requester of a reconfiguration through its

Avalon-MM reconfiguration interfaces and ensures that the corresponding

tx_reconfig_cal_busy or rx_reconfig_cal_busy is gated accordingly.

2.4 Clocking Scheme Signals

The table lists the clocking scheme signals for the SDI II IP core design examples.

Table 10. Clocking Scheme Signals

Clock Signal Name in Design Description

TX PLL Refclock

tx_pll_refclk

TX PLL reference clock, of any frequency that is divisible by

the transceiver for that data rate.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

25

Page 26

Clock Signal Name in Design Description

TX PLL Alt Refclock

TX Transceiver Clockout

TX PLL Serial Clock

RX Refclock

tx_pll_refclk_alt

tx_vid_clkout

tx_serial_clk

rx_cdr_refclk

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Note: You must connect this clock to a dedicated

transceiver reference clock pin.

• Parallel loopback with external VCXO

— Use a minimum clock frequency of 148.5 MHz

(single-rate/triple-rate) or 297 MHz (multi-rate) to

meet jitter performance specification.

— Using a higher clock frequency would require a

modification of the TX PLL reference clock value in

the TX PLL parameter editor.

• Parallel loopback without external VCXO

— The recommended frequency is 100 MHz.

• Serial loopback

— For this design, the TX PLL refclock is configured to

generate clock for integer frame rate.

— The minimum clock frequency is 148.5 MHz (single-

rate/triple-rate) or 297 MHz (multi-rate) to meet

jitter performance specification.

— Using a higher clock frequency would require a

modification of the TX PLL reference clock value in TX

PLL parameter editor.

Second TX PLL reference clock which can be any clock

frequency that is divisible by transceiver for that data rate.

This clock must be connected to a dedicated transceiver

reference clock pin.

• Serial loopback

— For this design example, TX PLL alt refclock is

configured to generate clock for fractional frame rate.

— The minimum clock frequency is 148.35 MHz (single-

rate/triple-rate) or 297.7 MHz (multi-rate) to meet

jitter performance specification.

— Using a higher clock frequency would require a

modification of the TX PLL reference clock value in

the TX PLL parameter editor.

Recovered clock from the transceiver.

• HD-SDI single rate

— 74.25 MHz (default)

— 74.1758 MHz (for the Dynamic TX clock switching

feature when you transmit video format with

fractional frame rate)

• 3G-SDI single rate, triple rate or multi rate

— 148.5 MHz (default)

— 148.35 MHz (for the Dynamic TX clock switching

feature when you transmit video format with

fractional frame rate)

Serial fast clock generated by TX PLL. The clock frequency is

set based on the data rate.

Transceiver clock data recovery (CDR) reference clock, of

any frequency that is divisible by the transceiver for that

data rate. Only a single reference clock frequency is

required to support both integer and fractional frame rates.

It must be a free running clock connected to the transceiver

clock pin.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

26

Page 27

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Clock Signal Name in Design Description

rx_core_refclk

• Parallel loopback with external VCXO

— For this design example, the minimum clock

frequency of 148.5 MHz is used in the multi-rate

design example. For single-rate and triple-rate design

examples, a higher reference clock (270 MHz) is used

instead.

— Using a higher clock frequency would require a

modification of the RX CDR reference clock value in

the Arria 10 Native PHY Transceiver parameter editor.

For triple or multi-rate modes, you need to modify

the reference clock value for every profiles.

• Parallel loopback without external VCXO and Serial

loopback

— The minimum clock frequency is 148.5 MHz.

— Using a higher clock frequency would require a

modification of the RX CDR reference clock value in

the Arria 10 Native PHY Transceiver parameter editor.

For triple or multi-rate modes, you need to modify

the reference clock value for every profiles.

Note: Do not share the TX PLL reference clock with the RX

transceiver reference clock for a parallel loopback

design. In parallel loopback designs, the TX PLL

clock is tuned to match the RX recovered clock

frequency.

SDI RX core reference clock.

The required frequency is 148.5 MHz. This clock must be a

free-running clock.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

27

Page 28

2 SDI II Design Example Detailed Description

Clock Signal Name in Design Description

RX Transceiver Clkout

Management Clock

rx_vid_clkout

rx_rcfg_mgmt_clk

tx_rcfg_mgmt_clk

Recovered clock from the transceiver.

• SD-SDI

— 148.5 MHz (default)

• HD-SDI

— 74.25 MHz when receiving integer frame rate

— 74.1758 MHz when receiving fractional frame rate

• 3G/6G/12-SDI

— 148.5 MHz when receiving integer frame rate

— 148.35 MHz when receiving fractional frame rate

A free running 100 MHz RX clock for both Avalon-MM

interfaces for reconfiguration and PHY reset controller for

transceiver reset sequence.

Component Required Frequency

Avalon-MM reconfiguration 100 – 125

Transceiver PHY reset controller 1 – 500

You may also connect this input clock to rx_core_refclk

and change the input clock frequency option to 149 MHz in

the parameter editor.

A free-running 100 MHz TX clock for both Avalon-MM

interfaces for reconfiguration and PHY reset controller for

transceiver reset sequence.

Component Required Frequency

Avalon-MM reconfiguration 100 – 125

Transceiver PHY reset controller 1 – 500

UG-20076 | 2017.05.08

(MHz)

(MHz)

2.5 Interface Signals

The tables list the signals for the SDI II IP core design examples.

Table 11. Top-Level Signals

Signal Direction Width Description

clk_fpga_b2_p

pcie_ob_refclk_p

refclk_dp_p

You may also connect this input clock to tx_pll_refclk

(assuming this clock is not connected to a VCXO that will be

tuned) and change the input clock frequency option to the

correct clock frequency in the parameter editor.

On-board Oscillator Signals

Input 1 100 MHz clock for reconfiguration Avalon-MM interfaces.

Input 1 100 MHz dedicated transceiver reference clock.

Input 1 270 MHz dedicated transceiver reference clock.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

28

Page 29

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Signal Direction Width Description

refclk_sdi_p

refclk_sma_p

refclk_fmcb_p

user_pb0

cpu_resetn

user_led_g

user_led_r

On-board Si516, SDI Cable Driver and Equalizer Related Pins

sdi_rx_p

sdi_tx_p

sdi_clk148_up

sdi_clk148_down

sdi_mf0_bypass

sdi_mf1_auto_sleep

sdi_mf1_mute

sdi_tx_sd_hdn

Input 1 148.5 or 148.35 MHz dedicated transceiver reference

Input 1 302 MHz dedicated transceiver reference clock.

Input 1 625 MHz dedicated transceiver reference clock.

Input 1 Push button to power down LMK03328 after switching

Input 1 Global reset.

Output 8 Green LED display.

Output 8 Red LED display.

Input 1 On-board SDI RX serial data.

Output 1 On-board SDI TX serial data.

Output 1 Voltage control for Si516.

Output 1 Voltage control for Si516.

Output 1 On-board SDI RX Equalizer Bypass.

Output 1 On-board SDI RX Equalizer Auto Sleep.

Output 1 On-board SDI RX Equalizer Mute.

Output 1 On-board SDI TX cable driver slew rate control.

On-board Oscillator Signals

clock.

Programmable to 148.3516 MHz from the Clock Control

GUI.

Programmable to 296.7033 MHz from the Clock Control

GUI.

User Push Buttons and LEDs

the jumper settings.

fmcb_gbtclk_m2c_p0

fmcb_dp_m2c_p2

fmcb_la_tx_p1

fmcb_dp_c2m_p0

fmcb_la_tx_p12

fmcb_la_tx_n12

fmcb_la_tx_p14

fmcb_la_tx_n14

fmcb_la_tx_p15

Nextera SDI FMC Daughter Card Pins on FMC Port B

Input 1 297 or 296.7 MHz dedicated transceiver reference clock

from FMC port B.

Input 1 SDI RX serial data from FMC port B.

Input 1 RX cable equalizer lock status on Nextera daughter card.

Output 1 SDI TX serial data from FMC port B.

Output 1 Initialize LMH1983 on Nextera daughter card.

Output 1 F sync signal LMH1983 on Nextera daughter card.

Output 1 V sync signal LMH1983 on Nextera daughter card.

Output 1 H sync signal LMH1983 on Nextera daughter card.

Output 1 Power-down signal LMH1983 on Nextera daughter card.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

29

Page 30

Table 12. RX/TX/DU Top Signals

Signal Direction Width Description

rx_cdr_refclk

rx_core_refclk

tx_pll_refclk

tx_pll_refclk_alt

rx_rcfg_mgmt_clk

tx_rcfg_mgmt_clk

rx_vid_clkout

tx_vid_clkout

Input 1 RX transceiver reference clock. This clock must be a free-

Input 1 SDI RX core clock. This clock must be a free-running

Input 1 TX PLL reference clock. This clock must be a free-running

Input 1 Secondary TX PLL reference clock. This clock must be a

Input 1 RX reconfiguration management clock, Avalon-MM

Input 1 TX reconfiguration management clock, and Avalon-MM

Output 1 RX transceiver recovered parallel clock for video data.

Output 1 TX transceiver recovered parallel clock for video data.

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Clocks

running clock.

clock.

clock.

free-running clock.

interface clock, and PHY reset control input clock. This

clock must be a free-running clock.

interface clock, and PHY reset control input clock. This

clock must be a free-running clock.

tx_resetn

rx_resetn

tx_rcfg_mgmt_resetn

rx_rcfg_mgmt_resetn

sdi_rx_rst_proto_out

Video Signal Interfaces (Interface with Video Image and Processing (VIP) Components)

rx_vid_data

rx_vid_datavalid

rx_vid_std

Reset

Input 1 TX core and PHY reset signal.

Input 1 RX core and PHY reset signal.

Input 1 TX reconfiguration reset signal.

Input 1 RX reconfiguration reset signal.

Output 1 Reset signal generated to reset the receiver downstream

protocol logic. This generated reset signal is synchronous

to rx_vid_clkout clock domain.

Output 20*N Receiver parallel video data out.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Output 1 Data valid signal generated from SDI RX core. The timing

must be synchronous to rx_vid_clkout and has the

following settings:

• SD-SDI: 1H 4L 1H 5L

• HD/3G/6G/12G-SDI: H

Output 3 Received video standard.

• 3'b000: SD-SDI

• 3'b001: HD-SDI

• 3'b011: 3G-SDI Level A

• 3'b010 3G-SDI Level B

• 3'b101: 6G-SDI 4 Streams Interleaved

• 3'b100: 6G-SDI 8 Streams Interleaved

• 3'b111: 12G-SDI 8 Streams Interleaved

• 3'b110: 12G-SDI16 Streams Interleaved

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

30

Page 31

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Video Signal Interfaces (Interface with Video Image and Processing (VIP) Components)

rx_vid_locked

rx_vid_hsync

rx_vid_vsync

rx_vid_f

rx_vid_trs

tx_vid_data

tx_vid_datavalid

tx_vid_std

tx_vid_trs

Output 1 Frame locked indicates that the IP core has spotted

Output N Horizontal blanking interval timing signal. The receiver

Output N Vertical blanking interval timing signal. The receiver

Output N Field bit timing signal. This signal indicates which video

Output N On-board SDI TX cable driver slew rate control.

Output 20*N Receiver output signal that indicates current word is

Input 1 Transmitter parallel data valid. The timing (H: High, L:

Input 3 Indicates the desired transmit video standard.

Input 1 Transmitter TRS input.

multiple frames with the same timing.

asserts this signal when the horizontal blanking interval

is active.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

asserts this signal when the vertical blanking interval is

active.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

field is currently active. For interfaced frame, 0 means

first field (F0) while 1 means second field (F1). For

progressive frame, the value is always 0.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

timing reference signal (TRS). This signal asserts at the

first word of 3FF 000 000 TRS.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Low) must be synchronous to tx_pclk clock domain

and has the following settings:

• SD-SDI = 1H 4L 1H 5L

• HD-SDI = H (for single-rate) and 1H 1L (triple-rate/

multi-rate)

• 3G/6G/12G-SDI = H

• 3'b000: SD-SDI

• 3'b001: HD-SDI

• 3'b011: 3G-SDI Level A

• 3'b010 3G-SDI Level B

• 3'b101: 6G-SDI 4 Streams Interleaved

• 3'b100: 6G-SDI 8 Streams Interleaved

• 3'b111: 12G-SDI 8 Streams Interleaved

• 3'b110: 12G-SDI16 Streams Interleaved

For use in LN, CRC, or payload ID insertion. Assert on

the first word of both end of active video (EAV) TRS and

start of active video (SAV) TRS.

sdi_tx_enable_crc

sdi_tx_enable_ln

sdi_tx_ln

Other SDI Video Protocol Interfaces

Input 1 Enable CRC insertion for all SDI video standards, except

SD-SDI.

Input 1 Enable LN insertion for all SDI video standards, except

SD-SDI.

Input 11*N LN insertion in the data stream when

sdi_tx_enable_ln = 1.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

31

Page 32

sdi_tx_ln_b

sdi_tx_vpid_overwrit

e

sdi_tx_line_f0

sdi_tx_line_f1

sdi_tx_vpid_byte1

sdi_tx_vpid_byte2

sdi_tx_vpid_byte3

sdi_tx_vpid_byte4

sdi_tx_vpid_byte1_b

sdi_tx_vpid_byte2_b

sdi_tx_vpid_byte3_b

sdi_tx_vpid_byte4_b

sdi_rx_coreclk_is_nt

sc_paln

sdi_tx_datavalid

sdi_rx_align_locked

sdi_rx_trs_locked

sdi_rx_clkout_is_nts

c_paln

sdi_rx_format

sdi_rx_ap

sdi_rx_eav

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Other SDI Video Protocol Interfaces

Input 11*N LN insertion in the data stream when

sdi_tx_enable_ln = 1.

Only for 3G level B, 6G 8 streams interleaved, and 12G

16 streams interleaved.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Input 1 Enable this signal to overwrite the existing payload ID

Input 11*N Indicates the line number to be inserted with the payload

Input 11*N

Input 8*N Payload ID byte to be inserted in the payload ID field.

Input 8*N

Input 8*N

Input 8*N

Input 8*N

Input 8*N

Input 8*N

Input 8*N

Input 1

Output 1 Data valid signal generated from SDI TX core. The timing

Output 1 Alignment locked indicating the IP core has spotted a

Output N TRS locked indicating the IP core has spotted six

Output 1 Indicates that the receiver is receiving video rate at

Output 4*N Received video transport format. Refer to the SDI II IP

Output N Active picture interval timing signal. This signal asserts

Output N Receiver output signal that indicates current TRS is EAV.

embedded in the data stream.

ID.

To indicate whether rx_coreclk is 148.5 MHz or 148.35

MHz:

• 0: 148.5 MHz

• 1: 148.35 MHz

(H: High, L: Low) is synchronous to tx_vid_clkout

and has the following settings:

• SD-SDI = 1H 4L 1H 5L

• HD-SDI = H (for single-rate) and 1H 1L (triple-rate/

multi-rate)

• 3G/6G/12G-SDI = H

TRS and word alignment performed.

consecutive TRS with same timing.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

integer or fractional frame rate:

• 0: Integer frame rate

• 1: Fractional frame rate

User Guide for the encoding value.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

when the active picture interval is active.

This signal is asserted at the fourth word of TRS, which is

the XYZ word.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

32

Page 33

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Other SDI Video Protocol Interfaces

sdi_rx_ln

sdi_rx_ln_b

sdi_rx_crc_error_c

sdi_rx_crc_error_y

sdi_rx_crc_error_c_b

sdi_rx_crc_error_y_b

sdi_rx_line_f0

sdi_rx_line_f1

sdi_rx_vpid_byte1

sdi_rx_vpid_byte2

sdi_rx_vpid_byte3

sdi_rx_vpid_byte4

sdi_rx_vpid_checksum

Output 11*N Received line number from protocol.

Output 11*N

Output N CRC error status signal from protocol.

Output N

Output N

Output N

Output 11*N Payload ID status from protocol.

Output 11*N

Output 8*N

Output 8*N

Output 8*N

Output 8*N

Output N

_error

sdi_rx_vpid_valid

sdi_rx_vpid_byte1_b

sdi_rx_vpid_byte2_b

sdi_rx_vpid_byte3_b

sdi_rx_vpid_byte4_b

sdi_rx_vpid_checksum

Output N

Output 8*N

Output 8*N

Output 8*N

Output 8*N

Output N

_error_b

sdi_rx_vpid_valid_b

Output N

tx_pll_refclk_sel

tx_rcfg_cal_busy

rx_rcfg_cal_busy

gxb_rx_serial_data

gxb_tx_serial_data

gxb_rx_ready

gxb_tx_ready

gxb_rx_cal_busy

gxb_tx_cal_busy

tx_pll_locked

Transceiver Interfaces

Input 1

Input 1 Transceiver calibration status to TX PHY reset controller.

Input 1 Transceiver calibration status to RX PHY reset controller

Input 1 RX transceiver serial data.

Output 1 TX transceiver serial data.

Output 1 RX transceiver status.

Output 1 TX transceiver status.

Output 1 Calibration status signal from RX transceiver.

Output 1 Calibration status signal from TX transceiver.

Output 1 TX PLL lock status.

Indicate which of pll_locked signals to be monitored

for TX PHY reset controller's reset sequencing.

Always set to 1'b0 if only one PLL is in use.

and Rx reconfiguration management module.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

33

Page 34

tx_pll_locked_alt

cdr_reconfig_busy

tx_reconfig_busy

gxb_du_rcfg_write

gxb_du_rcfg_read

gxb_du_rcfg_address

gxb_du_rcfg_writedat

a

gxb_du_rcfg_readdata

gxb_du_rcfg_waitrequ

est

gxb_rx_rcfg_write

gxb_rx_rcfg_read

gxb_rx_rcfg_address

gxb_rx_rcfg_writedat

a

gxb_rx_rcfg_readdata

gxb_rx_rcfg_waitrequ

est

gxb_tx_rcfg_write

gxb_tx_rcfg_read

gxb_tx_rcfg_address

gxb_tx_rcfg_writedat

a

gxb_tx_rcfg_readdata

gxb_tx_rcfg_waitrequ

est

rx_rcfg_readdata

rx_rcfg_waitrequest

rx_rcfg_write

rx_rcfg_read

rx_rcfg_address

rx_rcfg_writedata

tx_rcfg_readdata

tx_rcfg_waitrequest

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Transceiver Interfaces

Output 1 TX PLL alt lock status.

Output 1 RX CDR reconfiguration status.

Output 1 TX PLL/transceiver reconfiguration status.

Transceiver Reconfiguration Interfaces

Input 1 Reconfiguration interface signals from transceiver arbiter

to duplex mode transceiver.

Input 1

Input 10

Input 32

Output 32

Output 1

Input 1 Reconfiguration interface signals from transceiver arbiter

to RX transceiver.

Input 1

Input 10

Input 32

Output 32

Output 1

Input 1 Reconfiguration interface signals from transceiver arbiter

to TX transceiver.

Input 1

Input 10

Input 32

Output 32

Output 1

Input 32 Reconfiguration interface signals from RX reconfiguration

management module to transceiver arbiter.

Input 1

Output 1

Output 1

Output 10

Output 32

Input 32 Reconfiguration interface signals from TX reconfiguration

management module to transceiver arbiter

Input 1

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

34

Page 35

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Transceiver Reconfiguration Interfaces

tx_rcfg_write

tx_rcfg_read

tx_rcfg_address

tx_rcfg_writedata

tx_fpll_rcfg_write

tx_fpll_rcfg_read

tx_fpll_rcfg_writeda

Output 1

Output 1

Output 10

Output 32

Input 1 Reconfiguration interface signals to fPLL Avalon-MM

Input 1

Input 32

ta

tx_fpll_rcfg_address

tx_fpll_rcfg_readdat

Input 10

Output 32

a

tx_fpll_rcfg_waitreq

Output 1

uest

Table 13. Loopback Top Signals

Signal Direction Width Description

sdi_tx_clkout

sdi_rx_clkout

sdi_reclk_sysclk

Input 1 TX transceiver recovered parallel clock for video data.

Input 1 RX transceiver recovered parallel clock for video data.

Input 1 Input clock for reclock module (without external VCXO

interface.

Clocks

solution). This clock should be the same as fPLL

reconfig_clk.

sdi_rx_rst_proto

sdi_reclk_rst

sdi_rx_dataout

sdi_rx_dataout_valid

sdi_rx_std

sdi_rx_trs

sdi_rx_trs_locked

sdi_rx_frame_locked

sdi_tx_dataout_valid

Resets

Input 1 Reset signal from SDI RX core to indicate that the

protocol is currently held in reset.

Input 1 Reset signal to reclock module (without external VCXO

solution).

SDI Related Signals

Input 20*N Receiver recovered parallel video data.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Input 1 Data valid signal generated from SDI RX core.

Input 3 Received video standard from SDI RX core.

Input N Receiver output signal from SDI II IP core that indicates

current word is TRS.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Input N TRS locked status signal from SDI RX core.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Input 1 Frame locked status signal from SDI RX core.

Input 1 Data valid signal generated from SDI TX core.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

35

Page 36

sdi_rx_h

sdi_rx_format

sdi_rx_clkout_is_nts

c_paln

sdi_tx_datain

sdi_tx_datain_valid

sdi_tx_trs

sdi_tx_std

vcoclk_up

vcoclk_down

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

SDI Related Signals

Input 1 Horizontal blanking interval timing signal extracted from

SDI RX core.

Input 4 Received video transport format.

Input 1 Indication from SDI RX core that the receiver is receiving

video rate at integer or fractional frame rate.

Output 20*N Parallel video data input to SDI TX core.

Note: N = 4 (multi-rate design) or 1 (triple-rate design)

Output 1 Data valid for the transmitter parallel data to SDI TX

core.

Output 1 Transmitter TRS input to indicate that the current word is

a TRS to SDI TX core.

Output 3 Indicates the desired transmit video standard to SDI TX

core.

Voltage Control Signals for On-board Si516

Output 1 Voltage up signal to Si516 to increase the voltage.

Output 1 Voltage down signal to Si516 to decrease the voltage.

fPLL Reconfiguration Signals

pll_locked

pll_reconfig_readdat

Input 1 PLL lock status signal.

Input 32 Reconfiguration interface signals to fPLL Avalon-MM

a

pll_reconfig_waitreq

Input 1

uest

pll_reconfig_write

pll_reconfig_read

pll_reconfig_writeda

Output 1

Output 1

Output 32

ta

pll_reconfig_address

Output 10

Table 14. Transceiver Arbiter Signals

Signal Direction Width Description

On-board Oscillator Signals

clk

reset

rx_rcfg_en

tx_rcfg_en

rx_rcfg_ch

Input 1 Reconfiguration clock. This clock should be sharing the

Input 1 Reset signal. This reset should be sharing the same reset

Input 1 RX reconfiguration enable signal.

Input 1 TX reconfiguration enable signal.

Input 2 Indicates which channel to be reconfigured on RX.

interface.

same clock as reconfiguration management blocks.

as reconfiguration management blocks.

Always assign to 2'b00 for SDI case.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

36

Page 37

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Signal Direction Width Description

tx_rcfg_ch

rx_reconfig_mgmt_wri

Input 2 Indicates which channel to be reconfigured on TX.

Input 1 Reconfiguration Avalon-MM interfaces from RX

te

rx_reconfig_mgmt_rea

Input 1

d

rx_reconfig_mgmt_add

Input 10

ress

rx_reconfig_mgmt_wri

Input 32

tedata

rx_reconfig_mgmt_rea

Output 32

ddata

rx_reconfig_mgmt_wai

Output 1

trequest

tx_reconfig_mgmt_wri

Input 1 Reconfiguration Avalon-MM interfaces from TX

te

tx_reconfig_mgmt_rea

Input 1

d

tx_reconfig_mgmt_add

Input 10

ress

tx_reconfig_mgmt_wri

Input 32

tedata

tx_reconfig_mgmt_rea

Output 32

ddata

tx_reconfig_mgmt_wai

Output 1

trequest

reconfig_write

reconfig_read

reconfig_address

reconfig_writedata

rx_reconfig_readdata

rx_reconfig_waitrequ

Output 1 Reconfiguration Avalon-MM interfaces to transceiver.

Output 1

Output 10

Output 32

Input 32

Input 1

est

tx_reconfig_readdata

tx_reconfig_waitrequ

Input 1

Input 1

est

rx_cal_busy

tx_cal_busy

rx_reconfig_cal_busy

tx_reconfig_cal_busy

Input 1 Calibration status signal from RX transceiver.

Input 1 Calibration status signal from TX transceiver.

Output 1 Calibration status signal to RX transceiver PHY reset

Output 1 Calibration status signal from TX transceiver PHY reset

On-board Oscillator Signals

Always assign to 2'b00 for SDI case.

reconfiguration management.

reconfiguration management.

control.

control.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

37

Page 38

clk

rst

bar_100_75n

enable

patho

blank

no_color

sgmt_frame

tx_std

tx_format

dl_mapping

ntsc_paln

dout

dout_valid

trs

ln

dout_b

dout_valid_b

trs_b

ln_b

vpid_byte1

vpid_byte2

vpid_byte3

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

Video Pattern Generator Signals

Input 1 Clock signal. This clock must be connected to the

tx_vid_clkout input signal on TX/Du top.

Input 1 Reset signal. This reset signal should be synchronized

Input 1 Enable this signal to generate 100% color-bar pattern.

Input 1 This signal acts as a data valid signal to this module. This

Input 1 Enable this signal to generate pathological pattern.

Input 1 Enable this signal to generate blank signal.

Input 1 Enable this signal to generate bar with no color.

Input 1 Enable this signal to generate payload ID for segmented

Input 3 Indicates the desired transmit video standard. This input

Input 4 Indicates the desired transmit video format.

Input 1 Enable this signal to generate data streams with dual-

Input 1 Enable this signal to generate payload ID for fractional

Output 20*S

Output 1 Data valid output signal to be connected to the

with the tx_vid_clkout clock signal from the TX/Du

top.

Disable to generate 75% color-bar pattern.

signal should be connected to the sdi_tx_datavalid

signal from the TX/Du top.

frame video format when generating 1080i50 or 1080i60

video.

signal must match tx_vid_std on the TX/Du top.

link mapping.

Note: Applicable only for HD dual link or 3G Level B

dual link video standard.

frame rate video format. Disable to generate integer

frame rate video format.

Data output signal to be connected to the tx_vid_data

input signal on the TX/Du top.

tx_vid_datavalid input signal on the TX/Du top.

Output 1

Output 11*S Line number output signal to be connected to the

TRS output signal to be connected to the tx_vid_trs

input signal on the TX/Du top.

sdi_tx_ln input signal on the TX/Du top.

Output 20*S Data output signal for link B (HD dual link).

Output 1 Data valid output signal for link B (HD dual link).

Output 1 TRS output signal for link B (HD dual link).

Output 11*S Line number output signal to be connected to the

sdi_tx_ln_b input signal on the TX/Du top.

Input 8*N The payload ID output signal to be connected to

sdi_tx_vpid_byte1 input signal on TX/Du top.

Input 8*N The payload ID output signal to be connected to

sdi_tx_vpid_byte2 input signal on TX/Du top.

Input 8*N The payload ID output signal to be connected to

sdi_tx_vpid_byte3 input signal on TX/Du top.

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

38

Page 39

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

vpid_byte4

vpid_byte1_b

vpid_byte2_b

vpid_byte3_b

vpid_byte4_b

line_f0

line_f1

avmm_clk_in_clk

tx_clkout_in_clk

avmm_clk_reset_n

pattgen_rst_reset_in

Input 8*N The payload ID output signal to be connected to

Input 8*N The payload ID output signal to be connected to

Input 8*N The payload ID output signal to be connected to

Input 8*N The payload ID output signal to be connected to

Input 8*N The payload ID output signal to be connected to

Output 11*N The line number output signal to be inserted with the

Output 11*N The line number output signal to be inserted with the

Pattern Generator Control Module Signals

Input 1 Clock signal to Avalon-MM interface.

Input 1 Clock signal to Parallel I/O (PIO) IP. This clock must

Input 1 Reset signal to Avalon-MM interface.

Input 1 Input reset signals to a reset synchronizer which

0

pattgen_rst_reset_in

Input 1

1

pattgen_rst_reset_ou

Input 1 Output reset from the reset synchronizer. This reset

t

pattgen_ctrl_pio_out

Output 12 Output control signal from PIO to control the video

_port

Video Pattern Generator Signals

sdi_tx_vpid_byte4 input signal on TX/Du top.

sdi_tx_vpid_byte1_b input signal on TX/Du top.

sdi_tx_vpid_byte2_b input signal on TX/Du top.

sdi_tx_vpid_byte3_b input signal on TX/Du top.

sdi_tx_vpid_byte4_b input signal on TX/Du top.

payload ID. This signal must connect to

sdi_tx_line_f0 input signal on TX/Du top.

payload ID. This signal must connect to

sdi_tx_line_f1 input signal on TX/Du top.

share the same clock as video pattern generator.

synchronizes the reset to the tx_clkout_in_clk clock

domain.

synchronizes to the tx_clkout_in_clk clock domain

and connects to the video pattern generator’s input

reset.

pattern generator.

2.6 Video Pattern Generator Parameters

Customize the video pattern generator parameters according to your design.

Intel® Arria® 10 SDI II IP Core Design Example User Guide

39

Page 40

Table 15. Video Pattern Generator Parameters

D3 D4 D5 D6 D7 D8 D9 D10

Parameter Valid Value Default Value Description

OUTW_MULTP

SD_BIT_WIDTH

TEST_GEN_ANC

TEST_GEN_VPID

1, 4 1 Defines the width of the output portsh. Select 4

10, 20 10 Defines the generated SD interface bit width.

0, 1 0 Select 1 to generate the ancillary data packet in

0, 1 0 Select 1 to generate the payload ID packet in

2.7 Hardware Setup

To run the hardware test for parallel loopback designs, connect an SDI video generator

to the receiver input pin.

• Connect an external video analyzer to the TX instance to verify full functionality.

• To validate if the RX core locks to the signal and receives the video data correctly,

use the on-board LEDs that display the RX status.

2 SDI II Design Example Detailed Description

UG-20076 | 2017.05.08

for a multi-rate design, otherwise select 1.

This value must match with the SD interface bit

width parameter of the SDI II TX core in the

same design.

output stream. The module inserts the

embedded Data ID (DID) packet with 10’h242 if

TEST_GEN_VPID is not enabled.

output streams. The module inserts the

embedded Data ID (DID) packet with 10’h241.

To run the hardware test for serial loopback designs, connect the transmitter output

pin directly to the receiver input pin.

• To validate if the RX core locks to the signal and receives the video data correctly,

use the on-board LEDs that display the RX status.

• You may also connect an SDI signal analyzer to the transmitter output pin to view

the generated image.

Figure 16. Arria 10 GX Development Board User LEDs

Table 16. On-board User LED Functions

LEDs Function

D3–D5 Indicates the receiver video standard:

• 000: SD-SDI

• 001: HD-SDI

• 010: 3G Level B

• 011: 3G Level A

• 100: 6G 8 Streams Interleaved

continued...

Intel® Arria® 10 SDI II IP Core Design Example User Guide

40

Page 41

Top

RX Top

SDI II