Page 1

Intel® Arria® 10 Transceiver PHY

User Guide

Updated for Intel® Quartus® Prime Design Suite: 18.0

Subscribe

Send Feedback

UG-01143 | 2018.06.15

Latest document on the web: PDF | HTML

Page 2

Contents

Contents

1. Arria® 10 Transceiver PHY Overview ..............................................................................8

1.1. Device Transceiver Layout......................................................................................9

1.1.1. Arria 10 GX Device Transceiver Layout........................................................10

1.1.2. Arria 10 GT Device Transceiver Layout........................................................ 15

1.1.3. Arria 10 GX and GT Device Package Details ................................................ 17

1.1.4. Arria 10 SX Device Transceiver Layout........................................................ 17

1.1.5. Arria 10 SX Device Package Details............................................................ 19

1.2. Transceiver PHY Architecture Overview.................................................................. 20

1.2.1. Transceiver Bank Architecture....................................................................20

1.2.2. PHY Layer Transceiver Components........................................................... 25

1.2.3. Transceiver Phase-Locked Loops................................................................28

1.2.4. Clock Generation Block (CGB)...................................................................29

1.3. Calibration.......................................................................................................... 29

1.4. Intel Arria 10 Transceiver PHY Overview Revision History.......................................... 30

2. Implementing Protocols in Arria 10 Transceivers......................................................... 32

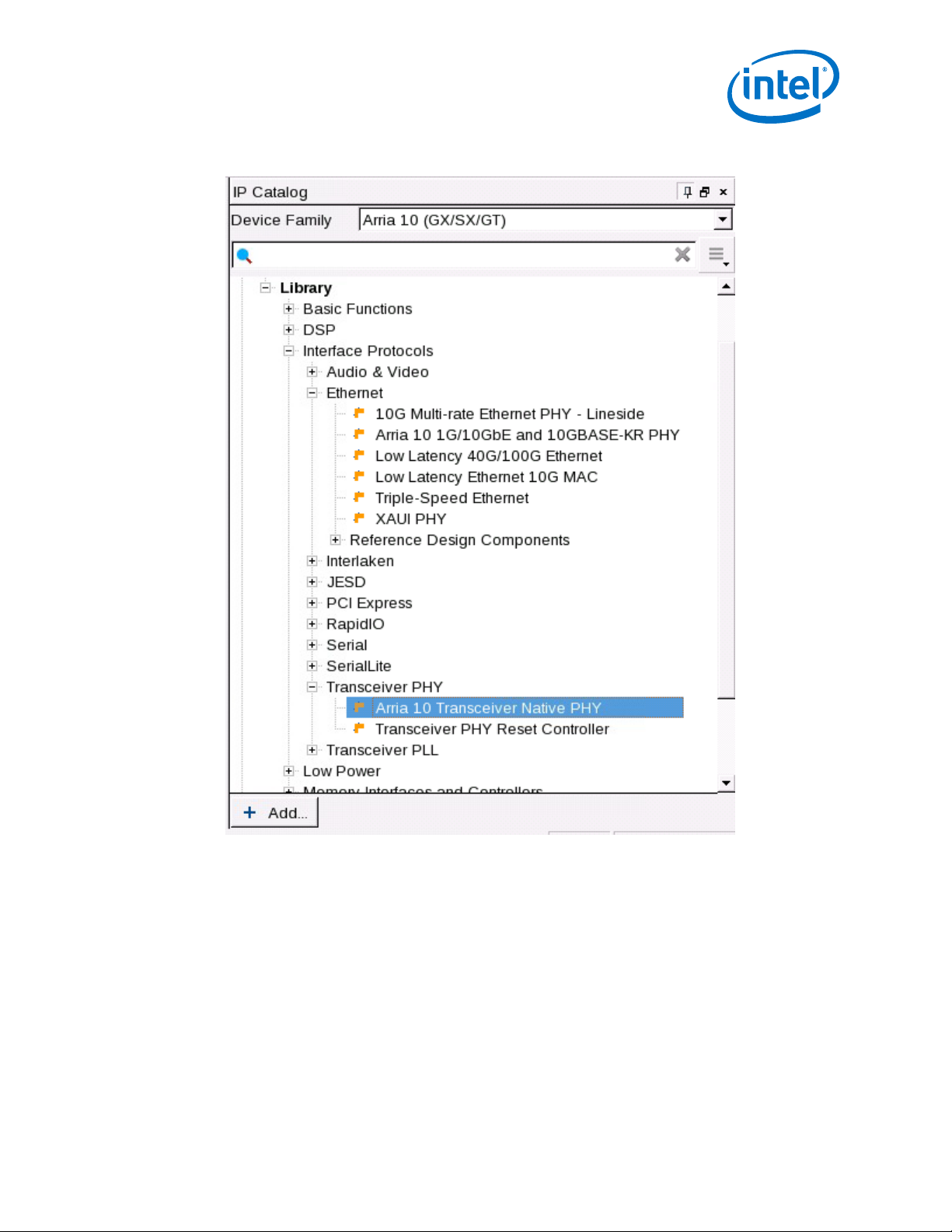

2.1. Transceiver Design IP Blocks................................................................................. 32

2.2. Transceiver Design Flow........................................................................................33

2.2.1. Select and Instantiate the PHY IP Core........................................................33

2.2.2. Configure the PHY IP Core.........................................................................35

2.2.3. Generate the PHY IP Core......................................................................... 36

2.2.4. Select the PLL IP Core.............................................................................. 36

2.2.5. Configure the PLL IP Core........................................................................ 38

2.2.6. Generate the PLL IP Core ......................................................................... 39

2.2.7. Reset Controller ......................................................................................39

2.2.8. Create Reconfiguration Logic..................................................................... 39

2.2.9. Connect the PHY IP to the PLL IP Core and Reset Controller........................... 40

2.2.10. Connect Datapath ................................................................................ 40

2.2.11. Make Analog Parameter Settings ............................................................. 40

2.2.12. Compile the Design................................................................................ 41

2.2.13. Verify Design Functionality...................................................................... 41

2.3. Arria 10 Transceiver Protocols and PHY IP Support....................................................41

2.4. Using the Arria 10 Transceiver Native PHY IP Core....................................................45

2.4.1. Presets................................................................................................... 48

2.4.2. General and Datapath Parameters .............................................................48

2.4.3. PMA Parameters......................................................................................51

2.4.4. Enhanced PCS Parameters ........................................................................55

2.4.5. Standard PCS Parameters........................................................................ 62

2.4.6. PCS Direct ............................................................................................ 67

2.4.7. Dynamic Reconfiguration Parameters.......................................................... 67

2.4.8. PMA Ports.............................................................................................. 73

2.4.9. Enhanced PCS Ports................................................................................ 76

2.4.10. Standard PCS Ports................................................................................ 86

2.4.11. IP Core File Locations............................................................................. 91

2.4.12. Unused Transceiver RX Channels.............................................................. 93

2.4.13. Unsupported Features.............................................................................94

2.5. Interlaken..........................................................................................................94

Intel® Arria® 10 Transceiver PHY User Guide

2

Page 3

Contents

2.5.1. Metaframe Format and Framing Layer Control Word.....................................95

2.5.2. Interlaken Configuration Clocking and Bonding............................................97

2.5.3. How to Implement Interlaken in Arria 10 Transceivers.................................103

2.5.4. Design Example..................................................................................... 106

2.5.5. Native PHY IP Parameter Settings for Interlaken........................................107

2.6. Ethernet........................................................................................................... 111

2.6.1. Gigabit Ethernet (GbE) and GbE with IEEE 1588v2..................................... 112

2.6.2. 10GBASE-R, 10GBASE-R with IEEE 1588v2, and 10GBASE-R with FEC

Variants................................................................................................ 124

2.6.3. 10GBASE-KR PHY IP Core .......................................................................135

2.6.4. 1-Gigabit/10-Gigabit Ethernet (GbE) PHY IP Core....................................... 164

2.6.5. 1G/2.5G/5G/10G Multi-rate Ethernet PHY IP Core.......................................199

2.6.6. XAUI PHY IP Core...................................................................................214

2.6.7. Acronyms.............................................................................................228

2.7. PCI Express (PIPE)............................................................................................ 229

2.7.1. Transceiver Channel Datapath for PIPE......................................................230

2.7.2. Supported PIPE Features.........................................................................231

2.7.3. How to Connect TX PLLs for PIPE Gen1, Gen2, and Gen3 Modes................... 240

2.7.4. How to Implement PCI Express (PIPE) in Arria 10 Transceivers....................246

2.7.5. Native PHY IP Parameter Settings for PIPE ...............................................248

2.7.6. fPLL IP Parameter Core Settings for PIPE...................................................253

2.7.7. ATX PLL IP Parameter Core Settings for PIPE..............................................255

2.7.8. Native PHY IP Ports for PIPE................................................................... 257

2.7.9. fPLL Ports for PIPE..................................................................................264

2.7.10. ATX PLL Ports for PIPE...........................................................................266

2.7.11. Preset Mappings to TX De-emphasis........................................................267

2.7.12. How to Place Channels for PIPE Configurations......................................... 268

2.7.13. PHY IP Core for PCIe (PIPE) Link Equalization for Gen3 Data Rate............... 274

2.7.14. Using Transceiver Toolkit (TTK)/System Console/Reconfiguration

Interface to manually tune Arria 10 PCIe designs (Hard IP(HIP) and PIPE)

(For debug only).................................................................................... 277

2.8. CPRI................................................................................................................279

2.8.1. Transceiver Channel Datapath and Clocking for CPRI...................................280

2.8.2. Supported Features for CPRI ..................................................................281

2.8.3. Word Aligner in Manual Mode for CPRI.......................................................283

2.8.4. How to Implement CPRI in Arria 10 Transceivers........................................ 284

2.8.5. Native PHY IP Parameter Settings for CPRI............................................... 285

2.9. Other Protocols..................................................................................................289

2.9.1. Using the "Basic (Enhanced PCS)" and "Basic with KR FEC" Configurations

of Enhanced PCS....................................................................................289

2.9.2. Using the Basic/Custom, Basic/Custom with Rate Match Configurations of

Standard PCS........................................................................................ 300

2.9.3. Design Considerations for Implementing Arria 10 GT Channels..................... 319

2.9.4. How to Implement PCS Direct Transceiver Configuration Rule.......................324

2.10. Simulating the Transceiver Native PHY IP Core..................................................... 325

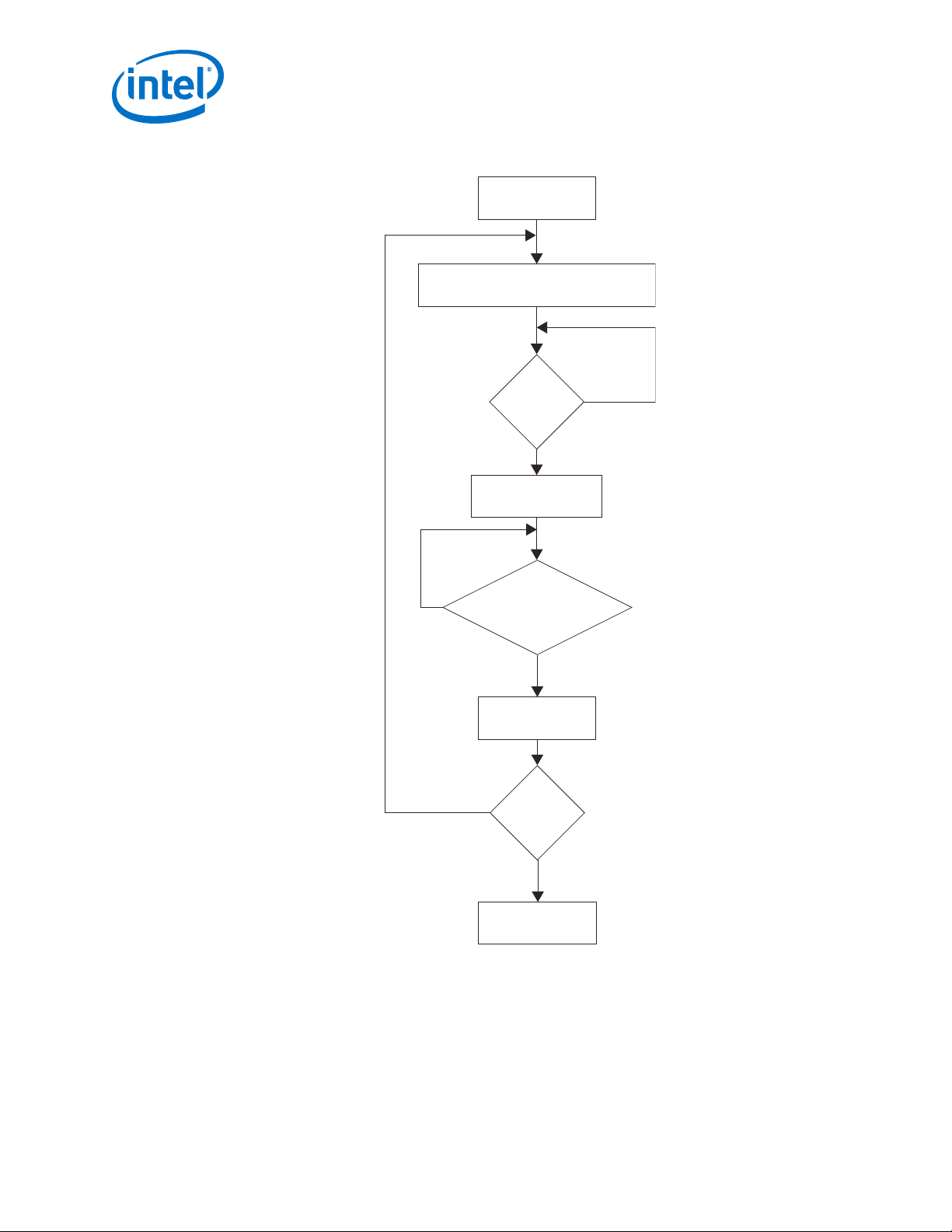

2.10.1. NativeLink Simulation Flow.................................................................... 326

2.10.2. Scripting IP Simulation..........................................................................331

2.10.3. Custom Simulation Flow........................................................................ 332

2.11. Implementing Protocols in Intel Arria 10 Transceivers Revision History.....................335

3. PLLs and Clock Networks............................................................................................ 347

3.1. PLLs................................................................................................................. 349

Intel® Arria® 10 Transceiver PHY User Guide

3

Page 4

Contents

3.1.1. Transmit PLLs Spacing Guideline when using ATX PLLs and fPLLs.................. 349

3.1.2. ATX PLL................................................................................................ 350

3.1.3. fPLL......................................................................................................359

3.1.4. CMU PLL............................................................................................... 368

3.2. Input Reference Clock Sources............................................................................372

3.2.1. Dedicated Reference Clock Pins...............................................................374

3.2.2. Receiver Input Pins.................................................................................374

3.2.3. PLL Cascading as an Input Reference Clock Source..................................... 375

3.2.4. Reference Clock Network.........................................................................375

3.2.5. Global Clock or Core Clock as an Input Reference Clock...............................375

3.3. Transmitter Clock Network..................................................................................375

3.3.1. x1 Clock Lines....................................................................................... 376

3.3.2. x6 Clock Lines....................................................................................... 377

3.3.3. xN Clock Lines....................................................................................... 379

3.3.4. GT Clock Lines....................................................................................... 381

3.4. Clock Generation Block....................................................................................... 383

3.5. FPGA Fabric-Transceiver Interface Clocking............................................................ 384

3.6. Transmitter Data Path Interface Clocking...............................................................386

3.7. Receiver Data Path Interface Clocking...................................................................387

3.8. Unused/Idle Clock Line Requirements................................................................... 389

3.9. Channel Bonding................................................................................................389

3.9.1. PMA Bonding......................................................................................... 389

3.9.2. PMA and PCS Bonding.............................................................................391

3.9.3. Selecting Channel Bonding Schemes.........................................................392

3.9.4. Skew Calculations.................................................................................. 393

3.10. PLL Feedback and Cascading Clock Network.........................................................393

3.11. Using PLLs and Clock Networks.......................................................................... 398

3.11.1. Non-bonded Configurations....................................................................398

3.11.2. Bonded Configurations.......................................................................... 403

3.11.3. Implementing PLL Cascading..................................................................408

3.11.4. Mix and Match Example.........................................................................409

3.11.5. Timing Closure Recommendations...........................................................413

3.12. PLLs and Clock Networks Revision History............................................................414

4. Resetting Transceiver Channels.................................................................................. 416

4.1. When Is Reset Required? ................................................................................... 416

4.2. Transceiver PHY Implementation.......................................................................... 417

4.3. How Do I Reset?................................................................................................ 418

4.3.1. Model 1: Default Model........................................................................... 418

4.3.2. Model 2: Acknowledgment Model..............................................................427

4.3.3. Transceiver Blocks Affected by Reset and Powerdown Signals....................... 432

4.4. Using the Transceiver PHY Reset Controller............................................................433

4.4.1. Parameterizing the Transceiver PHY Reset Controller IP............................... 435

4.4.2. Transceiver PHY Reset Controller Parameters............................................. 435

4.4.3. Transceiver PHY Reset Controller Interfaces............................................... 437

4.4.4. Transceiver PHY Reset Controller Resource Utilization.................................. 441

4.5. Using a User-Coded Reset Controller.....................................................................441

4.5.1. User-Coded Reset Controller Signals......................................................... 441

4.6. Combining Status or PLL Lock Signals .................................................................. 442

4.7. Timing Constraints for Bonded PCS and PMA Channels............................................ 443

4.8. Resetting Transceiver Channels Revision History..................................................... 445

Intel® Arria® 10 Transceiver PHY User Guide

4

Page 5

Contents

5. Arria 10 Transceiver PHY Architecture........................................................................ 447

5.1. Arria 10 PMA Architecture................................................................................... 447

5.1.1. Transmitter........................................................................................... 447

5.1.2. Receiver................................................................................................450

5.1.3. Loopback.............................................................................................. 460

5.2. Arria 10 Enhanced PCS Architecture.....................................................................461

5.2.1. Transmitter Datapath.............................................................................462

5.2.2. Receiver Datapath.................................................................................471

5.3. Arria 10 Standard PCS Architecture..................................................................... 479

5.3.1. Transmitter Datapath..............................................................................480

5.3.2. Receiver Datapath..................................................................................485

5.4. Arria 10 PCI Express Gen3 PCS Architecture......................................................... 495

5.4.1. Transmitter Datapath.............................................................................496

5.4.2. Receiver Datapath..................................................................................497

5.4.3. PIPE Interface........................................................................................498

5.5. Intel Arria 10 Transceiver PHY Architecture Revision History.....................................499

6. Reconfiguration Interface and Dynamic Reconfiguration .......................................... 502

6.1. Reconfiguring Channel and PLL Blocks...................................................................503

6.2. Interacting with the Reconfiguration Interface........................................................503

6.2.1. Reading from the Reconfiguration Interface............................................... 505

6.2.2. Writing to the Reconfiguration Interface.................................................... 505

6.3. Configuration Files............................................................................................. 506

6.4. Multiple Reconfiguration Profiles...........................................................................509

6.5. Embedded Reconfiguration Streamer.................................................................... 510

6.6. Arbitration.........................................................................................................512

6.7. Recommendations for Dynamic Reconfiguration......................................................515

6.8. Steps to Perform Dynamic Reconfiguration............................................................ 516

6.9. Direct Reconfiguration Flow................................................................................. 519

6.10. Native PHY IP or PLL IP Core Guided Reconfiguration Flow..................................... 519

6.11. Reconfiguration Flow for Special Cases................................................................ 521

6.11.1. Switching Transmitter PLL ....................................................................521

6.11.2. Switching Reference Clocks....................................................................523

6.12. Changing PMA Analog Parameters......................................................................527

6.12.1. Changing VOD, Pre-emphasis Using Direct Reconfiguration Flow................. 530

6.12.2. Changing CTLE Settings in Manual Mode Using Direct Reconfiguration Flow.. 531

6.12.3. CTLE Settings in Triggered Adaptation Mode.............................................531

6.12.4. Enabling and Disabling Loopback Modes Using Direct Reconfiguration Flow...533

6.13. Ports and Parameters........................................................................................535

6.14. Dynamic Reconfiguration Interface Merging Across Multiple IP Blocks...................... 542

6.15. Embedded Debug Features................................................................................ 544

6.15.1. Altera Debug Master Endpoint................................................................ 544

6.15.2. Optional Reconfiguration Logic............................................................... 544

6.16. Using Data Pattern Generators and Checkers....................................................... 550

6.16.1. Using PRBS Data Pattern Generator and Checker..................................... 550

6.16.2. Using Pseudo Random Pattern Mode........................................................559

6.17. Timing Closure Recommendations...................................................................... 560

6.18. Unsupported Features.......................................................................................563

6.19. Arria 10 Transceiver Register Map.......................................................................564

6.20. Reconfiguration Interface and Dynamic Revision History........................................ 564

Intel® Arria® 10 Transceiver PHY User Guide

5

Page 6

Contents

7. Calibration.................................................................................................................. 567

7.1. Reconfiguration Interface and Arbitration with PreSICE Calibration Engine .................567

7.2. Calibration Registers...........................................................................................569

7.2.1. Avalon-MM Interface Arbitration Registers................................................. 569

7.2.2. Transceiver Channel Calibration Registers..................................................570

7.2.3. Fractional PLL Calibration Registers...........................................................570

7.2.4. ATX PLL Calibration Registers...................................................................571

7.2.5. Capability Registers................................................................................571

7.2.6. Rate Switch Flag Register........................................................................573

7.3. Power-up Calibration.......................................................................................... 574

7.4. User Recalibration.............................................................................................. 576

7.4.1. Recalibration After Transceiver Reference Clock Frequency or Data Rate

Change.................................................................................................579

7.5. Calibration Example............................................................................................581

7.5.1. ATX PLL Recalibration............................................................................. 581

7.5.2. Fractional PLL Recalibration..................................................................... 581

7.5.3. CDR/CMU PLL Recalibration..................................................................... 582

7.5.4. PMA Recalibration...................................................................................582

7.6. Calibration Revision History................................................................................. 583

8. Analog Parameter Settings........................................................................................ 585

8.1. Making Analog Parameter Settings using the Assignment Editor................................585

8.2. Updating Quartus Settings File with the Known Assignment.................................... 585

8.3. Analog Parameter Settings List............................................................................586

8.4. Receiver General Analog Settings........................................................................ 588

8.4.1. XCVR_A10_RX_LINK..............................................................................588

8.4.2. XCVR_A10_RX_TERM_SEL......................................................................589

8.4.3. XCVR_VCCR_VCCT_VOLTAGE - RX............................................................589

8.5. Receiver Analog Equalization Settings.................................................................. 590

8.5.1. CTLE Settings........................................................................................ 590

8.5.2. VGA Settings......................................................................................... 593

8.5.3. Decision Feedback Equalizer (DFE) Settings.............................................. 594

8.6. Transmitter General Analog Settings.................................................................... 596

8.6.1. XCVR_A10_TX_LINK..............................................................................596

8.6.2. XCVR_A10_TX_TERM_SEL.......................................................................597

8.6.3. XCVR_A10_TX_COMPENSATION_EN........................................................ 597

8.6.4. XCVR_VCCR_VCCT_VOLTAGE - TX............................................................598

8.6.5. XCVR_A10_TX_SLEW_RATE_CTRL............................................................599

8.7. Transmitter Pre-Emphasis Analog Settings............................................................600

8.7.1. XCVR_A10_TX_PRE_EMP_SIGN_PRE_TAP_1T............................................600

8.7.2. XCVR_A10_TX_PRE_EMP_SIGN_PRE_TAP_2T............................................600

8.7.3. XCVR_A10_TX_PRE_EMP_SIGN_1ST_POST_TAP........................................601

8.7.4. XCVR_A10_TX_PRE_EMP_SIGN_2ND_POST_TAP....................................... 601

8.7.5. XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_PRE_TAP_1T......................... 602

8.7.6. XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_PRE_TAP_2T......................... 602

8.7.7. XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_1ST_POST_TAP..................... 603

8.7.8. XCVR_A10_TX_PRE_EMP_SWITCHING_CTRL_2ND_POST_TAP.....................604

8.8. Transmitter VOD Settings....................................................................................604

8.8.1. XCVR_A10_TX_VOD_OUTPUT_SWING_CTRL.............................................604

8.9. Dedicated Reference Clock Settings...................................................................... 605

8.9.1. XCVR_A10_REFCLK_TERM_TRISTATE.......................................................605

Intel® Arria® 10 Transceiver PHY User Guide

6

Page 7

Contents

8.9.2. XCVR_A10_TX_XTX_PATH_ANALOG_MODE................................................606

8.10. Unused Transceiver RX Channels Settings............................................................606

8.11. Analog Parameter Settings Revision History......................................................... 606

Intel® Arria® 10 Transceiver PHY User Guide

7

Page 8

UG-01143 | 2018.06.15

1. Arria® 10 Transceiver PHY Overview

This user guide provides details about the Arria® 10 transceiver physical (PHY) layer

architecture, PLLs, clock networks, and transceiver PHY IP. It also provides protocol

specific implementation details and describes features such as transceiver reset and

dynamic reconfiguration of transceiver channels and PLLs.

Intel® Arria 10 FPGAs offer up to 96 GX transceiver channels with integrated advanced

high speed analog signal conditioning and clock data recovery techniques for chip-tochip, chip-to-module, and backplane applications.

The Arria 10 GX and SX devices have GX transceiver channels that can support data

rates up to 17.4 Gbps for chip-to-chip applications and 12.5 Gbps for backplane

applications.

The Arria 10 GT device has up to 6 GT transceiver channels, that can support data

rates up to 25.8 Gbps for short reach chip-to-chip and chip-to-module applications.

Additionally, the GT devices have GX transceiver channels that can support data rates

up to 17.4 Gbps for chip-to-chip and 12.5 Gbps for backplane applications. If all 6 GT

channels are used in GT mode, then the GT device also has up to 54 GX transceiver

channels.

The Arria 10 transceivers support reduced power modes with data rates up to 11.3

Gbps (chip-to-chip) for critical power sensitive designs. In GX devices that have

transceivers on both sides of the device, each side can be operated independently in

standard and reduced power modes. You can achieve transmit and receive data rates

below 1.0 Gbps with oversampling.

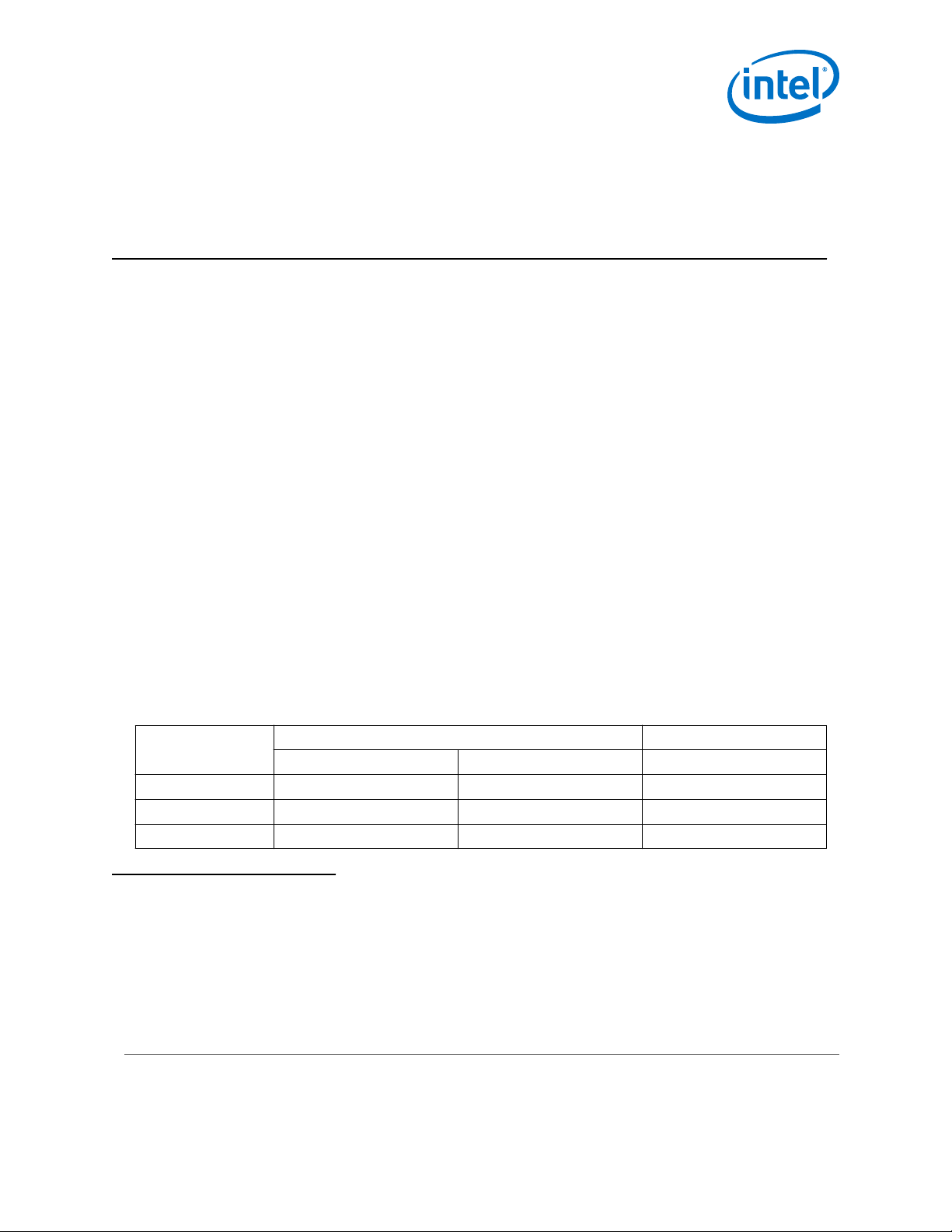

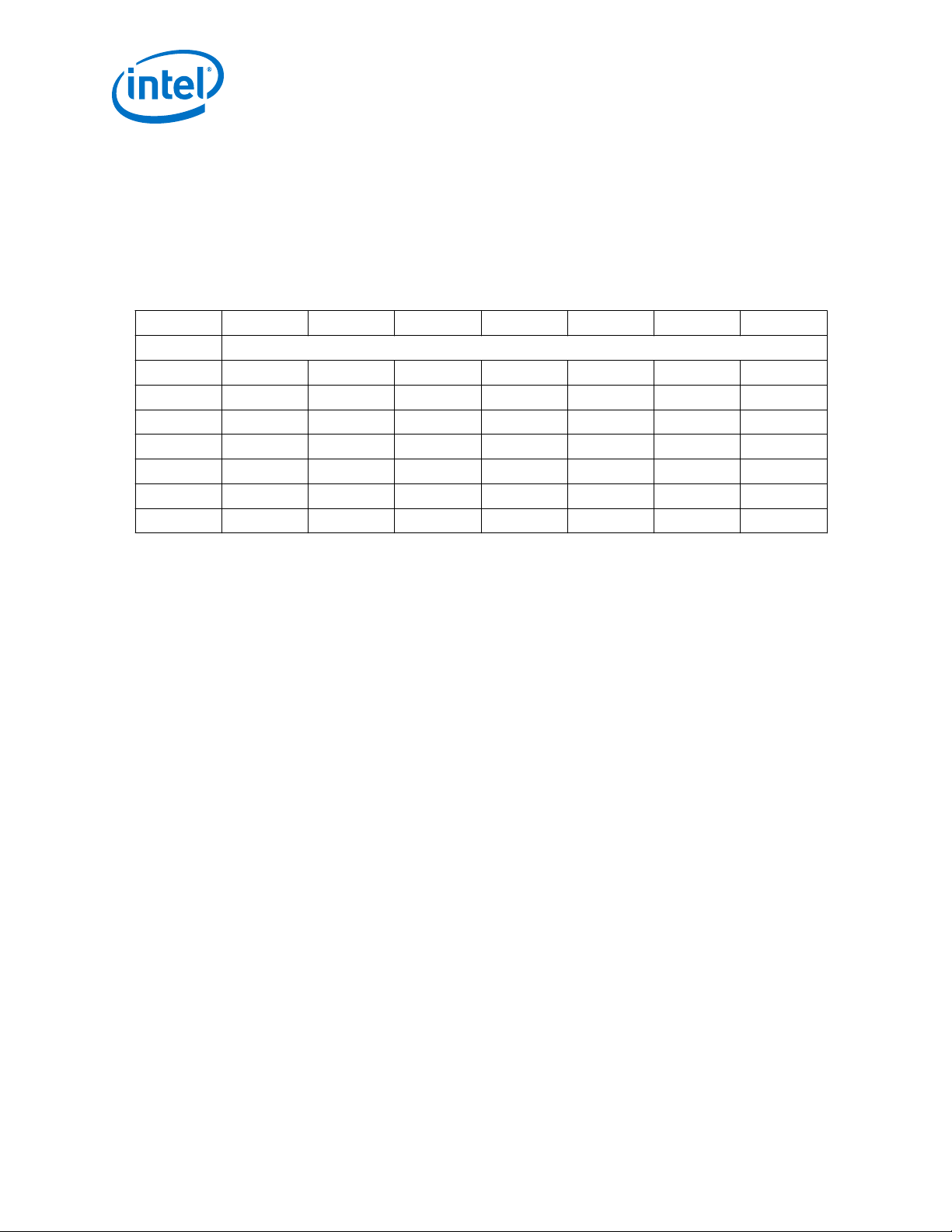

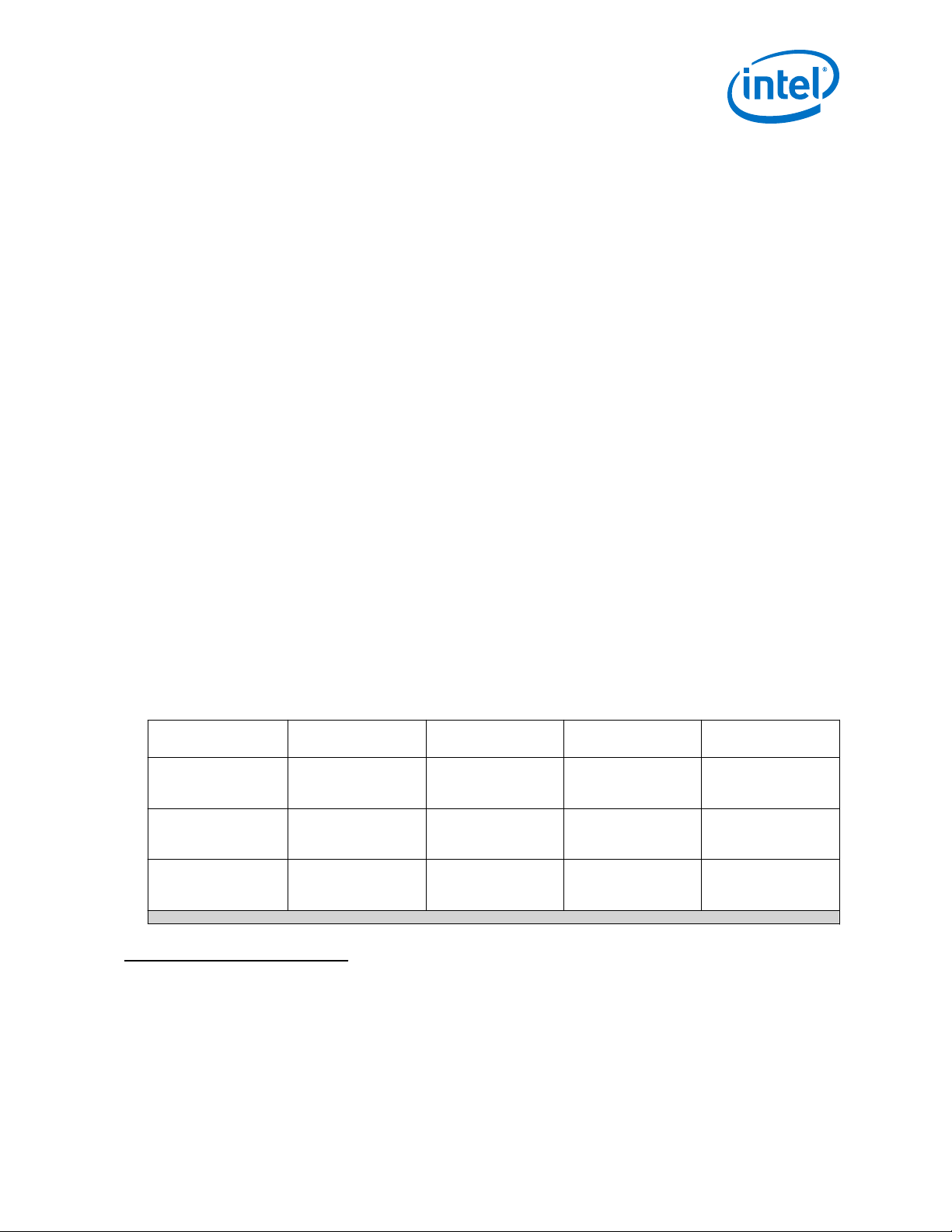

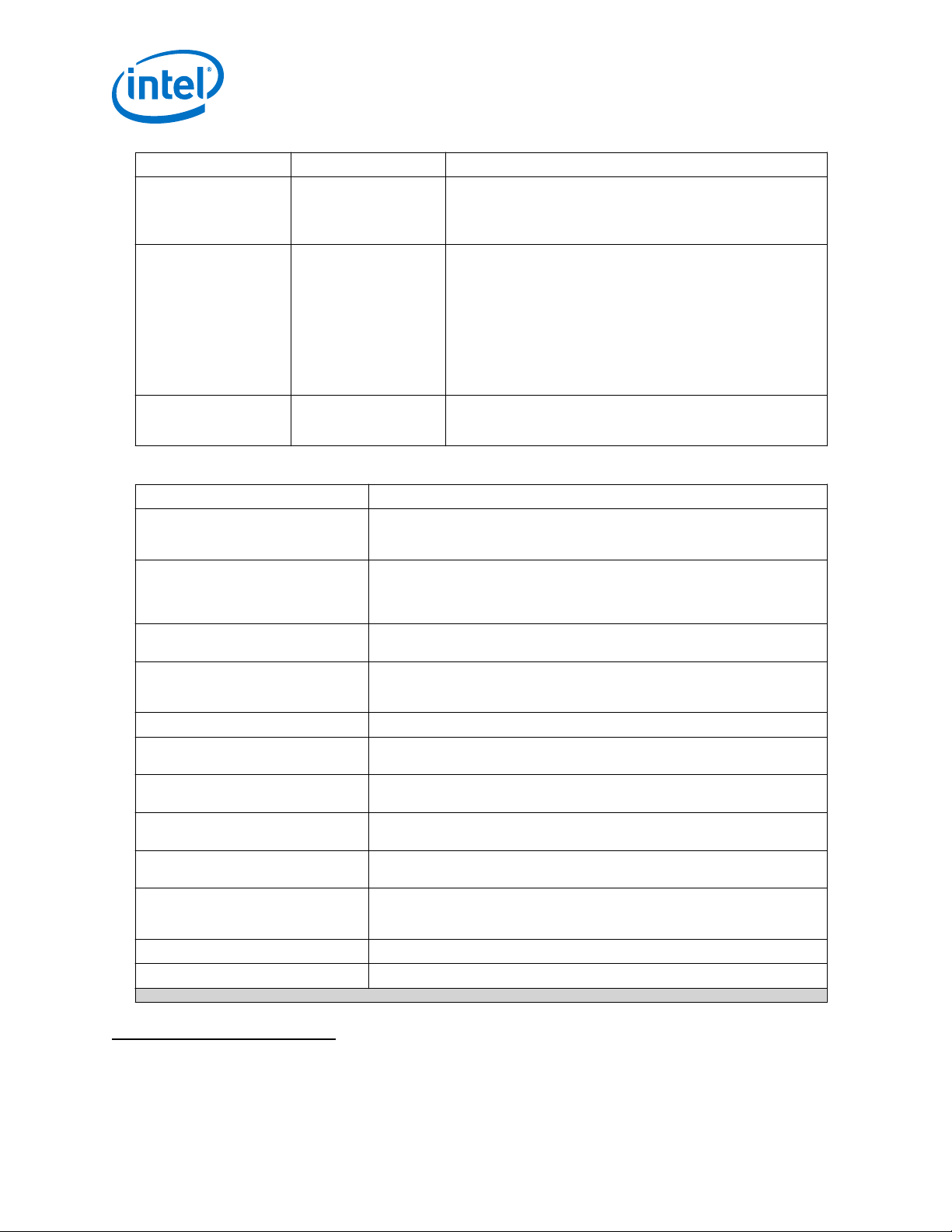

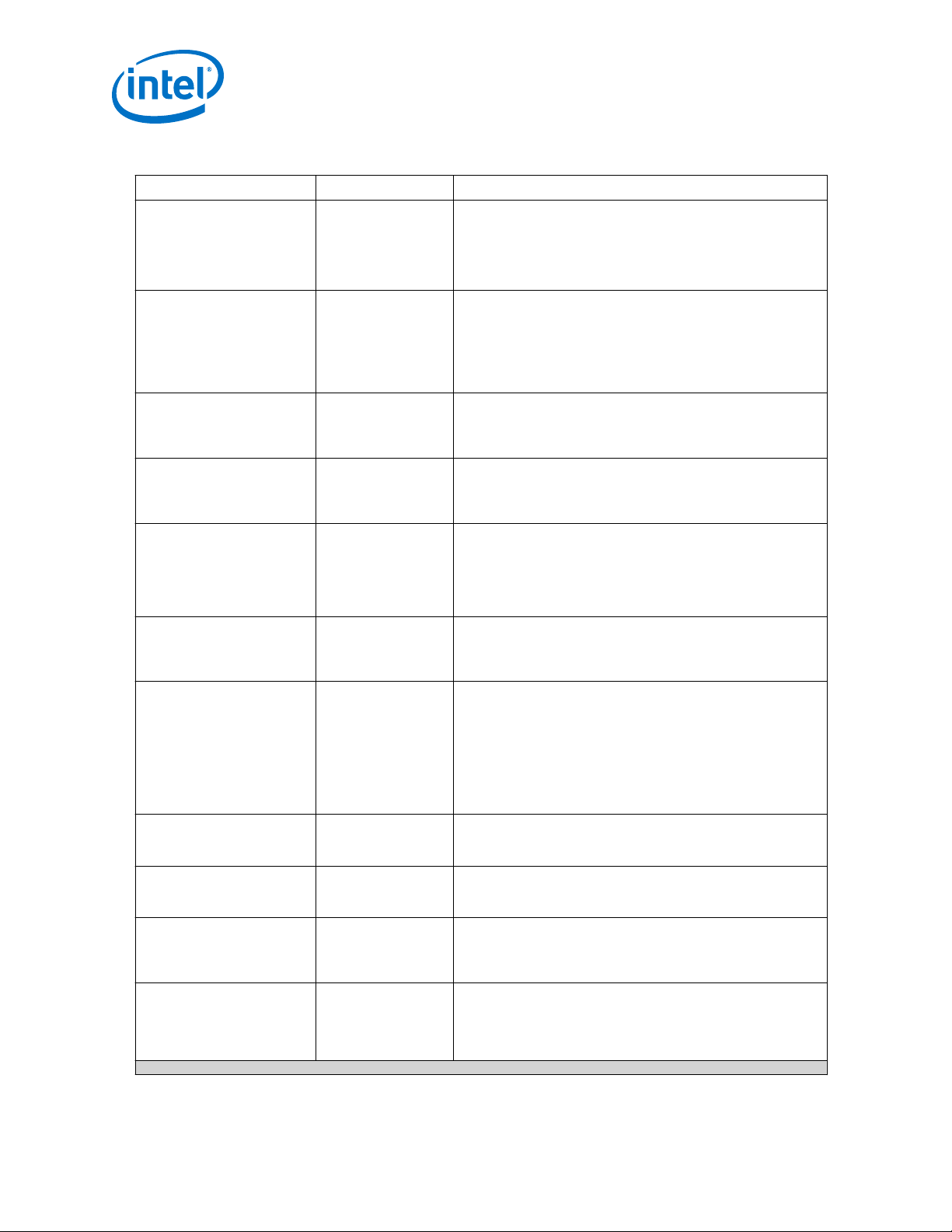

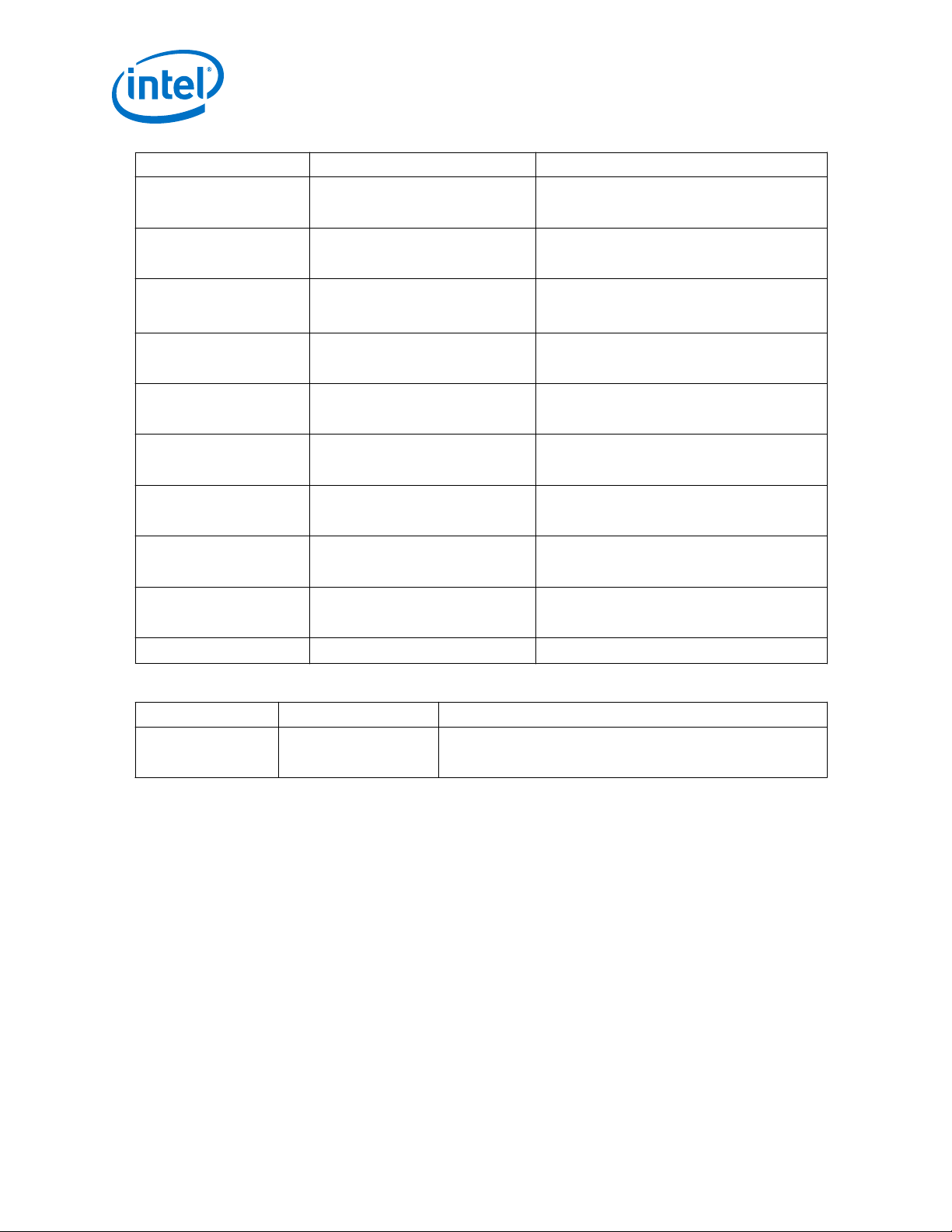

Table 1. Data Rates Supported by GX Transceiver Channel Type

Device Variant Standard Power Mode

Chip-to-Chip Backplane Chip-to-Chip

(3)

SX

(3)

GX

(4)

GT

(1)

To operate GX transceiver channels at designated data rates in standard and reduced power

1.0 Gbps to 17.4 Gbps 1.0 Gbps to 12.5 Gbps 1.0 Gbps to 11.3 Gbps

1.0 Gbps to 17.4 Gbps 1.0 Gbps to 12.5 Gbps 1.0 Gbps to 11.3 Gbps

1.0 Gbps to 17.4 Gbps 1.0 Gbps to 12.5 Gbps 1.0 Gbps to 11.3 Gbps

(1), (2)

Reduced Power Mode

modes, apply the corresponding core and periphery power supplies. Refer to the Arria 10

Device Datasheet for more details.

(2)

The minimum operational data rate is 1.0 Gbps for both the transmitter and receiver. For

transmitter data rates less than 1.0 Gbps, oversampling must be applied at the transmitter. For

receiver data rates less than 1.0 Gbps, oversampling must be applied at the receiver.

(3)

For SX and GX device variants, the maximum transceiver data rates are specified for the

fastest (–1) transceiver speed grade.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

(1), (2)

ISO

9001:2008

Registered

Page 9

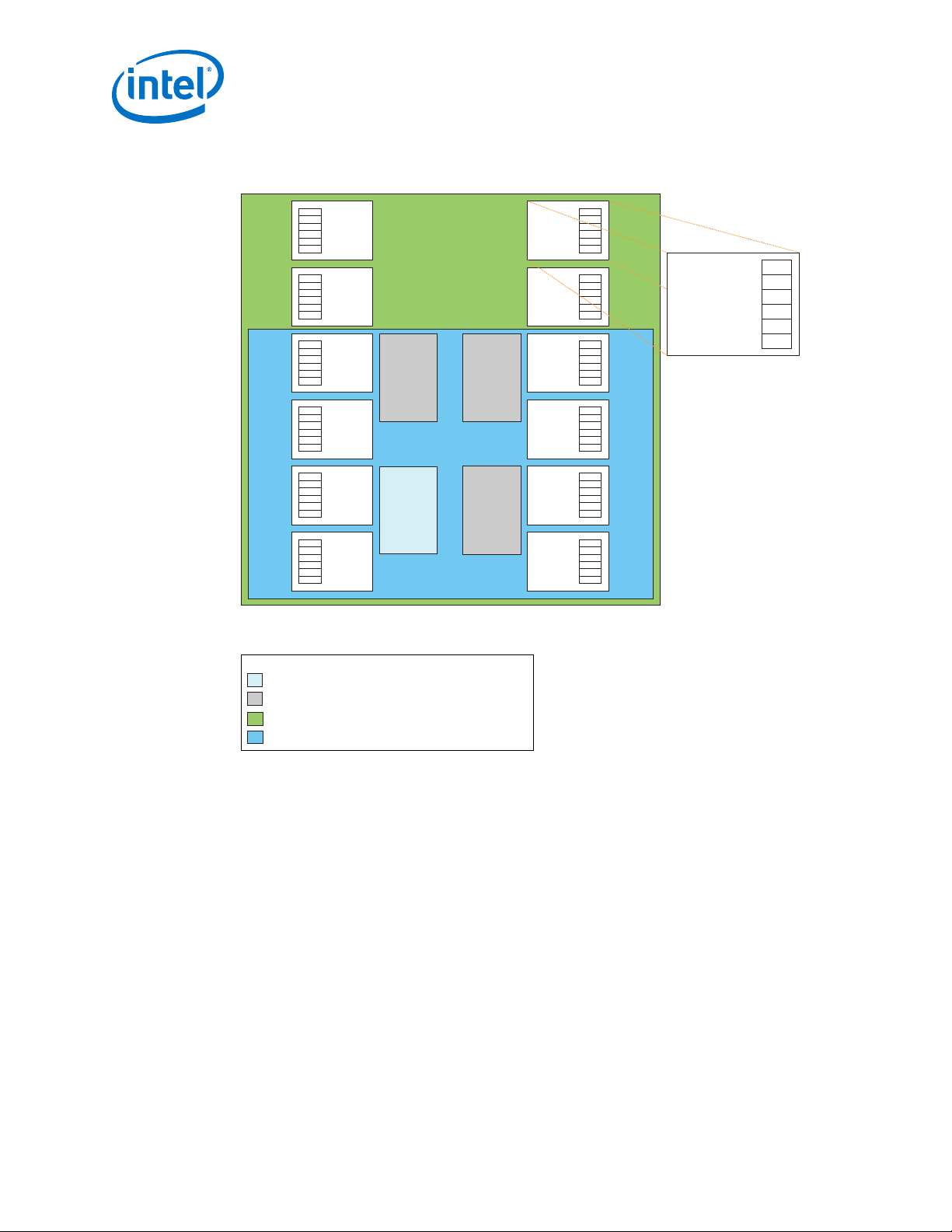

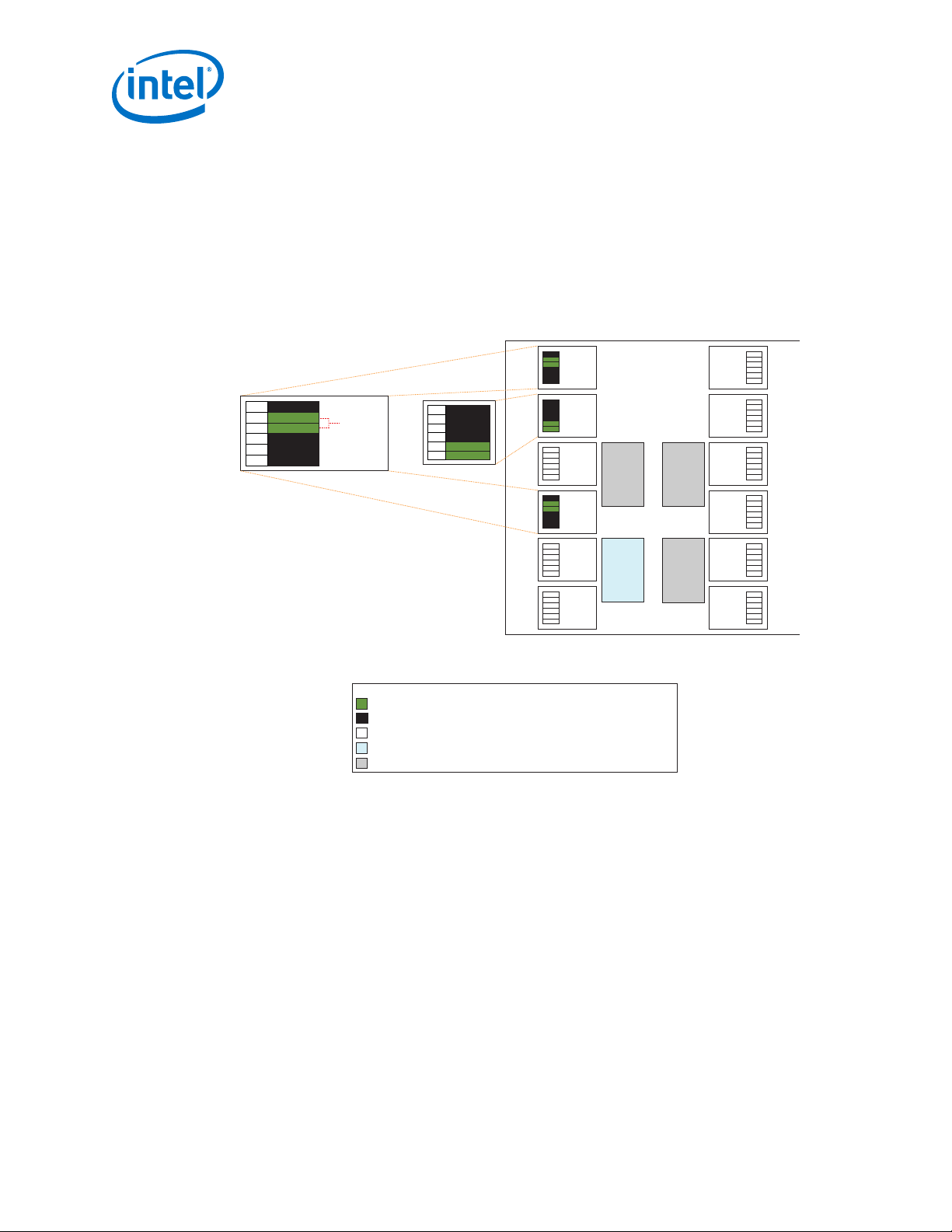

Core Logic Fabric

M20K Internal Memory Blocks

Transceiver Channels

Hard IP Per Transceiver: Standard PCS, PCIe Gen3 PCS, Enhanced PCS

PCI Express Gen3 Hard IP

PLLs

M20K Internal Memory Blocks

PCI Express Gen3 Hard IP

Variable Precision DSP Blocks

I/O PLLs

Hard Memory Controllers, General-Purpose I/O Cells, LVDS

M20K Internal Memory BlocksM20K Internal Memory Blocks

Variable Precision DSP Blocks

Core Logic Fabric

I/O PLLs

Hard Memory Controllers, General-Purpose I/O Cells, LVDS

M20K Internal Memory BlocksM20K Internal Memory Blocks

Variable Precision DSP Blocks

Transceiver Channels

PCI Express Gen3 Hard IP PCI Express Gen3 Hard IP

PLLs

Hard IP Per Transceiver: Standard PCS, PCIe Gen3 PCS, Enhanced PCS

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

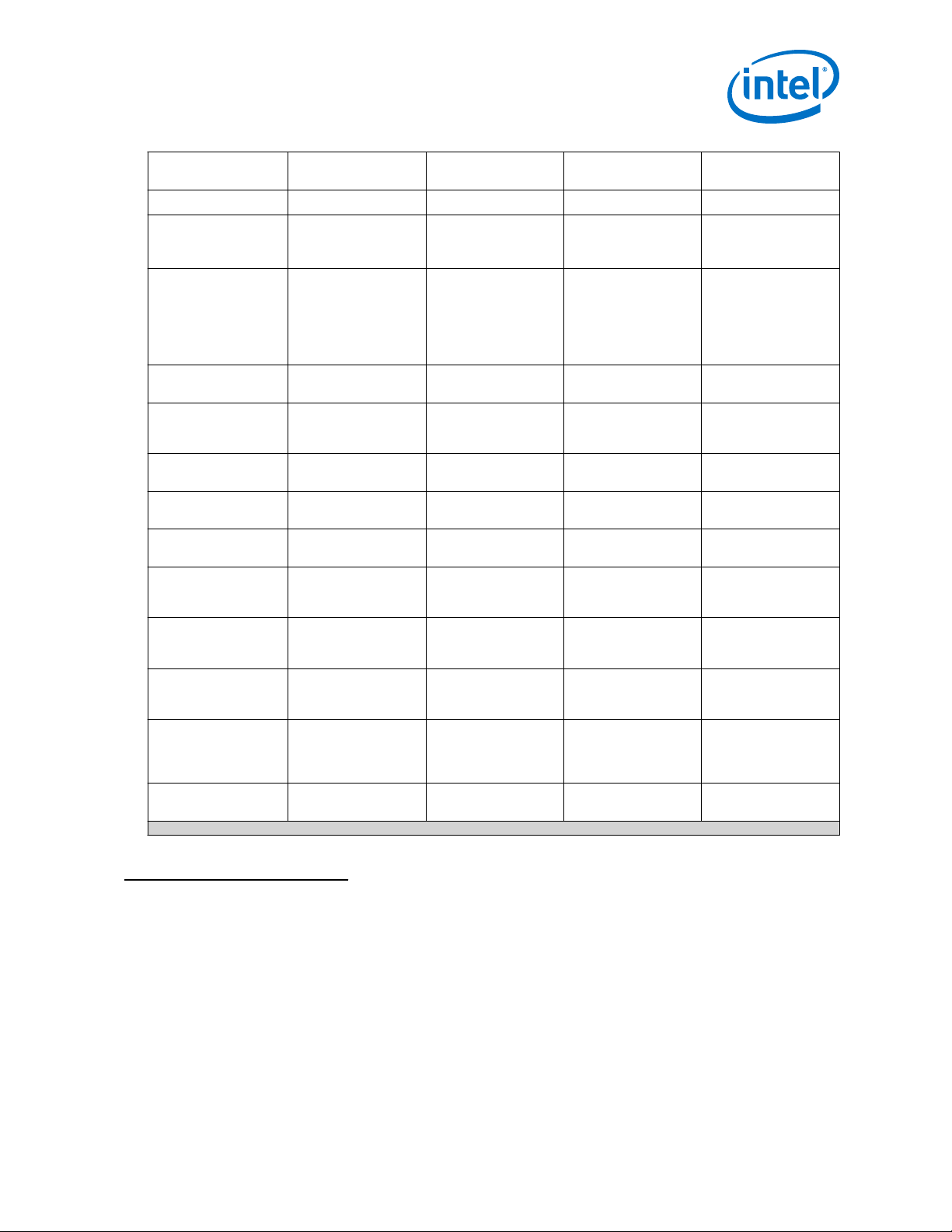

Table 2. Data Rates Supported by GT Transceiver Channel Type

Device Variant

GT 1.0 Gbps to 25.8 Gbps 1.0 Gbps to 12.5 Gbps

(4)

Data Rates

Chip-to-Chip Backplane

(5), (2)

Note: The device data rates depend on the device speed grade. Refer to IntelArria 10 Device

Datasheet for details on available speed grades and supported data rates.

Related Information

• IntelArria 10 Device Datasheet

• IntelArria 10 Device Overview

1.1. Device Transceiver Layout

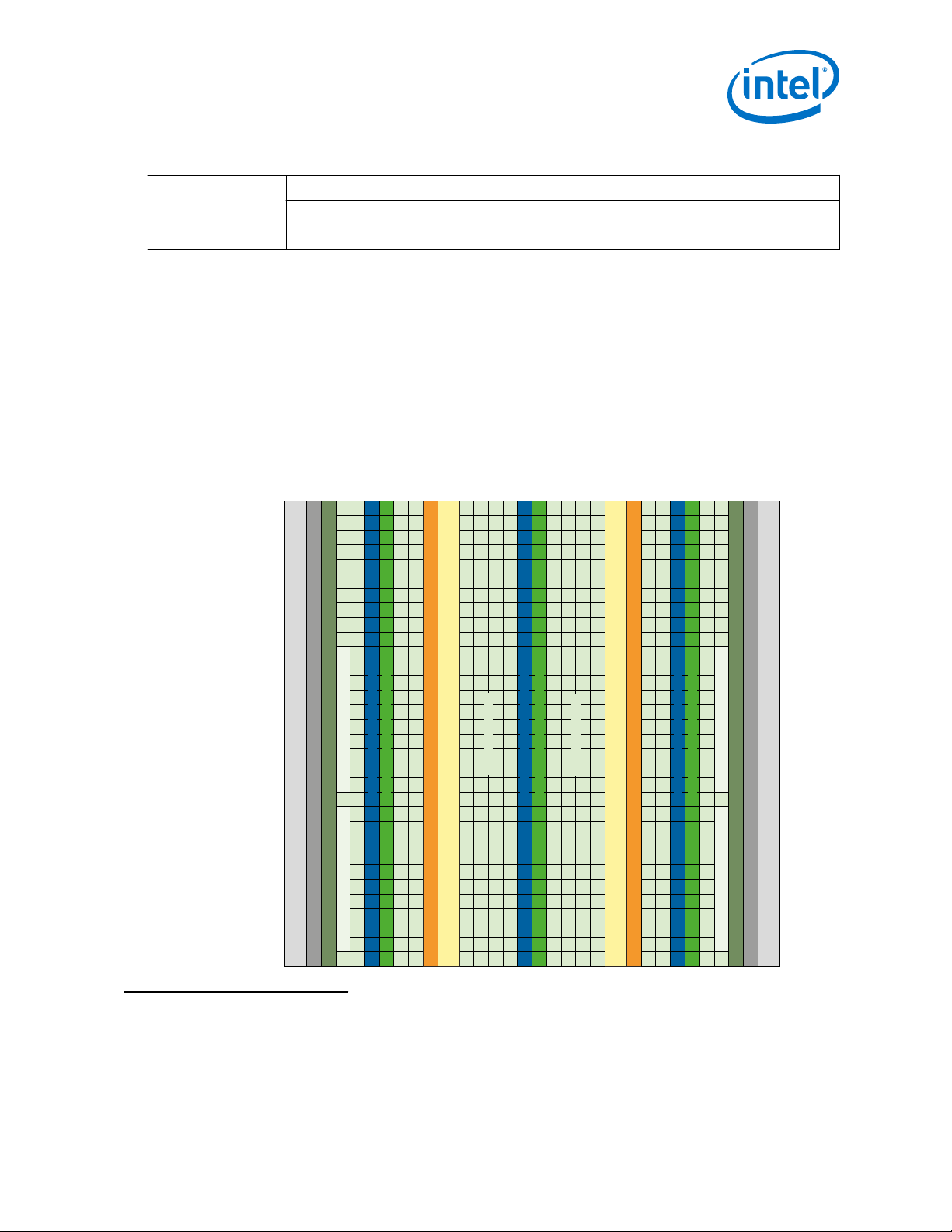

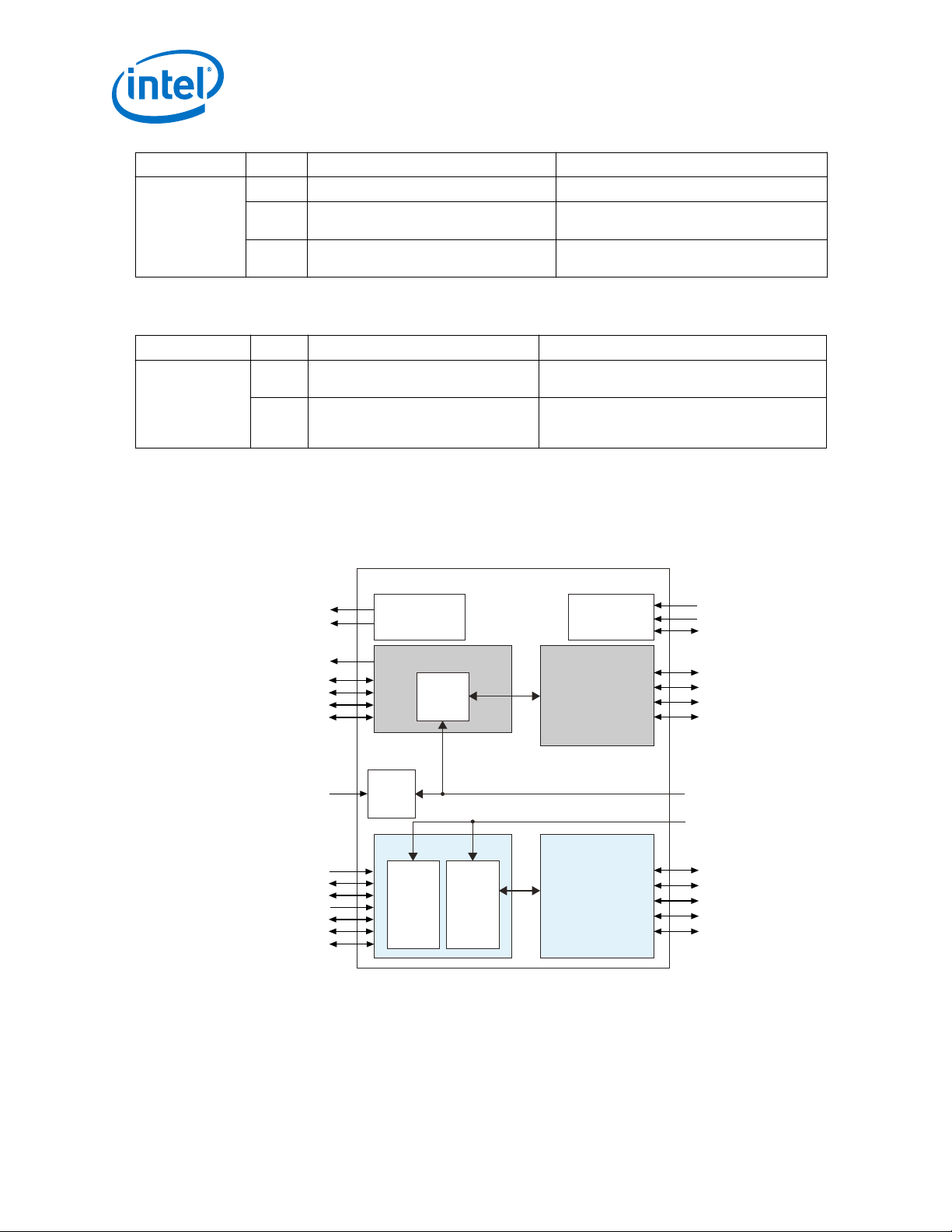

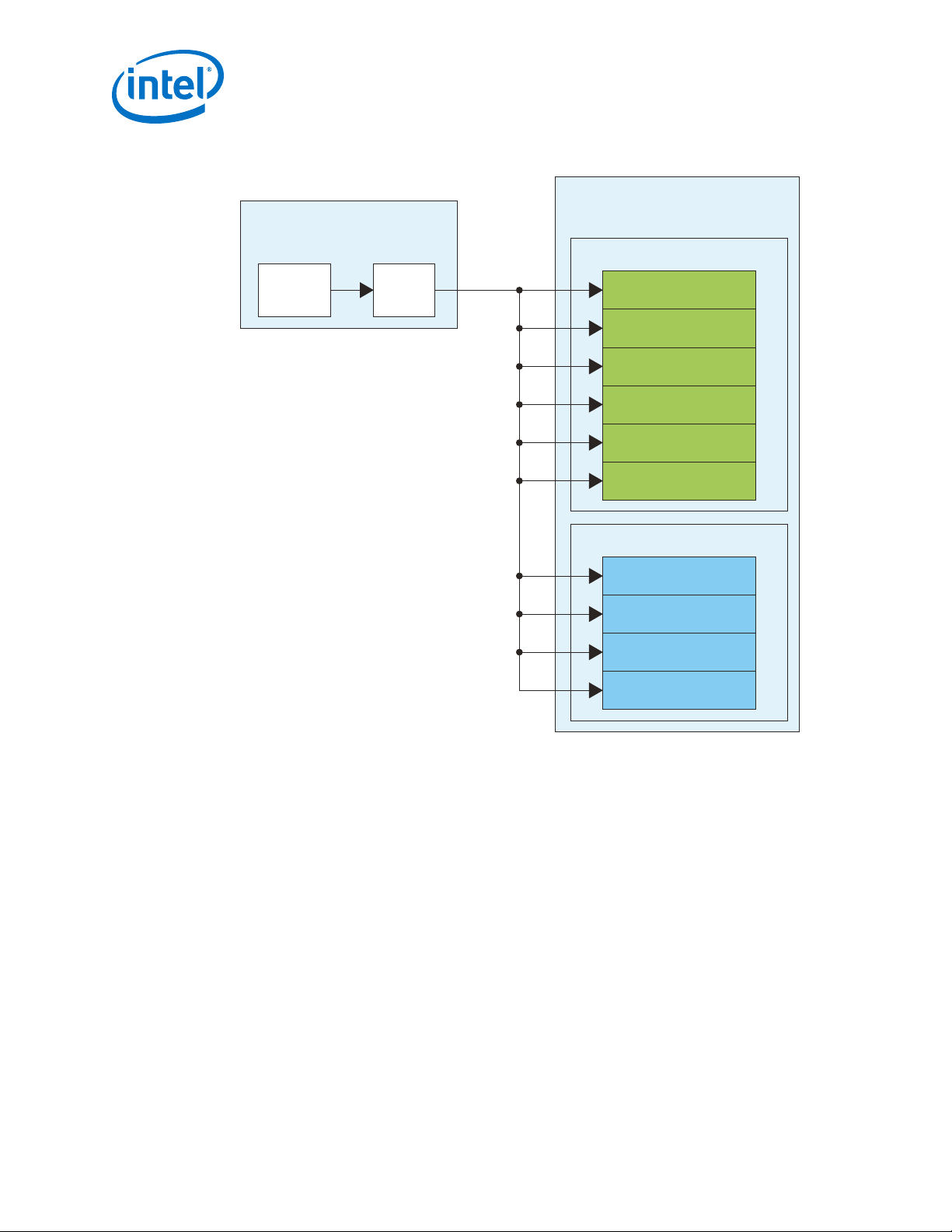

Figure 1. Arria 10 FPGA Architecture Block Diagram

The transceiver channels are placed on the left side periphery in most Arria 10 devices. For larger Arria 10

devices, additional transceiver channels are placed on the right side periphery.

(4)

For GT device variants, the maximum transceiver data rates are specified for (-1) transceiver

speed grade.

(5)

Because the GT transceiver channels are designed for peak performance, they do not have a

reduced power mode of operation.

Intel® Arria® 10 Transceiver PHY User Guide

9

Page 10

1.1.1. Arria 10 GX Device Transceiver Layout

The largest Arria 10 GX device includes 96 transceiver channels. A column array of

eight transceiver banks on the left and the right side periphery of the device is shown

in the following figure. Each transceiver bank has six transceiver channels. Some

devices have transceiver banks with only three channels. The transceiver banks with

only three channels are the uppermost transceiver banks. Arria 10 devices also include

PCI Express* Hard IP blocks.

The figures below illustrate different transceiver bank layouts for Arria 10 GX device

variants.

For more information about PCIe* Hard IP transceiver placements, refer to Related

Information at the end of this section.

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Intel® Arria® 10 Transceiver PHY User Guide

10

Page 11

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

GXBL1J

Transceiver

Bank

GXBL1I

Transceiver

Bank

GXBL1H

Transceiver

Bank

Transceiver

Bank

GXBL1F

Transceiver

Bank

Transceiver

Bank

GXBL1D

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

GXBL1G

Transceiver

Bank

Transceiver

Bank

GXBL1E

Transceiver

Bank

Transceiver

Bank

GXBL1C

GXBR4J

Transceiver

Bank

GXBR4I

GXBR4H

Transceiver

Bank

GXBR4G

Transceiver

Bank

GXBR4F

Transceiver

Bank

GXBR4E

Transceiver

Bank

GXBR4D

Transceiver

Bank

GXBR4C

PCIe

Gen1 - Gen3

Hard IP

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

Notes:

(1) Nomenclature of left column bottom transceiver banks always ends with “C”.

(2) Nomenclature of right column bottom transceiver banks may end with “C”, “D”, or “E”.

(1) (2)

Legend:

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

PCIe Gen1 - Gen3 Hard IP blocks without Configuration via Protocol (CvP) capabilities.

GX 115 UF45

GX 090 UF45

PCIe

Gen1 - Gen3

Hard IP

(with CvP)

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

Arria 10 GX device with 96 transceiver channels and four PCIe Hard IP blocks.

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 2. Arria 10 GX Devices with 96 Transceiver Channels and Four PCIe Hard IP

Blocks

Intel® Arria® 10 Transceiver PHY User Guide

11

Page 12

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

GXBL1H

GXBL1G

GXBL1F

GXBL1E

GXBL1D

GXBL1C

GXBR4H

GXBR4G

GXBR4F

GXBR4E

GXBR4D

GXBR4C

(1) (2)

Notes:

(1) Nomenclature of left column bottom transceiver banks always ends with “C”.

(2) Nomenclature of right column bottom transceiver banks may end with “C”, “D”, or “E”.

GX 115 SF45

GX 090 SF45

GX 115 NF45

GX 090 NF45

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

(with CvP)

PCIe

Gen1 - Gen3

Hard IP

Legend:

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

PCIe Gen1 - Gen3 Hard IP blocks without Configuration via Protocol (CvP) capabilities.

Arria 10 GX device with 48 transceiver channels and four PCIe Hard IP blocks.

Arria 10 GX device with 72 transceiver channels and four PCIe Hard IP blocks.

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 3. Arria 10 GX Devices with 72 and 48 Transceiver Channels and Four PCIe Hard

IP Blocks.

Intel® Arria® 10 Transceiver PHY User Guide

12

Page 13

Transceiver

Bank

Transceiver

Bank

GXBL1H

Transceiver

Bank

GXBL1G

Transceiver

Bank

GXBL1F

Transceiver

Bank

GXBL1E

Transceiver

Bank

GXBL1D

Transceiver

Bank

GXBL1C

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

GXBR4J

Transceiver

Bank

GXBR4I

Transceiver

Bank

GXBR4H

Transceiver

Bank

GXBR4G

Transceiver

Bank

GXBR4F

Transceiver

Bank

GXBR4E

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

GX 115 RF40

GX 090 RF40

CH2

CH1

CH0

Transceiver

Bank

(1)

(2)

Notes:

(1) Nomenclature of left column bottom transceiver banks always ends with “C”.

(2) Nomenclature of right column bottom transceiver banks may end with “C”, “D”, or “E”.

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

(with CvP)

PCIe

Gen1 - Gen3

Hard IP

Legend:

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

PCIe Gen1 - Gen3 Hard IP blocks without Configuration via Protocol (CvP) capabilities.

Arria 10 GX device with 66 transceiver channels and three PCIe Hard IP blocks.

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 4. Arria 10 GX Devices with 66 Transceiver Channels and Three PCIe Hard IP

Blocks

Intel® Arria® 10 Transceiver PHY User Guide

13

Page 14

Transceiver

Bank

Transceiver

Bank

GXBL1I

Transceiver

Bank

GXBL1H

Transceiver

Bank

GXBL1G

Transceiver

Bank

GXBL1F

Transceiver

Bank

GXBL1E

Transceiver

Bank

GXBL1D

Transceiver

Bank

GXBL1C

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

GX 115 NF40

GX 090 NF40

GX 066 NF40

GX 057 NF40

GX 066 KF35

GX 057 KF35

GX 048 KF35

GX 115 HF34

GX 090 HF34

GX 066 HF34

GX 057 HF34

GX 048 HF34

GX 032 HF35

GX 032 HF34

GX 027 HF35

GX 027 HF34

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

GXBL1J

GXBL1C

GXBL1D

GXBL1E

GXBL1F

GXBL1G

GXBL1H

GXBL1I

GXBL1J

Note:

(1) These devices have transceivers only on the left hand side of the device.

GX 066 KF40

GX 057 KF40

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

(with CvP)

Legend:

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

PCIe Gen1 - Gen3 Hard IP blocks without Configuration via Protocol (CvP) capabilities.

Arria 10 GX device with 48 transceiver channels and two PCIe Hard IP blocks.

Arria 10 GX device with 36 transceiver channels and two PCIe Hard IP blocks.

Arria 10 GX device with 24 transceiver channels and two PCIe Hard IP blocks.

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 5. Arria 10 GX Devices with 48, 36, and 24 Transceiver Channels and Two PCIe

Hard IP Blocks

Intel® Arria® 10 Transceiver PHY User Guide

14

Page 15

Transceiver

Bank

GXBL1D

Transceiver

Bank

GXBL1C

Transceiver

Bank

Transceiver

Bank

GX 048 EF29

GX 032 EF29

GX 027 EF29

GX 032 EF27

GX 027 EF27

GX 022 EF29

GX 022 EF27

GX 016 EF29

GX 016 EF27

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

Note:

(1) These devices have transceivers only on the left hand side of the device.

Legend:

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

Arria 10 GX device with 12 transceiver channels and one PCIe Hard IP block.

PCIe

Gen1 - Gen3

Hard IP

(with CvP)

Transceiver

Bank

GXBL1C Transceiver

Bank

PCIe Hard IP

GX 022 CU19

GX 016 CU19

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

GXBL1C

Note:

(2) These devices have transceivers only on the left hand side of the device.

Legend:

PCIe Gen1 - Gen3 Hard IP block with Configuration via Protocol (CvP) capabilities.

Arria 10 GX device with six transceiver channels and one PCIe Hard IP block.

(1)

(1) Only CH5 and CH4 support PCIe Hard IP block with CvP capabilities.

®

1. Arria

UG-01143 | 2018.06.15

10 Transceiver PHY Overview

Figure 6. Arria 10 GX Devices with 12 Transceiver Channels and One PCIe Hard IP

Block

Figure 7. Arria 10 GX Devices with 6 Transceiver Channels and One PCIe Hard IP Block

Related Information

• IntelArria 10 Avalon-ST Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-MM Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-ST Interface with SR-IOV PCIe Solutions User Guide

1.1.2. Arria 10 GT Device Transceiver Layout

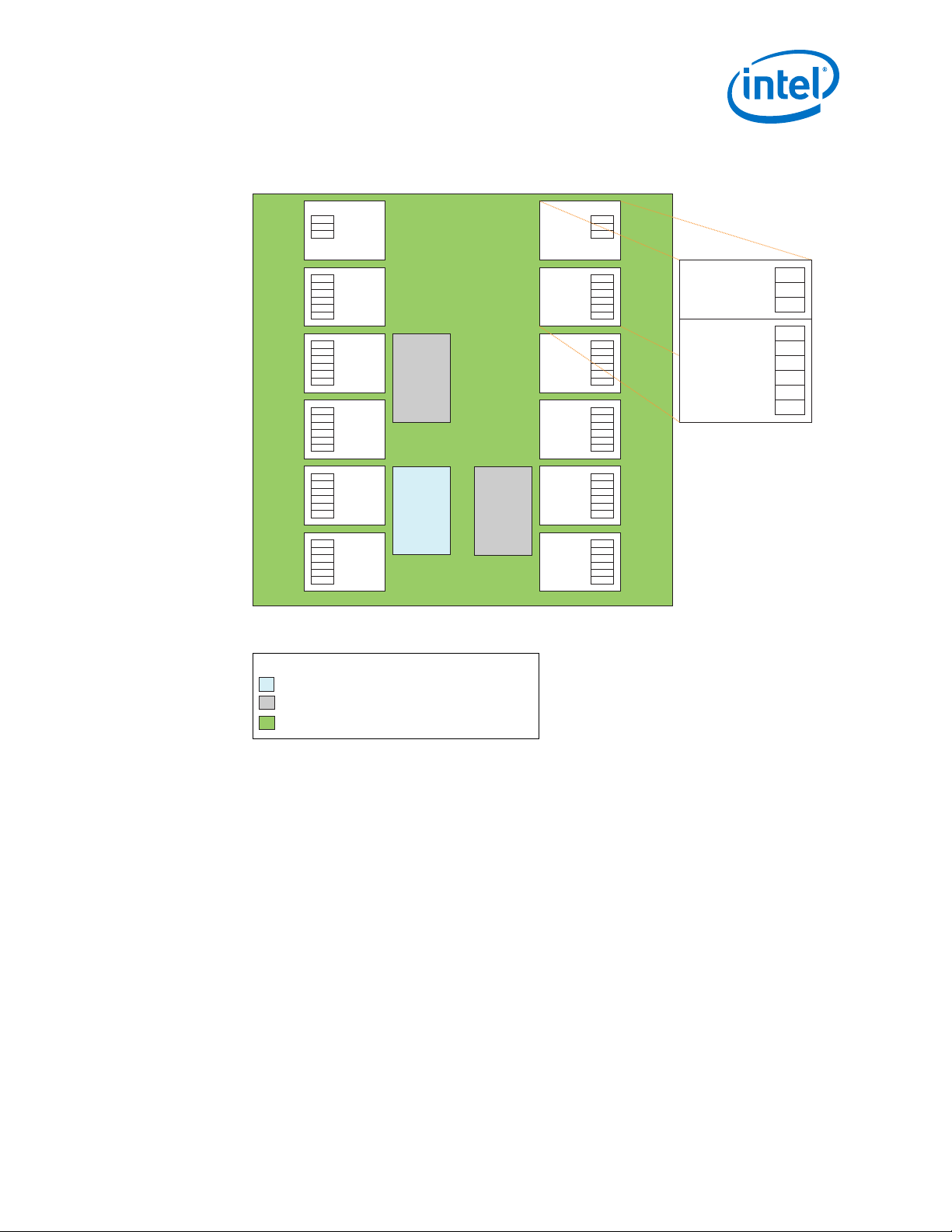

The Arria 10 GT device has 72 transceiver channels and four PCI Express Hard IP

blocks. A total of 6 GT transceiver channels that can support data rates up to 25.8

Gbps.

In the GT device, transceiver banks GXBL1E, GXBL1G, and GXBL1H each contain two

GT transceiver channels. Transceiver banks GXBL1E and GXBL1H channels 3 and 4 can

be used as GT or GX transceiver channel. Transceiver bank GXBL1G channels 0 and 1

can be used as GT or GX transceiver channels. When none of the GT capable

transceiver channels are used as GT transceiver channels, the entire transceiver

Intel® Arria® 10 Transceiver PHY User Guide

15

Page 16

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank (3)

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

GT 115 SF45

GT 090 SF45

GT Channels

Capable of Short

Reach 25.8 Gbps

GXBL1C

GXBL1D

GXBL1E

GXBL1F

GXBL1G

GXBL1H

GXBR4C

GXBR4D

GXBR4E

GXBR4F

GXBR4G

GXBR4H

Notes:

(1) Nomenclature of left column bottom transceiver banks always end with “C”.

(2) Nomenclature of right column bottom transceiver banks may end with “C”, “D”, or “E”.

(3) If a GT channel is used in transceiver bank GXBL1E, the PCIe Hard IP adjacent to GXBL1F and GXBL1E cannot be used.

(1) (2)

GX or Restricted

GT or GX

GT or GX

GX or Restricted

CH5

CH4

CH3

CH2

CH1

CH0

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

(with CvP)

Hard IP

Legend:

GX transceiver channels (channel 2 and 5) with usage restrictions.

GT transceiver channels (channel 0, 1, 3, and 4).

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

PCIe Gen1 - Gen3 Hard IP blocks without Configuration via Protocol (CvP) capabilities.

GX transceiver channels without usage restrictions.

GX or Restricted

GX or Restricted

GT or GX

GT or GX

CH5

CH4

CH3

CH2

CH1

CH0

GX or Restricted

GX or Restricted

GX or Restricted

GX or Restricted

®

1. Arria

10 Transceiver PHY Overview

UG-01143 | 2018.06.15

channels in the bank can be reconfigured as GX transceiver channels. However, when

any of the GT capable transceiver channels in transceiver banks GXBL1E, GXBL1G,

and GXBL1H is enabled as a GT transceiver channel, the remaining channels in the

transceiver bank cannot be used with the exception of the other GT capable channel in

the transceiver bank.

If you're using GT transceivers in bank GXBL1E, then the adjacent PCIe Hard IP block

cannot be used.

Figure 8. Arria 10 GT Device with 72 Transceiver Channels and Four PCIe Hard IP

Blocks

The GT device has 72 transceiver channels, which include 6 GT transceiver channels

supporting data rates greater than 17.4 Gbps. If all six GT transceiver channels are

used in GT mode, there are 54 GX transceiver channels that can drive chip to chip

data rates up to 17.4 Gbps and backplanes at data rates up to 12.5 Gbps and 12 GX

In the GT device, the GX transceiver channels on the entire right side can be used in

standard or reduced power mode. In GT devices where none of the GT channels are

used to operate in GT data rates above 17.4 Gbps, the transceiver channels on either

channels that are unusable.

the entire right side or entire left side can be used as GX channels in standard or

reduced power mode.

Related Information

• IntelArria 10 Avalon-ST Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-MM Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide

Intel® Arria® 10 Transceiver PHY User Guide

16

Page 17

®

1. Arria

UG-01143 | 2018.06.15

10 Transceiver PHY Overview

• IntelArria 10 Avalon-ST Interface with SR-IOV PCIe Solutions User Guide

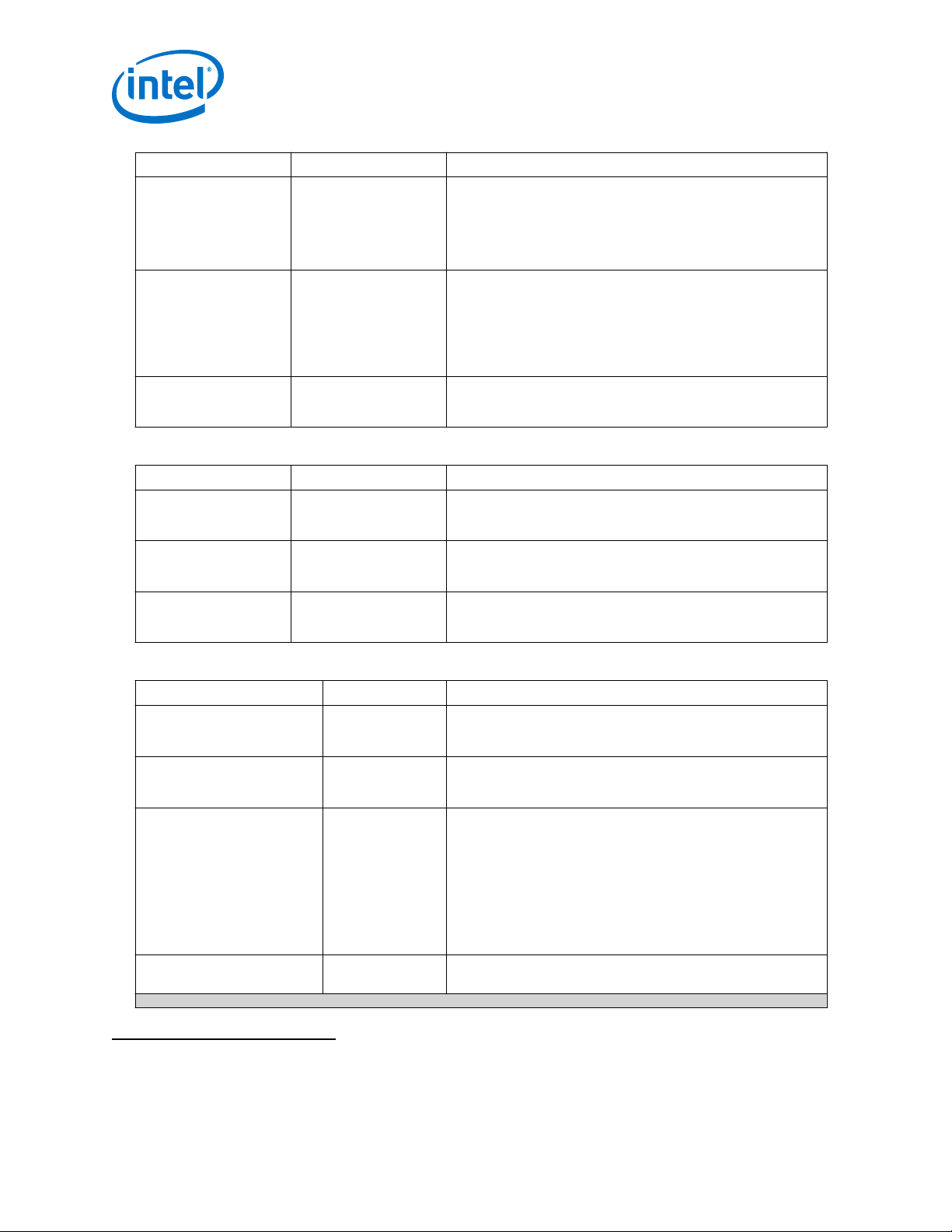

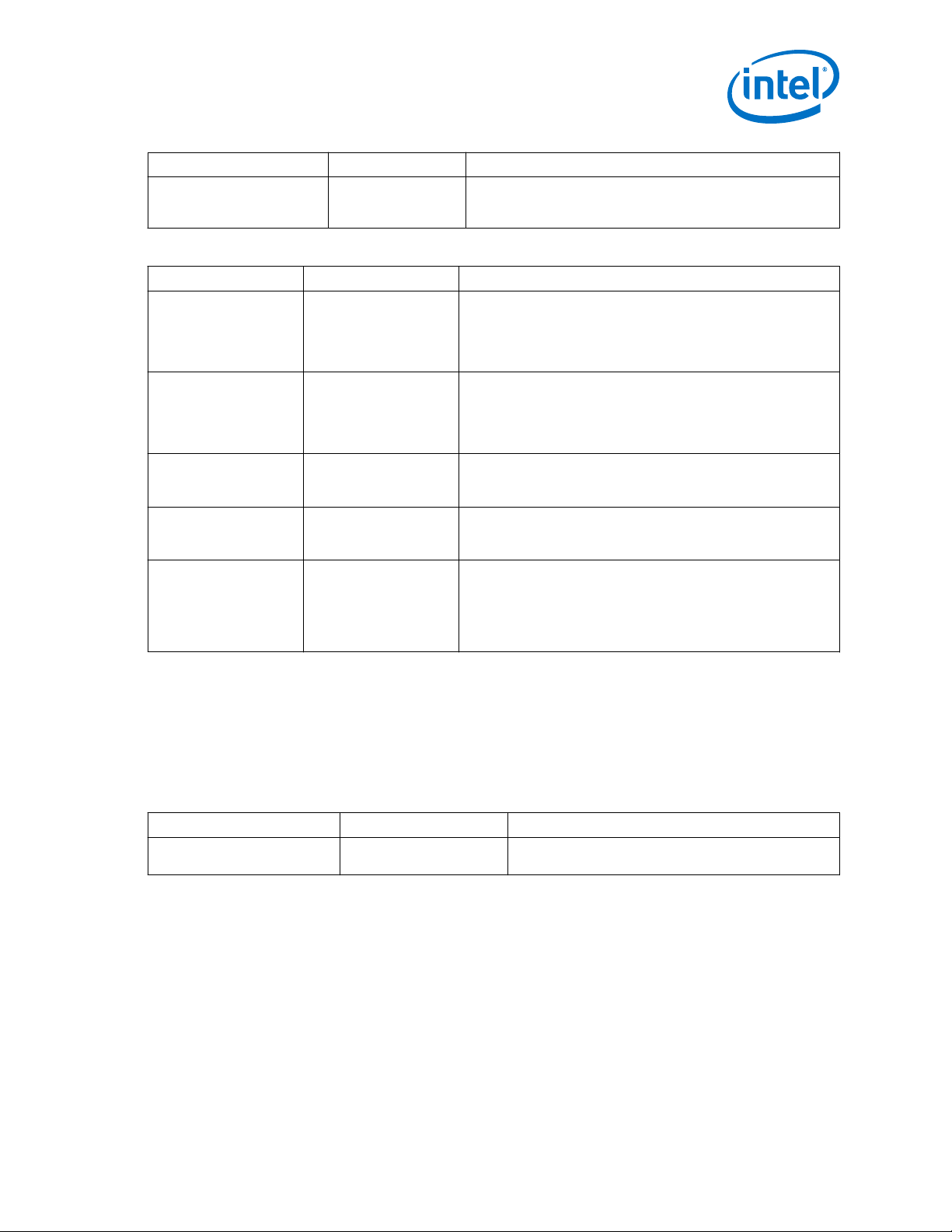

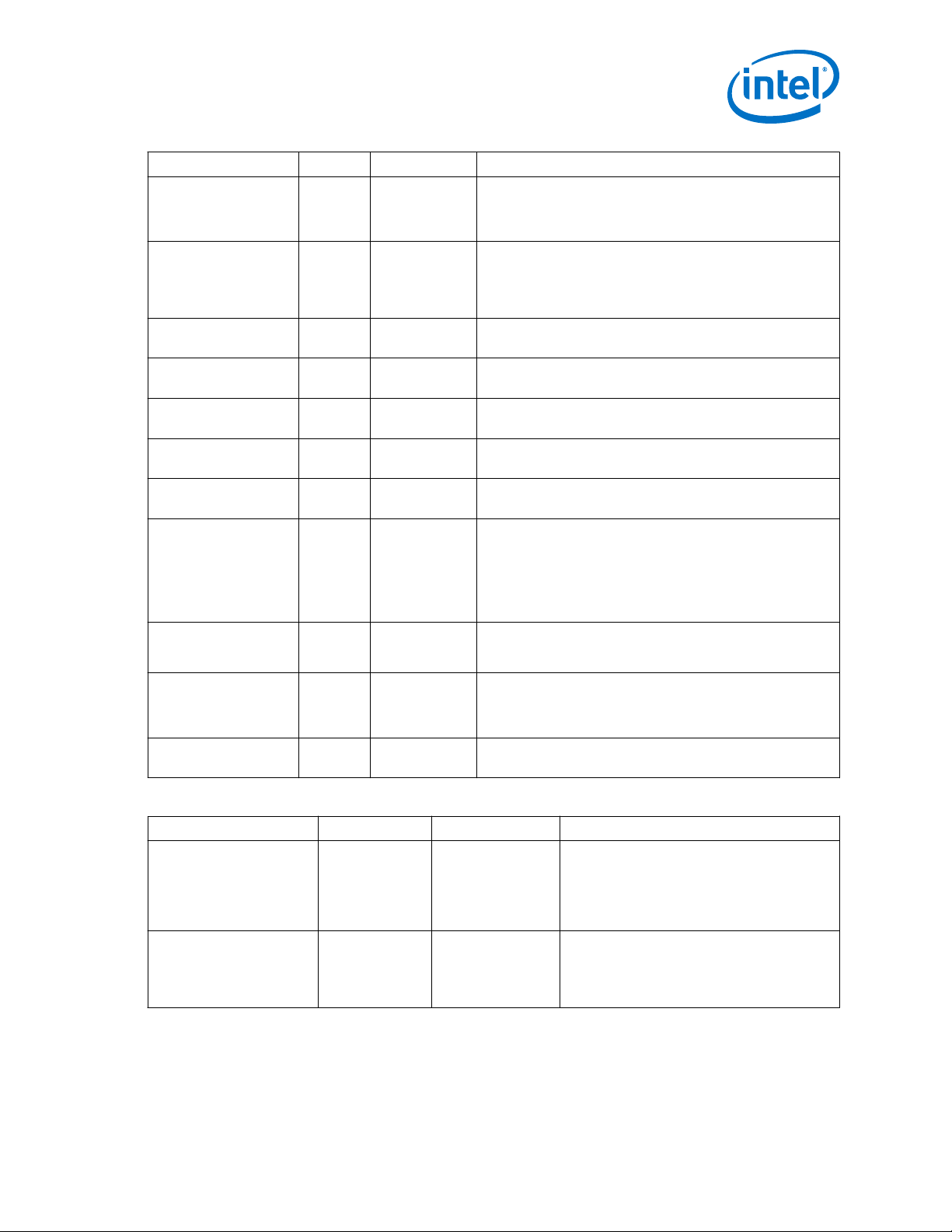

1.1.3. Arria 10 GX and GT Device Package Details

The following tables list package sizes, available transceiver channels, and PCI Express

Hard IP blocks for Arria 10 GX and GT devices.

Table 3. Package Details for GX Devices with Transceivers and Hard IP Blocks Located

on the Left Side Periphery of the Device

• Package U19: 19mm x 19mm package; 484 pins.

• Package F27: 27mm x 27mm package; 672 pins.

• Package F29: 29mm x 29mm package; 780 pins.

• Packages F34 and F35: 35 mm x 35 mm package size; 1152 pins.

• Package F40: 40 mm x 40 mm package size; 1517 pins. K = 36 transceiver channels, N = 48 transceiver

channels.

Device U19 F27 F29 F34 F35 K F40 N F40

Transceiver Count, PCIe Hard IP Block Count

GX 016 6, 1 12, 1 12, 1

GX 022 6, 1 12, 1 12, 1

GX 027 12, 1 12, 1 24, 2 24, 2

GX 032 12, 1 12, 1 24, 2 24, 2

GX 048 12, 1 24, 2 36, 2

GX 057 24, 2 36, 2 36, 2 48, 2

GX 066 24, 2 36, 2 36, 2 48, 2

GX 090 24, 2 48, 2

GX 115 24, 2 48, 2

Table 4. Package Details for GX and GT Devices with Transceivers and Hard IP Blocks

Located on the Left and Right Side Periphery of the Device

• Package F40: 40 mm x 40 mm package size; 1517 pins. R = 66 transceiver channels.

• Package F45: 45mm x 45mm package size; 1932 pins. N = 48 transceiver channels, S = 72 transceiver

channels, U = 96 transceiver channels.

• If you're using GT transceivers in bank GXBL1E, the nth adjacent PCIe Hard IP block cannot be used.

Device

GX 090 66, 3 48, 4 72, 4 96, 4

GX 115 66, 3 48, 4 72, 4 96, 4

GT 090 72, 4

GT 115 72, 4

R F40 N F45 S F45 U F45

Transceiver Count, PCIe Hard IP Block Count

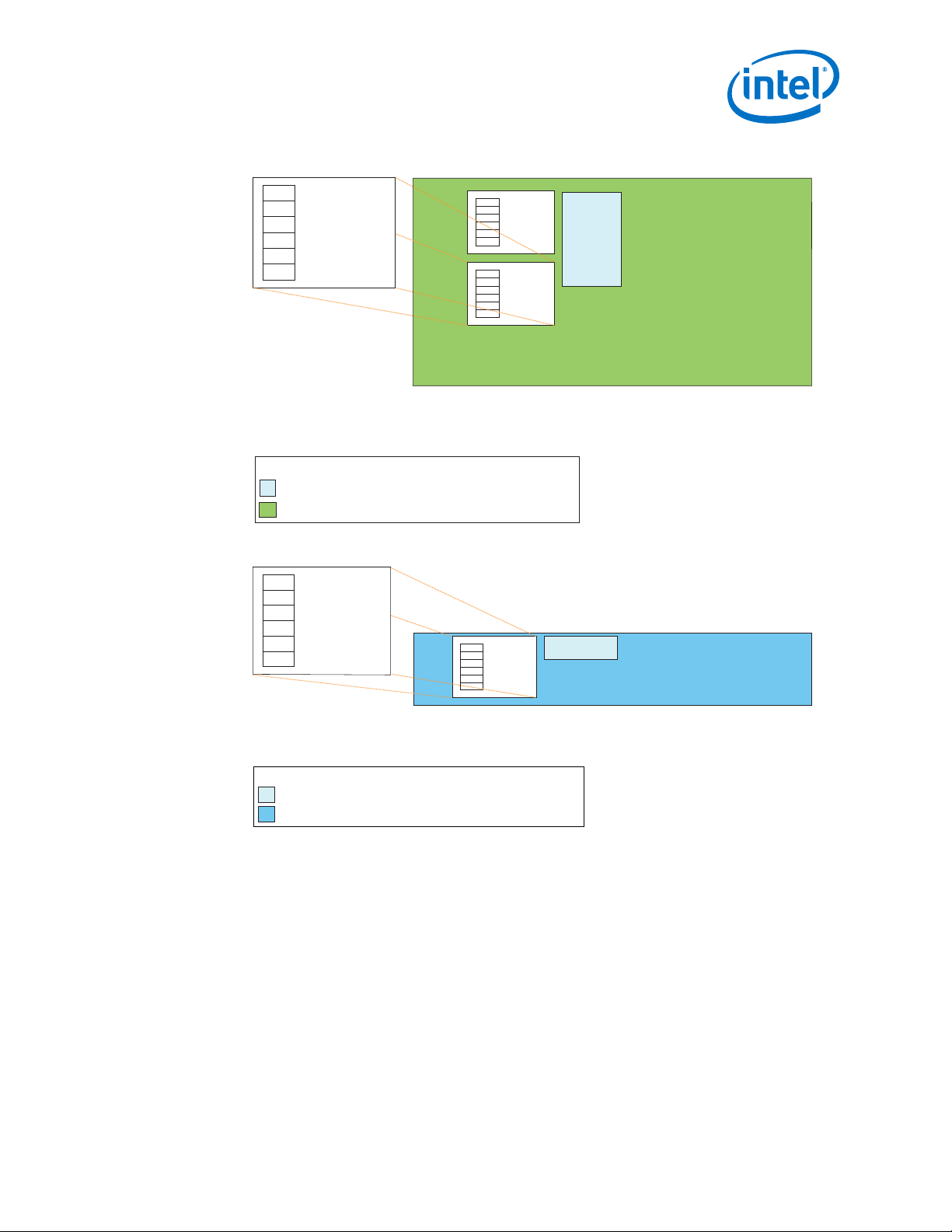

1.1.4. Arria 10 SX Device Transceiver Layout

The largest SX device includes 48 transceiver channels. All SX devices include GX

transceiver channel type. The transceiver banks in SX devices are located on the left

side periphery of the device.

Intel® Arria® 10 Transceiver PHY User Guide

17

Page 18

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

SX 066 NF40

SX 057 NF40

SX 066 KF35

SX 057 KF35

SX 048 KF35

SX 066 HF34

SX 057 HF34

SX 048 HF34

SX 032 HF35

SX 032 HF34

SX 027 HF35

SX 027 HF34

GXBL1C

GXBL1D

GXBL1E

GXBL1F

GXBL1G

GXBL1H

GXBL1I

GXBL1J

Note:

(1) These devices have transceivers only on the left hand side of the device.

Legend:

PCIe Gen1- Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

PCIe Gen1 - Gen3 Hard IP blocks without Configuration via Protocol (CvP) capabilities.

PCIe

Gen1 - Gen3

Hard IP

PCIe

Gen1 - Gen3

(with CvP)

Hard IP

Arria 10 SX device with 24 transceiver channels and two PCIe Hard IP blocks.

Arria 10 SX device with 36 transceiver channels and two PCIe Hard IP blocks.

Arria 10 SX device with 48 transceiver channels and two PCIe Hard IP blocks.

SX 066 KF40

SX 057 KF40

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

For more information about PCIe Hard IP transceiver placements, refer to Related

Information at the end of this section.

Figure 9. Arria 10 SX Device with 48, 36, and 24 Transceiver Channels and Two Hard IP

Blocks

Intel® Arria® 10 Transceiver PHY User Guide

18

Page 19

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

Transceiver

Bank

PCIe

Gen1 - Gen3

Hard IP

(with CvP)

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

SX 022 EF29

SX 022 EF27

SX 016 EF29

SX 016 EF27

SX 048 EF29

SX 032 EF29

SX 032 EF27

SX 027 EF29

SX 027 EF27

GXBL1D

GXBL1C

GXBL1D

GXBL1C

Note:

(1) These devices have transceivers only on the left hand side of the device.

Legend:

PCIe Gen1 - Gen3 Hard IP blocks with Configuration via Protocol (CvP) capabilities.

Arria 10 SX device with 12 transceiver channels and one Hard IP block.

Transceiver

Bank

GXBL1C Transceiver

Bank

PCIe Hard IP

SX 022 CU19

SX 016 CU19

CH5

CH4

CH3

CH2

CH1

CH0

Transceiver

Bank

Legend:

PCIe Gen1 - Gen3 Hard IP block with Configuration via Protocol (CvP) capabilities.

Arria 10 SX device with six transceiver channels and one PCIe Hard IP block.

Note:

(2) These devices have transceivers only on the left hand side of the device.

(1) Only CH5 and CH4 support PCIe Hard IP block with Configuration via Protocol (CvP) capabilities.

(1)

®

1. Arria

UG-01143 | 2018.06.15

10 Transceiver PHY Overview

Figure 10. Arria 10 SX Device with 12 Transceiver Channels and One Hard IP Block

Figure 11. Arria 10 SX Device with Six Transceiver Channels and One Hard IP Block

Related Information

• IntelArria 10 Avalon-ST Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-MM Interface for PCIe Solutions User Guide

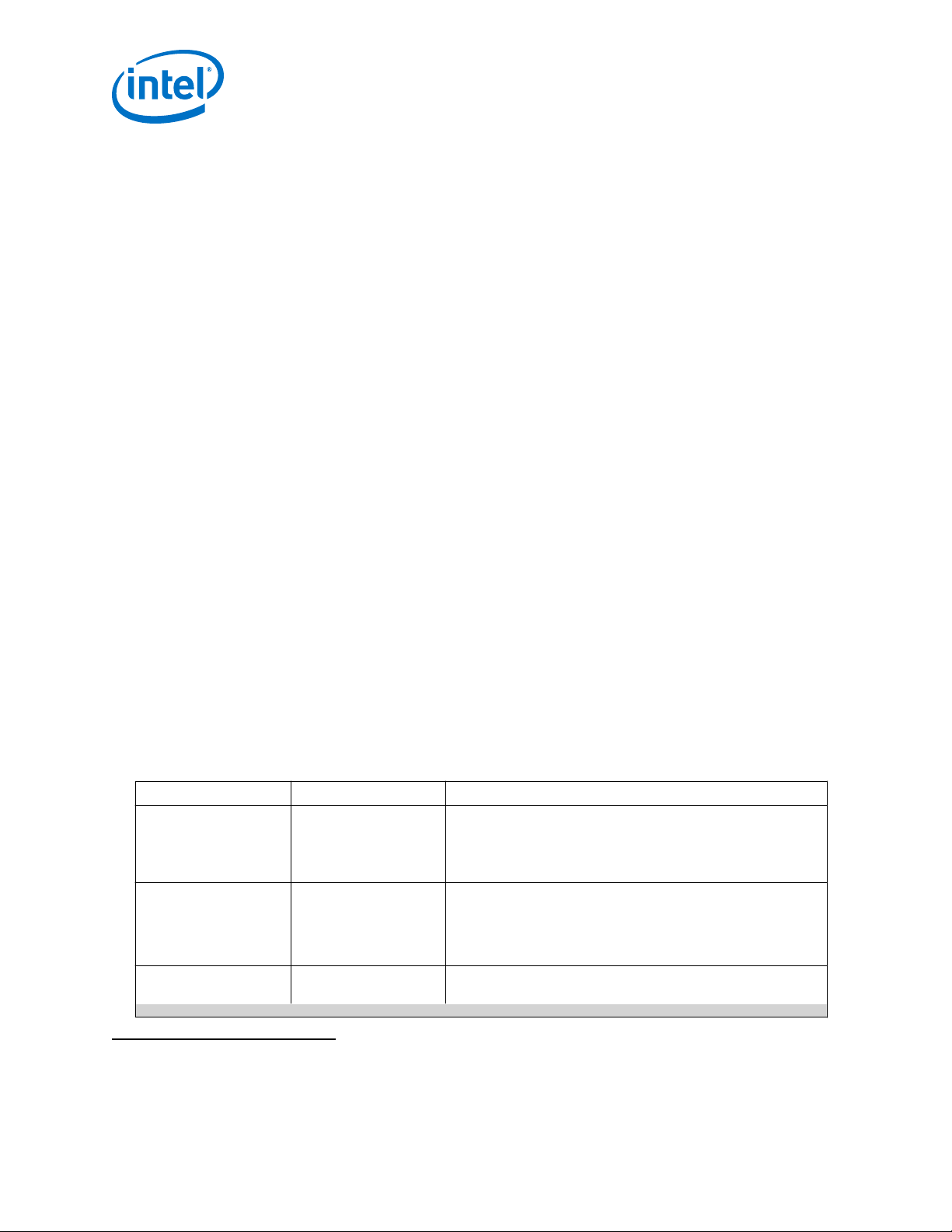

1.1.5. Arria 10 SX Device Package Details

• IntelArria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide

• IntelArria 10 Avalon-ST Interface with SR-IOV PCIe Solutions User Guide

The following tables list package sizes, available transceiver channels, and PCI Express

Hard IP blocks for Arria 10 SX devices.

Intel® Arria® 10 Transceiver PHY User Guide

19

Page 20

®

1. Arria

10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Table 5. Package Details for SX Devices with Transceivers and Hard IP Blocks Located

on the Left Side Periphery of the Device

• Package U19: 19mm x 19mm package; 484 pins.

• Package F27: 27mm x 27mm package; 672 pins.

• Package F29: 29mm x 29mm package; 780 pins.

• Packages F34 and F35: 35 mm x 35 mm package size; 1152 pins.

• Package F40: 40 mm x 40 mm package size; 1517 pins. K = 36 transceiver channels, N = 48 transceiver

channels.

Device U19 F27 F29 F34 F35 K F40 N F40

Transceiver Count, PCIe Hard IP Block Count

SX 016 6, 1 12, 1 12, 1

SX 022 6, 1 12, 1 12, 1

SX 027 12, 1 12, 1 24, 2 24, 2

SX 032 12, 1 12, 1 24, 2 24, 2

SX 048 12, 1 24, 2 36, 2

SX 057 24, 2 36, 2 36, 2 48, 2

SX 066 24, 2 36, 2 36, 2 48, 2

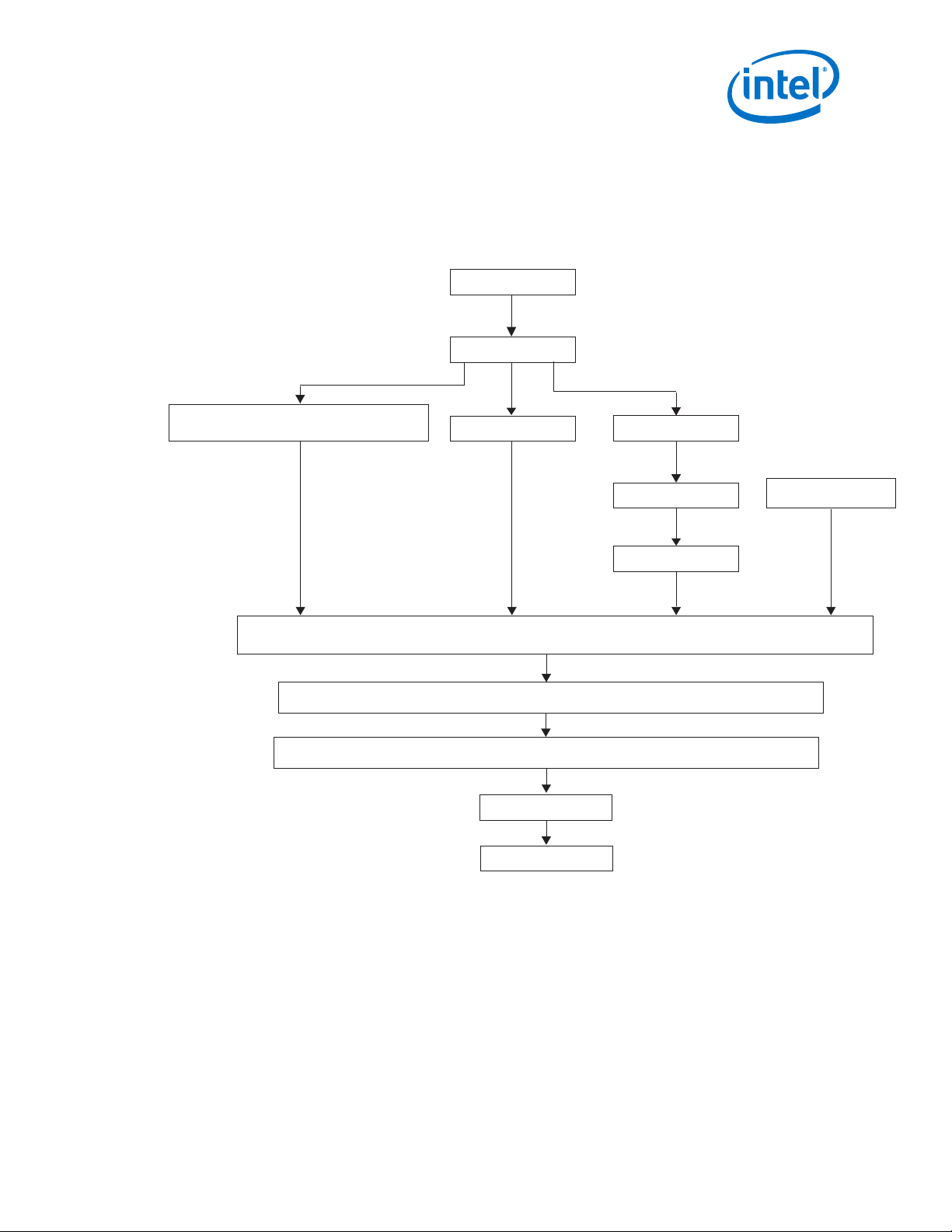

1.2. Transceiver PHY Architecture Overview

A link is defined as a single entity communication port. A link can have one or more

transceiver channels. A transceiver channel is synonymous with a transceiver lane.

For example, a 10GBASE-R link has one transceiver channel or lane with a data rate of

10.3125 Gbps. A 40GBASE-R link has four transceiver channels. Each transceiver

channel operates at a lane data rate of 10.3125 Gbps. Four transceiver channels give

a total collective link bandwidth of 41.25 Gbps (40 Gbps before and after 64B/66B

Physical Coding Sublayer (PCS) encoding and decoding).

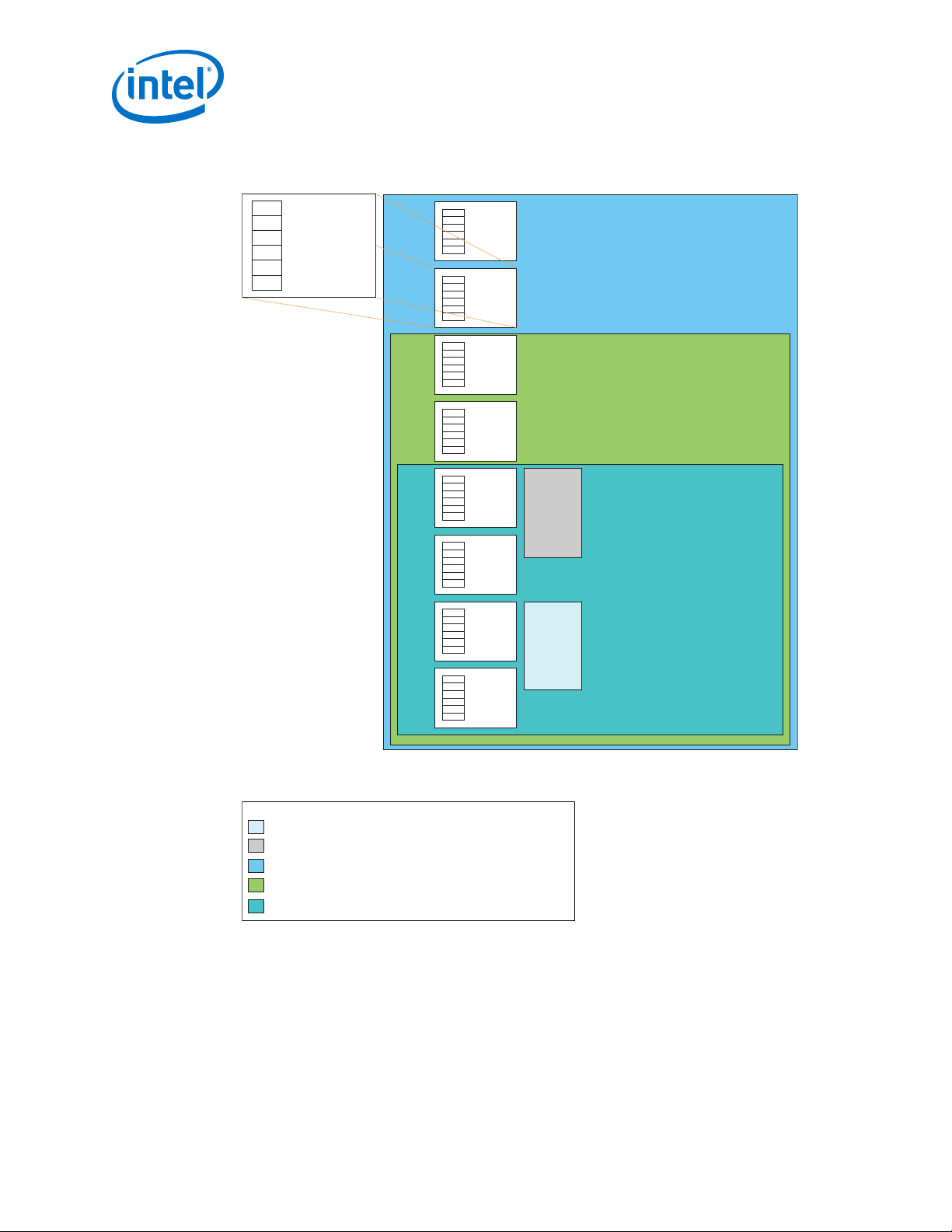

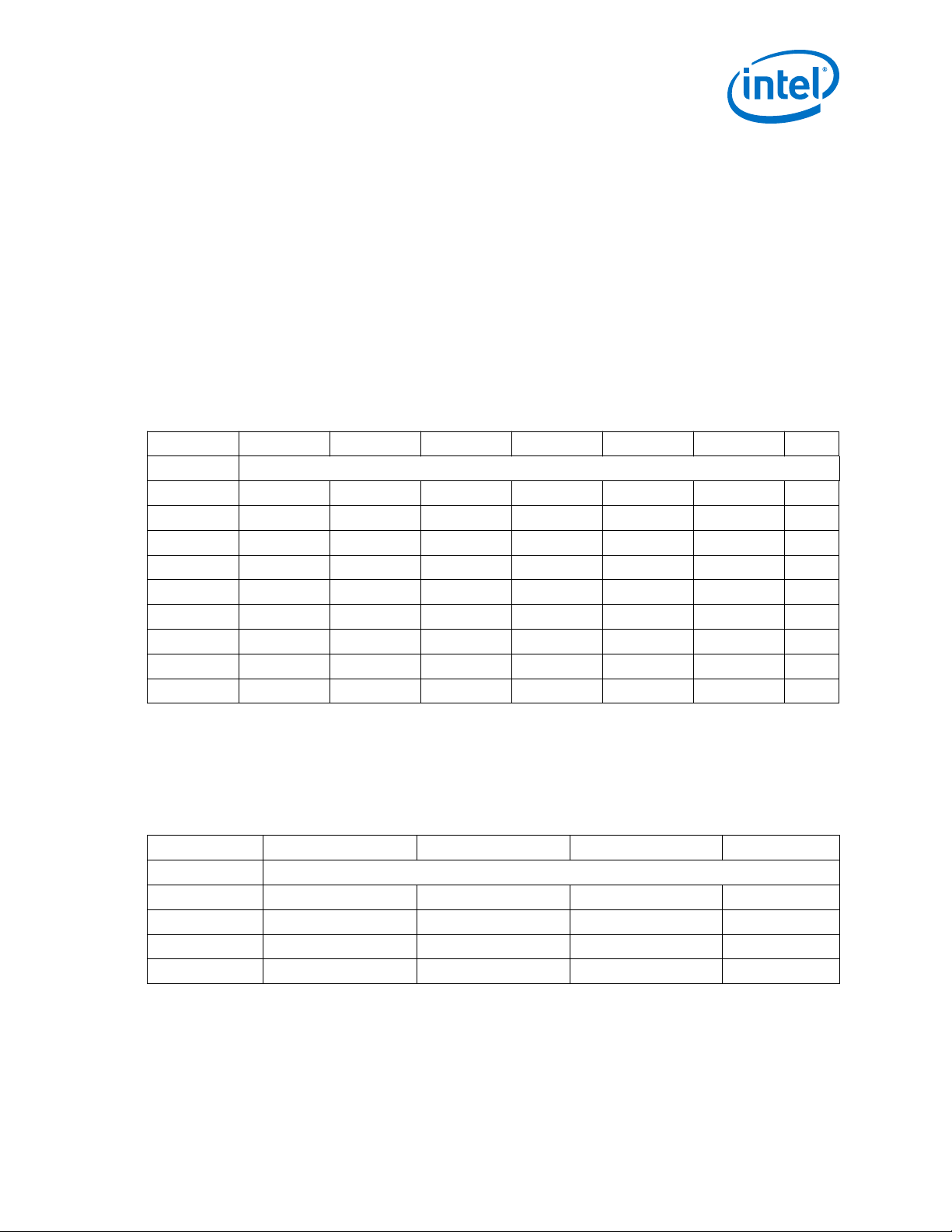

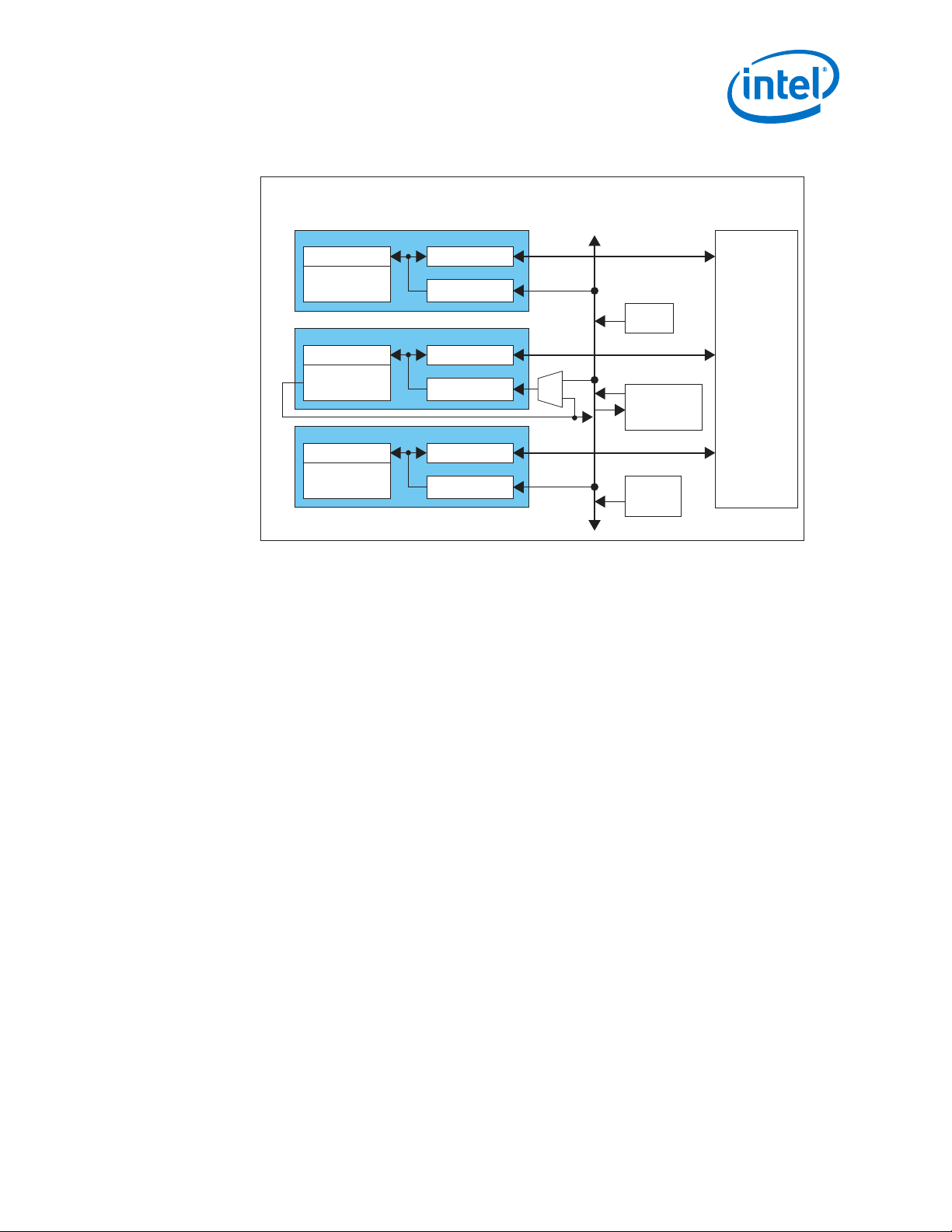

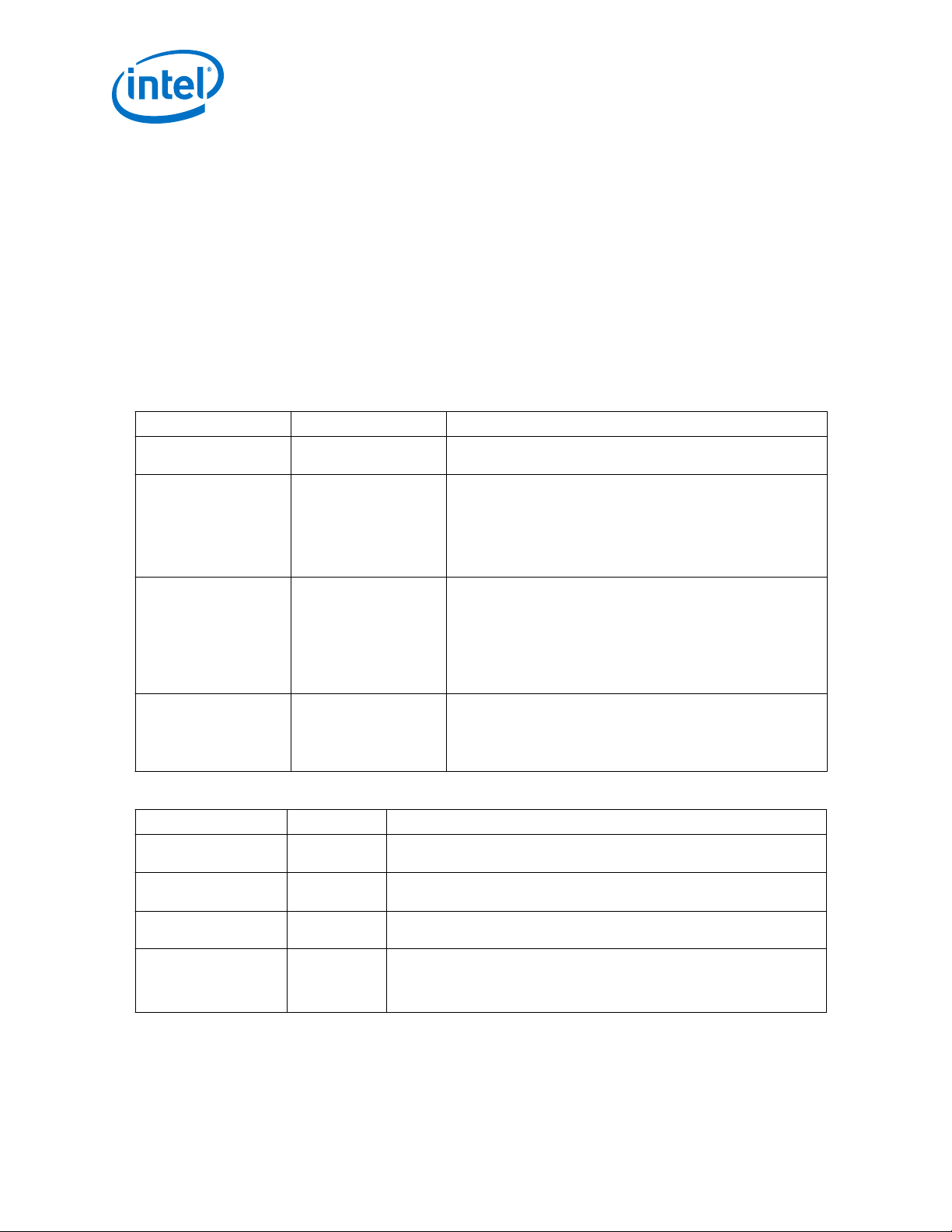

1.2.1. Transceiver Bank Architecture

The transceiver bank is the fundamental unit that contains all the functional blocks

related to the device's high speed serial transceivers.

Each transceiver bank includes six transceiver channels in all devices except for the

devices with 66 transceiver channels. Devices with 66 transceiver channels have both

six channel and three channel transceiver banks. The uppermost transceiver bank on

the left and the right side of these devices is a three channel transceiver bank. All

other devices contain only six channel transceiver banks.

The figures below show the transceiver bank architecture with the phase locked loop

(PLL) and clock generation block (CGB) resources available in each bank.

Intel® Arria® 10 Transceiver PHY User Guide

20

Page 21

PMA

Channel PLL

(CDR Only)

PCS

Local CGB2

CH2

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB1

CH1

PMA

Channel PLL

(CDR Only)

PCS

Local CGB0

CH0

FPGA Core

Fabric

Three-Channel GX Transceiver Bank

Master

CGB0

fPLL0

ATX

PLL0

Clock

Distribution

Network

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 12. Three-Channel GX Transceiver Bank Architecture

Note: This figure is a high level overview of the transceiver bank architecture. For details

about the available clock networks refer to the PLLs and Clock Networks chapter.

Intel® Arria® 10 Transceiver PHY User Guide

21

Page 22

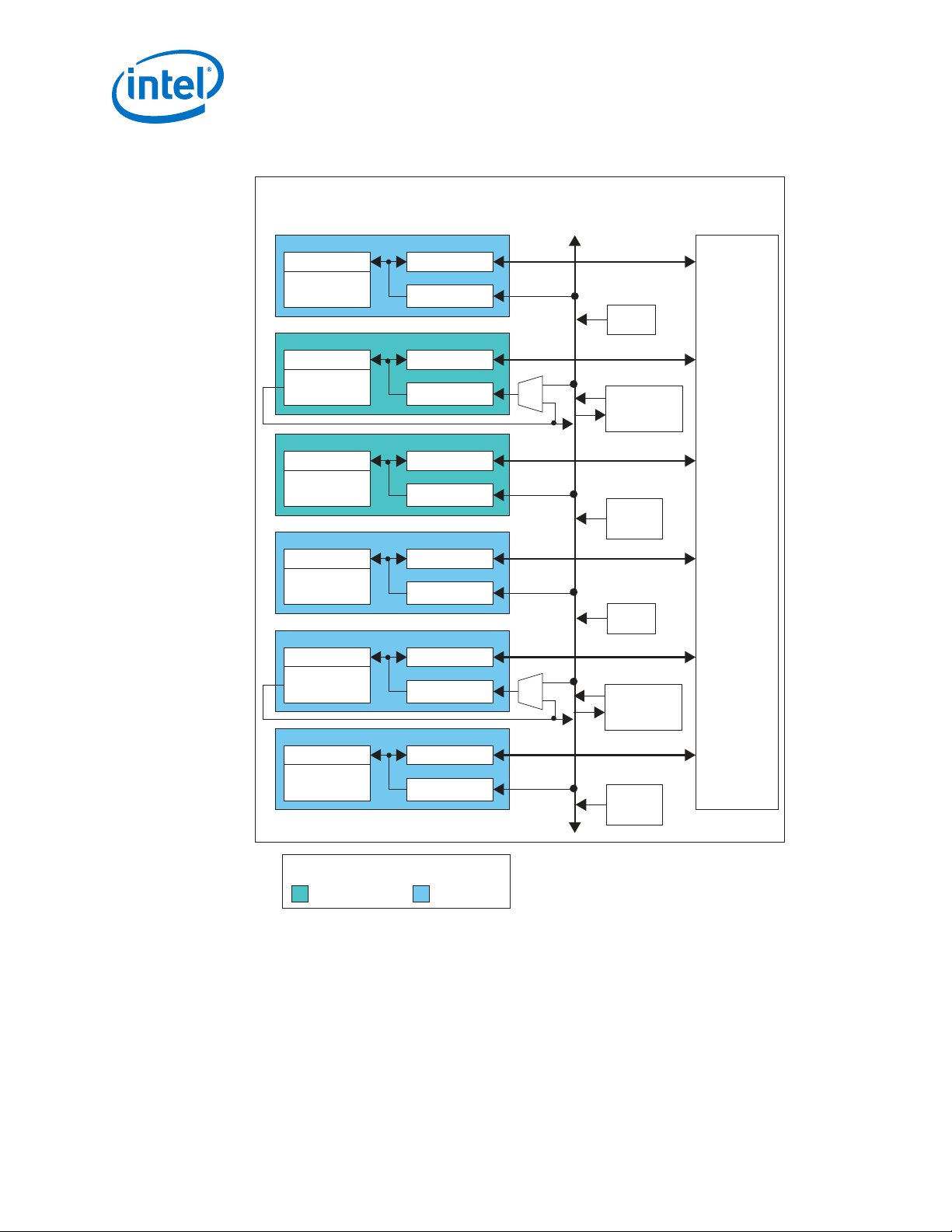

Figure 13. Six-Channel GX Transceiver Bank Architecture

PMA

Channel PLL

(CDR Only)

PCS

Local CGB5

CH5

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB4

CH4

PMA

Channel PLL

(CDR Only)

PCS

Local CGB3

CH3

PMA

Channel PLL

(CDR Only)

PCS

Local CGB2

CH2

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB1

CH1

PMA

Channel PLL

(CDR Only)

PCS

Local CGB0

CH0

FPGA Core

Fabric

Clock

Distribution

Network

Six-Channel GX Transceiver Bank

fPLL1

Master

CGB1

Master

CGB0

ATX

PLL0

ATX

PLL1

fPLL0

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Note: This figure is a high level overview of the transceiver bank architecture. For details

Intel® Arria® 10 Transceiver PHY User Guide

22

about the available clock networks refer to the PLLs and Clock Networks chapter.

Page 23

CH1

PMA

Channel PLL

(CDR Only)

PCS

Local CGB5

CH5

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB4

CH4

PMA

Channel PLL

(CDR Only)

PCS

Local CGB3

CH3

PMA

Channel PLL

(CDR Only)

PCS

Local CGB2

CH2

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB1

PMA

Channel PLL

(CDR Only)

PCS

Local CGB0

CH0

FPGA Core

Fabric

Clock

Distribution

Network

Six-Channel GT Transceiver Bank GXBL1G

fPLL1

Master

CGB1

Master

CGB0

ATX

PLL1

ATX

PLL0

fPLL0

GX Channel

GT/GX Channel

Legend

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 14. GT Transceiver Bank Architecture

In the GT device, the transceiver banks GXBL1E, GXBL1G, and GXBL1H include GT channels.

Note: This figure is a high level overview of the transceiver bank architecture. For details

about the available clock networks refer to the PLLs and Clock Networks chapter.

Intel® Arria® 10 Transceiver PHY User Guide

23

Page 24

CH1

PMA

Channel PLL

(CDR Only)

PCS

Local CGB5

CH5

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB4

CH4

PMA

Channel PLL

(CDR Only)

PCS

Local CGB3

CH3

PMA

Channel PLL

(CDR Only)

PCS

Local CGB2

CH2

PMA

Channel PLL

(CMU/CDR)

PCS

Local CGB1

PMA

Channel PLL

(CDR Only)

PCS

Local CGB0

CH0

FPGA Core

Fabric

Clock

Distribution

Network

Six-Channel GT

Transceiver Banks GXBL1E and GXBL1H

fPLL1

Master

CGB1

Master

CGB0

ATX

PLL1

ATX

PLL0

fPLL0

GX Channel

GT/GX Channel

Legend

®

1. Arria

Figure 15. GT Transceiver Bank Architecture for Banks GXBL1E and GXBL1H

10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Note: This figure is a high level overview of the transceiver bank architecture. For details

Intel® Arria® 10 Transceiver PHY User Guide

24

about the available clock networks refer to the PLLs and Clock Networks chapter.

The transceiver channels perform all the required PHY layer functions between the

FPGA fabric and the physical medium. The high speed clock required by the

transceiver channels is generated by the transceiver PLLs. The master and local clock

generation blocks (CGBs) provide the necessary high speed serial and low speed

parallel clocks to drive the non-bonded and bonded channels in the transceiver bank.

Page 25

Standard PCS

PCIe Gen3 PCS

Enhanced PCSKR FEC

PCS Direct

Hard IP

(Optional)

Soft PIPE

(Optional)

FPGA Fabric

Transmitter PCS

Transmitter PMA

Serializer

Standard PCS

PCIe Gen3 PCS

Enhanced PCSKR FEC

PCS Direct

Receiver PCS

Receiver PMA

DeserializerCDR

Notes:

(1) The FPGA Fabric - PCS and PCS-PMA interface widths are configurable.

(1)

(1)

(1)

(1)

®

1. Arria

UG-01143 | 2018.06.15

10 Transceiver PHY Overview

Related Information

• PLLs and Clock Networks on page 347

• Transceiver Basics

Online training course for transceivers.

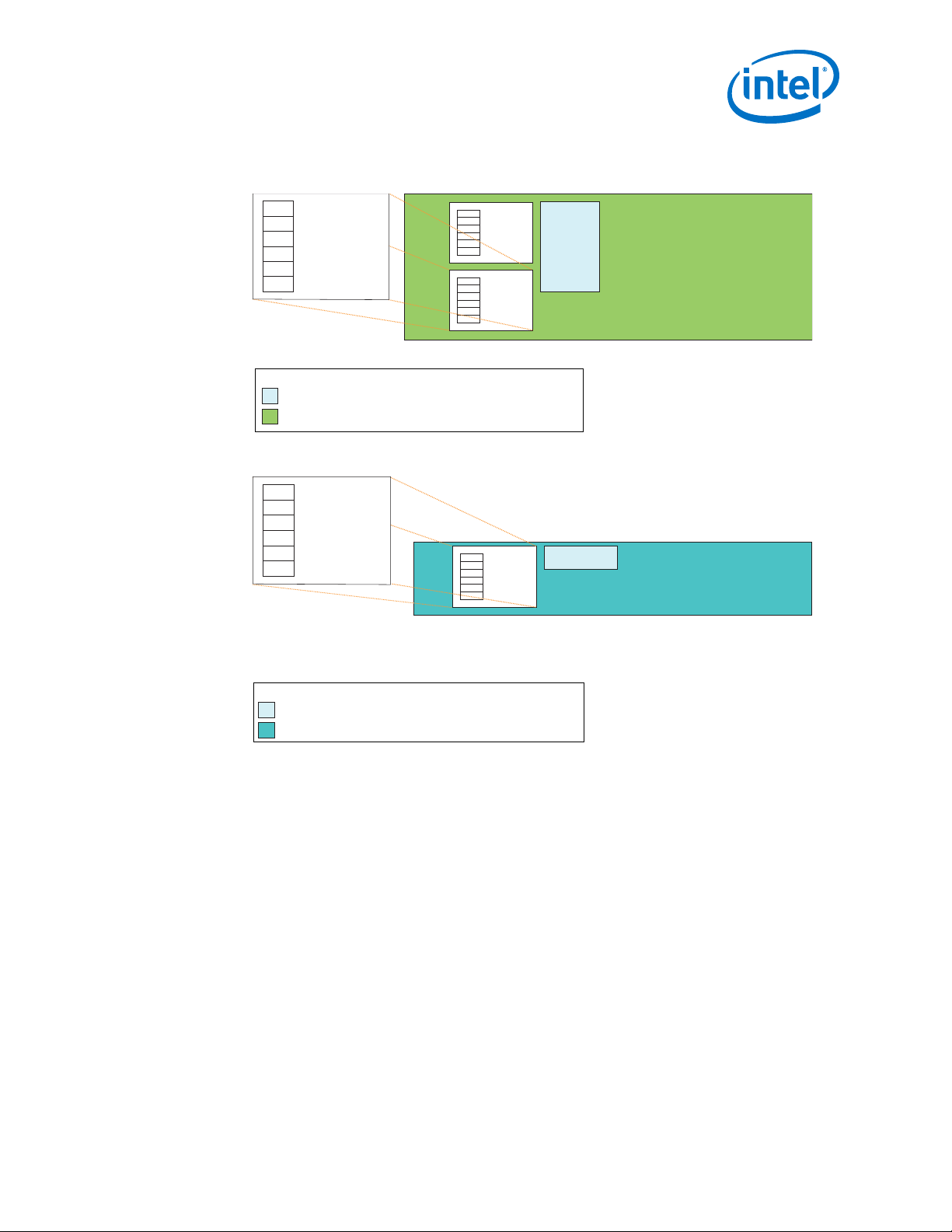

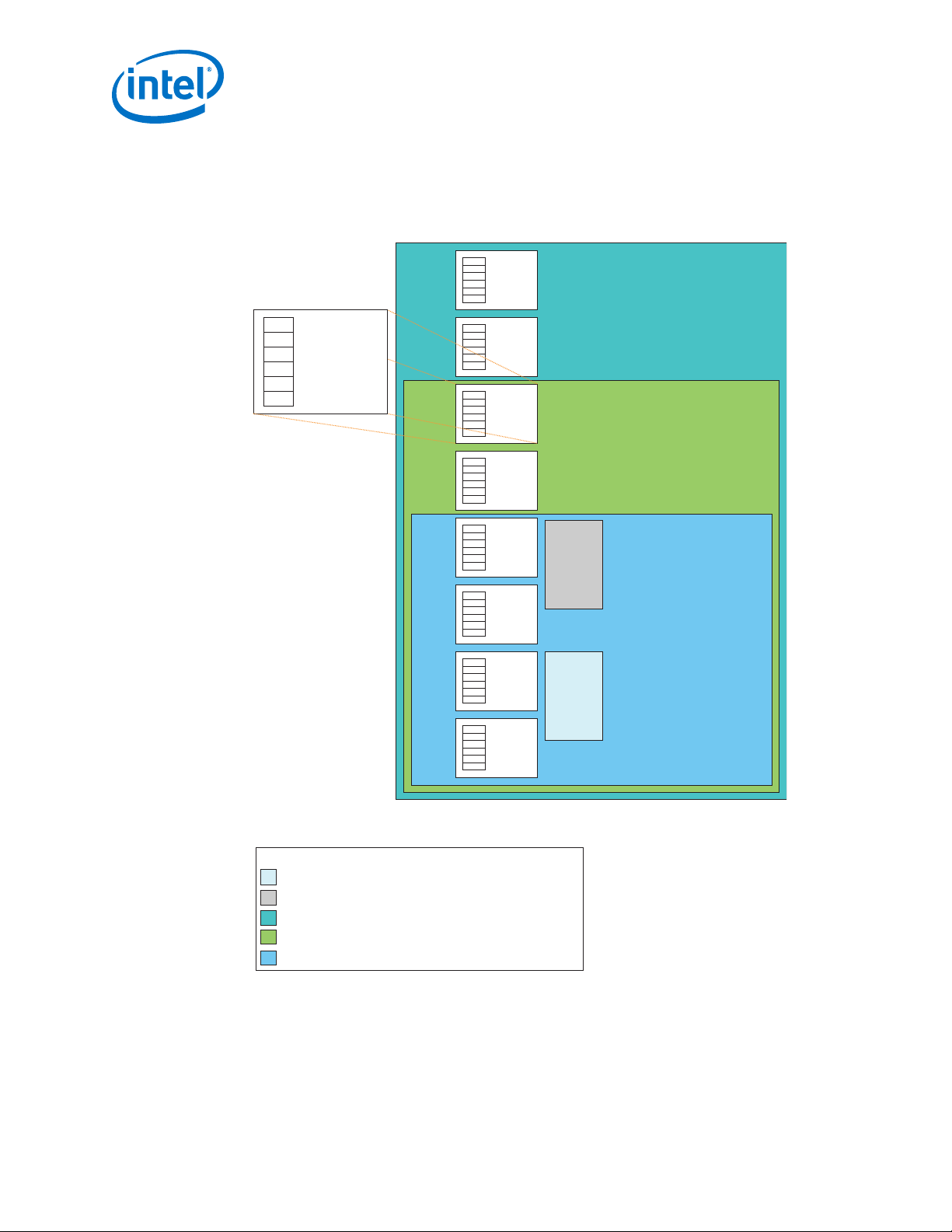

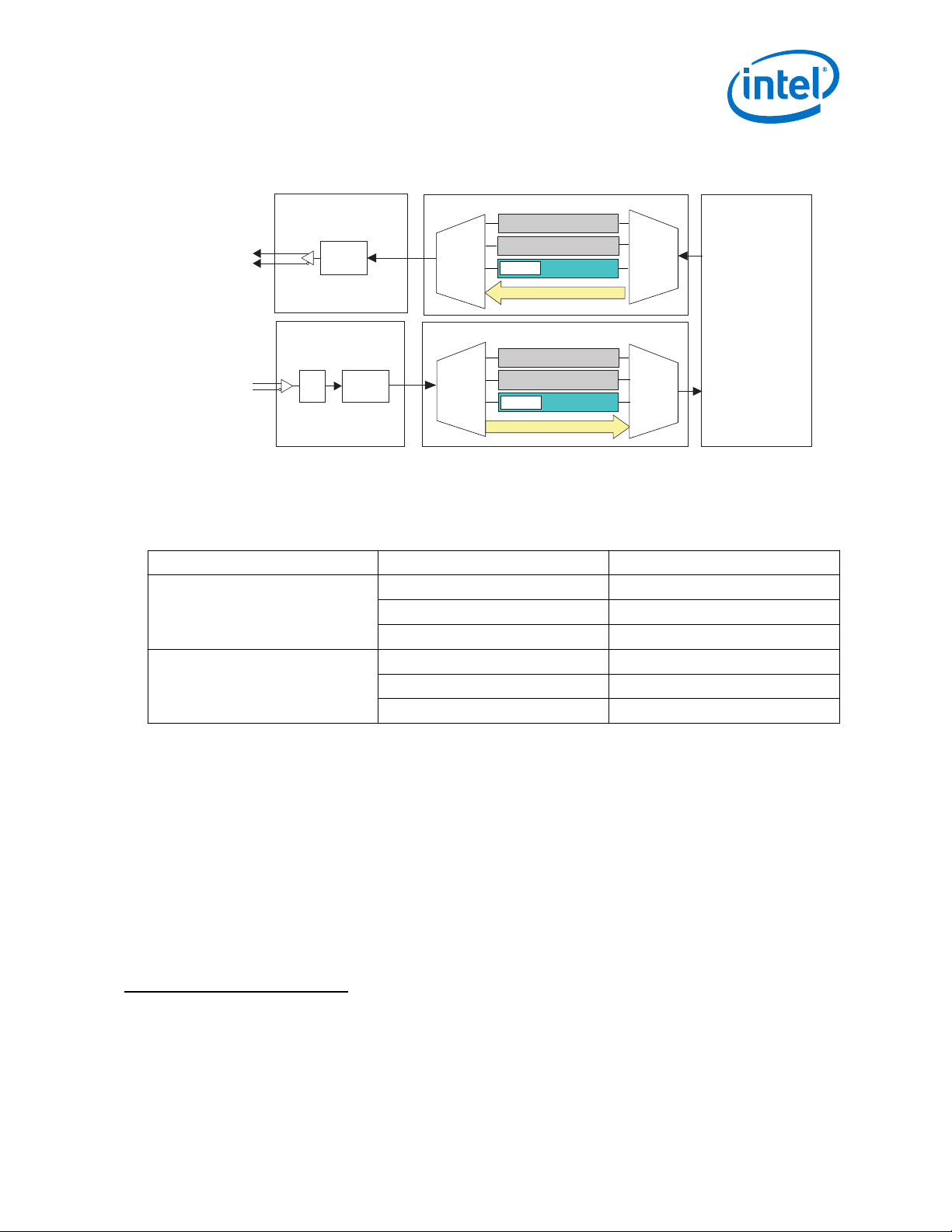

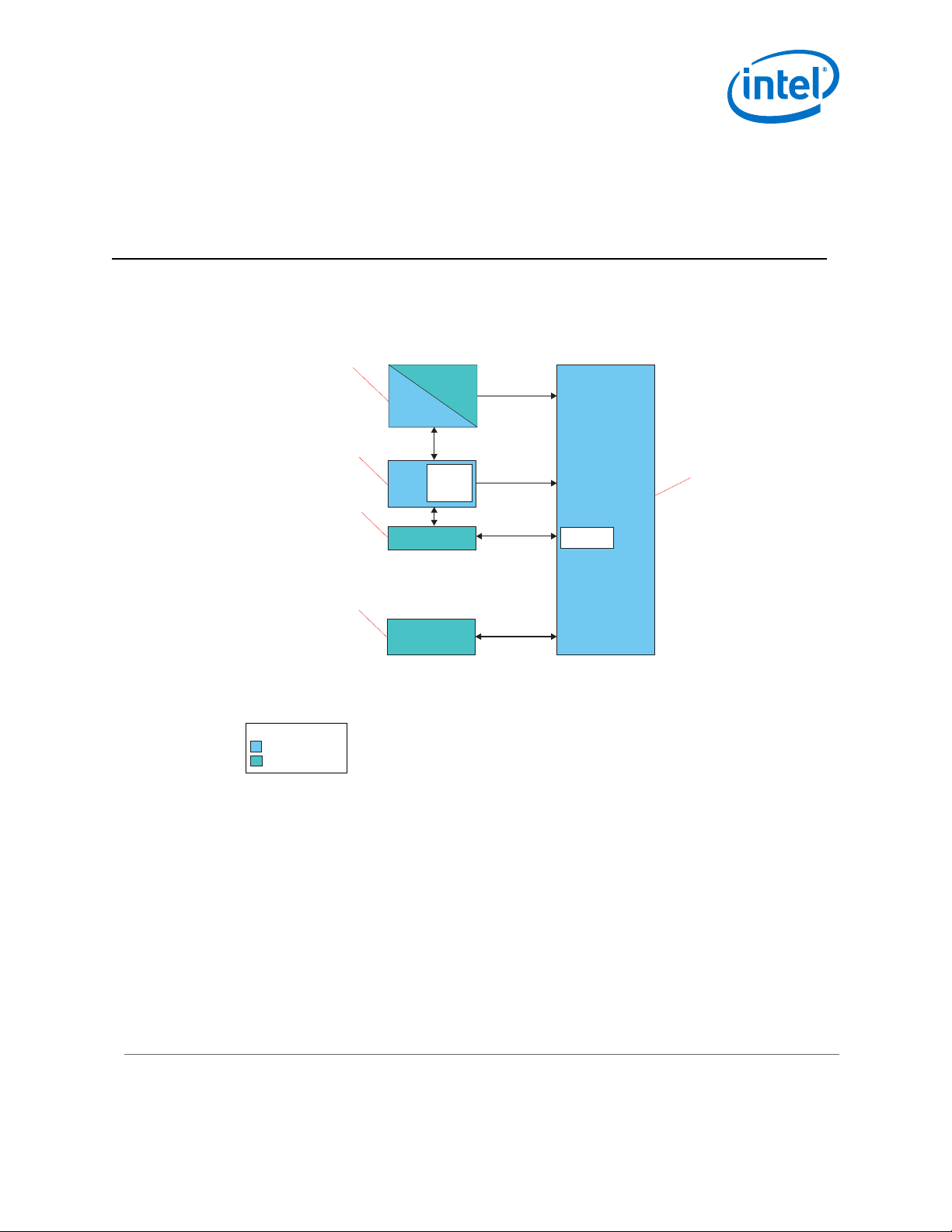

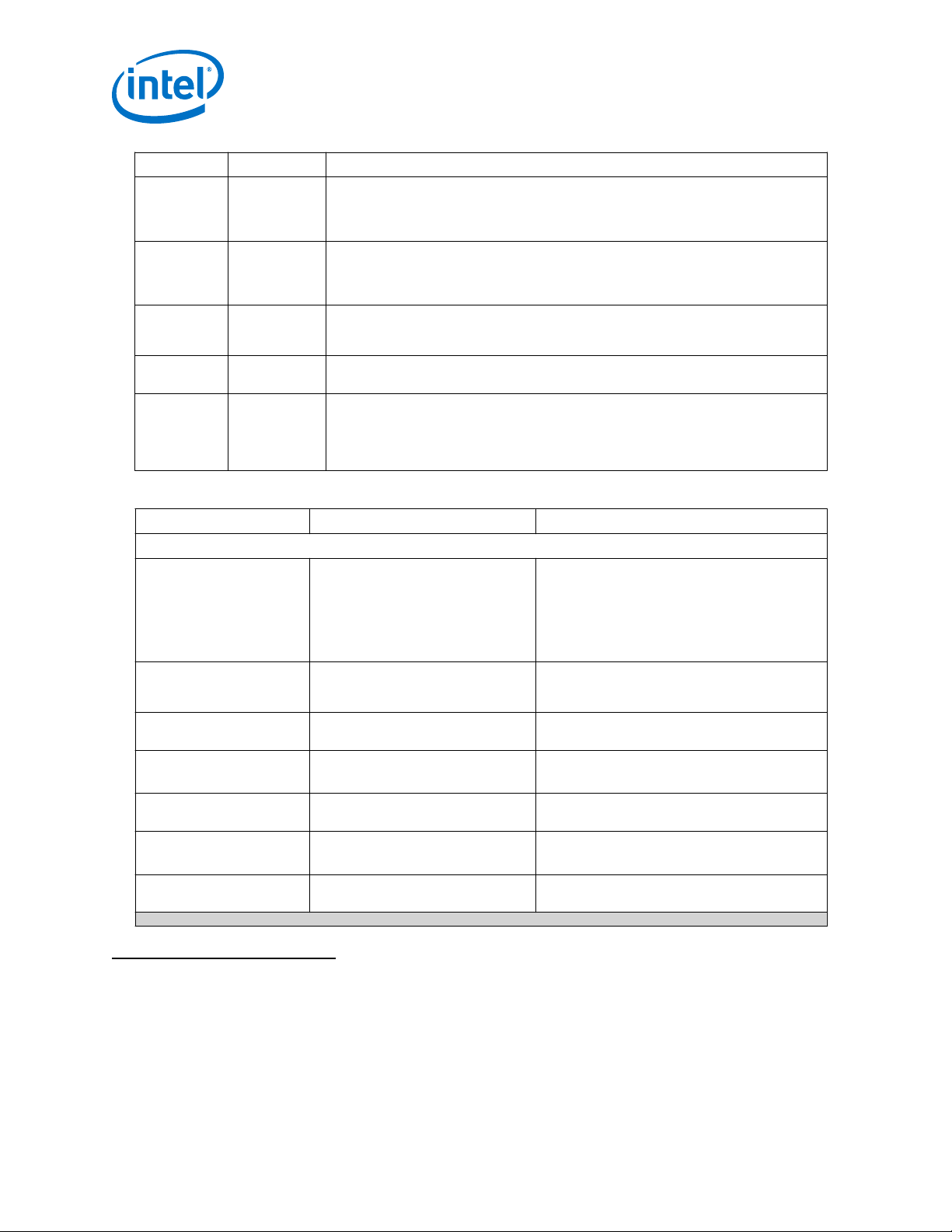

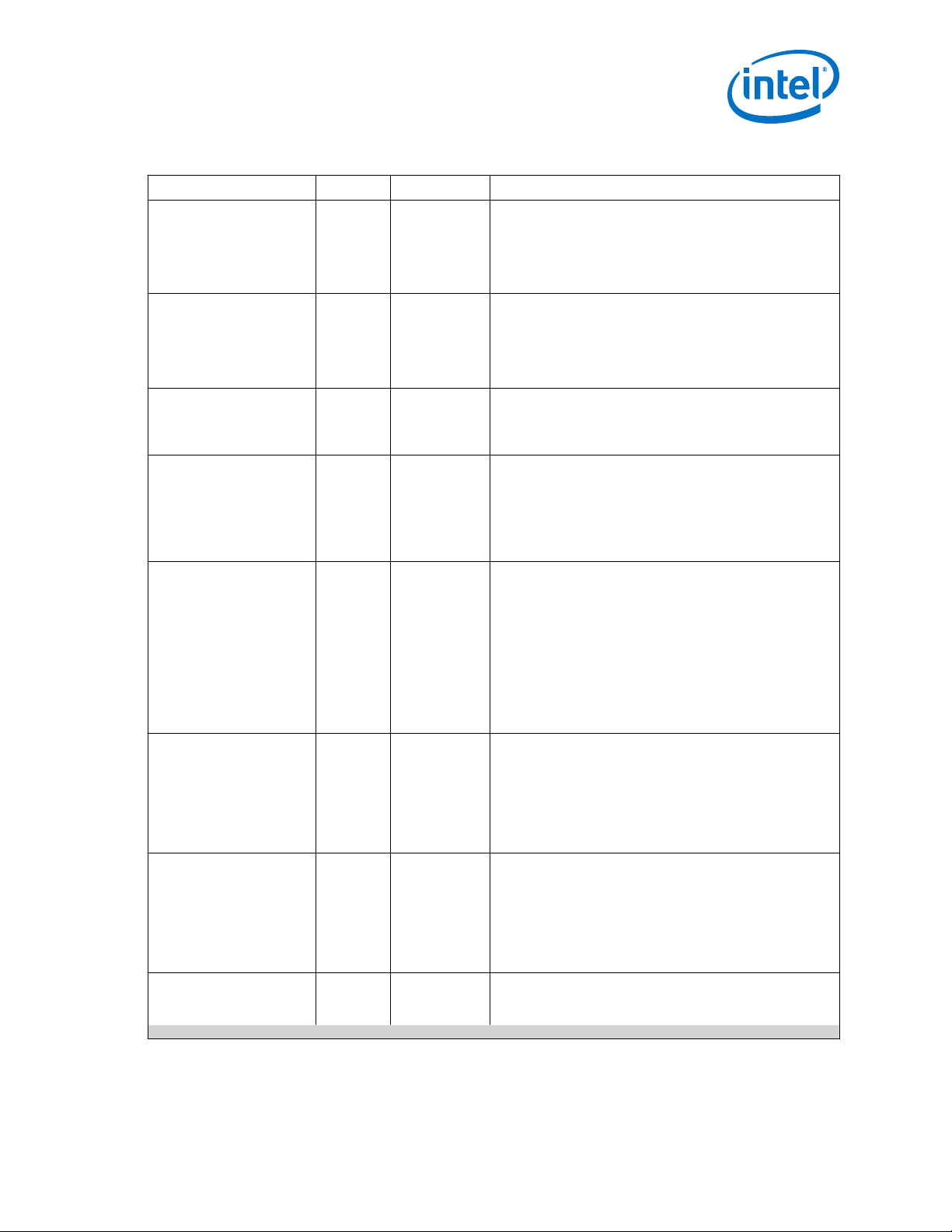

1.2.2. PHY Layer Transceiver Components

Transceivers in Arria 10 devices support both Physical Medium Attachment (PMA) and

Physical Coding Sublayer (PCS) functions at the physical (PHY) layer.

A PMA is the transceiver's electrical interface to the physical medium. The transceiver

PMA consists of standard blocks such as:

• serializer/deserializer (SERDES)

• clock and data recovery PLL

• analog front end transmit drivers

• analog front end receive buffers

The PCS can be bypassed with a PCS Direct configuration. Both the PMA and PCS

blocks are fed by multiple clock networks driven by high performance PLLs. In PCS

Direct configuration, the data flow is through the PCS block, but all the internal PCS

blocks are bypassed. In this mode, the PCS functionality is implemented in the FPGA

fabric.

1.2.2.1. The GX Transceiver Channel

Figure 16. GX Transceiver Channel in Full Duplex Mode.

Arria 10 GX transceiver channels have three types of PCS blocks that together support

continuous data rates between 1.0 Gbps and 17.4 Gbps.

Intel® Arria® 10 Transceiver PHY User Guide

25

Page 26

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

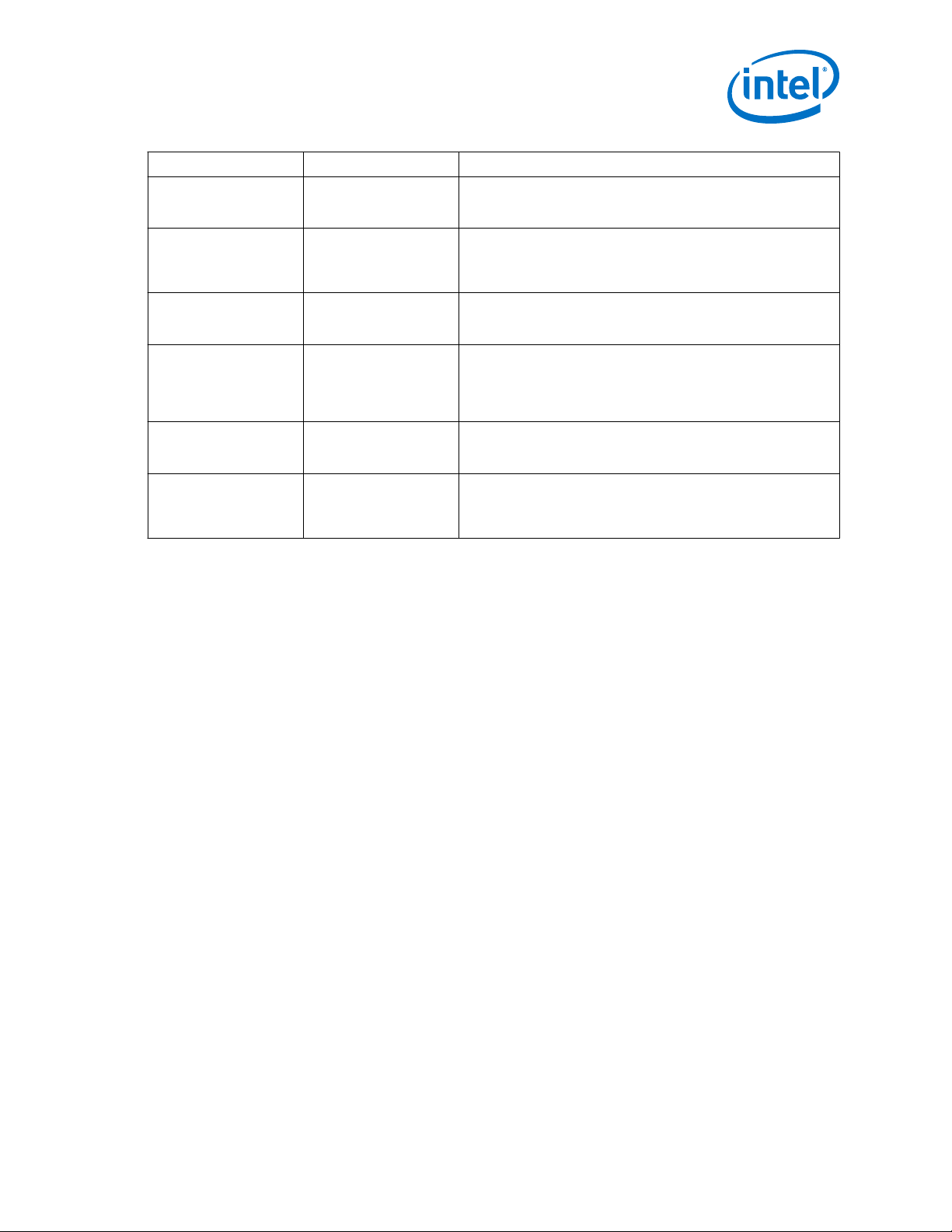

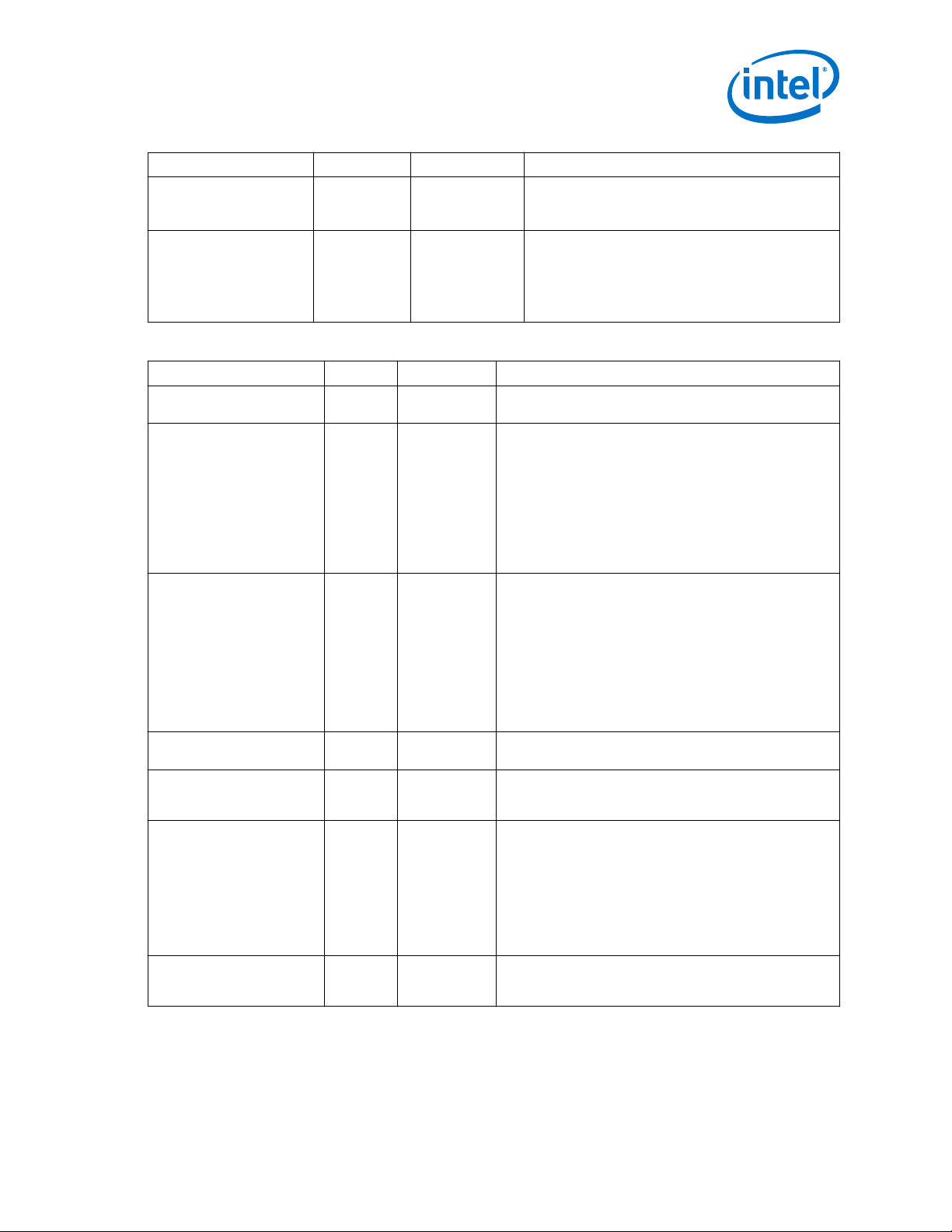

Table 6. PCS Types Supported by GX Transceiver Channels

PCS Type Data Rate

Standard PCS 1.0 Gbps to 10.81344 Gbps

Enhanced PCS 1.0 Gbps

PCIe Gen3 PCS 8 Gbps

(6)

to 17.4 Gbps

Note: 1. The GX channel can also operate in PCS Direct configuration for data rates from

1.0 Gbps to 17.4 Gbps. To operate GX transceiver channels in PCS Direct

designated data rates, refer to the IntelArria 10 Device Datasheet for more details

on power supply, speed grade, and transceiver configurations requirement.

2. The minimum operational data rate is 1.0 Gbps for both the transmitter and

receiver. For transmitter data rates less than 1.0 Gbps, oversampling must be

applied at the transmitter. For receiver data rates less than 1.0 Gbps,

oversampling must be applied at the receiver.

3. To operate GX transceiver channels with the PCS at designated data rates, refer to

the IntelArria 10 Device Datasheet for more details on power supply, speed grade,

and transceiver configurations requirement.

Related Information

IntelArria 10 Device Datasheet

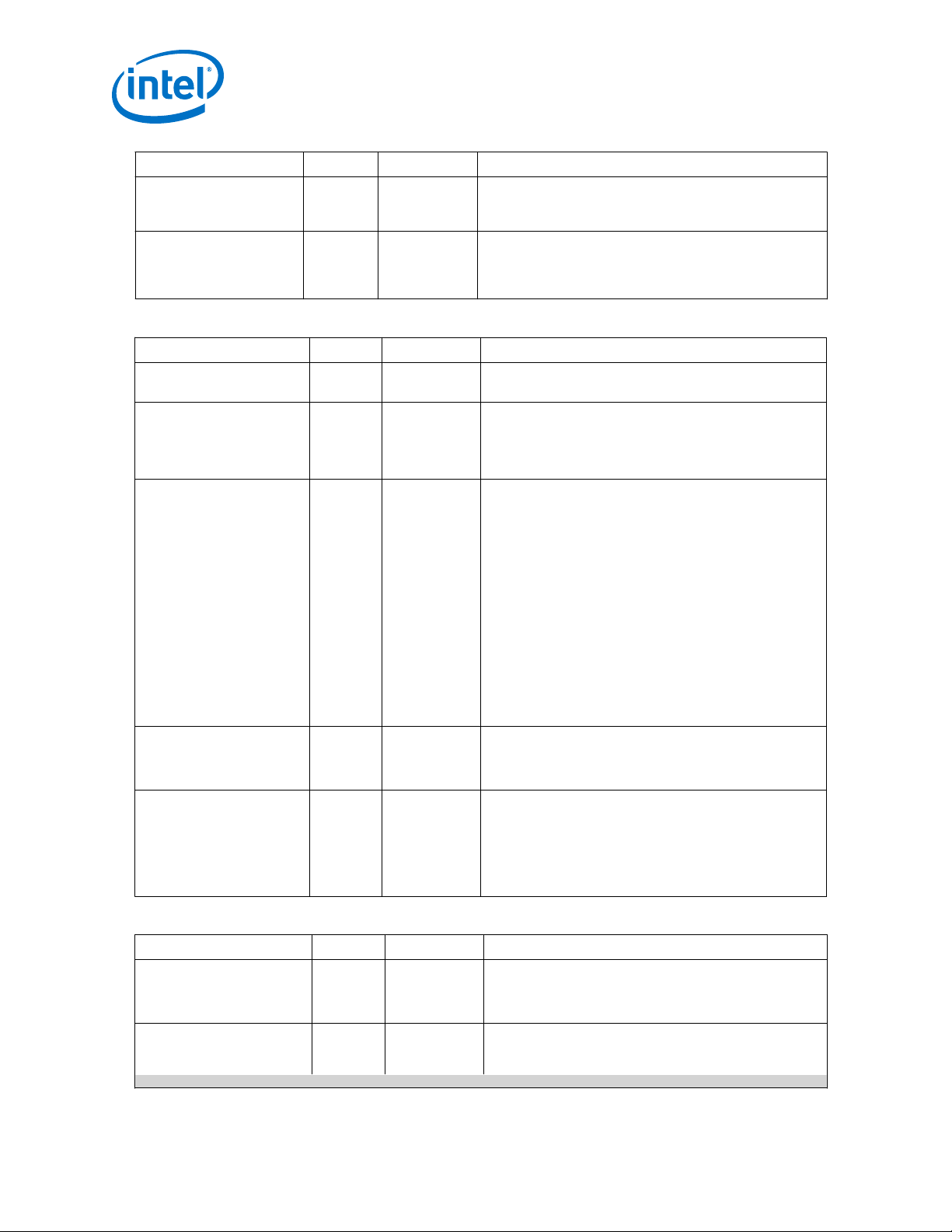

1.2.2.2. The GT Transceiver Channel

The GT transceiver channels are used for supporting data rates from 17.4 Gbps to

25.8 Gbps. The PCS Direct datapath that bypasses all PCS blocks is the primary

configuration used to support GT data rates from 17.4 Gbps to 25.8 Gbps.

Alternatively, the Enhanced PCS in Basic low latency configuration can also be used to

support GT data rates from 17.4 Gbps to 25.8 Gbps. The GT transceiver channels can

also be configured as GX transceiver channels. When they are configured as GX

transceiver channels, the Standard PCS, Enhanced PCS, and PCIe Gen3 PCS are

available and they support data rates from 1.0 Gbps to 17.4 Gbps.

(6)

Applies when operating in reduced power modes. For standard power modes, the Enhanced

PCS minimum data rate is 1600 Mbps.

Intel® Arria® 10 Transceiver PHY User Guide

26

Page 27

Notes:

(3) The Standard PCS and PCIe Gen3 PCS blocks are available when the GT channel is configured as a GX transceiver channel.

(1) The Enhanced PCS must be configured in Basic low latency mode to support data rate range from 17.4 Gbps to 25.8 Gbps.

(2) The FPGA Fabric - PCS and PCS-PMA interface widths are configurable.

Standard PCS

PCIe Gen3 PCS

Enhanced PCSKR FEC

PCS Direct

FPGA Fabric

Transmitter PCS

Transmitter PMA

Serializer

Standard PCS

PCIe Gen3 PCS

Enhanced PCSKR FEC

PCS Direct

Receiver PCS

Receiver PMA

DeserializerCDR

(1)

(1)

(2)

(2)

(2)

(2)

(3)

(3)

(3)

(3)

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Figure 17. GT Transceiver Channel in Full Duplex Mode Operating Between 17.4 Gbps

and 25.8 Gbps

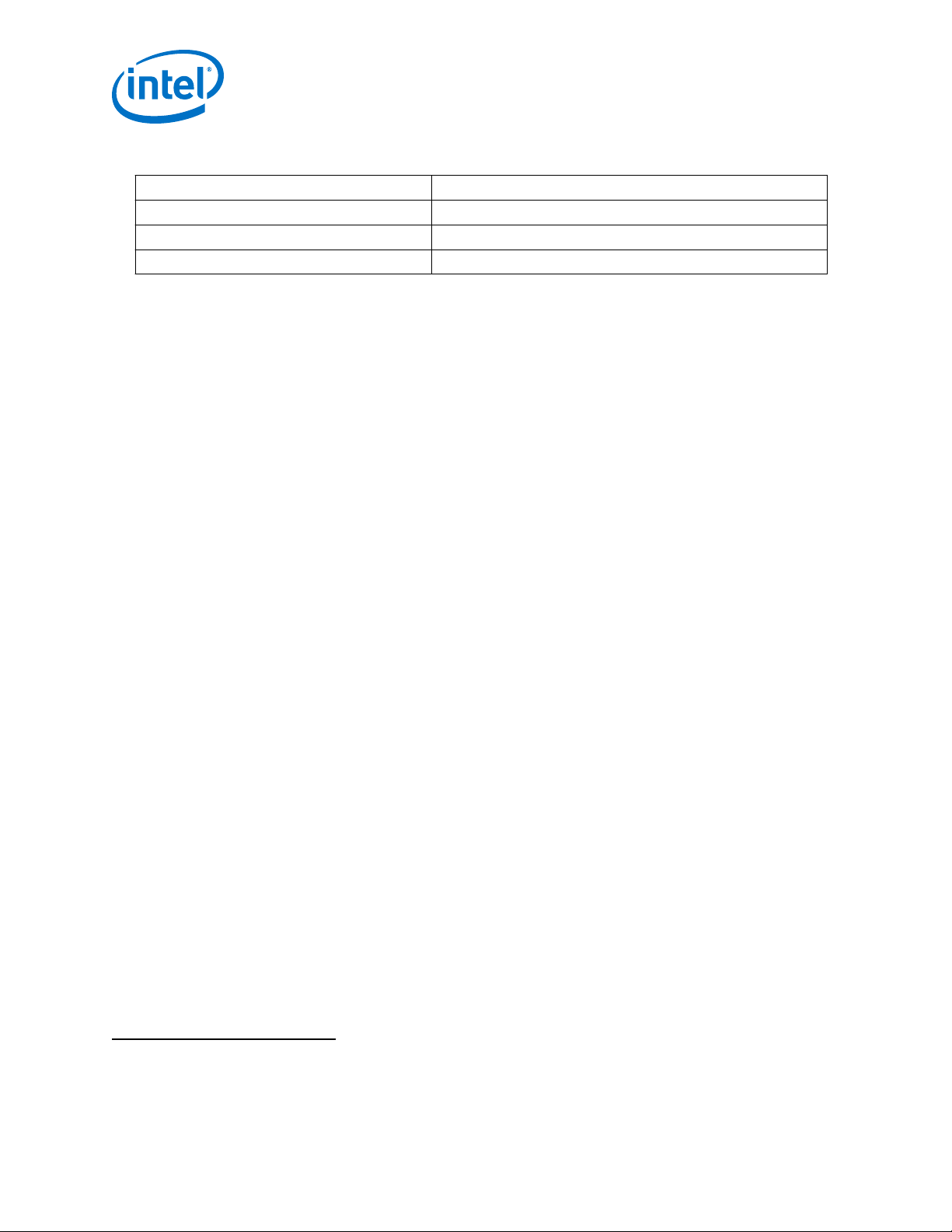

Table 7. PCS Types and Data Rates Supported by GT Channel Configurations

GT Channel Configuration PCS Type Data Rates Supported

GT Standard PCS Not available for GT configuration

Enhanced PCS 17.4 Gbps to 25.8 Gbps

PCIe Gen3 PCS Not available for GT configuration

GX Standard PCS 1.0 Gbps to 12 Gbps

Enhanced PCS 1.0 Gbps

PCIe Gen3 PCS 8 Gbps

Note: 1. The GT channels can also operate in PCS Direct configuration for data rates from

1.0 Gbps to 25.8 Gbps. The PCS Direct datapath that bypasses all PCS blocks is

the primary configuration used to support GT data rates from 17.4 Gbps to 25.8

Gbps. To operate GX and GT transceiver channels in PCS Direct designated data

rates, refer to the IntelArria 10 Device Datasheet for more details on power

supply, speed grade, and transceiver configurations requirement.

2. The minimum operational data rate is 1.0 Gbps for both the transmitter and

receiver. For transmitter data rates less than 1.0 Gbps, oversampling must be

applied at the transmitter. For receiver data rates less than 1.0 Gbps,

oversampling must be applied at the receiver.

3. To operate GX and GT transceiver channels with the PCS at designated data rates,

(7)

The Enhanced PCS must be configured in Basic low latency mode to support data rate range

refer to the IntelArria 10 Device Datasheet for more details on power supply,

speed grade, and transceiver configurations requirement.

from 17.4 Gbps to 25.8 Gbps.

(8)

Applies when operating in reduced power modes. For standard power modes, the Enhanced

PCS minimum data rate is 1600 Mbps.

(7)

(8)

to 17.4 Gbps

Intel® Arria® 10 Transceiver PHY User Guide

27

Page 28

Related Information

IntelArria 10 Device Datasheet

1.2.3. Transceiver Phase-Locked Loops

Each transceiver channel in Arria 10 devices has direct access to three types of high

performance PLLs:

• Advanced Transmit (ATX) PLL

• Fractional PLL (fPLL)

• Channel PLL / Clock Multiplier Unit (CMU) PLL.

These transceiver PLLs along with the Master or Local Clock Generation Blocks (CGB)

drive the transceiver channels.

Related Information

PLLs on page 349

For more information on transceiver PLLs in Arria 10 devices.

1.2.3.1. Advanced Transmit (ATX) PLL

1. Arria

®

10 Transceiver PHY Overview

UG-01143 | 2018.06.15

An advanced transmit (ATX ) PLL is a high performance PLL. It supports both integer

frequency synthesis and coarse resolution fractional frequency synthesis. The ATX PLL

is the transceiver channel’s primary transmit PLL. It can operate over the full range of

supported data rates required for high data rate applications.

Related Information

• ATX PLL on page 350

For more information on ATX PLL.

• ATX PLL IP Core on page 354

For details on implementing the ATX PLL IP.

1.2.3.2. Fractional PLL (fPLL)

A fractional PLL (fPLL) is an alternate transmit PLL used for generating lower clock

frequencies for 12.5 Gbps and lower data rate applications. fPLLs support both integer

frequency synthesis and fine resolution fractional frequency synthesis. Unlike the ATX

PLL, the fPLL can also be used to synthesize frequencies that can drive the core

through the FPGA fabric clock networks.

Related Information

• fPLL on page 359

For more information on fPLL.

• fPLL IP Core on page 362

For details on implementing the fPLL IP.

1.2.3.3. Channel PLL (CMU/CDR PLL)

A channel PLL resides locally within each transceiver channel. Its primary function is

clock and data recovery in the transceiver channel when the PLL is used in clock data

recovery (CDR) mode. The channel PLLs of channel 1 and 4 can be used as transmit

Intel® Arria® 10 Transceiver PHY User Guide

28

Page 29

®

1. Arria

UG-01143 | 2018.06.15

10 Transceiver PHY Overview

PLLs when configured in clock multiplier unit (CMU) mode. The channel PLLs of

channel 0, 2, 3, and 5 cannot be configured in CMU mode and therefore cannot be

used as transmit PLLs.

Related Information

• CMU PLL on page 368

For more information on CMU PLL.

• CMU PLL IP Core on page 370

For information on implementing CMU PLL IP.

1.2.4. Clock Generation Block (CGB)

In Arria 10 devices, there are two types of clock generation blocks (CGBs):

• Master CGB

• Local CGB

Transceiver banks with six transceiver channels have two master CGBs. Master CGB1

is located at the top of the transceiver bank and master CGB0 is located at the bottom

of the transceiver bank. Transceiver banks with three channels have only one master

CGB. The master CGB divides and distributes bonded clocks to a bonded channel

group. It also distributes non-bonded clocks to non-bonded channels across the x6/xN

clock network.

Each transceiver channel has a local CGB. The local CGB is used for dividing and

distributing non-bonded clocks to its own PCS and PMA blocks.

Related Information

Clock Generation Block on page 383

For more information on clock generation block.

1.3. Calibration

Arria 10 FPGAs contain a dedicated calibration engine to compensate for process

variations. The calibration engine calibrates the analog portion of the transceiver to

allow both the transmitter and receiver to operate at optimum performance.

The CLKUSR pin clocks the calibration engine. All transceiver reference clocks and the

CLKUSR clock must be free running and stable at the start of FPGA configuration to

successfully complete the calibration process and for optimal transceiver performance.

Note:

For more information about CLKUSR electrical characteristics, refer to IntelArria 10

Device Datasheet. The CLKUSR can also be used as an FPGA configuration clock. For

information about configuration requirements for the CLKUSR pin, refer to the

Configuration, Design Security, and Remote System Upgrades in Arria 10 Devices

chapter in the Arria 10 Core Fabric and General-Purpose I/O Handbook. For more

information about calibration, refer to the Calibration chapter. For more information

about CLKUSR pin requirements, refer to the IntelArria 10 GX, GT, and SX Device

Family Pin Connection Guidelines.

Related Information

• IntelArria 10 Device Datasheet

Intel® Arria® 10 Transceiver PHY User Guide

29

Page 30

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

• Configuration, Design Security, and Remote System Upgrades in Arria 10 Devices

• IntelArria 10 GX, GT, and SX Device Family Pin Connection Guidelines

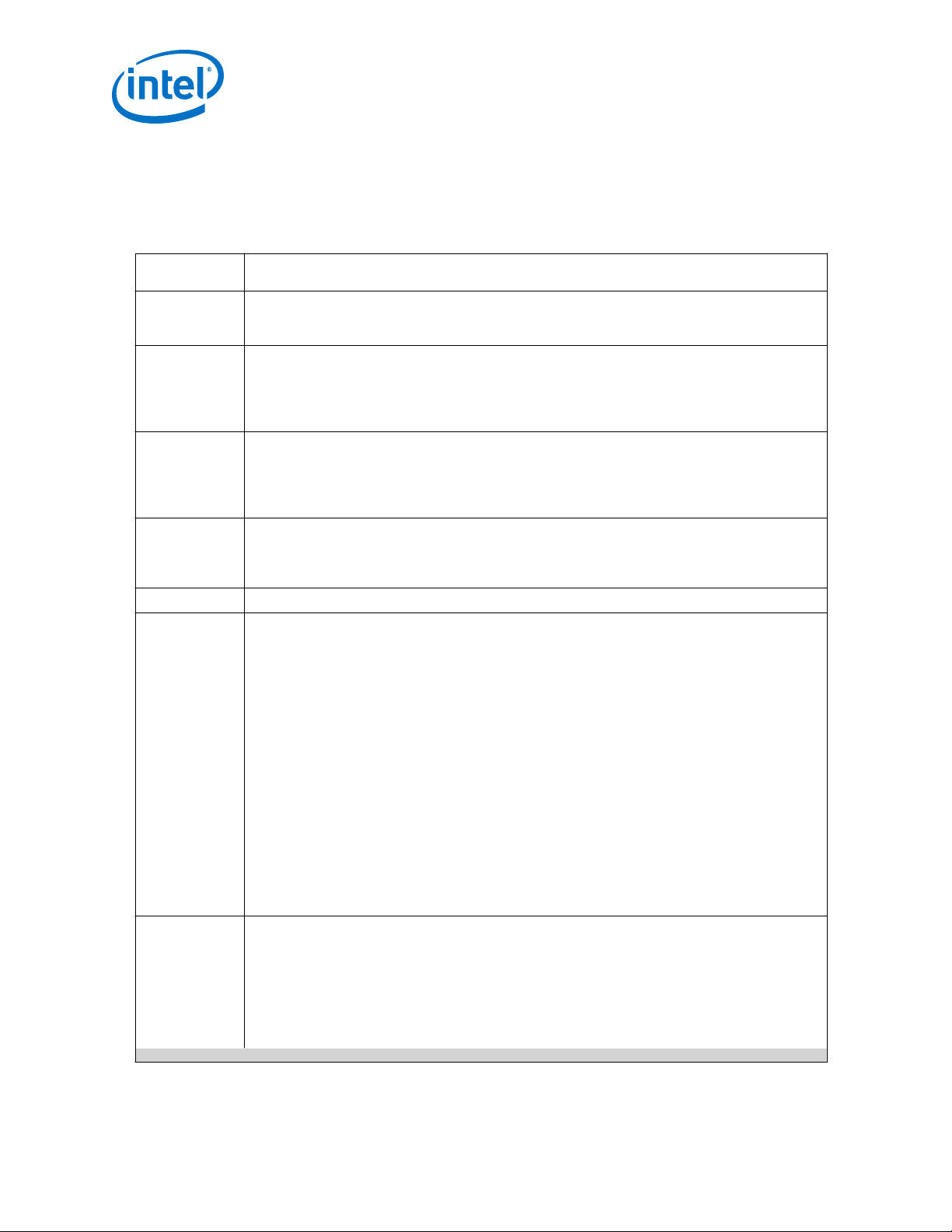

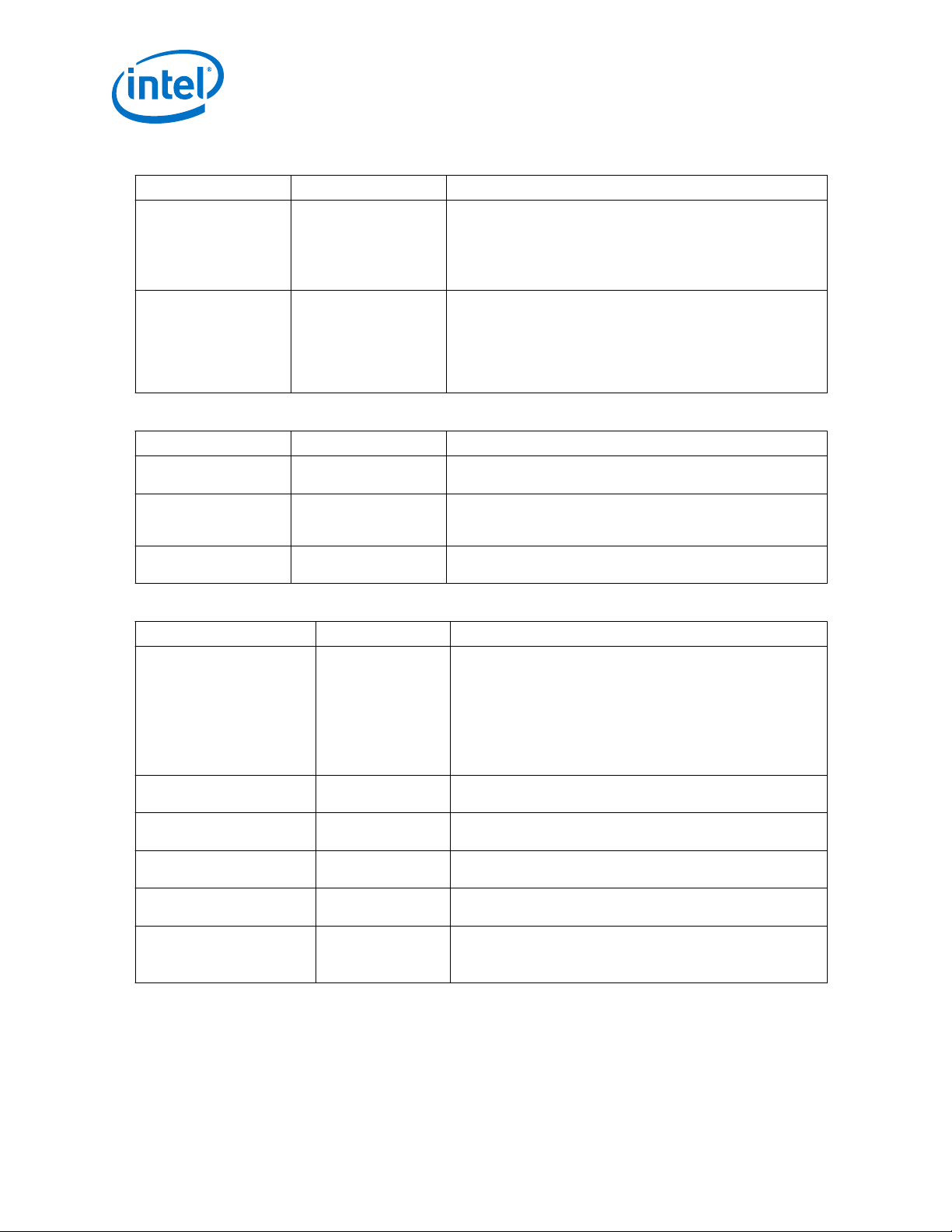

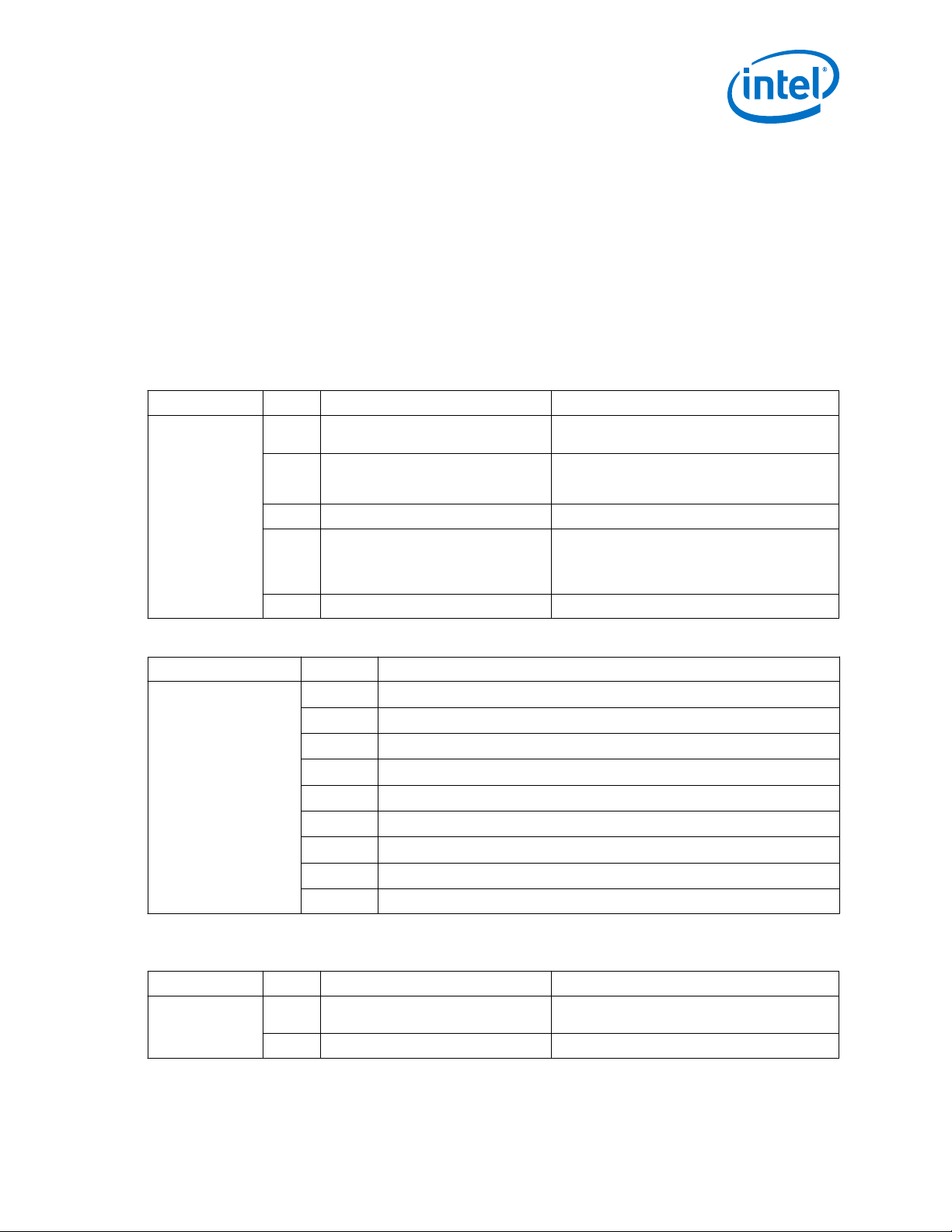

1.4. Intel Arria 10 Transceiver PHY Overview Revision History

Document

Version

2018.06.15 Made the following changes:

• Changed the data rate range for the Standard PCS in the "PCS types Supported by GX Transceiver

Channels" table.

2016.05.02 Made the following changes:

• Maximum backplane rate updated from 16.0 Gbps to 12.5 Gbps.

• No Backplane support when VCCR/T_GXB=0.95 (Low Power Mode).

• Added a footnote to refer to Arria 10 Device datasheet for PCS Types Supported by GX and GT

Transceiver Channels.

2016.02.11 Made the following changes:

• Changed the "Arria 10 GT Devices with 72 Transceiver Channels and Four PCIe Hard IP Blocks"

figure.

• Changed the "GT Transceiver Bank Architecture" figure.

• Added the "GT Transceiver Bank Architecture for Banks GXBL1E and GXBL1H" figure.

2015.11.02 Made the following changes:

• Changed the minimum data rate from 611 Mbps to 1.0 Gbps.

• Changed the location of a PCIe Hard IP block in the "Arria 10 GX Devices with 66 Transceiver

Channels and Three PCIe Hard IP Blocks" figure.

2015.05.11 Changed lower limit of supported data rate from 1.0 Gbps to 611 Mbps

2014.12.15 Made the following changes:

• Added statement that a 125-Mbps data rate is possible with oversampling in the "Arria 10

Transceiver PHY Overview" section.

• Changed the data rate ranges for Standard PCS and Enhanced PCS in the "PCS Types Supported by

GX Transceiver Channels" table.

• Changed the note in "The GX Transceiver Channel" section.

• Changed the data rate ranges for Standard PCS and Enhanced PCS in the "PCS Types and Data

Rates Supported by GT Channel Configurations" table.

• Added a legend entry to the "Arria 10 GT Devices with 96 Transceiver Channels and Four PCIe Hard

IP Blocks" figure.

• Added a legend entry to the "Arria 10 GT Devices with 72 Transceiver Channels and Four PCIe Hard

IP Blocks" figure.

• Added a legend entry to the "Arria 10 GT Devices with 48 Transceiver Channels and Two PCIe Hard

IP Blocks" figure.

• Changed the note to the "PCS Types and Data Rates Supported by GT Channel Configurations"

table.

• Changed the Data Rates Supported for GT channel Standard PCS and PCIe Gen3 PCS types in the

"PCS Types and Data Rates Supported by GT Channel Configurations" table.

• Added a related link to the Arria 10 GX, GT, and SX Device Family Pin Connection Guidelines in the

"Calibration" section.

2014.08.15 Made the following changes:

• Changed the maximum data rate for GT channels to 25.8 Gbps.

• Changed minimum data rate supported by GT transceiver channels to 1 Gbps from 611 Mbps.

• Changed the figure "Arria 10 GX Devices with Six Transceiver Channels and One PCIe Hard IP

Block" to adda a clarification about PCIe Hard IP block.

• Updated the legend for all figures in "Arria 10 GT Device Transceiver Layout" section.

• Changed the device package names in Table1-3 and Table 1-4 in "Arria 10 GX and GT Device

Package Details Section."

Changes

continued...

Intel® Arria® 10 Transceiver PHY User Guide

30

Page 31

1. Arria® 10 Transceiver PHY Overview

UG-01143 | 2018.06.15

Document

Version

• Updated figure "Arria 10 SX Device with 48,36, and 24 Transceiver Channels and Two PCIe Hard IP

Blocks.

• Updated figure "Arria 10 SX Devices with Six Transceiver Channels and One PCIe Hard IP Block" to

add a clarification about PCIe Hard IP.

• Updated the device package names in Table 1-5 in "Arria 10 SX Device Package Details" section.

• Removed all references of the note about PCS-Direct support available in future release.

2013.12.02 Initial release.

Changes