Page 1

21555 Non-Transparent PCI-toPCI Bridge

User Manual

July 2001

Order Number: 278321–002

Page 2

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to the m.

The 21555 Non-Transparent PCI-to-PCI Bridge may contain design defects or errors known as errata which may cause the product to deviate from

published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the

license. The i nf orm at i o n i n t h is do cum en t i s f ur n is he d f o r i nf o rm ati o na l u s e o nl y, is subject t o ch ang e w ith o ut n oti c e, an d s h ould not be construed as a

commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this

document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may

be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

Intel is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be cla imed as the property of others.

2 21555 Non-Transparent PC I-to-PCI Bridge User Manual

Page 3

Contents

Contents

1 Preface ..........................................................................................................................................11

1.1 Cautions and Notes ........................................................... ...... ....... ...... ....... ...... ....... ...... ....12

1.2 Data Units...........................................................................................................................12

1.3 Numbering ..........................................................................................................................12

1.4 Signal Nomenclature ..........................................................................................................13

1.5 Register Abbreviations........................................................................................................14

2 Introduction....................................................................................................................................15

2.1 Comparing a 21555 to a Transparent PPB.........................................................................15

2.2 Architectural Overview........................................................................................................18

2.2.1 Data Buffers...........................................................................................................18

2.2.2 Registers................................................................................................................18

2.2.3 Control Logic..........................................................................................................18

2.3 Special Applications............................................................................................................20

2.3.1 Primary Bus VGA Support.....................................................................................20

2.3.2 Secondary Bus VGA Support ................................................................................20

2.4 Programming Notes............................................................................................................20

2.4.1 Addressing.............................................................................................................20

2.4.2 Transaction Forwarding .........................................................................................21

2.4.3 ROM Access..........................................................................................................21

3 Signal Descriptions........................................................................................................................23

3.1 Primary PCI Bus Interface Signals .....................................................................................24

3.2 Primary PCI Bus Interface 64-Bit Extension Signals ..........................................................26

3.3 Secondary PCI Bus Interface Signals.................................................................................28

3.4 Secondary PCI Bus Interface 64-Bit Extension Signals .....................................................30

3.5 Miscellaneous Signals .......... ...... ....... ...... ....... ...... ...... ....................................... ....... ...... ... .31

4 Address Decoding .........................................................................................................................33

4.1 CSR Address Decoding......................................................................................................34

4.2 Expansion ROM Address Mapping (Decoding)..................................................................34

4.3 Memory 0 Transaction Address Decoding..........................................................................34

4.3.1 Using the BAR Setup Registers.............................................................................35

4.3.2 Direct Address Translation ....................................................................................36

4.3.3 Lookup Table Based Address Translation.............................................................37

4.3.4 Lookup Table Entry Format ...................................................................................40

4.3.5 Forwarding of 64-Bit Address Memory Transactions.............................................41

4.4 I/O Transaction Address Decoding.....................................................................................42

4.4.1 Indirect I/O Transaction Generation.......................................................................42

4.4.2 Subtractive Decoding of I/O Transactions ..... ....... ...... ....... ...... ....... .......................44

4.5 Configuration Accesses ......................................................................................................44

4.5.1 Type 0 Accesses to 21555 Configuration Space...................................................44

4.5.2 Initiation of Configuration Transactions by 21555..................................................45

4.6 21555 Bar Summary...... ....... ...... ....... ...... ....... ...... ....................................... ...... ....... ...... ....47

5 PCI Bus Transactions....................................................................................................................49

5.1 Transactions Overview .......................................................................................................49

21555 Non-Transparent PCI-to-PCI Bridge User Manual 3

Page 4

Contents

5.2 Posted Write Transactions ....... ...... ....... ...... ....... ...... ...... ....... ....................................... ...... .50

5.2.1 Memory Write Transactions...................................................................................51

5.2.2 Memory Write and Invalidate Transactions ....................................... ...... ....... ...... .51

5.2.3 64-bit Extension Posted Write Transaction............................................................52

5.2.4 Write Performance Tuning Options ............................................ ....... ...... ....... ...... .52

5.3 Delayed Write Transactions................................................................................................54

5.4 Delayed Read Transactions ...............................................................................................55

5.4.1 Nonprefetchable Reads.........................................................................................56

5.4.2 Prefetchable Reads ...............................................................................................57

5.4.3 Prefetchable Read Transactions Using the 64-bit Extension ................................57

5.4.4 Read Performance Features and Tuning Options.................................................57

5.5 64-Bit and 32-Bit Transactions Initiated by the 21555........................................................59

5.6 Target Terminations............................................................................................................60

5.6.1 Target Terminations Returned by the 21555.........................................................60

5.6.2 Transaction Termination Errors on the Target Bus................................................61

5.7 Ordering Rules....................................................................................................................61

6 Initialization Requirements ............................................................................................................65

6.1 Power Management, Hot-Swap, and Reset Signals...........................................................65

6.2 Reset Behavior ...................................................................................................................66

6.2.1 Central Function During Reset ..............................................................................68

6.3 21555 Initialization..............................................................................................................68

6.3.1 With SROM, Local, and Host Processors..............................................................69

6.3.2 Without Serial Preload................... ....... ...... ....................................... ...... ....... ...... .69

6.3.3 Without Local Processor... ....... ...... ....... ...... ...... ....... ...... ....... ...... ...........................70

6.3.4 Without Local Processor and Serial Preload .........................................................70

6.3.5 Without Host Processor........................ ...... ...... ....... ...... ....... .................................70

6.4 Power Management Support..............................................................................................70

6.4.1 Transitions Between Power Management States..................................................71

6.4.2 PME# Support .......................................................................................................71

6.4.3 Power Management Data Register................................ ....... ...... ....... ...... ....... ...... .72

6.5 CompactPCI Hot-Swap Functionality .................................................................................72

6.5.1 Overview of CompactPCI Controller Hardware Interface ......................................72

6.5.2 Insertion and Removal Process.............................................................................73

7 Clocking.........................................................................................................................................77

7.1 Primary and Secondary PCI Bus Clock Signals .................................................................77

7.2 21555 Secondary Clock Outputs........................................................................................78

7.3 66 MHz Support..................................................................................................................79

8 Parallel ROM Interface ..................................................................................................................81

8.1 Interface Signals.................................................................................................................81

8.2 Parallel and Serial ROM Connection..................................................................................84

8.3 PROM Read by CSR Access .............................................................................................84

8.4 PROM Write by CSR Access..............................................................................................86

8.5 PROM Dword Read............................................................................................................87

8.6 Access Time and Strobe Control........................................................................................88

8.7 Attaching Additional Devices to the ROM Interface............................................................89

9 Serial ROM Interface.....................................................................................................................91

9.1 SROM Interface Signals .....................................................................................................91

4 21555 Non-Transparent PC I-to-PCI Bridge User Manual

Page 5

Contents

9.2 SROMSROM Preload Operation........................................................................................91

9.3 SROM Configuration Data Preload Format ........................................................................92

9.4 SROM Operation by CSR Access ......................................................................................92

10 Arbitration ......................................................................................................................................97

10.1 Primary PCI Bus Arbitration Signals...................................................................................97

10.2 Secondary PCI Bus Arbitration Signals ..............................................................................97

10.3 Primary PCI Bus Arbitration................................................................................................98

10.4 Secondary PCI Bus Arbitration...........................................................................................98

10.4.1 Secondary Bus Arbitration Using the Internal Arbiter ............................................98

10.4.2 Secondary Bus Arbitration Using an External Arbiter..........................................100

11 Interrupt and Scratchpad Registers.............................................................................................101

11.1 Primary and Secondary PCI Bus Interrupt Signals...........................................................101

11.2 Interrupt Support...............................................................................................................101

11.3 Doorbell Interrupts ............................................................................................................103

11.4 Scratchpad Registers .......................................................................................................103

12 Error Handling .............................................................................................................................105

12.1 Error Signals.....................................................................................................................105

12.1.1 Primary PCI Bus Error Signals.............................................................................105

12.1.2 Secondary PCI Bus Error Signals........................................................................106

12.2 Parity Errors......................................................................................................................107

12.3 System Error (SERR#) Reporting.....................................................................................110

13 JTAG Test Port............................................................................................................................111

13.1 JTAG Signals....................................................................................................................111

13.2 Test Access Port Controller..............................................................................................112

13.2.1 Initialization..........................................................................................................112

14 I2O Support .................................................................................................................................113

14.1 Inbound Message Passing ...............................................................................................113

14.2 Outbound Message Passing.............................................................................................115

14.3 Notes ................................................................................................................................116

15 VPD Support................................................................................................................................119

15.1 Reading VPD Information .................................................................................................119

15.2 Writing VPD Information ...................................................................................................120

16 List of Registers........... ....... ...... ....... ...... ....... ...... ....... ...... ...... ....... ...... .........................................121

16.1 Register Summary............................................................................................................121

16.2 Configuration Registers ....................................................................................................122

16.3 Control and Status Registers............................................................................................126

16.4 Address Decoding ............................................................................................................130

16.4.1 Primary and Secondary Address ........................................................................130

16.4.2 Configuration Transaction Generation Registers.................................................140

16.5 PCI Registers....................................................................................................................147

16.5.1 Configuration Registers .......................................................................................147

16.5.2 Primary and Secondary Command Registers......................................................149

16.5.3 Device-Specific Control and Status Registers.....................................................156

16.6 I2O Registers....................................................................................................................165

21555 Non-Transparent PCI-to-PCI Bridge User Manual 5

Page 6

Contents

16.7 Interrupt Registers ............................................................................................................170

16.8 Scratchpad Registers . ...... ....... ...... ....... ...... ....... ...... ....................................... ...... ....... .....174

16.9 PROM Registers...............................................................................................................175

16.10 SROM Registers...............................................................................................................179

16.11 Arbiter Control............. ...... ....... ...... ....... ...... ....... ...... ...... ....... ...... ....... ...............................183

16.12 Error Registers..................................................................................................................183

16.13 Init Registers.....................................................................................................................185

16.14 JTAG Registers ................................................................................................................190

16.15 VPD Registers............................................ ....... ...... ...... ....... ...... ....... ...... ....... ...... ............192

Index .....................................................................................................................................................197

Figures

1 21555 Intelligent Controller Application......................................................................................16

2 21555 Microarchitecture .............................................................................................................19

3 BAR Setup Register Example ....................................................................................................35

4 Address Format..........................................................................................................................36

5 Direct Offset Address Translation...............................................................................................37

6 Downstream Address Translation Example ...............................................................................37

7 Address Translation Using A Lookup Table ...............................................................................39

8 Upstream Lookup Table Address Translation ............................................................................40

9 Lookup Table Entry Format ........................................................................................................41

10 Dual-Address Transaction Forwarding.......................................................................................42

11 CompactPCI Hot-Swap Connections .........................................................................................73

12 21555 Hot-Swap Insertion and Removal....................................................................................75

13 Synchronous Secondary Clock Generation................................................................................78

14 Parallel and Serial ROM Connections........................................................................................84

15 PROM Read Timing ...................................................................................................................85

16 PROM Write Timing....................................................................................................................87

17 Read and Write Strobe Timing ...................................................................................................88

18 Attaching Multiple Devices on the ROM Interface......................................................................90

19 SROM Write All Timing Diagram................................................................................................94

20 SROM Write Enable Timing Diagram.........................................................................................94

21 SROM Write Disable Timing Diagram........................................................................................94

24 SROM Check Status Timing Diagram........................................................................................95

22 SROM Erase Timing Diagram......... ...... ....... ...... ....... ...................................... ....... ...... ....... ...... .95

23 SROM Erase All Operation.........................................................................................................95

25 Secondary Arbiter Example........................................................................................................99

26 Signal trst_l States....................................................................................................................112

Tables

1 Signal Type Abbreviations..........................................................................................................13

2 Register Abbreviations ...............................................................................................................14

3 21555 and PPB Feature Comparison.........................................................................................17

4 Decoded and Not Decoded Addresses ......................................................................................20

5 Signal Pin Functional Groups.....................................................................................................23

6 Primary PCI Bus Interface Signals .............................................................................................24

6 21555 Non-Transparent PC I-to-PCI Bridge User Manual

Page 7

Contents

7 Primary PCI Bus Interface 64-Bit Extension Signals..................................................................26

8 Secondary PCI Bus Interface Signals.........................................................................................28

9 Secondary PCI Bus Interface 64-Bit Extension Signals .............................................................30

10 Miscellaneous Signals................................................................................................................31

11 Upstream Memory 2 Window Size ..... ....... ...... ....... ...... ...... ....... ...... ....... ...... ....... .......................38

12 Bar Summary..............................................................................................................................47

13 Delayed Write Transaction Target Termination Returns ............................................................55

14 Delayed Read Transaction Target Termination Returns............................................................56

15 Prefetch Boundaries ...................................................................................................................58

16 21555 Transaction Ordering Rules.............................................................................................62

17 Power Management, Hot-Swap, and Reset Signals...................................................................65

18 Reset Mechanisms .....................................................................................................................67

19 Power Management Actions.......................................................................................................71

20 Primary and Secondary PCI Bus Clock Signals.........................................................................77

21 PROM Interface Signals.............................................................................................................82

22 SROM Interface Signals.............................................................................................................91

23 Primary PCI Bus Arbitration Signals...........................................................................................97

24 Secondary PCI Bus Arbitration Signals ......................................................................................97

25 Arbiter Control Register............................................................................................................100

26 Primary and Secondary PCI Bus Interrupt Signals...................................................................101

27 Primary PCI Bus Error Signals .................................................................................................105

28 Secondary PCI Bus Arbitration Signals ....................................................................................106

29 Parity Error Responses.......... ....... ...... ....... ...... ....... ..................................................................107

30 JTAG Signals......................... ....... ...... ....... ...... ....................................... ...... ....... ...... .... ...........111

31 Register Cross Reference Table ..............................................................................................121

32 Configuration Space Address Register.....................................................................................122

33 CSR Address Map....................................................................................................................126

34 Primary CSR and Downstream Memory 0 Bar.........................................................................130

35 Secondary CSR Memory BARs................................................................................................131

36 Primary and Secondary CSR I/O Bars .....................................................................................132

37 Downstream I/O or Memory 1 and Upstream I/O or Memory 0 BAR........................................133

38 Downstream Memory 2 and 3 BAR, and Upstream Memory 1 BAR ........................................134

39 Upper 32 Bits Downstream Memory 3 Bar ...............................................................................135

40 Upstream Memory 2 Bar............... ...... ....... ...... ....... ...... ...... ....... ...............................................135

41 Downstream I/O or Memory 1 and Upstream I/O or Memory 0 Translated Base Register ......136

42 Downstream Memory 0, 2, 3, and Upstream Memory 1 Translated Base Register .................137

43 Downstream I/O or Memory 1 and Upstream I/O or Memory 0 Setup Registers .....................138

44 Downstream Memory 0, 2, 3, and Upstream Memory 1 Setup Registers ................................139

45 Upper 32 Bits Downstream Memory 3 Setup Register.............................................................140

46 Downstream and Upstream Configuration Address Registers.................................................141

47 Downstream Configuration Data and Upstream Configuration Data Registers........................142

48 Configuration Own Bits Register...............................................................................................142

49 Configuration CSR....................................................................................................................143

50 Downstream I/O Address and Upstream I/O Address Registers..............................................144

51 Downstream I/O Data and Upstream I/O Data Registers.........................................................145

52 I/O Own Bits Registers .............................................................................................................145

53 I/O CSR ....................................................................................................................................146

54 Lookup Table Offset Register...................................................................................................146

55 Lookup Table Data Register.....................................................................................................147

56 Upstream Memory 2 Lookup Table .... ....... ...... ....... ...... ...... ....... ...... ....... ..................................147

21555 Non-Transparent PCI-to-PCI Bridge User Manual 7

Page 8

Contents

57 Primary Interface Configuration Space Address Map ..............................................................148

58 Secondary Interface Configuration Space Address Map..........................................................148

59 Vendor ID Register...................................................................................................................148

60 Device ID Register....................................................................................................................148

61 Primary and Secondary Command Registers ..........................................................................149

62 Primary and Secondary Status Registers.................................................................................150

63 Revision ID (Rev ID) Register ..................................................................................................151

64 Primary and Secondary Class Code Registers ........................................................................152

65 Primary and Secondary Cache Line Size Registers.................................................................152

66 Primary Latency and Secondary Master Latency Timer Registers ..........................................153

67 Header Type Register ..............................................................................................................153

68 BiST Register ...........................................................................................................................153

69 Subsystem Vendor ID Register ................................................................................................154

70 Subsystem ID Register.............................................................................................................154

71 Enhanced Capabilities Pointe r Regis ter ....................................... ...... ....... ...... ....... ...... ............154

72 Primary and Secondary Interrupt Line Registers......................................................................154

73 Primary and Secondary Interrupt Pin Registers .......................................................................155

74 Primary and Secondary Minimum Grant Registers..................................................................155

75 Primary and Secondary Maximum Latency Registers..............................................................155

76 Device-Specific Control and Status Address Map....................................................................156

77 Chip Control 0 Register ............................................................................................................156

78 Chip Control 1 Register ............................................................................................................160

79 Chip Status Register.................................................................................................................162

80 Generic Own Bits Register .......................................................................................................164

81 I2O Outbound Post_List Status................................................................................................165

82 I2O Outbound Post_List Interrupt Mask ...................................................................................165

83 I2O Inbound Post_List Status...................................................................................................165

84 I2O Inbound Post_List Interrupt Mask......................................................................................166

85 I2O Inbound Queue..................................................................................................................166

86 I2O Outbound Queue ...............................................................................................................166

87 I2O Inbound Free_List Head Pointer........................................................................................167

88 I2O Inbound Post_List Tail Pointer...........................................................................................167

89 I2O Outbound Free_List Tail Pointer........................................................................................167

90 I2O Outbound Post_List Head Pointer .....................................................................................167

91 I2O Inbound Post_List Counter ................................................................................................168

92 I2O Inbound Free_List Counter................................................................................................168

93 I2O Outbound Post_List Counter .............................................................................................169

94 I2O Outbound Free_List Counter .............................................................................................169

95 Chip Status CSR ......................................................................................................................170

96 Chip Set IRQ Mask Register ....................................................................................................170

97 Chip Clear IRQ Mask Register .................................................................................................171

98 Upstream Page Boundary IRQ 0 Register ...............................................................................171

99 Upstream Page Boundary IRQ 1 Register ...............................................................................172

100 Upstream Page Boundary IRQ Mask 0 Register......................................................................172

101 Upstream Page Boundary IRQ Mask 1 Register......................................................................172

102 Primary Clear IRQ and Secondary Clear IRQ Registers..........................................................173

103 Primary Set IRQ and Secondary Set IRQ Registers ................................................................173

104 Primary Clear IRQ Mask and Secondary Clear IRQ Mask Registers.......................................174

105 Primary Set IRQ Mask and Secondary Set IRQ Mask Registers.............................................174

106 Scratchpad 0 Through Scratchpad 7 Registers........................................................................174

8 21555 Non-Transparent PC I-to-PCI Bridge User Manual

Page 9

Contents

107 Primary Expansion ROM BAR..................................................................................................175

108 Primary Expansion ROM Setup Register .................................................................................176

109 ROM Setup Register.................................................................................................................177

110 ROM Data Register ..................................................................................................................177

111 ROM Address Register.............................................................................................................178

112 ROM Control Register ..............................................................................................................178

113 Mode Setting Configuration Register........................................................................................179

114 Serial Preload Sequence.............. ...................................... ....... ...... ....... ...... ....... ...... ....... ........180

115 Arbiter Control Register............................................................................................................183

116 Primary SERR# Disable Register.............................................................................................184

117 Secondary SERR# Disable Register........................................................................................184

118 Power Management ECP ID and Next Pointer Register ..........................................................185

119 Power Management Capabilities Register................................................................................186

120 Power Management Control and Status Register ....................................................................187

121 PMCSR Bridge Support Extensions.........................................................................................187

122 Power Management Data Register...........................................................................................188

123 Reset Control Register .............................................................................................................188

124 CompactPCI Hot-Swap Capability Identifier and Next Pointer Register...................................189

125 CompactPCI Hot-Swap Control Register..................................................................................189

126 JTAG Instruction Register Options...........................................................................................190

127 Bypass Register........................................................................................................................191

128 Boundary-Scan Register.. ...... ....... ...... ....... ...... ....... ...................................... ....... ...... ....... ........191

129 Boundary Scan Order...............................................................................................................191

130 Vital Product Data (VPD) ECP ID and Next Pointer Register...................................................192

131 Vital Product Data (VPD) Address Register .............................................................................193

132 VPD Data Register ...................................................................................................................193

21555 Non-Transparent PCI-to-PCI Bridge User Manual 9

Page 10

Page 11

Preface 1

A brief description of the contents of this manual follows.

Chapter 1, “Preface” Provides information about the contents and organization of this book.

Chapter 2, “Introduction” Provides an overview of the 21555 functionality and architecture.

Chapter 3, “Signal Descriptions” Describes PCI signal pins grouped by function.

Chapter 4, “Address Decoding” Contains details about how addresses are decoded.

Chapter 5, “PCI Bus Transactions”

Chapter 6, “Initialization

Requirements”

Chapter 7, “Clocking” Describes 21555 clocking support.

Chapter 8, “Parallel ROM

Interface”

Chapter 9, “Serial ROM Interface” Describes the 21555 Serial ROM Interface.

Chapter 10, “Arbitration”

Chapter 11, “Interrupt and

Scratchpad Registers”

Chapter 12, “Error Handling” Describes parity error responses and system error reporting.

Chapter 13, “JTAG Test Port” Explains the implementation of JTAG test port.

Chapter 14, “I2O Support” Explains how the 21555 implements an I20 messaging unit.

Chapter 15, “VPD Support” Describes Vital Product Data support through SROM interface.

Chapter 16, “List of Registers”

Appendix A, “Acronyms” Definition of terms used in this book.

Describes how the 21555 implements

transactions.

Describes the reset operation and initialization requirements.

Describes the 21555 Parallel ROM Interface.

Explains how 21555 implements primary and secondary PCI bus

arbitration.

Describes interrupt support and scratchpad registers.

This chapter contains all of the 21555 register information and contains

a register summary.

the theory of operation about PCI

21555 Non-Transparent PCI-to-PCI Bridge User Manual 11

Page 12

Preface

1.1 Cautions and Notes

Caution: Cautions provid e in for mat ion to prevent damage to equipment or loss of data.

Note: Notes emphasize particularly important info rmation.

1.2 Data Units

This manual uses the following data-unit terminology.

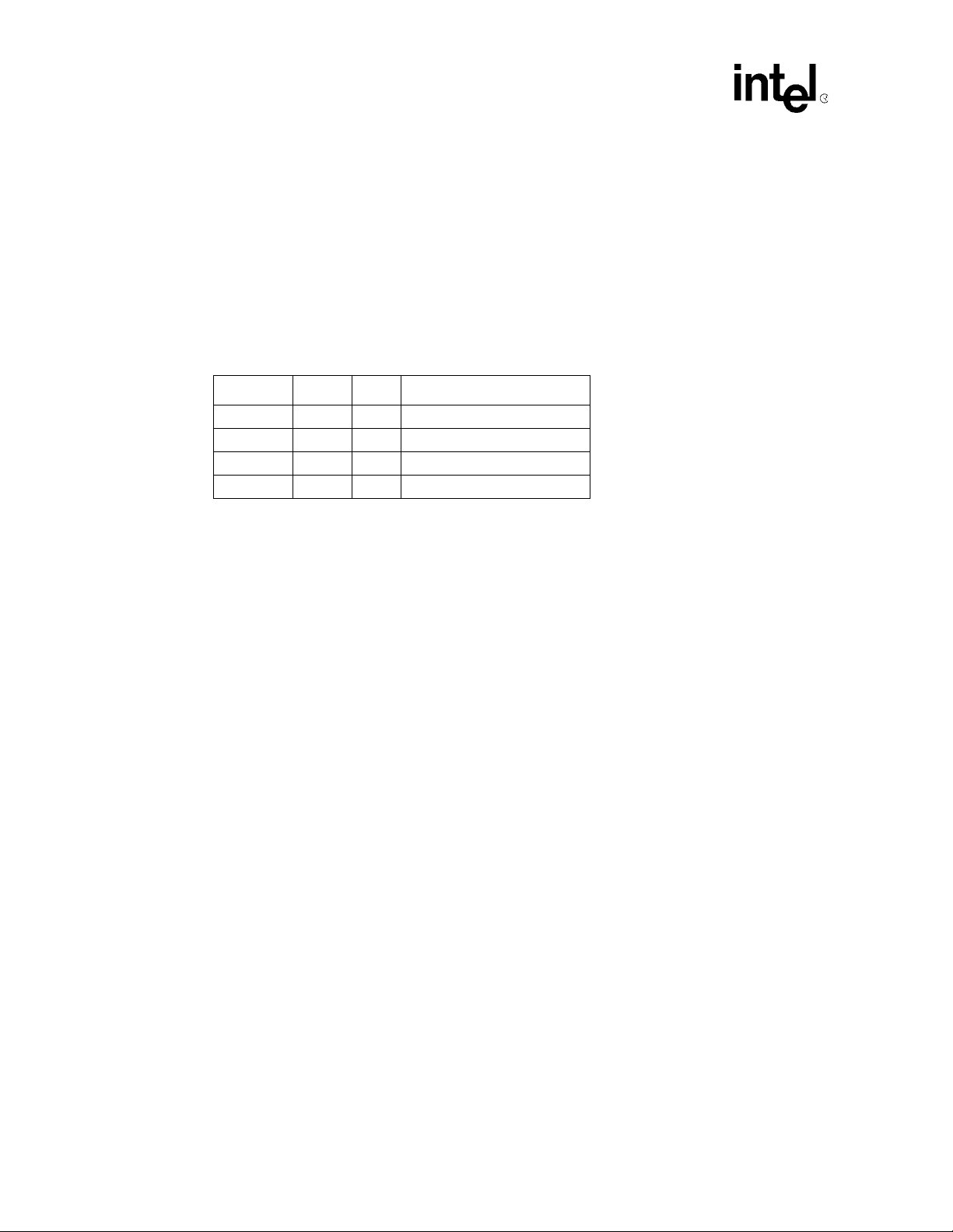

Term Words Bytes Bits

Byte ½ 18

Word 1 2 16

Dword 2 4 32

Quadword 4 8 64

1.3 Numbering

All numbers are decimal unless appended with a radix specifier.

• “h” is the hexadecimal radix.

• “b” is the binary radix.

A range of (numbers, bits, bytes, addresses and so on) within a larger group of numbers is specified with colon (:).

The range may be enclosed in [square brackets] as well.

• The left number is upper limit of the range.

• The right number is the lower limit of the range.

For example: Primary byte offset: 13:10h.

12 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 13

Preface

1.4 Signal Nomenclature

21555 device signal names are printed in lowercase typ e. Prefixes and s uffixes are tagged with a leading or trailing

letter and are delimited with an “_” underscore:

• The prefix “p_” denotes a primary bus signal. F or example: p_ad is the primary interface address/data bus.

• The prefix “s_” denotes a secondary bus signal. For example: s_ad is the secondary interface address/data bus.

• Other prefixes might appear. l_(load), pr_(parallel rom), and so on.

• The suffix “_l” means that the condition is qualified when that signal is low or approximately zero (0) volts.

For example: p_frame_l is a low-asserted signal.

• If no suffix is applied, it means that the condition is qualified when the signal is high or approximately equal to

vcc. For example: p_idsel is a high-asserted signal.

PCI signals that can be on either the primary interface or the secondary interface are printed in uppercase, normal

type. The names of low-asserted signals are followed by #. For example, “asserting FRAME#” can refer to the

assertion of the p_frame_l signal when the transaction is occurring on the primary bus or the assertion of the

s_frame_l signal when the transaction is occurring on the secondary bus.

Table 1 describes the Signal Type letter s th at ap pear in Table 6 through Table 10 in Chapter 3, “Signal

Descriptions”.

Table 1. Signal Type Abbreviations

Signal

Type

I Standard input only.

O Standard output only.

TS Tristate bidirectional.

STS

OD Standard open drain.

Description

Sustained tristate. Active low signal must be pulled high for one clock

cycle when deasserting.

21555 Non-Transparent PCI-to-PCI Bridge User Manual 13

Page 14

Preface

1.5 Register Abbreviations

When a register is associated with the primary interface, its name is preceded with Primary. When a register is

associated with the secondary interface, its name is preceded with Secondary. When a register is shared by both

interfaces, it is not preceded with Primary or Secondary. The byte offsets at which each register can be accessed

from each interface are listed in each register description.

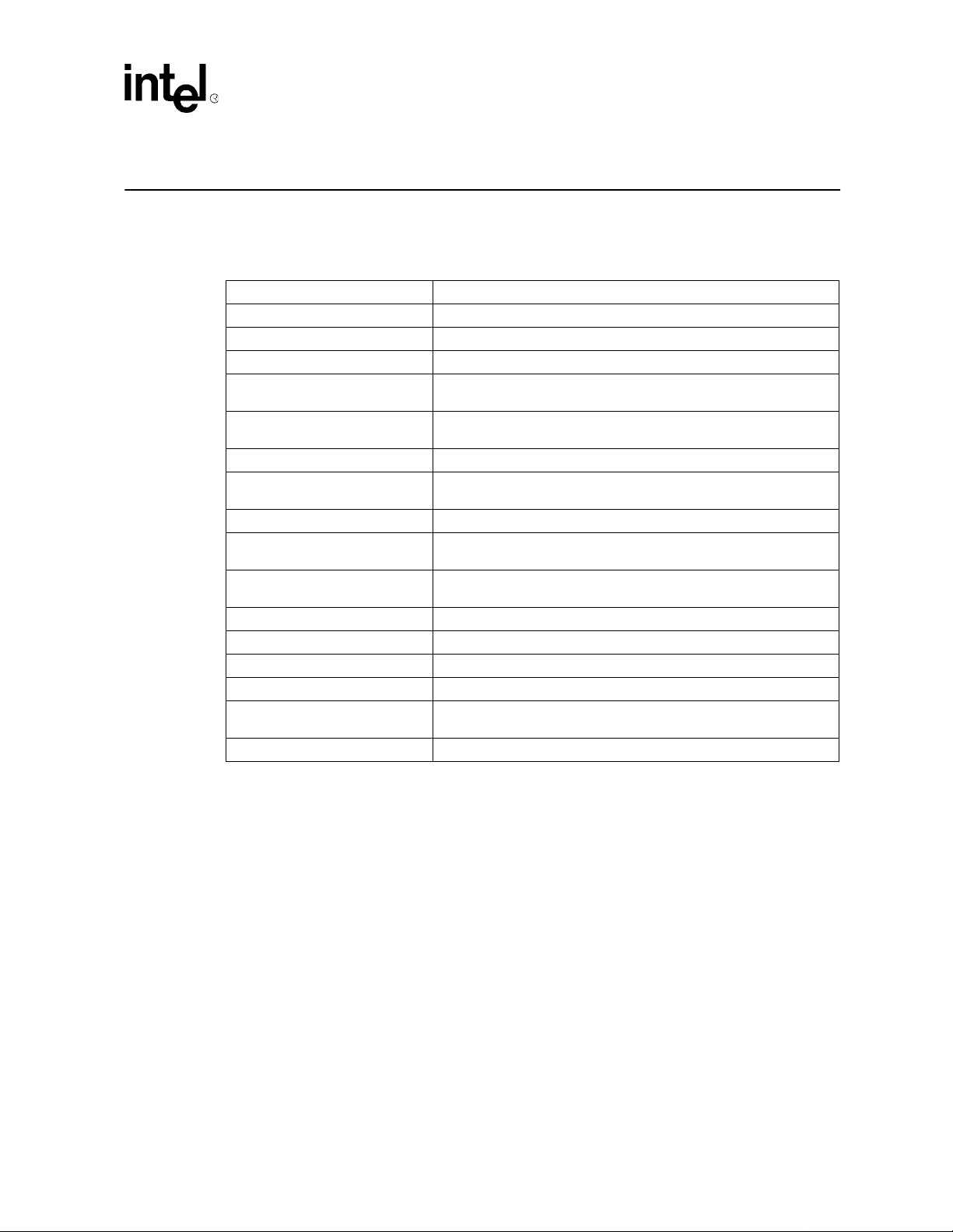

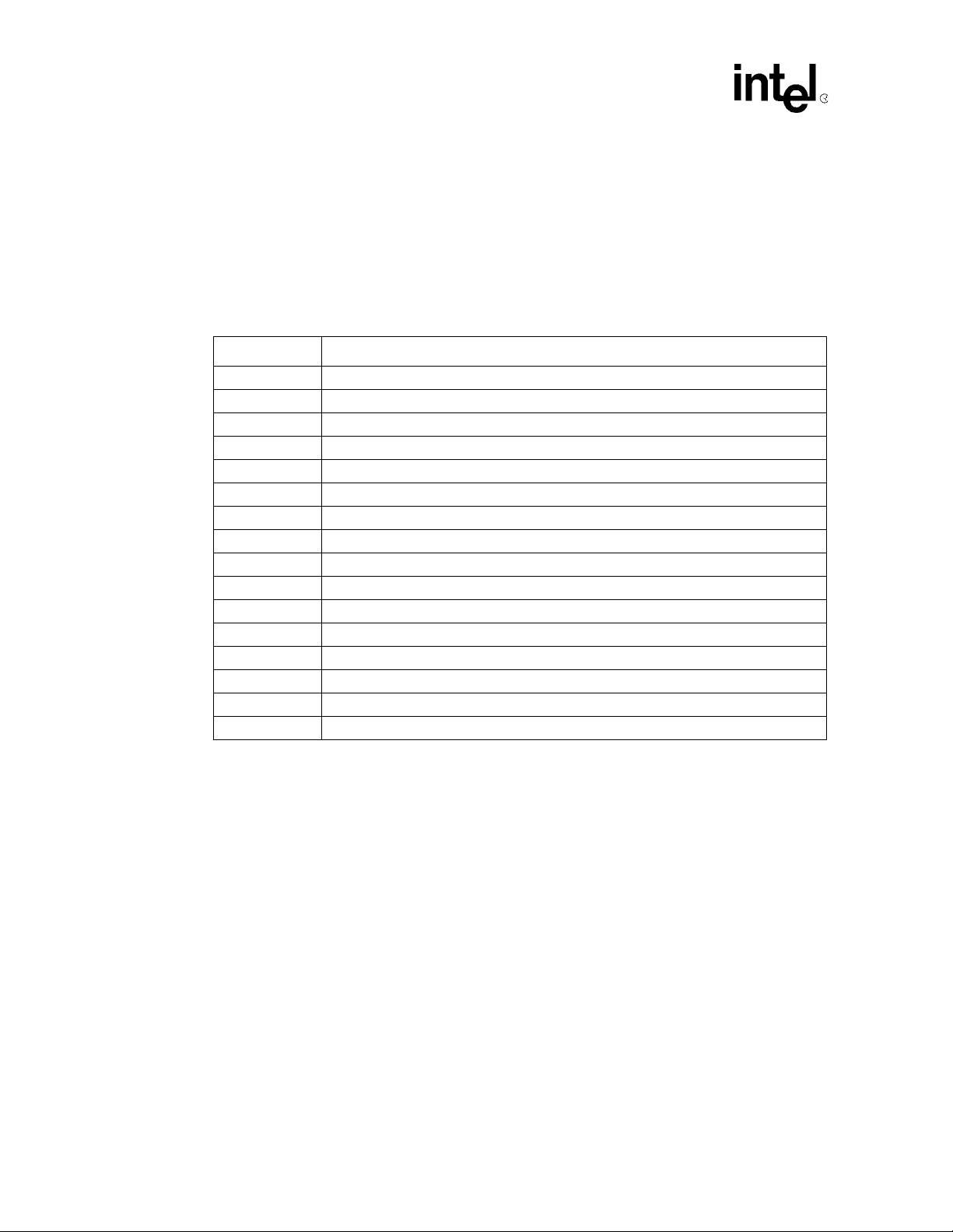

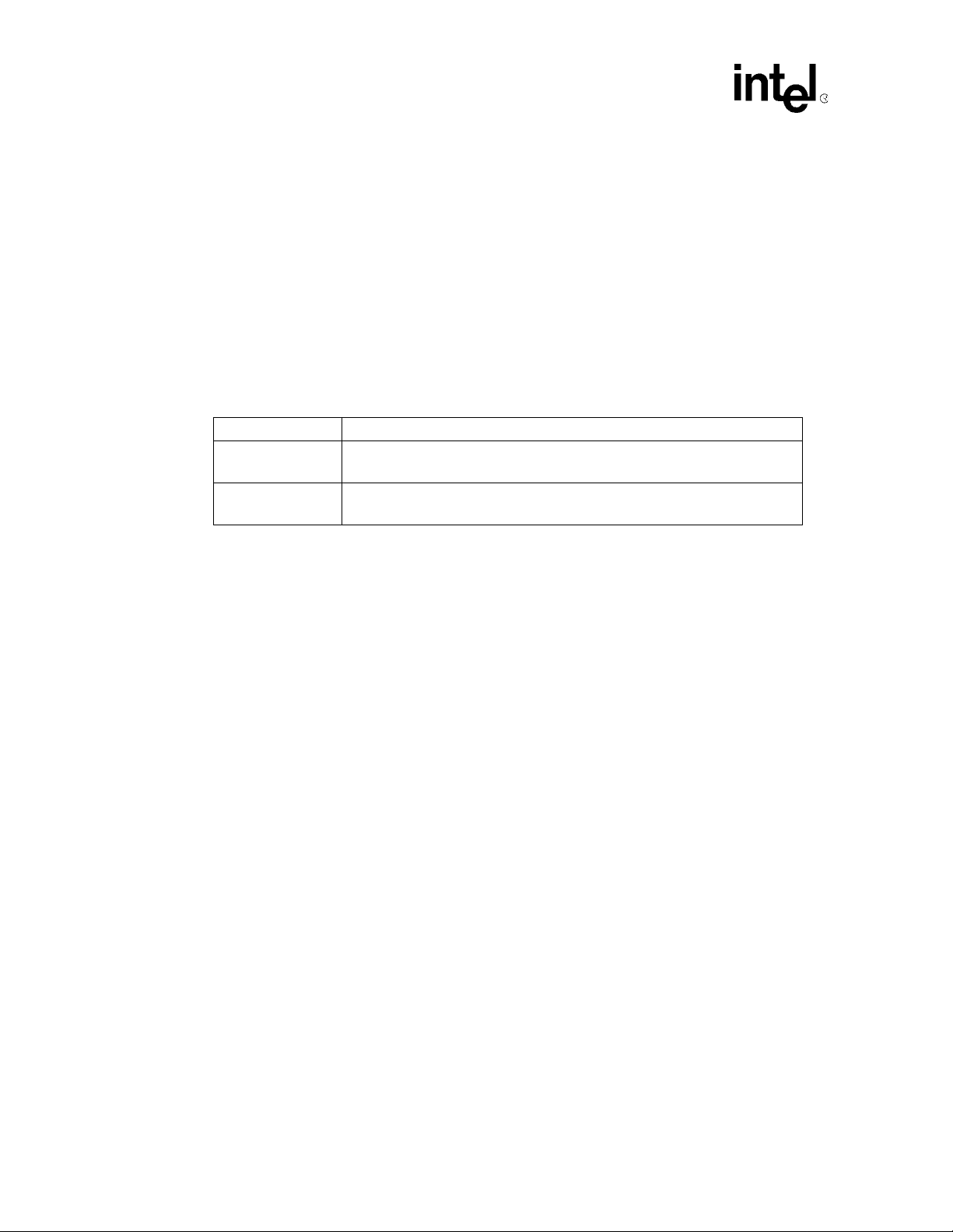

Table 2 lists the register access abbreviations.

Table 2. Register Abbreviations

Access Type Description

DCA Downstream configuration address.

DCD Downstream configuration data.

DIA Downstream I/O address.

DID Downstream I/O data

R Read only. Writes have no effect.

R/W Read/Write.

R/W1TC Read. Write 1 to clear.

R/W1TS Read. Write 1 to set.

R0TS Read 0 to set.

R/(WS) Read. Write from secondary interface only. Primary bus writes have no effect.

R/(WP) Read. Write from primary interface only. Secondary bus writes have no effect.

UCA Upstream configuration address.

UCD Upstream configuration data.

UIA Upstream I/O address.

UID Upstream I/O data .

W1TL Write 1 to load.

14 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 15

Introduction 2

The Intel® 21555 is a PCI peripheral devi ce t hat perf orm s P CI bridg i ng f unct ion s f or em bedd ed and i ntel lig ent I/O

applications. The 21555 has a 64-bit primary interface, a 64-bit secondary interface, and 66-MHz capability. In this

document the 21555 non-transparent device is compared to the related 21154 transparent devices. Both devices

have similar operating characteristic.

The 21555 is a “non-transparent” PCI-to-PCI Bridge (PPB) that acts as a gateway to an intelligent subsystem. It

allows a local processor to independently configu re and contr ol the local s ubsy stem. The 2 155 5 imp lem ents an I2 0

message unit that enables any local processor to function as an intelligent I/O processor (IOP) in an I20-capable

system. Since the 21555 is architecture independent, it works with any ho st an d local p rocess ors that s upp ort a PCI

bus. This architecture independence enables vendors to leverage existing investments while moving products to

PCI technology.

Unlike a transparent PPB, the 21555 is specifically designed to bridge between two processor domains. The

processor domain on the primary interface of the 21555 is referred to as the host domain, and its processor is the

host processor. The secondary bus interfaces to the local domain and the local processor. Special features include

support of:

• Independent primary and secondary PCI clocks. See Chapter 7.

• Independent primary and secondary address spaces.

• Address translation between the primary (host) and secondary (local) domains. See Chapter 4.

The 21555 allows add-in card vendors to pres ent a higher level of abstraction to the host system than is possible

with a transparent PPB. The 21555 uses a Type 0 configuration header, which presents the entire subsystem as a

single “device” to the host processor. This allows loading of a single device driver for the entire subsystem, and

independent local processor initialization and control of the subsystem devices. Since the 21555 uses a Typ e 0

configuration header, it does not require hierarchical PPB configuration code.

The 21555 forwards transactions between the primary and secondary PCI buses as does a transparent PPB. In

contrast to a transparent PPB, the 21555 can translate th e add ress o f a f orward ed tr ansa ction fr om a sy stem addr ess

to a local address, or vice versa. This mechanism allows the 21555 to hide subsystem resour ces from the host

processor and to resolve any resource conflicts that may exist between the host and local subsystems.

The 21555 operates at 3.3 V, but is also 5.0 -V I/ O to lera nt. A dap ter cards des i gned for th e 215 55 can be keyed as a

PCI universal card edge connector, permitting use in either a 5-V or 3-V slot.

2.1 Comparing a 21555 to a Transparent PPB

The 21555 is functionally similar to a transparent PPB in that both provide a connection path between devices

attached to two independent PC I buses. A 21555 and a PPB allow the electrical loading of devices on one PCI bus

to be isolated from the other bus while permitting concurrent operation on both buses. Since the PCI Local Bus

Specification restricts PCI option cards to a single electrical load, the ability of PPBs and the 21555 to spawn PCI

buses enables the design of multi-device PCI option cards. The key difference between a PPB and the 21555 is that

the presence of a PPB in a connection path between the host processor and a device is transparent to devices and

device drivers, while the presence of the 21555 is not. This difference enables the 21555 to provide features that

better support the use of intelligent controllers in the subsystem.

21555 Non-Transparent PCI-to-PCI Bridge User Manual 15

Page 16

Introduction

A primary goal of the PPB architecture is that PPB are transparent to devices and device drivers. For example, no

changes are needed to a device driver when a PCI peripheral is located behind a PPB. Once configured during

system initialization, a PPB operates without the aid of a device driver. A PPB does not require a device driver of its

own since it does not have any resources that must be managed by software dur ing run-time. This requirement for

transparency forced the usage of a flat addressing model across PPBs. This means that a given physical address

exists at only one location in the PCI bus hierarchy and that this location may be accessed by any d evice attached at

any point in the PCI bus hierarchy. As a consequence, it is not possible for a PPB to isolate devices or address

ranges from access by devices on the opposite interface of a PPB. The PPB architecture assumes that the resources

of any device in a PCI system are configured and managed by the host processor.

Figure 1 shows a hypothetical PCI add-in card used for an intelligent controller application. In some applications

the transparency of a PPB is not desired. For example,

Figure 1. 21555 Intelligent Controller Application

Intelligent Subsystem

Local

CPU

DRAM/

ROM

CPU-

PCI

Bridge

PCI

Device

PCI Bus

PCI

Device

Intel

21555

Device

PCI

Device

®

PCI Bus

Host

Core

Logic

Memory

Host

CPU

A8826-01

Assume:

• That the local processor on the add-in card is used to manage the resources of the devices attached to the add- in

card’s local PCI bus.

• That it is desirable to restrict access to these same resources from other PCI bus masters in the system and from

the host processor.

• That there is a need to resolve address conflicts that may exist between the hos t system and the local processor.

The non transparency of the 21555 is perfectly suited to this kind of configuratio n, where a transpar ent PPB woul d

be problematic.

Since the 21555 is non transparent, the device driver for the add-in card must be aware of the pres ence of the 21555

and manage its resources appropriately. The 21555 allows the entire subsystem to appear as a single virtual device

to the host. This enables configuration software to identify the appropriate driver for the subsystem.

With a transparent PPB, a driver does not need to know about the presence of the bridge and manage its resources.

The subsystem appears to the host system as individual PCI devices on a secondary PCI bus, not as a single virtual

device.

16 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 17

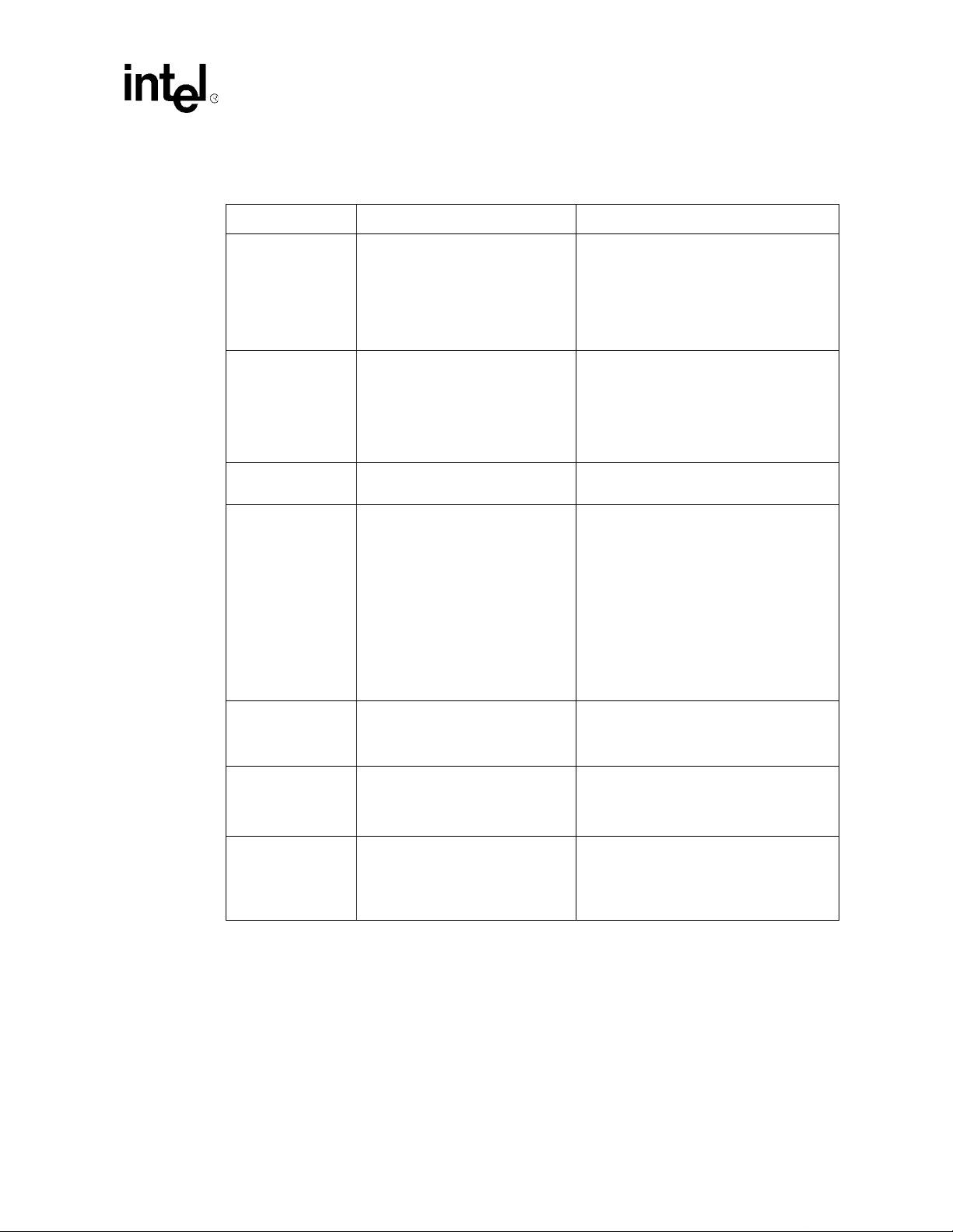

Table 3 shows compares a 21555 and to a transparent PPB.

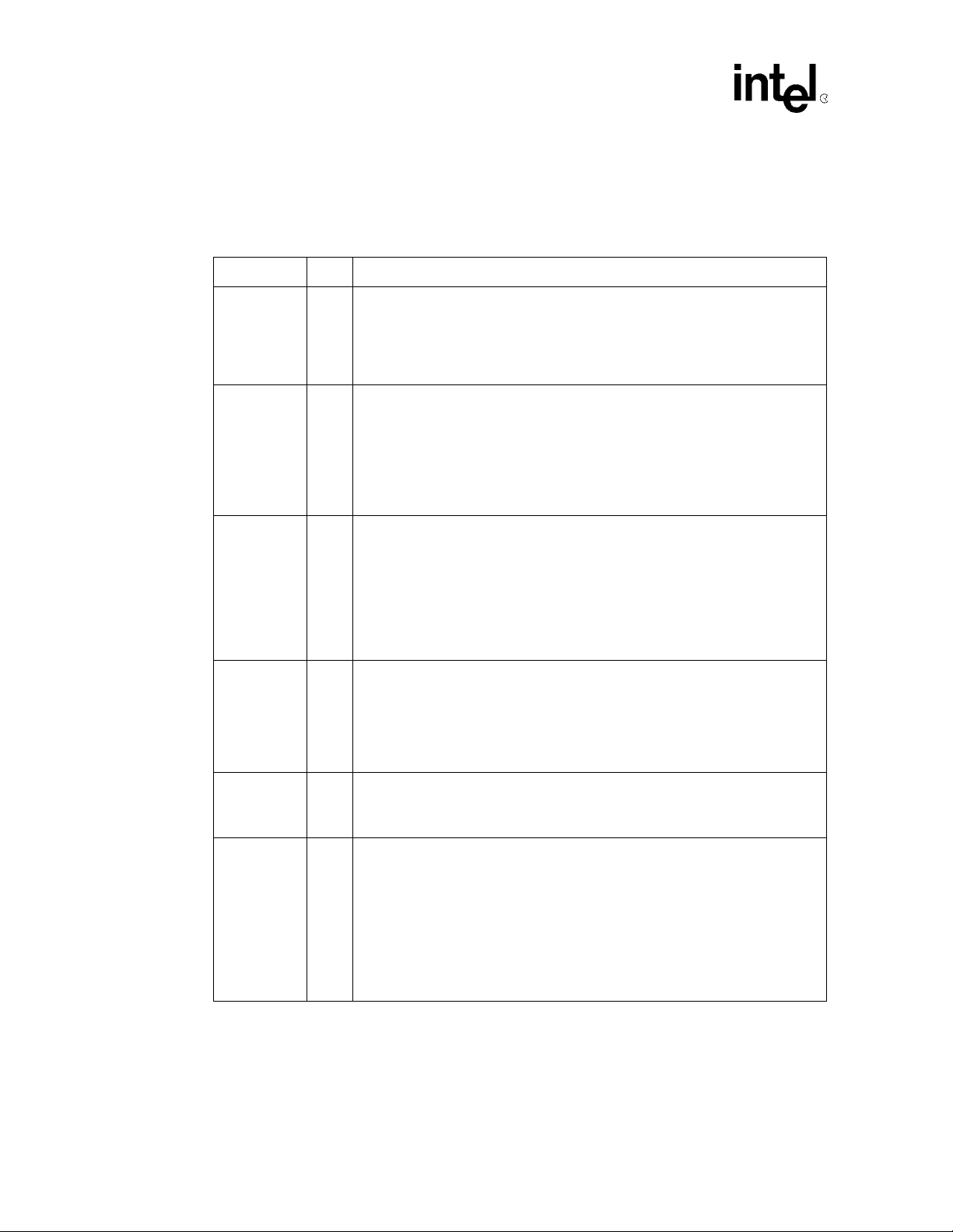

T a ble 3. 21555 and PPB Feature Comparison

Feature Non-Transparent PPB or 21555 Transparent PPB

Introduction

Transaction

forwarding

Address decoding

Address

translation

Configuration

-time resources

Run

Clocks

Secondary bus

central functions

• Adheres to PPB ordering rules.

• Uses posted writes and delayed

transactions.

• Adheres to PPB transaction error

and parity error guidelines,

although some errors may be

reported differently .

• Base address registers (BARs)

are used to define independent

downstream and upstream

forwarding windows.

• Inverse decoding is only used for

upstream transactions above the

4GB boundary.

Supported for both memory and I/O

transactions.

• Downstream devices are not

visible to host.

• Does not require hierarchical

configuration code (Type 0

configuration header).

• Does not respond to Type 1

configuration transactions.

• Supports configuration access

from the secondary bus.

• Implements separate set of

configuration registers for the

secondary interface.

Includes features such as doorbell

interrupts, I20 message unit, and so

on, that must be managed by the

device driver.

Generates secondary bus clock

output.

Asynchronous secondary clock input

is also supported.

Implements secondary bus arbiter.

This function can be disabled.

Drives secondary bus AD, C/BE#,

and PAR during reset. This function

can be disabled.

• Adheres to PPB ordering rules.

• Uses posted writes and delayed

transactions.

• Adheres to PPB transaction error and

parity error guidelines.

• PPB base and limit address registers are

used to define downstream forwarding

windows.

• Inverse decoding for upstream

forwarding.

None. Flat address model is assumed.

• Downstream devices are visible to host.

• Requires hierarchical configuration code

(Type 1 configuration header).

• Forwards and converts Type 1

configuration transactions.

• Does not support configuration access

from the secondary bus. Same set of

configuration registers is used to control

both primary and secondary interfaces.

Typically has only configuration registers; no

device driver is required.

Generates one or more secondary bus clock

outputs.

Implements secondary bus arbiter.

Drives secondary bus AD, C/BE#, and PAR

during reset.

21555 Non-Transparent PCI-to-PCI Bridge User Manual 17

Page 18

Introduction

2.2 Architectural Overview

This section describes the buffers, registers, and control logic of the 21555:

2.2.1 Data Buffers

Data buffers include the buffers along with the associated data path control logic. Delayed transaction buffers

contain the compare functionality for completing delayed transactions. The blocks also contain the watchdog timers

associated with the buffers. The data buffers are as follows:

• Four-entry downstream de layed trans action buffer.

• Four-entry upstream d elayed transaction buffer.

• 256-byte downstream posted write buffer.

• 256-byte upstream posted write buffer.

• 256-byte downstream read dat a buffer.

• 256-byte upstream read data buffer.

• T w o downs t ream I20 delayed transacti on ent rie s.

2.2.2 Registers

The following register blocks also contain address decode and translation logic, I20 message unit, and interrupt

control logic:

• Primary interface header Type 0 configuration registers.

• Secondary interface header Type 0 configuration registers.

• Device-specific configuration registers.

• Memory and I/O mapped control and status registers.

2.2.3 Control Logic

• The 21555 has the following control logic:

• Primary PCI target control logic.

• Primary PCI master control logic.

• Secondary PCI target control logic.

• Secondary PCI master control logic.

• ROM interface control logic for both serial and parallel ROM connections (interfaces between the ROM

registers and ROM signals).

• Secondary PCI bus arbiter interface to secondary bu s device request and grant lines, as well as the 21555

secondary master control logic.

• JTAG control logic.

18 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 19

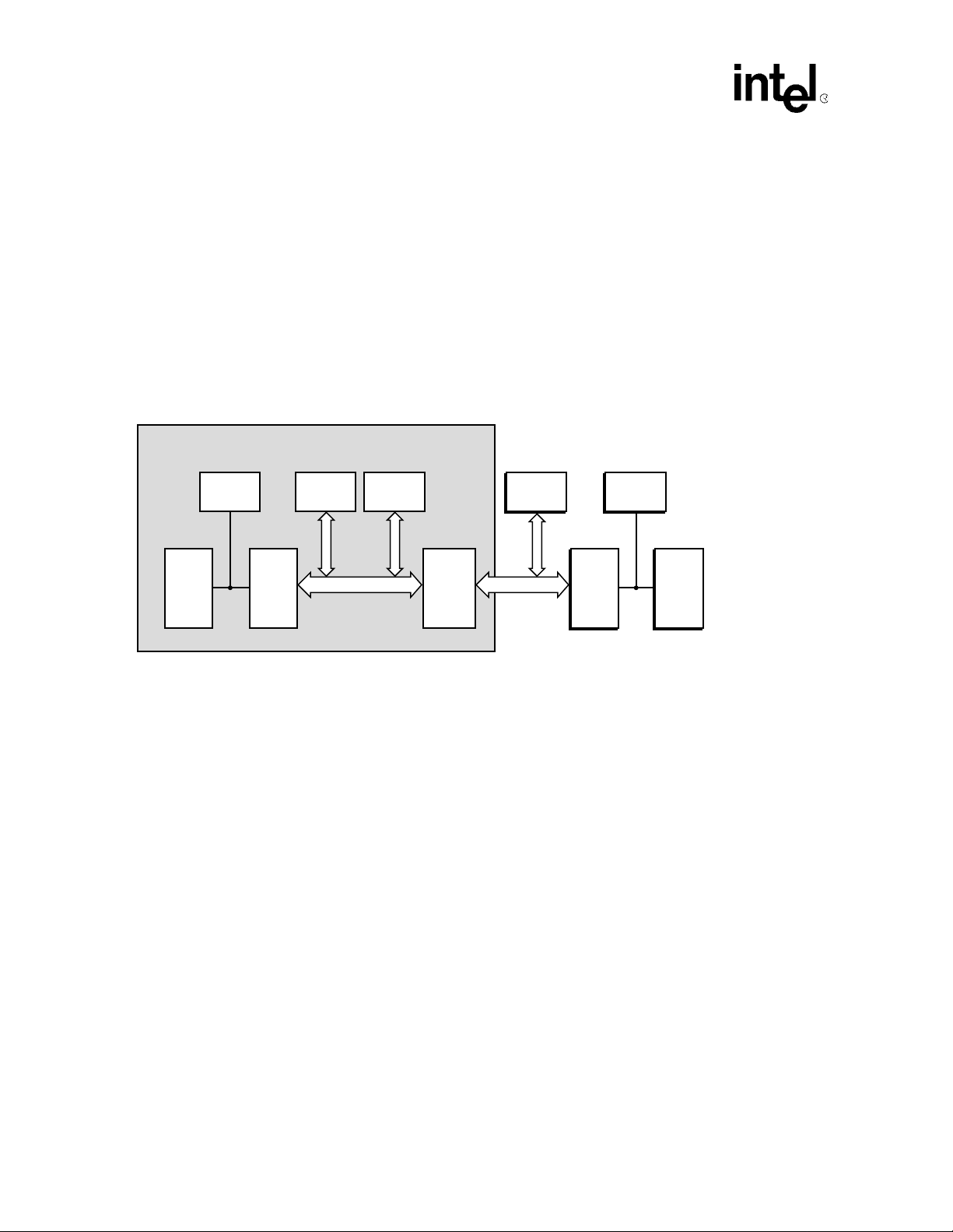

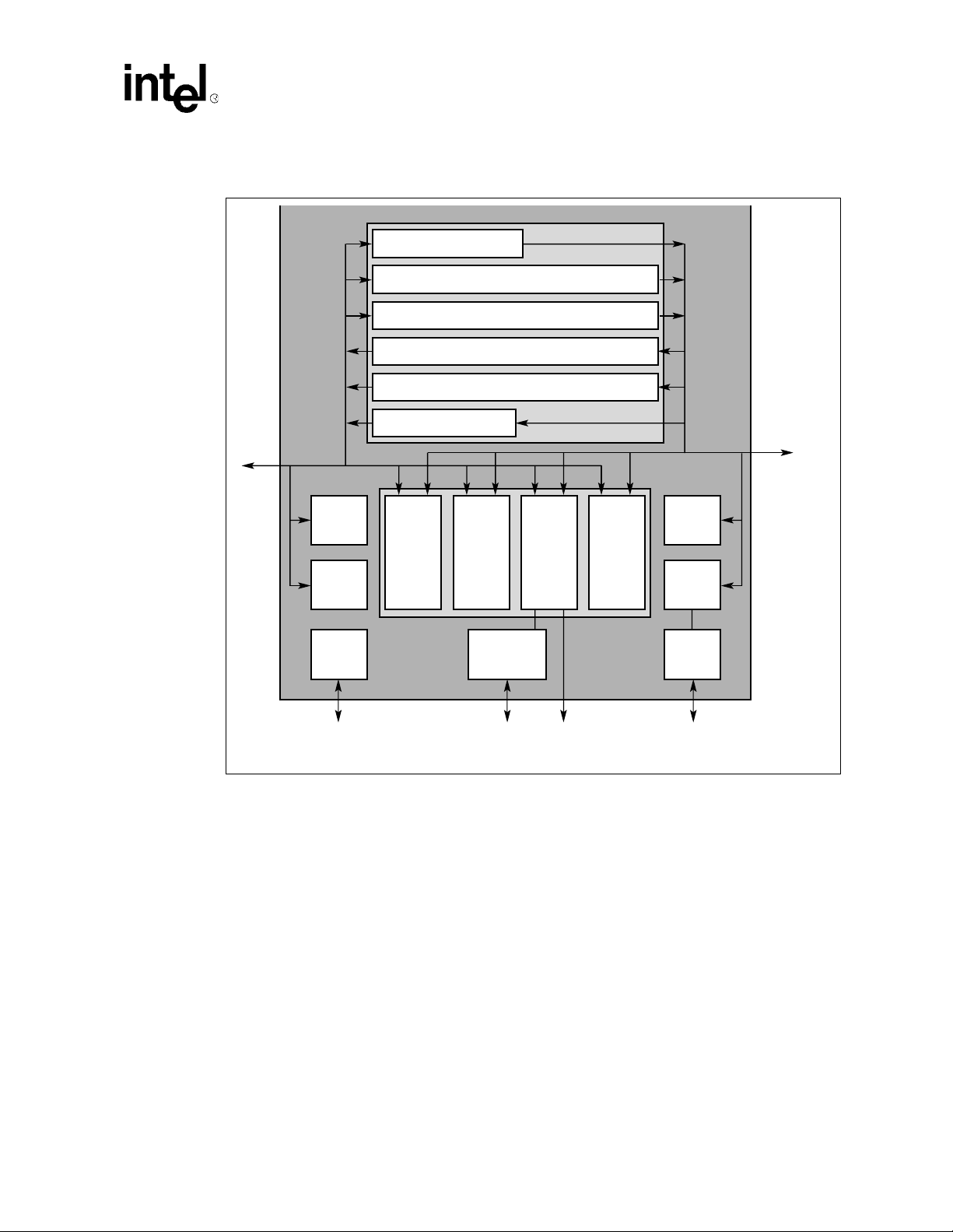

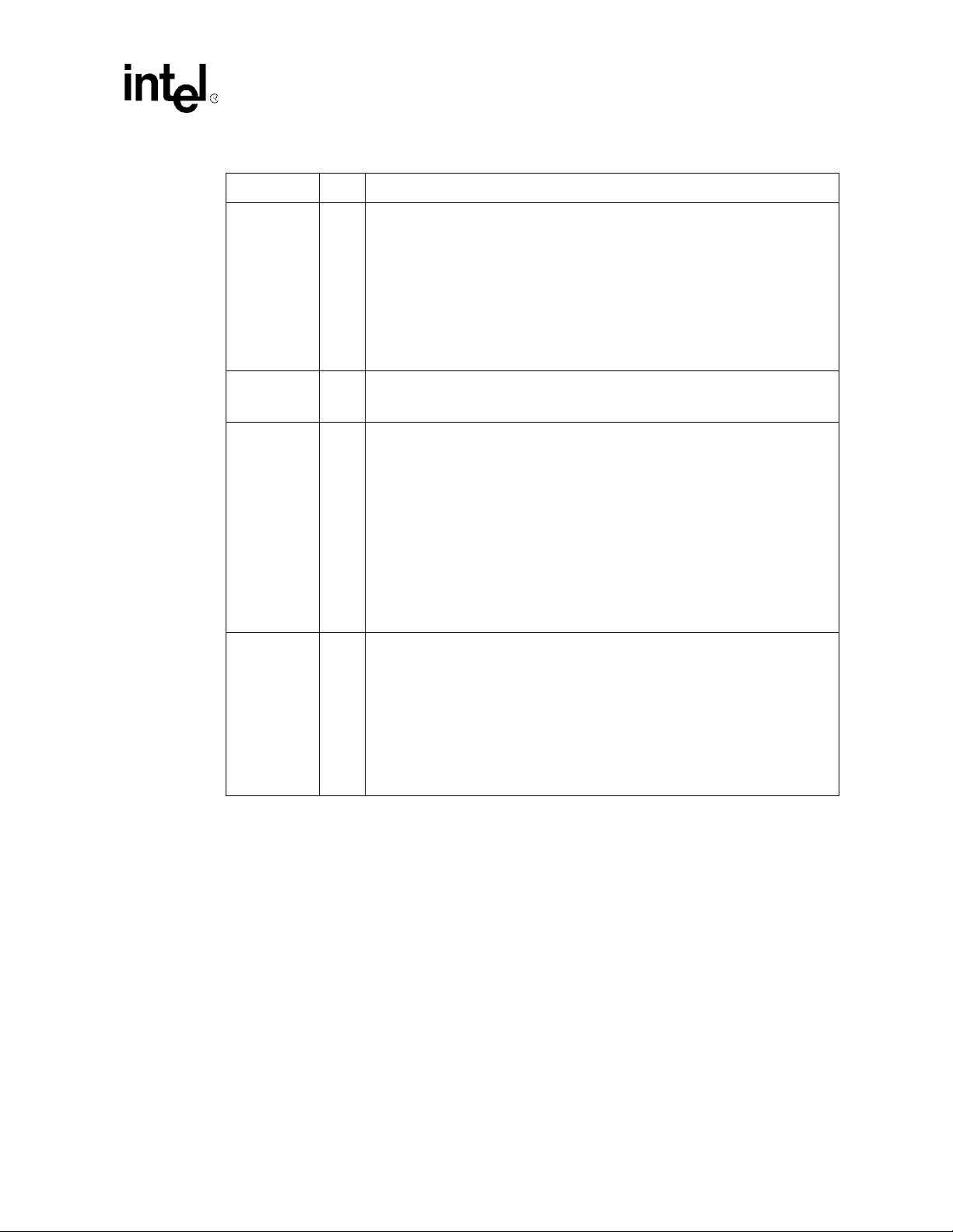

Figure 2 shows the 21555 microarchitecture.

Figure 2. 21555 Microarchitecture

21555

21555

Downstream Delayed Buffer

Downstream Posted Write Buffer

Upstream Read Data Buffer

Downstream Read Data Buffer

Upstream Posted Write Buffer

Introduction

rimary

PCI

Bus

Primary

Target

Control

Primary

Master

Control

JTAG

JTAG Signals

Upstream Delayed Buffer

Primary

Config

Registers

DeviceSpecific

Config

Registers

ROM Interface

ROM

Interface

Control

Signals

CSR

Registers

Interrupt

Signals

Secondary

Config

Registers

Secondary

PCI

Bus

Secondary

Target

Control

Secondary

Master

Control

Secondary

Bus

Arbiter

Secondary Arbiter

Signals

A7418-01

21555 Non-Transparent PCI-to-PCI Bridge User Manual 19

Page 20

Introduction

2.3 Special Applications

2.3.1 Primary Bus VGA Support

The 21555 provides hardware support that allows configuration of itself as a Video Graphics Adapter (VGA)

device. The primary class code should be preloaded through the serial ROM (SROM) or loaded by the local

processor with the value for a VGA device (Base Class 03h, Sub-Class 00h, Programming Interface 00h). This

allows the 21555 to present itself to the host as a VGA device.

The VGA Mode field in the Chip 0 Control register (see page 156) should be set to 01b to enable decoding of VGA

transactions on the primary bus for forwarding to the secondary bus. These bits can be set through SROM preload,

or either from a primary or secondary bus configuration write. Table 4 gives addresses that are decoded.

Table 4. Decoded and Not Decoded Addresses

Memory addresses [000BFFFFh : 000A0000h]

I/O addresses:

Bits not decoded.

AD[9:0]3BBh:3B0h

3DFh:3C0h

AD[31:16]000h

(No address translation is performed on these addresses.)

The 21555 cannot be enabled as a snooping agent on the primary bus. This is because the 21555 cannot guarantee

that it can buffer and forward all palette writes, since the 21555 has finite buffer space and no backoff mechanism

when snooping. The 21555 should not be configured to appear as a VGA device in those applications where it may

try to configure the 21555 as a snooping agent.

The parallel ROM can be used to store VGA BIOS code, which is mapped through the Primary Expansion ROM

BAR.

2.3.2 Secondary Bus VGA Support

The 21555 can be enabled to decode VGA transactions on the secondary bus for forwarding to the primary bus.

This is done by setting the VGA Enable field in the Chip Control 0 register to 10b. The addres ses that are decoded

are the same as for the primary VGA decode, and again the addresses are not translated.

Upstream forwarding of VGA transactions can be useful for applications that want to allow access to a primary bus

VGA device frame buffer by local processors in intelligent I/O or embedded subsystems.

Note: VGA decoding must not be enabled for both the pr imary and secondary interface. The value 11b is

illegal for the VGA Enable field and can yield unpredictable results.

2.4 Programming Notes

2.4.1 Addressing

The non-transparent addressing model that the 21555 uses can cause problems if not programmed properly.

Programming errors include:

20 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 21

Introduction

• Setting a translated base address for a downstream range to fall within an address range defined for upstream

forwarding. This would cause the 21555 to respond as a target on the secondary bus to a downstream

transaction that it has initiated as a master. The transaction would then be forwarded back to the primary bus.

The address on the primary bus depends on the translated base address value for that upstream range.

• Setting a translated base address for an upstream range to fall within an add ress r a nge for down stream

forwarding. This results i n similar behavior described in the previous condition, but in the opposite direction.

• Enabling I/O subtractive decoding in both directions. When an I/O transaction is subtractively decoded on the

primary bus and forwarded downst r eam by t he 2 155 5, and no t arget responds on the secondary bus, the 21555

subtractively decodes the transaction on the secondary bus and forwards it back upstream. Since there is no

address translation for subtractively decoded I/O trans actions, this results in the 21555 forwarding the

transaction downstream and upstream forever.

• Enabling VGA decoding in both directions. Refer to subtractive I/O decoding in the previous bullet. Again,

there is the case of a non translated I/O address decoded by the 21555 on both interfaces as a target and

forwarded to the opposite interface.

2.4.2 Transaction Forwarding

When using the indirect I/O transaction generation mechanism, the low tw o bits of the I/O address in the I/O

Address register must match the byte enables as described in the PCI Local Bus Specification, Revision 2.2. The

21555 does not correct any discrepancies between the byte enables and address bits [1:0].

2.4.3 ROM Access

Parallel and SROM access mechanisms do not accommodate multiple masters. That is, when more than one master

attempts to access the ROM during the same time period, wrong data may be returned or written to the ROM. There

is no semaphore method to guarantee atomicity of the ROM address, data, and control register accesses.

This also applies to a parallel ROM access through the Primary Expansion ROM BAR at the same time a secondary

bus master might be accessing ROM registers.

21555 Non-Transparent PCI-to-PCI Bridge User Manual 21

Page 22

Page 23

Signal Descriptions 3

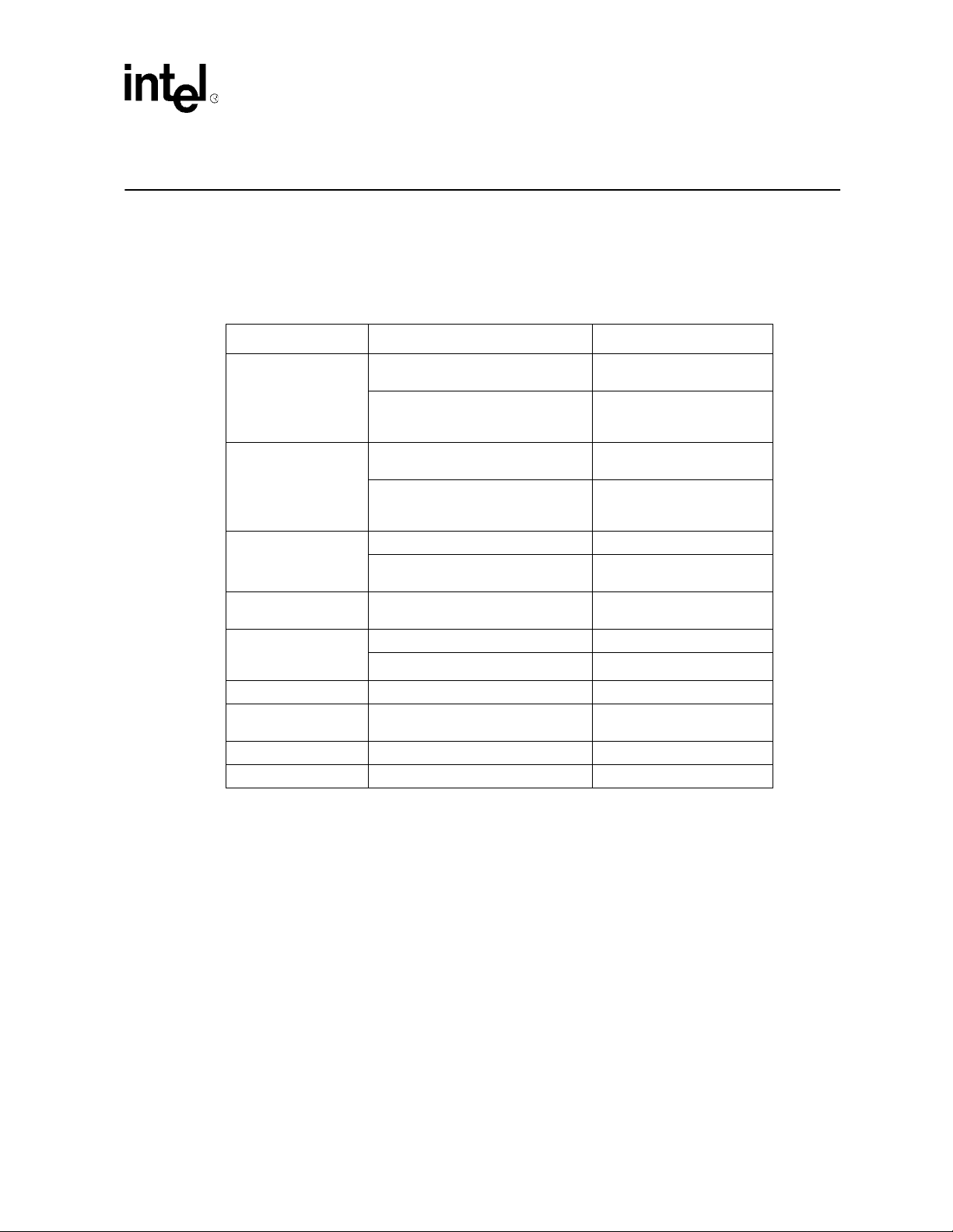

This chapter presents the theory of operation info rmation about the PCI sign al interface. See Chapter 16 for specific

information about PCI registers. Table 5 describes the PCI signal groups, function, and provides a page reference.

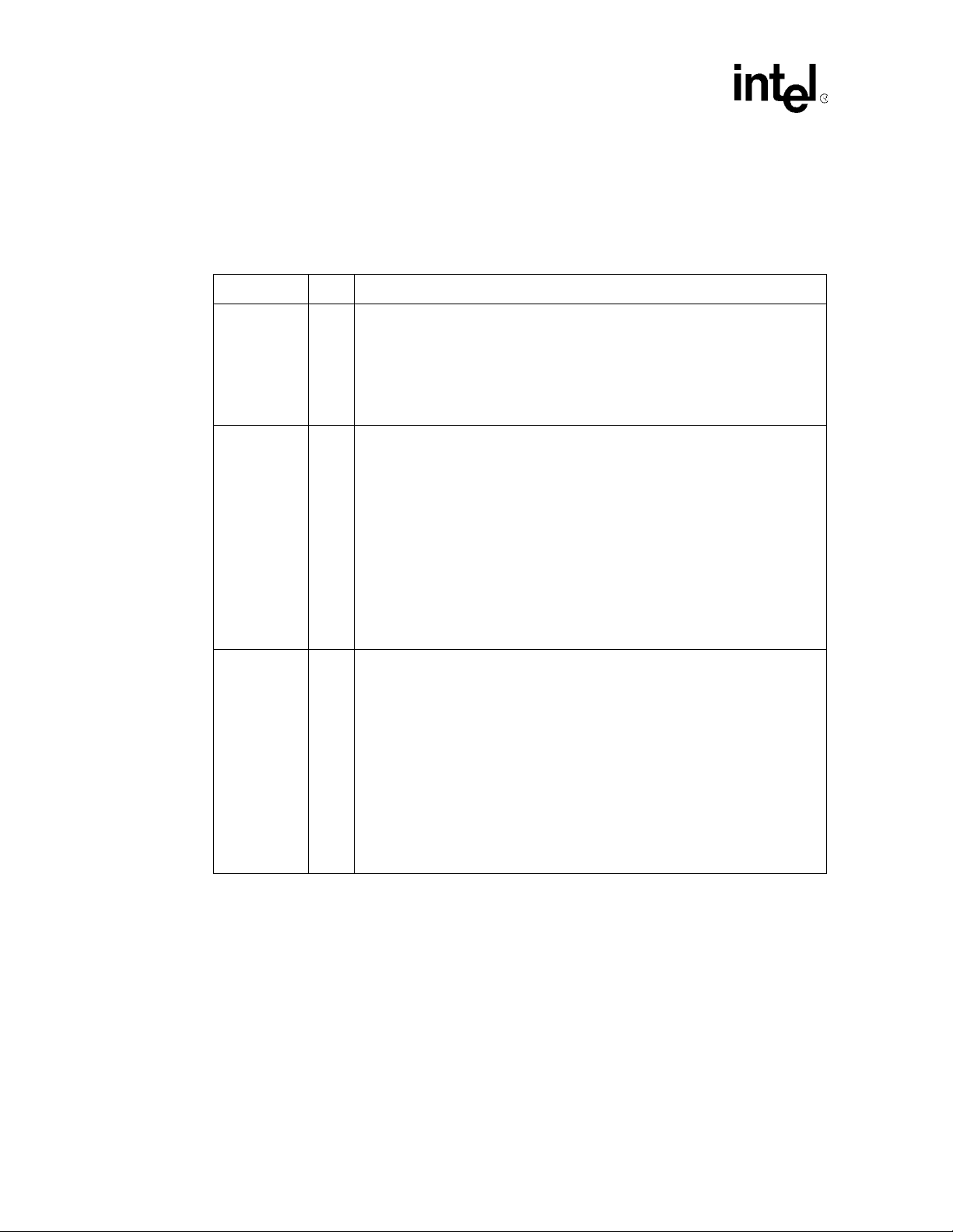

Table 5. Signal Pin Functional Groups

Group by Signal Pin Description See Page

All PCI pins required by the PCI Local

Primary Bus and

Extension interface

Signal Pins

Secondary Bus and

Extension Interface

Signal Pins

Miscellaneous Signal

Pins

Timing

Optional configuration

and expansion

memory.

Arbitration Primary PCI Bus Arbitration Signals Section 10.1 on page 97

Interrupt

Error Error Signals Section 12.1 on page 105

Test Access Port JTAG Signals Section 13.1 on page 111

Bus Specification, Revision 2.2.

All PCI 64-bit extension pins required

by the PCI Local Bus Specification,

Revision 2.2.

All PCI pins required by the PCI Local

Bus Specification, Revision 2.2.

All PCI 64-bit extension pins required

by the PCI Local Bus Specification,

Revision 2.2.

Two input voltage signaling pins. Section 3.5 on page 31

Power Management, Hot-Swap, and

Reset Signals

Primary and Secondary PCI Bus

Clock Signals

Interface Signals Section 8.1 on page 81

SROM Interface Signals Section 9.1 on page 91

Primary and Secondary PCI Bus

Interrupt Signals

Section 3.1 on page 24

Section 3.2 on page 26

Section 3.3 on page 28

Section 3.4 on page 30

Section 6.1 on page 65

Section 7.1 on page 77

Section 11.1 on page 101

21555 Non-Transparent PCI-to-PCI Bridge User Manual 23

Page 24

Signal Descriptions

3.1 Primary PCI Bus Interface Signals

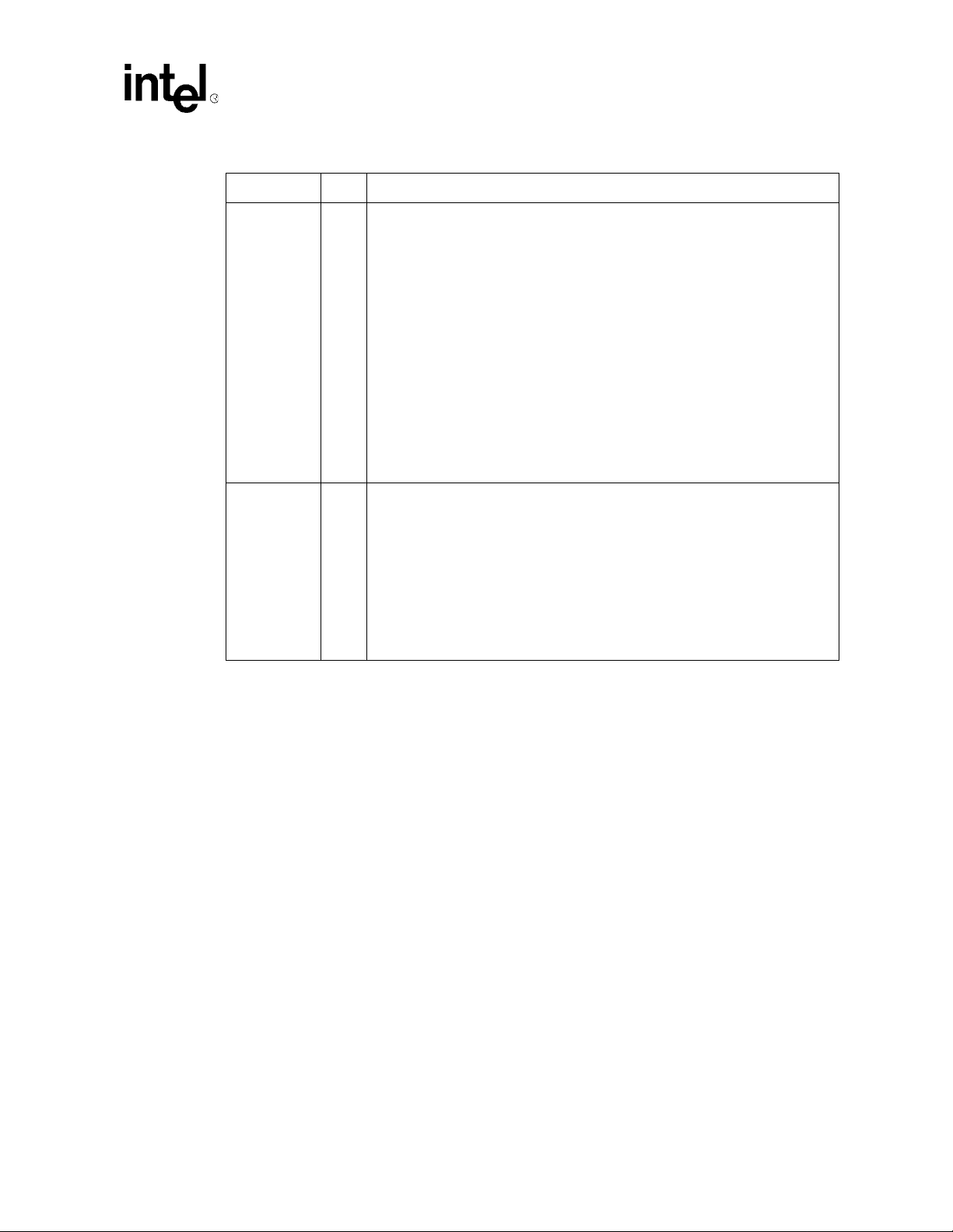

Table 6 describes the primary PCI bus interface signals. The letters in the “Type” column are described in Table 1.

T able 6. Primary PCI Bus Interface Signals (Sheet 1 of 2)

Signal Name Type Description

Primary PCI interface address and data. These signals are a 32-bit multiplexed

address and data bus. During the address phase or phases of a transaction, the

p_ad[31:0] TS

p_cbe_l[3:0] TS

p_devsel_l STS

p_frame_l STS

p_idsel I

p_irdy_l STS

initiator drives a physical address on p_ad[31:0].

During the data phases of a transaction, the initiator drives write data, or the target

drives read data, on p_ad[31:0]. When the primary PCI bus is idle, the 21555 drives

p_ad to a valid logic level when p_gnt_l is asserted.

Primary PCI interface command and byte enables. These signals are a multiplexed

command field and byte enable field. During the address phase or phases of a

transaction, the initiator drives the transaction type on p_cbe_l[3:0].

When there are two address phases, the first address phase carries the

dual-address command and the second address phase carries the transaction type.

For both read and write transactions, the initiator drives byte enables on

p_cbe_l[3:0] during the data phases. When the primary PCI bus is idle, the 21555

drives p_cbe_l to a valid logic level when p_gnt_l is asserted.

Primary PCI interface DEVSEL#. Signal p_devsel_l is asserted by the target,

indicating that the device is responding to the transaction. As a target, the 21555

decodes the address of a transaction initiated on the primary bus to determine

whether to assert p_devsel_l.

As an initiator of a transaction on the primary bus, the 21555 looks for the assertion

of p_devsel_l within five clock cycles of p_frame_l assertion; otherwise, the 21555

terminates the transaction with a master abort.

Upon completion of a transaction, p_devsel_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

Primary PCI interface FRAME#. Signal p_frame_l is driven by the initiator of a

transaction to indicate the beginning and duration of an access on the primary PCI

bus. Signal p_frame_l assertion (falling edge) indicates the beginning of a PCI

transaction. While p_frame_l remains asserted, data transfers can continue. The

deassertion of p_frame_l indicates the final data phase requested by the initiator.

Upon completion of a transaction, p_frame_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

Primary PCI interface IDSEL. Signal p_idsel is used as the chip select line for Type

0 configuration accesses to 21555 configuration space from the primary bus. When

p_idsel is asserted during the address phase of a Ty pe 0 configuration transaction,

the 21555 responds to the transaction by asserting p_devsel_l.

Primary PCI interface IRDY#. Signal p_irdy_l is driven by the initiator of a

transaction to indicate the initiator’s ability to complete the current data phase on the

primary PCI bus.

During a write transaction, assertion of p_irdy_l indicates that valid write data is

being driven on the p_ad bus.

During a read transaction, assertion of p_irdy_l indicates that the initiator is able to

accept read data for the current data phase. Once asserted during a given data

phase, p_irdy_l is not deasserted until the data phase completes.

Upon completion of a transaction, p_irdy_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

24 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 25

T able 6. Primary PCI Bus Interface Signals (Sheet 2 of 2)

Signal Name Type Description

Primary PCI interface parity. Signal p_par carries the even parity of the 36 bits of

p_ad[31:0] and p_cbe_l[3:0] for both address and data phases. Signal p_par is

driven by the same agent that drives the address (for address parity) or the data (for

data parity). Signal p_par contains valid parity one clock cycle after the addres s is

valid (indicated by assertion of p_frame_l), or one clock cycle after the data is valid

p_par TS

p_req_l TS

p_stop_l STS

p_trdy_l STS

(indicated by assertion of p_irdy_l for write transactions and p_trdy_l for read

transactions). Signal p_par is tristated one clock cycle after the p_ad lines are

tristated.

The device receiving data samples p_par as an inpu t to check for possible parity

errors. When the primary PCI bus is idle, the 21555 drives p_par to a valid logic

level when p_gnt_l is asserted (one clock cycle after the p_ad bus is pa r ked).

Primary PCI bus REQ#. Signal p_req_l is asserted by the 21555 to indicate to the

primary bus arbiter that it wants to start a transaction on the primary bus. Signal

p_req_l is tristated during the assertion of chip reset.

Primary PCI interface STOP#. Signal p_stop_l is driven by the target of a

transaction, indicating that the target is requesting the initiator to stop the transaction

on the primary bus.

• When p_stop_l is asserted in conjunction with p_trdy_l and p_devsel_l

assertion, a disconnect with data transfer is being signaled.

• When p_stop_l and p_devsel_l are asserted, but p_trdy_l is deasserted, a

target disconnect without data transfer is being signaled. When this occurs on

the first data phase, that is, no data is transferred during the transaction, this is

referred to as a target retry.

• When p_stop_l is asserted and p_devsel_l is deasserted, the target is

signaling a target abort.

Upon completion of a transaction, p_stop_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

Primary PCI interface TRDY#. Signal p_trdy_l is driven by the tar get of a

transaction to indicate the target's ability to complete the current data phase on the

primary PCI bus.

During a write transaction, assertion of p_trdy_l indicates that the target is able to

accept write data for the current data phase.

During a read transaction, assertion of p_trdy_l indicates that the target is driving

valid read data on the p_ad bus. Once asserted during a given data phase, p_trdy_l

is not deasserted until the data phase completes.

Upon completion of a transaction, p_trdy_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

Signal Descriptions

21555 Non-Transparent PCI-to-PCI Bridge User Manual 25

Page 26

Signal Descriptions

3.2 Primary PCI Bus Interface 64-Bit Extension Signals

Table 7 describes the primary PCI bus interface 64-bit extension signals. The letters in the “Type” column are

described in Table 1.

T able 7. Primary PCI Bus Interface 64

Signal Name Type Description

Primary PCI interface acknowledge 64-bit transfer.

Signal p_ack64_l should never be driven when p_req64_l is not driven.

p_ack64_l STS

p_ad[63:32] TS

p_cbe_l[7:4] TS

Signal p_ack64_l is asserted by the target only when p_req64_l is asserted by the

initiator, to indicate the target’s ability to transfer data using 64 bits.

Signal p_ack64_l has the same timing as p_devsel_l.

When deasserting, p_ack64_l is driven to a deasserted state for one clock cycle

and is then sustained by an external pull-up resistor.

Primary PCI interface address and data upper 32 bits.

The 21555 does not bus park these pins. These pins are tristated during the

assertion of p_rst_l. Signals p _ad[63:32] are driven to a valid value when the 64-bit

extension is disabled (p_req64_l is deasserted during p_rst_l assertion).

This multiplexed address and data bus provides an additional 32 bits to the primary

interface. During the address phase or phases of a transaction, when the

dual-address command is used and p_req64_l is asserted, the initiator drives the

upper 32 bits of a 64-bit address; otherwise, these bits are unde fined, and the

initiator drives a valid logic level onto the pins.

During the data phases of a transaction, the initiator drives the upper 32 bits of

64-bit write data, or the target drives the upper 32 bits of 64-bit read data, when

p_req64_l and p_ack64_l are both asserted.

When not driven, signals p_ad[63:32] are pulled up to a valid logic level through

external resistors.

Primary PCI interface command and byte enables upper 4 bits.

The 21555 does not bus park these pins. These pins are tristated during the

assertion of p_rst_l. Signals p_cbe_l[7:4] are driven to a valid value when the

64-bit extension is disabled (p_req64_l is deasserted during p_rst_l assertion).

These signals are a multiplexed command field and byte enable field. During the

address phase or phases of a transaction, when the dual-address command is used

and p_req64_l is asserted, the initiator drives the transaction type on p_cbe_l[7:4];

otherwise, these bits are undefined, and the initiator drives a valid logic level onto

the pins.

For both read and write transactions, the initiator drives byte enables for the

p_ad[63:32] data bits on p_cbe_l[7:4] during the data phases, when p_req64_l

and p_ack64_l are both asserted.

When not driven, signals p_cbe_l[7:4] are pulled up to a valid logic level through

external resistors.

-Bit Extension Signals (Sheet 1 of 2)

26 21555 Non-Transparent PCI-to-PCI Bridge Use r Manual

Page 27

T able 7. Primary PCI Bus Interface 64-Bit Extension Signals (Sheet 2 of 2)

Signal Name Type Descrip tion

Primary PCI interface upper 32 bits parity.