INOVC IA8044-PDW40I-01, IA8044-PLC40I-01, IA8344-PDW40I-01, IA8344-PLC40I-01 Datasheet

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 1 of 49 1-888-824-4184

FEATURES

• Form, Fit, and Function Compatible with the Intel 8044/8344

• Packaging options available: 40 Pin Plastic Dual In-Line Package (PDIP),

44 Pin Plastic Leaded Chip Carrier (PLCC)

• 8-Bit Control Unit

• 8-Bit Arithmetic-Logic Unit with 16-Bit multiplication and division

• 12 MHz clock

• Four 8-Bit Input / Output ports

• Two 16-Bit Timer/Counters

• Serial Interface Unit with SDLC/HDLC compatibility

• 2.4 Mbps maximum serial data rate

• Two Level Priority Interrupt System

• 5 Interrupt Sources

• Internal Clock prescaler and Phase generator

• 192 Bytes of Read/Write Data Memory Space

• 64kB External Program Memory Space

• 64kB External Data Memory Space

• 4kB Internal ROM (IA8044 only)

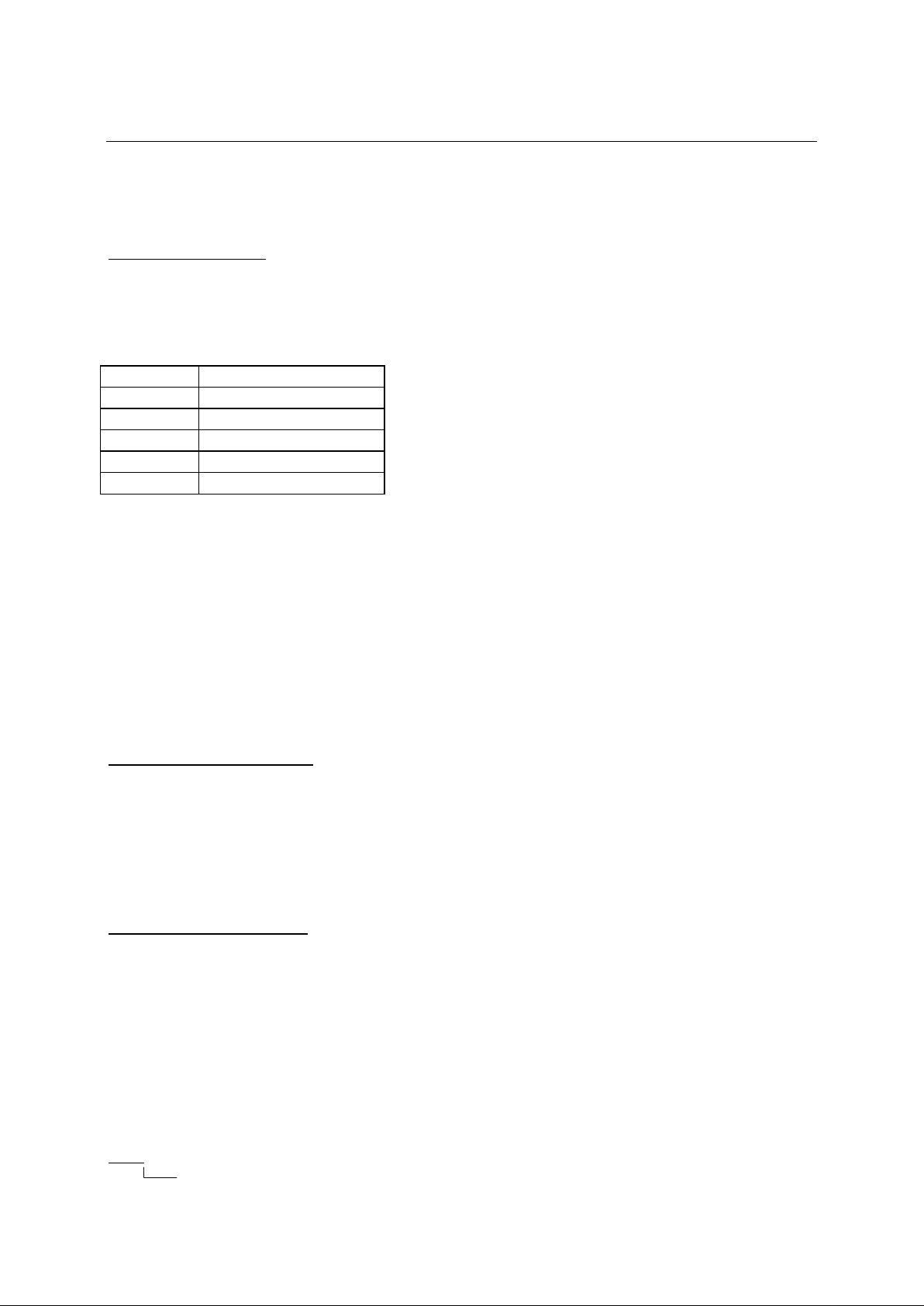

IA8044/IA8344 Variants

IA8044

4kB internal ROM with R0117 version 2.3 firmware, 192 byte internal RAM,

64kB external program and data space.

IA8344 192 byte internal RAM, 64kB external program and data space.

The IA8044/IA8344 is a "plug-and-play" drop-in replacement for the original IC. InnovASIC

produces replacement ICs using its MILESTM, or Managed IC Lifetime Extension System, cloning

technology. This technology produces replacement ICs far more complex than "emulation" while

ensuring they are compatible with the original IC. MILESTM captures the design of a clone so it can

be produced even as silicon technology advances. MILESTM also verifies the clone against the

original IC so that even the "undocumented features" are duplicated. This data sheet documents all

necessary engineering information about the IA8044/IA8344 including functional and I/O

descriptions, electrical characteristics, and applicable timing.

innovASIC

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 2 of 49 1-888-824-4184

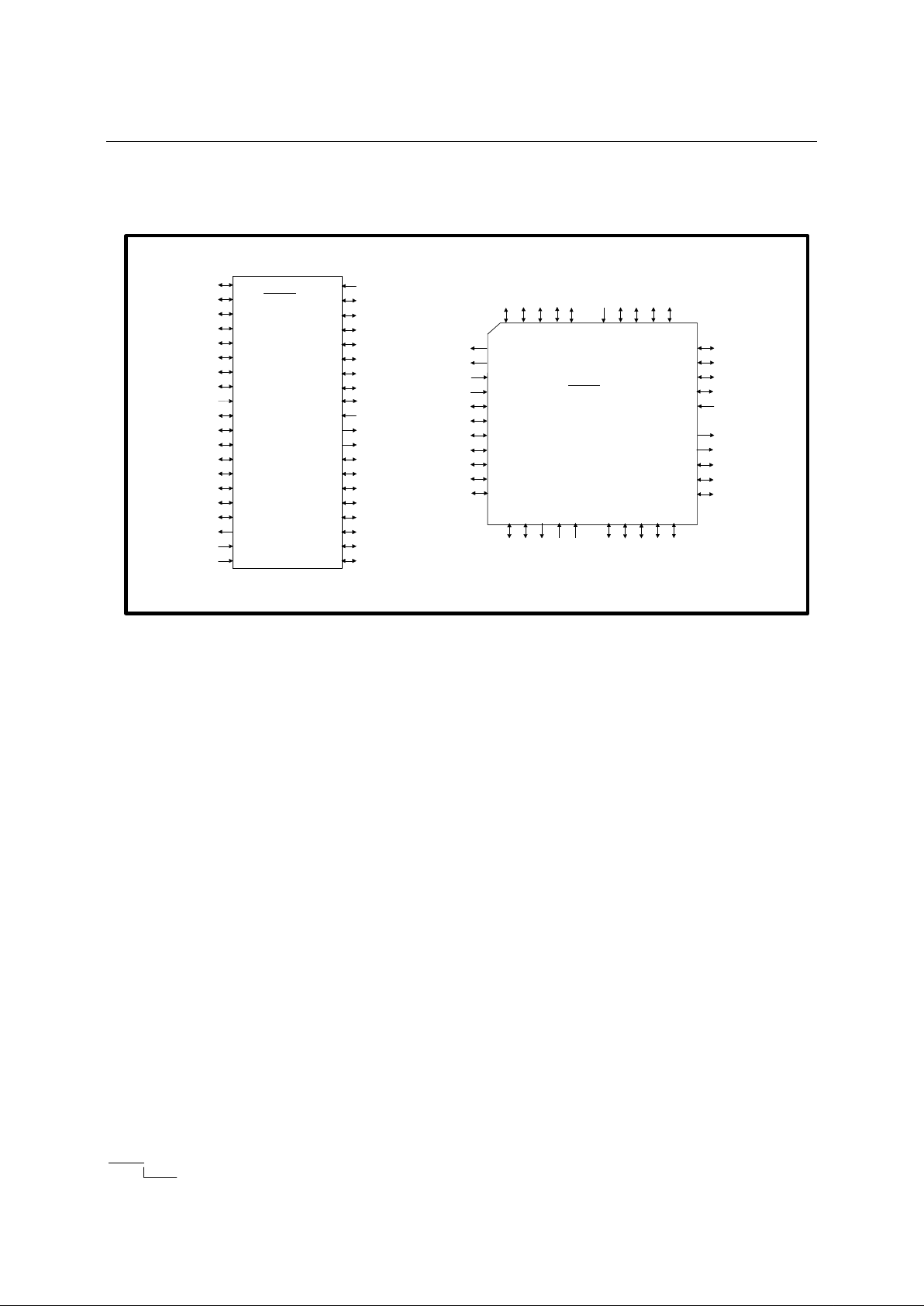

Package Pinout

(6)P1.5

(1)P1.0

(2)P1.1

(3)P1.2

(4)P1.3

(5)P1.4

(7)(RTS) P1.6

(8)

(9)RST

(10)

(11)

(12)(INT0) P3.2

(13)

(INT1) P3.3

(14)

40 Pin DIP

IA8X44

P0.7 (AD7)

EA

ALE

PSEN

(20)VSS

(15)

(SCLK/T1) P3.5

(16)

(WR) P3.6

(17)

(RD) P3.7

(18)

XTAL2

(19)XTAL1

(21)

(22)

(23)

(24)

P2.1 (A9)

P2.0 (A8)

(40)

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

(28)

(27)

(26)

(25)

(T0) P3.4

P2.3 (A11)

P2.2 (A10)

P2.5 (A13)

P2.4 (A12)

P2.7 (A15)

P2.6 (A14)

P0.5 (AD5)

P0.6 (AD6)

P0.3 (AD3)

P0.4 (AD4)

P0.1 (AD1)

P0.2 (AD2)

VCC

P0.0 (AD0)

(CTS) P1.7

(RXD) P3.0

(TXD) P3.1

P1.3

P1.4

P3.6

P2.6

44 Pin LCC

IA8X44

(12)N.C.

(7)P1.5

(8)P1.6

(9)P1.7

(10)RST/VPD

(11)P3.0

(13)P3.1

(14)P3.2

(15)P3.3

(16)P3.4

(17)P3.5

P0.4

ALE

N.C.

EA

P0.6

P0.5

XTAL2

P3.7

(6)

(5)

(4)

(3)

(2)

(1)

(44)

(43)

(42) P0.1

(41) P0.2

(40) P0.3

(34)

(39)

(38)

(37)

(36)

(35)

(33)

(32)

(31)

(30)

(29)

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

VCC

P0.0

P1.0

N.C.

P1.2

P1.1

VSS

XTAL1

P2.0

N.C.

P2.2

P2.1

P2.4

P2.3

P2.5

P2.7

PSEN

P0.7

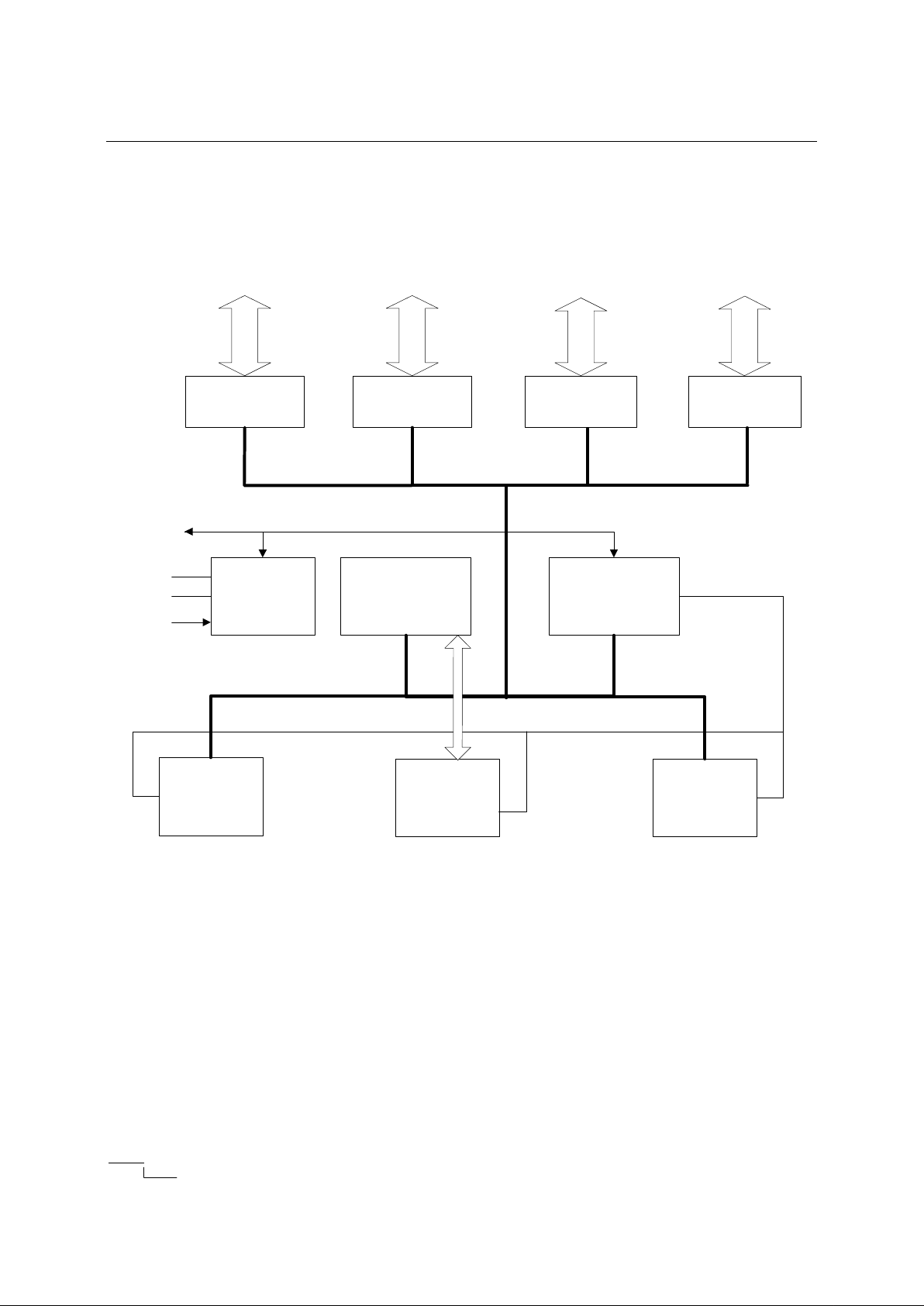

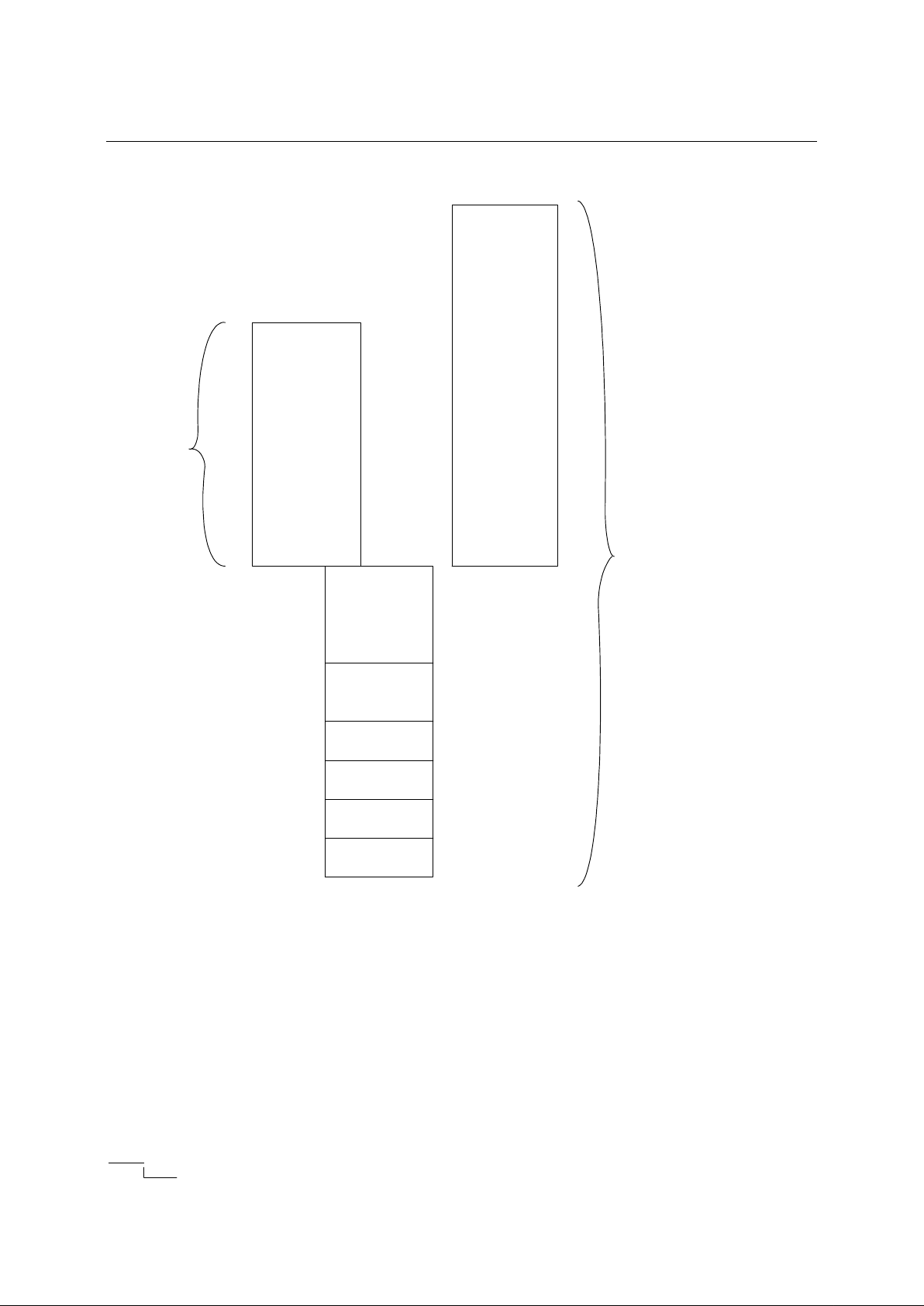

DESCRIPTION

The IA8044/IA8344 is a form, fit and function compatible part to the Intel 8X44 SDLC

communications controller. The IA8044/IA8344 is a Fast Single-Chip 8-Bit Microcontroller with an

integrated SDLC/HDLC serial interface controller. The IA8044/IA8344 is a fully functional 8-Bit

Embedded Controller that executes all ASM51 instructions and has the same instruction set as the

Intel 80C51. The IA8044/IA8344 can access the instructions from two types of program memory,

serves software and hardware interrupts, provides an interface for serial communications and a timer

system. The IA8044/IA8344 is fully compatible with the Intel 8X44 series. The functional block

diagram is shown below.

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 3 of 49 1-888-824-4184

Functional Block Diagram

192x8Dual Port

RAM

C8051

CPU

Interrupts

Timers

Port 0

ADDR/DATA/IO

Port 2

ADDR/DATA/IO

Port 1

SPCL FUNC/IO

Port 3

SPCL FUNC/IO

SIU

Control

Address/Data

Clock Gen.

& Timing

XTAL

Reset

Memory

Control

I/O for Memory, SIU, DMA, Interrupts, Timers

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 4 of 49 1-888-824-4184

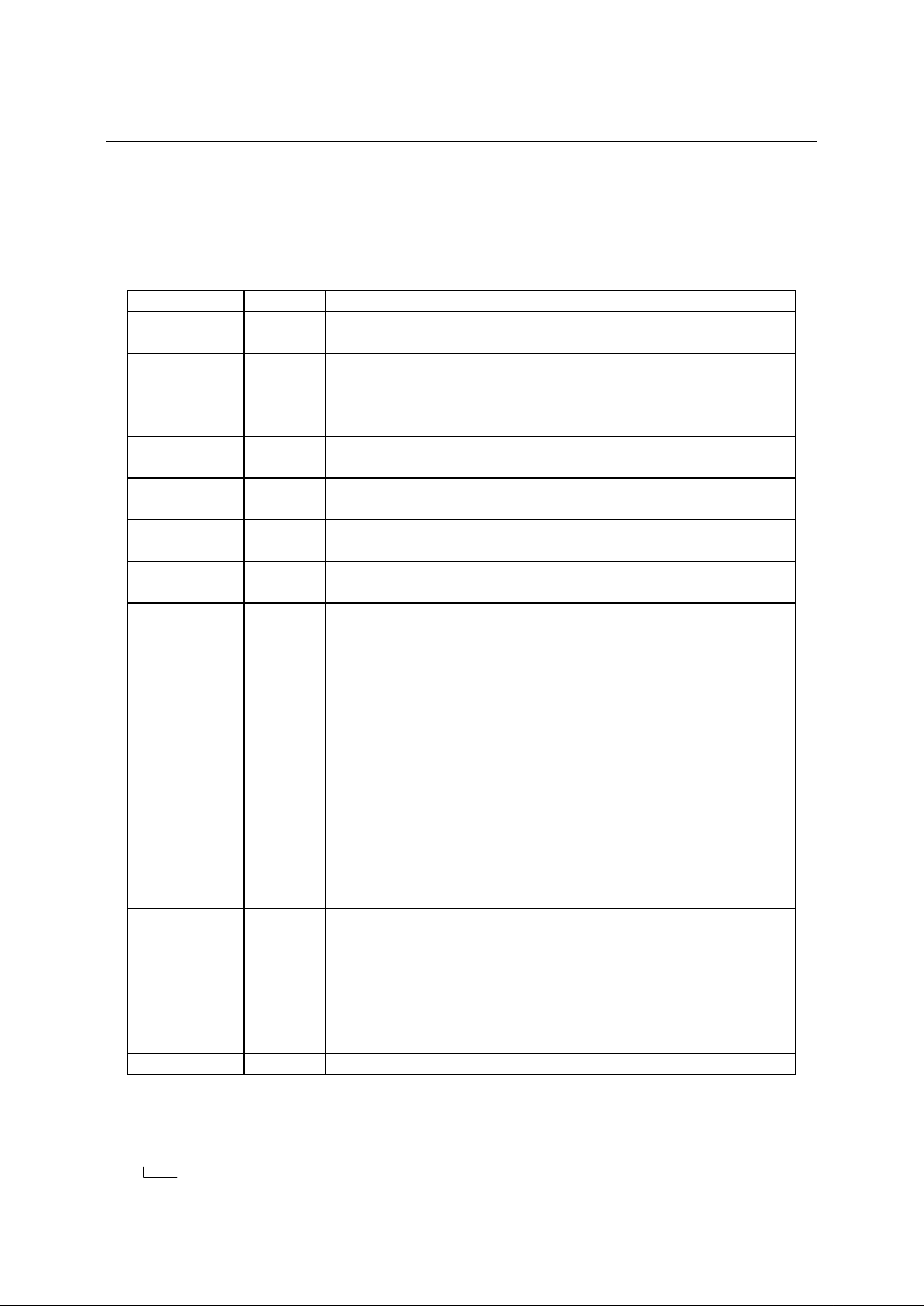

I/O Characteristics

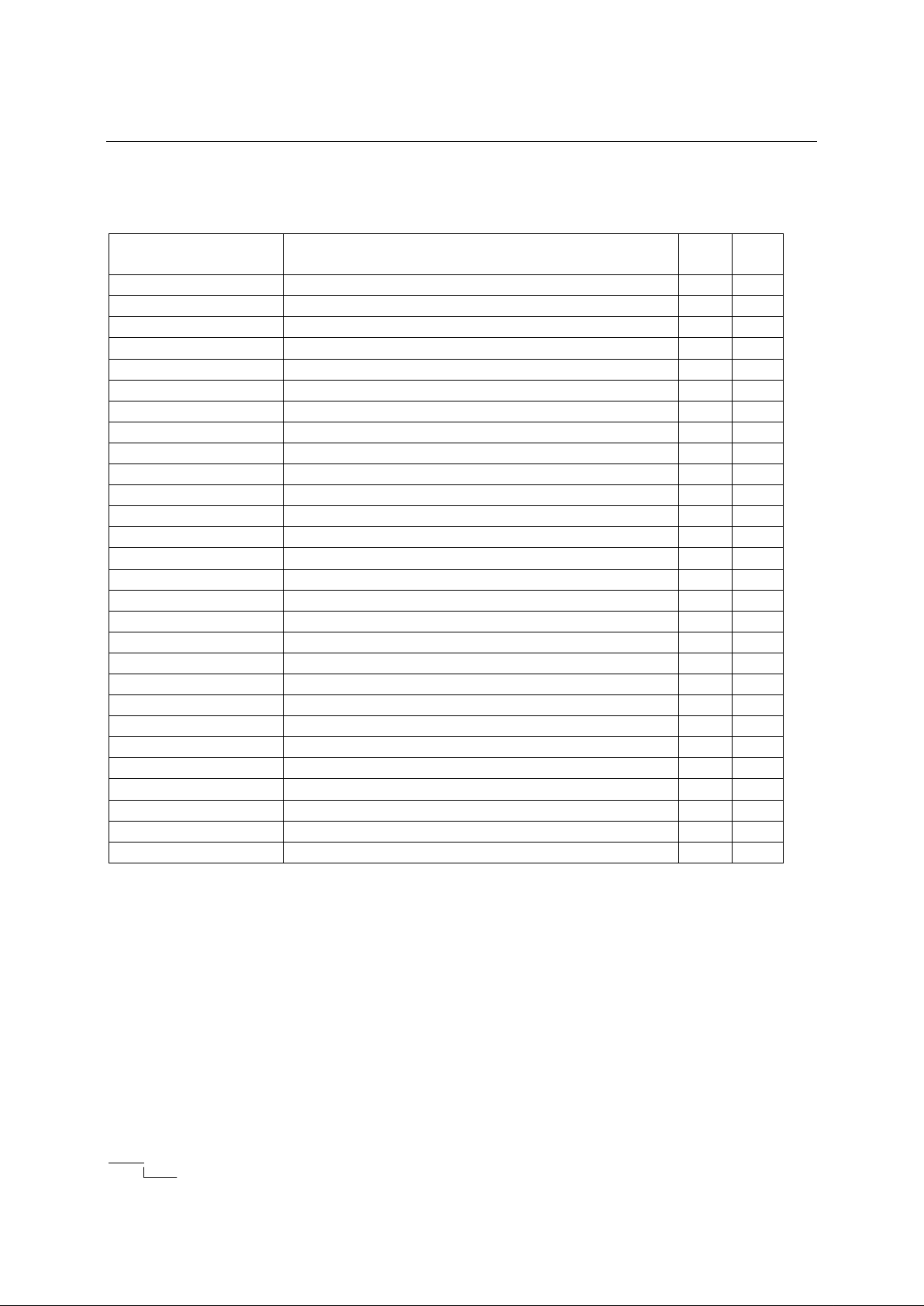

The table below describes the I/O characteristics for each signal on the IC. The signal names

correspond to the signal names on the pinout diagrams provided. The table below provides the I/O

description of the IA8044 and the IA8344.

Name Type Description

RST I Reset. This pin when held high for two machine cycles while

the oscillator is running will cause the chip to reset.

ALE O Address Latch Enable. Used to latch the address on the falling

edge for external memory accesses.

PSEN O Program Store Enable. When low acts as an output enable for

external program memory.

EA I External Access. When held low EA will cause the

IA8044/IA8344 to fetch instructions from external memory.

P0.7 – P0.0 I/O Port 0. 8 bit I/O port and low order multiplexed address/data

byte for external accesses.

P1.7 – P1.0 I/O Port 1. 8-bit I/O port. Two bits have alternate functions, P1.6

(RTS) and P1.7 (CTS).

P2.7 – P2.0 I/O Port 2. 8-bit I/O port. It also functions as the high order

address byte during external accesses.

P3.7 – P3.0 I/O Port 3. 8-bit I/O port. Port 3 bits also have alternate functions

as described below.

P3.0 – RXD. Receive data input for SIU or direction control

for P3.1 dependent upon datalink configuration.

P3.1 – TXD. Transmit data output for SIU or data

input/output dependent upon datalink configuration. Also

enables diagnostic mode when cleared.

P3.2 – INT0. Interrupt 0 input or gate control input for counter

0.

P3.3 – INT1. Interrupt 1 input or gate control input for counter

1.

P3.4 – T0. Input to counter 0.

P3.5 – SCLK/T1. SCLK input to SIU or input to counter 1.

P3.6 – WR. External memory write signal.

P3.7 – RD. External memory read signal.

XTAL1 I Crystal Input 1. Connect to VSS when external clock is used on

XTAL2. May be connected to a crystal (with XTAL2), or may

be driven directly with a clock source (XTAL2 not connected).

XTAL2 O Crystal Input 2. May be connected to a crystal (with XTAL1),

or may be driven directly with an inverted clock source (XTAL1

tied to ground).

VSS P Ground.

VCC P +5V power.

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 5 of 49 1-888-824-4184

Memory Organization

Program Memory

Program Memory includes interrupt and Reset vectors. The interrupt vectors are spaced at 8byte intervals, starting from 0003H for External Interrupt 0.

Reset Vectors

These locations may be used for program code, if the corresponding interrupts are not used

(disabled). The Program Memory space is 64K, from 0000H to FFFFH. The lowest 4K of program

code (0000H to 0FFFH) can be fetched from external or internal Program Memory. This selection is

made by strapping pin ‘EA’ (External Address) to GND or VCC. If during reset, ‘EA’ is held low,

all the program code is fetched from external memory. If, during reset, ‘EA’ is held high, the lowest

4K of program code (0000H to 0FFFH) is fetched from internal memory (ROM). Program

memory addresses above 4K (0FFFH) will cause the program code to be fetched from external

memory regardless of the setting of ‘EA’.

Data Memory

External Data Memory

The IA8044/IA8344 Microcontroller core incorporates the Harvard architecture, with separate

code and data spaces. The code from external memory is fetched by ‘psen’ strobe, while data

is read from RAM by bit 7 of P3 (read strobe) and written to RAM by bit 6 of P3 (write strobe). The

External Data Memory space is active only by addressing through use of the MOVX instruction and

the 16-bit Data Pointer Register (DPTR). A smaller subset of external data memory (8 bit

addressing) may be accessed by using the MOVX instruction with register indexed addressing.

Internal Data Memory

The Internal Data Memory address is always 1 byte wide. The memory space is 192 bytes

large (00H to BFH), and can be accessed by either direct or indirect addressing. The Special

Function Registers occupy the upper 128 bytes. This SFR area is available only by direct

addressing. Internal memory that overlaps the SFR address space is only accessible by indirect

addressing.

Location Service

0003H External Interrupt 0

000BH Timer 0 overflow

0013H External Interrupt 1

001BH Timer 1 overflow

0023H SIU Interrupt

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 6 of 49 1-888-824-4184

Internal Memory

8044 Internal Data Memory Addresses

00h to FFh

80h

FFh

80h

BFh

Indirect

Addressing

RAM

00h

07h

08h

17h

18h

1Fh

20h

2Fh

30h

7Fh

10h

0Fh

Register Bank 0

Register Bank 1

Register Bank 2

Register Bank 3

Bit Addressable

Memory

Internal Data Ram

Direct Addressing

Special Function

Registers

Addressable

BITS in SFRs

(128 BITS)

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 7 of 49 1-888-824-4184

Bit Addressable Memory

Both the internal RAM and the Special Function Registers have locations that are bit addressable in

addition to the byte addressable locations.

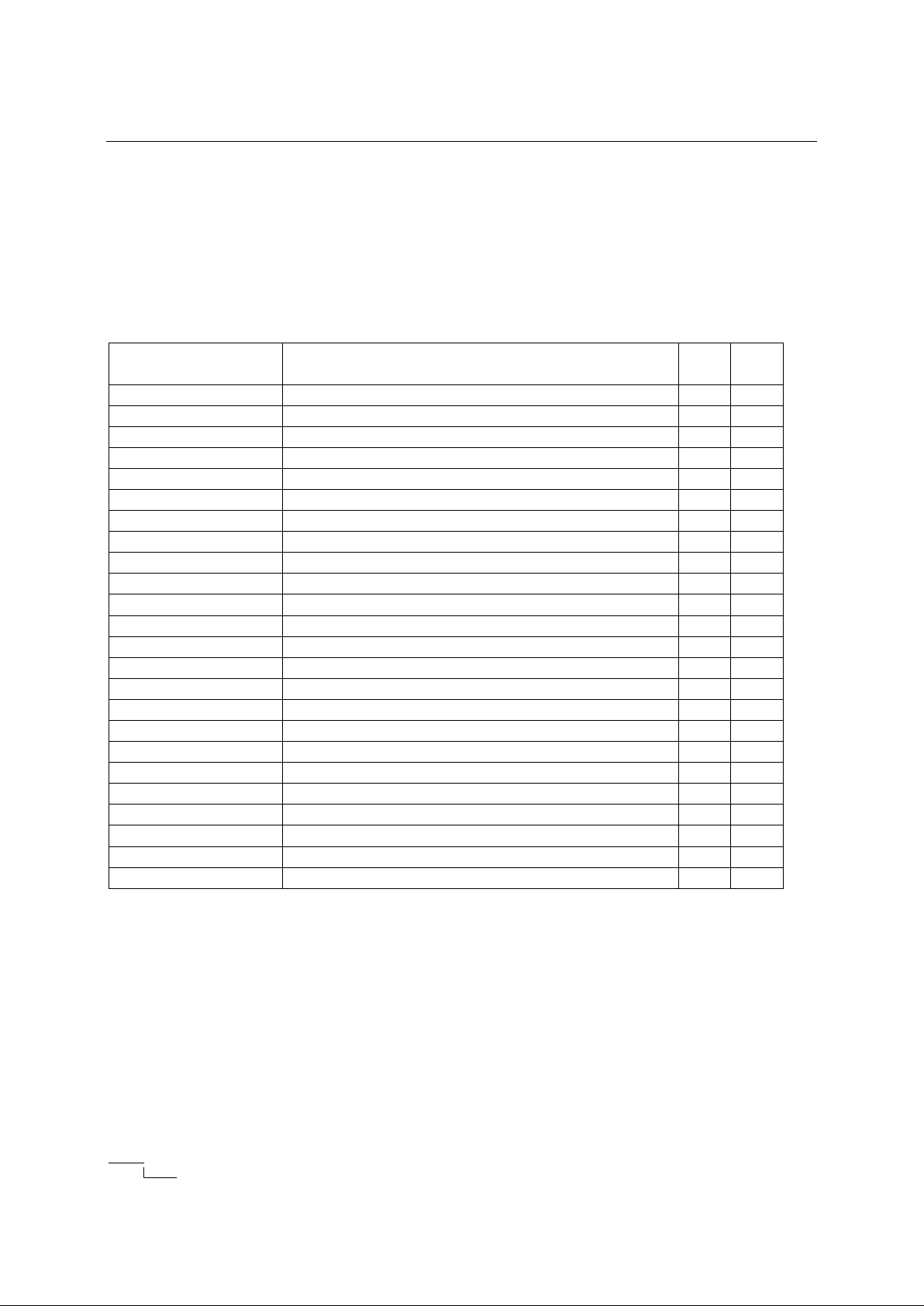

SFR Bit Addressable Locations

Byte Address bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 Register

F0h F7h F6h F5h F4h F3h F2h F1h F0h B

E0h E7h E6h E5h E4h E3h E2h E1h E0h ACC

D8h DFh DEh DDh DCh DBh DAh D9h D8h NSNR

D0h D7h D6h D5h D4h D3h D2h D1h D0h PSW

C8h CFh CEh CDh CCh CBh CAh C9h C8h STS

B8h - - - BCh BBh BAh B9h B8h IP

B0h B7h B6h B5h B4h B3h B2h B1h B0h P3

A8h AFh - - ACh ABh AAh A9h A8h IE

A0h A7h A6h A5h A4h A3h A2h A1h A0h P2

90h 97h 96h 95h 94h 93h 92h 91h 90h P1

88h 8Fh 8Eh 8Dh 8Ch 8Bh 8Ah 89h 88h TCON

80h 87h 86h 85h 84h 83h 82h 81h 80h P0

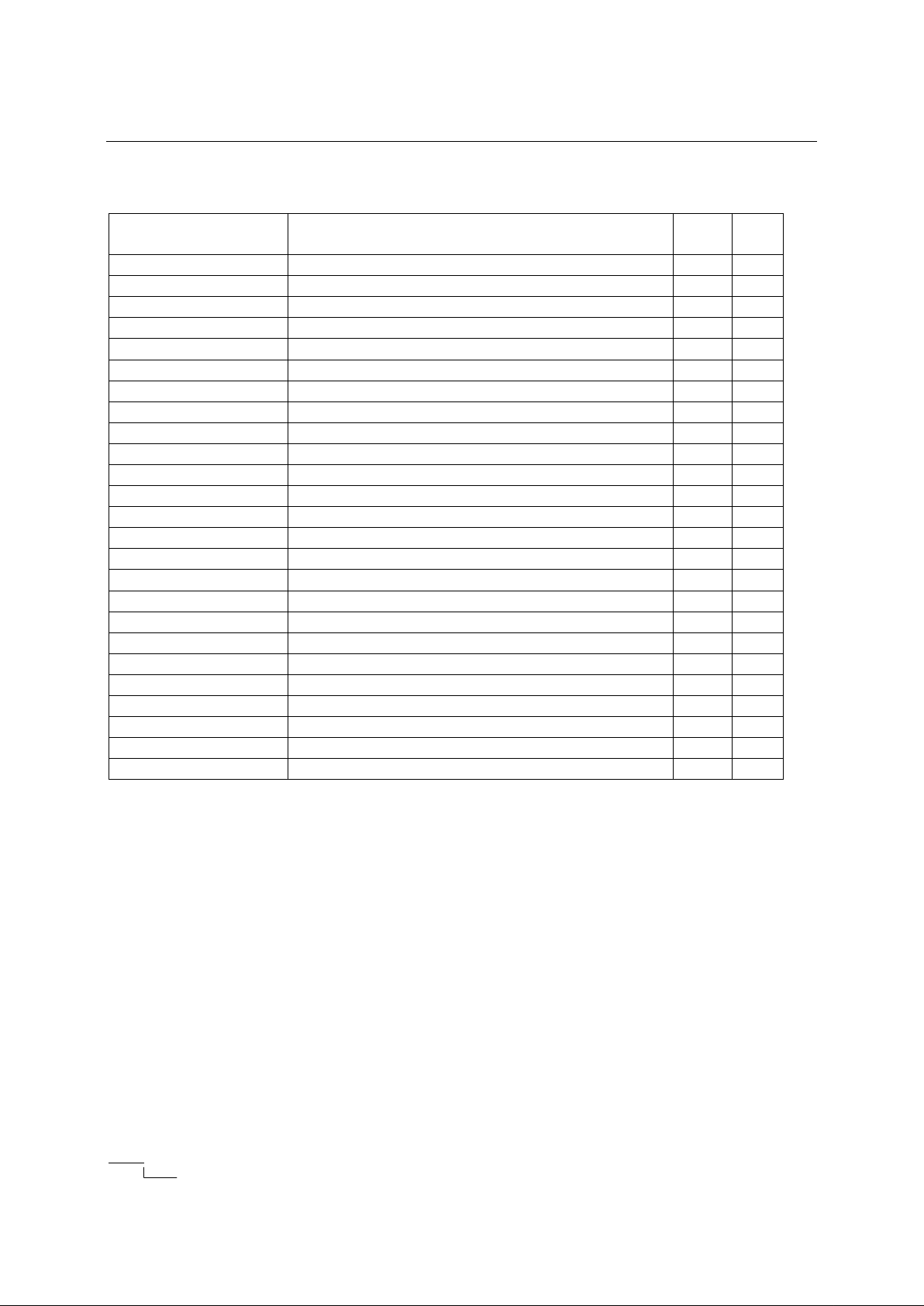

Internal RAM Bit Addressable Locations

Byte Address bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

30h-BFh Upper Internal Ram locations

2Fh 7Fh 7Eh 7Dh 7Ch 7Bh 7Ah 79h 78h

2Eh 77h 76h 75h 74h 73h 72h 71h 70h

2Dh 6Fh 6Eh 6Dh 6Ch 6Bh 6Ah 69h 68h

2Ch 67h 66h 65h 64h 63h 62h 61h 60h

2Bh 5Fh 5Eh 5Dh 5Ch 5Bh 5Ah 59h 58h

2Ah 57h 56h 55h 54h 53h 52h 51h 50h

29h 4Fh 4Eh 4Dh 4Ch 4Bh 4Ah 49h 48h

28h 47h 46h 45h 44h 43h 42h 41h 40h

27h 3Fh 3Eh 3Dh 3Ch 3Bh 3Ah 39h 38h

26h 37h 36h 35h 34h 33h 32h 31h 30h

25h 2Fh 2Eh 2Dh 2Ch 2Bh 2Ah 29h 28h

24h 27h 26h 25h 24h 23h 22h 21h 20h

23h 1Fh 1Eh 1Dh 1Ch 1Bh 1Ah 19h 18h

22h 17h 16h 15h 14h 13h 12h 11h 10h

21h 0Fh 0Eh 0Dh 0Ch 0Bh 0Ah 09h 08h

20h 07h 06h 05h 04h 03h 02h 01h 00h

18h-1Fh Register Bank 3

10h-17h Register Bank 2

08h-0Fh Register Bank 1

00h-07h Register Bank 0

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 8 of 49 1-888-824-4184

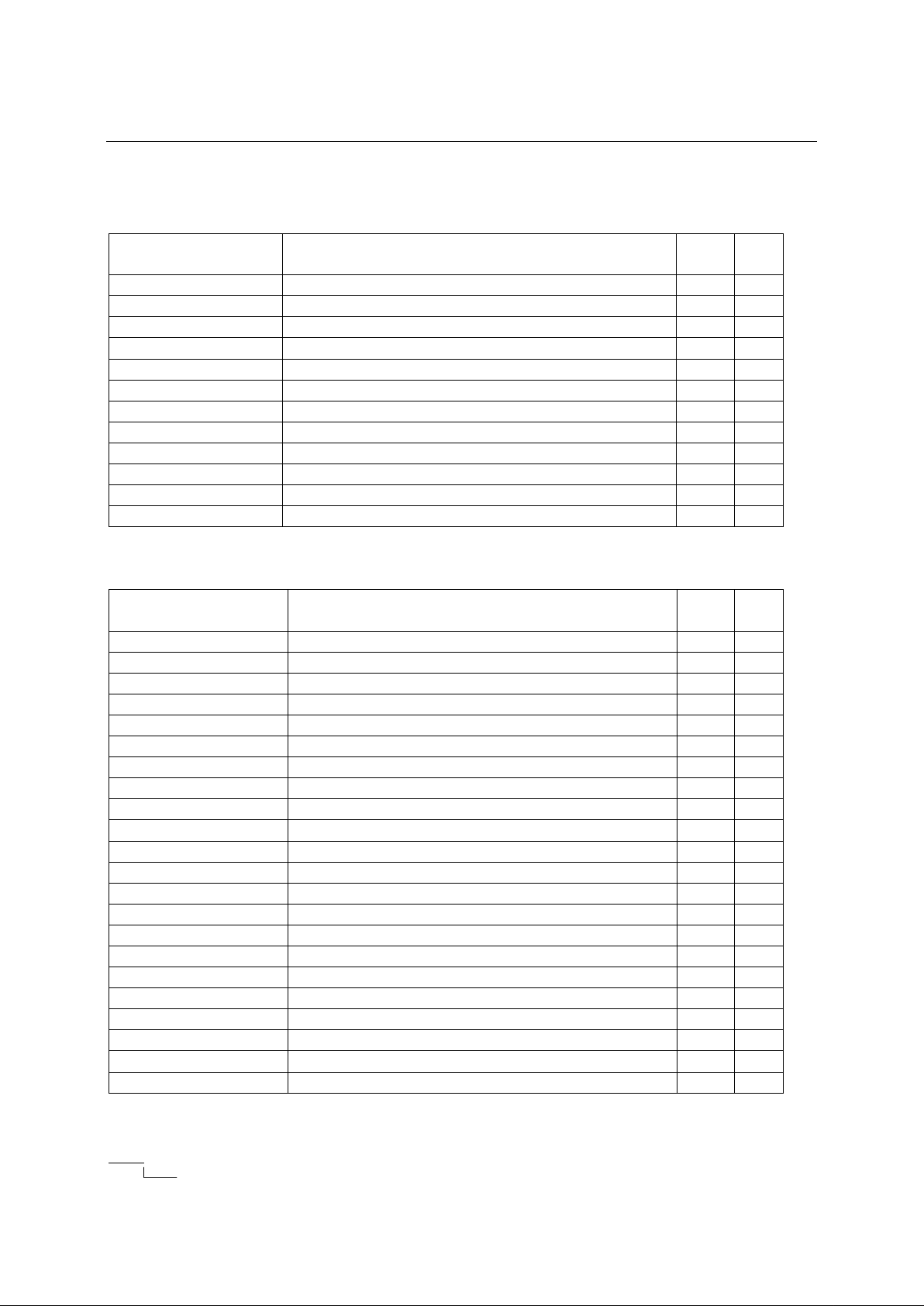

Instruction Set

The 8X44 architecture and instruction set are identical to the 8051’s. The following tables give a

survey of the instruction set of the IA8044/IA8344 Microcontroller core.

Arithmetic Operations

Mnemonic

Description

Byte

Cycle

ADD A,Rn

Add register to accumulator

1 1

ADD A, direct

Add direct byte to accumulator

2 1

ADD A,@Ri

Add indirect RAM to accumulator

1 1

ADD A,#data

Add immediate data to accumulator

2 1

ADDC A,Rn

Add register to accumulator with carry flag

1 1

ADDC A,direct

Add direct byte to A with carry flag

2 1

ADDC A,@Ri

Add indirect RAM to A with carry flag

1 1

ADDC A,#data

Add immediate data to A with carry flag

2 1

SUBB A,Rn Subtract register from A with borrow 1 1

SUBB A,direct Subtract direct byte from A with borrow 2 1

SUBB A,@Ri Subtract indirect RAM from A with borrow 1 1

SUBB A,#data Subtract immediate data from A with borrow 2 1

INC A Increment accumulator 1 1

INC Rn Increment register 1 1

INC direct Increment direct byte 2 1

INC @ Ri Increment indirect RAM 1 1

DEC A Decrement accumulator 1 1

DEC Rn Decrement register 1 1

DEC direct Decrement direct byte 2 1

DEC @Ri Decrement indirect RAM 1 1

INC DPTR Increment data pointer 1 2

MUL A,B Multiply A and B 1 4

DIV A,B Divide A by B 1 4

DA A Decimal adjust accumulator 1 1

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 9 of 49 1-888-824-4184

Logic Operations

Mnemonic

Description

Byte Cycle

ANL A,Rn

AND register to accumulator

1 1

ANL A,direct

AND direct byte to accumulator

2 1

ANL A,@Ri

AND indirect RAM to

accumulator 1 1

ANL A,#data

AND immediate data to accumulator

2 1

ANL direct,A

AND accumulator to direct byte

2 1

ANL direct,#data

AND immediate data to direct byte

3 2

ORL A,Rn OR register to accumulator 1 1

ORL A,direct OR direct byte to accumulator 2 1

ORL A,@Ri OR indirect RAM to accumulator 1 1

ORL A,#data OR immediate data to accumulator 2 1

ORL direct,A OR accumulator to direct byte 2 1

ORL direct,#data OR immediate data to direct byte 3 2

XRL A,Rn Exclusive OR register to accumulator 1 1

XRL A,direct Exclusive OR direct byte to accumulator 2 1

XRL A,@Ri Exclusive OR indirect RAM to accumulator 1 1

XRL A,#data Exclusive OR immediate data to accumulator 2 1

XRL direct,A Exclusive OR accumulator to direct byte 2 1

XRL direct,#data Exclusive OR immediate data to direct byte 3 2

CLR A Clear accumulator 1 1

CPL A Complement accumulator 1 1

RL A Rotate accumulator left 1 1

RLC A Rotate accumulator left through carry 1 1

RR A Rotate accumulator right 1 1

RRC A Rotate accumulator right through carry 1 1

SWAP A Swap nibbles within the accumulator 1 1

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 10 of 49 1-888-824-4184

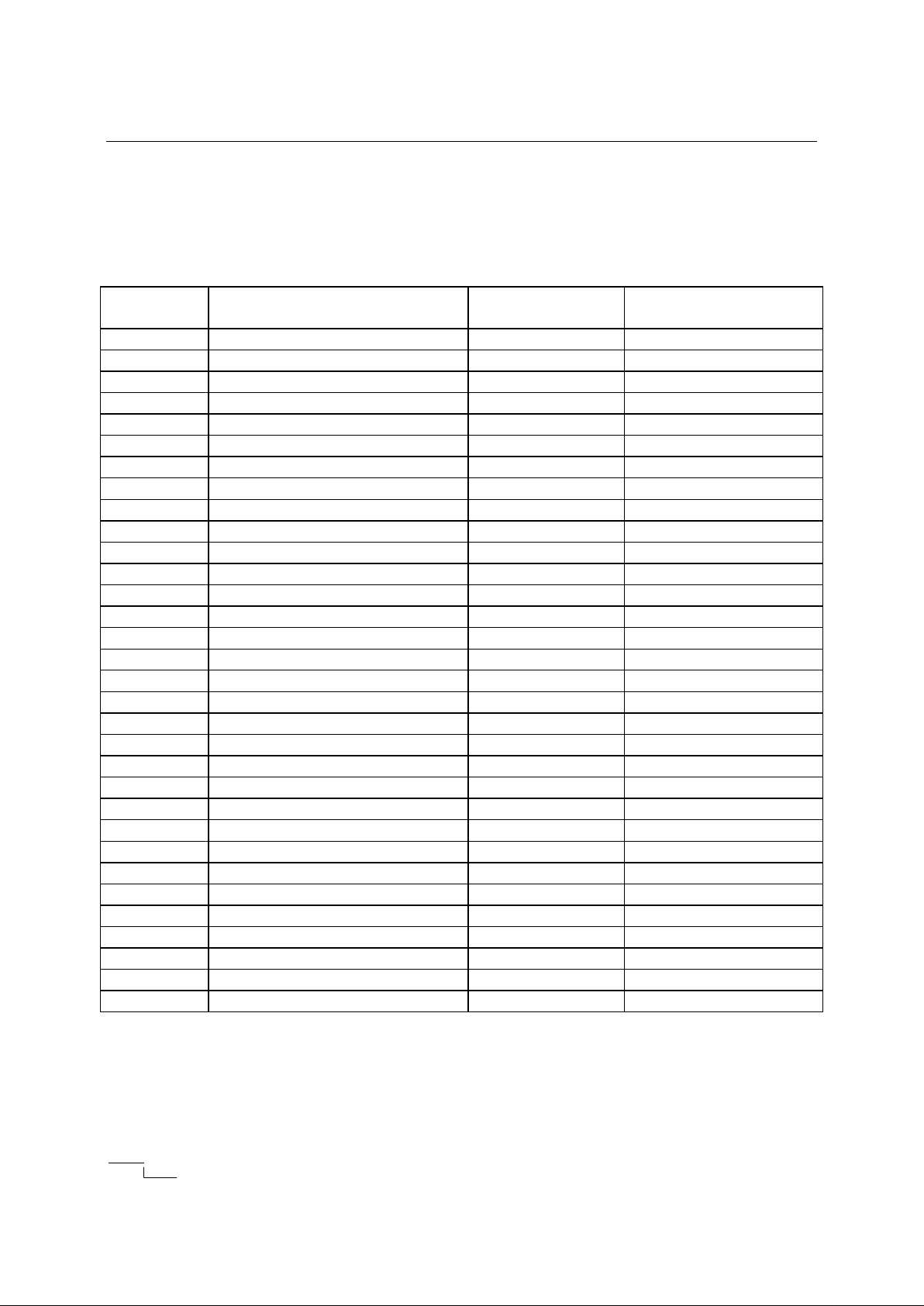

Data Transfer

Mnemonic

Description

Byte

Cycle

MOV A,Rn Move register to accumulator 1 1

MOV A,direct Move direct byte to accumulator 2 1

MOV A,@Ri Move indirect RAM to accumulator 1 1

MOV A,#data Move immediate data to accumulator 2 1

MOV Rn,A Move accumulator to register 1 1

MOV Rn,direct Move direct byte to register 2 2

MOV Rn,#data Move immediate data to register 2 1

MOV direct,A Move accumulator to direct byte 2 1

MOV direct,Rn Move register to direct byte 2 2

MOV direct,direct Move direct byte to direct byte 3 2

MOV direct,@Ri Move indirect RAM to direct byte 2 2

MOV direct,#data Move immediate data to direct byte 3 2

MOV @Ri,A Move accumulator to indirect RAM 1 1

MOV @Ri,direct Move direct byte to indirect RAM 2 2

MOV @ Ri, #data Move immediate data to indirect RAM 2 1

MOV DPTR, #data16 Load data pointer with a 16-bit constant 3 2

MOVC A,@A + DPTR

Move code byte relative to DPTR to accumulator 1 2

MOVC A,@A + PC Move code byte relative to PC to accumulator 1 2

MOVX A,@Ri Move external RAM (8-bit addr.) to A 1 2

MOVX A,@DPTR Move external RAM (16-bit addr.) to A 1 2

MOVX @Ri,A Move A to external RAM (8-bit addr.) 1 2

MOVX @DPTR,A Move A to external RAM (16-bit addr.) 1 2

PUSH direct Push direct byte onto stack 2 2

POP direct Pop direct byte from stack 2 2

XCH A,Rn Exchange register with accumulator 1 1

XCH A,direct Exchange direct byte with accumulator 2 1

XCH A,@Ri Exchange indirect RAM with accumulator 1 1

XCHD X,@ Ri Exchange low-order nibble indir. RAM with A 1 1

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 11 of 49 1-888-824-4184

Boolean Manipulation

Mnemonic

Description

Byte Cycle

CLR C Clear carry flag 1 1

CLR bit Clear direct bit 2 1

SETB C Set carry flag 1 1

SETB bit Set direct bit 2 1

CPL C Complement carry flag 1 1

CPL bit Complement direct bit 2 1

ANL C,bit

AND direct bit to carry flag

2 2

ANL C,bit

AND complement of direct bit to carry

2 2

ORL C,bit OR direct bit to carry flag 2 2

ORL C,bit OR complement of direct bit to carry 2 2

MOV C,bit Move direct bit to carry flag 2 1

MOV bit,C Move carry flag to direct bit 2 2

Program Branches

Mnemonic

Description

Byte Cycle

ACALL addr11

Absolute

subroutine call 2 2

LCALL addr16 Long subroutine call 3 2

RET Return from subroutine 1 2

RETI Return from interrupt 1 2

AJMP addr11

Absolute jump

2 2

LJMP addr16 Long jump 3 2

SJMP rel Short jump (relative addr.) 2 2

JMP @A + DPTR

Jump

indirect relative to the DPTR 1 2

JZ rel

Jump if accumulator is zero

2 2

JNZ rel

Jump if accumulator is not zero

2 2

JC rel

Jump if carry flag is set

2 2

JNC rel

Jump if carry flag is not set

2 2

JB bit,rel

Jump if direct bit is set

3 2

JNB b

it,rel

Jump if direct bit is not set

3 2

JBC bit,rel

Jump if direct bit is set and clear bit

3 2

CJNE A,direct,rel Compare direct byte to A and jump if not equal 3 2

CJNE A,#data,rel Compare immediate to A and jump if not equal 3 2

CJNE Rn,#data rel Compare immed. to reg. and jump if not equal 3 2

CJNE @Ri,#data,rel Compare immed. to ind. and jump if not equal 3 2

DJNZ Rn,rel Decrement register and jump if not zero 2 2

DJNZ direct,rel Decrement direct byte and jump if not zero 3 2

NOP No operation 1 1

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 12 of 49 1-888-824-4184

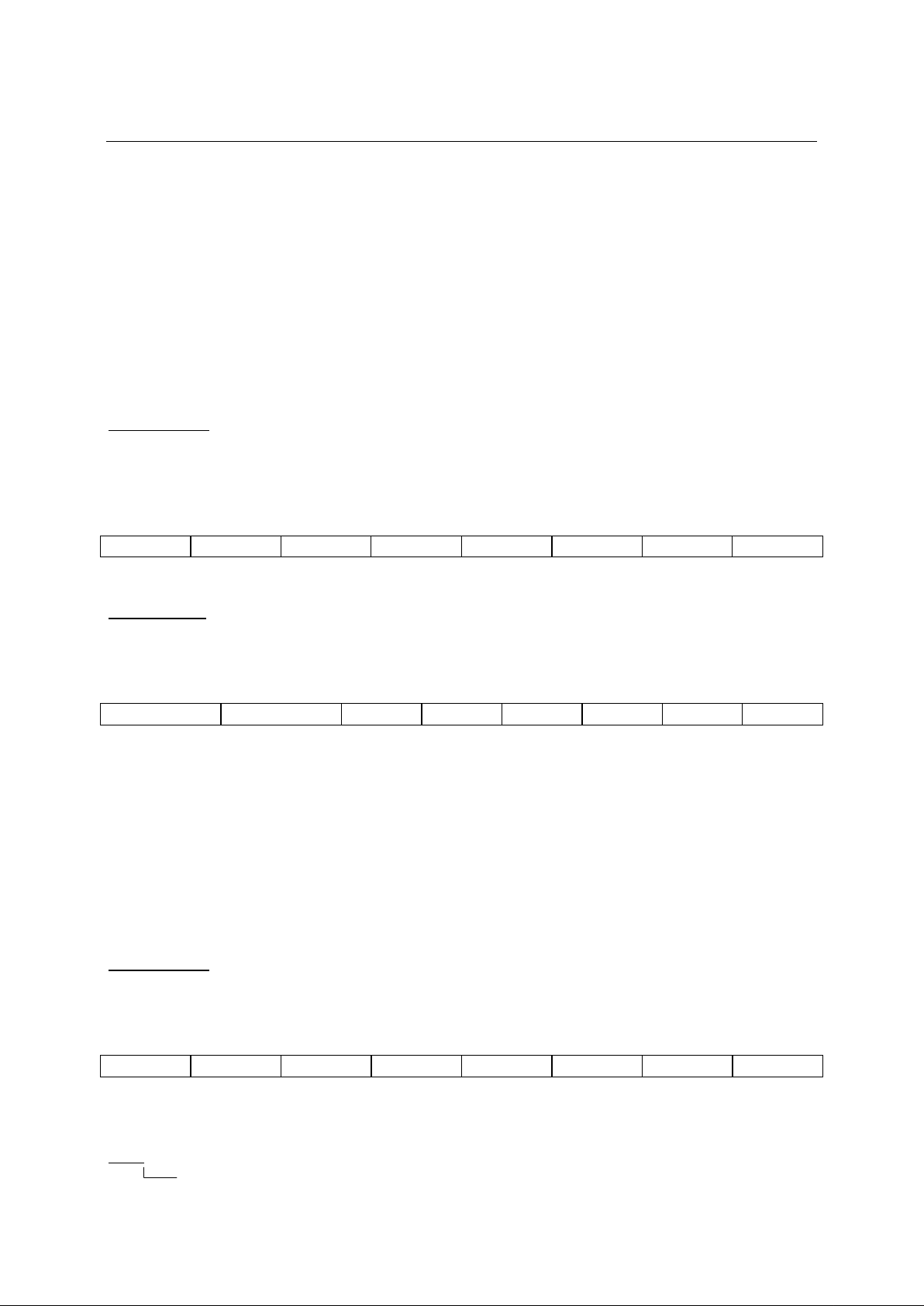

Special Function Registers

The IA8044/IA8344 contains the following special function registers:

Symbol Register Description Byte

Address(Hex)

Bit Addresses (Hex)

(MSB - LSB)

ACC Accumulator E0h E7h – E0h

B B register F0h F7h – F0h

PSW Program Status Word D0h D7h – D0h

SP Stack Pointer 81h DPH Data Pointer High Byte 82h DPL Data Pointer Low Byte 83h P0 Port 0 80h 87h – 80h

P1 Port 1 90h 97h – 90h

P2 Port 2 A0h A7h – A0h

P3 Port 3 B0h B7h – B0h

IP Interrupt Priority B8h BCh – B8h

IE Interrupt Enable A8h AFh,ACh – A8h

TMOD Timer/Counter Mode 89h TCON Timer/Counter Control 88h 8Fh – 88h

TH0 Timer/Counter 0 high byte 8Ch TL0 Timer/Counter 0 low byte 8Ah TH1 Timer/Counter 1 high byte 8Dh TL1 Timer/Counter 1 low byte 8Bh SMD Serial Mode C9h STS SIU Status and Command C8h CFh – C8h

NSNR SIU Send/Receive Count D8h DFh – D8h

STAD SIU Station Address CEh TBS Transmit Buffer Start Address DCh TBL Transmit Buffer Length DBh TCB Transmit Control Byte DAh RBS Receive Buffer Start Address CCh RBL Receive Buffer Length CBh RFL Receive Field Length CDh RCB Receive Control Byte CAh DMA CNT DMA Count CFh FIFO FIFO contents (3 bytes) DF,DE,DDh SIUST SIU State Counter D9h -

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 13 of 49 1-888-824-4184

Ports

Ports P0, P1, P2 and P3 are Special Function Registers. The contents of the SFR can be observed on

corresponding pins on the chip. Writing a ‘1’ to any of the ports causes the corresponding pin to be

at high level (VCC), and writing a ‘0’ causes the corresponding pin to be held at low level (GND).

All four ports on the chip are bi-directional. Each of them consists of a Latch (SFR P0

to P3), an output driver, and an input buffer, so the CPU can output or read data through any

of these ports if they are not used for alternate purposes.

Ports P0, P1, P2 and P3 can perform some alternate functions. Ports P0 and P2 are

used to access external memory. In this case, port ‘p0’ outputs the multiplexed lower 8 bits of

address with ‘ale’ strobe high and then reads/writes 8 bits of data. Port P2 outputs the higher 8

bits of address. Keeping ‘ea’ pin low (tied to GND) activates this alternate function for ports

P0 and P2.

Port P3 and P1 can perform some alternate functions. The pins of Port P3 are multifunctional.

They can perform additional functions as described below.

Pin Symbol Function

P3.0 RxD, I/O In point-to-point or multipoint configurations (SMD.3 = 0) this pin

is I/O and signals the direction of data flow on DATA (P3.1). In loop mode

(SMD.3 = 1) and diagnostic mode this pin is RxD, Receive Data

input.

P3.1 TxD, DATA In point to point or multipoint configurations (SMD.3 = 0) this pin

is DATA and is the transmit/receive data pin. In loop mode

(SMD.3 = 1) this pin is the transmit data, TxD, pin. Writing a ‘0’ to

this port buffer bit enables the diagnostic mode.

P3.2 INT0 External interrupt 0 input. Also gate control input for counter 0.

P3.3 INT1 External interrupt 1 input. Also gate control input for counter 1.

P3.4 T0 Timer/Counter 0 external input. Setting the appropriate bits in the

Special Function Registers TCON and TMOD activates this

function.

P3.5 T1, SCLK Timer/Counter 1 external input. Setting the appropriate bits in the

Special Function Registers TCON and TMOD activates this

function. . Can also function as the external clock source for the SIU.

P3.6 WR External Data Memory write strobe, active LOW. This function

is activated by a CPU write access to External Data Memory

(i.e. MOVX @DPTR, A).

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 14 of 49 1-888-824-4184

P3.7 RD External Data Memory read strobe, active LOW. This function is

activated by a CPU read access from External Data Memory (i.e. MOVX

A, @DPTR).

P1.6 RTS Request To Send output, active low.

P1.7 CTS Clear To Send input, active low.

Port Registers

Port 0 (P0):

General purpose, 8 bit, I/O port and multiplexed low order address and data bus with open-drain

output buffers.

P0

Bit: 7 6 5 4 3 2 1 0

P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0

Port 1 (P1):

General purpose, 8 bit, I/O port with pullups and auxiliary functions.

P1

Bit: 7 6 5 4 3 2 1 0

RTS/P1.7 CTS/P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

P1.0 -

P1.1 -

P1.2 -

P1.3 -

P1.4 -

P1.5 -

P1.6 RTS Request To Send output.

P1.7 CTS Clear To Send input.

Port 2 (P2):

General purpose, 8 bit, I/O port with pullups and high order address bus.

P2

Bit: 7 6 5 4 3 2 1 0

P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

IA8044/IA8344 Data Sheet

SDLC COMMUNICATIONS CONTROLLER

Copyright 2003 ENG210010112-00 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 15 of 49 1-888-824-4184

Port 3 (P3):

General purpose, 8-bit I/O port with pullups and auxiliary functions. Bits on this port also

functions as the SIU data transmit/receive I/O, external interrupt inputs, timer inputs and the read

and write strobes for external memory accesses.

P3

Bit: 7 6 5 4 3 2 1 0

RD WR T1 T0 INT1 INT0 TxD RxD

P3.0 RxD Serial input pin.

P3.1 TxD Serial output pin.

P3.2 INT0 External interrupt 0.

P3.3 INT1 External interrupt 1.

P3.4 T0 Timer/Counter 0 external input.

P3.5 T1 Timer/Counter 1 external input.

P3.6 WR External Data Memory write strobe, active LOW.

P3.7 RD External Data Memory read strobe, active LOW.

Loading...

Loading...