INOVC IA8255-PDW40C, IA8255-PDW40I, IA8255-PLC40C, IA8255-PLC40I Datasheet

Page 1 of 4

IA8255 Advanced Information Sheet

Programmable Peripheral Interface Adapter

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

FEATURES

• Form, Fit, and Function Compatible with the Intel 8255A and Harris

82C55A

• Packaging options available: 40 Pin Plastic DIP or 44 Pin Plastic Leaded

Chip Carrier

• 24 Programmable Input/Outputs

• Static Read/Write or Handshaking Modes

• Direct Bit Set/Reset Capability

• High Speed, No “Wait State” Operation

The IA8255 uses innovASIC’s innovative new f 3 Program to provide industry with parts that

other vendors have declared obsolete. By specifying parts through this program a customer is

assured of never having a component become obsolete again. This advanced information sheet

assumes the original part has been designed in, and so provides a summary of capabilities only. For

new designs contact innovASIC for more detailed information.

Intel is a registered trademark of Intel Corporation

Harris is a copyright trademark of Harris Corporation

Package Pinout

(6)

(1)

(2)

(3)

(4)

(5)

(7)

(8)

(9)A0

(10)PC7

(11)PC6

(12)PC5

(13)PC4

(14)

40 Pin DIP

IA8255

D2

D3

D4

D5

(20)PB2

(15)PC1

(16)PC2

(17)PC3

(18)PB0

(19)PB1

(21)

(22)

(23)

(24)

PB4

PB3

(40)

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

(28)

(27)

(26)

(25)

PC0

PB6

PB5

VCC

PB7

D6

D7

D0

D1

WR_n

RESET

PA6

PA7

PA4

PA5

CS_n

PA3

PA2

PA1

PA0

RD_n

GND

A1

PB0

PC2

PA6

PA7

WR_n

PA5

N. C.

PA2

PB2

PB3

PB5

PB7

PB6

44 Pin LCC

IA8255

(12)N. C.

(7)CS_n

(8)GND

(9)

A1

(10)A0

(11)PC7

(13)PC6

(14)PC5

(15)PC4

(16)PC0

(17)PC1

RESET

D4

N. C.

D3

D1

D0

PC3

(6)

(5)

(4)

(3)

(2)

(1)

(44)

(43)

(42)

(41)

(40)

PA0

RD_n

(34)

(39)

(38)

(37)

(36)

(35)

(33)

(32)

(31)

(30)

(29)

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

PA4

PA3

PA1

PB1

N. C.

PB4

VCC

D7

D6

D5

D2

Page 2 of 4

IA8255 Advanced Information Sheet

Programmable Peripheral Interface Adapter

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

The IA8255 is a programmable peripheral interface adapter mega-function designed to be

functionally equivalent to the Intel 8255A and Harris 82C55A devices. This function has 24 I/O

signals programmable in two groups of 12. Three modes of operation allow the following:

• Basic Input/Output (Mode 0) - Port A, Port B, Port C (upper), and Port C (lower) can be

independently configured as inputs or outputs to read or hold static data. Outputs are

latched, but inputs are not latched.

• Strobed Input/Output (Mode 1) - Port A and Port B can be independently configured as

strobed input or output buses. Signals from Port C are dedicated as control signals for data

handshaking.

• Bidirectional Bus (Mode 2) - Port A can also be configured as a bidirectional bus, with the

majority of Port C providing the control signals. In this case, Port B is still capable of

implementing one of the previous described modes.

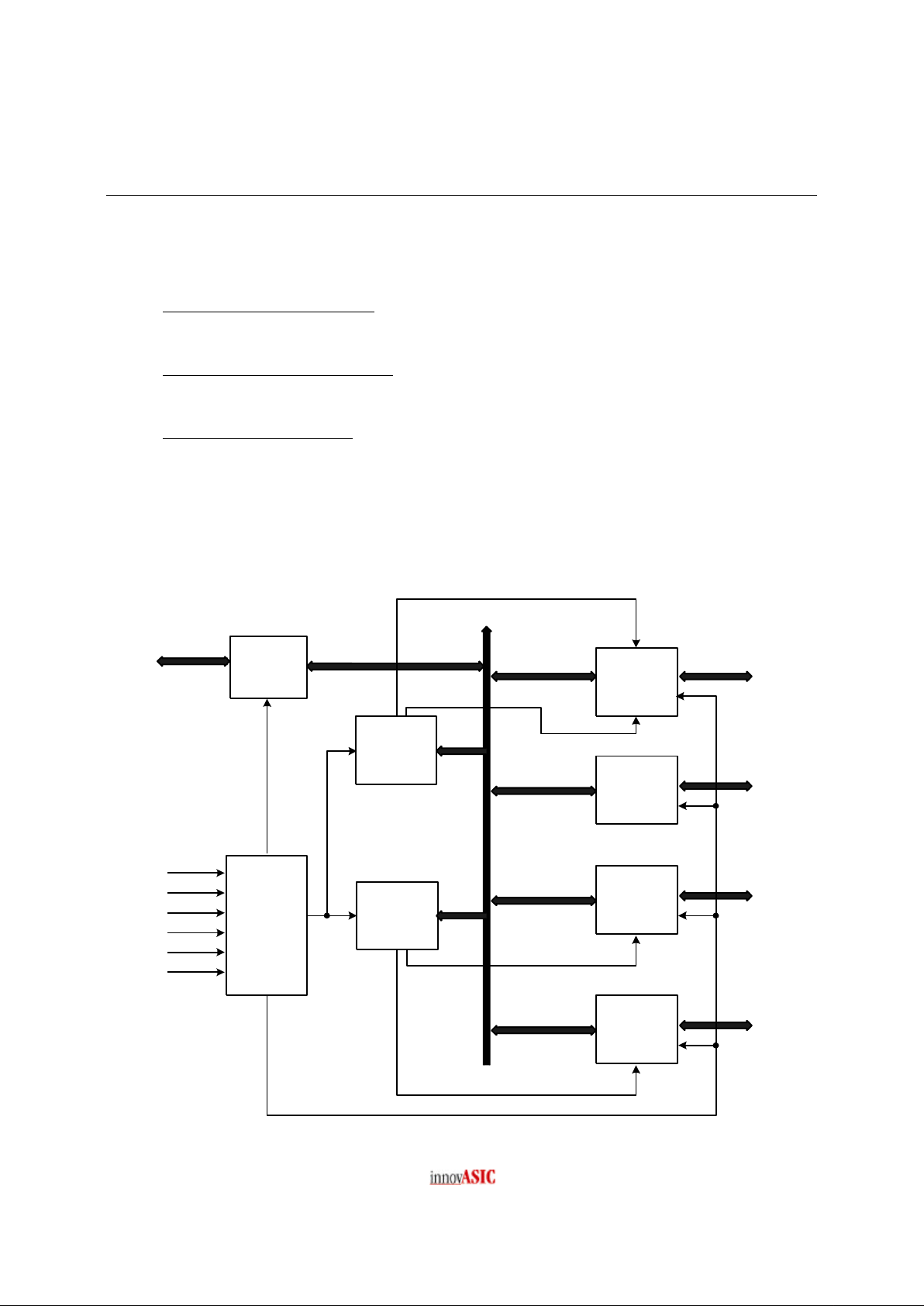

A block diagram is shown in Figure 1.

Functional Block Diagram

Figure 1

DATA BUS

BUFFER

GROUP A

CONTROL

GROUP B

CONTROL

8 BIT INTERNAL

DATA BUS

GROUP A

PORT A

(8)

GROUP A

PORT C

UPPER (4)

GROUP B

PORT C

LOWER

(4)

GROUP B

PORT B

(8)

CONTROL

REGISTER AND

LOGIC

A0

A1

CS_n

RESET

RD_n

WR_n

D7:D0

I/O

PA7:PA0

I/O

PC7:PC4

I/O

PC3:PC0

I/O

PB7:PB0

Loading...

Loading...