INOVC IA8237-PDW40I, IA8237-PLC40C, IA8237-PLC40I, IA8237-PDW40C Datasheet

Page 1 of 4

IA8237 Advanced Information Sheet

Programmable DMA Controller

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

FEATURES

• Form, Fit, and Function Compatible with the Intel 8237A and Harris

82C37A

• Packaging options available: 40 Pin Plastic Dip or 44 Pin Plastic Leaded

Chip Carrier

• Static Read/Write or Handshaking Modes

• Direct Bit Set/Reset Capability

• Memory-to-Memory Transfers

The IA8237 uses innovASIC’s innovative new f 3 Program to provide industry with parts that

other vendors have declared obsolete. By specifying parts through this program a customer is

assured of never having a component become obsolete again. This advanced information sheet

assumes the original part has been designed in, and so provides a summary of capabilities only. For

new designs contact innovASIC for more detailed information.

Intel is a registered trademark of Intel Corporation

Harris is a copyright trademark of Harris Corporation

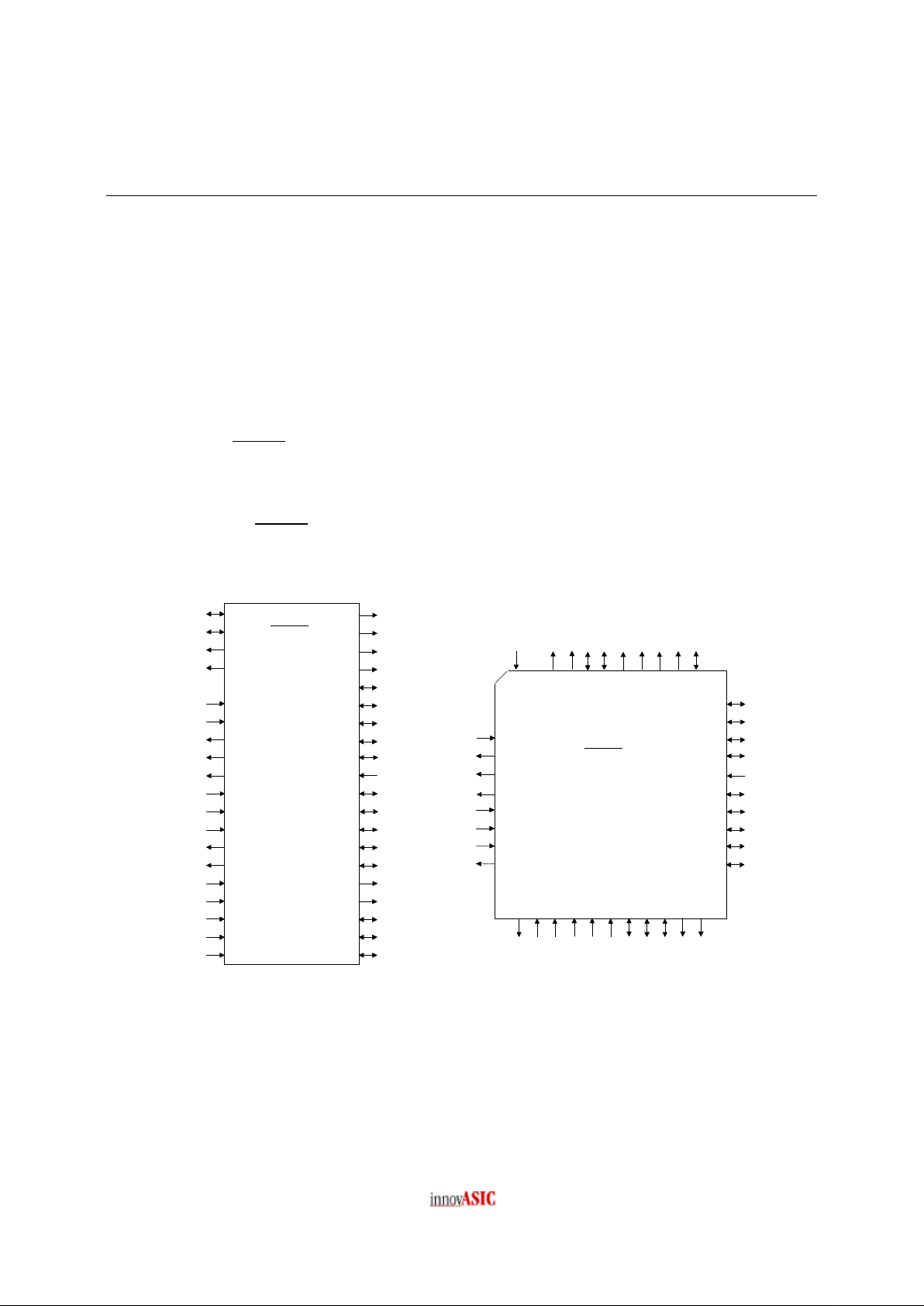

Package Pinout

(6)

(1)

(2)

(3)

(4)

(5)

(7)

(8)

(9)AEN

(10)HRQ

(11)CS_n

(12)CLK

(13)RESET

(14)

40 Pin DIP

IA8237

A0

VCC

DB0

DB1

(20)VSS

(15)DACK3

(16)DREQ3

(17)

DREQ2

(18)DREQ1

(19)DREQ0

(21)

(22)

(23)

(24)

DB6

DB7

(40)

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

(28)

(27)

(26)

(25)

DACK2

DACK1

DB5

DB4

DACK0

DB2

DB3

A2

A1

EOP_n

A3

A5

A4

A7

A6

READY

IOR_n

IOW_n

MEMR_n

MEMW_n

N. C.

HLDA

ADSTB

A3

DB1

DB0

VCC

A1

A2

N. C.

DB4

DB3

DB2

A0

44 Pin LCC

IA8237

(12)HRQ

(7)N. C.

(8)N. C.

(9)HLDA

(10)ADSTB

(11)AEN

(13)CS_n

(14)CLK

(15)RESET

(16)DACK2

(17)N. C.

DREQ2

DACK3

DREQ3

(6)

(5)

(4)

(3)

(2)

(1)

(44)

(43)

(42) A5

(41) A4

(40) EOP_n

N. C.

READY

(34)

(39)

(38)

(37)

(36)

(35)

(33)

(32)

(31)

(30)

(29)

(18)

(19)

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

A7

A6

IOW_n

IOR_n

MEMW_n

MEMR_n

DREQ0

DREQ1

DB7

VSS

DB5

DB6

DACK0

DACK1

Page 2 of 4

IA8237 Advanced Information Sheet

Programmable DMA Controller

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

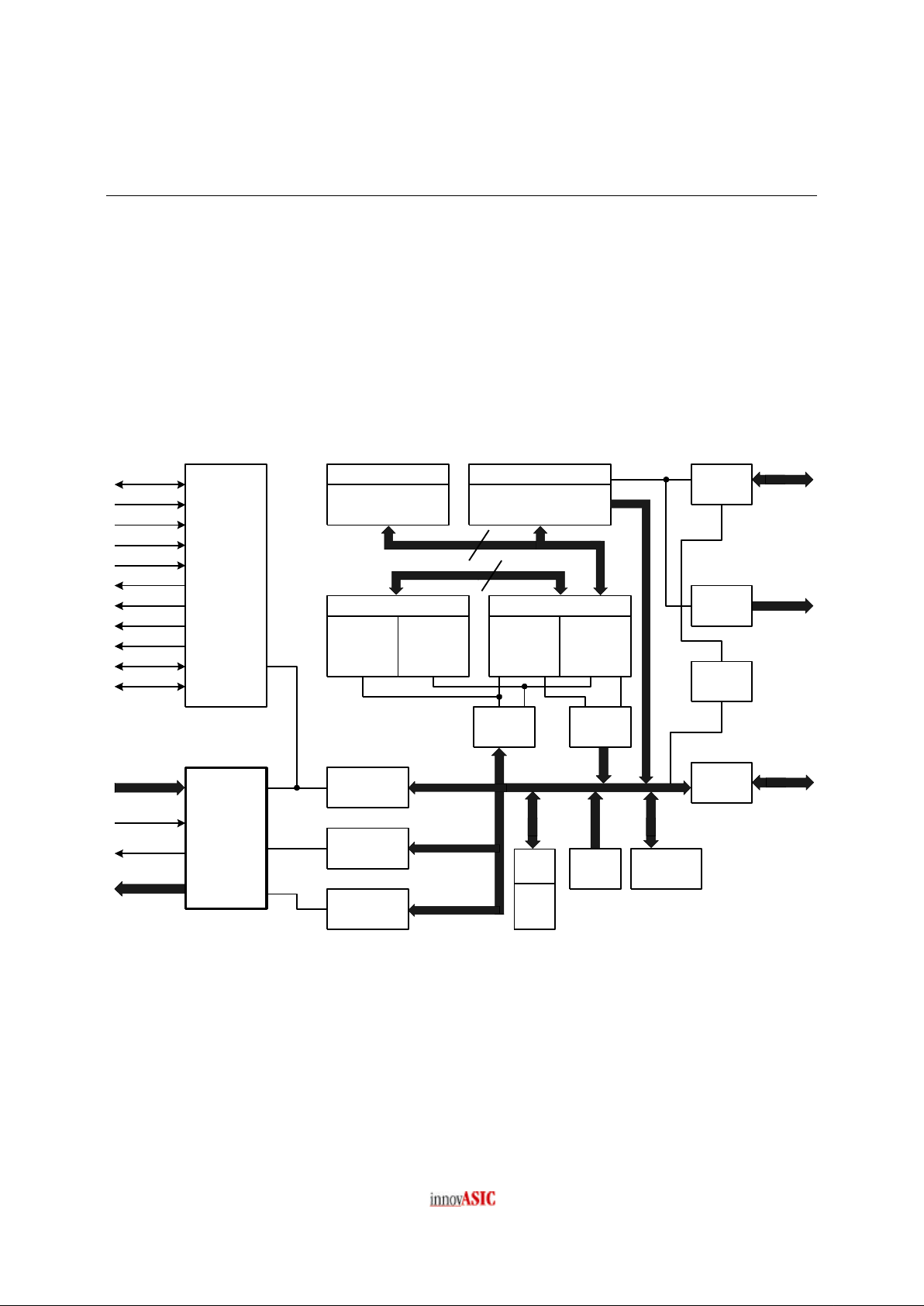

The IA8237 is a programmable direct memory access (DMA) mega-function designed to be

functionally equivalent to the Intel 8237A and Harris 82C37A devices. The A8237 controls data

transfers between memory and peripherals, memory-to-memory transfers, and block memory

initialization. Four independently programmable channels are available, and requests may be

generated via hardware or software.

A block diagram is shown in Figure 1.

Functional Block Diagram

Figure 1

TIMING

AND

CONTROL

ADSTB

MEMR_n

MEMW_n

IOR_n

IOW_n

CS_n

READY

CLK

AEN

EOP_n

RESET

PRIORITY

ENCODER

AND

ROTATING

PRIORITY

LOGIC

HDLA

HRQ_n

DREQ0_n

:

DREQ3_n

DACK0

:

DACK3

COMMAND

MASK

REQUEST

DECREMENTOR

TEMP WORD

COUNT REG

INC/DECREMENTOR

TEMP ADDRESS

REG

BASE

ADDRESS

BASE

WORD

COUNT

READ BUFFER

CURRENT

ADDRESS

CURRENT

WORD

COUNT

READ WRITE BUFFER

WRITE

BUFFER

READ

BUFFER

IO

BUFFER

TEMPORARYSTATUS

MODE

READ

WRITE

COMMAND

CONTROL

OUTPUT

BUFFER

IO

BUFFER

A0 : A3

A4 : A7

DB0 : DB7

16

16

INTERNAL DATA

BUS

Loading...

Loading...