INOVC IA6850-PDW24C, IA6850-PDW24I Datasheet

Page 1 of 4

IA6850 Advanced Information Sheet

Asynchronous Communications Interface Adapter (ACIA)

FEATURES

• Form, Fit, and Function Compatible with the Motorola MC6850

• Packaging option available: 24 Pin Plastic DIP

• Programmable Word Length, Stop Bits, and Parity

• Error Detection

• Divide by 1, 16, or 64 operation

• TBD Equivalent gates.

The IA6850 uses innovASIC’s innovative new f 3 Program to provide industry with parts that other

vendors have declared obsolete. By specifying parts through this program a customer is assured of

never having a component become obsolete again. This advanced information sheet assumes the

original part has been designed in, and so provides a summary of capabilities only. For new designs

contact innovASIC for more detailed information.

Motorola is a copyright trademark of Motorola, Inc.

VSS

RXDATA

RXCLK

TXCLK

RTS_n

TXDATA

IRQ_n

CS0

Package Pinout

(1)

(2)

24 Pin DIP

(3)

(4)

(5)

(6)

(7)

(8)

(9)CS2_n

(10)CS1

(11)RS

(12)VCC

IA6850

(24)

(23)

(22)

(21)

(20)

(19)

(18)

(17)

(16)

(15)

(14)

(13)

CTS_n

DCD_n

D0

D1

D2

D3

D4

D5

D6

D7

E

R/W_n

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

Page 2 of 4

IA6850 Advanced Information Sheet

Asynchronous Communications Interface Adapter (ACIA)

The IA6850 is an ACIA megafunction used to interface a microprocessor to a serial communications

channel, and is functionally equivalent to the Motorola MC6850. This function receives and transmits

data in a variety of configurations including 7 or 8 bit data words, odd, even, or nor parity, and 1 or 2

stop bits.

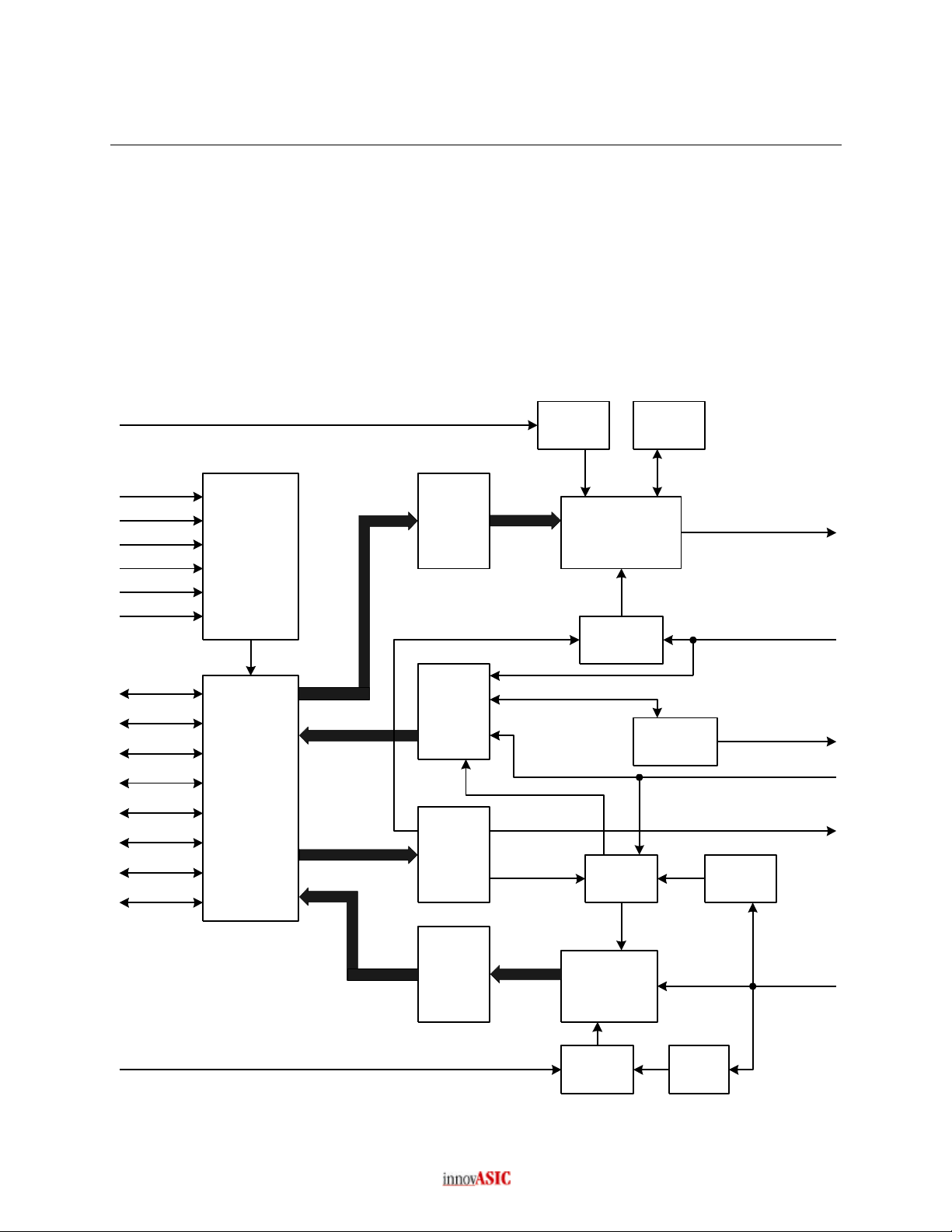

A block diagram is shown in Figure 1.

Functional Block Diagram

Figure 1

TXCLK

R/W_n

CS0

CS1

CS2_n

RS

E

D0

D1

D2

D3

D4

D5

D6

D7

CHIP

SELECT

AND

READ/WRITE

CONTROL

DATA

BUS

BUFFERS

TRANSMIT

DATA

REGISTER

STATUS

REGISTER

CONTROL

REGISTER

CLOCK

GEN

TRANSMIT

SHIFT

REGISTER

TRANSMIT

CONTROL

RECEIVE

CONTROL

PARITY

GEN

INTERRUPT

LOGIC

TXDATA

CTS_n

IRQ_n

DCD_n

RTS_n

PARITY

CHECK

RXCLK

RECEIVE

DATA

REGISTER

Copyright 1999, InnovASIC Inc.

Customer Specific IC Solutions

RECEIVE

SHIFT

REGISTER

CLOCK

GEN

RXDATA

SYNC

LOGIC

Loading...

Loading...