INOVC IA6805E2-PDW40I, IA6805E2-PLC44I Datasheet

IA6805E2 Data Sheet

Microprocessor Unit As of Production Version 00

FEATURES

• Form, Fit, and Function Compatible with the Harris CDP6805E2CE and

Motorola MC146805E2

• Internal 8-bit Timer with 7-Bit

Programmable Prescaler

• On-chip Clock

• Memory Mapped I/O

• Versatile Interrupt Handling

• True Bit Manipulation

• Bit Test and Branch Instruction

• Vectored Interrupts

• Power-saving STOP and WAIT Modes

• Fully Static Operation

• 112 Bytes of RAM

The IA6805E2 is a "plug-and-play" drop -in replacement for the original IC. innovASIC produces

replacement ICs using its MILESTM, or Managed IC Lifetime Extension System, cloning technology. This

technology produces replacement ICs far more complex than "emulation" while ensuring they are compatible

with the original IC. MILESTM captures the design of a clone so it can be produced even as silicon

technology advances. MILESTM also verifies the clone against the original IC so that even the

"undocumented features" are duplicated. This data sheet documents all necessary engineering information

about the IA6805E2 including functional and I/O descriptions, electrical characteristics, and applicable

timing.

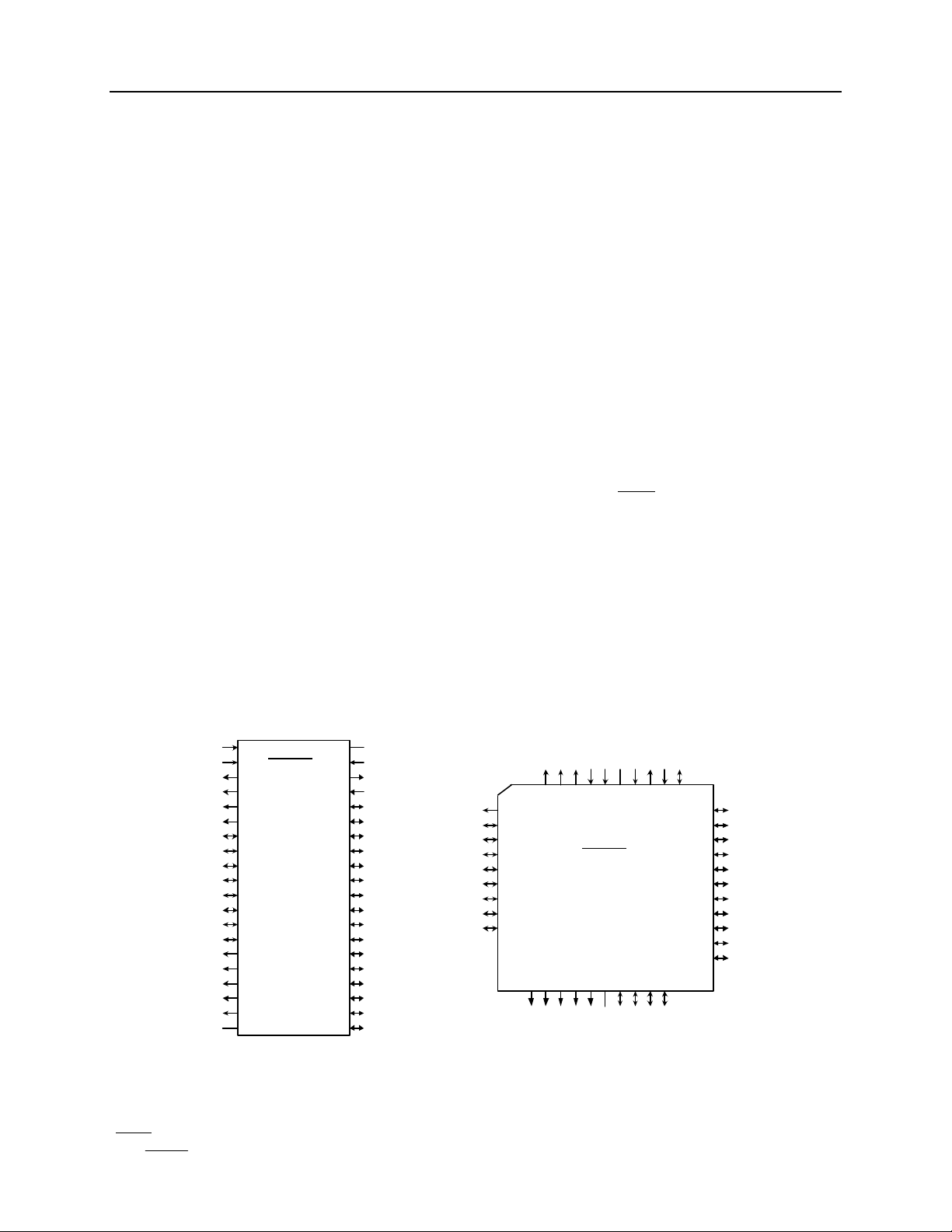

Package Pinout

IRQ_N

PA6

PA4

PA3

PA0

A10

(1)RESET_N

IA6805E2

(2)

40 Pin DIP

(3)

LI

(4)DS

(5)RW_N

(6)AS

(7)PA7

(8)

(9)PA5

(10)

(11)

(12)PA2

(13)PA1

(14)

(15)A12

(16)A11

(17)

(18)A9

(19)A8

(20)VSS

(40)

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

(28)

(27)

(26)

(25)

(24)

(23)

(22)

(21)

VDD

OSC1

OSC2

TIMER

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

B0

B1

B2

B3

B4

B5

B6

B7

PA6

RW_N

NC

DS

(6)

(5)

(18)

A12

(19)

A11

(4)

(20)

A10

(7)AS

(8)PA7

(9)

(10)PA5

(11)PA4

(12)PA3

(13)PA2

(14)PA1

(15)PA0

(16)NC

(17)NC

IRQ_N

RESET_N

LI

(3)

(2)

(1)

IA6805E2

44 Pin LCC

(21)

(22)

(23)

A8A9B7

VSS

VDD

(44)

(24)

OSC1

(43)

(25)

(42) OSC2

(26)

B5B6B4

PB0

(41) TIMER

(27)

(40)

(28)

NC

(39)

(38)

(37)

(36)

(35)

(34)

(33)

(32)

(31)

(30)

(29)

PB1

PB2

PB3

PB4

PB5

PB6

PB7

B0

B1

B2

B3

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 1 of 31 1-888-824-4184

IA6805E2 Data Sheet

Microprocessor Unit As of Production Version 00

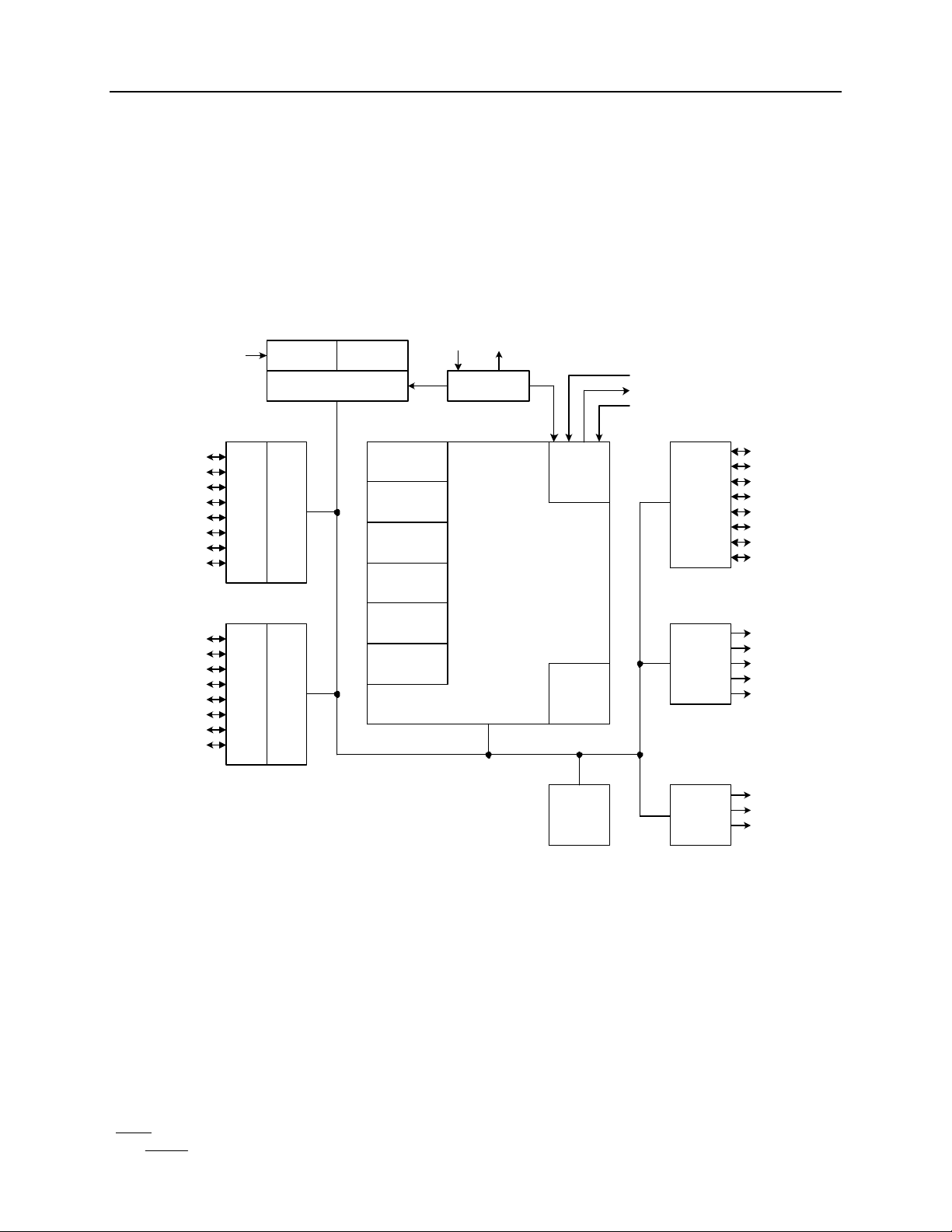

Description

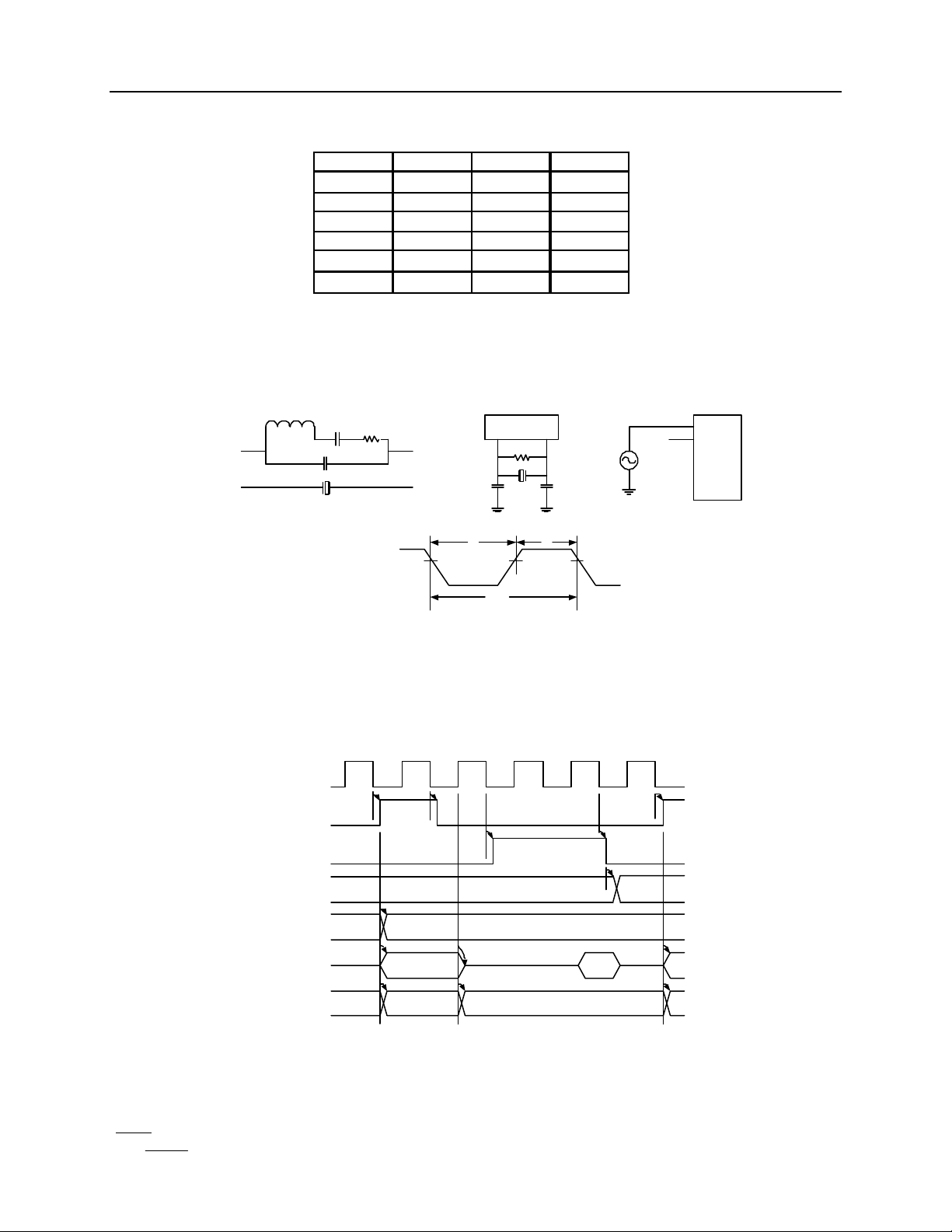

The IA6805E2 (CMOS) Microprocessor Unit (MPU) is a low cost, low power MPU. It features a

CPU, on-chip RAM, parallel I/O compatibility with pins programmable as input or output. The

following paragraphs will further describe this system block diagram and design in more detail.

PORT

A

I/O

LINES

PORT

B

I/O

LINES

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

TIMER

PA0

PORT

A

REG

PORT

B

REG

PRESCALER

TIMER CONTROL

DATA

DIR

REG

DATA

DIR

REG

TIMER/

COUNTER

ACCUMULATOR

8 A

REGISTER

8

CONDITION

REGISTER

5

POINTER

6

PROGRAM

COUNTER

5

PROGRAM

COUNTER

8

INDEX

CODE

STACK

HIGH

LOW

OSC1 OSC2

OSCILLATOR

X

CC

SP

PCH

PCL

CPU

RESET_N

CPU

CONTROL

ALU

112x8

RAM

IRQ_N

LI

B0

B1

B2

MUX

BUS

DRIVE

ADDRESS

DRIVE

BUS

CONTROL

B3

B4

B5

B6

B7

A8

A9

A10

A11

A12

AS

DS

RW_N

MULTIPLEXED

ADDRESS

DATA

BUS

ADDRESS

BUS

ADDRESS STROBE

DATA STROBE

READ/WRITE

Figure 1. System Block Diagram

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 2 of 31 1-888-824-4184

IA6805E2 Data Sheet

SS

RESET_n

IRQ_n

LI

DS

RW_n

AS

PA0-PA7/PB0-PB7

.

A8-A12

B0-B7

OSC1, OSC2

Microprocessor Unit As of Production Version 00

I/O Signal Description

The table below describes the I/O characteristics for each signal on the IC. The signal names

correspond to the signal names on the pinout diagrams provided.

SIGNAL NAME I/O

VDD and V

(Power and Ground)

(Reset)

(Interrupt Request)

(Load Instruction)

(Data Strobe)

(Read/Write)

(Address Strobe)

(Input/Output Lines)

N/A

I

I

O

O

O

O

I/O

DESCRIPTION

Source: These two pins provide power to the chip. VDDprovides +5 volts (±0.5) power

and VSS is ground.

TTL:Input pin that can be used to reset the MPU's internal state by pulling the reset_n

pin low.

TTL: Input pin that is level and edge sensitive. Can be used to request an interrupt

sequence.

TTL with slew rate control: Output pin used to indicate that a next opcode fetch is in

progress. Used only for certain debugging and test systems. Not connected in normal

operation. Overlaps Data Strobe (DS) signal. This output is capable of driving one

standard TTL load and 50pF.

TTL with slew rate control: Output pin used to transfer data to or from a peripheral or

memory. DS occurs anytime the MPU does a data read or write and during data transfer

to or from internal memory. DS is available at f

or STOP mode. This output is capable of driving one standard TTL load and 130pF.

TTL with slew rate control: Output pin used to indicate the direction of data transfer

from internal memory, I/O registers, and external peripheral devices and memories.

Indicates to a selected peripheral whether the MPU is to read (RW_n high) or write

(RW_n low) data on the next data strobe. This output is capable of driving one standard

TTL load and 130pF.

TTL with slew rate control: Output strobe used to indicate the presence of an address

on the 8-bit multiplexed bus. The AS line is used to demultiplex the eight least significant

address bits from the data bus. AS is available at f

WAIT or STOP modes. This output is capable of driving one standard TTL load and

130pF.

TTL with slew rate control: These 16 lines constitute Input/Output ports A and B.

Each line is individually programmed to be either an input or output under software

control of the Data Direction Register (DDR) as shown below in Table 1 and Figure 2

The port I/O is programmed by writing the corresponding bit in the DDR to a "1" for

output and a "0" for input. In the output mode the bits are latched and appear on the

corresponding output pins. All the DDR's are initialized to a "0" on reset. The output

port registers are not initialized on reset. Each output is capable of driving one standard

TTL load and 50pF.

÷ 5 when the MPU is not in the WAIT

OSC

÷ 5 when the MPU is not in the

OSC

TTL with slew rate control: These five outputs constitute the higher order nonmultiplexed address lines. Each output is capable of driving one standard TTL load and

(High Order Address Lines)

(Address/Data Bus)

Timer I

(System Clock)

Crystal

External Clock

O

I/O

I/O

130pF.

TTL with slew rate control: These bi-directional lines constitute the lower order

addresses and data. These lines are multiplexed with address present at address strobe

time and data present at data strobe time. When in the data mode, these lines are bidirectional, transferring data to and from memory and peripheral devices as indicated by

the RW_n pin. As outputs,these lines are capable of driving one standard TTL load and

130pF.

TTL: Input used to control the internal timer/counter circuitry.

TTL Oscillator input/output: These pins provide control input for the on-chip clock

oscillator circuits. Either a crystal or external clock is connected to these pins to provide

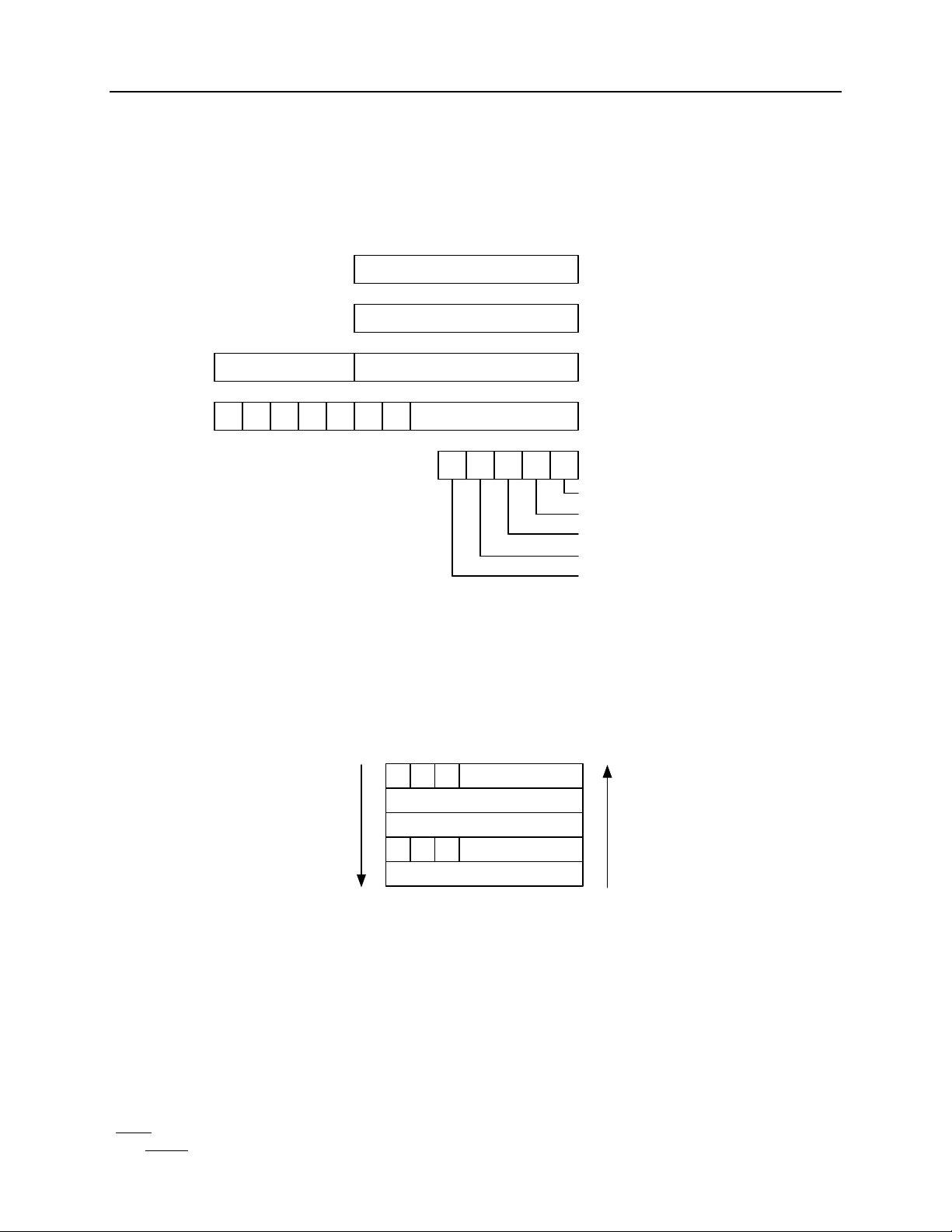

a system clock. The crystal connection is shown in Figure 3 . The OSC1 to bus

transitions for system designs using oscillators slower than 5MHz is shown in Figure 4 .

The circuit shown in Figure 3 is recommended when using a crystal. An external CMOS

oscillator is recommended when using crystals outside the specified ranges. To minimize

output distortion and start-up stabilization time, the crystal and components should be

mounted as close to the input pins as possible.

When an external clock is used, it should be applied to the OSC1 input with the OSC2

input not connected, as shown in Figure 3 .

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 3 of 31 1-888-824-4184

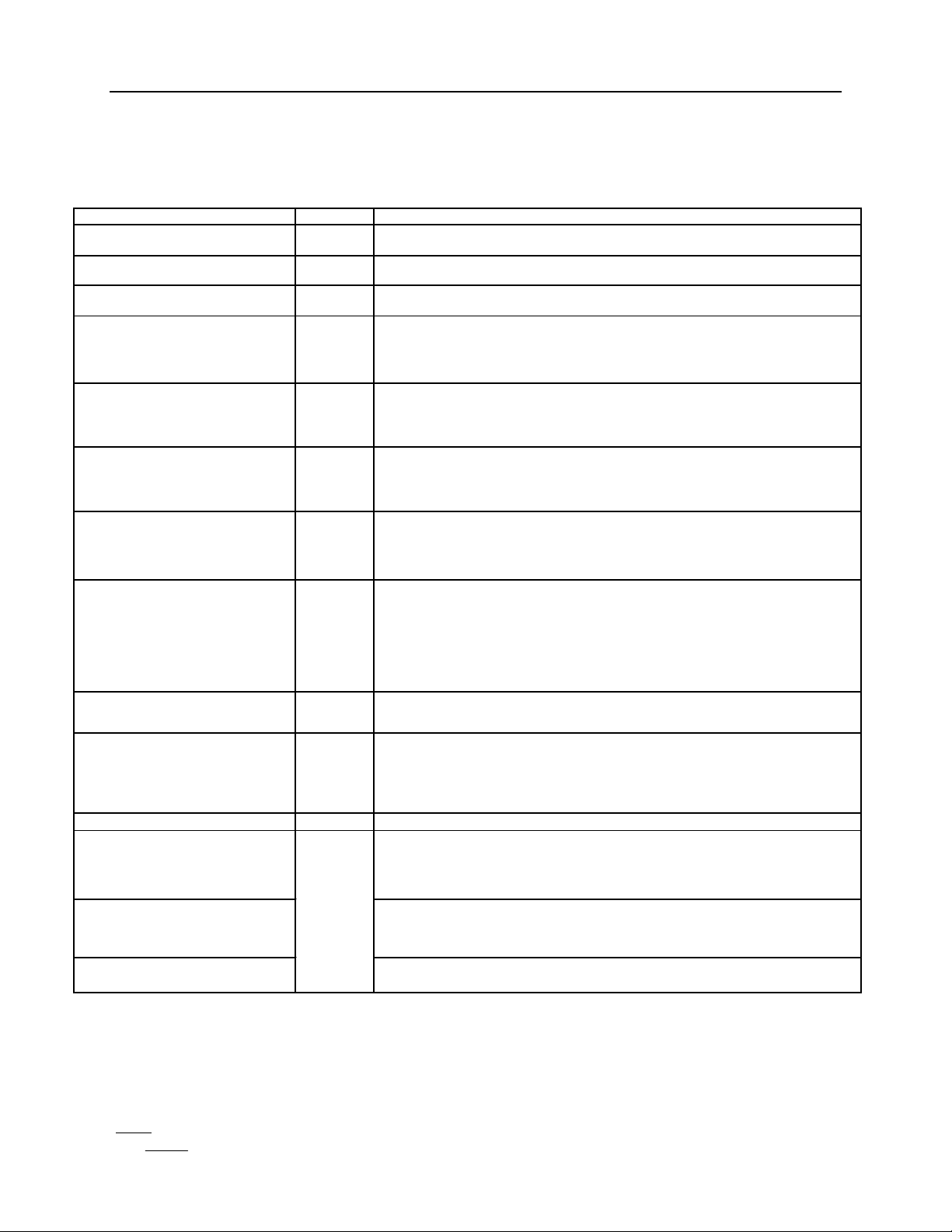

Table 1

IA6805E2 Data Sheet

Microprocessor Unit As of Production Version 00

I/O Pin Functions

R/W-n DDR I/O Pin Functions

0 0

0 1

1 0

1 1

I/O Port Circuitry and Register Configuration:

TO

The I/O pin is in input mode. Data is

written into the output data latch.

Data is written into the output data latch and

output to the I/O pin.

The state of the I/O pin is read.

the I/O pin is in an output mode. The

output data latch is read.

DATA DIRECTION

REGISTER

BIT

AND

FROM

CPU

DATA DIRECTION

A(B)

REGISTER

PORT A(B)

REGISTER

LATCHED

OUTPUT

DATA BIT

7 456 3 012

PIN

DDA7

(DDB7)

PA7

(PB7)

DDA6

(DDB6)

PA6

(PB6)

DDA5

(DDB5)

PA5

(PB5)

INPUT

REG

BIT

DDA4

(DDB4)

PA4

(PB4)

DDA3

(DDB3)

PA3

(PB3)

INPUT

I/O

PIN

DDA2

(DDB2)

PA2

(PB2)

OUTPUT

DDA1

(DDB1)

PA1

(PB1)

DDA0

(DDB0)

PA0

(PB0)

I/O

PIN

$0004 ($0005)

$0000 ($0001)

Figure 2. PA0-PA7/PB0-PB7 (Input/Output Lines)

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 4 of 31 1-888-824-4184

IA6805E2 Data Sheet

Ω75Ω

Ω

OSC1

OSC2

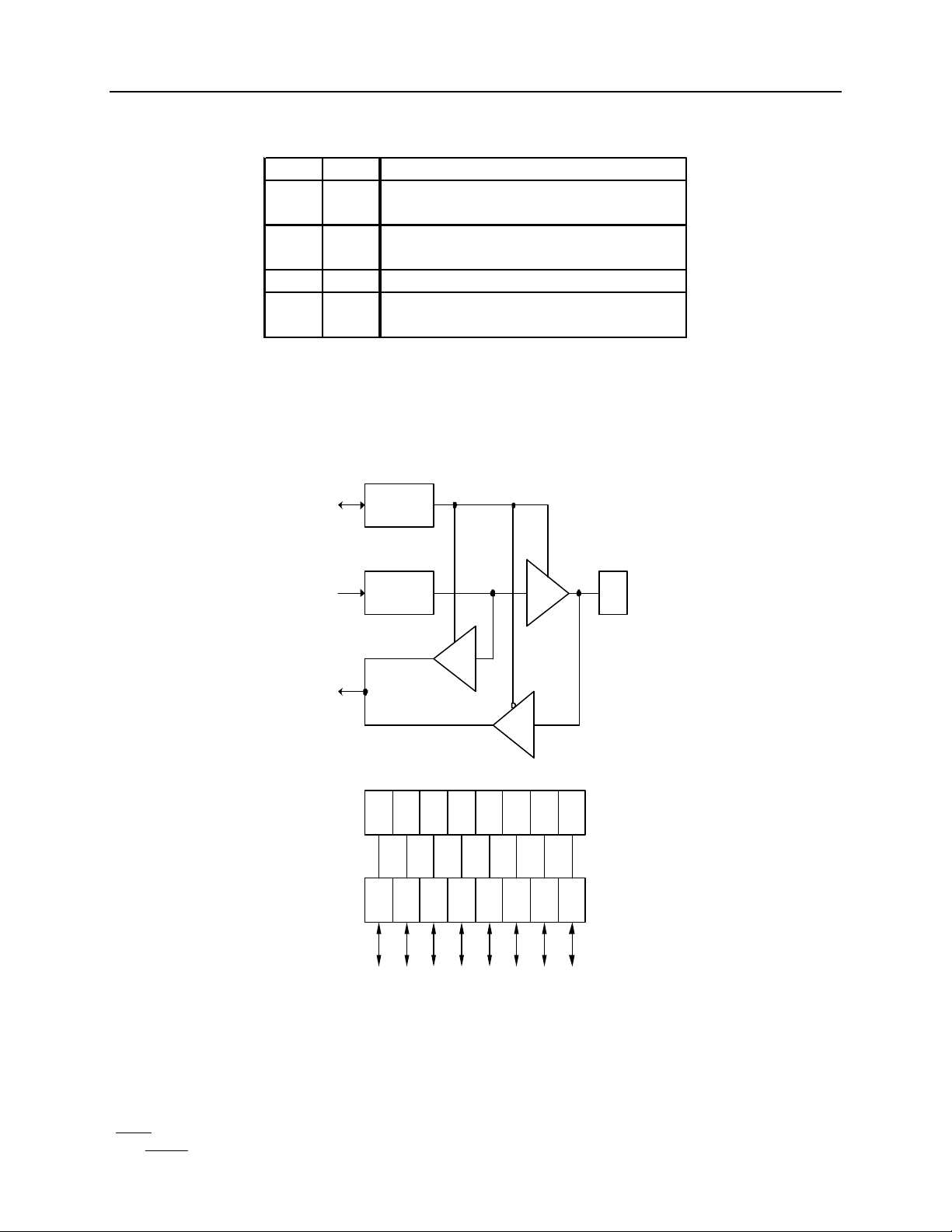

Figure 3. OSC1, OSC2 (System Clock)

Microprocessor Unit As of Production Version 00

Crystal Parameters Representative Frequencies:

5.0 MHz 4.0 MHz 1.0 MHz

RS max 50

C0 8 pF 7 pF 5 pF

C1 0.02 pF 0.012 pF 0.008 pF

Q 50 k 40 k 30 k

C

C

Oscillator Connections:

CRYSTAL CIRCUIT CRYSTAL OSCILLATOR CONNECTIONS

L

C1

38

38

OSC2

C0

15-30 pF 15-30 pF 15-40 pF

15-25 pF 15-25 pF 15-30 pF

RS

39

OSC1OSC2

39

OSC1

ia6805E2

38 39

OSC2 OSC1

C

10 M

OSC2

400

OSC1

39

OSC2

38

Ω

C

OSC1

NC

IA6805E2

t

OSC1 PIN

OL

t

t

OLOL

OSC1 to Bus Transitions Timing Waveforms:

OSC1

AS

DS

RW_n

A[12:8]

B[7:0]

MPU READ

B[7:0]

MPU WRITE

*READ DATA "LATCHED" ON DS FALL

MUX ADDR

MUX ADDR MPU WRITE DATA

t

OH

MPU

READ

DATA*

Figure 4. OSC1, OSC2 (System Clock)

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 5 of 31 1-888-824-4184

IA6805E2 Data Sheet

Microprocessor Unit As of Production Version 00

Functional Description

Memory:

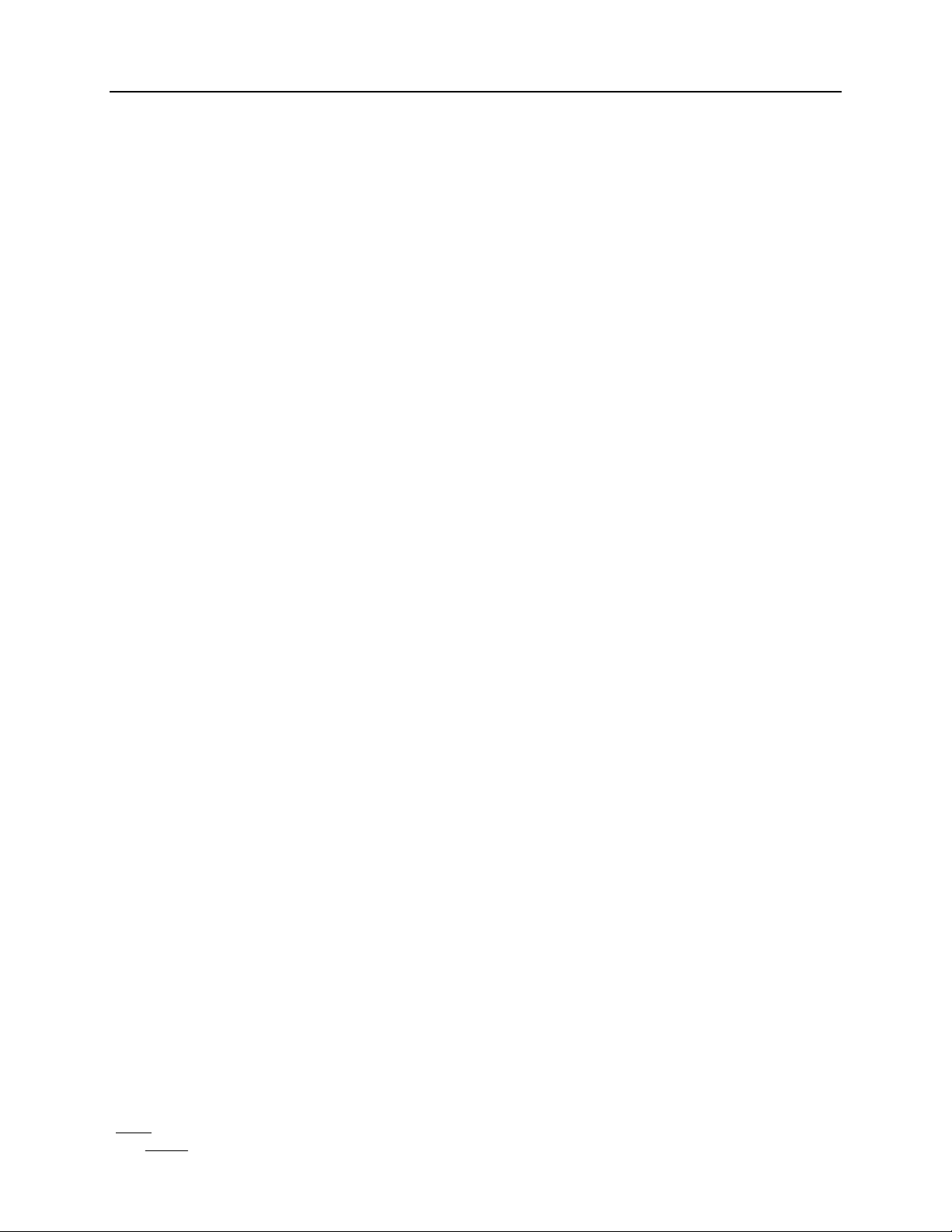

The MPU is capable of addressing 8192 bytes of memory and I/O registers. The locations

are divided into internal memory space and external memory space as shown in Figure 5.

The first 128 bytes of memory contain internal port I/O locations, timer locations, and 112

bytes of RAM. The MPU can read from or write to any of these locations. During program

reads from on chip locations, the MPU accepts data only from the addressed on chip

location. Any read data appearing on the input bus is ignored. The shared stack area is used

during interrupts or subroutine calls. A maximum of 64 bytes of RAM is available for stack

usage. The stack pointer is set to $7f at power up. The unused bytes of the stack can be used

for data storage or temporary work locations, but care must be taken to prevent it from

being overwritten due to stacking from an interrupt or subroutine call.

ACCESS VIA

PAGE 0

DIRECT

ADDRESS

INTERRUPT

VECTORS

0

I/O PORTS

TIMER RAM

127

128

255

256

EXTERNAL MEMORY

SPACE (8064 BYTES)

TIMER INTERRUPT FROM WAIT STATE ONLY

TIMER INTERRUPT

EXTERNAL INTERRUPT

SWI

8191

RESET

$0000

$007F

$0080

$00FF

$0100

$1FF6 - $1FF7

$1FF8 - $1FF9

$1FFA - $1FFB

$1FFC - $1FFD

$1FFE - $1FFF

0

1

2

3

4

5

6

7

8

9

10

15

16

63

64

127

PORT A DATA REGISTER

PORT B DATA REGISTER

EXTERNAL MEMORY SPACE

EXTERNAL MEMORY SPACE

PORT A DATA DIRECTION REGISTER

PORT B DATA DIRECTION REGISTER

EXTERNAL MEMORY SPACE

EXTERNAL MEMORY SPACE

TIMER DATA REGISTER

TIMER CONTROL REGISTER

EXTERNAL MEMORY SPACE

(112 BYTES)

RAM

STACK

(64 BYTES MAX)

Figure 5. Memory Map

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 6 of 31 1-888-824-4184

IA6805E2 Data Sheet

Figure 6. Programming Model

Microprocessor Unit As of Production Version 00

Registers:

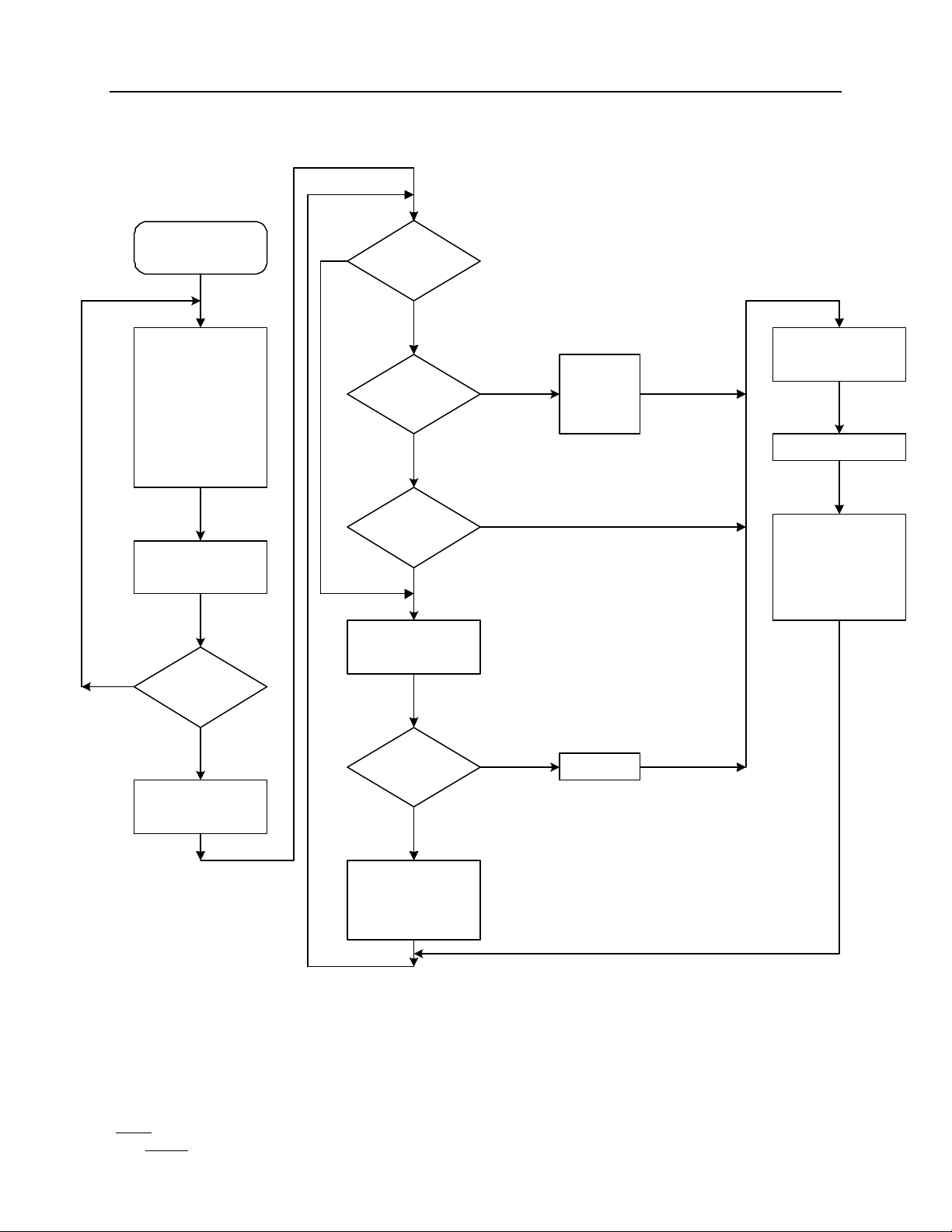

The following paragraphs describe the registers contained in the MPU. Figure 6 shows the

programming model an d Figure 7 shows the interrupt stacking order.

7 0

A

7 0

X

12 078

PCH

12 6 0

PCL

SP10 0 0 0 0 0

4

H I N Z C

CC

ACCUMULATOR

INDEX REGISTER

PROGRAM COUNTER

STACK POINTER

0

CONDITION CODE REGISTER

CARRY/BORROW

ZERO

NEGATIVE

INTERRUPT MASK

HALF CARRY

NOTE: Since the stack pointer decrements during pushes, the PCL is stacked first,

followed by PCH, etc. Pulling from the stack is in the reverse order.

STACK

INCREASING MEMORY

ADDRESSES

UNSTACK

CONDITION CODE

R

E

T

U

R

N

111

ACCUMULATOR

INDEX REGISTER

REGISTER

PCH000

PCL

I

N

T

E

R

R

U

P

T

DECREASING MEMORY

ADDRESSES

Figure 7. Interrupt Stacking Order

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 7 of 31 1-888-824-4184

IA6805E2 Data Sheet

Microprocessor Unit As of Production Version 00

A(Accumulator):

The accumulator is an 8-bit register used to hold operands and results of arithmetic

calculations or data manipulations.

X(Index Register):

The index register is an 8-bit register used during the indexed addressing mode. It contains

an 8-bit value used to create an effective address. The index register may also be used as a

temporary storage area when not performing addressing operations.

PC(Program Counter):

The program counter is a 13-bit register that holds the address of the next instruction to be

performed by the MPU.

SP(Stack Pointer):

The stack pointer is a 13-bit register that holds the address of the next free location on the

stack. During an MPU reset or the reset stack pointer (RSP) instruction, the stack pointer is

set to location $007f. The seven most significant bits of the stack pointer are permanently

set to 0000001. They are appended to the six least significant register bits to produce an

address range down to location $0040. The stack pointer gets decremented as data is pushed

onto the stack and incremented as data is removed from the stack. The stack area of RAM is

used to store the return address on subroutine calls and the machine state during interrupts.

The maximum number of locations for the stack pointer is 64 bytes. If the stack goes

beyond this limit the st ack pointer wraps around and points to its upper limit thereby losing

the previously stored information. Subroutine calls use 2 bytes of RAM on the stack and

interrupts use 5 bytes.

CC(Condition code Register):

The condition code register is a 5-bit register that indicates the results of the instruction just

executed. The bit is set if it is high. A program can individually test these bits and specific

actions can be taken as a result of their states. Following is an explanation of each bit.

C(Carry Bit):

The carry bit indicates that a carry or borrow out of the Arithmetic Logical Unit (ALU)

occurred during the last arithmetic instruction. This bit is also modified during bit test, shift,

rotate, and branch types of instructions.

Z(Zero Bit):

The zero bit indicates the result of the last arithmetic, logical, or data manipulation was zero.

N(Negative Bit):

The negative bit indicates the result to the last arithmetic, logical, or data manipulation was

negative (bit 7 in the result is high).

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 8 of 31 1-888-824-4184

IA6805E2 Data Sheet

Microprocessor Unit As of Production Version 00

I(Interrupt Mask Bit)

The interrupt mask bit indicates that both the external interrupt and the timer interrupt are

disabled (masked). If an interrupt occurs while this bit is set, the interrupt is latched and is

processed as soon as the interrupt bit is cleared.

H(Half Carry Bit)

The half carry bit indicates that a carry occurred between bits 3 and 4 of the ALU during an

ADD or ADC operation.

Resets:

The MPU can be reset by initial power up or by the external reset pin (reset_n).

POR(Power On Reset)

Power on reset occurs on initial power up. It is strictly for power initialization conditions

and should not be used to detect drops in the power supply voltage. There is a 1920 t

time out delay from the time the oscillator is detected. If the reset_n pin is still low at the

end of the delay, the MPU will remain in the reset state until the external pin goes high.

CYC

Reset_n

The reset_n pin is used to reset the MPU. The reset pin must stay low for a minimum of t

to guarantee a reset. The reset_n pin is provided with a Schmitt Trigger to improve noise

immunity capability.

Interrupts:

The MPU can be interrupted with the external interrupt pin (irq_n), the internal timer

interrupt request, or the software interrupt instruction. When any of these interrupts occur,

normal processing is suspended at the end of the current instruction execution. The

processor registers are saved on the stack (stacking order shown in Figure 7) and the

interrupt mask (I) is set to prevent additional interrupts. Normal processing resumes after

the RTI instruction causes the register contents to be recovered from the stack. When the

current instruction is completed, the processor checks all pending hardware interrupts and if

unmasked (I bit clear) proceeds with interrupt processing. Otherwise, the next instruction is

fetched and executed. Masked interrupts are latched for later interrupt service. External

interrupts hold higher priority than timer interrupts. At the end of an instruction execution,

if both an external interrupt and timer interrupt are pending, the external interrupt is

serviced first. The SWI gets executed with the same priority as any other instruction if the

hardware interrupts are masked (I bit set). Figure 8 shows the Reset and Interrupt processing

flowchart.

cyc

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 9 of 31 1-888-824-4184

IA6805E2 Data Sheet

Figure 8. Reset and Interrupt Processing Flowchart

Microprocessor Unit As of Production Version 00

RESET_N

PIN = LOW

RESET

I_CC <= 1

SP <= $007F

DDRs <= 0

CLR IRQ_N LOGIC

TIMER <= $FF

PRESCALER <= $7F

TCR <= $7f

PUT 1FFE,1FFF ON

ADDRESS BUS

Y

RESET

N

LOAD PC

FROM

1FFE/1FFF

IN

?

RESET_N

PIN = LOW

SET

I BIT

?

CLEAR

IRQ_N

EDGE

?

N

TCR6=0

AND

TCR7=1?

N

FETCH

INSTRUCTION

IS FETCHED

INSTRUCTION

AN SWI?

N

STACK

CLEAR

IRQ_N

REQUEST

LATCH

Y

Y

PC+1=>PC

IRQ_NY

TIMER

SWI

PC, X, A, CC

I <= 1

LOAD PC FROM:

SWI: 1FFC/1FFD

IRQ_N: 1FFA/1FFB

TIMER: 1FF8/1FF9

TIMER WAIT:1FF6/

1FF7

EXECUTE ALL

INSTRUCTION

CYCLES

Copyright 2002 ENG21108140100 www.innovasic.com

innovASIC Customer Support:

The End of Obsolescence Page 10 of 31 1-888-824-4184

Loading...

Loading...